PARALLEL MAZE ROUTING ALCORITHMS ON A HYPERCUBE MULTICOMPUTER

## A THESIS

SUBMITTED TO THE DEPARTMENT OF COMPUTER ENGINEERING AND INFORMATION SCIENCE AND THE INSTITUTE OF ENGINEERING AND SCHENCE OF BILKENT UNIVERSITY IN PARTIAL FULFILIMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

## PARALLEL MAZE ROUTING ALGORITHMS ON A HYPERCUBE MULTICOMPUTER

A THESIS SUBMITTED TO THE DEPARTMENT OF COMPUTER ENGINEERING AND INFORMATION SCIENCE AND THE INSTITUTE OF ENGINEERING AND SCIENCE OF BILKENT UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF SCIENCE

By Tahsin Mertefe Kurç November 1991

Tahsin Hertefe Kurg المحادثة ستعسف سقافا وسيدي المنتاب الراري

B. 9562

TK 7874 .K&7 1391

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a thesis for the degree of Master of Science

Aykaneet

Assoc. Prof. Dr. Cevdet Aykanat (Principal Advisor)

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a thesis for the degree of Master of Science.

Dr. Kemal Oflazer

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a thesis for the degree of Master of Science.

D. D. Mahard Para

Prof. Dr. Mehmet Bar

Approved by the Institute of Engineering and Science:

Miserary

Prof. Mehmet Baray, Director of the Institute of Engineering and Science

## ABSTRACT

### PARALLEL MAZE ROUTING ALGORITHMS ON A HYPERCUBE MULTICOMPUTER

Tahsin Mertefe Kurç M. S. in Computer Engineering and Information Science Supervisor: Assoc. Prof. Dr. Cevdet Aykanat November, 1991

Global routing phase is a time consuming task in VLSI layout. In global routing phase of the layout problem, the overall objective is to realize all the net interconnections using shortest paths. Efficient heuristics are used for the global routing phase. However, due to the assumptions and constraints they impose, heuristics may fail to find a path for a net even if one exists. Re-routing is required for such nets. This re-routing phase requires the exhaustive search of the wiring area. Lee's maze routing algorithm and Lee type maze routing algorithms are exhaustive search algorithms used in re-routing phase.

These algorithms are computationally expensive algorithms and consume large amounts of computer time for large grid sizes. Hence, these algorithms are good candidates for parallelization. Also, these algorithms require large memory space to hold the wiring grid. Therefore, the effective parallelization of these algorithms require the partitioning of the computations and the grid among the processors. Hence, these algorithms can be parallelized on distributed-memory message passing multiprocessors (multicomputers). In this work, efficient parallel Lee type maze routing algorithms are developed for hypercube-connected multicomputers. These algorithms are implemented on an Intel's iPSC/2 hypercube multicomputer.

Keywords: VLSI layout, maze routing, Lee's maze routing algorithm, Lee type maze routing algorithms, multicomputer, hypercube topology.

# ÖZET

## HİPERKÜP ÇOK İŞLEMCİLİ BİLGİSAYARINDA PARALEL LABİRENT YOL BELİRLEME ALGORİTMALARI

Tahsin Mertefe Kurç Bilgisayar Mühendisliği ve Enformatik Bilimleri Bölümü Yüksek Lisans Tez Yöneticisi: Doçent Dr. Cevdet Aykanat Kasım, 1991

Tümdevre tasarımında, devre bağlantılarının yapılması zaman alan bir iştir. Burada amaç bütün devre bağlantılarını en kısa yolları kullanarak yapmaktır. Eğer, her seferinde bir devre grubunun bağlantısı yapılırsa bunun adına *labirent* yol belirleme yöntemi denir.

Bu yöntem için, hüristik algoritmalar vardır. Ancak, bu tip algoritmalar devre bağlantılarına getirdikleri kısıtlamalardan dolayı, bazen var olan bağlantıları bulamazlar. Bu yüzden, devrelerin bulunduğu alanın, tümden taranması gerekebilir. Lee'nin algoritması ve Lee benzeri algoritmalar bu tip algoritmalardır.

Lee'nin algoritması ve Lee benzeri algoritmalar hesaplama bakımından pahalı ve devre yüzeyi icin çok bilgisayar hafızası gerektiren algoritmalardır. Bu nedenle bu tip algoritmalar çok islemcili bilgisayarlarda, paralel olarak çözmek için uygundur.

Bu çalışmada, Lee benzeri labirent yol bulma algoritmalarının, hiperküp çok işlemcili bilgisayarında paralelleştirilmesi anlatılmaktadır. Anahtar kelimeler : Tümdevre tasarımı, labirent yol bulma yöntemi, Lee'nin labirent yol bulma algoritması, Lee benzeri labirent algoritmaları, çok işlemcili bilgisayar, hiperküp topolojisi.

1

## ACKNOWLEDGEMENT

I wish to thank very much my supervisor Assoc. Prof. Dr. Cevdet Aykanat, who has guided and encouraged me during the development of this thesis.

I am grateful to Professor Mehmet Baray and Assoc. Prof. Dr. Kemal Oflazer for their remarks and comments on the thesis.

It is pleasure to express my thanks to all my friends for their valuable discussions and to my family for providing morale support during this study.

## Contents

| 1 | INTRODUCTION |                                                    | 1                                         |    |

|---|--------------|----------------------------------------------------|-------------------------------------------|----|

| 2 | SE           | SEQUENTIAL MAZE ROUTING ALGORITHMS                 |                                           | 10 |

|   | 2.1          | Lee's                                              | Maze Routing Algorithm                    | 10 |

|   | 2.2          | 2 Lee Type Algorithms For Routing of Multipin Nets |                                           | 13 |

|   |              | 2.2.1                                              | Using Prim's Algorithm                    | 17 |

|   |              | 2.2.2                                              | Using Kruskal's Algorithm                 | 18 |

| 3 | PA           | RALLI                                              | ELIZATION OF LEE'S ALGORITHM              | 23 |

|   | 3.1          | Grid I                                             | Partitioning and Mapping                  | 24 |

|   | 3.2          | 2 Parallel Front Wave Expansion                    |                                           | 29 |

|   |              | 3.2.1                                              | Expansion Starting From Source Only       | 29 |

|   |              | 3.2.2                                              | Expansion Starting From Source and Target | 35 |

|   | 3.3          | 3.3 Termination Detection                          |                                           | 42 |

|   |              | 3.3.1                                              | Global Synchronization                    | 42 |

|   |              | 3.3.2                                              | Counter Termination Scheme1               | 43 |

|   |              | 3.3.3                                              | Counter Termination Scheme2               | 43 |

|   | 3.4 | Overla  | apping Communication with Computation     | 46 |

|---|-----|---------|-------------------------------------------|----|

|   | 3.5 | Async   | hronous Scheme                            | 49 |

|   |     | 3.5.1   | Expansion Starting From Source Only       | 49 |

|   |     | 3.5.2   | Expansion Starting From Source and Target | 51 |

|   | 3.6 | Parall  | el Path Recovery and Sweeping             | 55 |

|   |     | 3.6.1   | Non-pipelined scheme                      | 57 |

|   |     | 3.6.2   | Pipelined Scheme                          | 57 |

|   | 3.7 | Experi  | imental Results                           | 63 |

| 4 | PAI | RALLE   | EL ALGORITHMS FOR MULTIPIN NETS           | 72 |

|   | 4.1 | Paralle | el Akers' Algorithm for Multipin Nets     | 72 |

|   | 4.2 | Paralle | el Kruskal's Steiner Tree Algorithm       | 74 |

|   | 4.3 | Experi  | mental Results                            | 77 |

| 5 | COI | NCLUS   | SIONS                                     | 84 |

### ix

# List of Figures

| 1.1 | Grid representation of the wiring surface in gate array layout.                                                                                       | 3  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | (a) Single bend path (heuristic can find such a path) (b) Two-<br>bend path (heuristic fails to find such a path)                                     | 4  |

| 1.3 | Routing of nets using heuristic (a) Routing of net $(S_1,T_1)$ (b)<br>Routing of net $(S_2,T_2)$ .                                                    | 5  |

| 1.4 | Routing of nets using heuristic (a) Routing of net $(S_3,T_3)$ (b)<br>Routing of net $(S_4,T_4)$ .                                                    | 6  |

| 1.5 | Heuristic fails to find the path for $(S_5,T_5)$ , because the path (dotted lines) violates cell capacities.                                          | 7  |

| 1.6 | 8 node hypercube structure                                                                                                                            | 8  |

| 2.1 | A sample global grid for Lee's maze routing algorithm                                                                                                 | 11 |

| 2.2 | Front wave expansion phase of the Lee's maze routing algorithm                                                                                        | 11 |

| 2.3 | Path recovery phase of the Lee's maze routing algorithm                                                                                               | 12 |

| 2.4 | Sweeping phase of the Lee's maze routing algorithm                                                                                                    | 13 |

| 2.5 | Front wave expansion phase of the Lee's algorithm (a) Initial cycles of front wave expansion phase (b) Successful termination of front wave expansion | 14 |

| 2.6  | Path recovery and sweep phases of Lee's algorithm after the front wave expansion phase (a) Path Recovery phase (b) Final configuration after sweep phase                          | 15 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.7  | The use of the sweep queue, cells marked as 1,2,3 are added into<br>the sweep queue at expansion cycles 3,3, and 2, respectively                                                  | 16 |

| 2.8  | Sequential version of the algorithm for routing multipin nets using Prim's algorithm                                                                                              | 18 |

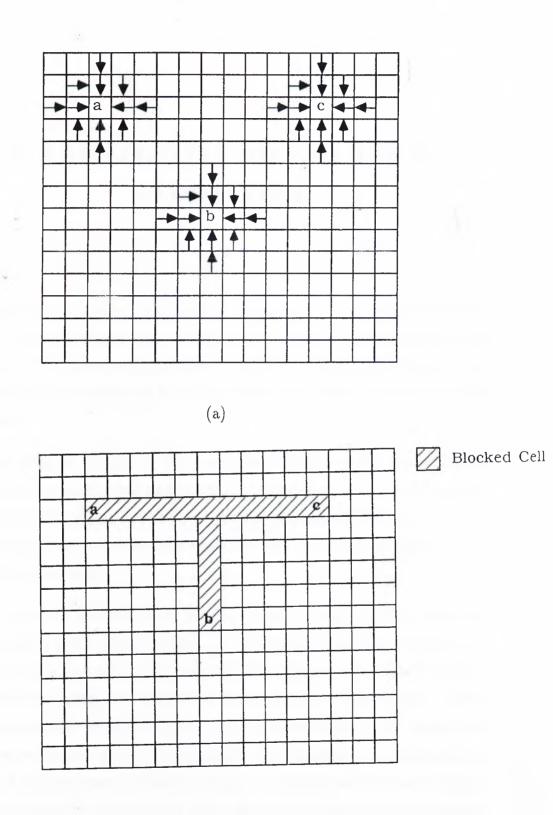

| 2.9  | Front wave expansion phase of the Akers' algorithm beginning<br>from the terminal cell 'a' (a) initial two cycles (b) Initial cycle<br>after the first path (a to b) is connected | 19 |

| 2.10 | The final configuration after all three pins are connected $\ldots$ .                                                                                                             | 20 |

| 2.11 | Sequential version of the algorithm for routing multipin nets<br>using Kruskal's algorithm                                                                                        | 21 |

| 2.12 | Routing of a three pin net using Kruskal's algorithm (a) Initial cycles of the algorithm (b) After connecting all pins                                                            | 22 |

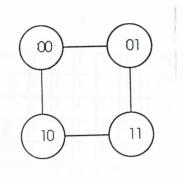

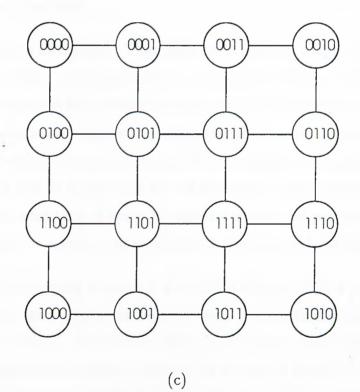

| 3.1  | Mesh embedding (a) hypercube of dimension 2 (b) hypercube of dimension 3 (c) hypercube of dimension 4                                                                             | 25 |

| 3.2  | Tiled decomposition of a 16x16 grid onto 2x4 mesh embedded<br>3-dimensional hypercube                                                                                             | 26 |

| 3.3  | Scattered decomposition of a 16x16 grid                                                                                                                                           | 28 |

| 3.4  | Decomposition of 16x16 grid into subblocks of (a) $h = w = 2$<br>(b) $h = 2w = 4$                                                                                                 | 30 |

| 3.5  | Local data structures for a node processor                                                                                                                                        | 31 |

| 3.6  | Node program for the Sonly scheme                                                                                                                                                 | 32 |

| 3.7  | Encoding the status information                                                                                                                                                   | 33 |

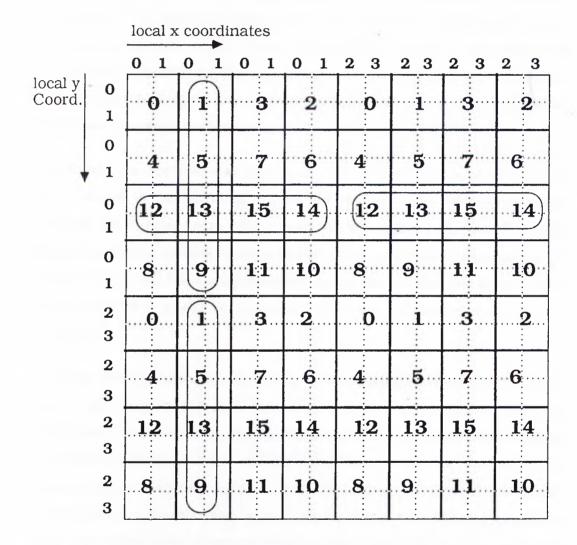

| 3.8  | Mapping of local coordinates onto the repeating mesh template                                                                                                                           | 36 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.9  | Expansion starting from source and target scheme (a) Initial cycles (b) Collision of two front waves                                                                                    | 38 |

| 3.10 | Node program for the S+T scheme                                                                                                                                                         | 39 |

| 3.11 | Host and node programs for the counter termination scheme 1                                                                                                                             | 44 |

| 3.12 | Host and node programs for the counter termination scheme 2                                                                                                                             | 45 |

| 3.13 | Overlapping communication and computation                                                                                                                                               | 47 |

| 3.14 | Host and node programs for the asynchronous Sonly scheme                                                                                                                                | 50 |

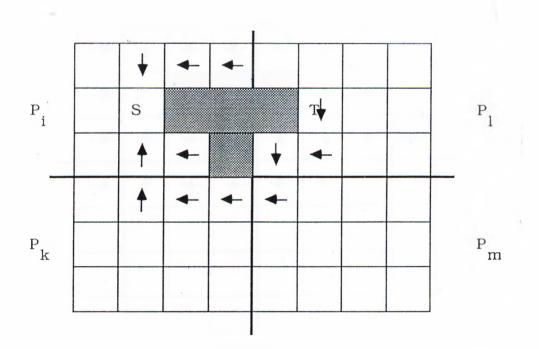

| 3.15 | Failure to find the shortest path. If processors $P_k$ , $P_m$ and $P_l$ are faster than processor $P_i$ , target T can be reached by a longer path                                     | 52 |

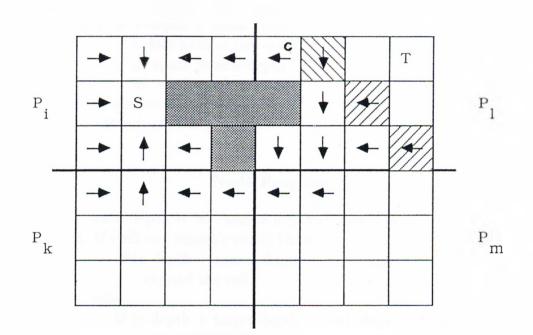

| 3.16 | Labeling of an already labeled cell by a shorter path, the shaded cells have been reached by a shorter path hence the cells expanding form cell c will relabel the shaded cells         | 53 |

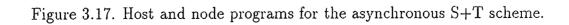

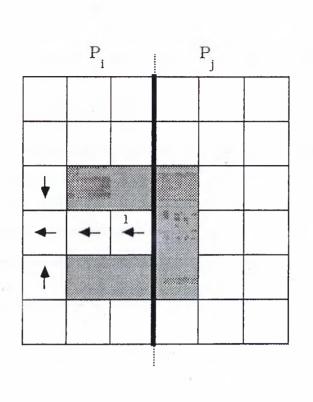

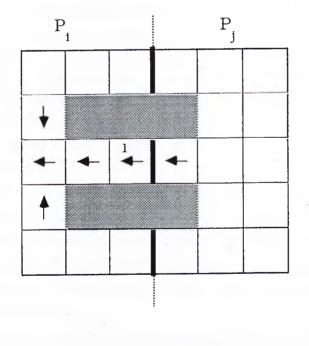

| 3.17 | Host and node programs for the asynchronous S+T scheme.                                                                                                                                 | 54 |

| 3.18 | (a) Cell 1 is added into the sweep queue without any extra com-<br>munication (b) Cell 1 is added into the sweep queue in parallel<br>algorithm while it is not in sequential algorithm | 58 |

| 3.19 | Host program for the non-pipelined path recovery and sweep phase                                                                                                                        | 59 |

| 3.20 | Node program for non-pipelined path recovery and sweeping scheme.                                                                                                                       | 59 |

| 3.21 | The calculation of r value                                                                                                                                                              | 60 |

| 3.22 | Node program for the pipelined path recovery and sweep phase.                                                                                                                           | 62 |

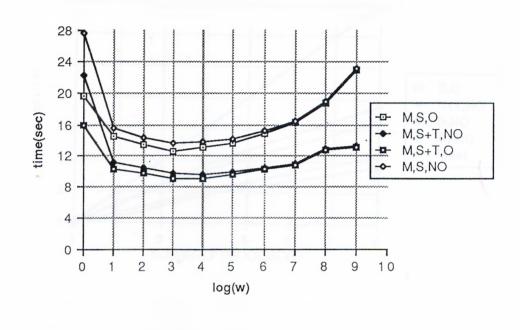

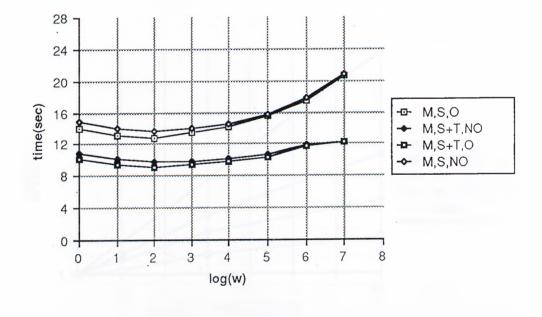

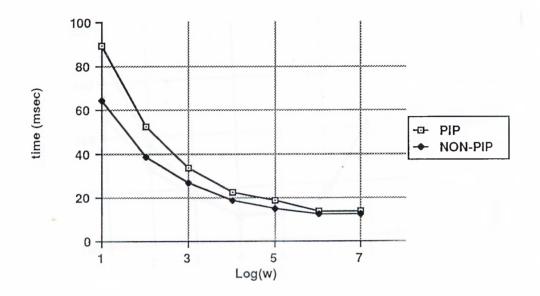

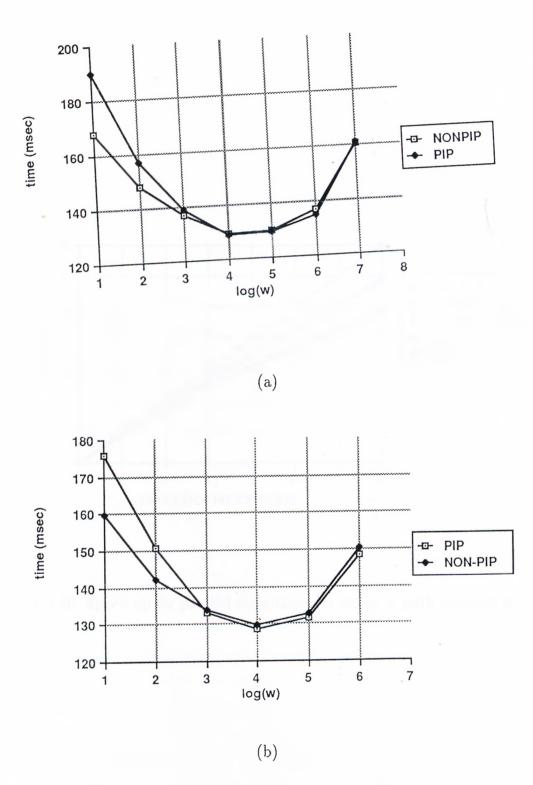

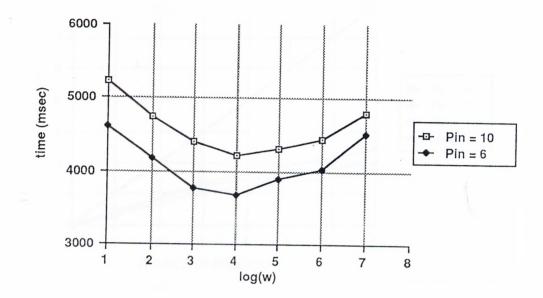

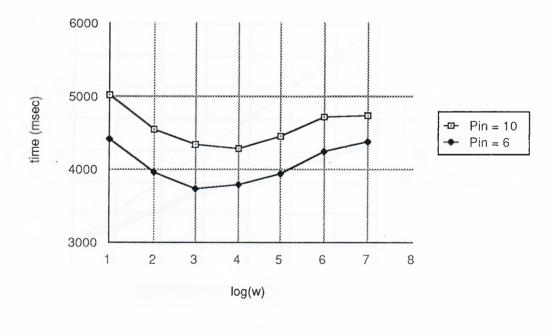

| 3.23 | Effect of w values on the performance of the parallel algorithm<br>for N = 1024, P = 4. (a) $h = w$ (b) $h = 2w$                                                                        | 65 |

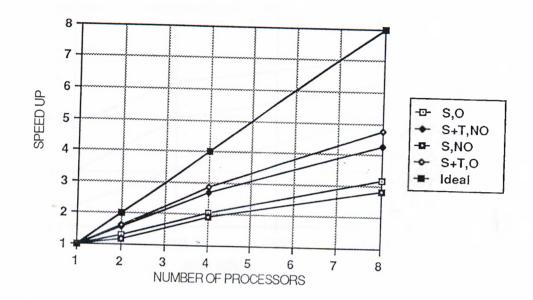

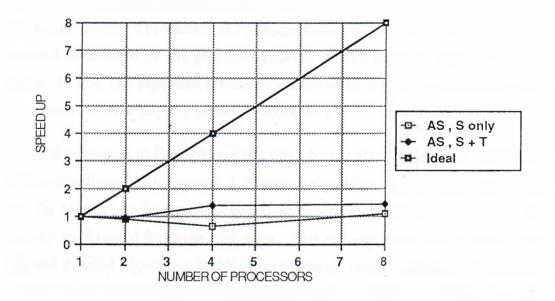

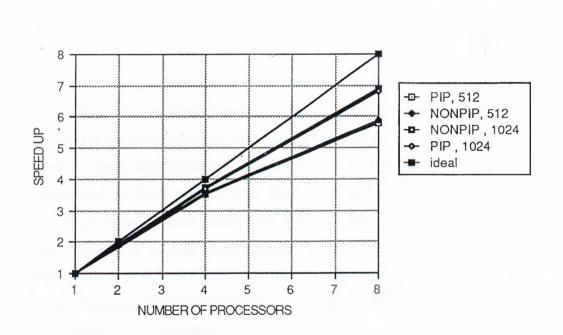

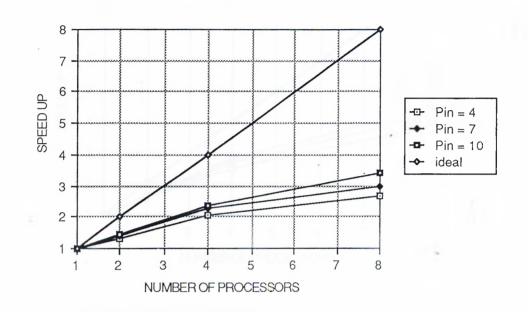

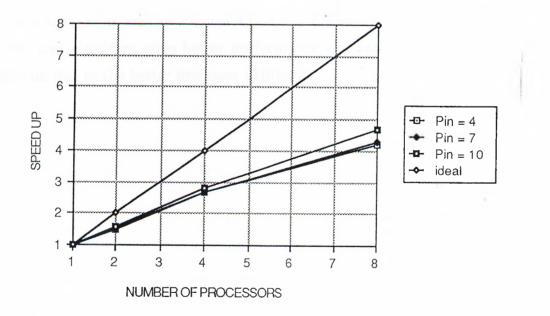

| 3.24 | Speed-up for various parallel algorithms for front wave expansion phase                                                                                                                                     | 66 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.25 | Speed-up vs grid size                                                                                                                                                                                       | 66 |

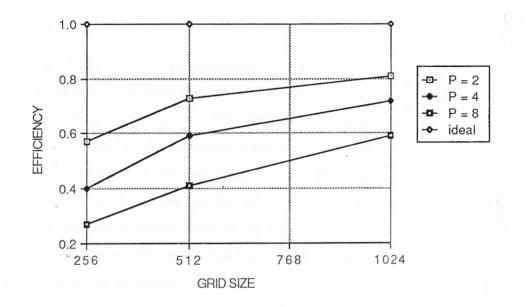

| 3.26 | Efficiency vs grid size                                                                                                                                                                                     | 67 |

| 3.27 | Speed-up figures for asynchronous algorithms                                                                                                                                                                | 67 |

| 3.28 | Effect of w values on the performance of path recovery (a) $h = w$ (b) $h = 2w$                                                                                                                             | 69 |

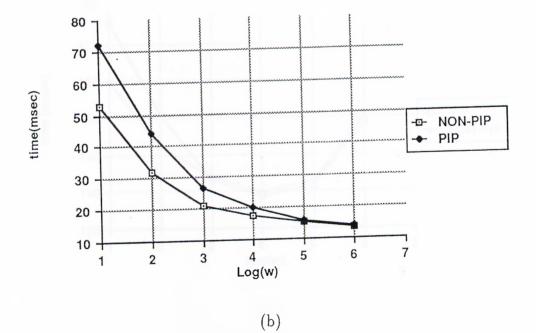

| 3.29 | Effect of w values on the performance of path recovery + sweep<br>(a) $h = w$ (b) $h = 2w \dots \dots \dots \dots \dots \dots \dots \dots \dots \dots \dots \dots \dots$                                    | 70 |

| 3.30 | Speed-up for parallel algorithms for sweep + path recovery phase                                                                                                                                            | 71 |

| 4.1  | Node program for Akers' algorithm                                                                                                                                                                           | 73 |

| 4.2  | Host program for parallel algorithm for multipin nets using Kruskal' algorithm                                                                                                                              |    |

| 4.3  | Node program for the parallel algorithm for multipin nets using Kruskal's algorithm                                                                                                                         | 76 |

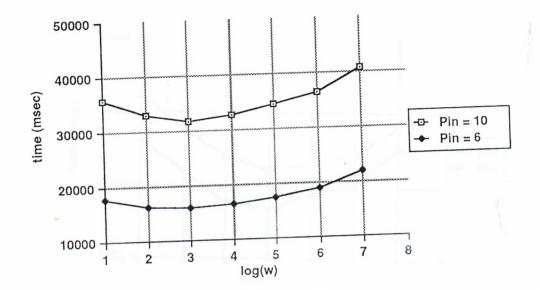

| 4.4  | Effect of h,w values on the execution of parallel Akers' algorithm<br>(a) $h = w$ (b) $h = 2w \dots \dots \dots \dots \dots \dots \dots \dots \dots \dots \dots \dots \dots \dots \dots \dots \dots \dots $ | 79 |

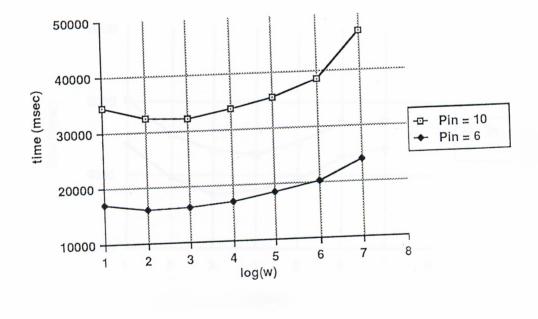

| 4.5  | Effect of h,w values on the execution of parallel Kruskal's Steiner tree algorithm (a) $h = w$ (b) $h = 2w$                                                                                                 | 80 |

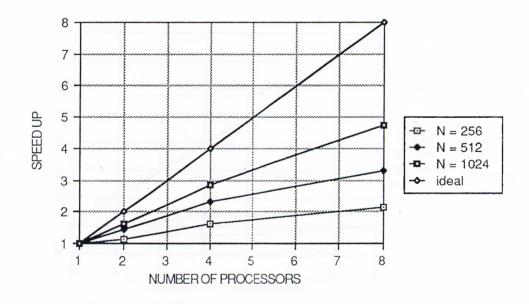

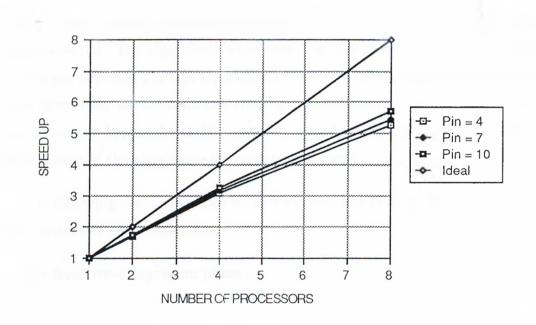

| 4.6  | Speed-up figure for parallel Akers' algorithm on a 512x512 grid for 4,7,10 pin nets                                                                                                                         | 81 |

| 4.7  | Speed-up figure for parallel Akers' algorithm on a 1024x1024<br>grid for 4,7,10 pin nets                                                                                                                    | 81 |

| 4.8  | Speed-up figure for parallel Kruskal's Steiner tree algorithm on a 512x512 grid for 4,7,10 pin nets                                                                                                         | 82 |

xiii

## LIST OF FIGURES

4.9 Speed-up figure for parallel Kruskal's Steiner tree algorithm on

a 1024x1024 grid for 4,7,10 pin nets

83

## 1. INTRODUCTION

With recent advances in VLSI technology, it is now feasible to manufacture integrated circuits with several hundred thousand, even millions of transistors. This manufacturing capability together with the economic and performance benefits of large scale VLSI systems necessitates the automation of the circuit design process. The circuit design process, the layout of integrated circuits on chips, is a complex task. The major research issue in the design automation is the development of efficient and easy-to-use systems for circuit layout.

In the combinatorial sense, the layout problem is a constrained optimization problem. A layout problem instance is given by a description of the circuit by a netlist. A netlist describes the switching elements and their connecting wires. The question is to find an assignment of the geometric coordinates of the circuit components in the planar layer(s) that minimizes certain cost criteria while maintaining the fabrication technology constraints. Most of the optimization problems encountered during the integrated circuit layout are intractable, that is they are NP-hard [1]. Hence, heuristic methods are used to find solutions in reasonable time. Usually, the layout problem is decomposed into subproblems which are then solved one after another. These subproblems are usually NP-hard as well, but they are more suitable for heuristic solutions than the whole layout problem. A typical layout problem decomposition is component placement followed by the global routing. In the global routing phase, the approximate course of wires are determined. The global routing phase is followed by *detailed routing* phase to determine the exact course of wires.

There are two major kinds of layout methodologies, full-custom layout and

semi-custom layout [1]. In full-custom layout, the design starts on an empty piece of silicon. The designer has a wide range of freedom in compound placement and routing. In semi-custom layout, this freedom is severely restricted. The design starts on a prefabricated silicon that already contains all switching elements (e.g. gate arrays) [1, 2] or involves the use of basic circuit components from geometrically restricted libraries (e.g. standard cells) (Chap. 1,pp. 18-26 in [1]). Semi-custom layout is more suitable for design automation.

In gate array layout, initially the design area is not empty. There are prefabricated switching elements (cells), such as boolean gates or flip-flops, on the wafer. In the gate array layout, the placement problem is actually an assignment problem. Each gate in the netlist of the given circuit is assigned a cell on the wafer that will implement this gate. These cells, implementing the gates, are then interconnected using only top metal layer(s) so that the given netlist description is realized. The fabrication in gate arrays is simpler since the last few steps of the fabrication process have to be custom-tailored. Furthermore gate arrays are less expensive since the number of masks to describe the given circuit is reduced considerably. The placement and detailed routing phases of layout problem are out of the scope of this work. More information on placement and detailed routing can be found in [1].

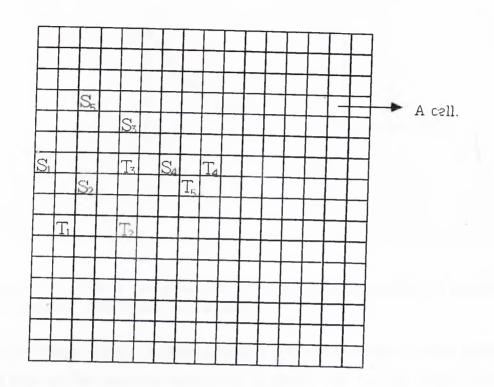

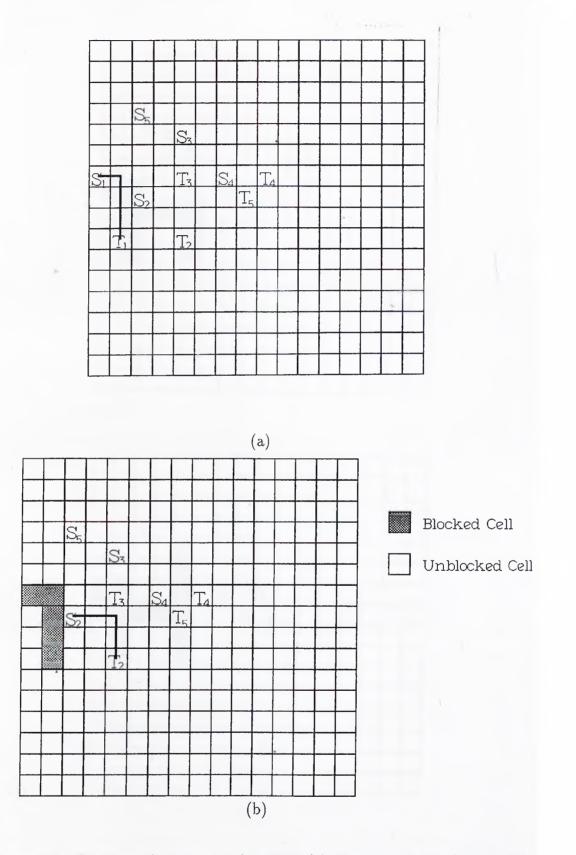

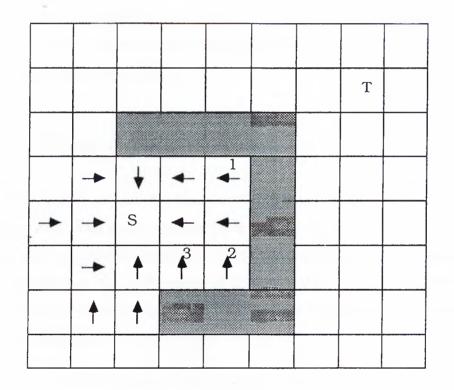

In global routing phase of the layout problem, the routing area can be represented as a 2-dimensional grid as shown in Fig. 1.1, when one metal layer is used for wiring. The grid (also called global grid) is divided into squares called *cells*. There are specially designated cells called *pins*, such as cells  $S_1$ ,  $T_1$ ,  $S_2$ ,  $T_2$  in Fig. 1.1. A net is defined to be the set of pins to be interconnected. For example, the net  $N_1$  is denoted by two pins  $S_1$  and  $T_1$ . In Fig. 1.1, all nets have two pins, hence they are called *two-pin nets*. However, in practice some of the nets may have more than two pins, such nets are called *multipin nets*. The overall aim in global routing is to realize all the net interconnections using the shortest paths. Here, a *path* is defined to be the interconnecting wire between the pins of a net. The paths are realized by passing wires through the channels in the cells. The vertical and horizontal lines between neighbor cells represent the channels. Wires can go from one cell to another adjacent cell by either crossing a vertical or a horizontal channel. Hence, moves from

Figure 1.1. Grid representation of the wiring surface in gate array layout.

a cell are restricted to four directions (south,north,west,east). However, due to the technological constraints, the channels are assigned with a channel capacity representing the number of wires that can cross that channel. As the interconnections between the pins (net terminals) are constructed some of the cells are declared to be blocked, that is no more wires can pass through those cells. In this work, for simplicity, each cell is assumed to have a wiring capacity of a single wire. If nets are interconnected (routed) one net at a time basis, the global routing phase reduces to *maze routing*.

Since there may be thousands of nets to be routed, global routing is a time consuming task. Hence, heuristics are used for global routing and maze routing [3, 4, 5, 6, 10]. However, due to the assumptions and constraints they impose, heuristic algorithms may fail to find a path even if one exists. This can be illustrated by Figs. 1.3 and 1.4. In these figures, the routing of nets are done by using a heuristic which allows routing of nets having at most a single

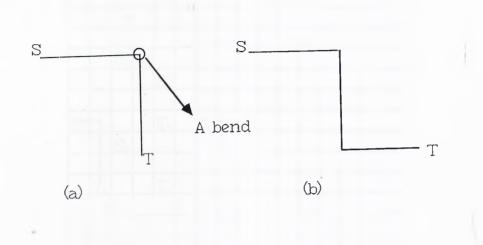

Figure 1.2. (a) Single bend path (heuristic can find such a path) (b) Two-bend path (heuristic fails to find such a path).

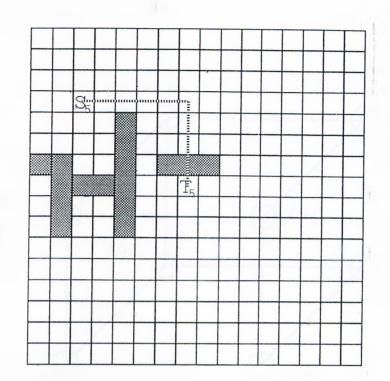

bend as shown in Fig. 1.2. After routing a net, the cell capacities are updated and cells on the path are declared as blocked. The routing of net  $(S_5,T_5)$ , however, can not be done by this heuristic, because heuristic can only find a single bend path (dotted lines in Fig. 1.5), which violates the cell capacities of some cells. The re-routing of this net is required. The re-routing of this net can be achieved by exhaustive search of the wiring area. Lee's maze routing algorithm and Lee type algorithms for multipin nets are such type of exhaustive search algorithms.

These algorithms are computationally expensive algorithms and consume large amounts of computer time for large grid sizes. Hence, these algorithms are good candidates for parallelization. Also, these algorithms require large memory space to hold the wiring grid. Therefore, the effective parallelization of these algorithms require the partitioning of the computations and the grid among the processors. Hence, these algorithms can be parallelized on distributed-memory message passing multiprocessors (multicomputers).

A multicomputer is an ensemble of processors interconnected in a certain topology. In a multicomputer, each processor has its own local memory and there is no globally shared memory in the system. Each processor runs independently (asynchronously). The cooperation, synchronization and data exchange

Figure 1.3. Routing of nets using heuristic (a) Routing of net  $(S_1,T_1)$  (b) Routing of net  $(S_2,T_2)$ .

Figure 1.4. Routing of nets using heuristic (a) Routing of net  $(S_3,T_3)$  (b) Routing of net  $(S_4,T_4)$ .

Figure 1.5. Heuristic fails to find the path for  $(S_5,T_5)$ , because the path (dotted lines) violates cell capacities.

between processors are achieved by explicit message-passing between processors. Therefore, the interconnection topology plays an important role on the performance of such computers.

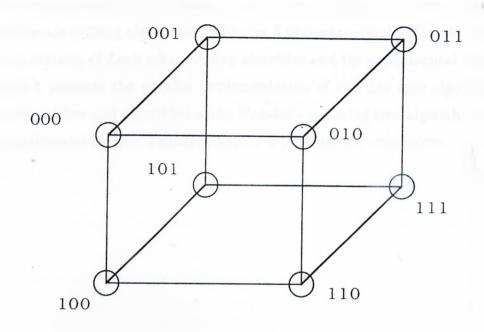

Among the many interconnection topologies such as ring, mesh etc., hypercube interconnection topology is the most popular topology. The popularity of hypercube topology comes from the fact that many other topologies (such as ring, mesh, tree) can be embedded onto hypercube [11]. In addition, there are commercially available hypercube connected multicomputers such as FPS T-series <sup>1</sup>, NCUBE <sup>2</sup>, iPSC/1 <sup>3</sup>, iPSC/2 <sup>4</sup>.

In such an architecture, for a d dimensional hypercube, there are  $2^d$  processors (nodes). Each node is connected directly to d other nodes. Figure 1.6 represents a 3-dimensional hypercube structure. The binary encoding of a processor differs in only one bit from the neighbor's encoding. The processors

<sup>&</sup>lt;sup>1</sup>FPS T-series is a registered trade mark of FPS Inc.

<sup>&</sup>lt;sup>2</sup>NCUBE is a registered trade mark of NCUBE Inc.

<sup>&</sup>lt;sup>3</sup>iPSC/1 is a registered trade mark of Intel Inc.

<sup>&</sup>lt;sup>4</sup>iPSC/2 is a registered trade mark of Intel Inc.

Figure 1.6. 8 node hypercube structure

can directly communicate to d neighbors only. The communication between processors that are not connected directly is done through other processors by either software or hardware. Maximum distance between two processors in a hypercube is d.

Achieving speed-up through parallelism in such architectures is not straightforward. The algorithm must be designed so that data and computations are distributed evenly among processors to achieve the maximum load balance. In a parallel machine with high communication latency, the algorithms must be designed so that the large amounts of computations are done between communication steps. Another factor effecting the parallel algorithms is the ability of parallel systems to overlap the computation with communication. A good parallel algorithm should exploit these factors and the topology of the architecture to achieve maximum speed-up.

In this work, the parallel implementation of Lee's maze routing algorithm

and Lee type multipin net algorithms on a commercially available multicomputer implementing the hypercube connection topology is addressed.

The organization of this thesis is as follows, Chapter 2 presents the sequential maze routing algorithms. Chapter 3 presents several different parallel implementations of *Lee's maze routing algorithm* and the experimental results. Chapter 4 presents the parallel implementation of two *Lee type* algorithms, Akers' algorithm and algorithm using Kruskal's spanning-tree algorithm, and the experimental results. Finally, Chapter 5 presents the conclusions.

# 2. SEQUENTIAL MAZE ROUTING ALGORITHMS

This chapter presents sequential maze routing algorithms used in exhaustive search of the wiring area. First section describes a well known algorithm, called Lee's maze routing algorithm [7], for routing two-pin nets. Some nets, however, as is stated in Chap. 1 may have more than two pins. Routing of such nets is the direct translation of *Steiner Tree problem*[15, 16] into the context of routing in rectangular grids. There are two algorithms that are the variations of Lee's maze routing algorithm. These algorithms are presented in section 2.

### 2.1 Lee's Maze Routing Algorithm

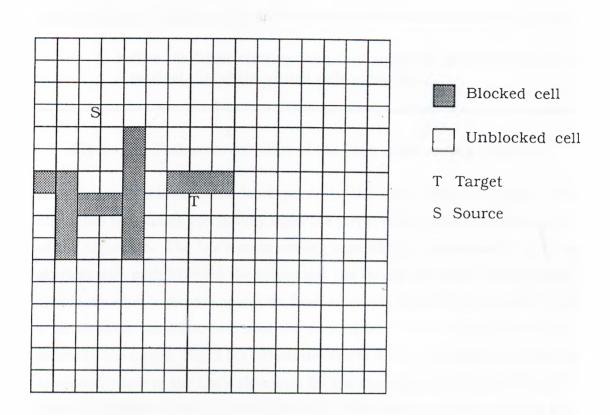

Lee's maze routing algorithm is a well known algorithm for routing two-pin nets. In the two-pin net problem, the routing area is represented as a twodimensional grid as shown in Fig. 2.1. Each cell has a status which may be blocked or unblocked initially. This status information is kept in a twodimensional array called *status array*. There are two special cells, called source (S) and target (T) (see Fig. 2.1). The aim is to find the shortest path between source and target cells.

Lee's maze routing algorithm consists of three phases, namely, front wave expansion, path recovery, and sweeping [8]. Front wave expansion phase is a breadth-first search strategy starting from the source cell. The description of the algorithm for the front wave expansion phase is given in Fig. 2.2.

The labeling operation (at Step 2) of a free and unlabeled adjacent cell

Figure 2.1. A sample global grid for Lee's maze routing algorithm

A queue, called expansion queue, initially contains only the source cell. A queue, called sweep queue, is initially empty. A two dimensional NxN *Status* array holds the status for the cells of an NxN grid. All the *free* cells are initially *unlabeled*.

- 1. Remove a cell c from the expansion queue.

- 2. Examine the four adjacent cells of the cell c using the current information in the *Status* array. Discard the *blocked* and already *labeled* adjacent cells. Update the status of the *unlabeled free* adjacent cells as *labeled* in the *Status* array and add those cells to the expansion queue. If all adjacent cells of the cell c are either blocked or already labeled, then add the cell c into the sweep queue.

- 3. Go to step 1 until either target cell is labeled or expansion queue becomes empty.

Figure 2.2. Front wave expansion phase of the Lee's maze routing algorithm

1. Follow the labels starting from the target cell until the source cell is reached. Label the visited cells as blocked.

#### Figure 2.3. Path recovery phase of the Lee's maze routing algorithm

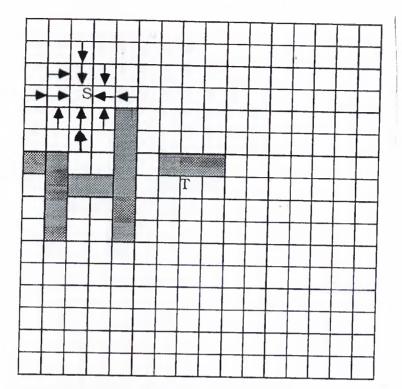

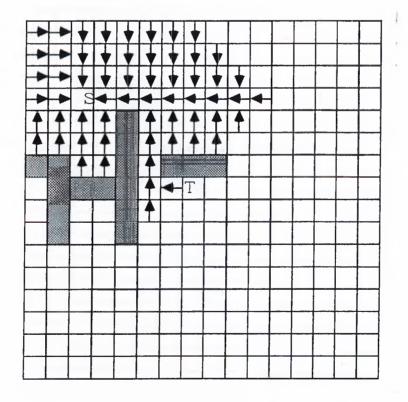

is performed such that, the label points to the cell c being expanded. The algorithm terminates successfully when the target cell t is labeled during Step 2 of the algorithm. The Lee's maze routing algorithm is guaranteed to find the shortest wire path between the source and the target. The algorithm may also terminate when a remove operation from an empty queue is attempted. Such a termination condition indicates the non-existence of a wire-path from the source to the target. Fig. 2.5(a) illustrates the first two cycles of the front wave expansion phase of the Lee's algorithm for the example grid shown in Fig. 2.1. Labeling process at Step 2 of the algorithm is illustrated by the following four labels,  $\downarrow$ ,  $\leftarrow$ ,  $\uparrow$ , and  $\rightarrow$  in the figure. The front wave expansion phase is followed by the path recovery and sweeping phases. Fig. 2.5(b) illustrates the successful termination of the front wave expansion phase.

In the path recovery phase, the labels are followed starting from the target cell to construct the path between source and target (see Fig. 2.6(a)). The algorithm is given in Fig. 2.3.

After the path recovery phase is completed, the labeled cells in the front wave expansion phase have to be unlabeled so that next net can be routed. This unlabeling operation is carried out in sweeping phase. The sweeping phase is given in Fig. 2.4.

At the end of front wave expansion phase the expansion queue contains the cells expanded in the last expansion cycle of the front wave expansion phase. These terminal cells are already labeled and connected to their parents. Thus, the cells labeled in the expansion paths starting from the source cell and terminating at these terminal cells can be unlabeled by following their labels (step 2 of the sweep algorithm). However, during the front wave expansion phase, some of the expansion paths initiated from the source cell are blocked

- 1. Remove a cell c from sweep queue or expansion queue

- 2. Follow the labels starting from c until a blocked or unlabeled cell is reached. Unlabel the visited cells in the status array.

- 3. Repeat steps 1 and 2 until both sweep queue and expansion queues are empty.

Figure 2.4. Sweeping phase of the Lee's maze routing algorithm

either due to blocked cells or due to the already labeled cells. The terminal cells of these blocked expansion paths are added into the sweep queue at step 2 of the front wave expansion algorithm (see Fig. 2.7). Hence, the cells labeled in these blocked expansion paths should also be unlabeled during the sweeping phase. Fig. 2.6(b) illustrates the final configuration after the *path recovery* and *sweeping* phases.

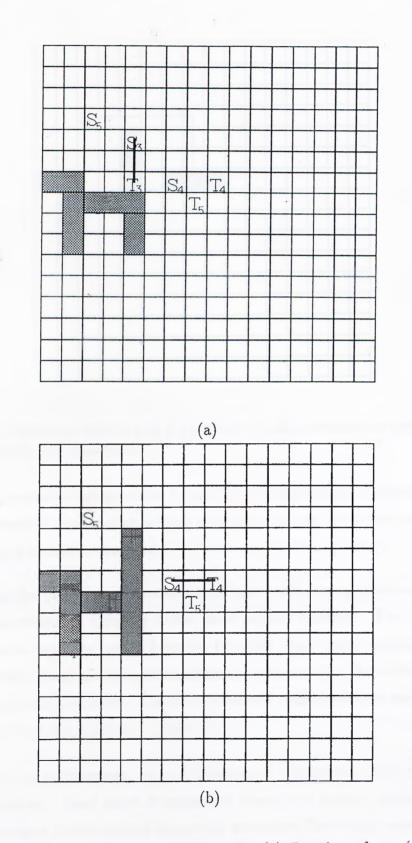

### 2.2 Lee Type Algorithms For Routing of Multipin Nets

The routing of multipin nets is the direct translation of *Minimum Steiner tree* problem [15] into the context of routing. The definition of the *Mininum Steiner* tree problem (or Steiner tree problem) for general graphs [1] is as follows :

Instance : A connected undirected graph  $G = (V^1, E^2)$  with edge cost function  $\lambda : E \rightarrow R_+$  and a subset  $R \subset V$  of required vertices.

configurations : All edge-weighted trees.

Solutions : All Steiner trees for R in G; that is, all subtrees of G that connect all vertices in R and all of whose leaves are vertices in R.

minimize :  $\lambda(T) = \sum_{e \in E_T} \lambda(e)$

The Steiner tree problem is an NP-hard problem. The existing approximate algorithms try to find an suboptimal solution in reasonable time. These

<sup>&</sup>lt;sup>1</sup>V represents the vertices of the graph G

<sup>&</sup>lt;sup>2</sup>E represents the edges of graph G

(a)

(b)

Figure 2.5. Front wave expansion phase of the Lee's algorithm (a) Initial cycles of front wave expansion phase (b) Successful termination of front wave expansion

Figure 2.6. Path recovery and sweep phases of Lee's algorithm after the front wave expansion phase (a) Path Recovery phase (b) Final configuration after sweep phase

15

Figure 2.7. The use of the sweep queue, cells marked as 1,2,3 are added into the sweep queue at expansion cycles 3,3, and 2, respectively.

approximate algorithms try to find a good Steiner tree by combining minimumspanning-tree and shortest path calculations. The cost of the Steiner tree  $T_{sub}$ , on grid graphs, found by these algorithms is bounded by

$$Cost(T_{Sub}) \le \frac{3}{2}Cost(T_{Opt}) \tag{2.1}$$

as shown in [16], where  $Cost(T_{Sub})$  is the cost of the suboptimal tree and  $Cost(T_{Opt})$  is the cost of optimal Steiner tree. In this work, parallelization of two algorithms that use Prim's and Kruskal's algorithms [1] for minimum-spanning-tree calculations and Lee's maze routing algorithm for the shortest path calculations is addressed. Following two sections present the sequential versions of these algorithms.

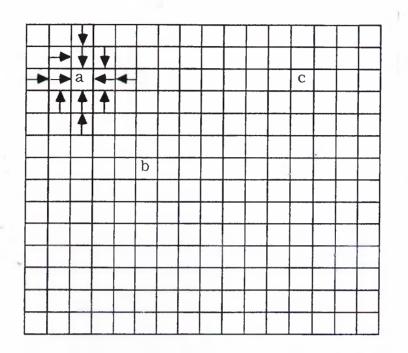

### 2.2.1 Using Prim's Algorithm

Using Prim's algorithm [1], Akers[1, 17] has developed an algorithm to route multipin nets. The algorithm uses Lee's routing algorithm for the connection of pins. Prim's algorithm is used for solving the *minimum spanning tree* problem. Akers' algorithm is a modification of this algorithm into the *Steiner tree* problem. The pins in the multipin net are called the terminal cells. The algorithm is given in Fig. 2.8.

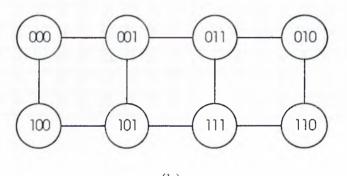

At step 2 of the algorithm, the set of sources consists of all the visited cells during the previously and currently constructed respective shortest paths. The propagation of the new front waves starts from all of these cells taking them as new sources. Fig. 2.9 and 2.10 illustrates the steps of the Akers' algorithm for connection of a multipin net.

- 1. Choose an arbitrary pin of the net and perform Lee's front wave expansion phase to propagate a unidirectional search wave starting from this pin cell until it hits another terminal cell.

- 2. Perform path recovery to construct the respective shortest path. Add all the cells visited during the path recovery phase into the set of sources.

- 3. Perform the sweeping phase to unlabel all labeled cells during step 2 for the next search wave.

- 4. Propagate unidirectional multi-search waves starting from the set of multi-sources in the expansion queue until an unlabeled terminal cell is reached.

- 5. Goto step 2 until all terminal cells of the net are labeled.

Figure 2.8. Sequential version of the algorithm for routing multipin nets using Prim's algorithm

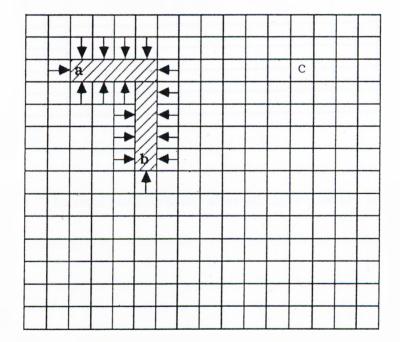

### 2.2.2 Using Kruskal's Algorithm

If we base the Steiner tree computations onto Kruskal's algorithm [1] a faster algorithm [1] can be derived for the connection of multipin nets. This algorithm basically propagates search waves starting from all required pins (terminal cells). The algorithm using Kruskal's spanning-tree algorithm (Kruskal's Steiner tree algorithm) is given in Fig. 2.11. At the beginning all pins form a distinct tree. During the search phase of the algorithm when two search waves starting from different trees collide these two trees are merged and a new tree is formed. There are two procedures to perform the above mentioned task.  $UNION(c_i, c_j)$  merges two different trees to which  $c_i$  and  $c_j$  belong.  $TREE(c_i)$  returns the tree that  $c_i$  belongs to. Since each cell may belong to different trees, the status information of a cell in status array indicates both the label status (labeled, unlabeled, blocked) and a tree information to be used in procedures  $TREE(c_i)$  and  $UNION(c_i, c_j)$ . Fig. 2.12 shows the routing of a single three pin net using this algorithm.

(a)

$\mathbb{Z}$ Blocked Cell

(b)

Figure 2.9. Front wave expansion phase of the Akers' algorithm beginning from the terminal cell 'a' (a) initial two cycles (b) Initial cycle after the first path (a to b) is connected.

Figure 2.10. The final configuration after all three pins are connected

- 1. Add all the terminal cells into the expansion queue.

- 2. Perform Lee's *front wave expansion* phase to propagate multi search waves starting from all terminal cells.

- (a) choose a cell c from queue and examine its adjacent cells  $a_c$ 's for expansion.

- (b) If  $a_c$  is a free cell then add  $a_c$  to expansion queue, label the cell to point to the parent cell c and update the tree information of  $a_c$  in status array so that the cell  $a_c$  belongs to the same tree as its parent.

- (c) If  $a_c$  is labeled and  $TREE(a_c)$  is not equal to TREE(c) this indicates the collision of two different front waves (search waves), then call  $UNION(c, a_c)$ . Save the pair of colliding adjacent cells.

- (d) If  $TREE(a_c) = TREE(c)$  or  $a_c$  is blocked, ignore the cell  $a_c$ .

- (e) If all four adjacent cells  $a_c$ 's of cell c are blocked or labeled such that they belong to the same tree with the cell c then add the cell c to the sweep queue.

- 3. Repeat step 2 until all trees are merged.

- 4. Perform path recovery starting from the collision points of different trees to form the interconnections between required pins.

- 5. Perform the sweeping phase.

Figure 2.11. Sequential version of the algorithm for routing multipin nets using Kruskal's algorithm

(b)

Figure 2.12. Routing of a three pin net using Kruskal's algorithm (a) Initial cycles of the algorithm (b) After connecting all pins

# 3. PARALLELIZATION OF LEE'S ALGORITHM

This chapter presents the principles and ideas used for the parallel implementation of Lee's algorithm. Lee's algorithm is a special case of multipin net algorithms. The ideas and principles for parallel implementation of Lee's algorithm will then be adopted for the parallel implementation of multipin net algorithms.

As indicated in Chapter 2, the Lee's Maze Routing algorithm consists of three phases, namely *front wave expansion*, *path recovery*, *sweeping* phases. Each phase of the algorithm has been parallelized, and the following sections present the proposed parallel algorithms for three phases. Each phase is considered independently.

The sequential complexity of the Lee's maze routing is due to the front wave expansion and sweeping phases. As is discussed in Section 3.2, the parallel front expansion scheme proposed in this chapter avoids interprocessor communication during the distributed sweeping phase computations. However, interprocessor communication can not be avoided during the distributed front wave expansion phase computations. Furthermore, as is discussed in Section 3.1, the processor utilization during the distributed front wave expansion computations is very sensitive to the grid partitioning scheme employed. Hence, the grid partitioning and mapping scheme is chosen by mainly considering the computational requirements of the front wave expansion phase.

## 3.1 Grid Partitioning and Mapping

The effective parallel implementation of the *front wave expansion* algorithm on a hypercube multicomputer requires the partitioning and mapping of the *expansion* computations and the data structures associated with the grid (i.e. *status* array). This partitioning and mapping should be performed in a manner that results in low interprocessor communication overhead and low processor idle time. Even partitioning of the status array onto the node processors is an easy task since a fixed size two dimensional grid is to be partitioned and mapped to the processors of the hypercube. Even partitioning of the expansion computations, on the other hand, is not easy because expansion computations are not predictable and depends on the data (blocked cells etc.). However, as will be explained later, the partitioning of the status array affects the partitioning of expansion computations, and as a result, affects the processor utilization and interprocessor communication overhead.

In the front wave expansion phase, the *atomic* operation can be considered as the *expansion* of a single cell in the current *front wave*. In this *atomic* process, the *north*, *east*, *south*, and *west* adjacent cells of the cell being expanded are examined. Hence, the nature of communication required in *front wave expansion* phase corresponds to a two dimensional mesh. That is, each processor needs to communicate only to its *north*, *east*, *south*, and *west* neighbors. Hence, only mesh embedded hypercube structure will be considered and partitioning and mapping of the grid is done considering only a mesh embedded hypercube structure. It is well known that, a  $2^{\lfloor d/2 \rfloor} x 2^{\lceil d/2 \rceil}$  processor mesh can be embedded into a *d*-dimensional hypercube [11]. Fig. 3.1(a), (b), and (c) represent the mesh embedding into hypercubes of dimensions 2, 3, and 4, respectively.

The even partitioning and mapping of the global status array is trivial since a two dimensional  $N \ge N$  mesh grid is to be partitioned and mapped onto a two dimensional mesh embedded hypercube. This mapping can be achieved by applying *tiled* decomposition in partitioning the grid. Assume that N is a power of two (i.e.  $N = 2^n$ ) and  $n > \lceil d/2 \rceil$ . In the *tiled* decomposition, the grid is covered with rectangles of size  $2^{n-\lfloor d/2 \rfloor} \ge 2^{n-\lceil d/2 \rceil}$  starting from the top left corner and then proceeding left to right and top to bottom. Each rectangle cover

(a)

(b)

Figure 3.1. Mesh embedding (a) hypercube of dimension 2 (b) hypercube of dimension 3 (c) hypercube of dimension 4

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 3 | 3 | 3 | 3 | 2 | 2 | 2 | 2 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 3 | 3 | 3 | 3 | 2 | 2 | 2 | 2 |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 3 | 3 | 3 | 3 | 2 | 2 | 2 | 2 |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 3 | 3 | 3 | 3 | 2 | 2 | 2 | 2 |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 3 | 3 | 3 | 3 | 2 | 2 | 2 | 2 |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 3 | 3 | 3 | 3 | 2 | 2 | 2 | 2 |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 3 | 3 | 3 | 3 | 2 | 2 | 2 | 2 |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 3 | 3 | 3 | 3 | 2 | 2 | 2 | 2 |

| 4 | 4 | 4 | 4 | 5 | 5 | 5 | 5 | 7 | 7 | 7 | 7 | 6 | 6 | 6 | 6 |

| 4 | 4 | 4 | 4 | 5 | 5 | 5 | 5 | 7 | 7 | 7 | 7 | 6 | 6 | 6 | 6 |

| 4 | 4 | 4 | 4 | 5 | 5 | 5 | 5 | 7 | 7 | 7 | 7 | 6 | 6 | 6 | 6 |

| 4 | 4 | 4 | 4 | 5 | 5 | 5 | 5 | 7 | 7 | 7 | 7 | 6 | 6 | 6 | 6 |

| 4 | 4 | 4 | 4 | 5 | 5 | 5 | 5 | 7 | 7 | 7 | 7 | 6 | 6 | 6 | 6 |

| 4 | 4 | 4 | 4 | 5 | 5 | 5 | 5 | 7 | 7 | 7 | 7 | 6 | 6 | 6 | 6 |

| 4 | 4 | 4 | 4 | 5 | 5 | 5 | 5 | 7 | 7 | 7 | 7 | 6 | 6 | 6 | 6 |

| 4 | 4 | 4 | 4 | 5 | 5 | 5 | 5 | 7 | 7 | 7 | 7 | 6 | 6 | 6 | 6 |

Figure 3.2. Tiled decomposition of a 16x16 grid onto 2x4 mesh embedded 3-dimensional hypercube

defines a partition of the grid. These partitions are then mapped to processors in such a way that, partitions that are adjacent in the grid are mapped to adjacent processors of the processor mesh embedded in the hypercube. In this mapping, each processor will be responsible for holding and updating the status information (local status array) for the cells belonging to its local grid partition. Each processor will be responsible for the expansion computations for the cells in its local grid partition. Figure 3.2 illustrates the tiled partitioning scheme for a 16x16 grid for a 2x4 mesh embedded 3-dimensional hypercube.

In the given mapping scheme, a grid cell is defined to be a boundary cell if and only if at least one of its neighbor cells (i.e. north,east,south, west) is in a different partition. It is obvious that only boundary cells have a potential to cause interprocessor communication. The volume of possible interprocessor communication can be reduced by decreasing the number of boundary cells. It is well known that the number of boundary cells in a rectangular partition with fixed number of cells can be minimized by choosing a square partition. The proposed mapping scheme achieves square partitions for even dimensional hypercubes (i.e. even d). For odd dimensional hypercubes the partitions are rectangles with long sides only twice the short sides. Such rectangle partitions minimize the number of boundary cells while maintaining the perfect balanced partitioning of the status array.

The tiled decomposition scheme ensures the mesh communication topology and even distribution of the data structures (status array) among the processors of the hypercube. This mapping scheme also minimizes the volume of interprocessor communication during the front wave expansion phase. However, in spite of these nice properties, it does not ensure the even distribution of the front wave expansion computations. Assume that, in Fig. 3.2, the source cell and the target cell are located at the top left and bottom right corner of the global grid, respectively. Also, assume that there are no blocked cells in the grid. During several initial cycles, only processor  $P_0$  will perform front wave expansion computations while remaining processors stay idle. Similarly, during several final cycles, only  $P_6$  will be busy with front wave expansion computations while the remaining processors stay idle. Hence, the tiled decomposition scheme yields very low processor utilization.

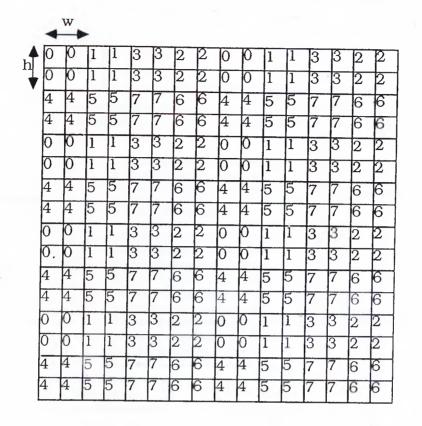

Processor utilization can be maximized by applying *scattered* decomposition scheme. Scattered decomposition scheme is achieved by imposing a periodic processor mesh template over the grid cells starting from the top left corner and proceeding left to right and top to bottom. Figure 3.3 illustrates the scattered decomposition of a 16x16 grid for a 2x4 mesh embedded 3-dimensional hypercube. In this scheme, adjacent grid cells in the grid are assigned to adjacent processors of the mesh embedded hypercube, thus ensuring the mesh communication topology. This scheme also ensures the even distribution of the status array among the processors of the hypercube. However, in the scattered decomposition, all local cells assigned to individual processors are boundary cells. In fact, for  $d \ge 2$ , all four neighbors of an individual local cell belong to adjacent processor communications. Thus, scattered decomposition scheme causes large volume of interprocessor communication.

| 0 | 1 | 3 | 2 | 0 | 1 | 3 | 2 | 0 | 1  | 3 | 2 | 0 | 1 | 3 | 2 |

|---|---|---|---|---|---|---|---|---|----|---|---|---|---|---|---|

| 4 | 5 | 7 | 6 | 4 | 5 | 7 | 6 | 4 | 5  | 7 | 6 | 4 | 5 | 7 | 6 |

| 0 | 1 | 3 | 2 | 0 | 1 | 3 | 2 | 0 | 1  | 3 | 2 | 0 | 1 | 3 | 2 |

| 4 | 5 | 7 | 6 | 4 | 5 | 7 | 6 | 4 | 5  | 7 | 6 | 4 | 5 | 7 | 6 |

| 0 | 1 | 3 | 2 | 0 | 1 | 3 | 2 | 0 | 1  | 3 | 2 | 0 | 1 | 3 | 2 |

| 4 | 5 | 7 | 6 | 4 | 5 | 7 | 6 | 4 | 5  | 7 | 6 | 4 | 5 | 7 | 6 |

| 0 | 1 | 3 | 2 | 0 | 1 | 3 | 2 | 0 | 1  | 3 | 2 | 0 | 1 | 3 | 2 |

| 4 | 5 | 7 | 6 | 4 | 5 | 7 | 6 | 4 | 5  | 7 | 6 | 4 | 5 | 7 | 6 |

| 0 | 1 | 3 | 2 | 0 | 1 | 3 | 2 | 0 | .1 | 3 | 2 | р | 1 | 3 | 2 |

| 4 | 5 | 7 | 6 | 4 | 5 | 7 | 6 | 4 | 5  | 7 | 6 | 4 | 5 | 7 | 6 |

| 0 | 1 | 3 | 2 | 0 | 1 | 3 | 2 | 0 | 1  | 3 | 2 | 0 | 1 | 3 | 2 |

| 4 | 5 | 7 | 6 | 4 | 5 | 7 | 6 | 4 | 5  | 7 | 6 | 4 | 5 | 7 | 6 |

| 0 | 1 | 3 | 2 | 0 | 1 | 3 | 2 | 0 | 1  | 3 | 2 | 0 | 1 | 3 | 2 |

| 4 | 5 | 7 | 6 | 4 | 5 | 7 | 6 | 4 | 5  | 7 | 6 | 4 | 5 | 7 | 6 |

| 0 | 1 | 3 | 2 | 0 | 1 | 3 | 2 | 0 | 1  | 3 | 2 | 0 | 1 | 3 | 2 |

| 4 | 5 | 7 | 6 | 4 | 5 | 7 | 6 | 4 | 5  | 7 | 6 | 4 | 5 | 7 | 6 |

Figure 3.3. Scattered decomposition of 16x16 grid

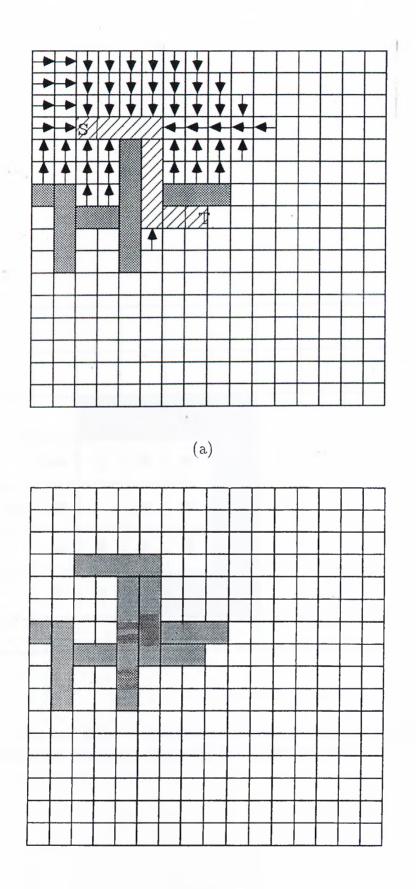

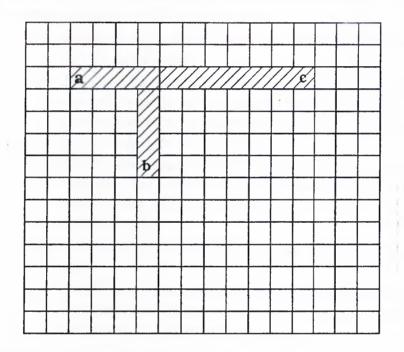

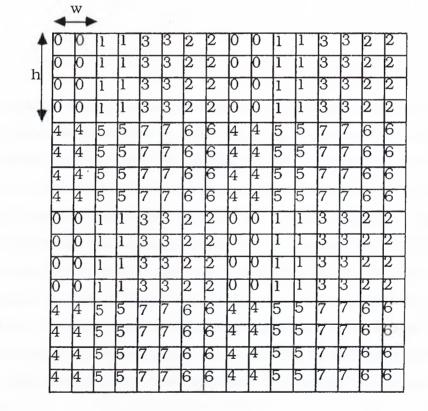

The analysis of these two decomposition schemes shows that there is a trade-off between processor utilization and volume of interprocessor communication. This trade-off is resolved by combining tiled and scattered decomposition schemes as is also proposed in [8]. In this scheme, NxN grid is transformed into a coarse grid by applying tiled decomposition assuming much larger  $P_1 x P_2$ mesh processor array, where  $P_1$  and  $P_2$  are powers of two,  $P_1 = P_2$  for even d,  $P_2 = 2P_1$  for odd d, and  $P_1 x P_2 \gg 2^d$  but  $P_1$  and  $P_2 \leq N$ . Hence, effectively the NxN grid is covered with hxw rectangle (or square) subblocks where  $h = \frac{N}{P_1}$ ,  $w = \frac{N}{P_2}$  and h, w values are power of two where  $h \ll N$ . Then, scattered decomposition is applied to the generated coarse grid. That is, a periodic processor mesh template (of size  $2^{\lfloor d/2 \rfloor} x 2^{\lceil d/2 \rceil}$ ) is imposed over the hxw grid subblocks starting from the top left corner and proceeding left to right and top to bottom. Figure 3.4 shows the mapping of  $2x^2$  and  $4x^2$  grid subblocks over a 16x16 routing grid to the processors of a 2x4 processor mesh embedded in a 3dimensional hypercube. In this scheme, h = w for even hypercube dimensions and h = 2w for odd hypercube dimensions. The width w of the rectangles constitutes the characteristic of the decomposition. This mapping scheme reduces to scattered mapping scheme when h = w = 1 ( $P_1 = P_2 = N$ ) and it reduces to tiled decomposition scheme when  $h = \frac{N}{2^{\lfloor d/2 \rfloor}}$  and  $w = \frac{N}{2^{\lfloor d/2 \rfloor}}$   $(P_1 = 2^{\lfloor d/2 \rfloor}$  and  $P_2 = 2^{\lceil d/2 \rceil}$ ). The processor idle time will decrease with decreasing w. However, the volume of interprocessor communication will decrease with increasing w. Hence, the trade-off between processor utilization and volume of interprocessor communication can be resolved by selecting an appropriate value for w.

#### 3.2 Parallel Front Wave Expansion

#### 3.2.1 Expansion Starting From Source Only

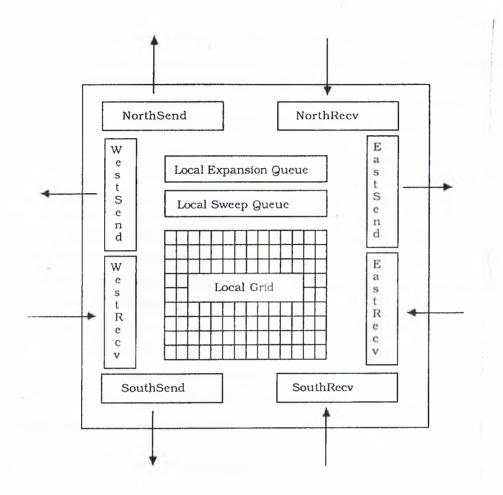

The expansion starting from source only (Sonly) scheme initiates a breadth first search starting from the source cell as in the original Lee's algorithm[7]. The status array is partitioned and mapped onto the node processors according to the mapping scheme presented in section 3.1. Hence, each processor stores and maintains a local status array to keep dynamic and static status information

(a)

(b)

Figure 3.4. Decomposition of 16x16 grid into subblocks of (a) h = w = 2 (b) h = 2w = 4

Figure 3.5. Local data structures for a node processor.

for its local cells. Each processor maintains a local expansion queue to process the *front wave expansion* for its local cells. Each processor also maintains a local *sweep* queue to store the blocked expansion paths for the *sweeping* phase. As is indicated in Section 3.1, the expansion of each local boundary cell require communication with at least one neighbor processor. Hence, in order to accomplish that communication, each processor also maintains four different *send* queues (*north, east, south,* and *west send* queues) for storing and transmitting cell coordinate information to its four neighbor processors in the mesh. Similarly, each processor maintains four *receive* queues to store information sent by its four neighbor processors. Fig. 3.5 illustrates the view of the local data structures for a node processor. The parallel algorithm is given in Fig. 3.6

The local x and y coordinates of the local cells in the current wave are stored in the local circular queues. One byte word Status(x, y) is allocated in Initially, all the local queues are empty. The host processor broadcast the coordinates of the source cell and target cell to all processors. The processor which owns the source cell location adds the local coordinates of the *source* cell to its local queue. Then each processor executes the following algorithm.

- 1. Each processor examines the cells in its local expansion queue for expansion in four directions. The local adjacent cells of the cells being expanded are examined for adding them to the local expansion queue for later expansion. The adjacent cells which are detected to belong to grid partitions assigned to neighbor processors are added to the corresponding *send* queues for later communication.

- 2. Each processor transmits the information in its four *send* queues to their destination processors.

- 3. Each processor examines the cells in its four *receive* queues for adding them to its local queue for later expansion.

- 4. Each processor repeats steps 1, 2, and 3 until host signals the termination of the *front wave expansion* phase.

Figure 3.6. Node program for the Sonly scheme

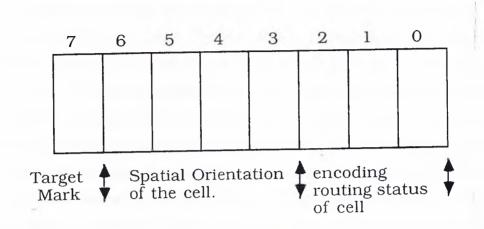

the two dimensional local status array for the status information of each local cell. The encoding of the status of a cell is shown in the Figure 3.7. The least significant three bits (bits 0,1,2) of Status(x,y) hold the current routing status of the local cell located at the local x and y coordinates. Six different routing status information are; blocked, unlabeled, and labeled from north, east, south and west. The status information is obtained by examining the value of these three bits. The values and the meanings are

- 000 : Unlabeled

- 001 : Blocked

- 010 : Labeled from North (Connected to North)

- 011 : Labeled from South

- 100 : Labeled from West

- 101 : Labeled from East.

Figure 3.7. Encoding the status information

As is discussed earlier, the expansion of a boundary cell necessitates interprocessor communication. Hence, each processor should store spatial orientation information in its status array for its local cells. Four bits (bits 3,4,5,6) in the one byte word are reserved for *spatial orientation* information in the local grid of the processor. The assertion of a particular bit indicates that the cell is in the local partition boundary in the corresponding expansion direction. That is, the adjacent cell in that expansion direction is not a local cell, and it is assigned to the neighbor processor in that expansion direction. Hence, that adjacent cell should be added into the particular send queue in that expansion directions. Note that, a cell may be a boundary cell in more than one *expansion* directions. For example, if bit  $b_5$  and bit  $b_6$  is asserted then the cell is at the *north-west* boundary. Also note that, bits  $b_6b_5b_4b_3 = 0000$  indicates that the cell is a local interior cell whose four adjacent cells belong to the local grid partition. This bitwise horizontal encoding scheme for spatial orientation is chosen in order to decrease the complexity of the local expansion computations.

Whenever, the processor which owns the *target* cell *labels* the *target* cell, (either at Step 1 or Step 3), it signals the host about the successful termination. The host processor, upon receiving such a message, broadcasts a message to all processors to terminate the *front wave expansion* phase and enter into the *path recovery* phase. Then, the processor which owns the target cell initiates a *path recovery* beginning from the *target* cell.

If a cell is found to belong to the partition assigned to a neighbor processor, the x,y coordinates of the cell are put into the corresponding send queue and sent to the neighbor processor. However, due to the partitioning of the global grid onto processors, each cell in a processor's local grid has local coordinates. Hence, when the non-local adjacent cell  $a_c$  of a boundary cell c is transferred to a neighbor processor, the x,y coordinates of the cell  $a_c$  have to be converted to the local coordinates in the receiving processor. This conversion operation is an overhead associated with the parallelization. The expansion computation associated with an individual cell has fine granularity. Hence, an efficient scheme should be devised for this conversion in order to keep this overhead low. This conversion can be performed using two schemes. In the first scheme, the local coordinates of the cell is converted to global coordinates and then to the local coordinates of the receiving processor. Such an operation is computationally expensive operation. In the second scheme, the local-to-local conversion is achieved directly. This efficient scheme is briefly discussed in the following paragraph.

Note that, the left-top corner of the global grid (and local grids) is chosen as the origin of the x-y coordinate system. Hence, x-coordinate increases in east direction and y-coordinate increases in the south direction. In the proposed mapping, grid cells in a particular row (column) of the global grid are partitioned into successive contiguous blocks of size w (h). Then, successive cell blocks in a row (column) of the global grid are mapped to the successive processors in a periodically repeating row (column) of the processor mesh template. Hence, local x-coordinates (y-coordinates) of a boundary cell between two successive processors in an individual mesh template differ by w (h). However, if a cell is a boundary cell between two boundary processors in a row (column) of the repeating processor mesh template, then its local coordinates are equal in these two adjacent processors. Note that, local y-coordinates (x-coordinates) of all cells in the same row (column) of the global grid are equal in all processors. Fig. 3.8 illustrates the local indexing of the local status arrays for the mapping of 16x16 grid to a 4x4 mesh embedded 4-dimensional hypercube. As is seen in this figure, w should be added/subtracted for the local-to-local conversions during the east-west communications between the following pairs of adjacent

processors (12-13, 13-15, 15-14), since 12-13-15-14 constitute a row of the processor mesh template. There is no need for conversion during the east-west communications between the pair of adjacent processors (14-12), since this pair of adjacent processors is the boundary processors of the repeating processor mesh template. Similarly, h should be added/subtracted for the local-to-local conversion during the north-south communications between the following pairs of adjacent processors (1-5, 5-13, 13-9), since 1-5-13-9 constitute a column of the processor mesh template. There is no need for conversion during the northsouth communications between the pair of processors (9-1), since this pair of adjacent processors is the boundary processors of the repeating processor mesh template.

In this scheme, each processor statically determines the number to be added for the local-to-local conversion for each boundary expansion direction by examining its particular location in the processor mesh template. Hence, the overhead associated for the local-to-local conversion required during the expansion of a boundary cell in the boundary direction is only a single addition operation.

In spite of the given partitioning scheme, the above parallel algorithm may result in low processor utilization for large h and w values. Some processors may still stay idle particularly during the initial and final front wave expansion cycles. This is due to the expansion of a single front wave beginning from the source cell. Note that, finding a routing path from source to target is equivalent to finding a path from target to source. Hence, two front waves, one beginning from the source (source front wave) and the other one beginning from the target (target front wave), can be expanded concurrently. If the source and the target cells are assigned to different processors, this scheme has a potential to increase the processor utilization.

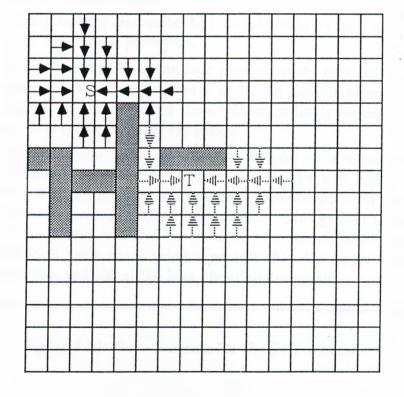

## 3.2.2 Expansion Starting From Source and Target

This scheme initiates breadth first search starting from the target cell as well as starting from the source cell[14]. Figure 3.9(a) illustrates the initial two cycles of this scheme for the example grid shown in Figure 2.1. The Figure 3.9(b)

Figure 3.8. Mapping of local coordinates onto the repeating mesh template

illustrates the *collision* of two concurrent *front waves* initiated from the source cell s and the target cell t. The parallel algorithm for expansion starting from source and target scheme (S+T scheme) is given in Fig. 3.10.

In this scheme, three identifying parameters are needed for each cell in the queues; its local x, y coordinates, and a tag to indicate the type of the front wave it belongs to. The cells that belong to the source front wave are identified with positive x, y coordinate values, whereas, the cells that belong to the target front wave are identified with negative x, y coordinate values. This tagging scheme is chosen in order to keep the local memory requirement due to local queues and the volume of communication low.

Note that, in the local status array the most significant bit of each status byte is unused in the encoding scheme shown in Fig. 3.7. Hence, the most significant bit of each status byte is reserved for *tagging* purposes. If a local cell has a *blocked* or *unlabeled* routing status, this bit conveys no information. If, however, a local cell has a *labeled* routing status, the value of this bit indicates whether the cell is *labeled* on the *target front wave*, or *labeled* on the *source front wave*.

During the expansion process at Step 1, the routing status of four adjacent cells of a cell being expanded are examined. If the current routing status of an adjacent cell is *unlabeled*, the local *x*,*y* coordinates of the adjacent cell are *tagged* accordingly (depending on the *tag* of the cell being expanded) and added to the local queue for later expansion. Then, the adjacent cell is labeled with the reverse expansion direction and *tagged* with the *tag* of the cell being expanded in the local *status* array. However, if the current routing status of an adjacent cell is *blocked* or *labeled* with the same *tag* of the cell being expanded, then the adjacent cell is discarded and added into the local sweep queue. Otherwise, if the adjacent cell is already *labeled* with a different *tag* compared to the *tag* of the cell being expanded, it shows the *collision* of two different *front waves*. The processor which detects the *collision* at Step 1, signals the host about the collision. It also includes the current value of the local cycle count and the local coordinates of the pair of adjacent cells in the message.

At Step 3, the local cells stored in the receive buffers are examined in a

| - | * |  |    |  |  |

|---|---|--|----|--|--|

|   |   |  |    |  |  |

|   |   |  | u) |  |  |

|   |   |  |    |  |  |

|   |   |  |    |  |  |

(a)

(b)

Figure 3.9. Expansion starting from source and target scheme (a) Initial cycles (b) Collision of two front waves

Initially, all local queues are empty and all local cycle counts are initialized to 1. The host processor broadcasts the coordinates of the *source* cell and the *target* cell to all processors. The processor which owns the source cell location adds the local coordinates of the *source* cell together with a source front wave *tag* to its local queue. Similarly, the processor which owns the *target* cell location adds the local coordinates of the *target* cell together with a *target* front wave *tag* to its local queue. Then each processor executes the following algorithm.

- 1. The cells in the local queue may belong either to the current source front wave or to the current target front wave. Each processor examines these cells accordingly for expansion in four directions. The local adjacent cells of the cells being expanded are examined for adding to the local queue for later expansion. The adjacent cells that are detected to belong to grid partitions assigned to neighbor processors are added to the corresponding send queues for later communication together with the tag of the cells being expanded.

- 2. Each processor transmits the information in its four *send* queues to their destination processors.

- 3. The adjacent cells in the four *receive* queues may belong either to the current *source front wave* or to the current *target front wave*. Each processor examines these cells accordingly for adding them to its local queue for later expansion.

- 4. Each processor, after incrementing its local cycle count by 1, checks whether it has received a message from the host. It proceeds to Step 1 if the message has not been received yet or if the message has been received with an upper bound value greater than or equal to the current value of the local cycle count. It terminates only if the local cycle count value is greater than the upper bound value received, and signal the host about its termination.

Figure 3.10. Node program for the S+T scheme.

similar way. However, each individual *collision* at this step will be detected concurrently by two neighbor processors. This situation corresponds to the mutual collision of two different type of *front waves* at two adjacent boundary cells in two adjacent grid partitions assigned to two neighbor processors. For example, if a processor detects a *collision* during the examination of a cell in its *east receive* queue, its *east* neighbor processor will concurrently detect the same *collision* during the examination of a cell in its *west receive* queue. In this case, those two neighbor processors will inform the host about the same *collision*.

The given parallel algorithm does not guarantee that all processors will be executing the same front wave expansion cycle at any instant of time. If a snapshot of the parallel system is taken, some of the processors may be found to be *leading* some others by a number of expansion cycles. A *leading* processor may be the first processor which detects a *collision*. Hence, if the host processor terminates the front wave expansion as soon as it receives a collision message, the path to be recovered may not be the shortest path from source to target. All lagging processors should be allowed to perform expansion until the cycle count of the *leading* processor which has detected the *collision* the first time. Those *lagging* processors have potential to detect collisions on earlier cycles. This is achieved by the scheme given at Step 4 of the algorithm. The host processor, after the receiving the first collision message, broadcasts the cycle count q in this message as an upper bound on the local cycle counts. The leading processors which have already performed the q-th front wave expansion cycle terminate and inform the processor about their termination. The lagging processors which have not yet performed the q-th front wave expansion cycle continue to execute the given algorithm until the q-th cycle. These processors also inform the host about their termination after executing the q-th cycle. Meanwhile, the host processor stores all the subsequent collision messages until it receives P termination messages. The host processor chooses the collision message with a minimum cycle count. Then it broadcasts the coordinates of the chosen pair of adjacent cells to signal the initiation of the path recovery phase.

As is explained earlier, at step 3, two neighbor processors will inform the

host about the same mutual collision. More than one pair of processors may try to inform the host about many such mutual collisions during the same or successive few cycles. In order to decrease message traffic for such situations, the pair of processors detecting the same collision may apply a local precedence relation for informing the host. For example, in a east-west mutual collision, only the processor which detects the collision during examining its west receive queue will inform the host about the collision. The neighbor processor which detects the same collision while examining its east receive queue will take no action for such collisions. The north-south mutual collisions are resolved similarly. This scheme also relieves the host processor from trying to detect such mutual collisions.

In the proposed parallel algorithm, the number of *expansion* cycles to be performed in the front wave expansion phase is reduced by a factor of two compared to the original parallel algorithm. Hence, the total number of local communications is reduced by a factor of two, since the number of local communications per *expansion* cycle is fixed to four. The proposed algorithm is also expected to reduce the total number of expanded cells, on the average, almost by a factor of two. Assume a large grid with no blockages. If the original algorithm requires q expansion cycles to reach the target cell, the proposed algorithm will require only q/2 expansion cycles to reach the collision of two front waves. The total number of cells expanded in the original algorithm will be 1 + 2q(q+1) compared to 2 + q(q+2) in the proposed algorithm[14]. The total number of expanded cells in both algorithms will of course vary when blockages exist in the grid. Unfortunately, the proposed algorithm increases the amount of computation required for the expansion of an individual cell. However, the computational overhead per cell expansion will decrease with increasing blockage percentage in the grid. As is discussed above, an unused bit in a local cell status word and unused bits in the cell coordinate information words are used for *tagging* purposes. In this way, the total memory requirement and communication volume requirement for an individual cell is not increased compared to the original algorithm. Hence, the proposed algorithm will also reduce the total volume of communication since the total number of expanded cells is reduced. Furthermore, the proposed parallel algorithm will increase the processor utilization, compared to the original algorithm, when source and

target cells are assigned to different processors. The relative increase in the processor utilization will grow with increasing h,w parameters, and with increasing mesh distance between the two processors which own the source and the target cells.

## 3.3 Termination Detection

At Step 3 of both parallel algorithms, each processor issues four synchronous (blocking) receive messages in order to receive information from its four neighbor processors. Hence, processors do not proceed to the next front wave expansion cycle before receiving messages from all four neighbors. In order to prevent deadlock, each processor always send messages to its four neighbors even if its send queues are empty. Hence, the synchronous receive messages at Step 3, constitute a local synchronization between neighbor processors. Due to this local synchronization, both of the above parallel algorithms are guaranteed to find the shortest path between the source and the target whenever a path from source to target exists. However, these parallel algorithms will not terminate if no path exists between the source and the target. In the parallel front wave expansion algorithms, the unsuccessful termination condition occurs only when the local expansion queues and the local receive queues of all processors become empty at the same expansion cycle. The schemes to provide global termination detection for such cases are discussed in this section.

## 3.3.1 Global Synchronization

In this scheme, host processor is used to perform global synchronization at the end of each expansion cycle[8]. At the end of each expansion cycle (after Step 4), each processor sends a message to the host to indicate whether its local queue is empty or not. Then each processor issues a synchronous receive to receive an enable message from the host to proceed with the next expansion cycle. Host waits for receiving local queue status information from all processors by issuing P successive synchronous receives. If host detects that all local queues are empty, then it broadcasts a signal to all processor of the hypercube to indicate the unsuccessful termination of the front wave expansion phase. Otherwise, host broadcasts an enable signal to all processors. Hence, no processor can start the (q+1)-th expansion cycle until all other processors complete the q-th expansion cycle. In this scheme, for each expansion cycle, host receives P messages serially and broadcasts the enable message in  $\log_2 P$  time. Thus, this scheme for global termination detection introduces a large amount communication overhead. Furthermore, it decreases the processor utilization since each processor has to be globally synchronized with all other processors (through host) before beginning the next front wave expansion cycle.

### 3.3.2 Counter Termination Scheme1

This scheme is very similar to the scheme proposed in [8]. In this scheme, host processor holds a counter to count the number of non-empty processors. This counter is initialized to 1 in *Sonly* scheme. In S+T scheme, this counter is initialized to 1 if source and target cells belong to the same processor or 2 if source and target cells belong to different processors. The host and node programs for this version of the counter termination scheme for a P processor hypercube are given in Fig. 3.11.

In this scheme host program has to wait for  $\triangle$  seconds after counter becomes 0, since there may be transient messages. This  $\triangle$  seconds is a machine specific parameter. After  $\triangle$  seconds, if there is no message then it means that each processor is empty and there is no transient message. Hence, the host program can terminate the program.

#### 3.3.3 Counter Termination Scheme2

In order to avoid the use of such a machine specific parameter, another counter termination scheme is proposed. In this scheme, host maintains a one dimensional array to keep a counter for each *front wave expansion* cycle. The host and node programs for this version of the counter termination scheme for a P processor hypercube are given in Fig. 3.12.

#### Host Program

- 1. Initialize the counter.

- 2. Enable front wave expansion