## AN EXECUTION TRIGGERED COARSE GRAINED RECONFIGURABLE ARCHITECTURE

A DISSERTATION SUBMITTED TO

THE DEPARTMENT OF ELECTRICAL AND ELECTRONICS

ENGINEERING

AND THE GRADUATE SCHOOL OF ENGINEERING AND SCIENCE

OF BILKENT UNIVERSITY

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

By Oğuzhan Atak December, 2012

| I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Doctor of Philosophy. |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Prof. Dr. Abdullah Atalar (Advisor)                                                                                                                                    |

|                                                                                                                                                                        |

|                                                                                                                                                                        |

| I certify that I have read this thesis and that in my opinion it is fully adequate,                                                                                    |

| in scope and in quality, as a dissertation for the degree of Doctor of Philosophy.                                                                                     |

| Prof. Dr. Erdal Arıkan                                                                                                                                                 |

|                                                                                                                                                                        |

|                                                                                                                                                                        |

| I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Doctor of Philosophy. |

Prof. Dr. Yalçın Tanık

|                             | Prof. Dr. Yusuf Ziya İder                                                |

|-----------------------------|--------------------------------------------------------------------------|

|                             |                                                                          |

|                             |                                                                          |

|                             |                                                                          |

|                             |                                                                          |

|                             |                                                                          |

|                             |                                                                          |

|                             |                                                                          |

|                             |                                                                          |

| n scope and in quality, as  | s a dissertation for the degree of Doctor of P                           |

| n scope and in quality, as  | s a dissertation for the degree of Doctor of P  Prof. Dr. Cevdet Aykanat |

| n scope and in quality, as  |                                                                          |

| n scope and in quality, as  |                                                                          |

| in scope and in quality, as |                                                                          |

| in scope and in quality, as |                                                                          |

| in scope and in quality, as |                                                                          |

| in scope and in quality, as |                                                                          |

| in scope and in quality, as |                                                                          |

|                             | Prof. Dr. Cevdet Aykanat                                                 |

|                             |                                                                          |

|                             | Prof. Dr. Cevdet Aykanat                                                 |

|                             | Prof. Dr. Cevdet Aykanat                                                 |

#### ABSTRACT

# AN EXECUTION TRIGGERED COARSE GRAINED RECONFIGURABLE ARCHITECTURE

Oğuzhan Atak

PhD in Electrical and Electronics Engineering

Supervisor: Prof. Dr. Abdullah Atalar

December, 2012

In this thesis, we present BilRC (Bilkent Reconfigurable Computer), a new coarse-grained reconfigurable architecture. The distinguishing feature of BilRC is its novel execution-triggering computation model which allows a broad range of applications to be efficiently implemented. In order to map applications onto BilRC, we developed a control data flow graph language, named LRC (a Language for Reconfigurable Computing). The flexibility of the architecture and the computation model are validated by mapping several real world applications. LRC is also used to map applications to a 90nm FPGA, giving exactly the same cycle count performance. It is found that BilRC reduces the configuration size about 33 times. It is synthesized with 90nm technology and typical applications mapped on BilRC run about 2.5 times faster than those on FPGA. It is found that the cycle counts of the applications for a commercial VLIW DSP processor are 1.9 to 15 times higher than that of BilRC. It is also found that BilRC can run the inverse discrete cosine transform algorithm almost 3 times faster than the closest CGRA in terms of cycle count. Although the area required for BilRC processing elements is larger than that of existing CGRAs, this is mainly due to the segmented interconnect architecture of BilRC, which is crucial for supporting a broad range of applications.

Keywords: Coarse-grained Reconfigurable Architectures (CGRA), Discrete Cosine Transform (DCT), Viterbi Decoder, Turbo Decoder, Fast Fourier Transform (FFT), Reconfigurable Computing, Field Programmable Gate Arrays (FPGA).

# ÖZET

# YÜRÜTÜME TETİKLEMELİ YENİDEN YAPILANDIRILABİLİR MİMARİ

Oğuzhan Atak Elektrik Elektronik Mühendisliği, Yüksek Lisans Tez Yöneticisi: Prof. Dr. Abdullah Atalar Aralık, 2012

Bu tezde, BilRC olarak adlandırdığımız yeni bir yapılandırılabilir mimari sunuyoruz. BilRC'nin ayırt edici özelliği, geniş bir yelpazedeki uygulamaların etkin bir şekilde gerçeklenmesine imkan sağlayan yürütmeye tetikli hesaplama mimarisidir. Uygulamaları BilRC üzerine yükleyebilmek için LRC (a Language for Reconfigurable Computing) olarak adlandırdığımız bir kontrol data akış diagram dili geliştirildi. Mimarinin ve hesaplama modelinin esnekliği, bir çok uygulamanın BilRC üzerinde gerçeklenmesi ile doğrulandı. LRC dilinde modellenen uygulamalar 90nm teknolojisinde üretilmiş ticari bir FPGA üzerine de yüklendi ve gerçekleme sonuçları karşılaştırıldı. Buna göre, FPGA'yı yapılandırmak için gereken hafıza miktarı BilRC için gereken miktarın ortalama olarak 33 katı olarak bulundu. BilRC 90nm teknolojisinde sentezlendi ve FPGA ile zamanlama karşılaştırması yapıldı. Ortalama olarak BilRC üzerindeki uygulamaların FPGA üzerindeki uygulamalardan 2.5 kat daha hızlı çalıştği bulundu. BilRC, ticari bir DSP işlemci ile de karşılaştırıldı, DSP üzerinde gerçeklenen uygulamalar için gereken saat çevrim sayısının BilRC için gerekenin 1.9 ile 15 kat arasında olduğu bulundu. BilRC'nin IDCT algorimasını, saat çevrimi açısından, literatürdeki en iyi CGRA'dan 3 kat daha hızlı çalıştırdığı bulundu. BilRC'nin diğer CGRA'lara göre dezavantajı işlem birimlerinin kapladığı alanın diğerlerine göre daha büyük olmasıdır. Bunun temel sebebi BilRC'de kullanılan ara bağlantı hatlarının karmaşıklığıdır.

Anahtar sözcükler: Yeniden Yapılandırılabilir Mimariler, Kesikli Kosinüs Dönüşümü, Viterbi Çözücü, Turbo Çözücü, Hızlı Fourier Dönüşümü, Sahada Programlanabilir Mantık Dizisi.

# Acknowledgement

I would like to express my deep gratitude to my supervisor Prof. Abdullah Atalar for his invaluable guidance, support, suggestions and encouragement during the course of this thesis. I am specifically grateful to him that he has installed several Linux servers and Cadence tools by himself to ease my work.

I would also like to thank Prof. Erdal Arikan for his interesting comments and invaluable suggestions.

I would like to thank my thesis progress and thesis defence jury members Prof. Murat Aşkar, Prof. Yavuz Oruç, Prof. Yalçın Tanık, Prof. Ziya İder and Prof. Cevdet Aykanat for their valuable comments and suggestions.

Finally, I would like to thank my family for their patience and great support.

Dedicated to my parents Duran and Ayşe.

# Contents

| 1 | Intr | oducti  | on                                        | 1  |

|---|------|---------|-------------------------------------------|----|

| 2 | Bill | RC Arc  | chitecture                                | 6  |

|   | 2.1  | Interco | onnect Architecture                       | 6  |

|   | 2.2  | Proces  | ssing Core Architectures                  | 10 |

|   |      | 2.2.1   | MEM                                       | 10 |

|   |      | 2.2.2   | ALU                                       | 11 |

|   |      | 2.2.3   | MUL                                       | 12 |

|   | 2.3  | Config  | guration Architecture                     | 13 |

| 3 | Exe  | cution  | -Triggered Computation Model              | 15 |

|   | 3.1  | Proper  | rties of LRC                              | 16 |

|   |      | 3.1.1   | LRC is a spatial language                 | 16 |

|   |      | 3.1.2   | LRC is a single assignment language       | 16 |

|   |      | 3.1.3   | LRC is cycle accurate                     | 17 |

|   |      | 3.1.4   | LRC has an execution-triggering mechanism | 17 |

CONTENTS ix

|   | 3.2 | Advant | tages of Execution Triggered Computation Model | 17 |

|---|-----|--------|------------------------------------------------|----|

|   | 3.3 | Modeli | ng Applications in LRC                         | 20 |

|   |     | 3.3.1  | Loop Instructions                              | 21 |

|   |     | 3.3.2  | Modeling Memory in LRC                         | 23 |

|   |     | 3.3.3  | Conditional Execution Instructions             | 24 |

|   |     | 3.3.4  | Initialization Before Loops                    | 26 |

|   |     | 3.3.5  | Delay Elements in LRC                          | 27 |

|   |     | 3.3.6  | Utilization of the Second Output               | 28 |

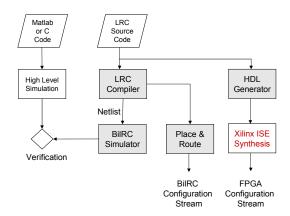

| 4 | Too | ls and | Simulation Environment                         | 30 |

|   | 4.1 | LRC C  | Compiler                                       | 30 |

|   | 4.2 | BilRC  | Simulator                                      | 31 |

|   | 4.3 | Placem | nent & Routing Tool                            | 31 |

|   | 4.4 | HDL 8  | generator                                      | 32 |

| 5 | Exa | mple A | Applications for BilRC                         | 33 |

|   | 5.1 | Maxim  | num Value of an Array (maxval)                 | 33 |

|   | 5.2 | Dot Pr | roduct of two Vectors                          | 35 |

|   | 5.3 | Finite | Impulse Response Filters                       | 36 |

|   | 5.4 | 2D-ID0 | CT Algorithm                                   | 39 |

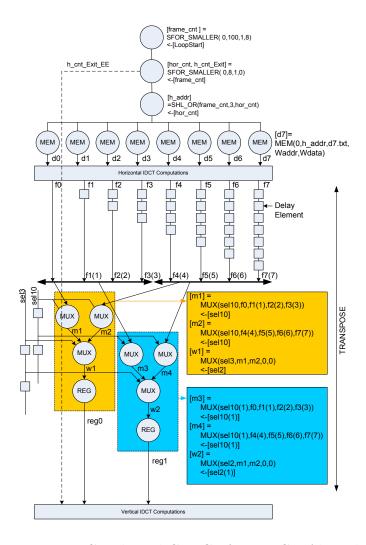

|   | 5.5 | FFT A  | dgorithm                                       | 42 |

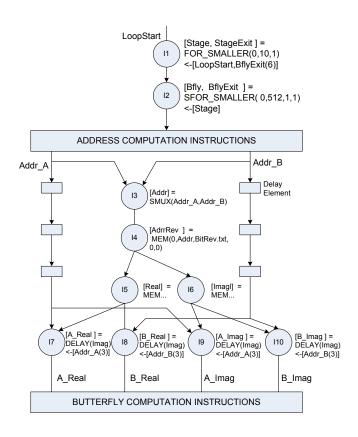

|   | 5.6 | Viterb | oi Decoder                                     | 43 |

CONTENTS

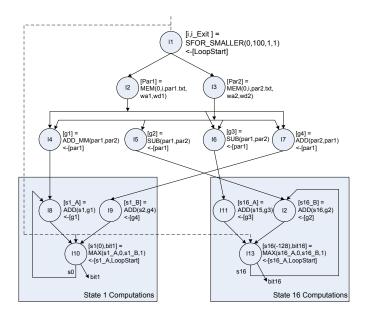

|              | 5.7  | UMTS Turbo Decoder                 | 46 |

|--------------|------|------------------------------------|----|

| 6            | Res  | ults                               | 49 |

|              | 6.1  | Physical Implementation            | 49 |

|              | 6.2  | Comparison to TI C64+ DSP          | 50 |

|              | 6.3  | Comparison to Xilinx Virtex-4 FPGA | 52 |

|              | 6.4  | Comparison to other CGRAs          | 55 |

| 7            | Con  | clusion                            | 58 |

| $\mathbf{A}$ | Acr  | onyms                              | 68 |

| В            | Inst | ruction Set Of BilRC               | 70 |

|              | B.1  | ABS                                | 70 |

|              | B.2  | ADD                                | 70 |

|              | В.3  | ADD_MM                             | 70 |

|              | B.4  | ADD_C                              | 71 |

|              | B.5  | AND                                | 71 |

|              | B.6  | BIGGER                             | 71 |

|              | B.7  | DELAY                              | 71 |

|              | B.8  | EQUAL                              | 72 |

|              | B.9  | FOR_BIGGER                         | 72 |

|              | B.10 | FOR_SMALLER                        | 72 |

CONTENTS xi

|              | B.11 MAX                   | 73 |

|--------------|----------------------------|----|

|              | B.12 MAX                   | 73 |

|              | B.13 MERGE                 | 73 |

|              | B.14 MUL_SHIFT             | 74 |

|              | B.15 MULTIPLEX             | 74 |

|              | B.16 NOT                   | 74 |

|              | B.17 NOT_EQUAL             | 75 |

|              | B.18 OR                    | 75 |

|              | B.19 SAT                   | 75 |

|              | B.20 SMUX                  | 75 |

|              | B.21 SFOR_BIGGER           | 76 |

|              | B.22 SFOR_SMALLER          | 76 |

|              | B.23 SHL_AND               | 76 |

|              | B.24 SHL_OR                | 76 |

|              | B.25 SHR_AND               | 77 |

|              | B.26 SHR_OR                | 77 |

|              | B.27 SMALLER               | 77 |

|              | B.28 SUB                   | 77 |

|              | B.29 XOR                   | 78 |

| $\mathbf{C}$ | LRC code of the Algorithms | 79 |

CONTENTS xii

| C.1  | 2D IDCT Algorithm              | 79 |

|------|--------------------------------|----|

| C.2  | Maxval Algorithm               | 83 |

| C.3  | Dot Product Algorithm          | 84 |

| C.4  | Maxidx Algorithm               | 85 |

| C.5  | 32-Tap FIR Fiter               | 86 |

| C.6  | Vecsum Algorithm               | 87 |

| C.7  | Fircplx Algoritm               | 87 |

| C.8  | 16-State Viterbi Algorithm     | 92 |

| C.9  | UMTS Turbo Decoder Algorithm   | 94 |

| C.10 | FFT Algorithm                  | 97 |

| C.11 | Multirate FIR Filter Algorithm | 98 |

| C.12 | Multichannel FIR Filter        | 99 |

# List of Figures

| 2.1 | Columnwise allocation of PEs in BilRC           | 7   |

|-----|-------------------------------------------------|-----|

| 2.2 | Input/Output Signal Connections                 | 8   |

| 2.3 | Schematic Diagram of PRB                        | 9   |

| 2.4 | An example of routing between two PEs           | 10  |

| 2.5 | Processing Core Schematic of MEM                | 11  |

| 2.6 | Processing Core Schematic of ALU                | 12  |

|     |                                                 |     |

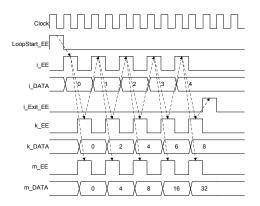

| 3.1 | Example CDFG and Timing Diagram                 | 16  |

| 3.2 | CDFG and LRC example for FOR_SMALLER            | 22  |

| 3.3 | Timing Diagram of FOR_SMALLER                   | 22  |

| 4 1 |                                                 | 0.1 |

| 4.1 | Simulation and Implementation Environment       | 31  |

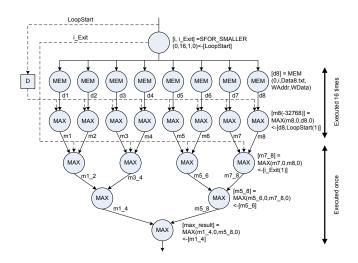

| 5.1 | LRC Code and CDFG of Maximum Value of an Array  | 34  |

|     |                                                 |     |

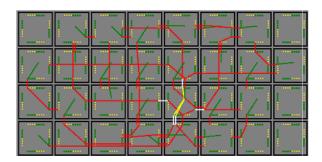

| 5.2 | Maxval algorithm placement and routing on BilRC | 36  |

| 5.3 | Part of the CDFG of dot product algorithm       | 37  |

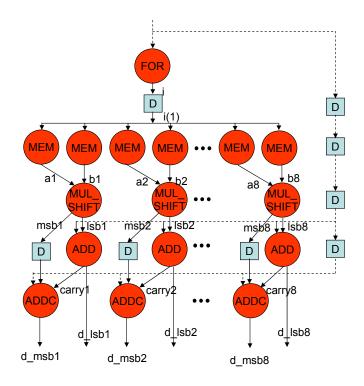

| 5.4 | LRC code and CDFG of 2D-IDCT Algorithm          | 41  |

|     |                                                 |     |

| LIST OF FIGURES | xiv |  |

|-----------------|-----|--|

|                 |     |  |

| 5.5 | LRC code and CDFG of FFT                | 42 |

|-----|-----------------------------------------|----|

| 5.6 | LRC code and CDFG of Viterbi Decoder    | 44 |

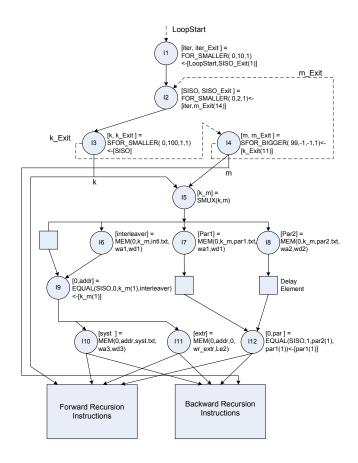

| 5.7 | LRC code and CDFG of UMTS Turbo Decoder | 46 |

# List of Tables

| 2.1 | Configuration data structure                                           | 13 |

|-----|------------------------------------------------------------------------|----|

| 2.2 | ALU Configuration Register                                             | 14 |

| 3.1 | Conditional Assignment Instructions in LRC                             | 26 |

| 6.1 | Timing Performance of PEs                                              | 50 |

| 6.2 | Areas of PEs with 90nm UMC process                                     | 50 |

| 6.3 | Cycle count performance of benchmarks                                  | 51 |

| 6.4 | Comparison of configuration sizes of BilRC and Xilinx Virtex<br>4 $$ . | 53 |

| 6.5 | Configuration Frames for FPGA Resources                                | 55 |

| 6.6 | Critical Path Comparison of BilRC and FPGA                             | 56 |

| 6.7 | Area, Timing and Cycle Count Results for the 2D-IDCT Algorithm         | 56 |

| 6.8 | IPC and Scheduling Density Comparison                                  | 57 |

# Chapter 1

# Introduction

To comply with the performance requirements of emerging applications and evolving communication standards, various architecture alternatives are available. FP-GAs compete with their large number of logic resources. For example, the largest Xilinx Virtex-7 FPGA can provide 6737 GMACS (Giga Multiply and Accumulate per Second) with its 5280 DSP slices<sup>1</sup> and it has 4720 embedded BRAMs each with a 18 Kbits capacity. The main disadvantage of FPGA is the lack of run-time programmability. To maximize the device utilization, FPGA designers partition the available resources among several sub-applications in such a manner that each application works at the chosen clock frequency and complies with the throughput requirement. The design phases of FPGAs and ASICs are quite similar except that ASICs lack post-silicon flexibility. For both FPGAs and ASICs, the function blocks in the application are partitioned to hardware resources spatially.

Unable to exploit the space dimension, DSPs fail to provide the performance requirement of many applications due to the limited parallelism that a sequential architecture can provide. This limitation is not due to the area cost of logic resources, but to lack of a computation model to exploit such a large number of logic resources. Commercial DSP vendors produce their DSPs with several accelerators. For example, Texas Instruments TMS320c6670 DSP has a Turbo

<sup>&</sup>lt;sup>1</sup>http://www.xilinx.com/support/documentation/data\_sheets/ds180\_7Series\_Overview.pdf

Decoder Coprocessor, FFT and Viterbi decoder accelerators for WCDMA, LTE and WiMAX standards. The disadvantage of such an approach is that the accelerators are designed considering only the applications and standards developed until that time, therefore these accelerators could be useless for emerging applications and evolving standards.

Application-specific instruction-set processors (ASIP) provide high performance with dedicated instructions having very deep pipelines. The basic idea behind the ASIP approach is to shrink the instructions in the loop body into a single or a few instructions so that the number of cycles spent for the loop kernel is reduced. For example, the FFT processors presented in [1, 2, 3, 4] have special instructions for the FFT kernel. ASIPs are designed in general for a specific algorithm or algorithms having similar computation kernel. For example, an ASIP [5] with a 15-pipeline stage is presented for various Turbo and convolutional code standards. A Multi-ASIP [6] architecture is presented for exploiting different parallelism levels in the Turbo decoding algorithm. The basic limitation of the ASIP approach is its weak programmability, which makes it inflexible for emerging standards. For instance, aforementioned ASIPs do not support Turbo codes with more than 8-states [6] and 16-states [5]. In order to make ASIPs flexible after fabrication, reconfigurable ASIPs (rASIP) have been proposed [7] having programmable function generators similar to that of FPGAs.

Coarse-grained reconfigurable architectures (CGRA) have been proposed to provide a better performance/flexibility balance than the alternatives discussed above. Hartenstein [8] compared several CGRAs according to their interconnection networks, data path granularities and application mapping methodologies. In a recent survey paper, De Sutter et al. [9] classified several CGRAs according to computation models while discussing the relative advantages and disadvantages. Compton et al. [10] discussed reconfigurable architectures containing heterogeneous computation elements such as CPU and FPGA, and compared several fine- and coarse-grained architectures with partial and dynamic configuration capability. According to the terminologies used in the literature [8, 9, 10], reconfigurable architectures (RA), including FPGAs, can be classified according to the configuration in three distinct models as single-time configurable, statically

reconfigurable and dynamically reconfigurable. Statically reconfigurable RAs are configured at loop boundaries, whereas dynamic RAs can be configured at almost each clock cycle. The basic disadvantage of statically reconfigurable RAs is that if the loop to be mapped is larger than the array size, it may be impossible to map. However, the degree of parallelism inside the loop body can be decreased to fit the application to CGRA. This is the same approach that designers use for mapping applications to an FPGA. In dynamically reconfigurable RAs, the power consumption can be high due to fetching and decoding of the configuration at every clock cycle. However, techniques have been proposed [11, 12] to reduce power consumption due to dynamic configuration. The interconnect topology of RAs can be either one-dimensional (1D) such as PipeRench [13, 14, 15] and RAPID [16, 17] or two-dimensional (2D) such as ADRES [18, 19, 20, 21, 22], MorphoSys [23], MORA [24, 25], REMARC [26], GARP [27, 28], KressArray[29, 30], RAW [31], MATRIX [32], COLT [33], PACT XPP [34, 35, 36] and conventional FPGAs.

RAs can have a point to point (p2p) interconnect structure as in ADRES, MORA, MorphoSys and PipeRench or a segmented interconnect structure as in KressArray, RAPID and conventional FPGAs. p2p interconnect has the advantage of deterministic timing performance. The clock frequency of the RA does not depend on the application mapped while the fanout of the Processing Elements (PE) is limited. If an operation has more sinks than the interconnects allow, one of the PEs is used to delay the data for one clock cycle. Limited p2p interconnect may increase the initiation interval [20] and cause performance degradation. For the segmented interconnect method, the output of a PE can be routed to any PE, while the timing performance depends on the application mapped. For FPGAs, the timing closure is similar to that of ASICs and is quite tedious, whereas for a segmented-interconnect CGRA timing closure is rather simple due to coarser granularity.

The execution control mechanism of RAs can be either of a statically scheduled type such as MorphoSys and ADRES, where the control flow is converted to data flow code during compilation, or a dynamically scheduled type such as KressArray, which uses tokens for execution control.

In this thesis, we present BilRC<sup>2</sup>, a statically reconfigurable CGRA with a 2D segmented interconnect architecture utilizing dynamic scheduling with execution triggering. KressArray is the most similar architecture with some basic differences: First, KressArray uses a data-driven execution control mechanism together with a centralized sequencer, whereas BilRC with no centralized controller, the execution control is distributed. Second, KressArray uses a dynamic global bus for both primary input/output and temporary data transfer in between PEs, and local static interconnect for PE communication, BilRC uses a segmented static interconnect for all communication requirements. Third, KressArray does not have any multiplier and memory unit in the array architecture which limits the applications that can be mapped on. BilRC, like FPGAs, have memory and multiplier PEs so that almost all applications can be implemented. Our contributions can be summarized as follows:

- An execution triggered computation model is presented and the suitability

of the model is validated with several real world applications. For this

model, a language for reconfigurable computing, LRC, is developed.

- A new CGRA employing segmented interconnect architecture with three types of PEs and its configuration architecture is designed in 90nm CMOS technology. The CGRA is verified up to the layout level.

- Full tool flow including a compiler for LRC, a cycle accurate SystemC simulator and a placement & routing tool for mapping applications to BilRC are developed.

- CGRAs are known to reduce configuration size, however there is no work on configuration size comparison of CGRAs and FPGAs. The applications modeled in LRC are converted to HDL with our LRC-HDL converter and then mapped onto an FPGA and to BilRC on a-cycle-by-cycle equivalent basis. Then, a comparison of precise configuration size and timing is done.

- It is known that CGRAs can provide better timing performance as compared to FPGAs. However, there is no work on comparing the timing

<sup>&</sup>lt;sup>2</sup>BilRC: Bilkent Reconfigurable Computer

performance of the two. Thanks to LRC and LRC-HDL generator, the critical path for several applications are found for both FPGA and BilRC for a timing performance comparison.

• The segmented interconnect structure is rather mature for FPGAs, however the required number of tracks (ports) for CGRAs has not been explored yet. We used state of the art placement and routing heuristics to minimize the number of ports required to implement several applications with challenging communication requirements.

The rest of the thesis is organized as follows: In Chapter 2, the architecture of PEs and the configuration mechanism are presented. Chapter 3 discusses the execution triggered computation model. In Chapter 4, the tools developed for application mapping to BilRC and FPGA are explained. In Chapter 5, mapping of a number of applications to BilRC is presented. The physical implementation results, cycle count performance, the critical path performance and a configuration size comparison are given in Chapter 6. The thesis is concluded in Chapter 7.

# Chapter 2

# BilRC Architecture

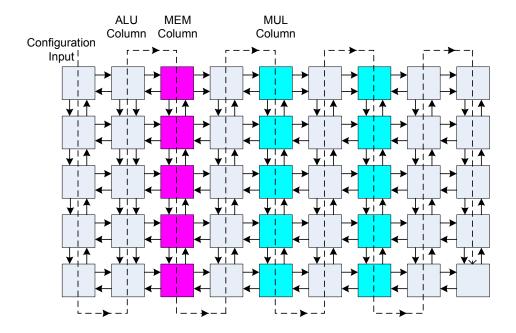

BilRC has three types of PEs: Arithmetic logic unit (ALU), memory (MEM) and multiplier (MUL). Similar to the some commercial FPGA architectures such as Stratix<sup>1</sup> and Virtex<sup>2</sup>, PEs of the same type are placed in the same column as shown in Fig 2.1. The architecture repeats itself every nine columns and the number of rows can be increased without changing the distribution of PEs. This PE distribution is obtained by considering several benchmark algorithms from signal and image processing and telecommunication applications. The PEs' distribution can be adjusted for better utilization for the targeted applications. For example, the Turbo decoder algorithm does not require any multiplier, but needs a large amount of memory. On the other hand, filtering applications require many multipliers, but not much memory. For the same reason, commercial FPGAs have different families for logic-intensive and signal processing-intensive applications.

#### 2.1 Interconnect Architecture

PEs in BilRC are connected to four neighboring PEs [2] by communication channels. Channels at the periphery of the chip can be used for communicating with

<sup>&</sup>lt;sup>1</sup>http://www.altera.com

<sup>&</sup>lt;sup>2</sup>http://www.xilinx.com

Figure 2.1: Columnwise allocation of PEs in BilRC

the external world.

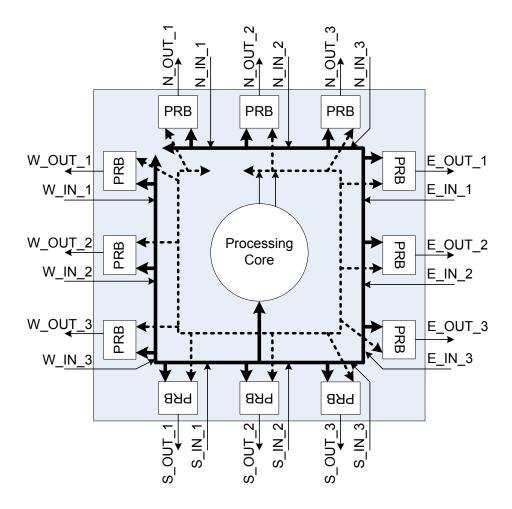

If the number of ports in a communication channel is  $N_p$ , the total number of ports a PE has is  $4N_p$ . The interconnect architecture is the same for all PE types. Fig. 2.2 illustrates the signal routing inside a PE for  $N_p = 3$ . There are three inputs and three outputs on each side. The output signals are connected to corresponding input ports of the neighbor PEs. The input and output signals are all 17 bits wide. 16 bits are used as data bits and the remaining *Execute Enable* (EE) bit is used as the control signal.

PEs contain processing cores (PC) located in the middle. Port route boxes (PRB) at the sides are used for signal routing. PCs of ALUs and MULs have two outputs and the PC of MEM has only one output. Each PC output is a 17 bit signal. The second output of a PC is utilized for various purposes, such as the execution control for loop instructions, the carry output of additions, the most significant part of multiplication, the maximum value of index calculation and the conditional execution control. PC outputs are routed to all PRBs. Therefore, any PRB can be used to route PC output in the desired direction. All input signals

Figure 2.2: Input/Output Signal Connections

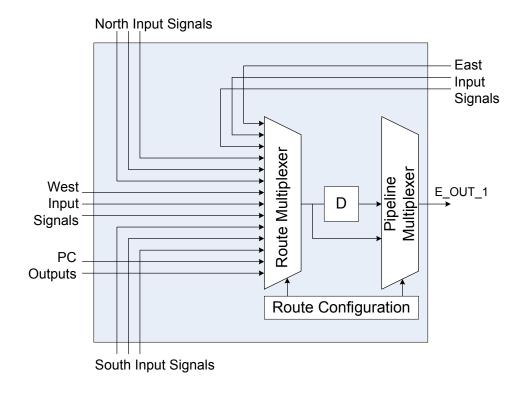

are routed to all PRBs and to the PC as shown in Fig. 2.2. The PC selects its operands from the input signals by using internal multiplexers. Fig. 2.3 shows the internal structure of PRB. The Route multiplexer is used to select signals coming from all input directions and from the PC. The pipeline multiplexer is used to optionally delay the output of the route multiplexer for one clock cycle. The idea of using multiplexers for signal routing has already been used in [37]. BilRC is configured statically, hence both the interconnects and the instructions programmed in PCs remain unchanged during the run.

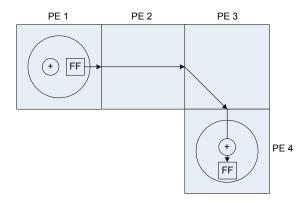

Fig. 2.4 shows an example mapping.  $PE_1$  is the source and  $PE_4$  is the destination while  $PE_2$  and  $PE_3$  are used for signal routing. It must be noted that the pipelining elements are not used. Inside  $PC_1$  an instruction is executed and

Figure 2.3: Schematic Diagram of PRB

the result is registered. The critical path starts from the output of the source PC. Then, the signal is routed through PE<sub>2</sub> and PE<sub>3</sub>.  $T_{HOP}$  is the time delay to traverse a PE (without using the pipelining element in PRB). Finally, the signal at PE<sub>4</sub> goes through the adder and reaches the output register in PC with a time delay of  $T_{PE}$ . The total delay,  $T_{CRIT}$ , between the register in PE<sub>1</sub> and the register in PE<sub>4</sub> is given as

$$T_{CRIT} = nT_{HOP} + T_{PE} (2.1)$$

where n=2 is the number of hops,  $T_{HOP}$  is the time delay to traverse one PE and  $T_{PE}$  is the time delay within a PE.

Figure 2.4: An example of routing between two PEs.

## 2.2 Processing Core Architectures

#### 2.2.1 MEM

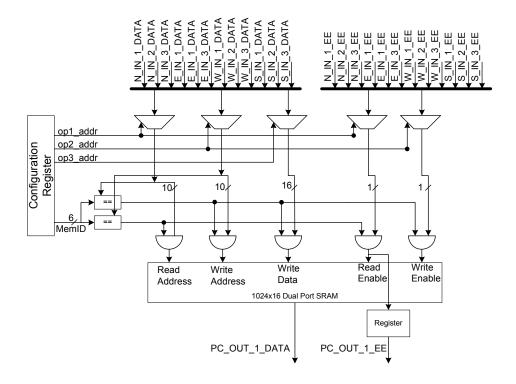

Fig. 2.5 shows the architecture of the processing core of MEM. PC has a data bus which is formed from all input data signals and an execute enable bus which is formed from all input EE signals. SRAM block in PC is a 1024×16 dual port RAM (10 address bits, 16 data bits). opl\_adr set by the configuration register determines which one of the 12 inputs is the read address. Similarly, op2\_adr chooses one of the inputs as the write address. The most significant six bits are compared with MemID stored in the configuration register. If they are equal, then read and/or write operations are performed. opr3\_addr selects the data to be written from one of the input ports. One of the input ports of SRAM is used only for writing and the other one is used only for reading. The read address and read enable signals are selected by op1\_adr from the data bus and the execute enable bus, respectively. The least significant 10 bits of data are used as the read address for SRAM and the most significant 6 bits are used as the Memory ID (MemID). MemID is used to form larger memory arrays by using multiple MEMs. If MemID in the data bus is equal to MemID in the configuration register, the data at location addressed by the read address signal is read and the output execute enable signal, (PC\_OUT\_1\_EE), is enabled. If MemIDs are not equal, the output signal is disabled. The write address and write enable signals are selected by op2\_adr in a similar way.

Figure 2.5: Processing Core Schematic of MEM

#### 2.2.2 ALU

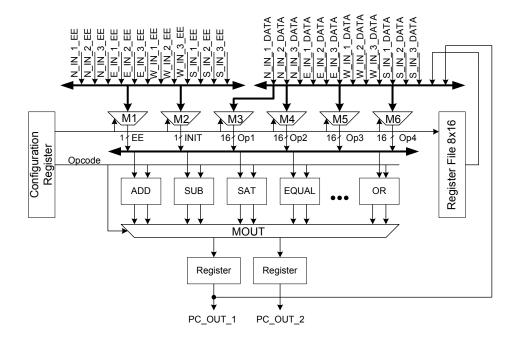

Fig. 2.6 shows the architecture of ALU. Similar to MEM, ALU has two buses for input data and execute enable signals. The instruction to be executed in ALU is programmed during configuration and the ALU executes the same instruction during application run. The operands to the instructions are selected from the data bus by using the multiplexers M3, M4, M5, M6. ALU has an  $8\times16$  register file for storing constant data operands. For example, an ALU with the instruction, ADD(A,100) reads the variable A from an input port and the constant 100 is stored in the register file during configuration. The output of the register file is connected to the data bus so that the instruction can select its operand from the register file. The execution of the instruction is controlled from the execute enable bus. The configuration register has a field to select the input execute enable signal from the execute enable bus. PC executes the instruction when the selected signal is enabled.

Figure 2.6: Processing Core Schematic of ALU

#### 2.2.3 MUL

The processing core of MUL is similar to that of ALU. The difference is the instructions supported in the two types of PEs. Multiplication and shift instructions are performed in this PE. The MUL instruction performs the multiplication operation on two operands. The operands can be from the inputs (variable operands) or from the register file (constant operands). The result of the multiplication is a 32-bit number that appears on two output ports. The most significant part of the multiplication is put on the second output, and the least significant part is put on the first output. Alternatively, the result of the multiplication can be shifted to the right in order to fit the result to a single output port by using the MUL\_SHR (multiply and shift to the right) instruction. This instruction executes in two clock cycles: the multiplication is performed in the first clock cycle and the shifting is performed in the second clock cycle. The rest of the instructions for all PEs are executed in a single clock cycle. The shift operation is performed by a barrel shifter. The remaining instructions supported in MUL are the instructions requiring a barrel shifter.

Table 2.1: Configuration data structure

| Conf. Item            | number of | Meaning                            |

|-----------------------|-----------|------------------------------------|

|                       | words     |                                    |

| PID                   | 1         | Processing Element ID              |

| N                     | 1         | Number of words in the configu-    |

|                       |           | ration packet                      |

| Configuration Regis-  | 3         | PC configuration register          |

| ter (CR)              |           |                                    |

| Route Configuration   | 5         | It is used to configure multiplex- |

| Register (RCR)        |           | ers in the PRBs                    |

| Output Initialization | 1         | loads the register for output ini- |

| Register              |           | tialization                        |

| Register File or Mem- | variable  | The register file of ALU or MEM    |

| ory Content Configu-  |           | or the SRAM of the MEM is ini-     |

| ration                |           | tialized                           |

## 2.3 Configuration Architecture

PEs are configured by configuration packets which are composed of 16-bit configuration words. Table 2.1 lists the data structure of the configuration packet. Each PE has a 16-bit-wide configuration input and a configuration output. These signals are connected in a chain structure as shown in Fig. 2.1. The first word of the configuration packet is the processing element ID (PID). It is used to address the configuration packet to a specific PE. A PE receiving the configuration packet uses it if the PID matches its own ID, otherwise it is forwarded to the next PE in the chain. The second word in the packet is the length of the configuration packet, this word is useful for register and memory initializations to indicate the size of the configuration packet. The configuration register (CR) is used to configure PC. The fields of the CR are illustrated in Table 2.2 for ALU. The configuration register of MEM does not require the fields opr4\_adr, EE\_adr, Init\_Addr, Init\_type and Init\_Enable, and the configuration register of MUL does not contain the opr4\_addr field, since none of the instructions require four operands. CR is 48 bits long for all PC types; the unused bit positions are reserved for future use. It must be noted that the bit width of the configuration register and the route configuration register depends on  $N_p$ . The number of words

Table 2.2: ALU Configuration Register

|             |         | <u> </u>                                     |

|-------------|---------|----------------------------------------------|

| Conf. Field | number  | Meaning                                      |

|             | of bits |                                              |

| opr1_addr   | 5       | Operand 1 Address                            |

| opr2_addr   | 5       | Operand 2 Address                            |

| opr3_addr   | 5       | Operand 3 Address                            |

| opr4_addr   | 5       | Operand 4 Address                            |

| EE_addr     | 5       | Execute Enable Input Address                 |

| Init_addr   | 4       | Initialization Input Address                 |

| op_code     | 8       | Selects the instruction to be executed       |

| Init_Enable | 1       | Determines whether the PC has an initializa- |

|             |         | tion or not                                  |

| Init_Type   | 1       | Determines the type of the initialization    |

for the fields given in the table is for  $N_p=4$ .

# Chapter 3

# Execution-Triggered Computation Model

Writing an application in a high-level language, such as C and then mapping it on the CGRA fabric is the ultimate goal for all CGRA devices. To get the best performance from the CGRA fabric, a middle-level language (assembly-like language) that has enough control on PEs and provides abstractions is necessary. The designers thus do not deal with unnecessary details, such as the location of the instructions in the 2D architecture and the configuration of route multiplexers for signal routing. Although there are compilers for some CGRAs which directly map applications written in a high-level language such as C to the CGRA [38, 34, 39, 28], the designers still need to understand the architecture of the CGRA in order to fine tune applications written in C-code for the best performance [9].

The architecture of BilRC is suitable for direct mapping of control data flow graphs (CDFG). A CDFG is the representation of an application in which operations are scheduled to the nodes (PEs) and dependencies are defined. We developed a *Language for Reconfigurable Computing* (LRC) for the efficient representation of CDFGs. In this thesis, it is assumed that the CDFG is available, generating CDFGs from a high level language is out of the scope of this work. Existing tools such as IMPACT [21] can be used to generate a CDFG in the form of

Figure 3.1: Example CDFG and Timing Diagram

an intermediate representation called LCode. IMPACT reads a sequential code, draws a data flow graph and generates a representation defining the instructions that are executed in parallel. Such a representation can then be converted to an LRC code.

## 3.1 Properties of LRC

#### 3.1.1 LRC is a spatial language

Unlike sequential (imperative) languages, the order of instructions in LRC is not important. LRC instructions have execution control inputs that trigger the execution. LRC can be considered as a graph drawing language in which the instructions represent the nodes and the data and control operands (dependencies) represent the connections between the nodes.

## 3.1.2 LRC is a single assignment language

LRC is a functional language similar to Single-Assignment-C language [40, 41]. During mapping to the PEs, each LRC instruction is assigned to a single PE. Therefore, the output of the PEs must be uniquely named. A variable can be

assigned to multiple values indirectly in LRC by using the self-multiplexer instruction, SMUX. Examples for SMUX are provided in Chapter 3.3.2 and Chapter 5.7.

#### 3.1.3 LRC is cycle accurate

In LRC, the number of clock cycles spent for the execution of an instruction is deterministic. Each instruction in LRC, except MUL\_SHR, is executed in a single clock cycle. Therefore, even before mapping to the architecture, cycle-accurate simulations are possible to obtain timing diagrams of the application.

#### 3.1.4 LRC has an execution-triggering mechanism

LRC instructions have explicit control signal(s), which trigger the execution of instruction assigned to the node. Instructions that are triggered from the same control signal execute concurrently, hence parallelism is explicit in LRC, i.e., the application designer can control the degree of parallelism.

# 3.2 Advantages of Execution Triggered Computation Model

The execution-triggered computation model can be compared to the data flow computation model [42]. The basic similarity is that both models build a data flow graph such that nodes are instructions and the arcs between the nodes are operands. The basic difference is that the data flow computation model uses tagged tokens to trigger execution; a node executes when all its operands (inputs) have a token and the tags match. Basically, tokens are used to synchronize operands and tags are used to synchronize different loop iterations. In LRC an instruction is executed when its execute enable signal is active. Application of the data flow computation model to CGRAs has the following problems: first, tagged tokens require a large number of bits; this in turn increases the interconnect area.

For example, the Manchester Machine [42] uses 54 bits for tagged tokens. Second, a queue is required to store tagged tokens which increases the area of PE. Third, a matching circuit is required for comparing tags, both increasing PE area and decreasing performance. For example, an instruction with three operands requires two pairwise tag comparisons to be made. Execution-triggered computation uses a single bit as execute enable; hence it is both area efficient and fast.

The execution-triggered computation model can be compared to the computation models of existing CGRAs. MorphoSys [23] uses a RISC processor for the control-intensive part of the application. The reconfigurable cell array is intended for the data-parallel and regular parts of the application. There is no memory unit in the array; instead, a frame buffer is used to provide data to the array. The RISC processor performs loop initiation and context broadcast to the array. Each reconfigurable cell runs the broadcast instructions sequentially. This model has many disadvantages. First, an application cannot be always partitioned into control-intensive and data-intensive parts, and even if it is partitioned, the intercommunication between the array and RISC creates a performance bottleneck. Second, the lack of memory units in the array limits the applications that can be run on the array. Third, the loop initiation is controlled by the RISC processor, hence the array can be used only for innermost loops.

ADRES[21] uses a similar computation model with some enhancements, the RISC processor is replaced with a VLIW processor. ADRES is a template CGRA. Different memory hierarchies can be constructed by using the ADRES core. For example, two levels of data caches can be attached to ADRES [22], or a multiported scratch pad memory can be attached [43, 44]. There is no array of data memories in the ADRES core. The VLIW processor is responsible for loop initiation and the control-intensive part of the application. Lack of parallel data memory units in the ADRES core limits the performance of the applications mapped on ADRES. For example, 8-state Turbo decoder algorithm requires at least 13 memory units for efficient implementation, as explained in Chapter 5.7. In a recent work on ADRES [43], a 4-ported scratchpad memory was attached to the ADRES core for applications requiring parallel memory accesses. BilRC targets more parallelism levels than does ADRES. In our recent work [2], we

have shown that it is possible to map an LDPC decoder that requires 24 parallel memory accesses in a single clock cycle. In ADRES, the loops are initiated from the VLIW processor. Hence, only a single loop can run at a time. ADRES has a mature tool suite, which can map applications written in C-language directly to the architecture. Obviously, this is a major advantage. The VLIW processor in the ADRES can also be used for the parts of the applications which require low parallelism.

MORA [25] is intended for multimedia processing. The reconfigurable cells are DSP-style sequential execution processors, which have internal 256-byte data memory for partial results and a small instruction memory for dynamic configuration of the cells. The reconfigurable cells communicate with an asynchronous handshaking mechanism. MORA assembly language and the underlying reconfigurable cells are optimized for streaming multimedia applications. The computation model is unable to adapt to complex signal processing and telecommunications applications.

RAPID [17] is a one-dimensional array of computation resources, which are connected by a configurable segmented interconnect. RAPID is programmed with RAPID-C programming language. During compilation the application is partitioned into static and dynamic configurations. The dynamic control signals are used to schedule operations to the computation resources. A sequencer is used to provide dynamic control signals to the array. The centralized sequencer approach to dynamically change the functionality requires a large number of control signals, and for some applications the required number of signals would not be manageable. Therefore, RAPID is applicable to highly regular algorithms with repetitive parts.

LRC is more efficient than the computation model of existing CGRAs from a number of perspectives:

1. LRC has flexible and efficient loop instructions. Therefore, no external RISC or VLIW processor is required for loop initiation. Arbitrary number of loops can be run in parallel. The applications targeted for LRC are not

limited to the innermost loops. For example, the IDCT algorithm has two loops one for horizontal and one for vertical processing, these loops can be pipelined so that after the first loop finishes the two loops run in parallel. Another example is that the turbo decoding algorithm has two loops one for processing the received symbols in the normal order and one for processing the received symbols in the interleaved order. Moreover these loops has two inner loops one for processing data in the forward direction and one for processing data in the reverse order. Such complex loop topologies can be easily modeled in LRC.

- 2. LRC has memory instructions to flexibly model the memory requirements of the applications. For example, the Turbo decoding algorithm requires 13 memory units. The access mechanism to the memories is efficiently modeled. The extrinsic information memory in the Turbo decoder is accessed by four loop indices. LRC has also flexible instructions to build larger-sized memory units. ADRES, MorphoSys and MORA have no such memory models in the array.

- 3. The execution control of LRC is distributed. Hence, there is no need for an external centralized controller to generate control signals, as is required in RAPID. The instruction set in LRC is flexible enough to generate complex addressing schemes, and no external address generators are required. While LRC is not biased to streaming applications, they can be modeled easily. It must be noted that LRC is not biased to any specific application, i.e., there are no application specific instructions.

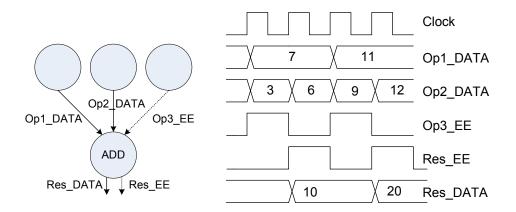

## 3.3 Modeling Applications in LRC

In a CDFG, every node represents a computation, and connections represent the operands. An example CDFG and timing diagram is shown in Fig. 3.1. The node ADD performs an addition operation on its two operands Op1\_Data and Op2\_Data when its third operand, Op3\_EE, is activated. Here, Op1 and Op2 are data operands and Op3 is a control operand. Below is the corresponding LRC line.

[Res, 0] = ADD(Op1, Op2) < -[Op3]

In LRC, the outputs are represented between the brackets on the left of the equal sign. A node can have two outputs; for this example only the first output, Res, is utilized. A "0" in place of an output means that it is unused. Res is a 17-bit signal that is composed of 16-bit data, Res\_Data, and a 1-bit execute enable signal, Res\_EE. The name of the function is provided after the equal sign. The operands of the function are given between the parentheses. The control signal that triggers the execution is provided between the brackets on the right of the "<-" characters. As can be seen from the timing diagram, the instruction is executed when its execute enable input is active. The execution of an instruction takes one clock cycle; therefore, the Res\_EE signal is active one clock cycle after Op3\_EE.

#### 3.3.1 Loop Instructions

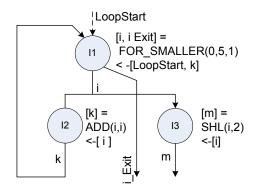

Signal processing and telecommunication algorithms contain several loops which are in nested, sequential or parallel topology. For example, FFT algorithm has a nested loop in which the outer loop counts the stages in the algorithm and the inner loop counts the butterflies within a stage. The loops are responsible for a great portion of the execution time. Therefore, efficient handling of loops is critical for the performance of most applications. LRC has flexible and efficient loop instructions. By using multiple LRC loop instructions, nested, sequential and parallel loop topologies can be modeled. A typical FOR loop in LRC is given as follows:

[i,i\_Exit]=FOR\_SMALLER(StartVal,EndVal,Incr)<-[LoopStart,Next]

This FOR loop is similar to that in C-language:

Figure 3.2: CDFG and LRC example for FOR\_SMALLER

Figure 3.3: Timing Diagram of FOR\_SMALLER

The FOR\_SMALLER instruction works as follows:

- When the LoopStart signal is enabled for one clock cycle, the data portion

of the output, i\_DATA, is loaded with StartVal\_DATA, and the control part

of the output i\_EE is enabled in the next clock cycle.

- When the Next signal is enabled for one clock cycle, i\_DATA is loaded with i\_DATA+Incr\_DATA and i\_EE is enabled if i\_DATA+Incr\_DATA is smaller than EndVal; otherwise, i\_Exit\_EE is enabled.

The parameters StartVal, EndVal and Incr can be variables or constants.

Fig. 3.2 shows an example CDFG having three nodes. The LRC syntax of the instructions assigned to the nodes is shown at the right of the nodes. All operands of FOR\_SMALLER are constant in this example. When mapped to PEs,

constant operands are initialized to the register file during configuration. ADD and SHL (SHift Left) instructions are triggered from i\_EE. Hence, their outputs k and m are activated at the same clock cycles as illustrated in Fig. 3.3. The Next input of the FOR\_SMALLER instruction is connected to the k\_EE output of the ADD instruction. Therefore, FOR\_SMALLER generates an i value for every two clock cycles. When i exceeds the boundary, FOR\_SMALLER activates the i\_Exit signal. The triggering of instructions is illustrated in Fig. 3.3 with dotted lines. SFOR\_SMALLER is a self-triggering FOR instruction given as

#### [i,i\_Exit]=SFOR\_SMALLER(StartVal,EndVal,Incr,IID)<-[LoopStart]

The SFOR\_SMALLER instruction does not require a Next input; but instead it requires a fourth constant operand, IID (Inter Iteration Dependency). SFOR\_SMALLER waits for the IDD cycles to generate the next loop index after generating the current loop index. This instruction triggers itself and can generate an index for every clock cycle when IID is 0. LRC has support for loops whose index variables are descending; these instructions are FOR\_BIGGER and SFOR\_BIGGER. The aforementioned for loop instructions can be used as a while loop by setting the Incr operand to 0. By doing so, it always generates an index value. This is equivalent to an infinite while loop. The exit from this while loop can be coded externally by conditionally activating the Next input.

#### 3.3.2 Modeling Memory in LRC

In LRC, every MEM instruction corresponds to a 1024-entry, 16-bit, 2-ported memory. One port is used for writing data to memory and the other port is used for reading data from the memory. The syntax for MEM instruction is given below:

[Out] = MEM(MemID, ReadAddr, InitFileName, WriteAddr, WriteIN)

The MEM instruction takes five operands. MemID is used to create larger memories as discussed earlier. ReadAddr is the read address port of the memory. This

signal is composed of ReadAddr\_Data and ReadAddr\_EE signals. The 10 least significant bits of ReadAddr\_Data are connected to the read address port of the memory. When ReadAddr\_EE is active, the data in the memory location addressed by ReadAddr\_Data is put on Out\_DATA in the following clock cycle and Out\_EE is activated. The InitFileName parameter is used for initializing the memory. The write operation is similar to reading. When WriteAddr\_EE is active, the data in WriteIN\_Data is written to the memory location addressed by WriteAddr\_Data. Program 1shows the code for forming a 2048-entry memory: The first memory

```

1: [Out1] = MEM(0, ReadAddr, File0, WriteAddr, WriteData)

```

- 2: [Out2] = MEM(1, ReadAddr, File1, WriteAddr, WriteData)

- 3: [Out] = SMUX (Out1, Out2)

**Program 1:** Building a 2048-Entry Memory in LRC

has MemID=0. This memory responds to both read and write addresses if they are between 0 and 1023; similarly, the second memory responds only to the addresses between 1024 and 2047. Therefore, the signals  $Out1_EE$  and  $Out2_EE$  cannot both be active in the same clock cycle. The SMUX instruction in the third line multiplexes the operand with the active EE signal. Due to the SMUX instruction, one clock cycle is lost. The SMUX instruction can take four operands. Therefore, up to  $4^n$  memories can be merged with n clock cycles of latency.

#### 3.3.3 Conditional Execution Instructions

Conditional executions are inevitable in almost all kinds of algorithms. Although some signal processing kernels such as FIR filtering do not require conditional executions, an architecture without conditional executions can not be considered complete. LRC has novel conditional execution control instructions. Below is a conditional assignment statement in C language:

```

if(A>B) {result=C;} else{result=D;}

```

Its corresponding LRC code is given as

```

[c_result,result] = BIGGER(A,B,C,D) <- [Opr]

```

BIGGER executes only if its execute enable input, Opr\_EE, is active. result is assigned to operand C if A is bigger than B; otherwise it is assigned to D. c\_result is activated only if A is bigger than B. Since c\_result is activated only if the condition is satisfied, the execution control can be passed to a group of instructions that is connected to this variable. The example C code below contains not only assignments, but also instructions in the if and else bodies.

```

if(A>B) {result=C+1;} else {result=D-1;}

```

This C-code can be converted to an LRC code by using three LRC instructions as shown in Program 2. The first line evaluates C+1, the second line evaluates D-1

```

1: [Cp1,0]=ADD(C,1)<-[C]

2: [Dm1,0]=SUB(D,1)<-[D]

3: [0,result]=BIGGER(A,B,Cp1,Dm1)<-[Opr]

```

**Program 2:** Use of Comparison Instruction in LRC

and in the third line, result is conditionally assigned to Cp1 or Dm1 depending on the comparison A>B. Conditional instructions supported in BilRC are as follows: SMALLER, SMALLER\_EQ (smaller or equal), BIGGER, BIGGER\_EQ (bigger or equal), EQUAL and NOT\_EQUAL. By using these instructions, all conditional codes can be efficiently implemented in LRC. ADRES [19] uses a similar predicated execution technique. In LRC two branches are merged by using a single instruction. In a predicated execution, a comparison is made first to determine the predicate, and then the predicate is used in the instruction. In LRC, the results of two or more instructions cannot be assigned to the same variable, since these instructions are the nodes in the CDFG. Therefore, the comparison instructions in LRC are used to merge two branches of instructions. Similar merge blocks are used in data flow machines [42] as well.

The conditional assignment instructions in LRC is summarized in Table-3.1.

Table 3.1: Conditional Assignment Instructions in LRC

| C Language Syntax | LRC Instruction |

|-------------------|-----------------|

| >                 | BIGGER          |

| >=                | BIGGER_EQ       |

| <                 | SMALLER         |

| <=                | SMALLER_EQ      |

| ==                | EQUAL           |

| ! =               | NOT_EQUAL       |

#### 3.3.4 Initialization Before Loops

```

1: min=32767;

2: for(i=0;i<255;i++){

3: A=mem[i];

4: if(A<min) {min=A;}

5: }

```

**Program 3:** Minimum value of an array in C

In the C-code in Program 3, the variable min is assigned twice, before the loop and inside the loop. Such initializations before loops are frequently encountered in applications with recurrent dependencies. Multiple assignment to a variable is forbidden in LRC as discussed in Chapter 3.1.2. An initialization technique has been devised for LRC instructions, which removes the need for an additional SMUX instruction.

The corresponding LRC code is given below: MIN finds the minimum of its

```

1: [i,i_Exit]=SFOR_SMALLER(0,256,1,0)<-[LoopStart]

2: [A,0]=MEM(0,i,filerand.txt,WriteAddr,WriteData)

3: [min(32767),0]=MIN(min,0,A,0)<-[A,LoopStart]</pre>

```

Program 4: Minimum value of an array in LRC

first and third operands<sup>1</sup>. The execute enable input of the MIN instruction is  $A\_EE$ . The second control signal between the brackets to the right of the "< -" characters, LoopStart, is used as the initialization enable. When this signal is active, the Data part of the first output is initialized. The parentheses after the output signal min represent the initialization value.

#### 3.3.5 Delay Elements in LRC

CDFG representation of algorithms requires many delay elements. These delay elements are similar to the pipeline registers of pipelined processors. A value calculated in a pipeline stage is propagated through the pipeline registers so that further pipeline stages use the corresponding data.

```

1: for(i=0;i<256;i++){

2:     A=mem[i];

3:     B=abs(A);

4:     C=B>>1;

5:     if(C>2047){R=2047;}

6:     else{R=C;}

7:     res_mem[i]=R;

8: }

```

**Program 5:** Pipelinining

In the C-code in Program 5, the data at location i is read from a memory A, its absolute value is calculated at B, shifted to the right by 1 at C and finally saturated and saved to the memory at location i. The corresponding LRC code is given in Program 6.

Although the LRC instructions are written in Program 6 in the same order as in the C-code in Program 5, this is not necessary. The order of instructions in LRC is not important. The IID operand of the SFOR\_SMALLER instruction is set to 0. Therefore, an index value, i, is generated from 0 to 255 at every clock cycle, i.e., software pipelining [45] is used. After six clock cycles, all the instructions

<sup>&</sup>lt;sup>1</sup>The second and fourth operands of MIN are used for the index of minimum calculation.

```

1: [i,i_Exit]=SFOR_SMALLER(0,256,1,0)<-[LoopStart]

2: [A,0]=MEM(0,i,filerand.txt,0,0)

3: [B,0]=ABS(A)<-[A]

4: [C,0]=SHR(B,0,1)<-[B]

5: [0,R]=BIGGER(C,2047,2047,C)<-[C]

6: [mem2,0]=MEM(0,0,0,i(4),R)

```

**Program 6:** Pipelining in LRC

are active at each clock cycle until the loop boundary is reached. Since the instructions are pipelined, the MEM instruction above cannot use i as the write address, but its four-clock-cycle delayed version. The number of pipeline delays is coded in LRC by providing it between the parentheses following the variable. It must be noted that the number of pipeline delays are constant and it must be determined at design time. A variable for a pipeline delay is not allowed, since these delay elements are part of the interconnection network which are fixed after the configuration. The requirement to specify delay value explicitly in LRC for pipelined designs makes code development a bit difficult. However, the difficulty is comparable to that of designing with HDL or assembly languages.

#### 3.3.6 Utilization of the Second Output

In LRC, some of the instructions have two outputs. The second output is used for a number of purposes. Although the basic Processing Core architecture is 16-bit, i.e., the operands of the instructions are 16-bits, it is possible to create larger size arithmetic. One purpose of the second output is as the carry output of an addition:

```

1: [R_lsb,carry] = ADD(A_lsb,B_lsb)<-[A_lsb]

2: [R_msb,0] = ADDC(A_msb(1),B_msb(1),carry)<-[A_lsb(1)]

```

**Program 7:** Utilization of the second output as the carry signal

In the code in Program 7, Alsb and Amsb represent the LSB and MSB

parts of an 32-bit signal. The instruction ADDC has an additional third operand carry. The first two operands are delayed one clock cycle to match them with the carry signal. It must be noted that only the least significant bit of the signal carry is utilized. However, routing a dedicated carry line in the interconnection network would be more problematic since this line is only utilized by the addition instruction. In BilRC, the second output of the PC is used for different purposes for different instructions, and it is routed in the interconnection network only if it is required.

The second output can also be utilized for finding the index of maximum of an array. In Program 8, a tree is formed by using the MAX instructions.

```

1: [max_01,ind_01] = MAX(A0,0,A1,1) <- [A0]

2: [max_23,ind_23] = MAX(A2,2,A3,3) <- [A2]

3: [max_45,ind_45] = MAX(A4,4,A5,5) <- [A4]

4: [max_67,ind_67] = MAX(A6,6,A7,7) <- [A6]

5: [max_03,ind_03] = MAX(max_01,index_01,max_23,ind_23) <- [max_01]

6: [max_47,ind_47] = MAX(max_45,index_45,max_67,ind_67) <- [max_45]

7: [max_07,ind_07] = MAX(max_03,index_03,max_47,ind_47) <- [max_03]

```

**Program 8:** Utilization of second output for finding index of maximum

# Chapter 4

# Tools and Simulation Environment

Fig. 4.1 illustrates the simulation and development environment. The four key components are:

# 4.1 LRC Compiler

Takes the code written in LRC and generates a pipelined netlist. Every instruction in LRC corresponds a node in CDFG which is assigned to a PC in BilRC and every connection between two nodes is a net. The net has the following information: input connection, output connection, the number of pipeline stages between the input and the output.

Figure 4.1: Simulation and Implementation Environment

### 4.2 BilRC Simulator

Performs cycle-accurate simulation of LRC code. BilRC simulator was written in SystemC<sup>1</sup>. The pipelined netlist is used as the input to BilRC simulator. PCs are interconnected according to the nets. If a net in the netlist file has delay elements, then these delay elements are inserted between PCs. The results of a simulation can be observed in three ways: from the SystemC console window, the Value Change Dump (VCD) file or the BilRC log files. Every PC output has been registered to SystemC's built-in function sc\_trace; thus by using a VCD viewer all PC output signals can be observed in a timing diagram.

#### 4.3 Placement & Routing Tool

This tool maps the nodes of CDFGs into a two-dimensional architecture, and finds a path for every net. Since the interconnection architecture of BilRC is similar to that of FPGAs, similar techniques can be used for placement and routing. However, unlike that of FPGAs, the interconnection network of BilRC is pipelined. This is the basic difference between FPGA and BilRC interconnection networks. BilRC place & route tool finds the location of the delay elements during the placement phase. The placement algorithm uses the simulated annealing

<sup>&</sup>lt;sup>1</sup>http://www.systemc.org/home/

technique with a cooling schedule adopted from [46]. The total number of delay elements that can be mapped to a node is  $4N_p$ . For every output of a PC, a pipelined interconnect is formed. When placing the delay elements, contiguous delay elements are not assigned to the same node. Such movements in the simulated annealing algorithm are made forbidden. A counter is assigned for every node, which counts the number of delay elements assigned to the node. The counter values are used as a cost in the algorithm. Therefore, delay elements are forced to spread around the nodes. The placement algorithm uses the shortest path tree algorithm for interconnect cost calculation. The algorithm used for routing is similar to that of the negotiation based router [47]. Fig. 5.2 shows the result of placement and routing of the maxval algorithm explained in Chapter 5.1.

#### 4.4 HDL generator

Converts LRC code to HDL code. Since LRC is a language to model CDFGs, it is easy to generate the HDL code from it. For each instruction in LRC, there is a pre-designed VHDL code. The HDL generator connects the instructions according to the connections in the LRC code. The unused inputs and outputs of instructions are optimized during HDL generation. The quality of the generated HDL code is very close to that of manual coded HDL. The generated HDL code can then be used as an input to other synthesis tools, such as the Xilinx ISE. The generated HDL code was used to map applications to an FPGA in order to compare the results with LRC code mapped to BilRC.

# Chapter 5

# Example Applications for BilRC

In order to validate the flexibility and efficiency of the proposed computation model, several standard algorithms selected from Texas Instruments benchmarks [48] are mapped to BilRC. We also mapped Viterbi and Turbo decoder channel decoding algorithms and multirate and multichannel FIR filters. For all cases, it is assumed that the input data are initialized into the memories and the outputs are directly provided to the device outputs.

## 5.1 Maximum Value of an Array (maxval)

The maximum value of an array can be computed in LRC in different ways depending on how the array stored in memories. The input array of size 128 is stored in 8 sub-arrays with a size of 16 each. The algorithm first finds the maximum values of the 8 sub-arrays by sequentially processing each data read from the memories, and then the maximum value from among these 8 values are computed. Fig. 5.1 illustrates the CDFG of the algorithm.

Figure 5.1: LRC Code and CDFG of Maximum Value of an Array

```

1: [LoopStart] = DELAY(PI) < - [PI]

2: [i, i_Exit] = SFOR_SMALLER( 0,16,1,0)<-[LoopStart]

3:

[d.1]

= MEM(0,i,Data1.txt,0,0)<-[]</pre>

4:

[d.2]

= MEM(0,i,Data2.txt,0,0)<-[]</pre>

5:

. . .

6:

[d.8]

= MEM(0,i,Data8.txt,0,0)<-[]

[m1(-32768)] = MAX(m1,0,d1,0) < -[d1,LoopStart(1)]

7:

8:

[m2(-32768)] = MAX(m2,0,d2,0) < -[d2,LoopStart(1)]

9:

10:

[m8(-32768)] = MAX(m8,0,d8,0) < -[d8,LoopStart(1)]

[m1_2] = MAX(m1,0,m2,0) < -[i_Exit(1)]

11:

12:

[m3_4] = MAX(m3,0,m4,0) < -[i_Exit(1)]

[m5_6] = MAX(m5,0,m6,0) < -[i_Exit(1)]

13:

[m7_8] = MAX(m7,0,m8,0) < -[i_Exit(1)]

14:

[m1_4] = MAX(m1_2,0,m3_4,0) < -[m1_2]

15:

[m5_8] = MAX(m5_6,0,m7_8,0) < -[m5_6]

16:

17:

[max\_result] = MAX(m1\_4,0,m5\_8,0) < -[m1\_4]

```

**Program 9:** Maximum Value of an Array

The signal, LoopStart, triggers the SFOR\_SMALLER instruction. The loop generates an index value for every clock cycle, starting from 0 and ending at 15. i is used as an index to read data from 8 memories in parallel. Then, 8 MAX instructions find the maximum values corresponding to each sub-array. The instruction corresponding to the eighth sub-array is shown below:

$$[m8(-32768)] = MAX(m8,0,d8,0) < -[d8,LoopStart(1)]$$

Here, the variable m8 is both output and input. At every clock cycle, m8 is compared to d8 and the larger one is assigned to m8. The LoopStart(1) signal (1 in parentheses indicates one clock cycle delay) is used to initialize m8 to -32768. It should be noted that if an instruction's output is also input to itself, the output variable is connected to the input bus inside the processing core. This is shown in Fig. 2.6, where PC\_OUT\_1 is connected to the input data bus. During compilation, LRC compiler finds the instructions whose output is also input, and then the PE is configured accordingly.

When the FOR loop reaches the boundary, i\_Exit\_EE is activated for one clock cycle, one-cycle-delayed version of i\_Exit\_EE is used to trigger the execution of four MAX instructions. The dotted lines in the figure represent the control signals and the solid lines represent signals with both control and data parts. The instructions in the MAX-tree are executed only once. The depth of the memory blocks in BilRC is 1024, whereas the maxval algorithm uses only 16 entries. This under-utilization of memory can be avoided by using register files instead of memories. ALU PEs have 8-entry register files, two ALU PEs can be used to build a 16 entry register file.

#### 5.2 Dot Product of two Vectors

This algorithm can be computed on BilRC in different ways depending on how the input vectors are stored. It will be assumed that the vectors a and b are stored in 8 memories. Thus, there are 8 sub arrays. In the LRC code given in

Figure 5.2: Maxval algorithm placement and routing on BilRC

Appendix C.3, first 8 dot products of the sub arrays are computed. Then, these partial dot products are summed up. This example shows the utilization of the second output of the MUL\_SHIFT instruction. The least and most significant parts of the multiplications are accumulated for each loop iteration. The carry output resulting from the adder is used as an input for the MSB part. Since the LSB addition takes one clock cycle, the MSB part of the multiplication is delayed one clock cycle to balance the two inputs.

### 5.3 Finite Impulse Response Filters

Digital filters can be implemented by using a tap delay line, multipliers and an adder tree. A 16-tap FIR filter can be described in LRC as given in the Program 10. In this example, it is assumed that both the filter input data which is stored in a memory and the filter coefficients are represented as 12-bit signed values. The write address and data ports of the memory are not used in this example. In a real implementation, these ports are used or the filter input data can be read from a primary input. SFOR\_SMALLER instruction in the first line generates an index at every clock cycle. This index value is used as the address of the memory in the second instruction. 16 MUL\_SHIFT instructions multiply the coefficients with the filter input data and shift the result to the right by 11. The second multiplier, mul1 uses one clock cycle delayed version of data, and the 16<sup>th</sup> multiplier uses 15 clock cycle delayed version of data. The tap delay line is implicitly defined in LRC by using the delayed versions of the input data. The

Figure 5.3: Part of the CDFG of dot product algorithm

results of the multiplication are used as input to an adder tree.

A multi-rate filter can be designed with LRC in a similar way. In order to design a multi-rate filter with rate 2, the MUL\_SHIFT instructions in Program 10 can be changed as given in Program 11. In this code, the second multiplier uses data(2), which is two clock cycle delayed version of data and third multiplier uses data(4) and so on. As compared to the single rate FIR, the number of delay elements in the algorithm is doubled. Since BilRC has plenty of delay elements, this does not create a problem.

The multi-rate filter described above can be used as a multichannel filter by multiplexing channel data at the filter input and demultiplexing the data at the filter output. The multiplexing at the filter input is shown in Program 12. In this code, SFOR\_SMALLER instruction generates an index for every two clock cycles, since its 4<sup>th</sup> operand, IID, is set to 1. The memory for the data\_ch1 uses i as the address and data\_ch2 uses i(1), one clock cycle delayed version of i. data\_ch1 and data\_ch2 are active for one clock cycle for every two clock cycle. The output

```

[i, i_Exit] = SFOR_SMALLER( 0,1024,1,0)<-[LoopStart]\

= MEM(0,i,data.txt,0,0)<-[]

#multiplication by filter coefficients

,-23 ,11)<-[data]

[mul0]

= MUL_SHIFT(data

[mul1]

= MUL_SHIFT(data(1) ,-39 ,11)<-[data(1)]

[mul15] = MUL_SHIFT(data(15),-23,11)<-[data(15)]</pre>

#adder tree

[add1_0] = ADD(mul0, mul1) < -[mul0]

. . .

[add1_7] = ADD(mul14, mul15) < -[mul14]

[add2_0] = ADD(add1_0, add1_1) < -[add1_0]

[add2_3] = ADD(add1_6, add1_7) < -[add1_6]

[add3_0] = ADD(add2_0, add2_1) < -[add2_0]

[add3_1] = ADD(add2_2, add2_3) < -[add2_2]

[filter_out] = ADD(add3_0, add3_1) < -[add3_0]

```

**Program 10:** FIR Filter

```

[mul0 ] = MUL_SHIFT(data ,-23 ,11)<-[data]

[mul1 ] = MUL_SHIFT(data(2) ,-39 ,11)<-[data(2)]

[mul2 ] = MUL_SHIFT(data(4) ,-39 ,11)<-[data(2)]

...

[mul15 ] = MUL_SHIFT(data(30),-23 ,11)<-[data(30)]</pre>

```

**Program 11:** Part of the Multi-Rate FIR Filter

of SMUX is active for every clock cycle and contains data from the first channel for one clock cycle and from the second channel in the following clock cycle.

```

[i,i_Exit] = SFOR_SMALLER( 0,1024,1,1)<-[LoopStart]

[data_ch1] = MEM(0,i,data.txt,0,0)<-[]

[data_ch2] = MEM(0,i(1),data.txt,0,0)<-[]

[data] = SMUX(data_ch1,data_ch2)<-[]</pre>

```

Program 12: Part of the Multi-Channel FIR Filter

### 5.4 2D-IDCT Algorithm

2D-DCT and its inverse, 2D-IDCT algorithms are widely used in image processing for compression and decompression respectively. In this work, we consider the implementation of (8x8) 2D-IDCT algorithm with LRC. We used a fixed point model of the Program [48]. The algorithm is composed of three parts: horizontal pass, transposition and vertical pass. In the horizontal pass, the rows of the 8×8 matrix are read and the 8-point 1D IDCT of the row is computed. Since there are 8 rows in the matrix, this operation is repeated 8 times. The transposition phase of the algorithm transposes the resulting matrix obtained from the horizontal pass. In the final phase, the matrix is read again row-wise and the 1D IDCT of each row is computed. The challenging part of the algorithm is the transposition phase.

Fig. 5.4 illustrates the CDFG and LRC of the algorithm. This algorithm computes 2D-IDCT of 100 frames, where a frame is composed of 64 words. The code assumes that the input data is stored in 8 arrays. While the input arrays are being filled, the IDCT computation can run concurrently. Hence, the time to get data to the memory can be hidden. The two SFOR\_SMALLER instructions at the beginning of the code are used for frame counting and horizontal line counting, respectively. The SHR\_OR instruction computes the address, which is used to read data from the eight memory locations. MUX (multiplex) instructions in the code are used for transposition. The MUX instruction has five operands: the first

```

[frame_cnt ] = SFOR_SMALLER( 0,100,1,8)<-[LoopStart]</pre>

[hor_cnt ]

= SFOR_SMALLER( 0,8,1,0)<-[frame_cnt]

[hor_addr] = SHL_OR(frame_cnt,3,hor_cnt)<-[hor_cnt]</pre>

#Read a Row

[data_1]

= MEM(0,hor_addr,data_1.txt,0,0)<-[]

. . .

[data_8]

= MEM(0,hor_addr,data_8.txt,0,0)<-[]

#Horizontal IDCT computations

[reg1\_wd\_m1] = MUX(sel10, f0, f1(1), f2(2), f3(3))

<-[sel10]

[reg1\_wd\_m2] = MUX(sel10,f4(4),f5(5),f6(6),f7(7)) < -[sel10]

=MUX(sel3,reg1_wd_m1,reg1_wd_m2,0,0)<-[sel3]

[reg1_wd]

[reg8\_wd\_m1] = MUX(sel10(7), f0, f1(1), f2(2), f3(3))

<-[sel10(7)]

[reg8\_wd\_m2]=MUX(sel10(7),f4(4),f5(5),f6(6),f7(7))

<-[sel10(7)]

[reg8_wd]

=MUX(sel3(7),reg8_wd_m1,reg8_wd_m2,0,0)

<-[sel3(7)]

#Vertical IDCT computations