Microelectronics Reliability 51 (2011) 2153-2162

Contents lists available at ScienceDirect

# Microelectronics Reliability

journal homepage: www.elsevier.com/locate/microrel

On the profile of frequency and voltage dependent interface states and series resistance in  $(Ni/Au)/Al_{0.22}Ga_{0.78}N/AlN/GaN$  heterostructures by using current–voltage (I-V) and admittance spectroscopy methods

S. Demirezen a,\*, Ş. Altındal a, S. Özçelik a, E. Özbay b,c

- <sup>a</sup> Department of Physics, Faculty of Science and Arts, University of Gazi, Teknikokullar, 06500 Ankara, Turkey

- <sup>b</sup> Nanotechnology Research Center, Bilkent University, Bilkent, 06800 Ankara, Turkey

- c Department of Physics, Department of Electrical-Electronics Engineering, Nanotechnology Research Center, Bilkent University, Ankara, Turkey

#### ARTICLE INFO

### Article history: Received 8 January 2011 Received in revised form 1 May 2011 Accepted 16 May 2011 Available online 8 June 2011

### ABSTRACT

In order to explain the experimental effect of interface states ( $N_{ss}$ ) and series resistance ( $R_s$ ) of device on the non-ideal electrical characteristics, current–voltage (I-V), capacitance–voltage (C-V) and conductance–voltage ( $G/\omega-V$ ) characteristics of (Ni/Au)/Al<sub>0.22</sub>Ga<sub>0.78</sub>N/AlN/GaN heterostructures were investigated at room temperature. Admittance measurements (C-V and  $G/\omega-V$ ) were carried out in frequency and bias voltage ranges of 2 kHz–2 MHz and (-5 V)–(+5 V), respectively. The voltage dependent  $R_s$  profile was determined from the I-V data. The increasing capacitance behavior with the decreasing frequency at low frequencies is a proof of the presence of interface states at metal/semiconductor (M/S) interface. At various bias voltages, the ac electrical conductivity ( $\sigma_{ac}$ ) is independent from frequencies up to 100 kHz, and above this frequency value it increases with the increasing frequency for each bias voltage. In addition, the high-frequency capacitance ( $C_m$ ) and conductance ( $G_m/\omega$ ) values measured under forward and reverse bias were corrected to minimize the effects of series resistance. The results indicate that the interfacial polarization can more easily occur at low frequencies. The distribution of  $N_{ss}$  and  $R_s$  is confirmed to have significant effect on non-ideal I-V, C-V and  $G/\omega-V$  characteristics of (Ni/Au)/Al<sub>0.22</sub>Ga<sub>0.78</sub>N/AlN/GaN heterostructures.

© 2011 Elsevier Ltd. All rights reserved.

# 1. Introduction

More than three decades; AlGaN/AlN/GaN high electron mobility transistors (HEMT) have attracted much attention due to their promising applications in microwave and optoelectronic devices [1–8]. They have been intensively studied as candidates for highpower devices, as well as for high-speed and high-temperature operations [1–8]. Controlling interface states ( $N_{ss}$ ) and series resistance  $(R_s)$  is an important issue in these structures for high power, high speed and high temperature applications [4]. In order to improve the performance of these devices the effect of surface passivation, dielectric layer (Al<sub>2</sub>O<sub>3</sub>, Si<sub>3</sub>N<sub>4</sub>) insertion, surface treatments with chemical or plasma have been investigated [4-8]. Nevertheless satisfactory understanding in all details such as the frequency dependence of  $N_{ss}$  and  $R_s$  as function of applied bias voltage has still not been achieved. This fact causes a high level of in-plane stress and threading dislocation density (DD) generation, as grown by metal-organic chemical vapor deposition (MOCVD) in the GaN epitaxial layer [6–8]. Surface preparation, interruption of the periodic lattice structure at the surface, formation of an insulator layer and barrier at metal/semiconductor (M/S) interface and impurity concentration of semiconductor leads to the formation many  $N_{\rm ss}$  and DD at M/S interface [9–15]. Moreover, interface preparation process, barrier height, high quality ohmic and Schottky contacts affect the performance of electronic devices [9,10,16–19]. Therefore, these possible sources of error must be taken into account to obtain accurate and reliable results.

Recently, the frequency dependence of the electrical characteristics of these devices has become an object of rather intense interest in the literature [11–25]. However, from experimental and theoretical point-of-view, the satisfactory description of the effect of these parameters on the C-V and  $G/\varpi-V$  characteristics still remains as an important problem. Therefore, the frequency dependent reverse and forward bias C-V and  $G/\varpi-V$  measurements in the wide frequency range can give us important information about the energy distribution of the interface states and the main electrical parameters of these structures.

In the ideal case, the capacitance of these structures is usually frequency independent. However, the situation is different especially in the weak inversion and depletion regions for low frequencies due to the existence of  $N_{ss}$  and their relaxation time, formation

<sup>\*</sup> Corresponding author. Tel.: +90 312 2021247; fax: +90 312 2122279. E-mail address: s.demirezen@gazi.edu.tr (S. Demirezen).

of the barrier height at MS interface and  $R_s$  of structure. The interface trapped charges in general called as the interface states exist within the forbidden band gap. These traps can be divided in four categories: (1) interface trap charges  $(Q_{it})$ , (2) fixed oxide charges  $(Q_f)$ , (3) oxide trapped charges  $(Q_{ot})$  and (4) mobile ionic charges  $(Q_m)$  such as sodium ions, which are mobile within the oxide under bias-temperature aging conditions. These interface charges can easily follow an ac signal and yield an excess capacitance and conductance to their real values at low frequencies. On the contrary, the charges at interface states can't follow an ac signal and can't produce an excess capacitance and conductance at high frequencies where the carrier life time of the charges  $(\tau)$  is much larger than 1/f. Therefore, the frequency dependent C-V and G/ $\omega$ -V measurements are very significant to obtain accurate and reliable results about these fabricated structures. The interface states usually cause a bias shift and frequency dispersion in the capacitance-voltage (C-V) and conductance-voltage ( $G/\omega-V$ ) curves [12,14,16] and they are effective especially in the depletion and inversion regions.

In addition, the series resistance is also an important parameter, which causes deviations in the electrical characteristics at only depletion region of these structures [9,15,20,21]. The  $R_s$  of device can cause a serious error in the *I–V*, *C–V* and  $G/\omega$ –*V* characteristics. In general, the origins of  $R_s$  can arise from five different sources: contact made by the probe wire to the gate; the ohmic and rectifier contacts; the resistance of the quasi-neutral bulk semiconductor between ohmic contact to semiconductor and the depletion layer edge at the semiconductor surface; the oxide charges or organic impurities in the interfacial layer and inhomogeneity of the density distribution of doping material in semiconductor [2]. To avoid these errors and the sensitivity limitation,  $R_s$  can be minimized by sample fabrication processes, making measurements at low frequencies so that the effect of  $R_s$  is negligible, the measurements carried out in dark and in sheeted box or cryostat and to make desired correction in the experimental measurements.

In order to extract the energy density distribution profile of interface states for these devices, several method have been suggested in the literature such as the high–low frequency capacitance ( $C_{HF}$ – $C_{LF}$ ) [20,22], quasi-static capacitance [21], surface admittance [15], forward bias current–voltage [18] and conductance techniques. Among them the more important ones are high-low frequency capacitance and conductance techniques [23].

The conductance method, as developed by Nicollian and Goetzberger [16,17], is based on the conductance losses resulting from the exchange of majority carriers between the interface states and the majority carrier band of the semiconductor when a small ac signal is applied to the these structures. The applied ac signal causes the Fermi level to oscillate about the mean positions governed by the dc bias, when the structure is in depletion. Therefore, the conductance technique gives an accurate simultaneous determination for interface states density, their relaxation time  $(\tau)$ and capture cross section as a function of energy  $(\sigma)$  [16,17,21]. According to this method, the interface states at the Fermi level change their occupancy by capture and emission process, and a conductance loss occurs, since the response of states lags behind the phase of the signal. The density of states is found from the conductance loss resulting from the interface states by measuring the ac conductance as a function of bias voltage in depletion at various frequencies.

In this study, we experimentally investigated the frequency dependence of forward and reverse bias C-V and  $G/\omega-V$  characteristics of (Ni/Au)/Al<sub>0.22</sub>Ga<sub>0.78</sub>N/AlN/GaN heterostructure in the wide frequency range of 2 kHz -2 MHz by considering both the interface states ( $N_{ss}$ ) and series resistance ( $R_s$ ) effects. Also the forward and reverse bias I-V characteristics of these structures were measured at room temperature. The interface states density values

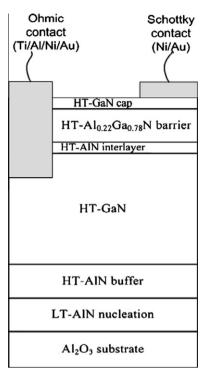

Fig. 1. Schematic diagram of the  $(Ni/Au)/Al_{0.22}Ga_{0.78}N/AlN/GaN$  heterostructures and a view of ohmic and Schottky contacts on the structures.

at M/S interface were obtained from admittance spectroscopy method.

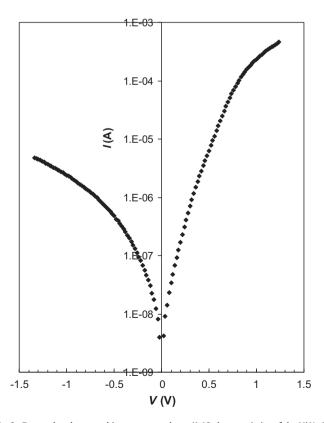

**Fig. 2.** Forward and reverse bias current–voltage (I-V) characteristics of the Ni/Au)/ Al<sub>0.22</sub>Ga<sub>0.78</sub>N/AlN/GaN heterostructure in semi-logarithmic scale at room temperature.

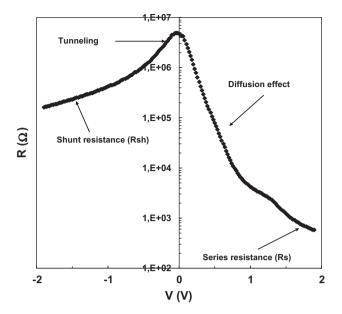

**Fig. 3.** The variation of  $R_S$  as a function of bias voltage for  $(Ni/Au)/Al_{0.22}Ga_{0.78}N/AlN/GaN$  heterostructure at room temperature.

## 2. Experimental procedures

The samples investigated in the present study were grown on C-face (0 0 0 1) sapphire (Al<sub>2</sub>O<sub>3</sub>) substrate by a low-pressure MOCVD reactor. Hydrogen was used as the carrier gas and Trimethylgallium (TMGa), trimethylaluminum (TMAI), ammonia (NH<sub>3</sub>) were used as Ga, Al and N precursors, respectively. Prior to the epitaxial growth, the substrate was cleaned in H<sub>2</sub> ambient at 1100 °C. As shown in Fig. 1 , 15 nm low-temperature (LT) AlN nucleation layer was grown at 840 °C with a 50 mbar reactor pressure. After the deposition of the LT-AlN nucleation layer, the wafers were heated to a high temperature (HT) for annealing. For the samples, approximately a 0.60  $\mu m$  HT-AlN buffer layer was deposited on the annealed nucleation layers at 1127 °C with a 400 nm/hr growth

rate. After the deposition of buffer layers, approximately 1.9  $\mu$ m HT–GaN layer was grown at 1040 °C. Finally, 1.5 nm thick AlN interlayer, a 27 nm thick Al $_{0.22}$ Ga $_{0.78}$ N barrier layer, and 3 nm GaN cap layer were grown at 1080 °C. All layers are nominally undoped.

For the contacts, since the sapphire substrate is insulating, the ohmic and Schottky contacts were made on the top surface. The ohmic contacts were prepared by the evaporation deposition of Ti/Al/Ni/Au (200 Å/2000 Å/300 Å/700 Å). After the metallization step, the contacts were annealed at 850 °C for 30s in  $\rm N_2$  ambient in order to form the ohmic contact. The Schottky contacts were prepared by the evaporation deposition of Ni/Au (300 Å/500 Å). Both ohmic and Schottky contacts were made on the top surface as 1.5 mm-diameter circular dots.

The current–voltage (I–V) characteristics were performed by the use of a Keithley 220 programmable constant current source, a Keithley 614 electrometer. The capacitance–voltage (C–V) and conductance–voltage (G/ $\omega$ –V) characteristics were measured in the 2 kHz–2 MHz frequency range, using a HP 4192 A LF impedance analyzer (5 Hz–13 MHz) and test signal of 40 mVrms. All of the measurements were carried out with a temperature controlled Janes vpf–75 cryostat.

#### 3. Results and discussion

## 3.1. The voltage dependent forward bias I–V characteristics

Fig. 2 shows the semi-logarithmic forward and reverses bias I-V characteristics of the (Ni/Au)/Al<sub>0.22</sub>Ga<sub>0.78</sub>N/AlN/GaN heterostructure at room temperature. The current voltage characteristics of the metal–semiconductor contacts (diodes) with a series resistance ( $R_s$ ) can be analyzed by the following relation [9]

$$I = I_0 \exp\left(\frac{q(V - IR_s)}{nkT}\right) \left[1 - \exp\left(\frac{-qV - IR_s}{kT}\right)\right]$$

(1)

where n is the ideality factor can be obtained from the slope of the straight line region of the  $\ln(I)$ –V plot, k is the Boltzmann constant,  $R_s$  is the series resistance of the structure, V is the applied bias voltage, T is the sample temperature in Kelvin. Here,  $I_o$  is the reverse

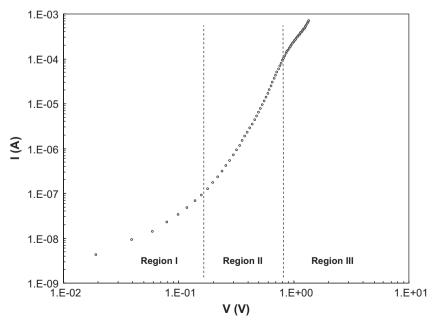

Fig. 4. The ln(I) vs. ln(V) characteristics of the  $(Ni/Au)/Al_{0.22}Ga_{0.78}N/AlN/GaN$  heterostructure at room temperature.

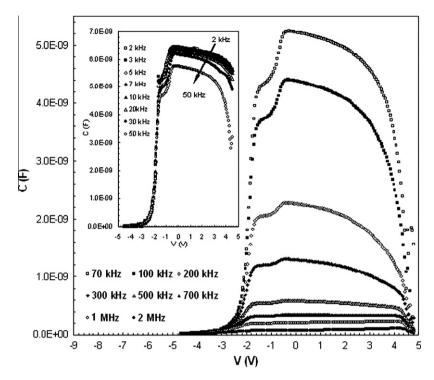

Fig. 5. The frequency dependent curves of the C-V characteristics of (Ni/Au)/Al<sub>0.22</sub>Ga<sub>0.78</sub>N/AlN/GaN heterostructure at room temperature.

saturation current derived from the straight line region of the forward bias current intercept at zero bias and is given by

$$I_0 = AA^*T^2 \exp\left(-\frac{q\Phi_{Bo}}{kT}\right) \tag{2}$$

Thus, the ideality factor (n) and zero bias barrier height ( $\Phi_{Bo}$ ) of structure were determined from Eqs. (1) and (2) as 2.36 and 0.74 eV. respectively. The high value of n was attributed to the high density of interface states localized at MS interface and the effect of barrier inhomogeneities [9,19]. As shown in Fig. 2, the presence of high  $R_S$  causes the downward concave curvature in the forward bias I-V plot at high bias voltages. The voltage dependent  $R_S$  profile of (Ni/Au)/Al<sub>0.22</sub>Ga<sub>0.78</sub>N/AlN/GaN heterostructure at room temperature was obtained from the I-V data by using Ohm's law  $(R_i = V_i/I_i)$ and is given in Fig. 3. The  $R_S$  and shunt resistance  $(R_{sh})$  values of structure were calculated from the R-V plot as  $0.578\,\mathrm{k}\,\Omega$  and 166.13 k  $\Omega$ , respectively. It is clear that the structure has low series resistance and high shunt resistance which actually is necessary for ideal devices. As shown in Fig. 3, the value of  $R_S$  gives a peak which can be explained by the effect of tunneling in the current conduction mechanism.

In order to detect the dominant current conduction mechanism, I-V characteristics of the  $(Ni/Au)/Al_{0.22}Ga_{0.78}N/AlN/GaN$  heterostructure was drawn also in logarithmic scale in Fig. 4. As can be seen in the figure, the forward bias current plot reveals three distinct regions: a linear region below "0.22 V", an excess current or "hump" at about "0.22 V"–"0.82 V", and a deviation from the ln(I) vs. V relationship above "0.82 V". Similar results have been reported in the literature [24–27]. Also, the non-saturation behavior was observed (Fig. 2) as a function of bias in the experimental reverse bias range. This behavior may be explained in terms of the spatial inhomogeneity of Schottky barrier height (SBH) [28,29], and the image force lowering effect of SBH [13,30].

In region I, the simple thermionic emission (TE) theory can be used to obtain main electrical properties of the structure. In

region II, the forward bias *I–V* characteristics as shown in Fig. 2 exhibit a "hump". Kar and Dahlke [14] have shown that "humps" in the forward current–voltage characteristics of MIS diodes originate from carrier generation-recombination at interface states and subsequent tunneling through the oxide to the metal. In region III, the forward *I–V* plot deviates from the relationship given by Eq. (1). The current through the diode appears to become limited by another process. The absolute

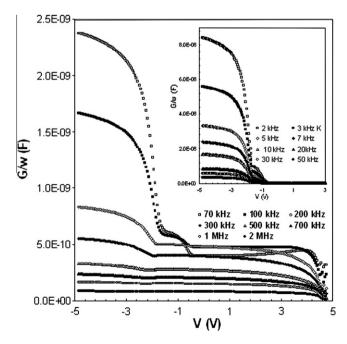

**Fig. 6.** The frequency dependent of  $G/\omega$ –V characteristics for (Ni/Au)/Al<sub>0.22</sub>Ga<sub>0.78</sub>N/AlN/GaN heterostructure at room temperature.

current values reveal that this limitation is not due to the series resistance of the bulk silicon or the ohmic contact. The most likely explanation is that, above "0.82 V", the current is determined by transport across the interfacial oxide layer. Possible conduction processes include quantum mechanical tunneling and Poole–Frenkel conduction via impurity states. Also in this region the injection of charge carriers takes place and causes an increase in the current.

3.2. The frequency dependent forward and reverse bias C–V and  $G/\omega$ –V characteristics

The forward and reverse bias C-V and  $G/\omega-V$  measurements were performed at room temperature in the frequency range of 2 kHz-2 MHz by using HP 4192A LF impedance analyzer and are given in Figs. 5 and 6, respectively. As shown in Fig. 5, C-V curves vary from the weak inversion region to strong accumulation region

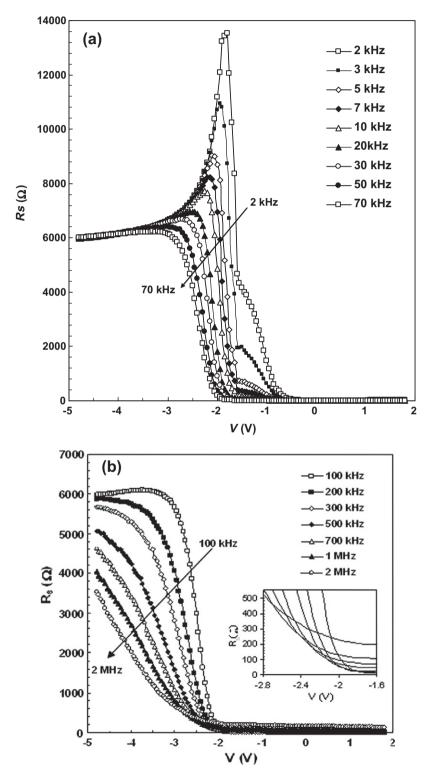

Fig. 7. R<sub>s</sub>-V characteristics of (Ni/Au)/Al<sub>0.22</sub>Ga<sub>0.78</sub>N/AlN/GaN heterostructure (a) at low frequencies (b) at high frequencies.

for each frequency. The high values of C and  $G/\omega$  at low frequencies are due to the excess capacitance which is resulting from the interface states localized at M/S interface. If the C-V measurements are carried out at sufficiently low frequencies (such that the carrier lifetime  $(\tau)$  of charge at trap is much lower than the reverse of angular frequency (1/2f), the  $N_{SS}$  will easily follow an ac signal and yield an excess capacitance and conductance to their measurement values [16,17].

However, at higher frequencies, the  $N_{SS}$  cannot follow the ac signal and in this case, the contribution of interface states capacitance  $(C_{ss})$  and conductance  $(G_{ss}/\omega)$  to the total measured capacitance  $(C_m)$  and conductance  $(G_m/\omega)$  negligibly small [16,17,31,32]. At high frequencies, the  $R_s$  become significant because of the low impedance of the device. In addition, the C-V characteristics of the  $(Ni/Au)/Al_{0.22}Ga_{0.78}N/AlN/GaN$  heterostructure shows two peaks. The first peak located at low forward bias (in depletion region) due to  $N_{ss}$  contribution shifts towards the low bias voltages with the increasing frequency. However, the second peak shown at high bias region disappears (due to the influence of the  $R_s$ ) when the frequency decreases [33].

There are several methods in literature for determining  $R_s$  values [17,34,35]. We have applied the admittance method developed by Nicollian and Brews [17]. This method provides the determination of  $R_s$  in both reverse and forward bias regions. According to this method, the real value of  $R_s$  for MIS or MOS structures can be subtracted from the measured  $C_m$  and  $C_m$  values at sufficiently high frequencies ( $f \ge 500 \text{ kHz}$ ) and in strong accumulation regions as following [17]

$$R_{\rm s} = \frac{G_{\rm m}}{G_{\rm m}^2 + (\omega C_{\rm m})^2} \tag{3}$$

where,  $\omega$  (=2 $\pi f$ ) is the angular frequency. The voltage dependent  $R_s$  values were calculated according to Eq. (3) and shown in Fig. 7a and b for low and high frequencies, respectively. These very significant values demanded that special attention should be given to effects of the  $R_s$  in the application of the admittance-based measurement methods (C-V and  $G/\omega$ -V). As seen in Fig. 7a and b, the  $R_s$ -V plots give a peak especially at low frequencies between about (-2)-(-1) V depending on frequency such that the peak disappears at high frequencies.

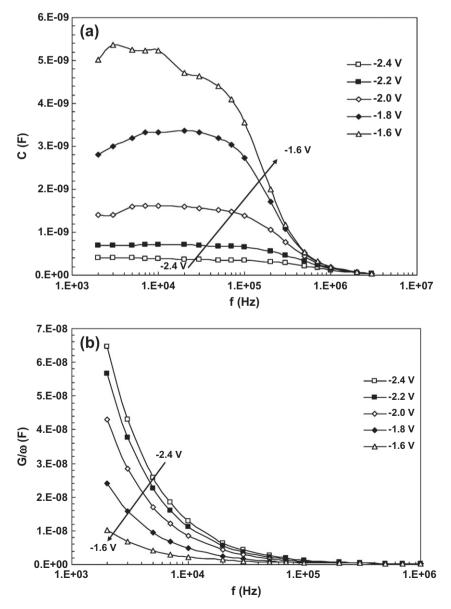

Fig. 8. The frequency dependence of: (a) the  $C(V_G)$ -f and (b)  $G/\omega(V_G)$ -f characteristics of the (Ni/Au)/Al<sub>0.22</sub>Ga<sub>0.78</sub>N/AlN/GaN heterostructure at room temperature.

In order to obtain the real values of C and  $G/\omega$  for the (Ni/Au)/  $Al_{0.22}Ga_{0.78}N/AlN/GaN$  heterostructures, the high frequencies measured capacitance ( $C_m$ ) and conductance ( $G_m/\omega$ ) as measured under forward and reverse bias voltages were corrected for the effect of  $R_s$  [17]. It can be seen from Fig. 7, the  $R_s$  values are dependent on both frequency and applied bias voltage and they change from region to region due to special distribution of interface states at M/S interface. Also, at low frequencies, the carrier lifetime ( $\tau$ ) in these traps is much lower than the reverse of angular frequency ( $1/2\pi f$ ), hence they can easily follow an ac signal and yield an excess capacitance and conductance to their measurement values [16,17].

In order to clarify the observed behavior of measured  $C_m$  and  $G_m/\omega$  in Figs. 5 and 6, we obtained the  $C_m$  and  $G_m/\omega$  values of (Ni/Au)/Al<sub>0.22</sub>Ga<sub>0.78</sub>N/AlN/GaN heterostructure as a function of frequency for five gate voltages and are given in Fig. 8a and b, respectively. As can be seen in these figures, both the  $C_m$  and  $G_m/\omega$  values almost decrease with the increasing frequency in the frequency range of 2 kHz-2 MHz. This behavior can be attributed to the existence of a continuous distribution of  $N_{ss}$  in the M/S interface, which leads to a progressive decrease in the response of the  $N_{ss}$  to the applied ac voltage [36–38]. On the other hand, it is well known that at low frequencies the charges at interface states can easily follow an external ac signal and yield excess capacitance and conductance especially in the depletion and weak inversion regions. As can be seen in Fig. 8a, "-1.6", "-1.8", and "-2.0 V" values corresponding to depletion region. On the other hand, "-2.2 V" and "-2.4 V" corresponds to inversion region. Also, while the interface states are especially effective in depletion region but series resistance is effective only at accumulation region. The other explanation of such behavior can be attributed to the particular distribution of interface states located at M/S interface with energy states in the semiconductor forbidden band gap. In addition, the higher value of C and  $G/\omega$  at low frequency are due to the excess capacitance ( $C_{ex}$ ) and conductance ( $G_{ex}/\omega$ ) resulting from the  $N_{ss}$  in equilibrium with the semiconductor that can follow the ac signal. As a result, in the depletion region the  $N_{ss}$  are responsible for the observed frequency dispersion in  $C(V_G)$  and  $G/\omega(V_G)$  plots.

The conductance of interface states  $G_{ss}$  as a function of frequency of the applied signal proposed by Nicollian and Brews is given by [17]

$$G_{SS} = \frac{C_{ox}^2 G}{(C_{ox} - C)^2 + (G/\omega)^2}$$

(4)

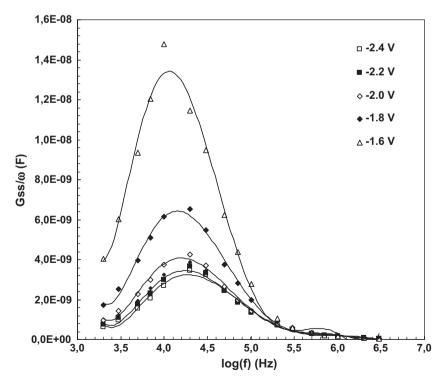

where C and  $G/\omega$  are the experimental capacitance and conductance of the heterostructure, respectively. As explained in Refs. [16,17,38-41], the conductance method yields more accurate and reliable results. Fig. 9 depicts the  $G_{ss}$  vs. log (f) plot for five gate voltages which show a maximum with the increasing bias, and the amplitude of the peak  $(G_{ss})_{max}$  decreases with the frequency  $(\omega_p)$  at which the occurred maxima moves towards lower value. This behavior can be explained by using the interface trap model. As indicated before, there exists an almost continuous distribution of  $N_{ss}$  energy levels. At a given bias, the Fermi energy level  $(E_F)$  fixes the occupancy of these trap levels and a particular electron density will exist at M/S interface which determines the capture rate of the related trap levels. Capture and emission occurs primarily by traps located within a few kT/q above and below the  $E_F$ . If the frequency is slightly different from the capture rate, losses are reduced because trap levels either do not respond or the response occurs at a different frequency. Therefore, the loss peak is a function of frequency, Furthermore, the peak value depends on capture rate, i.e., on the interface trap level occupancy, which is determined by the applied gate bias voltage [42,43].

The energy position in the band gap of semiconductor can be calculated as

$$E_C - E_{SS} = q(\Phi_S - \Phi_F) \tag{5}$$

Fig. 9. The frequency dependence of Gss characteristics obtained from the experimental forward bias capacitance and conductance measurements of (Ni/Au)/Al<sub>0.22</sub>Ga<sub>0.78</sub>N/AlN/GaN heterostructure at room temperature.

Fig. 10. The surface potential vs. V plot of the (Ni/Au)/Al<sub>0.22</sub>Ga<sub>0.78</sub>N/AlN/GaN heterostructure at room temperature.

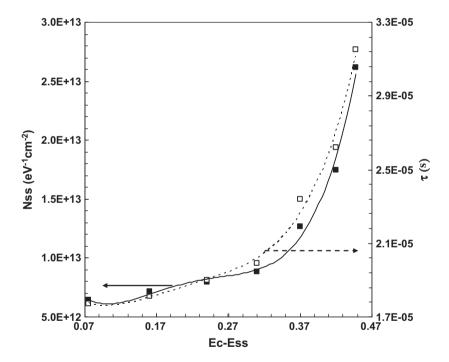

Fig. 11. The energy distribution of interface states and their time constant obtained from conductance method for  $(Ni/Au)/Al_{0.22}Ga_{0.78}N/AlN/GaN$  heterostructures at room temperature.

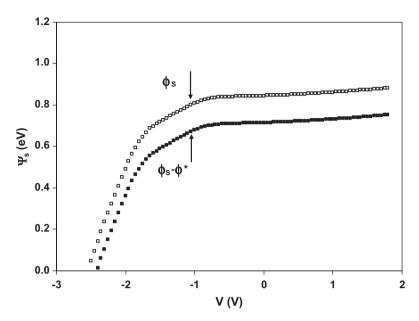

where  $\Phi_F$  is the position of Fermi energy level  $\Phi_F = kT/q \ln(N_C/N_D)$ . The surface potential  $(\Phi_s)$  as a function of bias is found from the numerical integration of the lowest measureable frequency C-V curve according to

$$\Phi_{S} = \int_{V_{a}}^{V_{i}} [1 - C_{LF}/C_{ox}] dV_{G} + \Phi^{*}$$

(6)

where  $V_a$  is the bias voltage in strong accumulation when the capacitance is equal to the oxide capacitance  $C_{\rm ox}$  and the integration constant  $\Phi^*$  was found by extrapolation of the  $C_{sc}^{-2}-\Phi_S$  curve in the depletion region (0.13 eV) to  $C_{sc}^{-2}=0$  [17,44]. The surface potential vs. applied voltage is shown in Fig. 10. The energy position is calcu-

lated by the Eq. (5). From the slope of the  $C^{-2}$  vs. V plot in the inversion region at 2 MHz, the doping density  $N_D$  of the substrate is determined to be  $2.48 \times 10^{14}$  cm<sup>-3</sup>. As can be seen in Fig. 9 for each gate bias the  $G_{ss}$ -ln(f) plot shows a peak, and due to the  $N_{ss}$  contribution the peak position shifts from low frequency to high as the bias changes from depletion toward the accumulation region as predict by the theory. Each plot goes through a maxima at  $\omega \tau = 1.98$  with values of  $(G_{ss})_{max} = 0.402$  qA  $N_{ss}$ . The ordinates and frequencies of the maxima yield density of the  $N_{ss}$  and their time constant " $\tau$ ", respectively. The values of the interface states and their relaxation time are shown in Fig. 11. It is observed that both interface state density  $N_{ss}$  and their time constant  $\tau$  show decrease

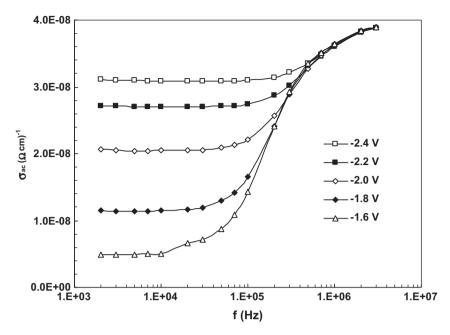

Fig. 12. Frequency dependence of ac electric conductivity ( $\sigma_{ac}$ ) for various applied voltage of (Ni/Au)/Al<sub>0.22</sub>Ga<sub>0.78</sub>N/AlN/GaN heterostructures at room temperature.

with the increasing energy from the bottom of the conduction band. As can be seen in Fig. 11, the values of  $N_{ss}$  rise exponentially with bias (or  $E_{ss}$ ) without any peak and minimum. On the other hand, Aydın et al. [40] found that density distribution profile of  $N_{ss}$  has U shape behavior. Similar results have been also reported in literature [45,46]. Such behavior of  $N_{ss}$  can be attributed to interface state continuum and not with single level states or bands of interfacial states as suggested by Kar and Dahlke [14]. The other explanation of such behavior may be the particular distribution of interface states where the charges located at the semiconductor/interfacial layer interface with energy states in the semiconductor forbidden band gap. In other word, the energy density distribution of  $N_{cc}$  profile depends on many factors such as frequency, the magnitude of external ac signal, applied dc voltage, the interfacial layer deposited or native, the fabrication process, the life time of charges at interface states and the homogeneity of interfacial layer. Therefore, the energy density distribution profile of  $N_{ss}$  may show changes from one sample to another.

The behavior of ac electrical conductivity ( $\sigma_{ac}$ ) of the (Ni/Au)/Al<sub>0.22</sub>Ga<sub>0.78</sub>N/AlN/GaN heterostructure at various voltages is presented in Fig. 12. It is noticed that the electrical conductivity generally increases with the increasing frequency. At low frequency, it is independent of frequency for each voltage. This behavior can be attributed to a gradual decrease in series resistance with increasing frequency [47].

## 4. Conclusions

The effects of  $N_{ss}$  and  $R_s$  on the non-ideal electrical characteristics of (Ni/Au)/Al<sub>0.22</sub>Ga<sub>0.78</sub>N/AlN/GaN heterostructures have been investigated by using I–V, C–V and  $G/\omega$ –V measurements at room temperature. The presence of high values of  $R_s$  leads to the downward concave curvature in the forward bias I–V and a peak in C–V characteristics at sufficiently high bias voltage. Experimental values of C and C0 show large frequency and bias voltage dispersion due to the presence of  $N_{ss}$  at MS interface and  $R_s$ . It is clear that the three regimes of accumulation, depletion and inversion are clearly shown for each C–V curve. Also, C–V curves have two distinctive peaks which are known to be related with depletion region (first peak) due to  $N_{ss}$  contribution and accumulation region (second

peak) due to the influence of  $R_s$ . The magnitude of these peaks was found to depend strongly on the values of  $R_s$ ,  $N_{ss}$  and the external ac signal superimposed on the dc bias. The ac electrical conductivity ( $\sigma_{ac}$ ) values for various bias voltages are almost independent of frequency up to 100 kHz, and after this frequency level they it increase with the increasing frequency. In addition, the high-frequency capacitance ( $C_m$ ) and conductance ( $G_m/\omega$ ) values measured under forward and reverse bias were corrected to minimize the effect of series resistance. The results indicate that the interfacial polarization can occur more easily especially at low frequencies. Experimental results confirmed that the  $N_{ss}$  and  $R_s$  are important parameters which influence the electrical characteristics of (Ni/Au)/Al<sub>0.22</sub>Ga<sub>0.78</sub>N/AlN/GaN heterostructures. Therefore, especially the measured C and  $G/\omega$  must be corrected to eliminate the effect of  $R_s$ .

#### References

- Arslan E, Butun S, Safak Y, Uslu H, Tascioglu I, Altındal S, et al. Microelectron Reliab 2011;51:370.

- [2] Mishra UK, Parikh P, Wu Y-F. Proc IEEE 2002;90:1022.

- [3] Lisesivdin SB, Demirezen S, Caliskan MD, Yildiz A, Kasap M, Ozcelik S, et al. Semicond Sci Technol 2008;23:095008.

- [4] Kim H, Schuette M, Jung H, Song J, Lee J, Lu W, et al. Appl Phys Lett 2006;89:053516.

- [5] Kim H, Thompson RM, Tilak V, Prunty TR, Shealy JR, Eastman LF. IEEE Electron Dev Lett 2003;24:421.

- [6] Yu H, Calışkan D, Özbay E. J Appl Phys 2006;100:033501.

- [7] Altındal S, Safak Y, Tascıoglu I, Ozbay E. Surf Interface Anal 2010;42:803.

- [8] Dadgar A, Hums C, Diez A, Bläsing J, Krost A. J Cryst Growth 2006;297:279. [9] Sze SM. Physics of semiconductor devices. 2nd ed. New York: Wiley; 1981.

- [10] Rhoderick EH, Williams RH. Metal-semiconductor contacts. 2nd ed. Oxford: Clarendon Press; 1988.

- [11] Crowell CR, Sze SM. J Appl Phys 1965;36:3212.

- [12] Card HC, Rhoderick EH. J Phys D: Appl Phys 1971;4:1589.

- [13] Rhoderick H. Metal-semiconductor contacts. New York: Oxford University Press: 1978.

- [14] Kar S, Dahlke WE. Solid-State Electron 1972;15:221.

- [15] Kar S, Varma S. J Appl Phys 1985;58:4256.

- [16] Nicollian EH, Goetzberger A. Appl Phys Lett 1965;7:216.

- [17] Nicollian EH, Brews JR. MOS physics and technology. New York: John Wiley & Sons; 1982.

- [18] Kar S, Narasimhan RL. J Appl Phys 1987;61(12):5353.

- [19] Demirezen S, Altındal Ş. Curr Appl Phys 2010;10:1188.

- [20] Kerberlau U, Kassing R. Solid State Electron 1979;22(1):37.

- [21] Khun M. Solid State Electron 1970;13(6):873.

- [22] Castagne R, Vapaille A. Surf Sci 1971;28(1):157.

- [23] Hung KK, Cheng YC. J Appl Phys 1987;62(10):4204.

- [24] Chowdhury P, Barshilia HC, Selvakumar N, Deepthi B, Rajam KS, Chaudhuri AR, et al. Physica B 2008;403:3718.

- [25] Okur S, Yakuphanoğlu F, Özsoy M, Kara Kadayıfçılar P. Microelectron Eng 2009;11:2305.

- Şahingöz R, Kanbur H, Voigt M, Soykan C. Synth Met 2008;158:727.

- [27] Gupta RK, Ghosh K, Kahol PK. Curr Appl Phys 2009;9:933.

- [28] Tung RT. Phys Rev B 1992;45:13509.

- [29] Sullivan JP, Tung RT, Pinto MR, Graham WR. J Appl Phys 1991;70:7403.

- [30] Kampen TU, Park S, Zahn DRT. Appl Surf Sci 2002;190:461.

- [31] Parlaktürk F, Altındal Ş, Tataroğlu A, Parlak M, Agasiev A. Microelectron Eng 2008;85:81.

- [32] Altındal Ş, Kanbur H, Yücedağ İ, Tataroğlu A. Microelectron. Eng. 2008;85:1495.

- [33] Chattopadhyay P, Raychaudhuri B. Solid State Electron 1993;36:605.

- [34] Norde H. J Appl Phys 1979;50:5052.

- [35] Cheung SK, Cheung NW. Appl Phys Lett 1986;49:85.

- [36] Yücedağ İ, Altındal Ş, Tataroğlu A. Microelectron Eng 2007;84:180.

- [37] Chattopadhyay P, Raychaudhuri B. Solid State Electron 1992;35:1023.

- [38] Akal B, Benamara Z, Gruza B, Bideux L, Bouiadjra NB. Mater Sci Eng C 2002:21:291.

- [39] Fernandez J, Godignon P, Berberich S, Rebollo J, Brezenanu G, Millian J. Solid-State Electron 1996;39:1359.

- [40] Aydın ME, Türüt A. Microelectron Eng 2007;84:2875.

[41] Liu WL, Chen YL, Balandin AA, Wang KL. J Nanoelectron Optoelectron 2006;1:258.

- [42] Evangelou EK, Konofaos N, Craven MR, Cranton WM, Thomas CB. Appl Surf Sci 2000;166:504.

- [43] Werner J, Ploog K, Queisser HJ. Phys Rev Lett 1986;57:1080.

- [44] Berglund CN. IEEE Trans Nucl Sci 1966;ED-13(10):701.

- [45] Singh A. Solid State Electron 1985;28:223.

- [46] Sands D, Brunson KM, Tayarani-Najaran MH. Semicond Sci Technol 1992;7:1091.

- [47] Tataroglu A, Altındal S, Bülbül MM. Microelectron Eng 2005;81:140.