## Diode behavior in ultra-thin low temperature ALD grown zinc-oxide on silicon

Nazek El-Atab, Samar Alqatari, Feyza B. Oruc, Tewfic Souier, Matteo Chiesa, Ali K. Okyay, and Ammar Nayfeh

Citation: AIP Advances **3**, 102119 (2013); doi: 10.1063/1.4826583 View online: http://dx.doi.org/10.1063/1.4826583 View Table of Contents: http://scitation.aip.org/content/aip/journal/adva/3/10?ver=pdfcov Published by the AIP Publishing

### Articles you may be interested in

Electrochemical deposition of iron sulfide thin films and heterojunction diodes with zinc oxide APL Mat. **2**, 032110 (2014); 10.1063/1.4869035

Low power zinc-oxide based charge trapping memory with embedded silicon nanoparticles via poole-frenkel hole emission Appl. Phys. Lett. **104**, 013112 (2014); 10.1063/1.4861590

Zinc-oxide charge trapping memory cell with ultra-thin chromium-oxide trapping layer AIP Advances **3**, 112116 (2013); 10.1063/1.4832237

Effect of in situ hydrogen plasma treatment on zinc oxide grown using low temperature atomic layer deposition J. Vac. Sci. Technol. A **31**, 01A124 (2013); 10.1116/1.4767813

Structure and optoelectronic properties of spray deposited Mg doped p -CuCrO 2 semiconductor oxide thin films J. Appl. Phys. **104**, 023712 (2008); 10.1063/1.2957056

# AIP Journal of Applied Physics

*Journal of Applied Physics* is pleased to announce André Anders as its new Editor-in-Chief

All article content, except where otherwise noted, is licensed under a Creative Commons Attribution 3.0 Unported license. See: http://creativecommons.org/licenses/by/3.0/ Downloaded to IP: 139.179.2.116 On: Mon, 14 Jul 2014 12:30:38

# Diode behavior in ultra-thin low temperature ALD grown zinc-oxide on silicon

Nazek El-Atab,<sup>1</sup> Samar Alqatari,<sup>1</sup> Feyza B. Oruc,<sup>2,3</sup> Tewfic Souier,<sup>1</sup> Matteo Chiesa,<sup>1</sup> Ali K. Okyay,<sup>2,3</sup> and Ammar Nayfeh<sup>1</sup> <sup>1</sup>Institute Center for Microsystems – Imicro, Department of Electrical Engineering and

<sup>2</sup>Department of Electrical and Electronics Engineering, Bilkent University,

06800 Ankara, Turkey

<sup>3</sup>UNAM-National Nanotechnology Research Center and Institute of Materials Science and Nanotechnology, Bilkent University, 06800 Ankara, Turkey

(Received 5 September 2013; accepted 10 October 2013; published online 18 October 2013)

A thin-film ZnO(n)/Si(p+) heterojunction diode is demonstrated. The thin film ZnO layer is deposited by Atomic Layer Deposition (ALD) at different temperatures on a p-type silicon substrate. Atomic force microscopy (AFM) AC-in-Air method in addition to conductive AFM (CAFM) were used for the characterization of ZnO layer and to measure the current-voltage characteristics. Forward and reverse bias n-p diode behavior with good rectification properties is achieved. The diode with ZnO grown at 80°C exhibited the highest on/off ratio with a turn-on voltage (V<sub>ON</sub>) ~3.5 V. The measured breakdown voltage (V<sub>BR</sub>) and electric field (E<sub>BR</sub>) for this diode are 5.4 V and 3.86 MV/cm, respectively. © 2013 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution 3.0 Unported License. [http://dx.doi.org/10.1063/1.4826583]

Extensive research is being conducted on the II-VI compound semiconductor zinc oxide owing to its optoelectronics properties and its wide technological applications. ZnO has been extensively studied recently in thin film transistors (TFTs), light emitting diodes (LED), and solar cells.<sup>1–3</sup> For low-cost flexible electronics, low temperature techniques are of critical importance. Sputtering, Atomic Layer Deposition (ALD), solution-based techniques, and pulsed laser deposition are some of the methods used to deposit ZnO.<sup>3–14</sup> ALD technique has grown in importance over the last years because it can achieve large area uniformity, precise thickness control, highly conformal deposition, and most importantly; it can be applied under low temperature growth which is crucial for the fabrication of low cost and flexible electronics. Earlier we showed a working SONOS memory using ALD grown ZnO.<sup>15</sup> In this work a ZnO/Si heterojunction n-p diode is grown by ALD and demonstrated by Conductive Atomic Force Microscopy (CAFM).

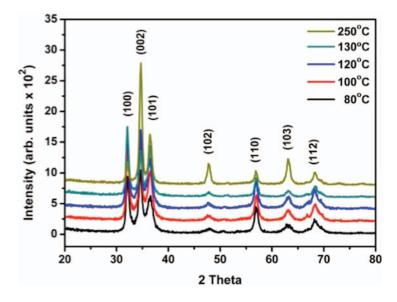

Before device fabrication processes, silicon wafers are placed in piranha solution (H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub> (4:1) ratio) for ten minutes in order to remove organic residues from the surface. Then the wafers are placed in dilute HF acid solution to remove native oxide and achieve hydrophobic surfaces for efficient device fabrication. The heterojunction diode is then fabricated by depositing 14 nm of ZnO by ALD at different temperatures on highly doped ( $5 \times 10^{18}$ /cm<sup>3</sup> Boron) p-type (100) Si wafer. ALD-deposited ZnO is n-type due to native crystallographic defects such as interstitial zinc and oxygen vacancies which behave as electron donors.<sup>15</sup> The polycrystalline nature of the deposited ZnO is analyzed by X-Ray Diffraction (XRD) measurements. All of the ALD grown ZnO thin films exhibit "*hexagonal wurtzite*" structure with characteristic XRD peaks at (100), (002), (101), (102), (110), (103) and (112) crystal orentations as shown in Fig. 1, indicating the formation of good polycrystalline ZnO thin films through ALD method.

After the ALD growth, AFM AC-in-Air method in addition to CAFM were used for the characterization of ZnO layer deposited at 80° and 130° on Si wafer. The AFM used is an Asylum

2158-3226/2013/3(10)/102119/7

**3**, 102119-1

© Author(s) 2013

FIG. 1. XRD data of ZnO thin films grown at various temperatures.

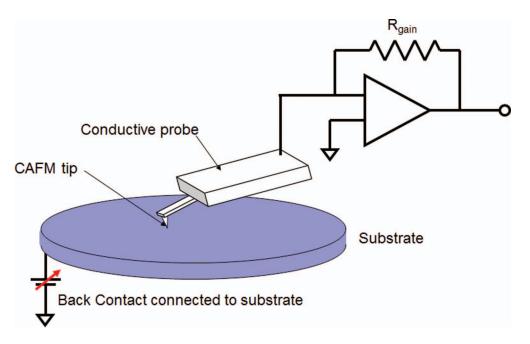

FIG. 2. CAFM setup showing the conductive probe and the transimpedance amplifier used to detect the current flow.

Research MFP-3D, with a dual-gain CAFM module for the electrical measurements. For topography imaging AC-in-Air method was used. The electrical mapping was done in contact mode using the dual-gain module.

The CAFM setup is shown in Fig. 2. As a matter of fact, testing the conductivity of the samples using the AFM is made possible in two ways: probing them horizontally allows for analyzing the electric properties of the ZnO thin film solely, while probing them vertically allows for analyzing the electric properties of the ZnO-Si junction, locally, as a whole. In this paper, we use the vertical approach of using conductive AFM to measure the local properties of the ZnO-Si junction, and apply voltage on the sample vertically. In order to perform conductive AFM, the electrode was in contact with a metal base, which the samples were put in contact with using silver paste. A diamond probe was used to test for conductivity under contact mode, while a silicon probe was used for collecting

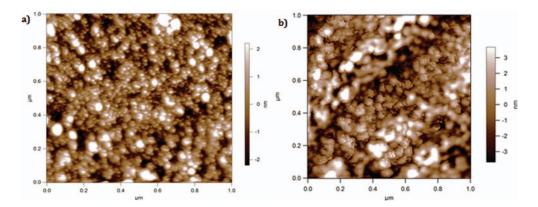

FIG. 3. Topography image of ZnO layer deposited by ALD a) at  $80^{\circ}$  b) at  $130^{\circ}$ .

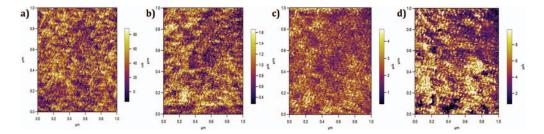

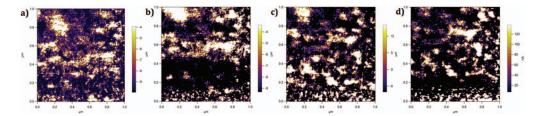

FIG. 4. Surface conductivity of 80° sample with different applied surface voltages. a) 1V, b) 2V, c) 3V, d) 4V.

FIG. 5. Surface conductivity of 130° sample with different applied surface voltages. a) 1V, b) 2V, c) 3V, d) 4V.

topography images in AC mode. In the conductivity experiments, the current flows between the tip and the sample, generating surface conductivity images and I-V curves at selected points, for the ZnO-Silicon sample.

$1 \times 1$  um<sup>2</sup> topography images were obtained of both 80° and 130° samples as shown in Fig 3(a) and Fig. 3(b), respectively. The surface roughness of the two samples did not significantly differ: the extracted surface RMS roughness is around 1.7 nm for the 80° sample, and 1.1 nm for the 130°. For the 80° sample; the biggest particle size was 60 nm and the smallest particle was 20 nm, while for the 130° sample; the biggest particle size was 60 nm and the smallest particle was 15 nm. This confirms that the deposited layer of ZnO is more of a continuous film rather than discrete islands. Furthermore, surface conductivity images were obtained for different applied surface voltages and at different locations. The surface conductivity images of the 80° and 130° samples depicted in Fig. 4 and Fig. 5, respectively, show that the the 80° sample surface conductivity is higher than the 130° sample. However, more measurements are still needed to confirm this finding. In addition, Fig. 4 and Fig. 5 portray non-homogeneous electric behavior across the surface of the thin film, despite its smoothness. The more conductive parts, as shown in the images, do not correlate to the grains or features shown in the topography images shown in Fig. 3. The inhomogeneity of the surface

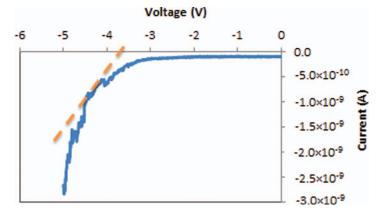

FIG. 6. Measured forward bias of the  $80^\circ$  diode showing a  $V_{ON}$  of 3.5 V.

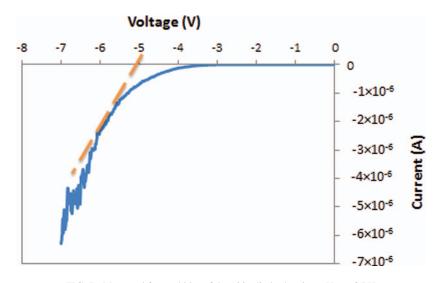

FIG. 7. Measured forward bias of the  $130^{\circ}$  diode showing a V<sub>ON</sub> of 5 V.

conductance could be attributed to grains of Si, defects in the thin film deposition, or the growth temperature, but the reason behind the inhomogeneous conductive behavior could not be verified.

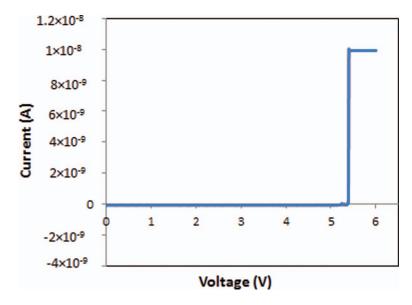

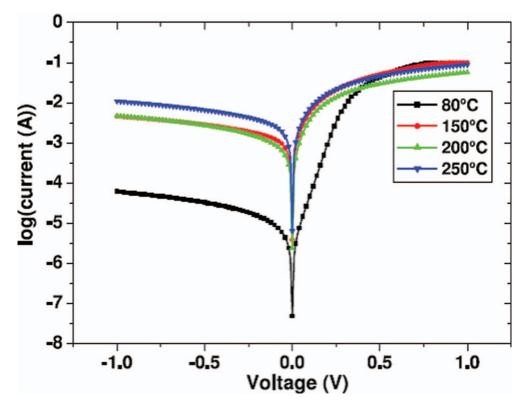

Additionally, CAFM detects the resulting current flow using a transimpedance amplifier.<sup>16</sup> Using this technique, I–V characteristics of the ZnO(n)/Si(p) device can be obtained. Fig. 6 and Fig. 7 plot the transfer characteristic (I-V) of the 80° and 130° samples, respectively, in the forward bias with the voltage being swept from 0V to -6V. The results exhibit a diode-like forward bias curve with a turn-on voltage of  $\sim 3.5$  V for the 80° sample while 5 V for the 130° sample. Also, the transfer characteristic (I–V) of the 80° sample in the reverse bias is shown in Fig. 8 with the voltage being swept from 0 to 6 V. In this sweep, an exponential increase in current is not seen due to the large barrier in reverse bias, as expected. Rather, a sharp increase in current is observed at around 5.4V which is more consistent with diode breakdown. This breakdown could be due to tunneling (zener) or impact ionization (avalanche). Using this breakdown voltage ( $V_{BR} = 5.4V$ ), the breakdown electric field ( $E_{BR}$ ) of the 14 nm ZnO layer is extracted to be 3.86 MV/cm. However, the 130° sample didn't show any reverse bias curve when the voltage was being swept from 0 V up to 6 V. Furthermore, the ZnO/Si heterojunction diode that has been fabricated based on 80°C-ALD-grown ZnO thin film exhibited the highest electrical rectification characteristics with an ON/OFF ratio reaching up to 10<sup>3</sup> as shown in Fig. 9.

The existence of a critical breakdown field in reverse bias and exponential increase in forward bias with the  $80^{\circ}$  sample confirms the creation of n-p heterojunction diode. Table I summarizes

FIG. 8. Measured reverse bias of the n-p ZnO/Si diode with  $V_{BR}$  of 5.4 V.

FIG. 9. Dark current (I) versus bias voltage (V) spectrum of the fabricated ZnO-Si diodes.

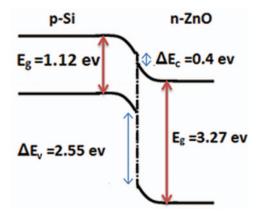

the results obtained for the diode with ZnO grown at 80° with key parameters  $V_{BR}$ ,  $E_{BR}$ , and  $V_{ON}$ . Moreover, the equilibrium energy band diagram of the ZnO(n)/Si(p) diode is represented in Fig. 10. The conduction and valence band offsets ( $\Delta E_c$  and  $\Delta E_v$ ) between Si and ZnO are 0.4 eV and 2.55 eV, respectively.<sup>17</sup> From the energy band diagram, it is shown that there is a 0.4 eV barrier for electrons and 2.55 eV barrier for holes. In the reverse bias, the barriers increase and hence the

#### 102119-6 El-Atab et al.

| V <sub>ON</sub> | 3.5 V      |

|-----------------|------------|

| V <sub>BR</sub> | 5.4 V      |

| E <sub>BR</sub> | 3.86 MV/cm |

TABLE I. Extracted values of V<sub>BR</sub>, E<sub>BR</sub>, and V<sub>ON</sub> of the n-p diode with ZnO grown at 80°C.

FIG. 10. Energy band diagram of the heterojunction n-ZnO/p-Si at zero voltage bias. The diagram shows the barrier for the electrons and holes.

low current is observed. At high enough electric field, tunneling or impact ionization dominates leading to breakdown.

In summary, a heterojunction diode was fabricated by low temperature ALD deposition of 14 nm of ZnO on silicon (p+) substrate. The current voltage characteristic measured is consistent with an n-p diode. The results showed that the diode with ZnO grown at  $80^{\circ}$  exhibited higher on/off ratio, and lower turn on voltage and turn on current than the  $130^{\circ}$  grown ZnO. Moreover, the results highlight the possible use of this ZnO low cost, flexible, and transparent electronic applications and for future low cost thin film photovoltaic cells.

### ACKNOWLEDGMENTS

We gratefully acknowledge Dr. Sabri Alkis and Amro Alkhatib for their contributions in the experiments and analysis provided in this paper.

- <sup>2</sup> A. Gupta and A. D. Compaan, "14% CdS/CdTe thin film cells with ZnO:Al TCO," in *Proceedings of the MRS Spring Meeting*, pp. 1–6, San Francisco, Calif, USA, 2003.

- <sup>3</sup> U. Rau and M. Schmidt, "Electronic properties of ZnOCd- SCu(In, Ga)Se2 solar cells—aspects of heterojunction formation," Thin Solid Films **387**, 141–146, (2001).

- <sup>5</sup> R. L. Hoffman, "ZnO-channel thin-film transistors: Channel mobility," J. Appl. Phys. 95, 5813–5819 (2004).

- <sup>6</sup> E. M. C. Fortunato, P. M. C. Barquinha, A. C. M. B. G. Pimentel, A. M. F. Goncalves, A. J. S. Marques, R. F. P. Martins, and L. M. N. Pereira, "Wide-bandgap high-mobility ZnO thin-film transistors produced at room temperature," Appl. Phys. Lett. 85, July 2004.

- <sup>7</sup> E. M. C. Fortunato, P. M. C. Barquinha, A. C. M. B. G. Pimentel, A. M. F. Goncalves, A. J. S. Marques, L. M. N. Pereira, and R. F. P. Martins, "Fully Transparent ZnO Thin-Film Transistor Produced at Room Temperature," Adv. Mater. 17, 590–594, March, 2005.

- <sup>8</sup> H. Yabuta, M. Sano, K. Abe, T. Aiba, T. Den, H. Kumomi, K. Nomura, T. Kamiya, and H. Hosono, "High-mobility thin-film transistor with amorphous InGaZnO~4 channel fabricated by room temperature rf-magnetron sputtering," Appl. Phys. Lett. 89 (2006).

- <sup>9</sup> M. J. Chen, J. R. Yang, and M. Shiojiri, "ZnO-based ultra-violet light emitting diodes and nanostructures fabricated by atomic layer deposition," Semiconductor Science and Technology 27 (2012).

- <sup>10</sup> N. Huby, S. Ferrari, E. Guziewicz, M. Godlewski, and V. Osinniy, "Electrical behavior of zinc oxide layers grown by low temperature atomic layer deposition," Appl. Phys. Lett. 92 (2008).

<sup>&</sup>lt;sup>1</sup>P. Jackson, D. Hariskos, E. Lotter *et al.*, "New world record efficiency for Cu(In,Ga)Se2 thin-film solar cells beyond 20%," Progress in Photovoltaics: Research and Applications, **19**, 894–897, (2011).

<sup>&</sup>lt;sup>4</sup> R. L. Hoffman, B. J. Norris, and J. F. Wager, "ZnO-based transparent thin-film transistors," Appl. Phys. Lett. **82**, 733–735 (2003).

102119-7 El-Atab et al.

- <sup>11</sup> S. Kwon, S. Bang, S. Lee, W. Jeong, H. Kim, S. C. Gong, H. J. Chang, H.-h. Park, and H. Jeon, "Characteristics of the ZnO thin film transistor by atomic layer deposition at various temperatures," Semicond. Sci. Technol. 24, March 2009.

- <sup>12</sup> J. Siddiqui, E. Cagin, D. Chen, and J. D. Phillips, "ZnO thin-film transistors with polycrystalline(Ba,Sr)TiO3 gate insulators," Appl. Phys. Lett. 88 (2006).

- <sup>13</sup> D. Kim, H. Kang, J.-M. Kim, and H. Kim, "The properties of plasma-enhanced atomic layer deposition (ALD) ZnO thin films and comparison with thermal ALD," Appl. Surf. Sci. **257**, 3776–3779, Feburary 2011.

- <sup>14</sup> H. S. Kim, F. Lugo, S. J. Pearton, D. P. Norton, Yu-Lin Wang, and F. Ren, "Phosphorus doped ZnO light emitting diodes fabricated via pulsed layer deposition," Appl. Phys. Lett. 92 (2008).

- <sup>15</sup> F. B. Oruc, F. Cimen, A. Rizk, M. Ghaffari, A. Nayfeh, A. K. Okyay, "Thin-Film ZnO Charge-Trapping Memory Cell Grownin a Single ALD Step," Electron Device Lett. 33, 1714–1716 (2012).

- <sup>16</sup> M. Lanza, L. Aguilera, M. Porti, M. Nafria, and X. Aymerich, "Improving the electrical performance of a CAFM for gate oxide reliability measurements," Electron Devices (2009).

- <sup>17</sup> J. H. Hea and C. H. Ho, "The study of electrical characteristics of heterojunction based on ZnO nanowires using ultrahighvacuum conducting atomic force microscopy," Appl. Phys. Lett. **91** December 2007.