### **Calhoun: The NPS Institutional Archive**

### **DSpace Repository**

Theses and Dissertations

1. Thesis and Dissertation Collection, all items

2021-09

# A FIELD-PROGRAMMABLE GATE ARRAY IMPLEMENTATION OF A COGNITIVE RADAR TARGET RECOGNITION SYSTEM

## Sessions, Calvin A.

Monterey, California. Naval Postgraduate School

http://hdl.handle.net/10945/69474

This publication is a work of the U.S. Government as defined in Title 17, United States Code, Section 101. Copyright protection is not available for this work in the United States.

Downloaded from NPS Archive: Calhoun

Calhoun is the Naval Postgraduate School's public access digital repository for research materials and institutional publications created by the NPS community. Calhoun is named for Professor of Mathematics Guy K. Calhoun, NPS's first appointed -- and published -- scholarly author.

> Dudley Knox Library / Naval Postgraduate School 411 Dyer Road / 1 University Circle Monterey, California USA 93943

http://www.nps.edu/library

# NAVAL POSTGRADUATE SCHOOL

**MONTEREY, CALIFORNIA**

# THESIS

### A FIELD-PROGRAMMABLE GATE ARRAY IMPLEMENTATION OF A COGNITIVE RADAR TARGET RECOGNITION SYSTEM

by

Calvin A. Sessions

September 2021

Thesis Advisor: Co-Advisor: Ric Romero Douglas J. Fouts

Approved for public release. Distribution is unlimited.

| <b>REPORT DOCUMENTATION PAGE</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                      |                                          | Form Approved OMB<br>No. 0704-0188                     |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------|--|

| Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instruction, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188) Washington, DC 20503.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                      |                                          |                                                        |  |

| 1. AGENCY USE ONLY<br>(Leave blank)2. REPORT DATE<br>September 20213. REPORT TYPE AND DAT<br>Master's thes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                      | YPE AND DATES COVERED<br>Master's thesis |                                                        |  |

| COGNITIVE RADAR TARGET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4. TITLE AND SUBTITLE<br>A FIELD-PROGRAMMABLE GATE ARRAY IMPLEMENTATION OF A<br>COGNITIVE RADAR TARGET RECOGNITION SYSTEM5. FUNDING NUMBERS6. AUTHOR(S) Calvin A. Sessions6. Calvin A. Sessions6. Calvin A. Sessions |                                          |                                                        |  |

| 7. PERFORMING ORGANIZA<br>Naval Postgraduate School<br>Monterey, CA 93943-5000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ATION NAME(S) AND ADDF                                                                                                                                                                                               | ESS(ES)                                  | 8. PERFORMING<br>ORGANIZATION REPORT<br>NUMBER         |  |

| 9. SPONSORING / MONITOR<br>ADDRESS(ES)<br>N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ING AGENCY NAME(S) AN                                                                                                                                                                                                | D                                        | 10. SPONSORING /<br>MONITORING AGENCY<br>REPORT NUMBER |  |

| <b>11. SUPPLEMENTARY NOTE</b> official policy or position of the I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                      |                                          | he author and do not reflect the                       |  |

| 12a. DISTRIBUTION / AVAILABILITY STATEMENT       12b. DISTRIBUTION CODE         Approved for public release. Distribution is unlimited.       A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                      |                                          |                                                        |  |

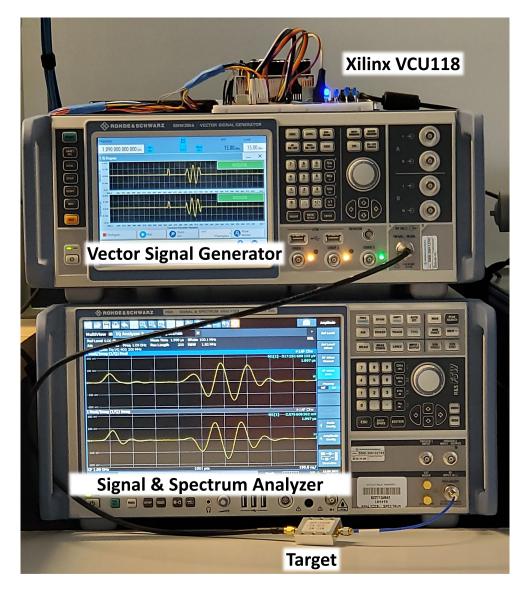

| <b>13. ABSTRACT (maximum 200 words)</b><br>The objective of this study is to design a field-programmable gate array (FPGA) implementation of a cognitive radar (CRr) target recognition system for electronic warfare applications. This thesis expands on the closed-loop adaptive matched waveform transmission technique called probability of weighted energy (PWE). This work also investigates the feasibility of applying the PWE technique in a functional digital hardware realization. Initially, a PWE Monte Carlo simulation model is developed in the Verilog hardware description language that is simulated in the Xilinx Vivado environment. The Verilog module components developed in the Monte Carlo model are then incorporated into a CRr target recognition system experiment utilizing the Xilinx VCU118 Evaluation Board. The VCU118 features the Virtex UltraScale+high-performance FPGA to accomplish CRr adaptive waveform generation and transmission, digital signal processing requirements, and target classification. The Rohde & Schwarz SMW200A Vector Signal Generator and FSW Signal & Spectrum Analyzer function as the radar system transmitter and receiver, respectively, while the FPGA implementation enables the closed feedback loop used by the CRr. |                                                                                                                                                                                                                      |                                          |                                                        |  |

| 14. SUBJECT TERMS<br>cognitive radar, probability of weighted energy, field-programmable gate array, target15. NUMBER OF<br>PAGESclassification, eigenwaveform99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                      |                                          |                                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                      | 10 (ECUDIT)                              | 16. PRICE CODE                                         |  |

| CLASSIFICATION OF C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3. SECURITY<br>LASSIFICATION OF THIS<br>AGE                                                                                                                                                                          | 19. SECURITY<br>CLASSIFICATI<br>ABSTRACT | 20. LIMITATION OF<br>ION OF ABSTRACT                   |  |

| Unclassified Un<br>NSN 7540-01-280-5500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | nclassified                                                                                                                                                                                                          | Unclassified                             | UU<br>Standard Form 298 (Rev. 2-89                     |  |

Prescribed by ANSI Std. 239-18

#### Approved for public release. Distribution is unlimited.

#### A FIELD-PROGRAMMABLE GATE ARRAY IMPLEMENTATION OF A COGNITIVE RADAR TARGET RECOGNITION SYSTEM

Calvin A. Sessions Lieutenant Commander, United States Navy BS, Western Washington University, 2005

Submitted in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

from the

### NAVAL POSTGRADUATE SCHOOL September 2021

Approved by: Ric Romero Advisor

> Douglas J. Fouts Co-Advisor

Douglas J. Fouts Chair, Department of Electrical and Computer Engineering

#### ABSTRACT

The objective of this study is to design a field-programmable gate array (FPGA) implementation of a cognitive radar (CRr) target recognition system for electronic warfare applications. This thesis expands on the closed-loop adaptive matched waveform transmission technique called probability of weighted energy (PWE). This work also investigates the feasibility of applying the PWE technique in a functional digital hardware realization. Initially, a PWE Monte Carlo simulation model is developed in the Verilog hardware description language that is simulated in the Xilinx Vivado environment. The Verilog module components developed in the Monte Carlo model are then incorporated into a CRr target recognition system experiment utilizing the Xilinx VCU118 Evaluation Board. The VCU118 features the Virtex UltraScale+ high-performance FPGA to accomplish CRr adaptive waveform generation and transmission, digital signal processing requirements, and target classification. The Rohde & Schwarz SMW200A Vector Signal Generator and FSW Signal & Spectrum Analyzer function as the radar system transmitter and receiver, respectively, while the FPGA implementation enables the closed feedback loop used by the CRr.

# Table of Contents

| 1    | Introduction                                    | 1  |

|------|-------------------------------------------------|----|

| 1.1  | Thesis Objective                                | 2  |

| 1.2  | Thesis Organization                             | 2  |

| 2    | Cognitive Radar for Target Recognition          | 3  |

| 2.1  | Cognitive Radar Overview                        | 3  |

| 2.2  | Probability of Weighted Energy Theory           | 4  |

| 3    | Verilog Modeling and Design Simulation          | 9  |

| 3.1  | Verilog Model Overview                          | 9  |

| 3.2  | Verilog Model Design Description                | 9  |

| 3.3  | Verilog Model Results                           | 36 |

| 3.4  | Chapter Summary                                 | 42 |

| 4    | Hardware Design and RF Implementation           | 43 |

| 4.1  | Hardware Implementation Overview.               | 43 |

| 4.2  | Closed-loop Radar Configuration                 | 43 |

| 4.3  | Functional Design Description and Demonstration | 57 |

| 4.4  | Hardware Implementation Observations            | 68 |

| 4.5  | Chapter Summary                                 | 69 |

| 5    | Summary and Conclusion                          | 71 |

| 5.1  | Recommendations for Future Work                 | 73 |

| Lis  | t of References                                 | 75 |

| Init | tial Distribution List                          | 79 |

# List of Figures

| Figure 2.1  | Block Diagram of the Cognitive Radar Perception-Action Cycle.<br>Source: [2]                                               | 3  |

|-------------|----------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.2  | Basic Hardware Block Diagram of Perception-Action Cycle Model.<br>Source: [18].                                            | 4  |

| Figure 2.3  | PWE Adaptive Matched Waveform Transmission Block Diagram.         Source: [5].                                             | 5  |

| Figure 2.4  | Cognitive Radar Closed Feedback Loop Block Diagram Using PWE.<br>Source: [9]                                               | 6  |

| Figure 3.1  | Q15.16, 32-bit Signed Fixed-Point Representation in Verilog                                                                | 10 |

| Figure 3.2  | Q15.16, 32-bit Signed Fixed-Point Multiplication in Verilog                                                                | 11 |

| Figure 3.3  | Top Level Block Diagram of PWE Target Recognition Monte Carlo         Design in Verilog                                    | 13 |

| Figure 3.4  | Finite State Machine Behavioral Algorithm for Monte Carlo Model in Verilog                                                 | 15 |

| Figure 3.5  | Schematic Diagram of Division and Square Root Verilog Modules                                                              | 18 |

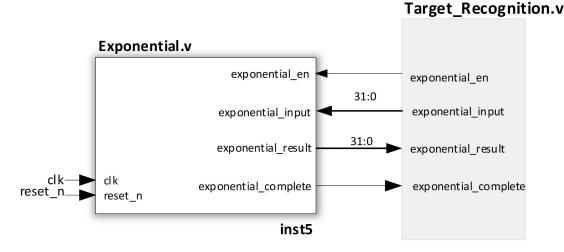

| Figure 3.6  | Exponential Verilog Module Schematic Diagram                                                                               | 19 |

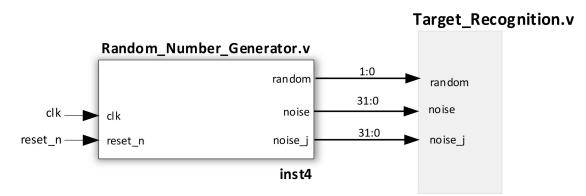

| Figure 3.7  | Pseudo-Random Number Generator Verilog Module Schematic .                                                                  | 21 |

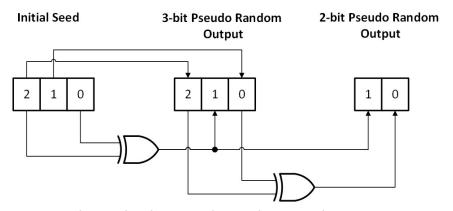

| Figure 3.8  | 2-bit and 3-bit Pseudo-Random Number Generator, Verilog Schematic<br>Representation                                        | 22 |

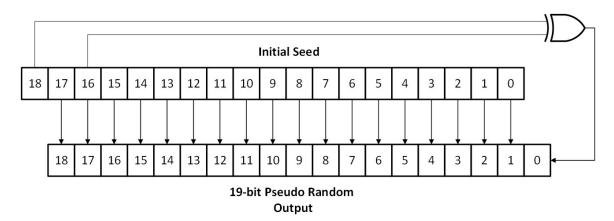

| Figure 3.9  | 19-bit Pseudo-Random Number Generator, Verilog Schematic Representation                                                    | 22 |

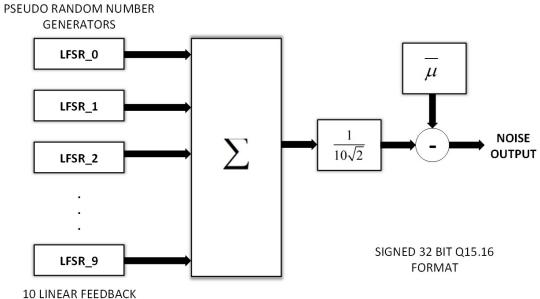

| Figure 3.10 | Pseudo-Gaussian Noise Generator Performed in Verilog Using 10 19-<br>bit Pseudo-Random Number Generators                   | 23 |

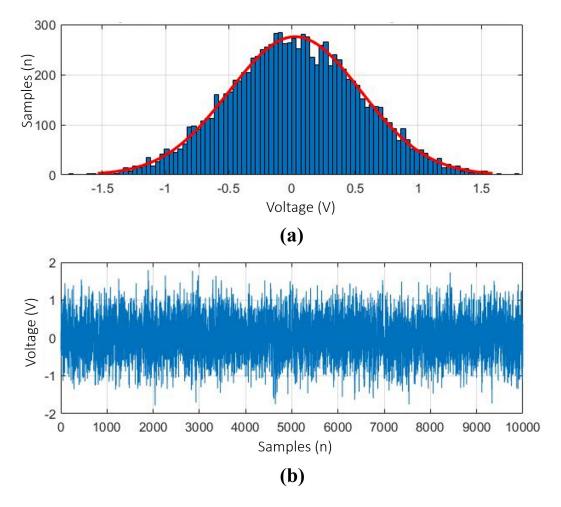

| Figure 3.11 | (a) Histogram of Gaussian Noise Model Using Verilog Noise Gener-<br>ator (b) Gaussian Noise Generation Over 10,000 Samples | 24 |

| Figure 3.12 | Transmit Waveform Generator Verilog Module Schematic                                                                                                                            | 25 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.13 | Transmit Waveform Generator Finite State Machine Behavioral Process of <i>XPWE.v</i>                                                                                            | 26 |

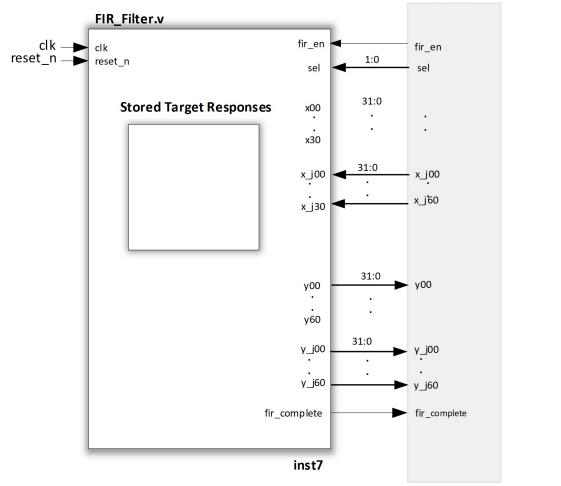

| Figure 3.14 | Finite Impulse Response Filter Verilog Module Schematic, FIR.v                                                                                                                  | 27 |

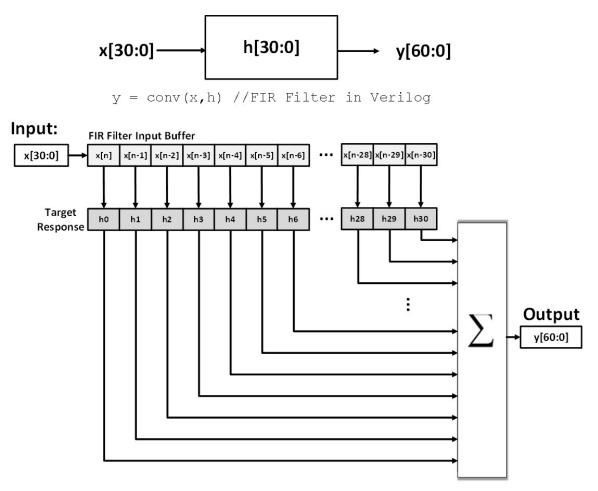

| Figure 3.15 | Finite Impulse Response Filter Block Diagram in Verilog                                                                                                                         | 28 |

| Figure 3.16 | (a) In-Phase and (b) Quadrature FIR Filter Output Performed in Verilog                                                                                                          | 29 |

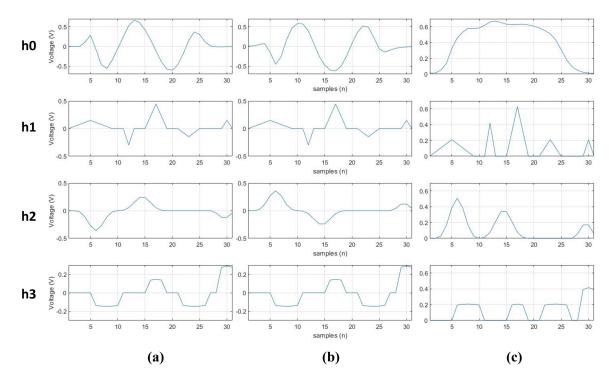

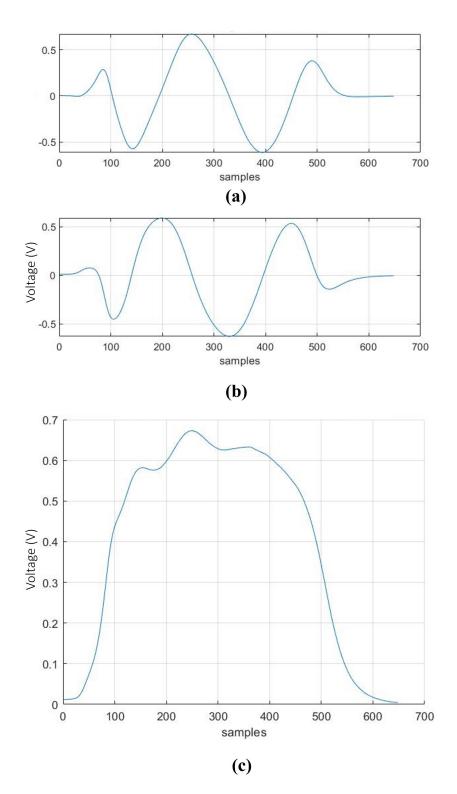

| Figure 3.17 | (a) In-Phase, (b) Quadrature, and (c) Magnitude Target Responses<br>Stored in System                                                                                            | 30 |

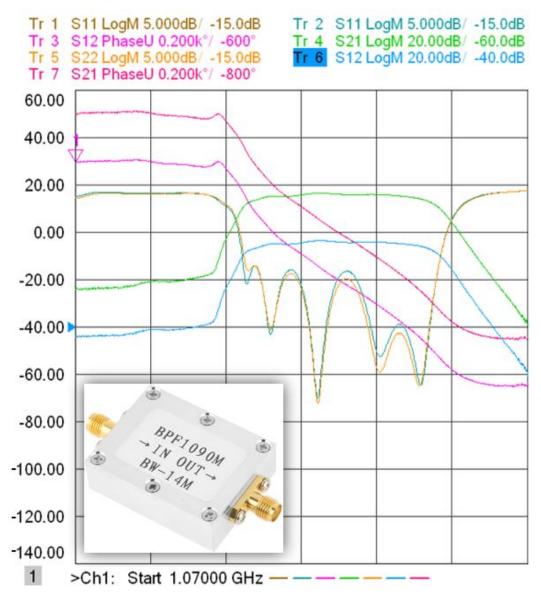

| Figure 3.18 | Vector Network Analyzer Measurements: Magnitude and Phase of a 1.090 GHz Narrowband Bandpass Filter in the Frequency Domain                                                     | 32 |

| Figure 3.19 | Baseband: (a) In-Phase, (b) Quadrature, and (c) Magnitude Derived from 1.090 GHz Bandpass Filter Measurements from VNA                                                          | 33 |

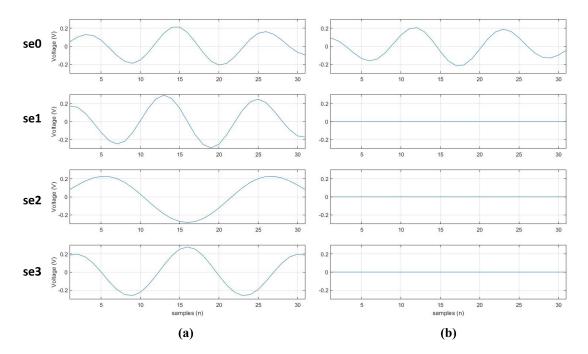

| Figure 3.20 | Baseband: (a) In-Phase, and (b) Quadrature Target Eigenwaveforms<br>Stored in the System                                                                                        | 34 |

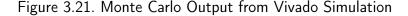

| Figure 3.21 | Monte Carlo Output from Vivado Simulation                                                                                                                                       | 36 |

| Figure 3.22 | Adaptive Waveform Transmission from Vivado Simulation, where $E_x = -10$ dB units, the Randomly Selected Target is <i>target</i> 0, and the Correct Classification is <b>h0</b> | 38 |

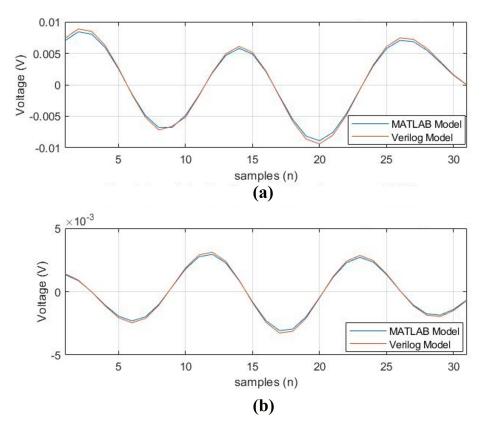

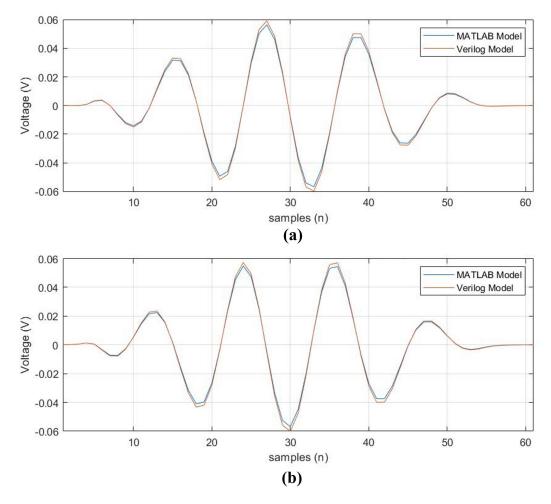

| Figure 3.23 | (a) In-Phase and (b) Quadrature Adaptive Transmit Waveform, <b>x</b> , $E_x$<br>= -30 dB units: Verilog Model vs. MATLAB Model                                                  | 39 |

| Figure 3.24 | (a) In-Phase and (b) Quadrature FIR Filter Output, $\mathbf{S} = \mathbf{x} * \mathbf{h0}$ , $E_x = -30$ dB units: Verilog Model vs. MATLAB Model                               | 40 |

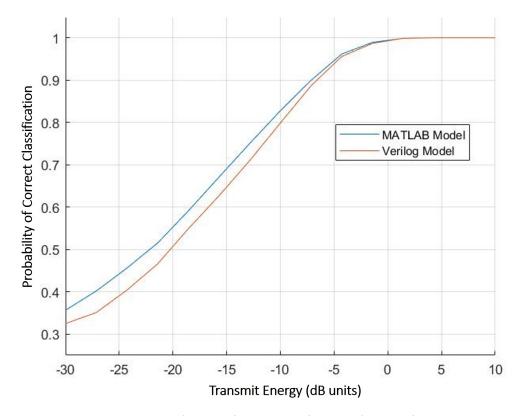

| Figure 3.25 | Monte Carlo Simulation Results: Verilog Implementation vs. MAT-LAB Implementation                                                                                               | 41 |

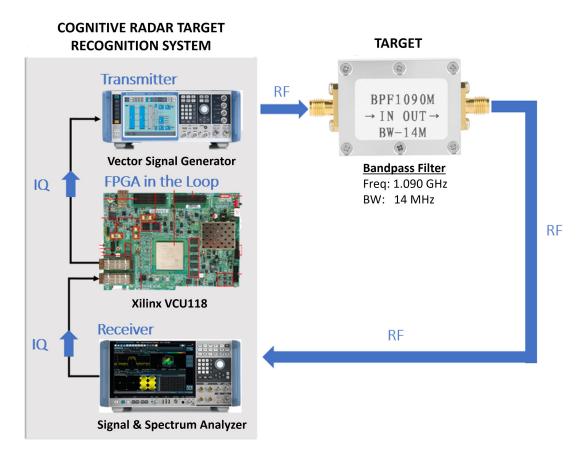

| Figure 4.1  | Closed-loop RF System Diagram of the Cognitive Radar Target<br>Recognition System Experiment. Processor: VCU118, Transmitter:<br>SMW200A, Receiver: FSW                         | 44 |

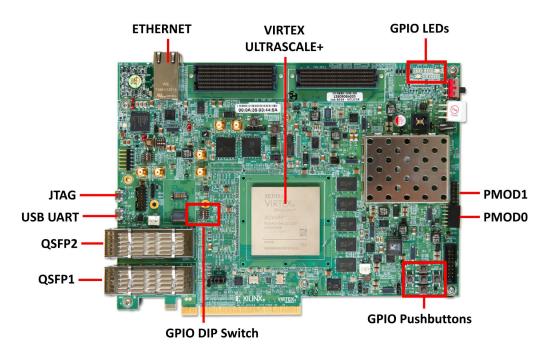

| Figure 4.2  | Xilinx VCU118 Evaluation Board Featuring the Virtex UltraScale+<br>XCVU9P-L2FLGA2104E FPGA. Adapted from [23]                                                                                      | 46 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

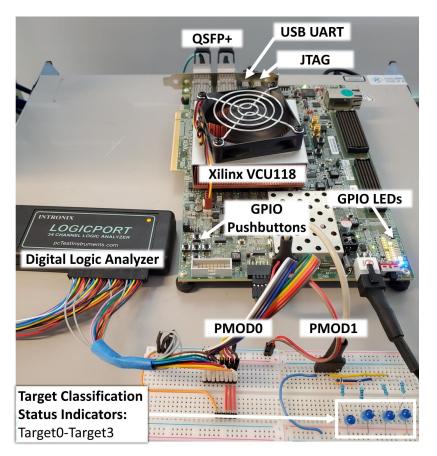

| Figure 4.3  | Cognitive Radar Target Recognition System Equipment Setup                                                                                                                                          | 47 |

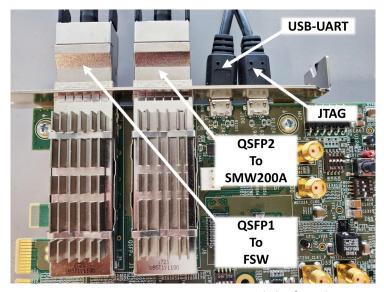

| Figure 4.4  | VCU118 QSFP+ Connections to Rohde & Schwarz Equipment and PC                                                                                                                                       | 48 |

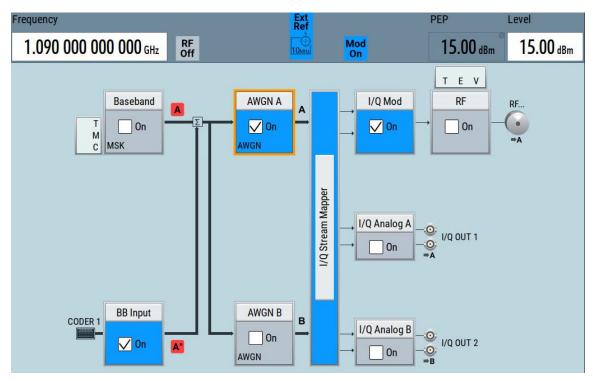

| Figure 4.5  | SMW200A Signal Flow Block Diagram Configuration: Baseband<br>High Speed Digital IQ with Optional Additive White Gaussian Noise                                                                     | 49 |

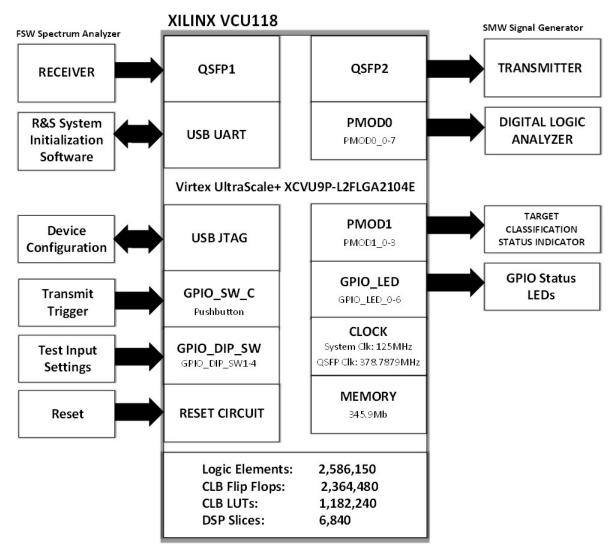

| Figure 4.6  | Xilinx VCU118 Block Diagram and Hardware System IO                                                                                                                                                 | 50 |

| Figure 4.7  | Hardware System IO Configuration                                                                                                                                                                   | 51 |

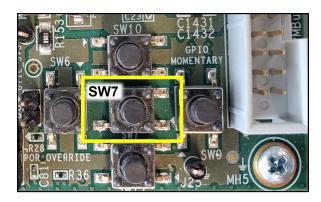

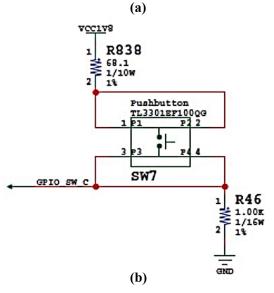

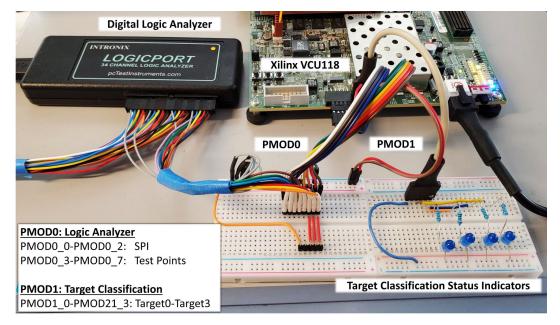

| Figure 4.8  | (a) Xilinx VCU118 Evaluation Board GPIO Momentary Pushbut-<br>ton Input, SW7: Adaptive Waveform Trigger. (b) SW7 Schematic<br>Diagram. Source [23]                                                 | 52 |

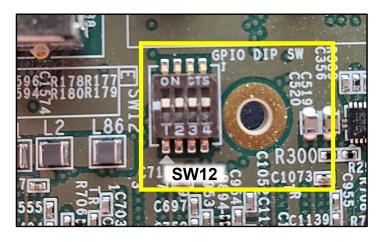

| Figure 4.9  | (a) Xilinx VCU118 Evaluation Board GPIO DIP Switch Input. (b) SW12 Schematic Diagram. Source: [23]                                                                                                 | 53 |

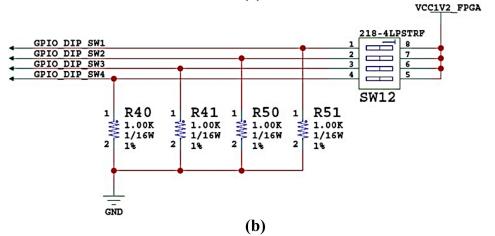

| Figure 4.10 | Xilinx VCU118 Evaluation Board GPIO Status LEDs                                                                                                                                                    | 54 |

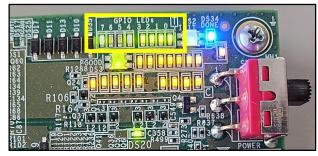

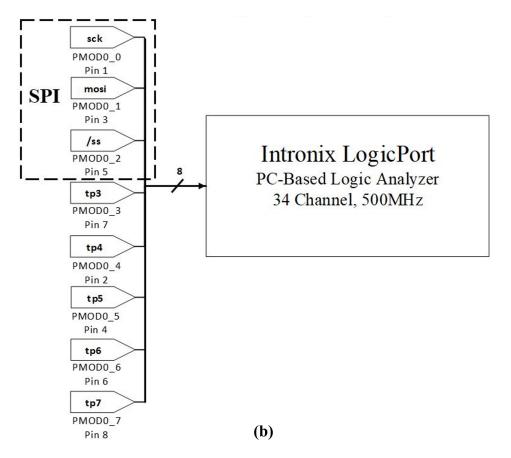

| Figure 4.11 | <ul><li>(a) Xilinx VCU118 Evaluation Board PMOD0 Right Angle Header</li><li>Female Receptacle. (b) Output Test Signals to Logic Analyzer.</li><li>Source: [23]</li></ul>                           | 55 |

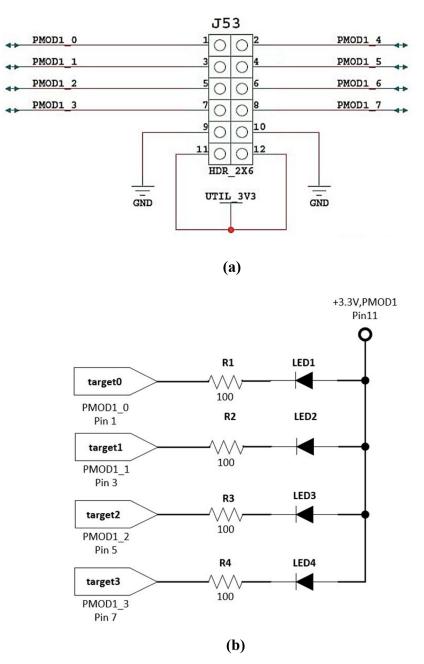

| Figure 4.12 | <ul><li>(a) Xilinx VCU118 Evaluation Board PMOD1 Male Pin Header Output Signals. (b) Target Classification Indicator LEDs. Source:</li><li>[23]</li></ul>                                          | 56 |

| Figure 4.13 | Xilinx VCU118 Evaluation Board, PMOD0 and PMOD1 Connec-<br>tions                                                                                                                                   | 57 |

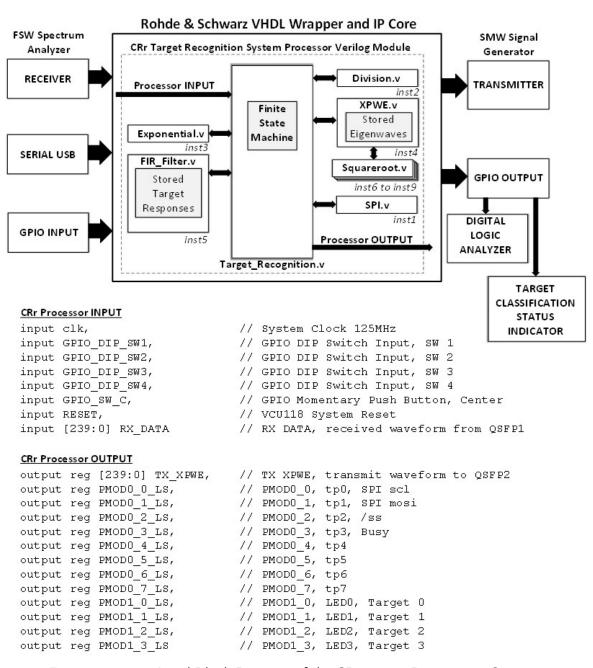

| Figure 4.14 | Top Level Block Diagram of the CRr Target Recognition System design in Verilog Instanced in a VHDL Wrapper                                                                                         | 59 |

| Figure 4.15 | CRr Finite State Machine in Verilog                                                                                                                                                                | 60 |

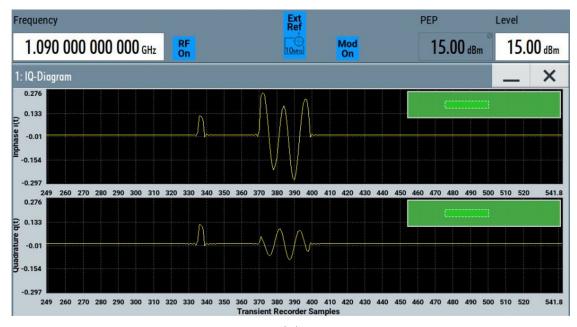

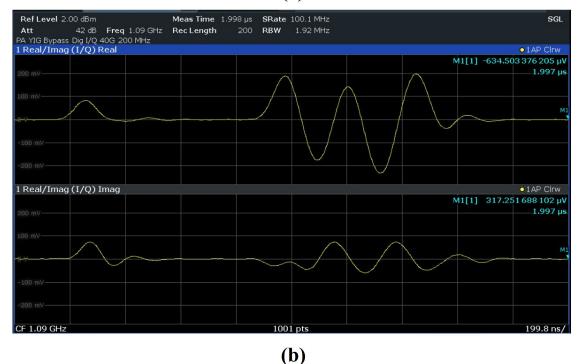

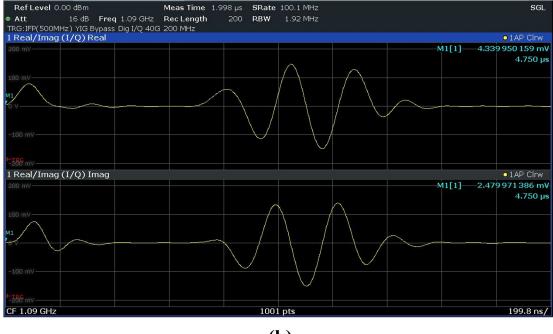

| Figure 4.16 | (a) Initial Transmitted Waveform, <b>x</b> , with Reference Pulse Transmitted by SMW200A and (b) Target Return Waveform, <b>y</b> with Reference Pulse Captured by FSW, where $ptheta[0:3] = 0.25$ | 62 |

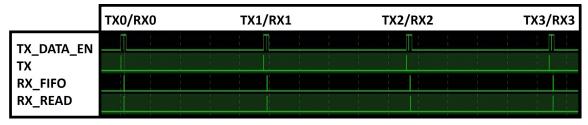

| Figure 4.17 | Timing Analysis of TX/RX HS DIG IQ Data Captured on the Digital Logic Analyzer                                                                                                                                 | 63 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

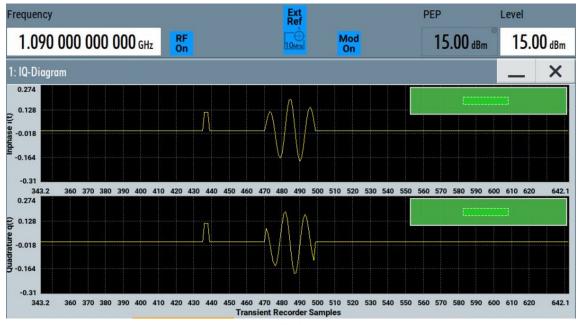

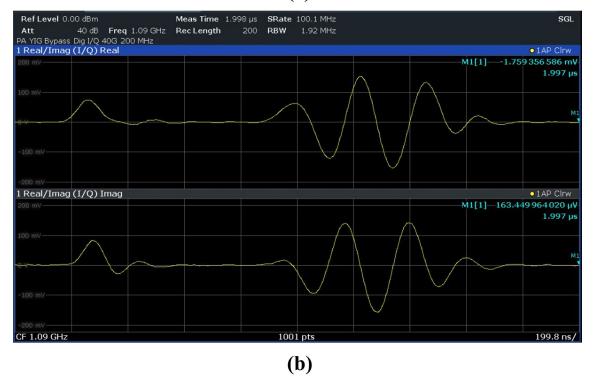

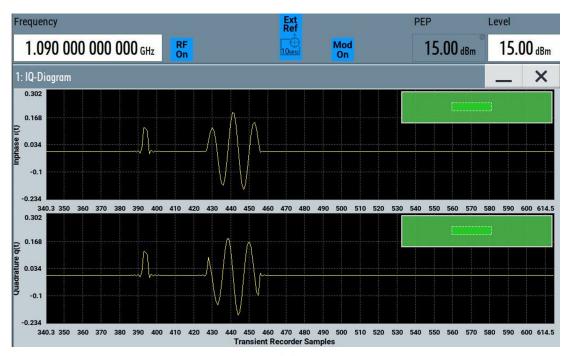

| Figure 4.18 | (a) Subsequent Adaptive Waveform, <b>x</b> , Transmitted by the SMW200A Signal Generator and (b) Target Return Waveform, <b>y</b> , Captured by the FSW Spectrum Analyzer (Bottom), where $ptheta0 = 0.9987$ . | 64 |

| Figure 4.19 | Digital Logic Analyzer Displaying the Update Probabilities (Top)<br>and <i>ptheta</i> 0 History for <i>target</i> 0 after 2 Transmit/Receive Iterations<br>(Bottom)                                            | 65 |

| Figure 4.20 | Digital Logic Analyzer Displaying 4 Adaptive Waveform HS DIG IQ Transmit and Receive Cycles                                                                                                                    | 65 |

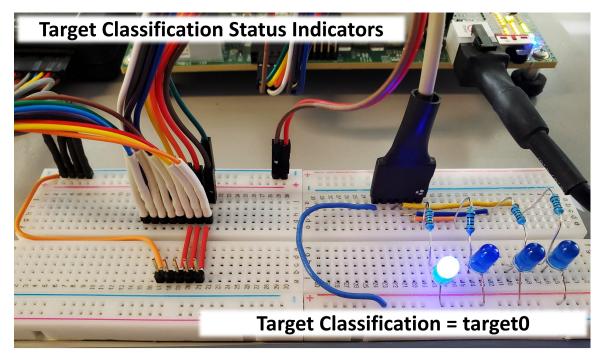

| Figure 4.21 | Target Classification Status Indicators, target0 Determined by System                                                                                                                                          | 66 |

| Figure 4.22 | Digital Logic Analyzer Data: Target Classification Decision (Top) and <i>ptheta</i> 0 History of <i>target</i> 0 Determined by System                                                                          | 66 |

| Figure 4.23 | (a) Last Adaptive Waveform, <b>x</b> , Transmitted by the SMW200A Signal Generator and (b) Target Return Signal, <b>y</b> , Captured by the FSW Spectrum Analyzer (Bottom), where $ptheta0 = 1.0$              | 67 |

# List of Tables

| Table 3.1 | Stored Target Responses | <br>31 |

|-----------|-------------------------|--------|

| Table 3.2 | Stored Eigenwaveforms . | <br>35 |

# List of Acronyms and Abbreviations

| ADC   | analog-to-digital converter               |

|-------|-------------------------------------------|

| CLB   | configurable logic block                  |

| CRr   | cognitive radar                           |

| DAC   | digital-to-analog converter               |

| DSP   | digital signal processing                 |

| EM    | electromagnetic                           |

| EMS   | electromagnetic spectrum                  |

| ES    | electronic support                        |

| EW    | electronic warfare                        |

| FIFO  | first-in, first-out                       |

| FIR   | finite impulse response                   |

| FPGA  | field-programmable gate array             |

| FSM   | finite state machine                      |

| GPIO  | General Purpose Input/Output              |

| JEMSO | Joint Electromagnetic Spectrum Operations |

| ю     | input/output                              |

| IP    | intellectual property                     |

| IQ    | in-phase/quadrature                       |

| LED   | light emitting diode                      |

.. .

| LFSR  | linear-feedback shift register                                   |

|-------|------------------------------------------------------------------|

| LUT   | look-up table                                                    |

| LVDS  | low-voltage differential signaling                               |

| MAP   | maximum a posteriori                                             |

| NATO  | North Atlantic Treaty Organization                               |

| PDF   | probability density function                                     |

| PWE   | probability of weighted energy                                   |

| QSFP+ | Quad Small Form-Factor Pluggable+                                |

| RCS   | radar cross section                                              |

| RF    | radio frequency                                                  |

| SNR   | signal-to-noise ratio                                            |

| SoC   | System-on-Chip                                                   |

| SPI   | serial peripheral interface                                      |

| TCL   | tool command language                                            |

| UART  | Universal Asynchronous Receiver/Transmitter                      |

| VHDL  | Very High-Speed Integrated Circuit Hardware Description Language |

# Acknowledgments

I would like to thank my thesis advisors, Professor Douglas Fouts and Professor Ric Romero, for their guidance, mentorship, and expertise throughout my time at the Naval Postgraduate School. The combination of their industry and academic experience provided me with the immense support required for completing a hardware intensive, applications-oriented project.

I would also like to extend my gratitude to the Electrical and Computer Engineering Laboratory Director, Mr. Robert Broadston, and Radar Lab Manager, Mr. Manuel Badiola, for their laboratory test equipment assistance and access to project resources. For all hardware applications engineering support and technical contributions, I would like to thank Mr. PB Balasubramanium of Rohde and Schwarz.

Finally to my beautiful wife and high school sweetheart, Janet, and our two bright and handsome boys, Cayden and Camren, I would like to express my deepest appreciation for their continued love, energy, and strength during this process. I could not have achieved this accomplishment without their enduring support.

# CHAPTER 1: Introduction

Joint military target identification and tracking systems require a high degree of confidence and reliability when maneuvering across the volatile electromagnetic spectrum (EMS). In Joint Publication 3-85 [1], the framework for Joint Electromagnetic Spectrum Operations (JEMSO) is established as an integrated necessity to achieve and maintain battlespace awareness within the operational environment in support of force protection, intelligence, and military objectives, as well as deconfliction and coordination efforts during peacetime operations. Specifically, electronic support (ES), a division of electronic warfare (EW), is delivered through radar system capabilities enabling target detection within the EMS "for the purpose of immediate threat recognition, targeting, planning" and execution of joint and combined military operations [1].

Challenges resulting from the increasing demand of conventional radar employment in the congested electromagnetic (EM) maneuver spaces, however, have led to the emergence of cognitive radar (CRr) research [2]. Interest in CRr systems has gained attention in modern radar development over the past 15 years [2] due to its fully adaptive, dynamic closed-loop capabilities that enable real-time decision-making within its environment through the employment of the cognitive remote sensing perception-action cycle [3]. In the recent North Atlantic Treaty Organization (NATO) technical study on CRr systems [4], the NATO Sensor Electronics Technology Task Group further validates the integration of cognitive radar sensing applications in military and peacekeeping missions as a solution to improve existing radar technology, as well as fostering new development of ES-related capabilities.

In this thesis, we expand on the CRr research developments conducted in [5]–[14] and focus on a hardware realization of a CRr target classification system and its proposed implementation into ES operations. Specifically, we incorporate the real-time adaptive matched waveform transmission technique, which is termed as probability of weighted energy (PWE), through the implementation of a high-performance field-programmable gate array (FPGA) system design.

## **1.1 Thesis Objective**

The objective of this study is to design an FPGA implementation of a CRr target recognition system utilizing the PWE adaptive waveform transmission technique developed in [5], [8], [14].

This proof-of-concept study investigates the feasibility of incorporating PWE adaptive matched waveform theory into a real-time hardware application that is accomplished in two parts. In the first part of this study, a PWE Monte Carlo model consisting of 15,000 trials is developed, synthesized, and simulated in the Xilinx Vivado [15] environment using the Verilog hardware description language. This model incorporates a previously developed PWE MATLAB simulation [16] as a benchmark that is realized into a digital logic design.

In the second part of this study, a functional digital hardware implementation of the CRr target recognition system is demonstrated with the Xilinx VCU118 Evaluation Board and incorporates the Verilog module designs developed in the PWE Monte Carlo simulation model. The VCU118, featuring the Virtex UltraScale+ high-performance FPGA, is used to accomplish CRr adaptive waveform generation, digital signal processing requirements, and target classification. The Rohde & Schwarz (R&S) SMW200A Vector Signal Generator and FSW Signal & Spectrum Analyzer function as the radar system transmitter and receiver, respectively. Together, with the custom FPGA hardware design and R&S radio frequency (RF) equipment, a hardware-in-the-loop emulation of a CRr system with automatic target recognition is presented.

## **1.2 Thesis Organization**

We first provide a conceptual background on cognitive radar systems and discuss the PWE adaptive matched waveform theory in Chapter 2. In Chapter 3, we describe the PWE Verilog-based Monte Carlo design process and summarize the Vivado simulation results. The CRr hardware implementation is then covered in Chapter 4, where we begin with a hardware and equipment overview. We later present the FPGA-based Verilog design process and functional proof-of-concept demonstration. At the end of Chapter 4, we report the target classification functionally of the CRr hardware design and experimental observations. Finally, in Chapter 5, we complete this body of work with a thesis summary, conclusion, and recommendations for future work.

# CHAPTER 2: Cognitive Radar for Target Recognition

## 2.1 Cognitive Radar Overview

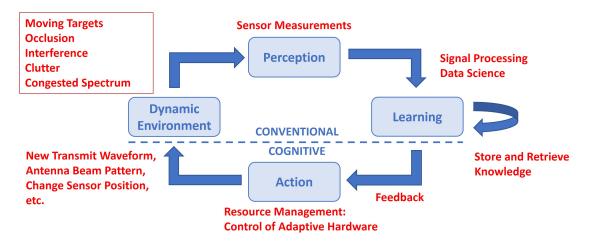

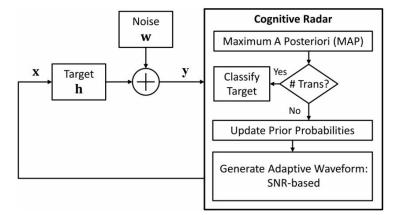

In [3], the concept of a CRr is formally defined as a radar system comprised of the following attributes: (1) intelligent signal processing that "builds on learning through integration of the radar with the surrounding environment"; (2) feedback from the receiver to facilitate intelligence; and (3) preservation of received radar return information. While conventional radar systems may feature the limited ability to adapt to its changing environment based on processed received radar returns, the CRr dynamically incorporates the transmitter into a fully adaptive, closed feedback loop perception-action cycle, allowing the radar to: a) learn from return signal interaction with the EM environment and b) update the transmitted radar signal with respect to Bayesian decision inference and prior knowledge [3], [17], [18]. Shown in Figure 2.1 is a block diagram representation of the CRr perception-action cycle from [2].

Figure 2.1. Block Diagram of the Cognitive Radar Perception-Action Cycle. Source: [2].

Fundamental components required to realize the CRr model include: (1) digital signal processing (DSP) capabilities with the real-time computational ability to measure and process environmental data; (2) digital memory to store and retrieve new observations and prior knowledge; and (3) radar transmitter/receiver hardware to support the adaptively reconfigured waveform synthesis and interaction process within the EMS [18], as depicted in Figure 2.2. Supporting hardware requirements include, but are not limited to, digital-to-analog converters (DACs) and analog-to-digital converters (ADCs) for data/RF translation, as well as other radar-based communication system components.

Figure 2.2. Basic Hardware Block Diagram of Perception-Action Cycle Model. Source: [18].

## 2.2 Probability of Weighted Energy Theory

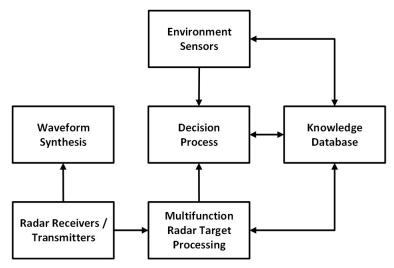

The target recognition framework introduced by Goodman et al in [17] utilizes eigen-based adaptive waveform transmissions with sequential multiple hypothesis testing to facilitate confidence-based decisions. These concepts were further developed in [5]–[14], where one of the techniques was an improved signal-to-noise ratio (SNR)-based matched waveform technique called "probability of weighted energy" (PWE). Prior work demonstrates the PWE technique to be an effective target classification method, reducing latency, minimizing computational complexity, and eliminating search algorithms used in previously developed methods [5].

Also referred to as "probability of weighted eigenwaveforms" [11], the notion of PWE is derived in [5], [8], [14] and is summarized here for convenience. PWE facilitates target recognition through a sequence of multiple radar transmissions generated from the summation of known matched optimal waveforms under SNR (eigenwaveforms),  $|X_i^{opt}(f)|^2$ , that correspond to stored target responses [5]. Each eigenwaveform is individually weighted proportionally by their respective hypothesis probability,  $P_i$ . In the frequency domain, this transmit waveform is represented as  $|X_T(f)|^2$ , which is depicted in Figure 2.3 and is

$$|X_T(f)|^2 = \sum_{i=1}^M P_i |X_i^{opt}(f)|^2.$$

(2.1)

Figure 2.3. PWE Adaptive Matched Waveform Transmission Block Diagram. Source: [5].

The initial transmission waveform, assuming equal prior probabilities, consists of eigenwaveforms equally scaled by the probabilities  $P_1 = P_2 = P_2... = P_M = 1/M$ , where M represents the total number of stored target responses. Probability updates are calculated using Bayesian principles based on the observed interaction with the interrogated target via the radar return signal. The subsequent waveform is then recalculated, generated, and then re-transmitted. This process is repeated for multiple iterations that is pre-defined in the system. Upon processing the last radar return received signal, the CRr target recognition system classifies the interrogated target based on the most likely hypothesis dictated by the last probability update through maximum a posteriori (MAP) decision [5]. The PWE CRr closed feedback loop block diagram is depicted in Figure 2.4. Assuming normalized sampling time, let  $\mathbf{x}$  represent the complex-valued adaptive transmit waveform,  $\mathbf{y}$  be the received target return signal,  $\mathbf{h}$  be the target response, and \* be the convolution operation. The target return signal with additive Gaussian noise,  $\mathbf{w}$ , is

$$\mathbf{y} = \mathbf{h} * \mathbf{x} + \mathbf{w}. \tag{2.2}$$

Figure 2.4. Cognitive Radar Closed Feedback Loop Block Diagram Using PWE. Source: [9].

From the CRr adaptive waveform generator of Figure 2.4, each optimal target eigenwaveform is derived from the autocorrelation,  $\mathbf{R}_{\mathbf{H}}$ , of the target response convolution matrix,  $\mathbf{H}$ , with respect to the known target response,  $\mathbf{h}$ . The autocorrelation is

$$\mathbf{R}_{\mathbf{H}} = \mathbf{H}^H \mathbf{H},\tag{2.3}$$

where H denotes the Hermitian operation and H is

$$\mathbf{H} = \begin{bmatrix} \mathbf{h} & 0 & 0 & 0 \\ \cdot & \mathbf{h} & 0 & 0 \\ \cdot & \cdot & \cdot & \cdot \\ \cdot & \cdot & \mathbf{h} \end{bmatrix}.$$

(2.4)

The target eigenwaveform produced from Equations 2.3 and 2.4 is represented as  $\bar{\mathbf{q}}_{max}$  [8].

Using  $\bar{\mathbf{q}}_{i,max}$ , where i = 1, 2, 3...M, corresponding to the *M* target hypotheses, the initial transmit waveform of Equation 2.1 can be expressed in the discrete time domain as

$$\mathbf{x}_{\text{pwe}} = \sum_{i=1}^{M} \sqrt{P_i} \bar{\mathbf{q}}_{i,\text{max}}.$$

(2.5)

This summation of individual eigenwaveforms is then normalized in relation to its energy,  $E_{x_{pwe}}$ . To incorporate any transmit energy,  $E_x$ , the transmit waveform becomes

$$\mathbf{x} = \sqrt{E_x} \frac{\mathbf{x}_{\text{pwe}}}{\sqrt{E_{x_{\text{pwe}}}}}.$$

(2.6)

Referring to the received target return signal,  $\mathbf{y}$ , of Figure 2.4, each individual target hypothesis,  $\mathcal{H}$ , is expressed as

$$\mathcal{H}_{1} : \mathbf{y} = \mathbf{x} * \mathbf{h}_{1} + \mathbf{w} = \mathbf{H}_{1}\mathbf{x} + \mathbf{w}$$

$$\mathcal{H}_{2} : \mathbf{y} = \mathbf{x} * \mathbf{h}_{2} + \mathbf{w} = \mathbf{H}_{2}\mathbf{x} + \mathbf{w}$$

$$\mathcal{H}_{3} : \mathbf{y} = \mathbf{x} * \mathbf{h}_{3} + \mathbf{w} = \mathbf{H}_{3}\mathbf{x} + \mathbf{w}$$

(2.7)

$$\cdots$$

$$\mathcal{H}_{M} : \mathbf{y} = \mathbf{x} * \mathbf{h}_{M} + \mathbf{w} = \mathbf{H}_{M}\mathbf{x} + \mathbf{w}.$$

Probability updates are determined from the probability density function (PDF) corresponding with previous probability calculations,  $P_{i,k}$ , which are then used to generate the subsequent transmit waveform. The probability update is given by

$$P_{i,k+1} = \beta p\left(\mathbf{y}_{k+1} | \mathcal{H}_i\right) P_{i,k}, \qquad (2.8)$$

where k represents the waveform iteration count,  $y_{k+1}$  is the most recent target return signal, and  $\beta$  ensures unit total probability [14]. Per Figure 2.4, when the last target return signal is received, target classification is determined through a MAP algorithm. In previous PWE works, 4 or more iterations have been used to perform target classification.

# CHAPTER 3: Verilog Modeling and Design Simulation

## 3.1 Verilog Model Overview

In this chapter, we build upon the PWE concepts introduced in Chapter 2. Prior to realizing the CRr target recognition system design in hardware, we develop, synthesize, and simulate a PWE Monte Carlo model in the Xilinx Vivado Design Suite using the Verilog hardware description language. This Monte Carlo simulation model, consisting of 15,000 trials, utilizes a previously developed PWE simulation implemented in MATLAB [16] as a benchmark and translates its algorithms into a digital system logic design.

In the first part of this chapter, we focus on the Verilog design parameters, high-level architecture, and finite state machine (FSM) algorithm. Individual Verilog module components are further detailed later in Section 3.2, as well as a description and derivation of the target hypothesis parameters. At the end of this chapter, we present the simulated Vivado results in Section 3.3. In this model development, we not only examine the PWE digital hardware logic design feasibility, but we also provide the Verilog building blocks for the FPGA implementation and hardware system integration, which is presented in Chapter 4.

## 3.2 Verilog Model Design Description

### 3.2.1 Performance Factors and Data Handling

Several device performance factors are considered early in this Monte Carlo Verilog model development to facilitate the ultimate hardware design implementation objective. Device performance factors include: (1) data size and memory constraints; (2) timing-related limitations and latency; (3) hardware real estate and internal routing considerations; and (4) device capabilities. Specifically, this Verilog model incorporates the Xilinx VCU118 Evaluation Board parameters in Vivado based on its hardware performance, features, and test equipment compatibility that will be further detailed in Chapter 4.

Of the performance factors listed, data size is a major design consideration, serving as a critical standard that is incorporated into all Verilog modules. One of the challenges with adapting a hardware design from a computer-generated simulation modeled in a high-level programming language, such as MATLAB, is achieving the required precision and range with respect to data size. With MATLAB, the default data type is 64-bit, double-precision floating-point values ranging from  $-2.22507 \times 10^{308}$  to  $1.79769 \times 10^{308}$  with  $2.2204 \times 10^{-16}$  accuracy [19]. In this hardware design, a 32-bit, signed fixed-point representation is selected to meet data precision requirements with the VCU118 and to interface with Rohde & Schwarz intellectual property (IP) core and proprietary data bus formats.

Using the signed 32-bit Q15.16 format [20], which is shown in the example of Figure 3.1, the sign of a generic fixed-point value, x[31:0], is represented at the most significant bit (bit 31). Bits 0 through 15 represent the fractional portion, with the implied radix point set between bits 15 and 16. The integer portion is represented in bits 16 through 30. This data format provides a range from -32,768 to approximately 32,767.999985, with 0.000015 (2<sup>-16</sup>) precision. Overflow and underflow handling is considered and incorporated throughout the design process. The appropriate scaling factors and Verilog code to generate a printed output in the Vivado Tool Command Language (TCL) Console is demonstrated at the bottom of Figure 3.1.

Scaling Factor =  $2^{-16}$

Fixed Point Representation :  $x[31:0] \times 2^{-16}$

Integer Bits, 15-bit

Fraction Bits, 16-bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Integer Bits, 15-bit

Fraction Bits, 16-bit

31

30

29

28

27

26

25

24

23

22

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Implied Radix Point

\$itor(\$signed(x)\*2.0\*\*-16.0) // Verilog Test Bench Output

Figure 3.1. Q15.16, 32-bit Signed Fixed-Point Representation in Verilog

Another data processing consideration related to hardware logic designs adapted from highlevel programming language models is the action of performing fundamental mathematical functions, such as multiplication, division, square root, and exponential expressions. Although Vivado IP cores can be used to perform such tasks, in this project, we design a set of mathematical Verilog modules from the bottom-up to control proper 32-bit Q15.16 data handling between Verilog instances to allow flexibility for design-specific functions. These Verilog modules will be discussed later in Section 3.2.4.

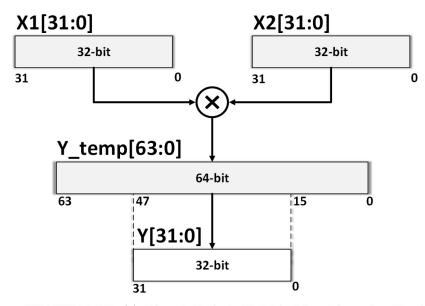

The process depicted in Figure 3.2 is performed for all 32-bit fixed-point multiplication expressions in this design. As illustrated, the product of two 32-bit values, which is generalized in this example as X1[31:0] and X2[31:0], yields a 64-bit result that is stored in a temporary register. To properly represent the product, this temporary value is shifted to the right by 16 bits and then stored into a 32-bit final product register, which is generalized here as Y[31:0]. This method provides an adequate approximation suitable for the accuracy requirements of this design. For designs requiring higher accuracy, an 8-bit shift can be performed on both the multiplicand and multiplier with rounding-error logic incorporated into the algorithm.

Y = (X1\*X2)>>16 // Fixed Point Multiplication in Verilog Figure 3.2. Q15.16, 32-bit Signed Fixed-Point Multiplication in Verilog

Note for all division functions where the divisor is constant, such as x/4 where x is a generic variable, fractional multiplication is incorporated for latency and hardware routing considerations, as well as simplicity. In such situations, fractional parameters are defined as constants in Verilog and implemented as multiplication functions, such as 0.25x. The division module, to be discussed later, uses Euclidean iterative algorithms [21], which can be costly and generally less accurate in comparison to multiplying by known fractional constants.

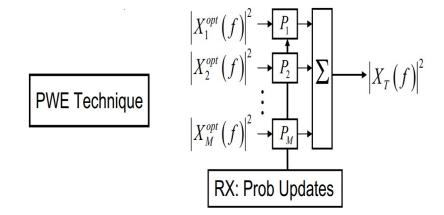

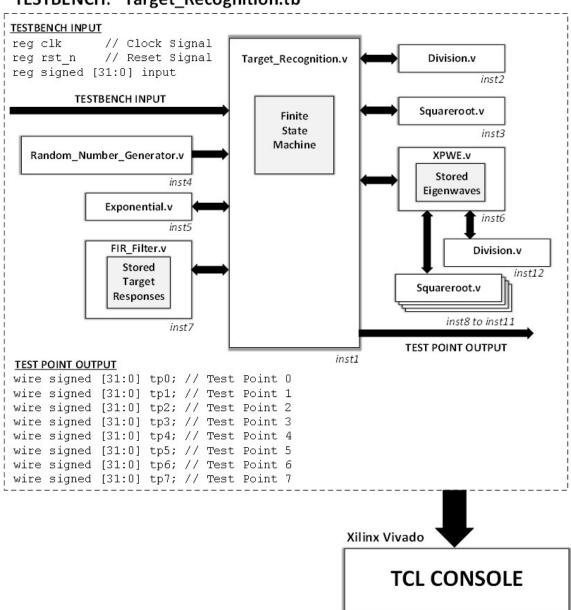

### **3.2.2** Top Level Design Description

The system diagram shown in Figure 3.3 features the top level Monte Carlo simulation Verilog module, *Target\_Recognition.v*, which is instantiated under the testbench, *Target\_Recognition.tb*. The testbench delivers the clock, reset signal, and a 32-bit test input parameter to the target recognition module. *Target\_Recognition.v* processes and generates eight 32-bit output values to the testbench that are defined as test points in Figure 3.3. All output values are translated in the testbench module and printed to the tool command language (TCL) console in Vivado for observation.

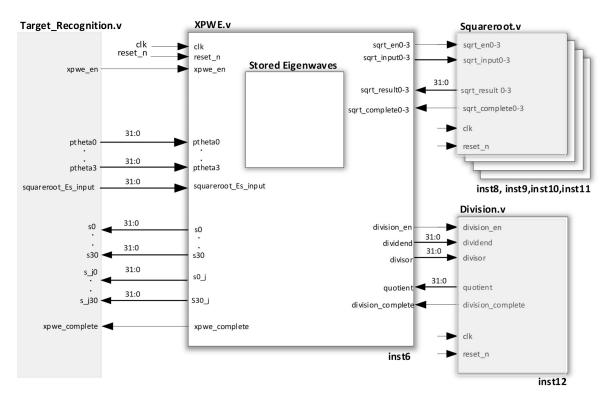

*Target\_Recognition.v* manages all behavioral logic, data processing, and input/output (IO) handling through the FSM algorithm, which is further described in Section 3.2.3. As depicted in Figure 3.3, a total of 10 Verilog modules (*inst2 – inst11*) are instantiated under *Target\_Recognition.v* to support all processing requirements. The main supporting modules featured are *Division.v* (*inst2, inst12*), *Squareroot.v* (*inst3, inst8 – inst11*), *Random\_Number\_Generator.v* (*inst4*), *Exponential.v* (*inst5*), *XPWE.v* (*inst6*), and *FIR\_Filter.v* (*inst7*). All modules are further detailed in Sections 3.2.4 through 3.2.8.

TESTBENCH: Target\_Recognition.tb

Figure 3.3. Top Level Block Diagram of PWE Target Recognition Monte Carlo Design in Verilog

As an overview, *Division.v* provides 32-bit fixed-point division and fractional results using Euclidean iterative methods [21]. *Squareroot.v* provides a 32-bit fixed-point square root approximation using an iterative algorithm involving calculating the nearest square [21]. *Random\_Number\_Generator.v* is comprised of a 3-bit linear-feedback shift register (LFSR) to generate a random number to select a target hypothesis (in a Monte Carlo trial) and twenty 19-bit LFSRs to approximate and simulate in-phase and quadrature Gaussian noise using the Central Limit Theorem. *Exponential.v* makes use of an elaborate look-up table (LUT) to quickly determine exponential functions. The PWE adaptive transmit waveform, **x**, is generated in the *XPWE.v* module, which holds the stored target hypothesis eigenwaveforms. Finally, the finite impulse response (FIR) module, *FIR\_Filter.v*, utilizes multiply-and-accumulate techniques to preform convolution functions. The four target responses are stored in this module.

#### **3.2.3** Finite State Machine Description

Shown in Figure 3.4, the FSM incorporates the PWE classification technique into a Monte Carlo procedure. The system initially generates a PWE adaptive matched waveform, **x**, which is transmitted at a set transmit energy,  $E_x$ . In a separate process, a simulated target return waveform, **y**, is generated based on a randomly selected target response at the beginning of each Monte Carlo trial (as mentioned previously). After each transmission, the probability corresponding to each target hypothesis is calculated. The subsequent adaptive waveform is generated using the updated probabilities. This process is repeated for 4 adaptive transmissions. After processing the last target return, a MAP decision determines the target classification, which is then compared with the target that was selected in the first trial (purely for the purposes of evaluating classification performance). The probability of correct classification,  $P_{cc}$ , is calculated after 1,000 Monte Carlo trials for each increasing transmit energy,  $E_x$ . The transmit energy ranges from -30 dB units up to 10 dB units and is incremented into 15 levels for a total of 15,000 trials.

| State | Description                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------|

| 0     | System Initialization: Read Transmit Energy Level input from testbench                                          |

|       | Store into register ks                                                                                          |

| 1     | FOR LOOP: ks[0:14], 15 iterations at increasing Energy Levels, E <sub>x</sub>                                   |

|       | Determine Square root of Energy Level scaling associated with ks value                                          |

| 2     | Generate Adaptive Transmit Waveform, x                                                                          |

|       | Probability update input $ptheta[0:3] = 0.25$ <b>XPWE.v</b>                                                     |

| 3     | Read Results from XPWE Module                                                                                   |

| 4     | FOR LOOP: <i>kms</i> [0:999], 1000 trials at each Energy Level, E <sub>x</sub>                                  |

|       | Assign Randomly Selected Target Random_Number_Generator.v                                                       |

| 5     | FOR LOOP: <i>iter</i> [0:3], Transmit Adaptive Waveform for 4 iterations                                        |

|       | Generate Complex-Valued Target Return: $\mathbf{s}_g = \mathbf{x}^* \mathbf{h}$ convolution <b>FIR_Filter.v</b> |

| 6     | Read Results from FIR_Filter.v, $s_g$                                                                           |

| 7     | Add Noise to Target Return Signal, $y = s_g + w$ Random_Number_Generator.v                                      |

| 8     | FOR LOOP: il = 0:3, 4 iterations for each Target Response                                                       |

|       | For each Target Response, Update: $S = x^*h_h$ convolution FIR_Filter.v                                         |

| 9     | Read Results from FIR_Filter. S                                                                                 |

| 10    | Likelihood Calculation (a): $SS = re[S'S]$                                                                      |

| 11    | Likelihood Calculation (b): $b = 2re[S'y]$                                                                      |

| 12    | Likelihood Calculation (c): re[b]-SS                                                                            |

|       | If il < 4, Return to State 8                                                                                    |

| 13    | Calculate PDF value Exponential.v                                                                               |

| 14    | Calculate Probability Update for each Target Hypothesis Division.v                                              |

| 15    | Update Transmission Waveform, x XPWE.v                                                                          |

| 16    | Read Results from XPWE Module                                                                                   |

|       | Increment <i>iter</i> counter: If <i>iter</i> < 4, Return to State 5                                            |

| 17    | Target Classification: Determine Max ptheta against target_sel                                                  |

|       | Update error counter for each mismatch                                                                          |

| 18    | Increment kms counter: If kms < 999, Return to State 4                                                          |

| 19    | Update Probability of Correct Classification, P <sub>cc</sub> Division.v                                        |

| 20    | Increment ks counter: If ks < 14, Return to State 1                                                             |

| 21    | End Monte Carlo Simulation                                                                                      |

|       |                                                                                                                 |

Figure 3.4. Finite State Machine Behavioral Algorithm for Monte Carlo Model in Verilog

The FSM in Figure 3.4 is comprised of 22 states. In State 0, following system initialization, the target recognition module receives the transmit energy value from the testbench input and stores the value in a designated register defined in Verilog as ks. The value of ks is then associated with the corresponding energy scaling value,  $\sqrt{E_x}$  from Equation 2.5, which is determined by a LUT in State 1. Note that *Squareroot.v* (*inst*3) was originally designed to perform this function, however, utilizing a LUT to represent  $\sqrt{E_x}$  constants is not only faster, but yields greater accuracy in the overall performance.

In State 2,  $\sqrt{E_x}$  and the probability update values, which are designated by  $P_i$  and ptheta[0:3] in Verilog, are sent to the *XPWE.v* module to generate the adaptive transmit waveform, **x**. Note that during this first transmission, each probability value is initialized as ptheta[0:3] = 1/4. The FSM then transitions to State 3, where it remains until *XPWE.v* returns the complex-valued transmit waveform result, **x**, which is defined in Verilog as registers s[30:0] and  $s_j[30:0]$ .

In a parallel process, *Random\_Number\_Generator.v* generates both in-phase and quadrature Gaussian noise values and a 2-bit pseudo-random number with every clock cycle. In State 4, the 2-bit output provides *target\_recognition.v* with a random target selection value, *target\_sel*, associated with a target hypothesis response, **h**. This *target\_sel* value is sent to *FIR\_Filter.v* in State 5, where the convolved result,  $\mathbf{s}_g = \mathbf{x} * \mathbf{h}$ , is stored into an array represented by 61 registers. The FSM subsequently transitions to and remains in State 6 until  $\mathbf{s}_g$  is ready. The simulated Gaussian noise from *Random\_Number\_Generator.v* is then added to  $\mathbf{s}_g$  in State 7 to generate a simulated complex-valued target return waveform,  $\mathbf{y}$ , represented in Verilog as yy[60:0] = sg[60:0] + Noise[60:0] and  $yy_j[60:0] = sg_j[60:0]$  $+ Noise_j[60:0]$ , in accordance with Equation 2.7.

For iteration count, il[0:3], the complex-valued adaptive transmit waveform, which is represented in Verilog as s[30:0] and  $s_j[30:0]$ , is convolved with each stored target response, hh[0:3][30:0], in States 8 and 9, and thus resulting in S[0:3][60:0] and  $S_j[0:3][60:0]$ . Using these outputs and the simulated complex-valued target response, the likelihood value is calculated in States 10 through 13 by evaluating each target hypothesis PDF, as depicted in Figure 3.4 and dictated in Equation 2.8 in Chapter 2. *Exponential.v* is called in State 13 to generate the likelihood value and update ptheta[0:3] in State 14.

In States 15 and 16, the adaptive waveform,  $\mathbf{x}$ , is re-calculated and transmitted via *XPWE.v* using the updated *ptheta*[0:3] values. This process is repeated in States 5 through 16 for 4 iterations, as monitored by the iteration counter, *iter*. The FSM then transitions into State 17 after the last target return waveform is processed.

In State 17, target classification is determined by the system from the final *ptheta*[0:3] values and then compared against *target\_sel* that was randomly selected in State 4. The error counter, *err*, is incremented for every incorrect target classification result. States 4 through 18 are repeated for 1000 trials before transitioning to State 19 to calculate  $P_{cc}$ , where  $P_{cc} = 1 - (err/1000)$ . States 1 through 19 are repeated until 15  $E_x$  levels are complete. State 20 increments and evaluates the  $E_x$  levels to be used, until all of the 15,000 trials are simulated. The transition into State 21 marks the conclusion of the Monte Carlo simulation.  $P_{cc}$  and target classification errors for each  $E_x$  level are printed out onto the Vivado TCL Console.

#### **3.2.4** Verilog Module Description: Mathematical Functions

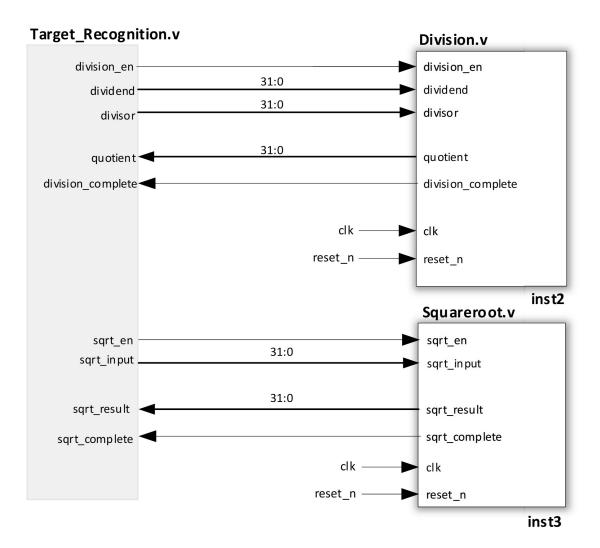

As mentioned previously in Section 3.2.1, division, square root, and exponential math functions are developed in this project to support signed 32-bit fixed-point operations while preserving Q15.16 data formatting between modules. Figures 3.5 and 3.6 provide detailed representations of the Verilog modules as schematic diagrams, which are depicted as *Division.v*, *Squareroot.v*, and *Exponential.v*.

Note that the inter-module communication standard applied throughout this project incorporates a device *enable* signal originating from the module requesting service that is accompanied by input data. A device *complete* signal and the processed output data are then returned to the originator from the service-providing module upon process completion. The requesting module sets the *enable* signal for the duration of the process and then subsequently de-asserts the *enable* signal upon acknowledging receipt of the *complete* signal. Specific to the math modules shown in Figures 3.5 and 3.6, the *enable* ports are represented as *division\_en*, *sqrt\_en*, and *exponential\_en*. The device *complete* ports are depicted as *division\_complete*, *sqrt\_complete*, and *exponential\_en*. All modules operate with respect to the rising edge of the clock input.

Figure 3.5. Schematic Diagram of Division and Square Root Verilog Modules

Figure 3.6. Exponential Verilog Module Schematic Diagram

Shown at the top right portion of Figure 3.5, the *division.v* module receives *dividend* and *divisor* input values as signed 32-bit data and outputs a signed 32-bit *quotient* up to three decimal places. The division procedure incorporates Euclidean iterative processes to approximate integer and fractional calculations [21]. The division module returns *quotient* = 0 for all cases where either the *dividend* = 0 or the fraction is less than 0.001. If the *divisor* = 0 or is less than or equal to  $3.0518 \times 10^{-5}$ , the division module returns the maximum Q15.16 system value, approximately 32,767.999985, to represent infinity. This module is primarily used to calculate probability updates and *XPWE.v* scaling.

In the square root process, shown at the bottom right of Figure 3.5, a simple counter and iterative multiplication approach are used to estimate the square root of the data input received,  $sqrt\_input$ , by calculating the nearest square [21]. As the iteration counter, k, increments, the square of k, denoted as  $k\_product$ , is calculated and compared to the input value. The scaled resulting output,  $sqrt\_result$ , is generated if  $k\_product$  is greater than or equal to the input. Module inputs less than or equal to zero are designed to return a zero value, as Squareroot.v does not support calculating imaginary outputs. This function is incorporated in XPWE.v for calculating the probability update scaling, per Equation 2.5.

The square root module outputs an approximation, accepting inputs up to 31-bits where each k count used to determine the nearest square rounds to increments of  $2^{-16}$ . The average percent error is approximately 5%, which of course should be dictated by practical system requirements. We deem this error acceptable in this work. For higher value inputs, such as  $\sqrt{10}$ , errors are observed to be approximately 0.06%, while smaller input values, such as  $\sqrt{0.001}$ , yield approximately 11.25% error. Although the algorithm is simple to implement, the associated latency costs accumulated is a drawback. Future work requiring greater precision at increased speed can incorporate algorithms, such as the "Babylonian Method." This would require designing a more precise division algorithm.

As illustrated in the schematic of Figure 3.6, *exponential.v* receives a signed 32-bit input, *exponential\_input* and delivers the 32-bit output, *exponential\_result*. The output is generalized by the function  $e^x$ , where the variable x is again used to describe a generic input value. This method uses two sets of LUTs to handle positive and negative input values that are 665 and 709 elements wide, respectively. A MATLAB algorithm was developed offline to determine required values stored in the LUTs. Because of the risk of data overflow or underflow related to signed 32-bit ranges, input values  $x \ge 10.39063$  yield output  $e^x = 32,553.00621$ . For values  $x \le -11.078$ , the module outputs  $1.54465 \times 10^{-5}$ . These ranges and approximations are deemed acceptable for the performance in this design application, which typically results in less than 1% error. The exponential module is used to calculate the likelihood value in probability update calculations, as shown in Equation 2.8.

Despite the speed, simplicity, and acceptable accuracy of incorporating a LUT method, cost considerations related to the circuitry and/or memory expended may be a factor for more complex designs. To free up register usage, simple case statements are utilized to develop the LUTs. For future work, it is recommended to implement the "Coordinate Rotation Digital Computer" (CORDIC) algorithm for increased performance, accuracy, and design efficiency [21].

#### 3.2.5 Verilog Module Description: Random Number Generator

The pseudo-random number generator is depicted in the schematic diagram shown in Figure 3.7. Two different LFSR designs are implemented to generate the randomly selected target and complex-valued noise that were previously described in Section 3.2.3. *Random\_Number\_Generator.v* runs independently from the FSM and generates a 2-bit pseudo-random output, *random*, and two 32-bit pseudo-Gaussian outputs, *noise* and *noise\_j*, at each rising clock edge input.

Figure 3.7. Pseudo-Random Number Generator Verilog Module Schematic

Figure 3.8 illustrates a simple 3-bit LFSR design inspired by [22], which generates a pseudo-random counting sequence by feeding bits 0 and 2 of the 3-bit input register into an Exclusive OR gate that is routed to bit 1 of the 3-bit output register. As shown in the diagram, bits 2 and 1 of the input register are assigned directly to bits 2 and 0 of the 3-bit output, respectively. A second Exclusive OR gate with inputs originating from bits 2 and 0 of the 3-bit output register is then routed to bit 0 of the 2-bit output register. The output of the first Exclusive OR gate from the 3-bit input register provides the assignment for bit 1 of the 2-bit output register.

Upon system initialization, the 3-bit input register is loaded with a seeded value and the counter updates with respect to the clock. The 2-bit pseudo-random register is routed to the *Random\_Number\_Generator.v* output, *random*, which is fed directly into the target recognition top-level model. This output is only read, however, during State 4 of the FSM shown in Figure 3.4 and detailed in Section 3.2.3.

Figure 3.8. 2-bit and 3-bit Pseudo-Random Number Generator, Verilog Schematic Representation