# A NEW DIALECT OF SOFL: SYNTAX, FORMAL SEMANTICS, AND TOOL SUPPORT

by

Johan Sarel van der Berg

Submitted in partial fulfilment of the requirements for the degree

Master of Science (Computer Science)

in the

Department of Electrical, Electronic and Computer Engineering

Faculty of Engineering, Built Environment and Information Technology

University of Pretoria, Pretoria

December 2018

# **Summary**

# A NEW DIALECT OF SOFL: SYNTAX, FORMAL SEMANTICS, AND TOOL SUPPORT

by

### Johan Sarel van der Berg

| Supervisor: | Prof. S. Gruner                                                                |

|-------------|--------------------------------------------------------------------------------|

| Department: | Faculty of Engineering, Built Environment and Information Technology           |

| University: | University of Pretoria                                                         |

| Degree:     | Master of Science (Computer Science)                                           |

| Keywords:   | Process algebra, Formal modeling, Formal semantics, mCRL2, Restricted dialect, |

|             | SMT-Solver, Structured Object Orientated Formal Language, SOFL, Tool support,  |

|             | Z3                                                                             |

Structured Object Orientated Formal Language (SOFL) is a formal method design methodology that combines data flows diagrams and predicates in order to describe processes that can be refined. This methodology creates a very versatile method of describing a system, which system properties can be proven rigorously. Data flows are grouped by ports that define from which data flows data can be consumed or on which flows data can be generated. For predicates, Logic of Partial Functions (LFP) are used; and an undefined element that is also used to indicate if a data flows do not contain any data.

Over time SOFL "evolved organically" and a number of features were added: usability was the main consideration for a feature being added. For a formal language to be useful there must be no uncertainty of a specific design's meaning. With SOFL, there is a possible contradiction between the requirement that a process's precondition must be true when the process fire, and the fire rules. This contradiction is due to the use of LPF.

Semantics (the meaning) of SOFL was not always updated to keep track of the changes made to SOFL which resulted in an outdated and incomplete semantic. The incompleteness of the semantics is a significant factor motivating the work done in this dissertation.

In this dissertation, a dialect of SOFL is created to define a semantic. Not all the elements of SOFL are added in order that a simpler semantic can be defined. Elements that were removed include:

- LPF,

- Classes, and

- Non-deterministic broadcast nodes.

Semantics of the dialect is created by a two-step process: firstly, an intuitive understanding of the dialect is created, and secondly, both static and dynamic semantics are defined by means of translations.

A translation is a mapping from the dialect to a formal language that describes a certain aspect of the dialect. Static semantics defines the meaning of the elements that are "fixed" in their state: SMT-LIB is used as the target language to describe the static semantics of the dialect. Dynamic semantics describes how an element in a design changes over time: the process algebra mCRL2 is used as the formal language which describes the dynamic behaviour of the dialect.

The SMT-Solver Z3 and tools included in mCLR2 are used to analyse the translation of the dialect. Use of these tools allows properties that are necessary for a design to have a well defined meaning, to be proven. Properties that can be proven include: a process can fire, a process can fire an infinite number of times, and a predicate that described a property.

An Eclipse plug-in is created so that translation is not required to be done manually. After a design is translated the tools Z3 and mCRL2 are run using script files and the results of the analysis are displayed on the screen. The desired properties could be proven but for a moderate size design, but as the size of the design increased the analysis of the translation could not be completed due to computational problem. Usability of the tool can be improved by not only using a textual representation of a design, but also visual representations as in SOFL.

As a result, properties that are necessary for a design to have a well-defined meaning, can be proven using these tools.

# Acknowledgement

During the course of the dissertation there were several discussions with the following experts that were especially helpful: Stefan Gruner (Supervisor), Shaoying Liu, Markus Roggenbach, Jan Friso Groote, Stefan Blom, Jaco v.d. Pol, Christian Dietrich and the anonymous reviewers that provided their insightful comments on my and Prof Guner's paper draft for SOFL+MSVL'18 workshop. The comments received after the examination from the external reviewers were also valuable.

# Contents

| Li | ist of | Figures          |                                 | viii   |

|----|--------|------------------|---------------------------------|--------|

| Li | ist of | Tables           |                                 | ix     |

| 1  | Intr   | oduction         |                                 | 1      |

|    | 1.1    | History of SOFL  |                                 | <br>1  |

|    |        | 1.1.1 Origins    |                                 | <br>1  |

|    |        | 1.1.2 Structure  | ed design                       | <br>2  |

|    |        |                  | Orientation                     | 2      |

|    |        | 1.1.4 Parallelis | sm and Concurrency              | <br>2  |

|    |        |                  | ion                             | 3      |

|    |        | 1.1.6 Semantic   | es                              | <br>3  |

|    | 1.2    | Problem Statem   | ent                             | <br>4  |

|    | 1.3    | Method           |                                 | <br>5  |

|    | 1.4    |                  |                                 | 5      |

|    | 1.5    | Modification     |                                 | <br>6  |

|    |        | 1.5.1 Refineme   | ent and Hierarchical Structures | <br>6  |

|    |        | 1.5.2 Logic Us   | age in Specification            | <br>7  |

|    |        | 1.5.3 Data Flo   | ows Diagrams                    | <br>9  |

|    |        | 1.5.4 Data Ty    | pes                             | <br>10 |

|    | 1.6    | Associated publi | -<br>ication                    | <br>10 |

|    | 1.7    | Outline          |                                 | <br>10 |

| 2  | Rela   | ated Work        |                                 | 12     |

|    | 2.1    |                  | v                               | <br>12 |

|    |        | 0                | es                              | 13     |

|    |        | -                |                                 | 13     |

|    |        |                  | ts                              | 14     |

|    | 2.2    |                  | rification                      | 14     |

|    |        |                  | es                              | 15     |

|    |        | -                |                                 | 15     |

|    |        |                  | ıts                             | 15     |

|    | 2.3    |                  |                                 | 15     |

|    |        | 2.3.1 Static Se  |                                 | 15     |

|    |        | 2.3.2 Dynamic    | e Semantics                     | 16     |

|    |        |                  | f Refinement                    | 16     |

|   |              | 2.3.4   | Comments                            |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 17 |

|---|--------------|---------|-------------------------------------|---|-----|---|---|---|-------|---|---|---|---|---|---|---|---|----|

|   | 2.4          | Summ    | ary                                 | • |     |   |   |   |       |   |   |   |   |   |   |   |   | 18 |

| 3 | Des          | criptio | n of SOFL Dialect                   |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 19 |

|   | 3.1          | Syntax  | ζ                                   |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 19 |

|   |              | 3.1.1   | Module                              |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 19 |

|   |              | 3.1.2   | Behaviour                           |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 20 |

|   |              | 3.1.3   | Processes                           |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 25 |

|   |              | 3.1.4   | Expression and Function             |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 26 |

|   |              | 3.1.5   | Syntax Differences                  |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 26 |

|   | 3.2          | Semi-I  | Formal Semantics                    |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 27 |

|   |              | 3.2.1   | Program Graph                       |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 28 |

|   |              | 3.2.2   | Predicate Transforms                |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 30 |

|   |              | 3.2.3   | Refinement                          |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 35 |

|   |              | 3.2.4   | Action Systems                      |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 38 |

|   | 3.3          |         | ation                               |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 41 |

|   | 0.0          | VCIIIC  | auton                               | • | •   | • | • | • | <br>• | • | • | • | • | • | • | • | • | 71 |

| 4 |              | tic Sen |                                     |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 43 |

|   | 4.1          | Type (  | Checking                            | • |     |   |   | • |       |   | • |   |   |   |   | • |   | 43 |

|   |              | 4.1.1   | Basic Types                         |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 43 |

|   |              | 4.1.2   | Data Flow Types                     |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 43 |

|   | 4.2          |         | and Variable Definitions            |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 45 |

|   | 4.3          | Motiva  | ation for Use of SMT-Solver         |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 46 |

|   | 4.4          | SMT-I   | $LIB Usage \dots \dots \dots \dots$ |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 47 |

|   | 4.5          | Transl  | ations                              |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 49 |

|   |              | 4.5.1   | Refinement                          |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 49 |

|   |              | 4.5.2   | Invariants and Initialisation .     |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 52 |

|   |              | 4.5.3   | Node State Space Transition .       |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 53 |

|   |              | 4.5.4   | Execution Path Approximation        |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 56 |

| 5 | Dyr          | amic 9  | Semantics                           |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 60 |

| J | •            | Firing  |                                     |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 60 |

|   | $5.1 \\ 5.2$ | 0       |                                     | • | • • |   |   | • | <br>• |   | • | • | • | • | • | • | • | 62 |

|   |              |         | ation for Process Algebra           |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 64 |

|   | 5.3          |         | 2 usage                             |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 68 |

|   | 5.4          |         | s Algebra Description               |   |     |   |   |   |       |   |   |   |   |   |   |   |   |    |

|   | 5.5          |         | f Action System                     |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 72 |

|   | 5.6          |         | Logic                               |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 75 |

|   |              | 5.6.1   | mu-Calculus formulæ                 |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 77 |

|   |              | 5.6.2   | Property Formulæ                    |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 78 |

|   | 5.7          | Analys  | sis using mCRL2                     | • |     |   |   | • |       |   | ٠ | • | • | • |   | • | • | 79 |

| 6 | Dev          | eloped  | Tool and Evaluation                 |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 83 |

|   | 6.1          | _       | oped Tool                           |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 83 |

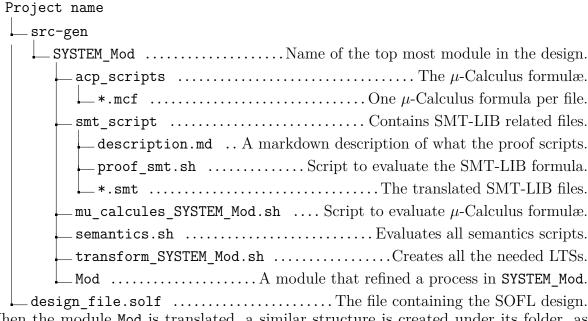

|   |              | 6.1.1   | Workspace                           |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 84 |

|   |              | 6.1.2   | Xtext Parsing                       |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 85 |

|   |              | 6.1.3   | Xtext Semantics Verification.       |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 85 |

|   |              | 6.1.4   | Translation Generation              |   |     |   |   |   |       |   |   |   |   |   |   |   |   | 86 |

|              |       | 6.1.5 Final Analysis Step       |

|--------------|-------|---------------------------------|

|              | 6.2   | Examples                        |

|              |       | 6.2.1 Small Example             |

|              |       | 6.2.2 Large Example             |

|              |       | 6.2.3 Multi-port Example        |

|              |       | 6.2.4 Producer Delivery Example |

|              | 6.3   | Time Analysis                   |

|              | 6.4   | Correctness of Tool             |

| 7            | Futi  | are Work and Discussion 98      |

|              | 7.1   | User Experience                 |

|              | 7.2   | Language usability              |

|              | 7.3   | Correctness of Tool             |

|              | 7.4   | Specifying Properties           |

|              | 7.5   | Semantics                       |

|              | 7.6   | Thoughts on SOFL                |

|              |       | 7.6.1 Non-determinism           |

|              |       | 7.6.2 Classes and Data Types    |

|              |       | 7.6.3 Semantics                 |

|              | 7.7   | Conclusion                      |

| Bi           | bliog | raphy 103                       |

| $\mathbf{A}$ | Gra   | mmar 109                        |

|              | A.1   | Module and CDFD Syntax          |

|              | A.2   | Behaviour                       |

|              | A.3   | Process and Port Syntax         |

|              | A.4   | Type Syntax                     |

|              | A.5   | Expression and Function Syntax  |

| В            | Exa   | mple Specification 116          |

|              | B.1   | Small Example                   |

|              |       | B.1.1 Specifications            |

|              |       | B.1.2 mCRL2 Description         |

|              |       | B.1.3 Results                   |

|              | B.2   | Multi-port Example              |

|              | В 3   | Producer 130                    |

# List of Figures

| 1.1  | SOFL design with deadlock                                                |

|------|--------------------------------------------------------------------------|

| 2.1  | Related work                                                             |

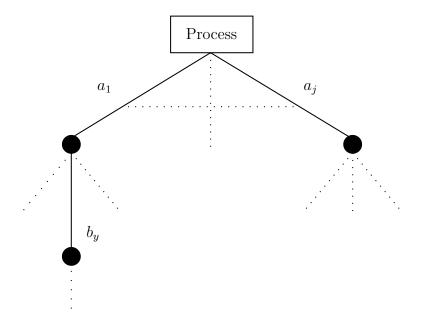

| 2.2  | A task review tree of an expression                                      |

| 3.1  | Example of a CDFD                                                        |

| 3.2  | A conditional structure representation                                   |

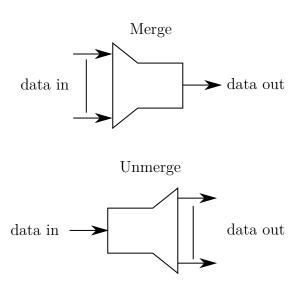

| 3.3  | Merging and separating structure representation                          |

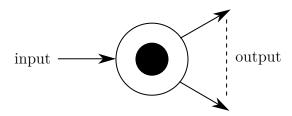

| 3.4  | A broadcast structure representation                                     |

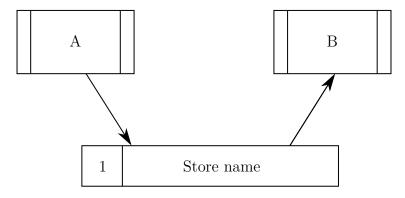

| 3.5  | A graphical representation of a data store                               |

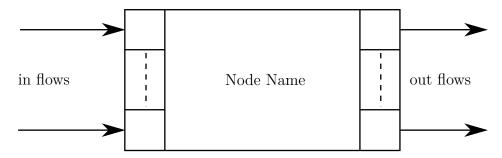

| 3.6  | A graphical representation of a process                                  |

| 3.7  | Example of program diagram                                               |

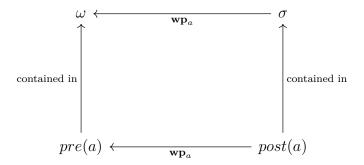

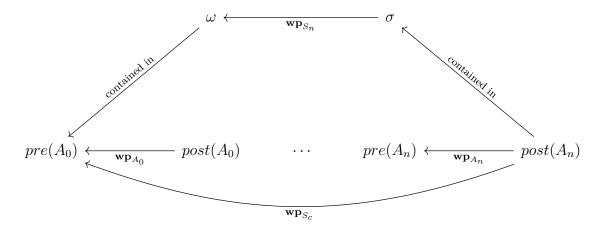

| 3.8  | Predicate transform diagram                                              |

| 3.9  | Predicate transform diagram and "execution" paths                        |

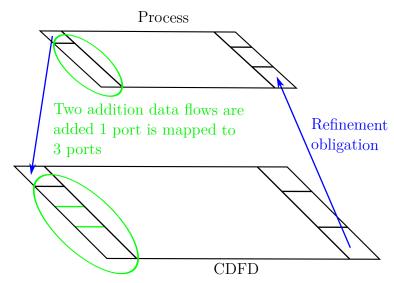

| 3.10 | Process refined by CDFD                                                  |

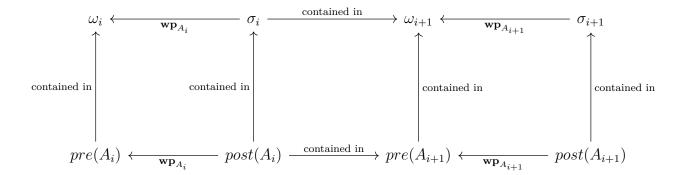

| 3.11 | Predicate transform diagram during refinement                            |

| 3.12 | CDFD verification order                                                  |

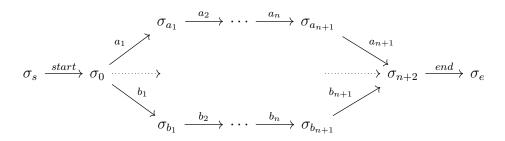

| 4.1  | The pre image of an action $a_i$                                         |

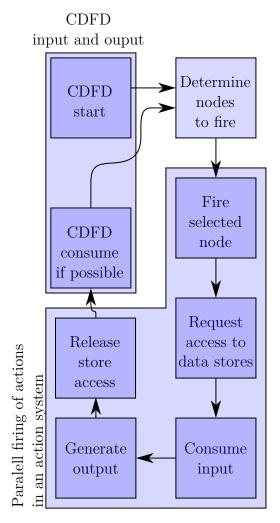

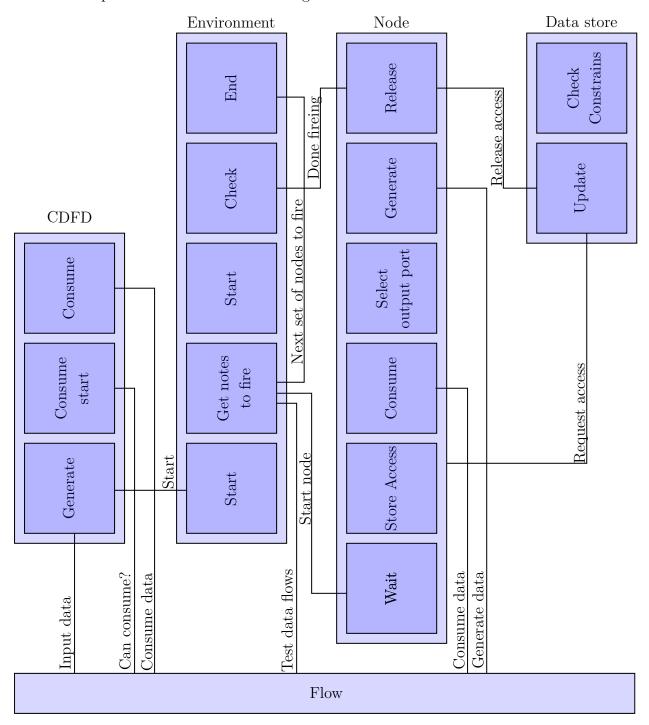

| 5.1  | Event order in mCRL2 description                                         |

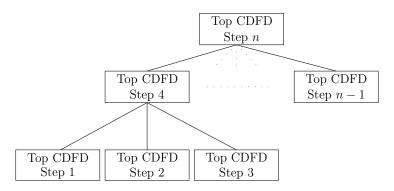

| 5.2  | Tree of behaviours                                                       |

| 5.3  | Tree of process algebra                                                  |

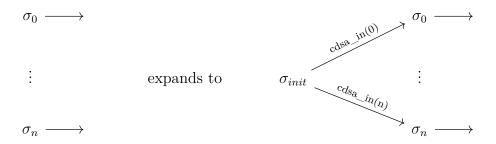

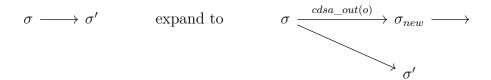

| 5.4  | ACP processes used to specify a CDFD                                     |

| 5.5  | Small example's LTS showing a CDFD's input/output 81                     |

| 5.6  | Small example's LTS showing data store access and nodes that fire 82     |

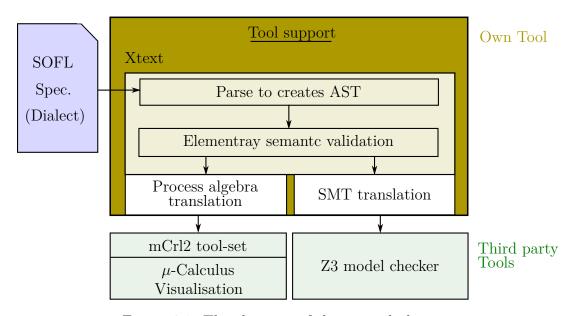

| 6.1  | The elements of the created plug-in                                      |

| 6.2  | Editor for the syntactic and semantic analysis of SOFL specifications 87 |

| 6.3  | CDFD of small example                                                    |

| 6.4  | CDFD of large example                                                    |

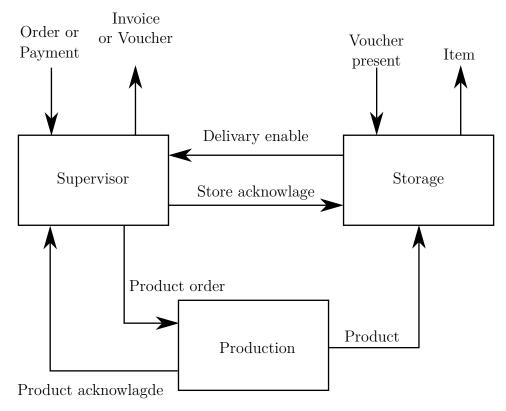

| 6.5  | State transition diagram of a delivery system                            |

| 6.6  | CDFD of producer example                                                 |

# List of Tables

| 1.1 | Operation tables for LPF                           | 8 |

|-----|----------------------------------------------------|---|

|     | Description of actions used in the ACP description |   |

|     | Analysis of SMT-LIB results                        |   |

# Chapter 1

# Introduction

Design of a system is one of the first steps before a system can be implemented, and assurance that a design is correct is an important aspect of a good design. A design language is used to assist in designing a system. A "good" design language will provide assistance by only allowing designs that have a well-defined semantics.

Structured Object Orientated Formal Language (SOFL) is a formal method design methodology that provides limited assistance. Throughout this dissertation the description given in [46] will be used as defining the SOFL "standard". Familiarity with SOFL will be assumed. This dissertation will focus on a dialect of SOFL and the semantics of the dialect.

# 1.1 History of SOFL

SOFL has a long history and "evolved organically" as new features were added. This section gives an overview of the development of SOFL.

### 1.1.1 Origins

The foundation of SOFL is rooted in Formal Requirement Specification Method (FRSM) [40,41] which provided the basis of data flow diagrams and processes. FRSM is a structured system analysis method based on DeMarco data flow diagrams using data processing units called processes and structures – both are also called nodes. These are used to control the flow of data in the diagrams (like conditional structures). Nodes are related to transition in Petri-Nets [31] and have the same properties in that only some input data can be used to produce output on some of its output data flows. In FRSM and SOFL these groupings of data flows are called ports, and each node has a set of input and output ports.

A formal methods element is added for each process by defining the pre and post conditions, and allowing a process to be refined (decomposed) using a Condition Decision Flow Diagram (CDFD). The predicates are defined using the notation of the Vienna Development Method (VDM) [32], which allows the use of undefined elements that are used when a data flows contains no data and a sub-expression cannot be evaluated.

#### 1.1.2 Structured design

A top-down approach to designing systems and applying SOFL in the design was considered in [47] and used in the phase of SOFL where the client is engaged to identify the requirements of the system. Moving from the top to the bottom, a hierarchical structure is created using CDFD, which adds addition information at each level. Each level needs to be defined with enough abstraction so that lower levels can be adapted to the solution without needing too many changes to the levels above. The lowest level is much more formal and the focus is on how to perform the needed actions instead of defining the functionality that is required from the system.

Whenever the hierarchy focuses on how to perform the needed actions, the approach is called a scenario-based method and a bottom-up approach is taken. This approach is usually much more formal since each node used in a CDFD is already defined and the requirements of each node need to be satisfied whenever the nodes are used.

A tool was also developed in [47] as an aid in using both top-down and bottom-up design processes. As an example of how to implement these ideas, a train ticket purchasing system was considered.

#### 1.1.3 Object-Orientation

In [51] an approach to combining Unified Modeling Language (UML)<sup>1</sup> classes into SOFL is considered by viewing each SOFL process as an instance of a class. In order to determine how useful this integration is, top-down and bottom-up design strategies were considered. It was found that integration did not solve all the problems of a conventional object-oriented design.

The use of template classes as a data type was introduced in [52] and new firing rules are put forward. The new execution rules are simplified by only requiring that all input flows contain data of a node, for the node to be enabled. This is different from the firing rules defined in [46] where the requirement is for input data flows connected to the same port. The parallelism of general data flow diagrams [17] was also made explicit by allowing more than one process to execute at the same time. This parallelism requires that data stores are accessed so that the value they store remains consistent, read/write mutual exclusion.

### 1.1.4 Parallelism and Concurrency

Data flow diagrams define implicit parallelism [17] by allowing different computational units to consume data (when all the data needed to perform the computation is available) and execute the nodes that consume data in parallel. A CDFD allows processes to be implemented on different computational units. This was formalised for SOFL in [14]. By explicitly indicating the concurrency in a design, the implementer is given additional guidance when an implementation is created from the design.

Regions were defined for a CDFD in order to group processes together to indicate that their "execution" is independent of the other processes in the same CDFD. Total

<sup>&</sup>lt;sup>1</sup>http://www.uml.org/

independence is not required since, in addition to data flows, message passing is defined which allows processes in different regions to communicate.

#### 1.1.5 Verification

Specification-Based Testing (SBT) [62,63] is where data values are created that satisfy a specification and those values are used to verify that an implementation functions correctly. For SOFL, SBT generated data is used to perform a "spot check" simulation in order to determine if a specification is correct.

Generation of data for a SOFL design uses a predicate based method [55], Functional Scenario (FS) [36], or a combination of the two methods. A predicate based approach is where the structure of predicate is used to decompose into sub-expressions. The "intended" input data values are determined so that different grouping of data values satisfy the different sub-expressions. The idea is that the generated data will test functionality captured by the predicates of a specification during simulation. FS is where processes in a CDFD are grouped together and the input and output values of these groupings are analysed. The data values, used as intermediate values between the processes, are not considered. This approach gives abstractions of processes used in CDFD which are easier to verify than the complete CDFD.

Simulations used to "execute" a specification that are based on data values that satisfy input and output predicates, are given in [42]. An improvement [38] that uses a visual approach to show the simulations uses Message Sequence Chart (MSC) [29] sequential diagram and FS to generate data used in the simulation.

Proving properties that are a logical consequence of a design makes use of Review Task Tree (RTT) [45]. RTT is a visual representation of a predicate that gives a tree of the expression structure. This is used to assist in proving the property expressed by the predicate. This technique was applied to an ATM example [43] and tool support was developed in [39].

#### 1.1.6 Semantics

Semantics define the meaning of the specification language's syntax. Semantics is usually defined very formally by using precisely defined concepts and a logical framework. Usually semantics is divided into two parts; static semantics is used to define elements that do not change, and dynamic semantics is used to define how elements change over time. Static [19, 20] and dynamic [30] semantics of SOFL are defined using Objective-Z and First Order Logic (FOL), respectively. Other work done on semantics of SOFL is [48], where the semantics of pre/post condition are revisited. In this case, each refinement step is required to be a valid program step, thereby adding an additional constrain on what defines a valid refinement.

A simplification of SOFL was considered in [25,26,75] and called Predicate Data Flow Diagram (PDFD) where each process is allowed to have only one input and output port. This semantics is not directly applicable to SOFL but gives a "gentle" introduction to similar elements used in SOFL.

#### 1.2 Problem Statement

Structured Object Orientated Formal Language (SOFL) "evolved organically" over the years since 1995 [57]. The semantics was not updated with every change made to SOFL. If a semantic was given, it was usually not integrated with existing semantics and it was discussed separately from previous semantics. Having one semantics that describes all aspects using the same "language", helps to understand the semantics as well as to identify elements that need to be improved.

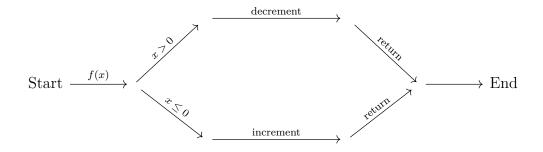

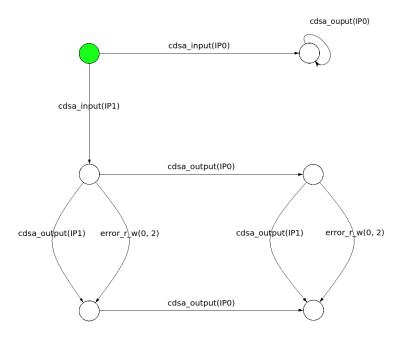

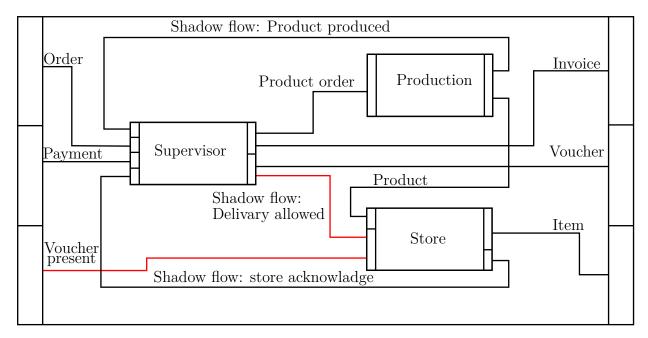

Figure 1.1: A valid design in SOFL design that deadlocks intermediately

The verification of specifications is not a trivial task, therefore, considerable work was done before it could be determined if a SOFL design was valid. A deadlock-free design is an important property of a design, and Figure 1.1 shows a CDFD where the process is immediately in a deadlock state. This is not a valid design because it does not satisfy [46, Def 30] since the design cannot produce any output, and the amount of work needed to verify increases exponentially as the size of the design increases. Currently only simulations of SBT are defined to verify properties of a SOFL specification, however, more formal methods will provide more confidence in a design.

This study aims to provide a semantic for a dialect of SOFL and define how a specification is verified using this semantic. Part of the aim will be to determine how effective the verification process function is. The goals are summarised as follows:

- 1. Obtain a dialect of SOFL that is minimal for defining the semantics.

- 2. Create a semantics for the dialect of SOFL which satisfy the following properties:

- (a) A semi-formal unified view exists for both static and dynamic semantics.

- (b) A static semantics of the dialect.

- (c) A dynamic semantics of the dialect.

3. Decrease the workload, or obtain more information with the same workload, as designers already have a large workload solving the formulæ needed to prove a design is valid.

#### 1.3 Method

During the research, areas of interest were identified where certain techniques were applied. The areas and the techniques are described below:

- **Design language.** A dialect is created that is based on SOFL by removal of elements or modifications. The purpose of these changes is to define a semantics, therefore reasons related to the semantics are used.

- **Approximation of semantics.** For the semantics, created approximations are used. The reason for using approximations is that not all the information is available<sup>2</sup> when the specific type of semantics is described, and considering complete state information will result in a scenario that is not always computable during analysis.

- **Unified view.** A general idea of the meaning of a specification is needed by both the designer and the implementer of the specification. A semi-formal unified view creates a common understanding between the designer, implementer, and the semantics of the dialect.

- **Translations.** Translation are used to create mappings from the unified view to either Satisfiability Modulo Theories (SMT)-LIB or a process algebra. SMT-LIB is used to define the static semantics since information of the static element in the design is used in creating the translation. The process algebra is used to define the dynamic semantics since the fire rules of nodes are used in the translation; here the process algebra is used to describe the behaviour during "execution" of a CDFD.

- **Proving properties.** The model created by the semantics for each design allows designs that are not considered to be valid. These larger than necessary models are used so that it can be determined if a design contains unwanted properties. This approach was taken to prevent "forcing" a model to satisfy certain properties, by using the minimum amount of information when creating the translations.

- **Automation.** In order to prevent an increased workload for the designer, automation is used to perform the translation and checks where possible. The tools, Eclipse and Z3 [61], and tool-set micro Common Representation Language 2 (mCRL2) [16], are used during the translations and proving of properties.

#### 1.4 Contributions

A dialect is created so that the semantics of the dialect is "smaller" than the semantics of SOFL and therefore more manageable when analysing. This dialect does not considerably

<sup>&</sup>lt;sup>2</sup>This is due to the separation between static and dynamic semantics.

change the meaning of a design and gives the option to extend it to create a language that has equivalent, if not better, descriptive power than SOFL.

SOFL allows a number of specification that are not valid<sup>3</sup> and provides very limited support to detect invalid specifications. The designer needs to use labour-intensive methods to analyse a design. This requires that the designer is an "expert" is SOFL, logic, and concurrent systems, to name but a few. By automating some verification, the usability of the created dialect of SOFL was improved, and therefore sightly less expert knowledge is needed to use the dialect.

From the literature review, no other case was found where the same techniques as here were applied to define the semantics of SOFL. An approximation is created for the semantics that allows a design to have properties that are not allowed. Since a model can be created, the properties can be tested formally. This is very close to the approach taken in [46], but they eliminate design as soon as a property is not satisfied. This early elimination will not allow the model to be created, as a result, the properties need to be verified manually.

The theory applied to define a semantics is older than the semantics that exist for SOFL. Independent development of the theory resulted in tools being created that are based on the theory used in this dissertation, and some of these tools are used here to perform formal verification.

The new semantics requires that all nodes must terminate, and that all nodes and CDFDs generate data. Termination of nodes allows the use of the idea of "total" correctness, which is also the basis for the "Correctness by Construction" approach. The requirement that all nodes generate data is needed by the description in a process algebra, but also gives the added advantage of finer control of how processes fire. Instead of allowing a number of nodes that consume data to result in termination of a CDFD, a subset of these nodes can be defined and each subset can independently result in the CDFD terminating.

Modal formulæ can now be defined to describe dynamic properties of a CDFD. This allows the use of a program to verify the formulæ, and results in a lighter workload for the designer. The translations used to create the formulæ can be improved, and important problems like detecting deadlock is still open for designs of moderate size.

#### 1.5 Modification

Comparing the newly created dialect with original SOFL, a number of modifications exist, and this section describes the modifications that have the most impact. Modifications are also made to the syntax and the syntax of the dialect is given in Appendix A.

#### 1.5.1 Refinement and Hierarchical Structures

A process in a CDFD is refined by defining a new CDFD so that the process is described in more detail. This refinement of processes creates a hierarchical structure of CDFDs. SOFL uses a hierarchical structure for one of two purposes:

1. To capture the requirement of the system being designed. A top-down approach.

<sup>&</sup>lt;sup>3</sup>For example see Figure 1.1

2. To create a more formal specification where the focus is how to realise the requirements. A bottom-up approach.

Both these uses create a hierarchical structure where a lower level in the structure adds additional information to the specification.

The use of a hierarchical structure in this dissertation will be closer to the description given in item 2 (in the above list) during analysis of the semantics. This allows a more formal approach as well as working with fewer "undefined" elements when a specific CDFD is analysed. During analysis, it is assumed that each process in the CDFD is implementable and the higher in the hierarchical structure the CDFD is, the "greater" this assumption. By starting analysis at the end point in the hierarchical structure, the designer adds all the information possible and any assumptions about processes in the CDFD being analysed. This will create an analysis with less assumption compared to starting the analysis from the top. This approach is very similar to "Correctness by Construction" [35] and [18].

A CDFD sometimes requires the use of additional input and output data flows that do not exist in the process being refined. These new data flows are introduced in an ad-hoc manner. The data type transported by the data flows must be derived from the port to which the data flows is connected. No information is provided about which groups of the input data flows must consume input, or which groups of output data flows are allowed to generate data simultaneously. The dialect requires that each CDFD has input and output ports like any process.

#### 1.5.2 Logic Usage in Specification

Logic is used in SOFL to define state spaces of data values that are allowed to be assigned to either data store or data flows. This section compares Logic of Partial Functions (LPF) and FOL before it is decided in favour of FOL, after which, other modifications related to the application of logic are discussed.

#### Case for use of LPF

SOFL uses LPF [27, 33] for defining any predicate. LPF extends FOL by allowing three "elementary values": "true", "false" and "undefined" value ( $\bot$ ) and evaluation of conjunction, disjunction, negation and implication are shown in Tables 1.1. An application of LPF is to define the pre and post condition of a function where the function might not terminate when the pre condition is not satisfied. This allows evaluation of a formula pre condition  $\longrightarrow$  post condition as part of a larger formula without the need to consider the special case where the function does not terminate. A more elaborated description of LPF in formal specifications is given in [23,34]. This is a very specific application, and fortunately it is not applicable to SOFL when a process' pre and post condition are considered, since termination of processes is guaranteed.

There is merit in using LPF in SOFL when formulæ are created that contain variables that refer to "complex" data types, i.e., lists. Consider the evaluation of a function lst(0)/len(lst) > 10 where lts is an empty list, thus the value of lst[0] is undefined, as well as division by a zero value. It can be seen that a "pre condition" of the function is

| $\wedge$ | Т | Т       | F |

|----------|---|---------|---|

| Т        | Т | $\perp$ | F |

| 上        | 上 | $\perp$ | F |

| F        | F | F       | F |

| V | Т |   | F       |

|---|---|---|---------|

| T | Т | Т | Т       |

|   | Т | 1 | $\perp$ |

| F | Т | 上 | F       |

(a) Operation table of conjunction in LPF

| Т       | F |

|---------|---|

| $\perp$ | 上 |

| F       | Т |

(b) Operation table of disjunction in LPF

| $\longrightarrow$ | Т | 上 | F       |

|-------------------|---|---|---------|

| Т                 | Т | T | F       |

|                   | Т | T | $\perp$ |

| F                 | Т | Т | Т       |

(c) Operation table of negation in LPF

(d) Operation table of implication in LPF

Table 1.1: Operation tables for LPF

that the list must not be empty, and avoiding the case of undefined values the function should be written as

$$\left(len(lst)>0\longrightarrow \left(\frac{lst(0)}{len(lst)}>10\right)\right)\vee false.$$

and only evaluate lst(0)/len(lst) > 10 when len(lst) > 0 is true.<sup>4</sup> By using LPF, "tricks" as above are not necessary to express the above formula. The difficulty in defining a formula where a sub-expression is undefined (like lst[0] in the above case) is a general problem in formal specification and not specific to SOFL. Since the purpose is to understand SOFL better, this scenario is not sufficient to motivate the use of LPF in the dialect of SOFL.

#### Case for use of FOL

SOFL uses one formula to define a pre condition and another to define a post condition of a process. These formulæ reference the connected data flows and data stores that the process has access to. Whenever a formula uses a data flows that does not contain a value, the value "undefined" is assigned to the variable associated with the data flows. However useful this is for the designer, it creates "hidden" relations between input (or output) ports of a process, which can lead to unexpected behaviour.

For example: Consider a process with two input ports where the first port is connected to a data flow a and the second data flow connected to data flows b and c, where the pre condition is given by  $(a \ge 0 \land bound(b)) \lor (b \ge 10)$ . The process will fire when there are data on a or on b and c, but the pre condition will only evaluate to true if there is data on b. Since the pre condition must evaluate to true when the process fires, for the design to be valid it must always be the case that, if there is data on a there must be data on b. Thus, that there must be data on a and b contradicts the idea that a port groups related data flows together and data is consumed from these data flows grouped together. This is an example of a process that is not useful in a specification as its meaning is questionable. This is due to the use of "undefined" values in the formula that cause the behaviour.

<sup>&</sup>lt;sup>4</sup>This is non-standard type of formula evaluation in LPF and FOL, also see [34]

Use of LPF addresses a general problem of when pre and post conditions are used to define a specification of a function, but also allows the definition of a process so that a "hidden" relationship between its input ports is created. The focus of this dissertation is to define a semantics for a dialect of SOFL and not to solve general problems in formal methods. Therefore, it is considered more important to address the "hidden" relationship that can exist between input ports of a process.

#### **State Space**

Use of predicate transform (i.e., the weakest precondition) is central to the idea of proving correctness of data being transformed, see [35] and [18]. These ideas are indirectly used in SOFL, but these concepts were used directly when the semantics for the dialect was defined. The state of CDFD is changed by a predicate transform and therefore no predicate is allowed to change the state of a CDFD. State changes are realised by a transition caused by process and a transformation defined by the combined effect of data flow through a CDFD.

The use of explicit specifications will increase the complexity of defining state spaces. Removal of explicit specifications avoids this complexity and the use of a language like Guard Command Language (GCL) [18], and allows the use of CDFD to define how state spaces change. A process is now only allowed to specify state changes by its pre and post condition, and refinement by a CDFD adds additional information on how the state changes are realised.

#### Initialising a Module

SOFL defines initial values of data stores by defining explicit values, where these values are computed by evaluating expressions. Since a fixed value is just a state space that only allows that value, there is no reason that a state space cannot be used to define the initialisation of a CDFD.

#### Restricted Usage of Logic

In [43] an invariant of module was used to reference data flows. The use of predicate in such a manner is seen as very informal, since there is no semantics defined to describe how the evaluation of the predicate interacts with the semantics.

The approach taken in defining the semantics of the dialect is to create a graph from a CDFD, and the graph is used as the Kripke structure [10] of a modal logic. This allows modal formulæ to be firmly rooted in the semantics of the dialect, and allows properties of a data flow diagram to be investigated by using modal formulæ.

### 1.5.3 Data Flows Diagrams

The most notable change to the data flow diagram is that there is no support for a graphical representation of a CDFD. This negatively affects the ease of use from a designer's perspective, but does not prevent the problem statement from being addressed.

Non-deterministic broadcast nodes are not allowed in the dialect, as the semantic of a non-deterministic broadcast requires knowledge of the "future". Knowledge of the "future"

would increase the complexity of the semantics and translation and it was decided that the increase in complexity is not worthwhile.

Shadow data flows are introduced too, so that ports not connected to data flows (as defined in classical SOFL) are now connected to shadow flows. They are treated the same as active data flows when determining if a node can fire. Passive data flows influence the process that can fire by enabling or disabling the process. The use of a passive data flow to prevent a node from consuming data is seen as totally foreign to the basic idea of a data flow diagram; each computational unit in a data flow diagram consumes data for processes as soon as the data is available. Thus, passive data flows are removed.

It is also not permitted for a node to be able to consume data from more than one input port at any given time. Allowing consumption from more than one input at a time not only increases the number of possible input and output relations of a node, but also raises the question of the meaning of ports. The idea behind a port is to define input values that need to be consumed together so that a node can use those inputs to produce output.

#### 1.5.4 Data Types

Predicate and data types have a close relationship [72] since predicates can be used to define a new data type by allowing some values to be of a more general type, and not allowing other values of the same general type. This logical view of types, and the fact that self-referencing requires special attention in logic, will be used as the main reason not to include classes.

Classes are removed from the dialect, since they are very similar to a module and create an indirect reference between two very similar elements containing each other when an instance of a class is transported by a data flow. Not being able to use classes is a disadvantage, but it will not influence the ability to analyse the dynamic behaviour of a design.

Union types define a type that can be any one of a predefined list of types. Inclusion of union types would increase the complexity of determining the type of expression without addressing the problem statement. Therefore, union types are removed from the dialect.

The translation to SMT-LIB is only defined for numerical types and does not support the other data types allowed in the dialect. By only using numerical types, the same kind of results are expected as when using a more complex type, but without the additional computational complexity.

### 1.6 Associated publication

The article [4] was accepted for publication in the proceedings of the SOFL+MSVL'18 workshop, in partial fulfilment for the degree, Master of Science (Computer Science).

#### 1.7 Outline

The rest of the chapters in this dissertation are divided as follows:

- Chapter 2 gives an overview of the related work that focuses on SOFL and are applicable to the work in this dissertation.

- Chapter 3 defines the dialect that is considered in this dissertation and gives a description of the semantics of the dialect by defining an action system used to describe the semantics in terms of state spaces and execution paths of a semantics.

- Chapter 4 defines a translation to SMT-LIB to define an approximation of the dialects' static semantics.

- Chapter 5 defines a translation to a process algebra to define an approximation of the dialects' dynamic semantics.

- Chapter 6 gives a short overview of the tool developed and analyses three examples in order to illustrate the ability to prove properties.

- Chapter 7 discusses future work that will add value to SOFL of the current dialect.

- Appendix A gives the grammar of the dialect.

- Appendix B gives the specification in the dialect of the example in this dissertation.

# Chapter 2

# Related Work

This chapter discusses previous research done on SOFL that is related to the work done in this dissertation; also, a critical discussion focusing on the semantics and verification thereof is included. Work related to this dissertation is that which focussed on the development of a semantics for SOFL, see Section 2.3. Other, less related work, is that which focussed on how to prove properties of a SOFL design, see Sections 2.1 and 2.2, but is still related since the techniques were also used to verify the static semantics.

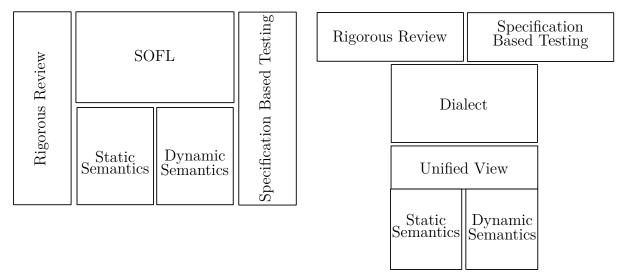

(a) Relation of the related literature with SOFL (b) Relation of the related literature with the Dialect

Figure 2.1: Showing relation between the different areas of related work with SOFL and the dialect.

## 2.1 Rigorous Review

Rigorous Review is the most formal phase of the SOFL design process and is described in [46, Chap 17]. The ideas are expanded in [53], where it is called Rigorous Inspection

Method (RIM). During rigorous review, both the purpose and static semantics of a specification are verified.

#### 2.1.1 Properties

Properties of a design that are of interest are categorised either as:

- properties that determine if a designed system is properly designed as per user requirements or

- properties of a design that are required to make the design a valid SOFL design.

Rigorous review is used to determine if any of the above types of properties are satisfied by a design.

#### 2.1.2 Method

RTT [45] [46, Sec 17.3] is a visual notation based on fault tree that is used to prove properties based on the static semantics of SOFL. A tree is used to represent a property that needs to be proven and the property is divided into parts to create the tree. This makes it easier to prove properties at lower levels. Each node in the tree defines a sub-expression and whether the sub-expression must or can hold, by either using a rectangle or a rectangle with rounded corners, for the sub-expression to be satisfied. Below its shape is a smaller shape that defines how the children of the nodes must be interpreted; this can be either:

| 1. | All t | he | children's | properties | must | hold | Щ. |  |

|----|-------|----|------------|------------|------|------|----|--|

5. The property of its only child hold

$$\Diamond$$

.

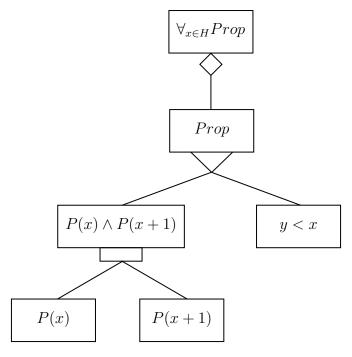

The must/can hold requirement of the expression must be read with one of the above listed properties and if the node is a leave node, the sub-expression is assumed to be true. Figure 2.2 gives the decomposition of the predicate

$$\forall_{x \in H} (P(x) \land P(x+1)) \lor (\exists_{y \in H} y \le x)$$

using task review trees. Using the tree to evaluate the predicate, each leave node is evaluated and the node is replaced by its value. A node with all its children evaluated in the previous step is then evaluated by applying the operation specified by the box. This process is repeated until the value of the root node is determined.

Figure 2.2: A task review tree of an expression

RIM [53] is an approach that combines FS and RTT to prove properties of a design. FSs are used to group elements from a CDFD together to describe an input/output relation that is also associated with a property that needs to be proven. Each operation involved in the FS must first be inspected after which the FS is inspected. Inspection is the process proving that a FS/operation satisfies some property using RTT.

#### 2.1.3 Comments

RIM is a very useful approach to verify that a specification satisfies certain properties. The use of FS allows a CDFD to be further divided into groups of elements where each group is responsible for realising a specific set of properties. Since the generation of FS can be automated [55], the most labour-intensive part of RIM is the use of RTT. The use of RTT also requires the designer to have a good background in logic and a thorough understanding of the semantics of SOFL.

RTT can be used to verify the dynamic semantics<sup>1</sup> of a design, but as the size of the design increases, the complexity of the trees used to represent the properties also increases. This would make it unfeasible to prove certain properties of large designs.

### 2.2 Specification Verification

Formal Specification-Based Inspection (FSBI) is an additional inspection method based on SBT, and is introduced in [50] to support RIM when a design is verified. Using this new approach, dynamic aspects of a specification are verified by considered "execution" paths for each FS.

<sup>&</sup>lt;sup>1</sup>Property that relates data flows are used in [43]

#### 2.2.1 Properties

An FS defines a transformation that transforms a state space associated with the input of the FS to the state space of its outputs. Verification of such a transform's properties is a verification of a specification's dynamic semantics.

#### 2.2.2 Method

The method of applying FSBI requires a considerable number of steps and these are:

- **Derive FS.** The first step is to derive functional scenarios for a CDFD, as described in the method section of [54].

- **Derive program paths.** Create program paths. This is not an easy task [24] however a method is given in [50].

- Link scenarios to paths. The program paths created need to be associated with a scenario in order to divide the analysis into smaller problems and prove the properties associated with each FS.

- **Analyse paths to detect defects.** The paths are analysed and it is determined whether the required properties are satisfied or not.

- **Produce an inspection report.** A report is created that reflects the findings of the specification's analysis.

#### 2.2.3 Comments

The use of FSBI is a labour-intensive approach but does provide a "middle ground" between the formal part of the verification and its usability. The part of the analysis that is the most labour-intensive is the analysis of paths and linking them to FS. For each decision of where data flows in a CDFD are placed, an additional path needs to be created. These decisions are due to condition structures or processes that contain more than one output port.

#### 2.3 Semantics

The semantics of SOFL defines the precise meaning of the different elements that a specification contains. This part of defining SOFL is very formal and requires the use of a logical language with well-defined concepts. Previous work done on the semantics is limited; however, those of interest are discussed here.

#### 2.3.1 Static Semantics

Static semantics [19, 20] of SOFL is defined using the language Object-Z [21] to describe the meaning of the semantics. Object-Z is itself a formal specification that includes advanced ideas such as classes and angelic choice operation. The semantics of Object-Z

is already well-defined. These advanced concepts are very useful in defining SOFL, and a static semantics is created that defines all the needed concepts of SOFL, as required by [46].

For each of the elements in SOFL, an Objective-Z class is created to describe the properties of the element and its relation to the other elements.

#### 2.3.2 Dynamic Semantics

Dynamic semantics [30] of SOFL was defined in order to resolve uncertainty of the semantics that existed after SOFL was introduced, [57]. Since no formal static semantics existed at that time [30], some static elements were first informally defined and are used in defining the dynamic semantics.

The dynamic semantics are defined using Structure Operation Semantics (SOS) [66] where there is separation between the "state" of the system being defined and the "rules" used to change the state of the system. Each of these rules are only applied to the "state" being transformed when the "state" satisfies some condition. Definition of the fire rule of a node is of the most interest: The node fires when the following conditions are satisfied:

- 1. A process p exists that can consume data.

- 2. The pre condition is true in the current state.

- 3. The post condition is true in the state after the processes fire.

When the above rules can be satisfied, the process fires and the new "state" of the system is created. Determining the next set of nodes and type of nodes that can fire is also defined with similar rules.

#### 2.3.3 Revisit of Refinement

A fundamental investigation was done in [48] of the type of refinement relation used in formal specifications. For the usual refinement relation for a process B that is refined by a process C, the refinement is defined by requiring that the predicates

$$pre(B) \longrightarrow pre(C)$$

$pre(B) \land post(C) \longrightarrow post(B)$

are true and is the same conditions required by [46, Def 22] for a refinement of process. The problem with this relation is that a process can be refined into a process that cannot be implemented. To address this problem, an extension of the refinement relation is suggested and given by

$$\forall_{s \in \Sigma} pre_A(s) \longrightarrow \exists_{s' \in \Sigma} \cdot (port_A(s, s') \longrightarrow post_A(s, s')) \land (\neg post_A(s, s') \longrightarrow s = s')$$

where

- 1.  $pre_A(s)$  is the pre-condition of process A and s is the state in which the predicate is evaluated.

- 2.  $post_A(s, s')$  is the post condition of process A, s is the initial state and s' is the final state after A is applied to s.

- 3.  $\Sigma$  denotes the set of all states.

This additional relation ensures that if the post condition of the process cannot be satisfied in a new state, then the new state and the initial state are equal. Thus, the complete refinement relation (with simplifications) is defined by

$$pre(B) \longrightarrow pre(C)$$

$$pre(B) \land post(C) \longrightarrow post(B)$$

$$\forall_{s \in \Sigma} pre_C(s) \longrightarrow \exists_{s' \in \Sigma} \cdot (post_C(s, s') \lor s = s').$$

The right-hand side of the last formula states that there exists a state where the post condition is true or the state remains unchanged.

#### 2.3.4 Comments

The semantics of SOFL was defined after the method was created, which is not unusual, but the dynamic semantics was formalised in 1997, whereas the static semantics was only formalised in 1999 and 2002. This creates a curious situation where the dynamic semantics is based on only a semi-formal idea of the static semantics. By not having a formalised static semantics, it is not always clear that the static semantics will allow a model, therefore the dynamic semantics can be based on a model that does not exist.

Object-Z was used [19, 20] to define a static semantics using advance concepts of Object-Z. Advance concepts are useful and assist considerably in defining the semantics; however, the author does not agree with their use. Object-Z is a complete specification as well as VDM on which predicates of SOFL are based. By using a language with almost the same "level" of abstraction to define the semantics of another language, uncertainty is created, as some concepts might not be well-defined. In [20] the semantics of a SOFL class is defined by an Objective-Z class. For this approach to be acceptable, SOFL is required to be defined by a fragment of Object-Z, and therefore the semantics of SOFL is automatically defined by Object-Z's semantics. This approach is very similar to defining a programming language<sup>2</sup> in terms of another language. For a programming language, this approach is acceptable, since the original defines the semantics and the expressibility of the new language.

Dynamic semantics defined in [30] does not follow a constructive approach. The approach follows defined rules and only models that satisfy those rules are allowed. This is a proper approach to define a semantic, but it sometimes lacks an intuitive<sup>3</sup> understanding of the semantics. Conditions for the fire rule require knowledge of the "future" when the post condition of a node is used to determine whether a node is permitted to fire. The

<sup>&</sup>lt;sup>2</sup>For example: Xtend, https://www.eclipse.org/xtend/documentation/index.html

<sup>&</sup>lt;sup>3</sup>This is partially addressed in [30] by using comments for the rules defined.

properties of non-existing output are required to determine if output should be generated: this is a curious situation since a data flow diagram processes data from its input to output without first testing the output that could be created. A node in a data flow diagram does use knowledge of availability of data on its output data flows to determine if the node can fire. The information that the node uses is not "future" knowledge as the node only fire if there is no token on output data flows, and only the node can generate on the output data flows.

The update refinement relation of [48] is not applicable to SOFL, as state changes are only influenced by nodes when they fire. There is no reason for pre and post condition to be used as a "double" check to make sure the fire rules function correctly. SOFL defines only one post condition for all the output port of a node where any of the ports are allowed to generated data. This could allow unwanted scenarios during refinement as described in [48].

### 2.4 Summary

Both Rigorous Review and Specification Base Testing are more suitable to verifying properties that are required by the system and not to verify semantics, since properties of a system are more diverse and those required by the semantics are fixed when the language is defined.

Both static and dynamic semantics are very old and are seen as too abstract for a formal specification language. Better separation between pre and post condition and the firing rules of nodes is needed.

# Chapter 3

# Description of SOFL Dialect

The SOFL dialect specifications are defined using text files, but for clarity of this dissertation the graphical representation for CDFDs is still used. Section 3.1 gives an overview of how the dialect specification is defined with particular focus on the syntax changes made to create the dialect. For a complete description of the grammar see Appendix A; familiarity with [46] is also assumed.

A semi-formal description is defined in Section 3.2 and is used as a starting point when static and dynamic semantics are defined.

## 3.1 Syntax

In this section, examples are given for each component to illustrate how the syntax of the dialect is different from those of original SOFL.

#### 3.1.1 Module

A module is a container used to group the elements in a design. When the module inherits from a parent module, the module also inherits the variable and types in the parent module. Processes are defined in a module, and they define the computational units in a specification. Functions are only used as part of an expression. The behaviour of a module defines how processes in a module are used to realise a module's behaviour. An example of a module's specification is given below with comments:

```

module NameOfDesign / ParentModuleName

/*Type declaration*/

type

TypeName = Type;

AnotherTypeName = AnotherType

/*

Variable declaration

*/

var

ext # wd external_to_system : Type;

```

```

ext rd store_of_parent;

new_store : Type

/*

Constant declaration

*/

const

constant_name = /*expression*/;

another_constant = /*another_expression */

/*Invariant declaration*/

inv

Invariant_one;

Invariant_two

behaviour /*Behaviour specification*/

end_behaviour

/*Process specification*/

/*Function specification*/

endmodule

```

Only predefined types, as defined in [46], can be used in a module to define new types, and defined types can be used in all the modules that inherit from it directly or indirectly. If a module reuses a type name, then the new type "over shadows" the previously defined type.

The variables are either defined in the current module or accessed from an external source. Variables from an external source are indicated by ext # and can have either read or write access. Other external variables are inherited from the parent module after the stores are filtered by the process that this module refines. These are indicated by the keywords ext rd or ext wr, depending if read or write access is required to the variable. Constants are special variables, as after their initialisation by an expression they have read-only access.

Invariants are used to define predicates that must be evaluated to true between times when processes fire, and invariants can only access variables that are visible in the current module.

The behaviour, processes, expressions and functions are considered below since they are more complex than the other elements.

#### 3.1.2 Behaviour

Behaviour elements are textual representations of a CDFD and define how a process is being refined. They have input and output ports related to the process being refined. An example of a graphical representation is given in Figure 3.1 and a textual representation is given by:

```

behaviour BehaviourName(

tmp_data:real | middle: real | tmp_added: real)

out data:real | out added: real

```

```

/*

Define addition input/output data with their data types

added(added_input:real) added_output:nat0

/*

When addition flows are added the input/output ports

need to be redefined. Type information is not added

since they are redundant.

*/

grouping(tmp_data | middle,added_input | middle | tmp_added)

out data | out added, added output

state_condition in 1 out 1 pre true post true

state condition in 4 out 2 pre true post true

/*

Structure node definitions

*/

/*

Data flow definitions

*/

end behaviour

```

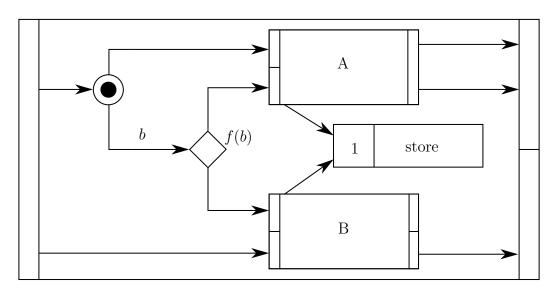

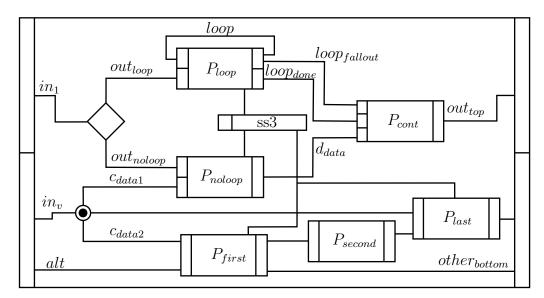

Figure 3.1: Example of a CDFD. The CDFD is drawn inside a process symbol since it must also contain input and output ports in the dialect

The meaning of a CDFD is based on a data flow diagram [17], where each computational element processes data as soon as all its input data flows contain data. In the case of CDFDs, data flows are grouped to indicate from which input flows data can be consumed, and on which output flows data can be generated: these groupings are called ports.

The behaviour element is used to refine a process, and the process being refined determines restrictions on the input and output behaviour of the CDFD. In order for the CDFD to perform the transformation from input to output, it might be necessary for additional input or output data flows to be defined. These additional data flows and the data flows from the process being refined also need to be grouped by ports, for the input and output of the behaviour element to be well-defined. Newly introduced data flows must be associated with at least one port, but may be associated with more. This is allowed since the process being refined will determine when the CDFD fires.

A CDFD defines how input are transformed into output and therefore also define a predicate transform. The pre and post conditions are made explicit for each pair of ports using a **state\_condition** statement block. The predicate does not define a state change in the CDFD only the allowed input and output states, whereas the data flows and nodes are used to realise the state change.

Control nodes assist data flows to transport data to the process that will perform the needed computations. The permitted control nodes are:

- 1. Conditional structures

- 2. Merging and separating structures

- 3. Broadcast structures

The remainder of this section describes these components and gives a graphical representation of data flows, data stores and the control nodes.

#### **Data flows**

Data flows are the carriers of data between different components in a CDFD. Each data flow is associated with a fixed type and is in one of two states: having data or not having data.

Two types of data flows are used, these are: active and shadow flows, and are defined by indicating the node and variable connected to the flows where the left-hand side of => is the source and the right-hand side is the destination.

```

flow behavior.tmp_added => proc Combine.tmp_added

flow proc Combine.out_added => behavior.out_added

shadow flow cast Broad.out_added => proc Combine.out_added

```

An active flow is defined by flow and a shadow flow by shadow flow. After the node identification the variable name is given, except for the behaviour which does not require a name, as only one such element is contained in a module. The source and destination name must be the same as well as their type. In the dialect, it is not possible for a port not to be connected to a data flow, and shadow flows are introduced for this purpose. The only difference between shadow and active flows is that the value carried by shadow flows meaning is limited to the presence or absence of data: the fire rules are the same.

#### Conditional structures

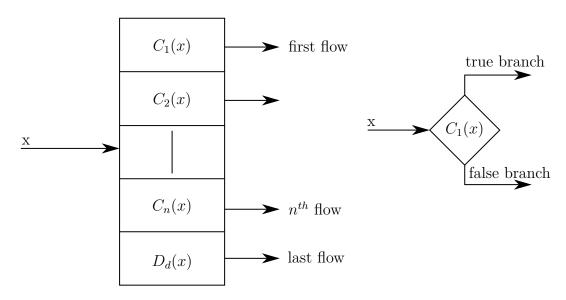

Two representations are given for a conditional structure in Figure 3.2. When only two output branches exist a diamond shape is used. When more than two output branches

exist, the pairwise conjunction of the predicates must be false and disjunction of all output predicates must be true, given the allowed input values. A textual specification is given by:

```

condition ConditionName(input)

out1: out1 > 0,

out2: out2 < 0,

out3: out3 = 0

end condition</pre>

```

where the type of the output variables are the same and are defined by the input variable. These variables are connected via data flows to other variables contained in other elements.

Figure 3.2: A conditional structure representation.

#### Merging and Separating structures

A merging structure takes n input values and produces one value with a type equal to the product [46, Chapter 10] of the input types, and each component of the output is equal to their respective input value. Separating structures undo the effect of merging structures (see Figure 3.3). The purpose of these structures is two fold:

- 1. To reduce the number of data flows in a diagram

- 2. When the condition of a condition structure depends on more than one data flow, a merging structure creates one data flow required by a conditional structure.

```

merge MergedName(var1, var2, var3)

out_combined

end_merge

```

```

unmerge UnmergedName(in_combined)

var1,

var2,

var3

end_unmerge

```

Figure 3.3: Merging and separating structure representation

#### Broadcast structures

A broadcast structure that duplicates the input and places it on all output flows without changing the data value, is shown in Figure 3.4. The textual specification is given by:

```

broadcast Cast(indata)

out_data_1,

out_data_2,

out_data_3

end_broadcast

```

Figure 3.4: A broadcast structure representation

#### Data stores

A variable defined in the module is also referred to as a data store when used in a CDFD. Figure 3.5 shows how data stores are associated with a process. Process A has write

Figure 3.5: A graphical representation of a data store

access whereas process B has read access to the data store. The type of the data store cannot change during the lifetime of the data store.

#### 3.1.3 Processes

Processes are the elements in a module that perform computations as well as providing the opportunity to refine process by another module. An input/output state transform is defined similarly to a behaviour element, and the pre/post conditions are defined by state\_condition statements. Process also defines access required to data store that are visible in the current module, and only those data store which a process has access to can be inherited by the module that refine the process.

A graphical representation of a process is given in Figure 3.6; its textual specification is given by:

In the last predicate transform defined, the function CallToFunction is applied to the variable loop as it was before the execution of a process, by referring to it by ~loop. The pre/post condition of the process does not define a change of state stores or data flows values; they only define the state in which the process is allowed to execute and the allowed state after execution. State change is realised by defining a module that refines the process.

Figure 3.6: A graphical representation of a process

#### 3.1.4 Expression and Function

Expressions form a large part of a specification as they are used to define predicates, constant values, and the initial state space of a CDFD. Expressions are defined in [46], but it is important to note that an expression cannot change an input value and cannot use a process in its evaluation. Functions are used as an abbreviation for an expression and can only be used as part of an expression. An example of a specification is given by:

#### 3.1.5 Syntax Differences

The grammar of SOFL [46, Appendix A] is modified to obtain a grammar for the dialect and the exact locations where the grammar was modified are indicated in the Appendix. This section gives the changes made to the grammar of SOFL. Whenever a syntax rule is removed or modified which results in other rules no longer being referenced in the grammar, those rules are also removed from the grammar. The modified rules are not named explicitly, but rather the keyword that is removed is used.

#### CDFD and Module Related

Removal of the visual representation of a CDFD has considerable effect as the "name" of the CDFD cannot be used in the specification. The visual representation is replaced by a behaviour ... end\_behaviour statement block that contains all the definition of elements of interest that were defined in the visual representation of a CDFD, and is used to define the CDFD in the dialect. The statement block also replaces behav which is used in SOFL to associate a CDFD with a module, but in the dialect the CDFD is part of the module.

SOFL is allowed to reference previously defined elements in other places of the specification. Syntactical element of the form Identifier('.'Identifier)\* and references of previously defined elements are removed.

#### **Process Related**

Definition of a process's pre and post conditions is replaced by a **state\_condition** statement for each input and output port pair.

When a process is refined, the keyword decomposition is used in the dialect and uses the name of the module that refines the process. SOFL use the keyword decom and the name of the CDFD that refines the process.

The initial state of a module in the dialect is defined using predicates and the Init process, whereas SOFL uses an explicit specification. An example of a Init process in the dialect is given by:

```

process Init()

ss3 < 20;

ss3 > 11

end process

```

Explicit specification of processes is not allowed, thus the keyword explicit is removed.

#### Types related

The types removed are "classes", "undefined" (part of LPF) and "universal" as well as keywords used to define element and functions defined in SOFL that use removed types as parameters. Thus, the removed keywords are:

- 1. universal

- 2. sign

- 3. nill

- 4. undefined

- 5. bound

#### Expression related

The most notable change to expression is that no "imperative" expression is used, thus assignments are only allowed as part of a let ... in ... statement block. Also, all elements of expression that are used with types removed are also removed.

SOFL also allows a quantifier over a collection of data values, e.g.

```

forall[el: list containing values | expression]

```

where the dialect only allows use of data types over which a quantifier can be used.

### 3.2 Semi-Formal Semantics

This section starts by defining the semantics using an intuitive view of how a program can be represented by state graphs (program graphs), Section 3.2.1. This is followed by how the predicate transform represents the state change by a node in these graphs

(Section 3.2.2). Predicate transforms are then used to describe the input and output state spaces of a CDFD. From these input / output relations an action system (Section 3.2.4) is created that gives a formal description of a CDFD's program graph.

The hierarchical structure created by a CDFD refining processes (Section 3.2.3) is used to combine the semantics of different CDFDs together. No dynamic behaviour is defined between levels in the hierarchical structure.

Throughout this process, conditions are defined that need to be satisfied for the final semantics to be sensible. This is done to place additional focus on those properties and motivates how those properties are applicable to the dialect. Finally, the conditions are also used to determine which properties can be verified during either static or dynamic verification.

## 3.2.1 Program Graph

A program graph<sup>1</sup> is used to present how different elements of a program execute; where each vertex in the graph defines the state of the program. A transition from one state to another is labelled by all the nodes that fire in a CDFD at a specific time. This view is different from a data flow diagram of [17] in which the operations are represented by vertices. The two views are equivalent but the meaning of vertices and edges is swapped.

A program graph is given in Figure 3.7 of the function:

```

function func(x)

if x > 0

return x + 1

else

return 2*x

```

Each of the paths in the graph give a sequence of state transitions that are used to compute the results of the program. Such a path is called an execution path and this path is used to represent the sequence of computation performed. By allowing a program to perform more than one operation per transition in the execution path, parallelism is represented, therefore such parallelism is inherently part of a CDFD since it is based on data flow diagrams.