8597847

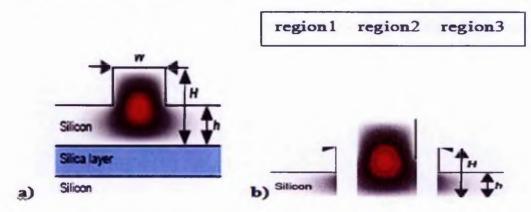

.

811-04-99

P

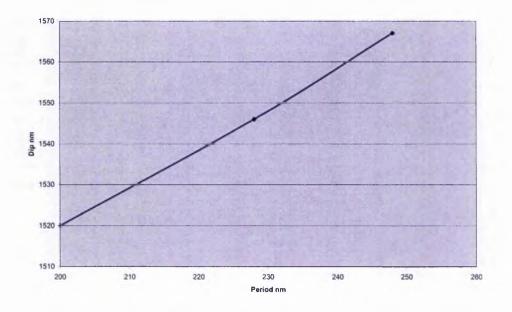

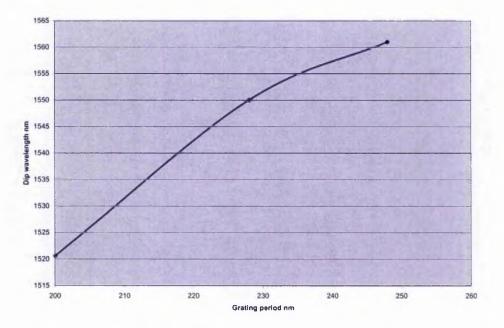

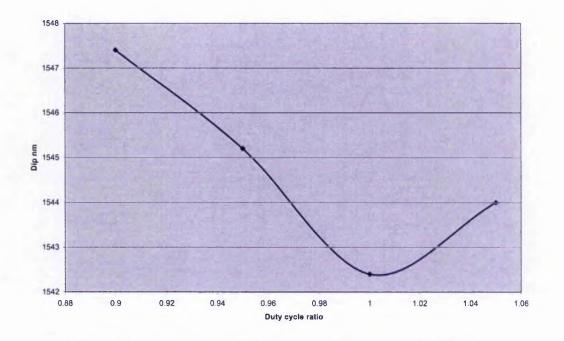

All rights reserved

## INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

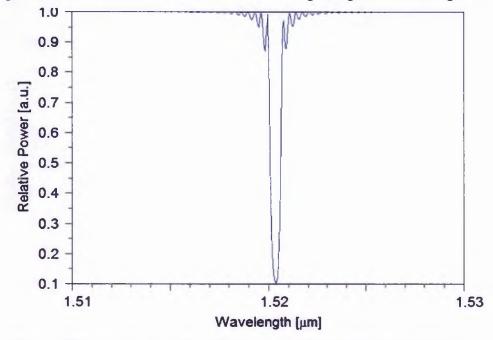

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

Published by ProQuest LLC (2017). Copyright of the Dissertation is held by the Author.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

> ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346

First Order Bragg Grating Filters in Silicon on Insulator Waveguides

By

Peter Michael Waugh

A Thesis presented to the Faculty of Engineering and Physical Sciences, University of Surrey, for the award of Doctor of Philosophy (PhD.)

**Faculty of Engineering and Physical Sciences**

**Advanced Technology Institute (ATI)**

**University of Surrey**

**Guildford**, Surrey

GU2 7XH, UK

© P.M. Waugh

Email: <u>p.waugh@surrey.ac.uk</u>

## Abstract

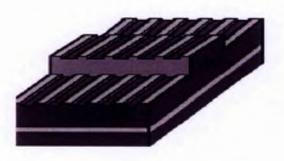

The subject of this thesis is the design; analysis, fabrication and characterisation of first order Bragg Grating optical filters in Silicon-on-Insulator (SOI) planar waveguides. It is envisaged that this work will result in the possibility of Bragg Grating filters for use in Silicon Photonics. It is the purpose of the work to create as far as is possible flat surface waveguides so as to facilitate Thermo-Optic tuning and also the incorporation into rib-waveguide Silicon Photonics.

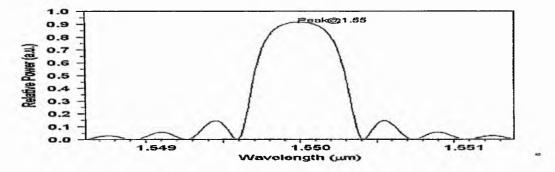

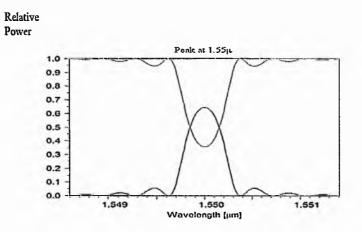

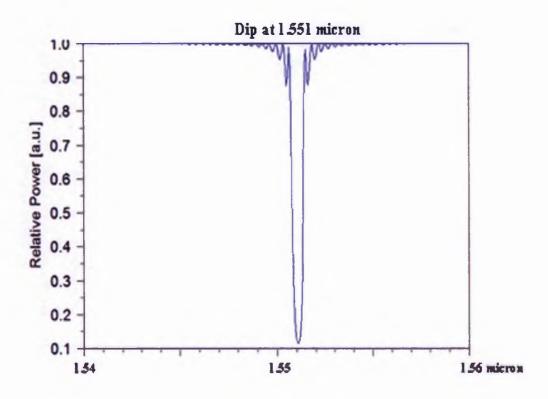

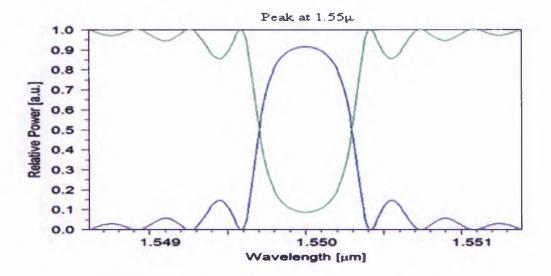

The spectral response of the shallow Bragg Gratings was modelled using Coupled Mode Theory (CMT) by way of RSoft Gratingmod <sup>TM</sup>. Also the effect of having a Bragg Grating with alternate layers of refractive index 1.5 and 3.5 was simulated in order to verify that Silica and Silicon layered Bragg Gratings could be viable.

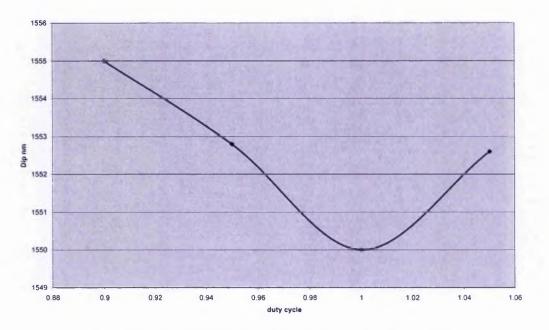

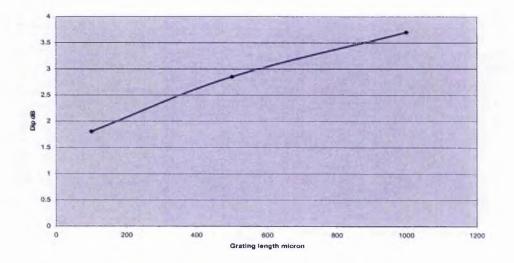

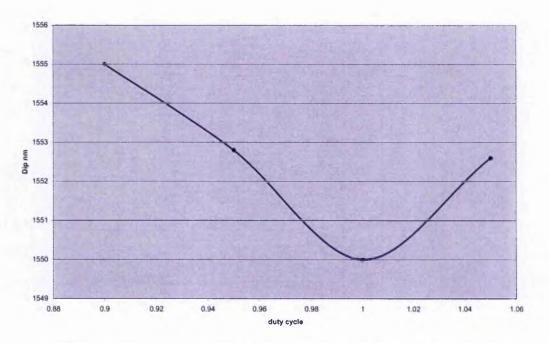

A series of Bragg Gratings were patterned on 1.5 micron SOI at Philips in Eindhoven to investigate the variation of grating parameters with a) the period of the gratings b) the duty cycle (or mark to space ratio) of the gratings and c) the length of the region converted to Bragg Gratings (i.e. the number of grating period repetitions).

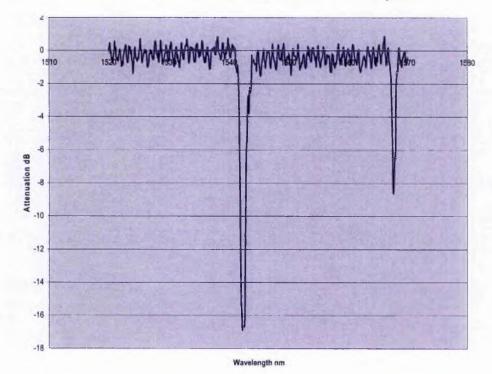

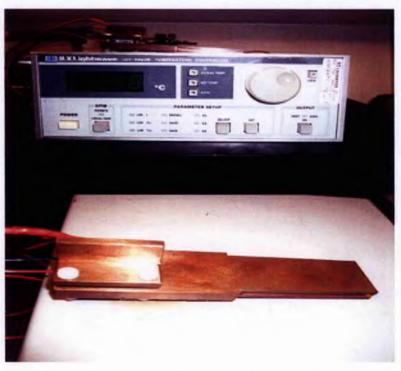

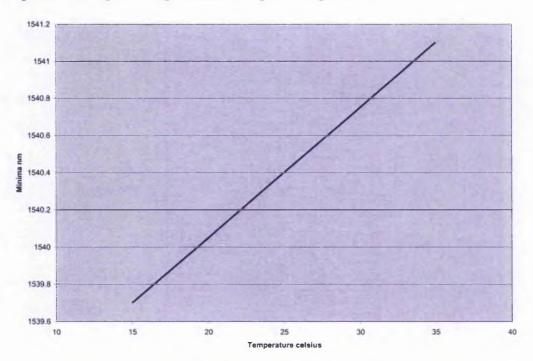

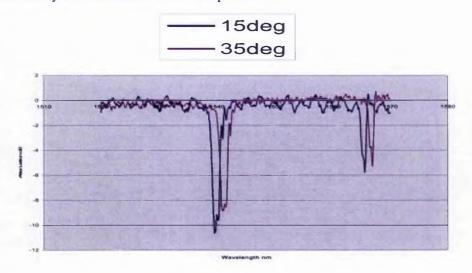

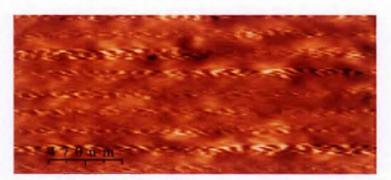

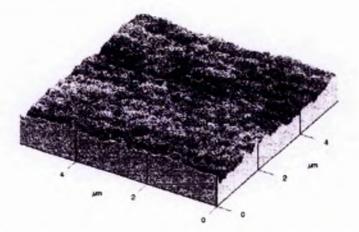

One set of gratings were thermally oxidised at Philips in Eindhoven (this was to simulate the effects of oxidising Porous Silicon) and another set were ion implanted with Oxygen ions at the Ion Beam Facility, University of Surrey. The gratings were tested and found to give transmission minima at approximately 1540 nanometres and both methods of creating flat surfaces were found to give similar minima. Atomic Force Microscopy was applied to the grating area of the Ion as Implanted samples in the ATI, University of Surrey, which were found to have surface undulations in the order of 60 nanometres.

Key words: Silicon-on-Insulator (SOI), Bragg Grating filter, Coupled Mode Theory (CMT), Thermo-Optic (TO).

### Acknowledgements

This thesis could not have been achieved without the excellent patience, guidance and encouragement of my supervisor Professor Graham Reed. His direction proved invaluable with respect to technical matters, research approaches and the presentation of this work. I am especially grateful for the opportunity provided thanks to his leadership and for him taking a chance with me as a research student at a time when perhaps no one else would have done! I am grateful for advice with fabrication to Dr Graham Ensell of Southampton University, Mr Tony Blackburn, Mr David Guite and Naser (thanks for help and advice with L-Edit and related problems) at Innos Ltd. without whose help fabrication would not have been possible. I would like to express my gratitude to Dr. Mingming Jiang and Matthew Frank at RSoft for their invaluable help with Gratingmod. Also thanks to Professor Russell Gwilliam and Dr Chris Jeynes at Nodus at Surrey University for help with the ion implantation and to Philips at Eindhoven for providing the thermal oxidation and cleaving the finished products. Also thanks to Professor Gwilliam for providing the annealing help that I required. I would also like to thank Dr Goran Mashanovich for his wise counsel with respect to grating design and help with project managing and proof reading a very diverse PhD and as well as this to express considerable thanks to Drs Mashanovich and William Headley for their help with the sometimes tortuous testing and preparation and presentation of experimental results. I also would like to express my gratitude to Dr Neil Emerson for his help with report writing and planning. I would like to extend my thanks to Dr J. Keddie for his invaluable help with ellipsometric problems.

I would also like to thank EPSRC and Surrey University for supporting my PhD studentship, I am very grateful for the opportunity that their patience has granted. Working with members of the Advanced Technology Institute's Silicon Photonics group has been a great pleasure. I am indebted to a number of talented people including Dr C.E. Png, Dr S.T. Lim, Dr W. Headley and especially Dr S.P.Chan for help in the lab and discussing various aspects of the work and for tuition received especially in the early days when I was very green. It has been a pleasure to work with my research colleagues B. Timotijevic, F. Gardes (thanks for helping with the SEM), S. Howe (thanks for helping with the AFM), P. Yang, R. Loiacono, N. Owens and especial thanks to D. Thomson and N. Wright for help with rib waveguides and the clean room! I would also like to thank others at the ATI for their kind help and

consideration including but not exhaustively S. Ahmed, M. Webb, M. Lourenco and G. Kerr. I hope that thanks to the support of so many good people that this thesis will prove to be of use to further the understanding of Optical Electronics in general and Silicon Photonics in particular.

Thank you also to the technical staff at Surrey University for providing much needed help and support and especially to John Underwood for help with stripping Silicon Nitride. It can't possibly have been easy putting up with me as a research student, so once again, MANY THANKS!

Finally and perhaps most especially thanks to my wife Angela for putting up with me poring over my laptop for countless hours: a more or less completely computer oriented vegetable: lost to the world!

| CONTENTS                              | 4  |

|---------------------------------------|----|

| Publications                          | 6  |

| 1 Introduction                        | 7  |

| 2 Literature Review                   | 13 |

| 2.1 Silicon on Insulator              | 13 |

| 2.2 Oxygen Layers by Ion Implantation | 20 |

| 2.3 Devices                           | 27 |

| 3 Theory                              | 52 |

| 3.1 Bragg Gratings in SOI             | 52 |

| 3.2 Waveguides in SOI                 | 58 |

| 3.3 Ellipsometry                      | 60 |

| 3.4 The Bulk Implant                  | 62 |

| 3.5 Ion Implantation                  | 63 |

| 4 Device Design                       | 69 |

| 4.1 Single Mode Operation             | 69 |

| 4.2 Waveguide Design                  | 69 |

| 4.3 Bragg Grating Design              | 70 |

| 4.4 Ellipsometry                      | 79  |

|---------------------------------------|-----|

| 4.5 Bulk Implant                      | 81  |

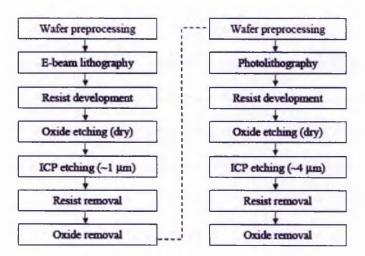

| 5 Device Fabrications                 | 84  |

| 5.1 Introduction                      | 84  |

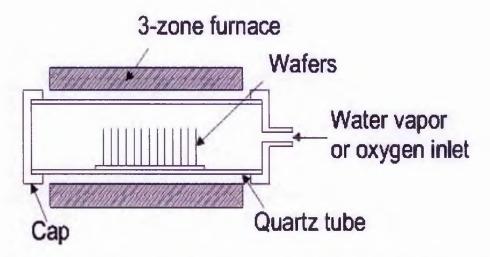

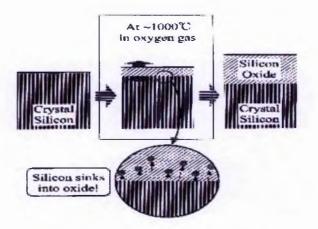

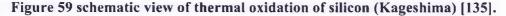

| 5.2 Thermal Oxidation                 | 87  |

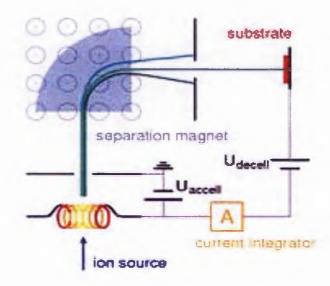

| 5.3 Ion Implantation                  | 92  |

| 5.4 Polishing                         | 100 |

| 6 Experimental Techniques             | 108 |

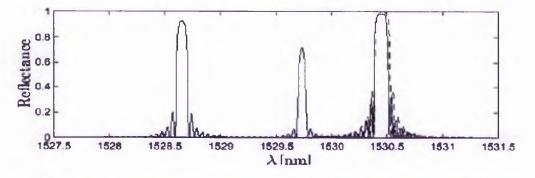

| 7 Experimental Results                | 116 |

| 8 Discussion                          | 143 |

| 9 Conclusion                          | 152 |

| 10 Future Work                        | 153 |

| 11 References                         | 158 |

| Appendix 1: Srim                      | 171 |

| Appendix 2: RSoft Gratingmod Software | 172 |

## Publications

- 1. A. P. Knights, M. P. Bulk, P. E. Jessop, P. Waugh, R. Loiacono, G. Z. Mashanovich, G. T. Reed, and R. M. Gwilliam, "Optical filters utilizing ion implanted Bragg gratings in SOI waveguides", Advances in Optical Technologies, (accepted) 2008.

- G. T. Reed, G. Z. Mashanovich, W. R. Headley, B. Timotijevic, F. Y. Gardes, S. P. Chan, P. Waugh, N. G. Emerson, C. E. Png, M. J. Paniccia, A. Liu, D. Hak, and V. M. N. Passaro, "Issues associated with polarisation independence in silicon photonics," IEEE J. Select. Topics Quant. Electron., vol. 12, pp. 1335–1344, 2006.

- W. R. Headley, G. T. Reed, G. Z. Mashanovich, B. Timotijevic, F. Y. Gardes, D. Thomson, P. Y. Yang, E. J. Teo, D. J. Blackwood, M. B. H. Breese, A. A. Bettiol, and P. Waugh, "Future prospects for silicon photonics," SPIE Europe Microtechnologies for the New Millennium, Gran Canaria, Spain, 2-4 May, 2007.

- G. T. Reed, P. Y. Yang, W. R. Headley, P. M. Waugh, G. Z. Mashanovich, D. Thomson, R. M. Gwilliam, E. J. Teo, D. J. Blackwood, M. B. H. Breese, and A. A. Bettiol, "Novel fabrication techniques for silicon photonics," Proc. SPIE, vol. 6477, 2007.

## **1** Introduction

Primitive means of communication included torches, semaphore, and photo phone [1] and had low communication capacity. Analogue electrical and microwave communications are improvements but carry considerable loss and come somewhat expensive in the usage of copper wiring.

In the modern world there is an increasing need for high speed, high bandwidth communication. This is to address the demand for voice, music, video and digital communication not just between countries but also continents as globalisation progresses and the number of consumers increases. Transmission rates over the last 100 years have improved due to the invention of (1860) telegraph, (1900) telephone, (1940) coaxial cable, (1960) microwave and (1990) optical amplifiers (erbium doped fibre amplifiers [1].

The invention of the laser in 1960 (Maiman: Ruby Laser [2]) provided a radiation source with potential for use as an information carrier. Also the increasing usefulness of fibre optic cable through the seventies with reducing loss over long distances led to the realisation of intercontinental fibre optic communications. Present day optical fibres have a transmission rate capacity in excess of terabits per second and as they have the lowest attenuation in the 1.5 micron wavelength window, such wavelengths are used as long distance carriers. Wavelength Division Multiplexing (WDM) increases the carrying potential of a single fibre and is thus used in modern telecommunications systems.

Copper wiring as well as being expensive, suffers from technical disadvantages: for example at high frequency or bit rate the wires tend to radiate electro-magnetic radiation which causes a loss of energy from the wire. This loss can lead to the possibility of electronic eavesdropping. Glass fibres for fibre optics on the other hand are derived from Silica a commonplace and cheap material. Also they tend to be secure as optical tapping is easily detectable. Thus for some time communication across the Atlantic, for example, has been via optical cable. A contribution to making the situation more optically ergonomic was the development of the Erbium Doped Fibre Amplifier (EDFA) in the early 1990's which meant that optical signals could be

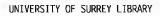

amplified without electronic conversion [3]. Erbium doping creates intermediate energy level transitions which make amplification possible. Figure 1 shows the energy states in an EDFA: the optical pump transfers the electrons to the highest state I11/2 from this they rapidly decay to the intermediate metastable state I13/2. The passage of a photon of just the right energy stimulates return to the ground state I15/2 and photonic amplification occurs [4].

Figure 1 Energy level diagram of EDFA [4].

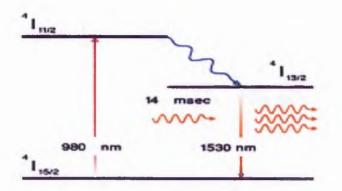

Figure 2 Schematic of an optical fibre amplifier [3].

Figure 2 shows the schematic of an optical amplifier: the three signals are combined with a pump signal and passed into a doped fibre loop where the amplification occurs and the three signals pass on down the fibre in the same direction but larger in amplitude. Electronic level broadening occurs with doping Rare Earth ions into glass and this causes the range of amplifiable wavelengths to be broadened and thus a single amplifier can be used to amplify all signals carried on a fibre [3, 5]. There is a limit to what can reasonably be achieved with fibres due to cost both for installation

and extraneous components and this tends to limit its use to intercontinental or long distance applications. Researchers have been considering for several decades the possibility of all optical networks whereby expensive and time consuming conversions from photonic to electronic signals could be avoided or at least kept to a minimum. The possibility of integrating all the necessary components (from the telecommunications point of view) onto one single chip has for some time been the goal of much of opto-electronics.

However, the means of gaining optical integration was an enigma for optical researchers. For some time it was thought that Lithium Niobate would provide the key since its optical properties were very convenient in terms of rotating the plane of polarisation of laser light under applied electrical voltage. Unfortunately it proved initially difficult to machine and provide wafers similar to Silicon and also gave complicated circuits for manufacturing and so this has caused a reduction in interest.

Silicon would initially seem an unlikely candidate since it has no linear electro-optic effect for modulation and cannot provide a conventional semiconducting light emitter in the manner of III-V or II-VI compounds (e.g. Gallium Arsenide or Zinc Selenide). However, Silicon does have noticeable second order optical characteristics and this has led to the recent development of Raman amplification and lasing [6-16].

A Raman amplifier is an optical amplifier based on Raman gain [11]. The Raman active medium is usually an optical fibre, although it can also be a bulk crystal, for example. An input signal can be amplified while co or counter propagating with a pump beam, the wavelength of which is typically a few tens of nanometres shorter. For Silica fibres, maximum gain is obtained for a frequency offset of about 10 to 15 THz between pump and signal, depending on the core composition.

Compared with Erbium Doped Fibre Amplifiers, a Raman amplifier's typical features are [12]:

- Potential for generating gain in very different wavelength regions provided that a suitable pump source is available.

- Tailoring of the gain spectrum by using different pump wavelengths simultaneously.

- Requires high pump power (possibly raising laser safety issues) and high pump brightness, but can also generate high output powers.

- Requires longer fibre lengths (but transmission fibre in a telecom system may be used).

- Potentially lower noise.

- Fast reaction to changes of the pump power (particularly for co-propagating pump).

As well as these developments in optics developments in electronics are of interest at this stage. Silicon-on Insulator (SOI) has long been a matter of interest to the electronics trade since it produces high quality radiation hardened components which have lower leakage and stray capacitance than their bulk Silicon counterparts and thus considerable money and research have combined to yield the present Ultra Large Scale Integration (ULSI) that we increasingly have today.

Problems facing this ULSI are speed and power dissipation and the solution to this may well be strained Silicon on SOI ( for a discussion of this, please see **The Present** and **The Future** in Chapter Two) in which case the SOI share of the market for ULSI may well increase dramatically from its present few per cent.

Once this has occurred some optical integration may well be necessary in terms of optically induced Wavelength Division Multiplexing both at the inter-chip level and ultimately at the intra-chip level to avoid information bottlenecks.

To further hybridise optics with this ULSI will not be easy but as long as the optics researchers can produce an easy 'bolt-on' for what the electronics engineers are already making, the possibility of 'doing business' between the two groups must exist, and this is an exciting prospect especially with the eventual prospect of all optical hardware somewhere in the overview.

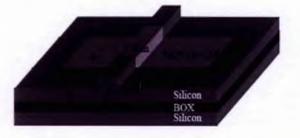

One of the great advantages of SOI from the point of view of Silicon Photonics is the large difference in refractive index between the Buried oxide (BOX) layer of Silica and the surrounding Silicon. This means that with a waveguide above the BOX a very high degree of optical confinement may be achieved. This gives rise to the possibility of considerable miniaturisation compared with other forms of guiding and this can improve device performance and cost efficiency [17].

Wavelength Division Multiplexing (WDM) has long been recognised as being useful in terms of addressing the need for increasing bandwidth in the telecommunications sector since it means that several signals can be sent down the same optical fibre. One way of providing the multiplexing and demultiplexing that is required for WDM is to use Bragg Gratings at each end, whether it be of a fibre or a waveguide connection. More attention is being placed on systems where WDM takes its place as a part of an all optical network since it was to be expected that this would result in speed and bandwidth benefits.

#### **Bragg Gratings**

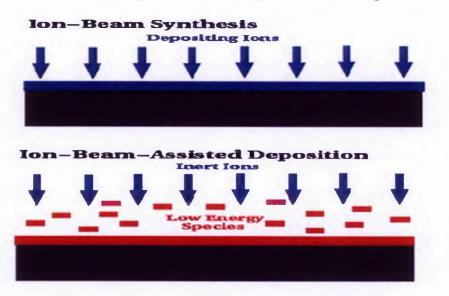

Some of the above WDM components such as add-drop filters, wavelength routers, Fabry-Perot cavities and tuneable filters can be achieved using Bragg Gratings and it is the purpose of this project to design, fabricate, test and characterise flat surfaced Bragg Gratings in SOI. Two different techniques have been chosen for this and an attempt at comparison will be made.

#### **Project Overview**

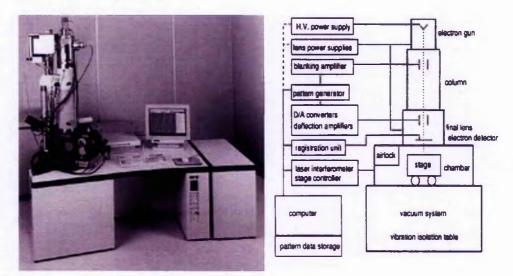

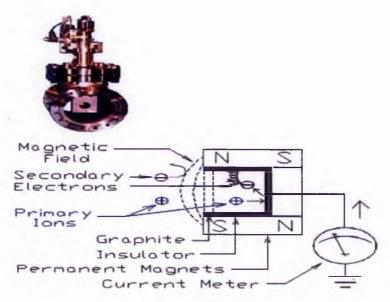

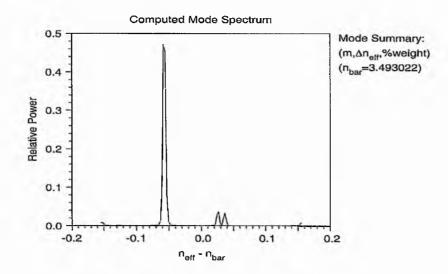

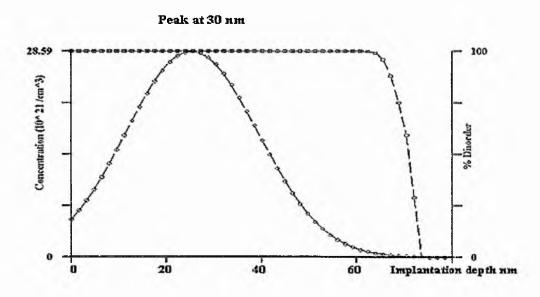

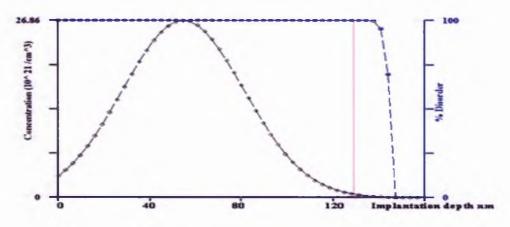

I started my project by examining the propagation of light down a rib waveguide using Beamprop <sup>TM</sup> by way of simulation. Also using simulation, modality was checked for a 1.5 micron rib waveguide with Beamprop <sup>TM</sup> and thirdly the expected reflectivity/transmission from a shallow grating was modelled with Gratingmod <sup>TM</sup>. Beamprop can analyse TM/TE optical propagation down rib waveguides and Gratingmod can analyse optical reflection and transmission down waveguide structures with applied gratings. Both are based upon the principles of coupled mode theory. It became apparent that 75nm of grating depth approximately was required to produce 90% reflectivity and this was modelled using Suspre. Suspre is effectively a graphic representation of skew Gaussian implantation tables derived for various types of ions implanted into different elements or compounds based on the work of Lindhard et al and Dearnalay et al [42 and 43 respectively]. Srim <sup>TM</sup> was also used as a check and this is based upon a Monte Carlo analysis of ion bombardment.

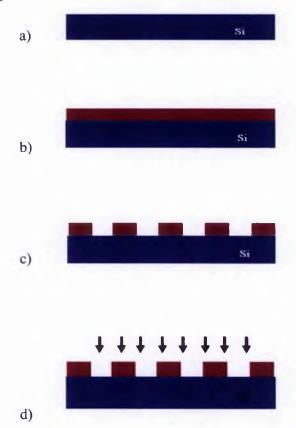

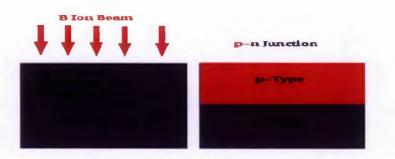

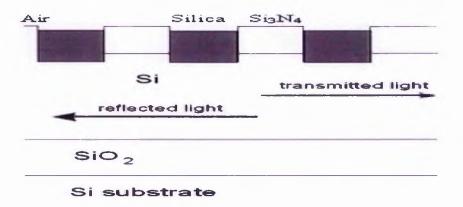

Ordinary Silicon wafers were implanted with Oxygen at Nodus at Surrey University and as-implanted and annealed samples were investigated using ellipsometry which gave evidence of Oxide creation. Two 1.5 micron (1 micron BOX) SOI wafers were obtained and masked, using Silicon Nitride, with a suitable grating pattern at Philips in Eindhoven in Holland. Of these one was ion implanted at Surrey and one was thermally oxidised at Philips to simulate the formation of a flat surface grating by way of porous silicon techniques. This was to try and make a comparison of the two possibilities of fabricating flat gratings in SOI. The wafers were cleaved at Philips to provide planar surface gratings which were then investigated at Surrey.

#### **Chapter Layout**

This thesis is organised into the following chapters describing the design, fabrication and measurement of first order gratings on 1.5 micron SOI.

Chapter 2 will provide a review of differing Bragg Grating filters especially implemented on waveguide structures, as well as reviewing situations in WDM, Ion Implantation and Electronics.

Chapter 3 will describe the theory of Bragg Gratings.

Chapter 4 will detail the design and analysis of Bragg Gratings.

Chapter 5 will discuss the different fabrication techniques.

Chapter 6 contains techniques for optimising the results from the grating samples.

Chapter 7 contains the results achieved.

Chapter 8 contains the conclusions from the work relating to the various techniques and recommendations for the future based on the current work.

Chapter 9 contains the suggestions for future work.

Finally Chapter 10 contains the index to all the references in the text and literature review.

## 2 Literature Review

#### 2.1 Silicon on Insulator

Silicon on Insulator (SOI) is a layered structure consisting of a thin layer of Silicon which is created on an insulating substrate which is usually Sapphire or Silicon Dioxide. Thus SOI circuits differ from generic CMOS (Complementary Metal Oxide Semiconductor) circuits in that their Silicon junction is above an electrical insulator. This process reduces the amount of electrical charge that the transistor has to move during a switching operation: increasing speed (up to 15%) and reducing switching energy (up to 30%) over CMOS based chips and hence power consumption.

SOI devices are usually latch up (where both complementary output transistors conduct causing either malfunction or destruction of the device) resistant and there is a reduction in leakage current: very useful for low power circuit design. SOI chips also reduce the soft error rate, which is data corruption caused by cosmic rays and natural radioactive background signals. Finally CMOS chips have impurities: called dopants added to allow for charge storage via capacitance, SOI chips are not doped which reduces the capacitance allowing for faster and cooler operation. (In semiconductor production, doping refers to the process of intentionally introducing impurities into an extremely pure (also referred to as intrinsic) semiconductor in order to change its electrical properties. For the group IV semiconductors such as silicon, germanium, and silicon carbide, the most common dopants are acceptors from group III or donors from group V elements (Group number refers to the Roman numerals of the columns in the periodic table of the elements). Boron, arsenic, phosphorus and occasionally gallium are used to dope silicon. Boron is the p-type dopant of choice for silicon integrated circuit production, since it diffuses at a rate which makes junction depths easily controllable. By doping pure silicon with group V elements such as phosphorus, extra valence electrons are added which become unbonded from individual atoms and allow the compound to be electrically conductive, n-type semiconductor. Doping with group III elements, such as boron, which are missing the fourth valence electron creates "broken bonds", or holes, in the silicon lattice that are free to move. This is electrically conductive, p-type semiconductor.)

Silicon on Insulator dates back to the early 1960's with the first development of Silicon on Sapphire (SOS) [18, 19].

Silicon on Sapphire is a hetero-epitaxial wafer that consists of a thin layer of Silicon grown on a Sapphire wafer using Chemical Vapour Deposition (CVD) epitaxial method where the Silicon atoms are assembled one by one on the surface of the Sapphire wafer. Because the crystal structure of Silicon is similar to Sapphire (non-conformity between the crystal lattice of silicon and sapphire being circa 12.5 % [18, 19]) the SOS structure appears to be one crystal with a strong molecular bond between the two materials.

SOS is a part of the Silicon on Insulator (SOI) family of CMOS (Complementary Metal-Oxide Semiconductor) technologies. Initially the SOS technology was developed for use in military and space applications requiring high temperature and 'radiation hardened' chips. But commercial use of them started from when the first CMOS circuits were formed. A typical manufacture of SOS would involve the growth of high purity artificial Sapphire crystals. The Silicon is then deposited by the decomposition of Silane gas (SiH<sub>4</sub>) on heated Sapphire substrates. Silicon on Sapphire is popular with radiation hard applications in the military and aerospace industries. Apart from the expense, the electrical properties of SOS have a tendency to degrade as a result of the high dislocation density due to the lattice mismatch between the Silicon and the Sapphire hence SOI designers looked to alternatives for the top end market.

Today bulk silicon CMOS technology is the dominant semiconductor technology for microprocessors, memories and Application Specific Integrated Circuits (ASICS). The main advantage of CMOS over other technologies (e.g. Gallium Arsenide and bipolar technology) is the much smaller power dissipation and especially when static: power is only used during switching and this allows for more gate integration on a single I.C. and thus better performance.

#### Wafer Bonding

Silicon wafers can be bonded together. This provides a route to fabricating SOI structures. The wafer which will ultimately become the substrate is oxidised, creating

the desired BOX thickness. A second (donor) wafer which will ultimately become the site for active devices is pressed into close contact with the first wafer and the sandwich is heated in a furnace. Bond strength generally increases with temperature. Finally the second wafer is thinned to leave a final Silicon layer of the desired thickness. This thinning can be done in several ways. A major amount of Silicon from the donor wafer can be removed by etching or grinding. Etching may be rendered selective by implanting an etch stop prior to bonding.

#### **BESOI** (bond and etch back SOI)

Besoi was introduced in the early 1970s and involves the oxidation of the surface of two silicon wafers, the formation of a chemical bond between the matching oxide faces and the etching and polishing of the top wafer to give the SOI [20]. Wafer bonding is the preferred means of producing thick SOI: where the BOX and Silicon over layer are thicker than 1 micron [20].

#### Smartcut

The favoured manner to create SOI material through wafer bonding makes use of mechanical stress to cleave the undesired portion of the donor wafer.

A silicon wafer is taken and thermally oxidised. Next hydrogen is implanted at high density (c.  $10^{17}$  cm<sup>-2</sup>) at a depth beneath the oxide layer. Finally the wafer is bonded to a second wafer and thermal processing is undertaken at 600 and 1100 degrees C to split the first wafer at the hydrogen implanted depth and improve the bonding between the two wafers [20]. Polishing may be necessary after cleaving to restore flatness.

#### Simox

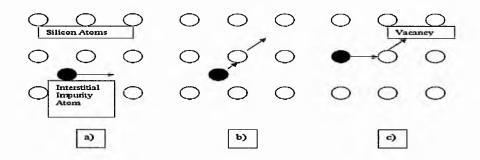

Silica was inexpensive but difficult to bond to Silicon due to crystalline differences until the development of Simox (Separation by IMplantation of OXygen). Oxygen can be implanted at high energy into a Silicon substrate at a high enough dose that subsequent high temperature annealing forms an Oxide layer underneath the surface layer of Silicon with both layers forming a molecular bond. The Oxide is an insulator thus producing the Silicon on Insulator structure. This is especially of use for thin SOI material (where BOX and Silicon over layer thickness is less than 1 micron). Ion implantation of Oxygen or Nitrogen into Silicon at doses high enough to produce stoichiometric Silicon Dioxide and Silicon Nitride has been reported since the 1960's (Watanabe and Tooi 1966 and Pavlov and Shitova 1967 [21, 22]).

Such implants require extremely high doses compared to implanting dopants. For example to dope Silicon heavily requires a volume concentration of  $10^{18}$  ions cm<sup>-3</sup>, which substitutes one dopant atom for roughly 1000 Silicon atoms. For typical I.C. dimensions this requires a dose per area of  $10^{15}$  ions cm<sup>-2</sup>. In contrast a stoichiometric Oxide dose would be 1000 times greater [23, 24].

The structure resulting from such a high dose implant of Oxygen depends strongly upon the dose and energy of the implant and the temperature of the wafer during implantation. As the dose increases Oxygen builds up to the solubility limit. Further increases result in the formation of disconnected islands of Silica [23, 24]. These islands may form at the surface (lower implant energy) or below the surface (higher energy).

In conventional ion implantation the ions damage the Silicon crystal structure, typically heavy doping is capable of creating a crystalline to amorphous transition. As a result, following implantation the wafer is annealed at temperatures of 900 to 1100 degrees and the crystal structure is re-established by a process called Solid Phase Epitaxy (SPE). This process is driven by the lower free energy of the crystalline state compared to the amorphous, and depends on the presence of a crystal template (the deeper bulk Silicon) in intimate contact with the by now amorphous surface layer. However with Simox the BOX prevents SPE and so the damage caused by the implant must be healed (at least in part) during the implantation. This is achieved by performing the implant at about 500 degrees. The over layer contains significant damage but this can be corrected by subsequent annealing.

In 1978 Izumi, Doken and Ariyoshi of NTT fabricated a CMOS ring oscillator on SOI material prepared by implanting  $O^+$  ions into Silicon [25]. They named the SOI material Simox. By 1982 NTT had demonstrated a 1k SRAM on Simox. A high current implanter was developed also in the late 1970's making Simox development

easier. This was followed by an improvement in annealing techniques. Also a gradual take-up by some of the famous names in electronics occurred as well as interest in terms of integrated optics [24]. Annealing at 1300 degrees was found to result in a flatter interface to the BOX. Also the structure of the Silicon over layer is improved [23, 25].

Optical annealing at 1405 degrees [26] improves these features further. Both the mobility and the solubility of Oxygen in Silicon increase with temperature. Small Oxide precipitates dissolve as the annealing temperature increases: tending to condense on the larger precipitates, an example of a process called Ostwald ripening [27]. At sufficiently high temperatures the only precipitate surviving is the BOX. To minimise the free surface energy the interface between buried Oxide and Silicon becomes planar and smooth.

The reason such a structure is of value in fabricating integrated circuits is that individual transistors can easily be isolated from each other and from the bulk substrate. Without the Buried Oxide (BOX) each transistor is connected to its neighbours and to the substrate electrically. While this electrical coupling can be minimised by careful doping to minimise electrical leakage currents, nevertheless there remain a variety of parasitic loss mechanisms. Replacing these back biased junctions with an insulator improves the isolation very significantly and several benefits accrue. First, it becomes easier to reduce transistor size and increase packing density since junction isolation requires wasting space. Furthermore with the most common transistor configuration CMOS latch up can occur; with close packing SOI makes this impossible. Second, once the transistors are well insulated from the substrate soft errors resulting from the adsorption of ionising radiation are reduced by many orders of magnitude. The reason is that the active Silicon surface is typically 0.2 micron thick compared to the 600 micron thickness of the substrate. In circuits constructed on bulk Silicon the carriers created by adsorption of jonising radiation anywhere in the substrate may diffuse into the active circuit. In circuits constructed on SOI only those carriers which are generated in the top active layer affect the circuit and a thin active layer minimises the problem. Thus SOI found an early market in military and aerospace applications. Third, because the transistors are better isolated from the substrate parasitic losses are reduced. This enables higher speed operation at lower power consumption. This speed/power consumption advantage opens three very high volume consumer applications. One is communications equipment where the SOI speed advantage can substitute for some more expensive alternatives such as Silicon/Germanium or Gallium Arsenide for high frequency applications. A second is microprocessors for portable battery operated applications such as lap top computers where the reduced power consumption is critical. A third is in high end microprocessor applications such as network servers because of the speed advantage. Fourth, higher temperature IC operation is possible as a direct consequence of the isolation of the active device area by the BOX from electron and holes thermally generated in the substrate: once again only those created in the thin active region of Silicon affect the circuit.

SOI can be made hybrid with bulk Silicon by local implantation, for example CMOS logic on SOI with power switching on bulk i.e. providing yet further hardware modularisation and integration. Quite apart from electronic applications where the isolation of individual transistors from each other and from the substrate is the primary advantage, SOI technology has found applications in other fields. Since it is possible to etch Silicon and Silica with high selectivity, the presence of a buried Oxide permits one to fabricate complex microscopic three dimensional structures. Two applications for such structures are sensors and integrated optics [28, 29].

#### The Present and the Future

With technologies such as strained Silicon on SiGe on insulator and also sSOI (strained Silicon on Insulator, whereby the process of straining the Silicon increases carrier mobility and therefore improves the high frequency response) currently established as viable present/future options in SOI [30, 31] the future is looking good for SOI. Its increased speed compared with generic CMOS (Complementary Metal Oxide Semiconductor) and lower power dissipation and the other advantages outlined above should ensure increased take-up by industry in the run up to meeting the demands posed by ULSI (Ultra Large Scale Integration).

Strained silicon on insulator is the resultant of combining strained silicon with SOI thus combining the isolation, lower power dissipation and radiation hardening of SOI with the extra speed associated with improved carrier mobility that comes with strained silicon. The imposition of a SiGe layer and with a much thinner silicon layer underneath causes the strain and increases the speed by as much as 30%.

Strained Silicon on SOI provides high frequency benefits up to 30% increase in speed and lowers the output resistance, increasing the drive capability along with the usual SOI benefit of lower power dissipation.

Problems exist with straining such as the fact that holes under strain move at one third the speed of electrons and that Germanium's presence in the strained substrate is undesirable since it causes electrical degradation, however these seem to have been surmounted by the process of local epitaxial straining and the removal of the Germanium in the case of sSOI to leave strained Silicon on Silica. To date it is possible to retain the strain in the strained Silicon over layer to 70nm depth but no further and this will present logistical problems in terms of hybridising with Silicon Photonics but these are likely to be less significant than with other alternatives (e.g. problems with fine machining Lithium Niobate) [32, 33].

Companies of the calibre of IBM, AMD and Intel [34, 35, and 36] are pursuing an interest in sSOI and it cannot be long before market developments in consumer electronics occur and ensure its take up and have the predictable effect on SOI's section of the semiconductor wafer market with the knock-on reduction in SOI wafer unit cost. Attempts at updating SOS have been made [19] but these will still have the disadvantage of poorer integration possibilities and Sapphire degradation and SOS's high speed advantage has been all but wiped out by sSOI etc. The majority of the market is affected by companies of the order of Intel and TI but with modern integration requiring speeds of 4GHz and up, as well as the advent of 65nm process technology sSOI can provide the hardware whilst reducing problems with on-chip power dissipation and heat due to its low capacitance format. It is the author's contention that it is only a matter of time before SOI's ( in one form or another) market share is considerably boosted due to the need for further/higher levels of integration and speed and the low power dissipation in SOI. Inter chip and intra chip communications can be achieved using WDM and two Bragg Gratings. From the author's perspective developments in electronics and research in Silicon Photonics are at an interesting stage and the coincidental breakthroughs in both areas of research could well see an early turning to hybrid Electronic/Silicon-Photonic devices to assist with speed/integration problems.

#### 2.2 Surface and Buried Layers in Silicon by means of Ion Implantation.

#### 2.2.1 Surface Layers

The formation of Silicon Dioxide by ion beam implantation into Silicon surfaces goes back to the 1960s.

Watanabe and Tooi [21] reported the creation of a surface layer of Silicon Dioxide after implantation of low energy reactive oxygen ions. They used p-type Silicon wafers with resistivity of 100 ohm-cm. The ion beam was accelerated to 60 keV. This gave a penetration depth of approximately 0.12 micron after irradiation with a current density of  $20\mu$ A/cm<sup>2</sup> for 200 minutes at sample temperatures ranging from room temperature to 300 degrees Celsius. They further proposed that if the ion energy was increased it would be possible to create a buried Oxide layer. The significance of this work is mainly the initiation of SiO<sub>2</sub> synthesis by ion implantation. Table 1 shows their comparison of IR absorption peak, Dielectric strength and constant and resistivity at 300 degrees K between their 150nm ion implanted film and thermally grown oxide and shows that with the exception of dielectric strength their oxide formed by ion bombardment was of similar quality to thermally grown oxide generally accepted at that time to be the best available silica.

|                                  | Ion Implanted Oxide | Thermal Oxide |

|----------------------------------|---------------------|---------------|

| IR Absorption Peak (µ)           | 9.4                 | 9.3           |

| Dielectric Strength (10^6 V/cm)  | 7                   | 8.5           |

| Dielectric Constant (300 degrees | 3.9                 | 3.2           |

| Absolute at 1 kHz)               |                     |               |

| Resistivity at 300 degrees       | 10^17               | 10^15~10^17   |

| Absolute (Ohm-cm)                |                     | :             |

Table 1 shows a comparison of thermally grown and implanted films [21].

Pavlov and Shitova performed similar work [22]; implanting into the (111) surface of n-type Silicon with a resistivity of 1 ohm cm. However, they gave no details on implantation dosage or energy. They reported on the formation of a surface Silica layer with the possible presence of Silicon and Silicon Monoxide.

Dylewski and Joshi created stoichiometric Silica by high dose  $O_2^+$  implantation into Silicon wafers [37] and found that Infra Red (IR) transmission spectra consistent with SiO and SiO<sub>2</sub> were obtained depending on the ion dose ( the latter at a dose of  $10^{18}$ ions per cm<sup>2</sup> at 30keV). Post implantation annealing was found to release a substantial amount of bond strain and also rendered the Silica layers impervious to water attack. This was thought to be due to polymerisation of the SiO<sub>4</sub> tetrahedra, therefore reducing the porosity. In some previous papers there had been some ambiguity over what existed in the surface implant i.e. Silicon, Silicon Monoxide and/or Silica. This paper suggested that this may have been due to ion implantation dose variations.

The authors demonstrated the quality of their work by carefully defining their implantation parameters, which may well not have been well defined in earlier low dose ( $<<10^{18}$  ions/cm.<sup>2</sup>) surface layers created by implantation and by demonstrating that Silicon Monoxide and Silicon Dioxide were obtained in the surface layer dependant on the dose of Oxygen implantation ions and obtaining results consistent with their theory by both infra red transmission techniques and electron microscope reflection diffraction studies on their samples [38].

The same authors [39] implanted  $O_2$  ions at 30keV and ion beam current density about 15 microampere/cm<sup>2</sup> and 10<sup>18</sup> ions/cm<sup>2</sup> found that the dielectric breakdown properties of Silica films formed by implantation were similar to those created by thermal oxidation of Silicon but found a time dependence of the breakdown process and attributed this to Sodium ion contamination in the formed Silica films, unfortunately they gave no indication as to how the contamination had occurred.

At low current to voltage values the characteristics were ohmic (resistive) and at higher values the characteristics followed a power law consistent with space charge limitation. Annealing increased the resistivity of the films and moved the knee of the ohmic/space charge I-V characteristic to lower values and increased the slope of the space charge curve. Annealing also reduced the dielectric breakdown resistance and reduced polarity dependence of breakdown, possibly due to shrinkage reducing overall breakdown levels and Sodium ion dispersion within the crystalline structure, respectively.

Badawi and Anand [40] formed stoichiometric Silica in Silicon using  ${}^{32}O_2^+$  ion implantation (i.e. implanting molecular, positively charged Oxygen at an atomic mass

unit of 16 since e.g. 18 can be used to create an Oxide marker layer). After annealing they found that the high dose implant produced a surface layer of Silica whereas the medium and low doses produced buried layers (high being 7, medium being 4 and low being  $2.5 \times 10^{22}$  ions/cm<sup>3</sup>: peak volumetric concentrations of ions, the area dose being approximately  $10^{17}$  O<sub>2</sub> ions/cm<sup>2</sup>). The thickness of the films was found to be greater than that predicted by the theory derived by Lindhard, Scharff and Schiott [41] and tables provided by Dearnalay et al [42]. This was attributed to enhanced diffusion during subsequent annealing and also preferential diffusion to the surface. Surface state effects were reduced to a similar level as observed in thermally grown Oxide by two stages of annealing at 750 degrees C and 900 degrees C for one hour.

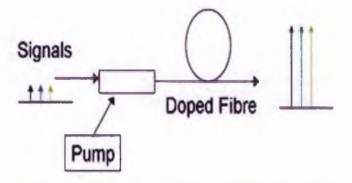

Figure 3 Transmission IR spectra for Badawi and Anand's 50 keV implants for the low dose curves A-High dose curves C, a) as-implanted, b) annealed at 450 degrees, c) 600, d) 750 and e) annealed at 900 degrees and finally the curve marked D in e) for a thermally grown Oxide of thickness 200nm [40].

The infra red transmission is shown in figure 3 and shows a progressive improvement in comparison with thermally grown oxide curve D in section (e) of figure 3 as the annealing temperature is raised. Oxide thickness was confirmed with ellipsometry and quality from C-V measurement. Gill and Wilson [43] observed using Rutherford Back Scattering (RBS) that monocrystalline Silicon implanted with Oxygen at 40 and 60 keV penetrated to a similar depth for the same energy for varying ion doses but that at about 0.75 x  $10^{18}$  ions/cm.<sup>2</sup> and above the RBS spectra demonstrated a saturation situation similar to that obtained with thermally derived Oxide RBS spectra. They determined this saturation occurred when  $n_0/n_{si} = 2$  (where  $n_0$  is the number of Oxygen atoms present and  $n_{si}$  is the number of Silicon atoms present). The Oxygen then appears to undergo radiation enhanced diffusion which would explain, for example, the fact that the region between the peak and the surface was fully oxidised.

#### 2.2.2 Buried Layers By Oxygen Implantation:

Izumi at al [25] formed buried layers of Silica by atomic ion implantation since this was more energy efficient in terms of buried layer formation than molecular Oxygen (using 150 keV and a dose of 1.2 x  $10^{18}$  ions/cm.<sup>2</sup>) to give a Buried Oxide (BOX) layer at a depth of 370nm, and sufficient Oxygen to form stoichiometric silica after annealing. Oxygen and Carbon were seen at the surface of the specimen but unfortunately no reasons for the contamination were given and Carbon contamination is not reported by subsequent authors with respect to buried layers. The layer was 210nm thick. Dislocation and stacking faults were formed at the surface of the Silicon top layer when Oxygen and Carbon contamination was high and for this reason the substrate surface was removed before growing a layer of epitaxial Silicon. The authors' intention in this work was to create a material system which allowed electrical isolation for electronic components fabricated at the surface. To demonstrate this, they created a CMOS/SIMOX (Complementary Metal Oxide Semiconductor/Separation by IMplantation of OXygen) ring oscillator benefiting from total dielectric isolation, which in turn exhibited twice the speed of bulk Silicon devices of the same size. Hence this work became the benchmark for future SIMOX work.

Hemment et al [45] produced buried Oxide layers by implanting doses in excess of  $1.4 \times 10^{18} \text{ O}^+$  ions/cm<sup>2</sup>. They found that an implantation temperature of 400-500 °C and a furnace anneal at 1150 °C for 2-4 hours were necessary to reduce implantation damage and create mono-crystalline Silicon at the surface. However, the 1150 °C

anneal still left some Silica grain boundaries and this resulted in higher leakage currents at +/- 10 volts DC.

Jaussaud et al [46] reported the creation of buried Oxide layers in Silicon by implanting  $O^+$  ions at 3 x  $10^{18}$  ions/cm<sup>2</sup>. They observed threading dislocations at a concentration of  $10^{10}$  per cm<sup>2</sup> in the top layer of Silicon, as well as Silica precipitates. The latter were mainly removed by annealing at 1150 °C for two hours, this increasing the size of the Silica layer and the authors concluded that a much lower dose would have sufficed.

Celler et al [27] reported a 1405 °C irradiative anneal which almost took the Silicon back to its melt temperature of 1412 °C, which removed both defects and Silica precipitates untouched by lower temperature anneals. This resulted in a single crystalline homogeneous Silicon layer with sharp interfaces.

Van Ommen et al [47] and [48] and Stoemenos et al [49] had worked on Silica precipitates in buried Oxide layers and concluded that there was an effective method of Silicon interstitial migration during implantation which must be athermal.

Also Van Ommen et al [47] observed the creation of a Silica super-lattice with time invariant beam current as this had the virtue of almost zero threading dislocations (as observed by transverse electron microscopy) in most of the Silicon over-layer with some remaining near to the buried Oxide layer surface, obviously this would be a matter of interest if the utmost purity were required in the mono-crystalline over layer. Performing the same experiment but with a time variant beam current did not result in the formation of a super-lattice.

Olego et al [26], using Raman spectroscopy (by shining 413.1 nm laser light into the uppermost Silicon over layer of Silicon on Silica structures and observing the varying red Stokes shifts in the Raman spectra), found tensile strains between the various layers in re-crystallised Silicon layers (annealed after implantation), which they attributed to the Silica precipitates. The degree of strain varied from maximum in the as-implanted state decreasing with anneals at 1100, 1200, 1300 and 1405 °C (lamp annealed) with the Silicon annealed at the latter temperature being virtually indistinguishable from virgin Silicon. From the Stokes red shifts, strains of 11.3 kbar were found in the sample annealed at 1100 degrees, 3.3 kbar at 1200 degrees and 1.5 kbar at 1300 degrees, with zero in the lamp annealed sample (1405 degrees).

Duncan et al [50] studied Silicon on Insulator (SOI) using photoluminescence (PL), and found that etch pit counts and defect concentrations decreased with increasing anneal temperature up to 1275 °C. Photo Luminescent defects in SOI are similar to those in Czochralski grown, and plastically deformed Silicon.

Narayan et al [51] found that by implanting at optimum substrate temperature (475-540 °C) and subsequently annealing at 1300 °C for 3-6 hours, dislocation densities in the top Silicon layer could be minimised to about  $10^{5}$ /cm<sup>2</sup>.

Reeson [52] found that Oxygen implanted into Silicon above a critical value which can be defined as that for which the maximum concentration of implanted species achieves a volume concentration appropriate to the stoichiometric compound and forms Silicon Dioxide. The value required depends on the ion species and target material and for 200keV atomic Oxygen implants into Silicon is  $1.4 \times 10^{18}$  ions/cm<sup>3</sup> and forms stoichiometric Silica whereas Nitrogen implantation results in the formation of a non stoichiometric end products, but different rates of redistribution apply for Nitrogen or Oxygen. The crystallinity of the silicon over layer is restored by annealing for both Nitrogen and Oxygen implanted buried layers. With Oxygen this is caused by precipitate dissolution whereas with Nitrogen it is caused by defect annealing and re-crystallisation.

Bussmann et al [23] confirmed the implantation and annealing parameters i.e. Oxygen doses at 0.4, 1.8 or 2.2 x  $10^{18}$  atomic Oxygen ions/cm<sup>2</sup> with an implantation temperature of 500 degrees C. and annealing at 1300 degrees C. for up to 5 hours or 1350 for 4 hours. Also they achieved total dielectric isolation of the top Silicon layer by enclosing it in Silicon Dioxide and they demonstrated very well the progressive absorption of the lower Silica islands with progressive annealing temperature and time to give a smooth and linear lower Silicon Dioxide surface.

Blake [24] pointed out that the structure resulting from a high dose Oxygen  $(10^{18} \text{ ions/cm}^2)$  implant depends strongly on the dose and energy of the implant and the temperature of the wafer during implantation. His report gave a good historical overview of oxygen implantation into silicon as well as annealing and a good account of optical annealing. Figure 4 shows a transmission electron microscope image of a

cross section of a Simox wafer showing from the top the silicon over layer, the buried oxide layer and the silicon substrate.

Figure 4: Shows a Simox XTEM cross section with the silicon over layer on top and BOX (buried oxide layer) in the middle and substrate underneath [24].

As Oxygen is implanted the dose builds up to the solubility limit, and any further increases result in the formation of islands of Silica which are initially disconnected. These islands may form at the surface (lower implant energy - at about 30-40 keV) or below the surface (higher implant energy e.g. about 200keV for buried layer). Indeed implantation was initially envisaged for replacing thermal Oxidation of Silicon since implantation gives far greater control of doping. Performing the implant at 500 °C gives heating during implantation, and with a surface implant it is possible that solid phase epitaxy will help restore the original silicon crystallinity, which is not possible in buried Oxide formation in a process such as the formation of SIMOX. A good discussion of optical annealing is provided in this paper, demonstrating that it is superior to furnace annealing at 1300 °C if it is available. The author also reports that Silicon tubing was implemented in the first commercial implanters to reduce metal contamination, that threading dislocations could be reduced by several implant and annealing steps, and that channelling (in this case in SIMOX) was reduced by the use of a chopper wheel to minimise beam waggle. Ion selectivity is very important in the implantation apparatus as, for example, two layers could be formed with Oxygen: one for atomic Oxygen ions and a separate layer for molecular Oxygen ions since they would have different penetration depths for the same energy, one being twice as massive as the other.

#### Summary and Conclusion

Oxygen implantation into Silicon is a well established means of forming  $SiO_2$  layers in silicon. The majority of the work has been carried out for buried layers to develop SOI substrates such as SIMOX.

However, significant work also exists related to surface implants. Initial work with surface layers was dogged by problems with dosage, implantation temperature and beam current variation. However, later work produced good quality layers if these parameters were carefully monitored and kept at the right level. Buried Oxide layers always have a problem with threading dislocations and even the best work [26, 27] still gave a level of  $10^5$  /cm<sup>2</sup> in the bottom third of the Silicon over layer, which may not be a problem for Mosfet designers but would conceivably cause problems for Silicon Photonics for example increasing absorption/scattering problems in rib waveguides and affecting the refractive index. This would be at least one of the reasons for the prevalence of Smartcut in Silicon Photonics [20].

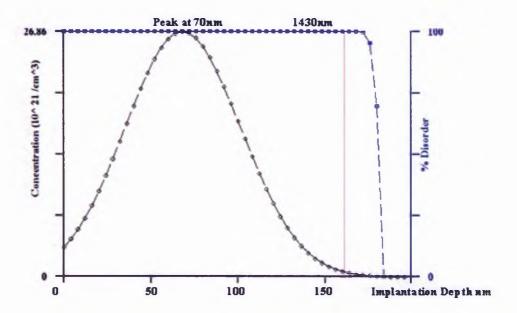

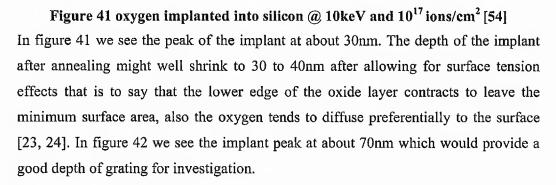

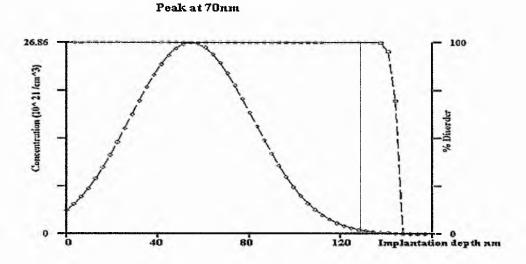

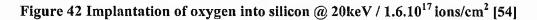

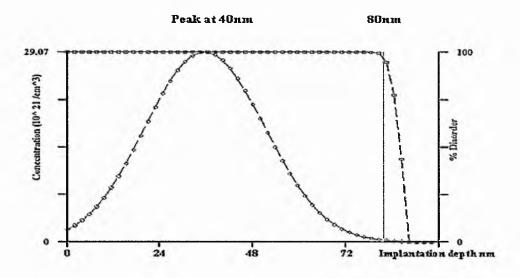

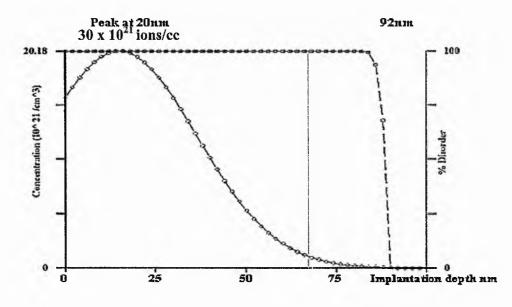

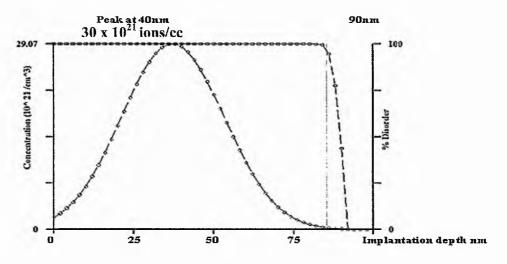

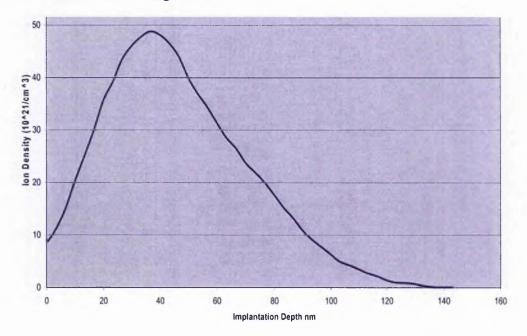

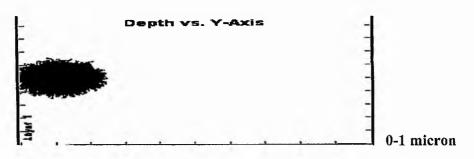

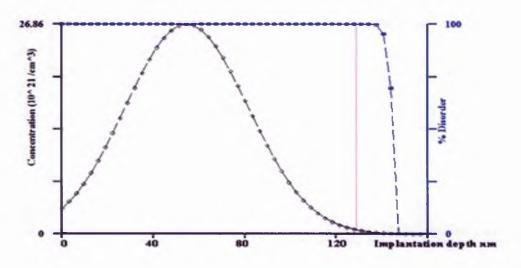

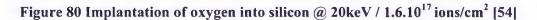

Surface layers of Silica can readily be created in Silicon using, for example, a dose of  $1.6 \times 10^{17}$  ions of O<sup>+</sup> per cm<sup>2</sup> to give a layer depth of 75 nm at 20 keV energy as shown in the Suspre <sup>TM</sup> simulation in figure 5 [53, 54].

Figure 5 shows a plot of oxygen implantation into silicon (20 keV and 1.6 x  $10^{17}$  ions/cm<sup>2</sup> Suspre <sup>TM</sup> simulation.

# 2.3 DEVICES IN INTEGRATED OPTICS WITH RELEVANCE TO BRAGG GRATINGS IN SILICON ON INSULATOR TECHNOLOGY.

#### 2.3.1 BRAGG GRATINGS.

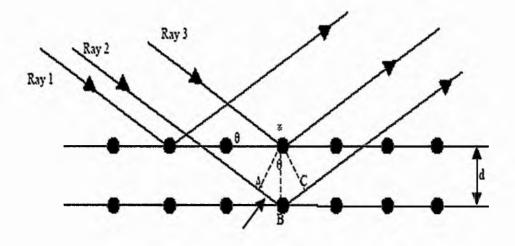

Bragg Gratings were first described by Sir William Lawrence Bragg approximately one hundred years ago. Periodic structures of the order of the wavelength of the diffracting electromagnetic radiation cause changes in the amplitude and phase of an incident beam in accordance with Bragg's Law. Bragg's Law refers to the simple equation:

$$N\lambda = 2dsin(\theta) \tag{1}$$

Where  $\lambda$  is the wavelength of the light, which is incident at an angle  $\theta$  on crystal lattice planes of spacing d. This was derived by the English physicists H.Bragg and his son Sir W.L.Bragg in 1913 to explain why the cleavage faces of crystals appear to reflect X-ray beams at certain angles of incidence, and brought together much thinking about the nature of crystals and lattice planes and the effects thereof on incident electro-magnetic radiation.

Bragg's law is used to determine the structure of a crystal by the angles of the beams of light refracted from it. This observation is an example of X-ray wave interference, commonly known as X-Ray Diffraction (XRD), and was direct evidence for the periodic atomic structure of crystals which had been postulated for centuries. The Braggs were awarded the Nobel Prize in physics in 1915 for their work in determining crystal structures beginning with Sodium Chloride, Zinc Sulphide and Diamond. Although Bragg's law was used to explain the interference pattern of X-rays scattered by crystals, diffraction has been developed to study the structure of all states of matter with any beam, e.g., ions, electrons, neutrons, and protons, with a wavelength similar to the distance between the atomic or molecular structures of interest. Various diffraction orders are created by the constructive interference and these are given by the value of N in Bragg's Law.

#### 2.3.2: Wavelength Division Multiplexing (WDM) Systems.

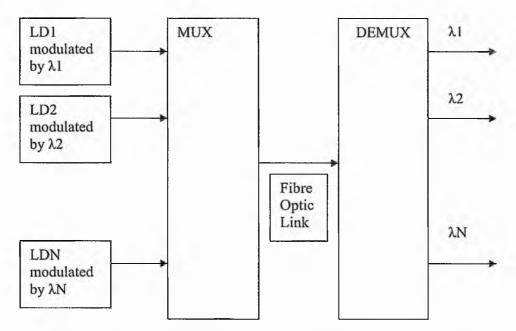

One way of increasing the bandwidth of an existing optical link without modifying the fibre is to employ the technique of wavelength division multiplexing. In this technique (see figure 6) several different signals are transmitted simultaneously down the fibre on carriers of different wavelength: the signals coming from laser diodes of different frequency then fed into different modulators (whether amplitude, frequency or code modulation). The modulated signals are then combined in the multiplexer before sending down the optical fibre. At the receiving end the signals are then separated into the different frequency components by the de-multiplexer.

Figure 6 Block diagram of wavelength division multiplexing system.

The main difficulty is in separating the signals at the detector; inevitably, both signal loss and a certain amount of cross talk between the signals are experienced. Several possible methods of signal separation have been proposed [55] such as the use of a prisms or Arrayed Waveguide gratings. Another possibility is to use a diffraction grating to produce the same effect. Kintaka et al [57] have fabricated an optical waveguide demultiplexer for two-wavelength channels from guided waves to free space waves. The waveguide demultiplexer consisted of two types of gratings, i.e. Guided Mode Selected Focussing Grating Couplers and Different Guided Mode-Coupling Distributed Bragg Reflectors (GMS-FGCs and DGM-DBRs). The

wavelength demultiplexing with 5nm spacing was experimentally demonstrated. Experimental work is being continued to improve device performances such as output efficiency, wavelength selectivity and propagation loss. An add-drop multiplexing device is also under study [57]. This work is not done in SOI and could not easily be transferred to SOI without the provision of high quality relevant Bragg Gratings but nonetheless proves how extremely useful this technology is and especially at a time when on chip WDM technology is becoming necessary to avoid information pile-up between information processing and storage "nodes". It is exactly this sort of application that makes the provision of quality Bragg diffraction gratings a matter of interest to optics designers. Wavelength Division Multiplexing (WDM) operates on the principle of combining different optical wavelengths of light and sending these down an optical fibre. Obviously if N (c.f. figure 6) different wavelengths are combined (multiplexed) at the sending end and de-multiplexed at the receiving end the bandwidth is increased by a factor of N [58]. Dense Wavelength Division Multiplexing (DWDM) was developed with a capacity of 64 to 160 parallel channels at 50 or even 25 GHz intervals and spacing of the order of nanometres. Coarse Wavelength Division Multiplexing (CWDM) comprises up to 18 wavelengths in the range 1270 to 1610 nm spaced by 20 nm [59].

### 2.3.3 FABRY-PEROT EFFECT AND APPLICATIONS

The Fabry-Perot phenomenon is based around the provision of two planar mirrors with a transparent medium between for example the Helium Neon laser with the gas in a container, and external optical excitation and a silvered/semi silvered mirror to provide the 633nm output. (What is a matter of considerable interest to silicon photonics engineers is the development of a silicon laser. The usage of a 100% reflecting Bragg grating at one end of a rib waveguide and the partial reflecting Bragg grating at the other end provides a part of the solution, but the rest is the stuff of Nobel prizes). This creates a situation where only light which has a wavelength which is an integral dividend of the spacing between the mirrors resonates: all other wavelengths decay in the cavity. In SOI (Silicon on Insulator) these mirrors may be replaced by Bragg Gratings since a Bragg grating is a filter/reflector and can be used in a Fabry-Perot and hence many of the following devices may be replicated in SOI.

Over the last 40 years or so a number of devices have been proposed using this technique: not just in terms of lasing but also in terms of interferometers and filtering where only the correct wavelength of light constructively combines in the interferometer or only the correct wavelength of light traverses the filter. These devices are a matter of interest in terms of SOI since like the Distributed Bragg Reflector (DBR: [60]) they may possibly be analogized by Bragg Gratings in the place of the mirrors and semiconductor material in the place of the cavity filling. Also if the Bragg Gratings could be tuned in terms of frequency response then the laser, interferometer or filter could be of a variable nature yet further increasing its usefulness. Bragg Gratings in SOI are a plausible solution to this technological challenge. Two possible techniques exist for the tuning of variable Bragg filters one is to thermally control the gratings in which case a flat surface would be helpful in terms of heat transfer and the second is electrical as proposed by Cutolo et al [61]. Although the latter is only a theoretical treatment simulated in Medici TM and could do with experimental verification. Some interferometric applications are described in the following although it should be said that the fundamental effect of the Fabry-Perot is to act as a filter and again the Bragg Grating has the same function so many analogues should be possible.

**(a)**

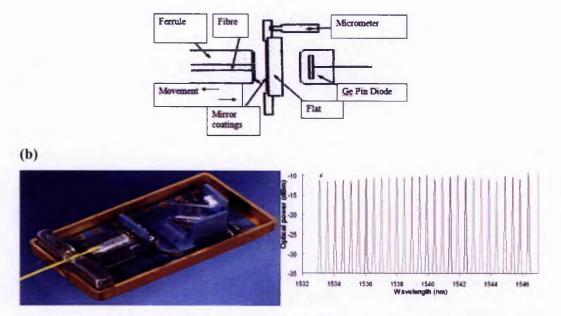

Figure 7 (a) Fibre coupled Fabry-Perot interferometer [62] and (b) industrial usage thereof by way of VTT ELECTRONICS [62]

The Fibre coupled Fabry-Perot interferometer (FCFPI) shown in figure 7a) consists of a single mode fibre mounted within a connector ferrule [62]. The end face is polished and a broadband multilayer dielectric reflection coating deposited by vacuum evaporation. The cavity is tuned by moving the fibre end axially using a piezoelectric electromechanical transducer. A cavity gap of 6 micron produced a FWHM line-width of 5nm, a FSR (free spectral range) of 180nm at 1.5 micron and etalon finesse of 37. To tune the pass band over the FSR, the cavity gap is changed by only half a wavelength. Its main limitation is the degradation in performance produced by the divergence of the beam in the optical cavity. An example of industrial use is given in figure 7b) showing a tunable laser module, and single mode tuning from 1533nm to 1547nm by changing the piezo-electric voltage from 60 volts to 24 volts respectively. To enable investigation of cascaded FPI, micro-optic bulk FPI devices have been developed [63] and these offer many advantages over the single stage FPI such as improvement in cross talk performance, lower insertion loss and higher finesse.

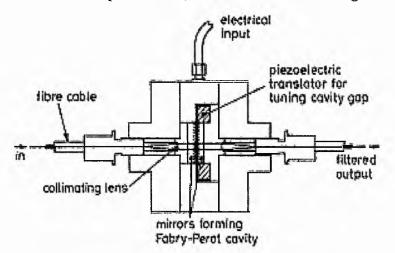

Figure 8 Micro-optic Fabry-Perot interferometer [64].

Figure 8 shows a micro optic Fabry-Perot interferometer (FPI): the incoming fibre is terminated by connector components and coupled to a collimated optimised rod lens [64, 65]. The light then passes through the FPI and is coupled to the outgoing fibre by means of a second rod lens with a piezoelectric actuator controlling the F-P gap.

This device offers a tuning range between 1.25 and 1.53 micron with FWHM line width of 4.7nm. SOI alternatives offer cheaper, more reliable solutions.

#### 2.3.4 BRAGG GRATING TUNEABLE FILTERS

#### (a) Fibre Bragg Gratings

For more than ten years Fibre Bragg Gratings have found increasing applications in Wavelength Division Multiplexing (WDM) communications systems [66, 67]. They help stabilise diode lasers and provide channel filtering for add-drop modules [67]. An optical Fibre Bragg Grating can be made by producing periodic variations in the fibre refractive index along a short section in the core of an optical fibre (often this is done by the usage of photo resist and exposure to a high output laser e.g. the excimer) [66]. This phase grating acts as a band rejection filter, reflecting wavelengths that satisfy the Bragg condition. The first demonstration of fabrication of narrowband high reflecting Bragg Gratings by Hill et al in 1978 [68] with the writing of gratings within fibres has attracted considerable interest. By utilising the sensitivity of the grating wavelength to strain and thermal changes, it can be used to realise sensors and narrowband tuneable optical filters [69-72]. However, the low temperature sensitivity of 0.0125nm/°C [71] severely limits the tuning range. Compressive Bragg grating tuneable filters [73] actuated with a linear motor have been realised by taking into account the good stress and strain properties of Silica optical fibres and the fact that Silica is 23 times stronger under compression than under tension. Tuning ranges of up to 32nm have been reported but the tuning speed was limited to a few seconds [75]. In 1997, locco et al [74] improved the tuning speed into the millisecond region by compressing the Bragg grating with a piezoelectric stack actuator. A tuning range of 15nm and a settling time of less than 2ms were obtained at a wavelength of 1550nm. Such a device is of potential use in wavelength multiplexing or as a wavelength selective filter where tuning speed is crucial. High finesse fibre Fabry-Perot interferometers, (FFP) provide ultra high selectivity but their spectra are periodic in frequency, so the number of supported channels in a WDM line is proportional to the Free Spectral Range (FSR). Fibre gratings provide a true band pass filter but their band pass selectivity is generally lower than that attainable with FFPs. These limitations can be solved using a structure that combines the selectivity of the FFP and the band pass nature of a fibre grating as was theoretically described in [75] by Capmany et al. The first experimental demonstration of the filter operation is

presented [76] and a range of tuning of several hundreds of Gigahertz can be achieved by using a combination of coarse and fine tuning stages, achieving a maximum tuning range limited only by the thermal stability of the grating. Betts et al demonstrated a variable finesse Fabry-Perot Interferometer using Bragg gratings. This was a very sensitive instrument although this is only viable for fibre optics [77].

#### (b) Bragg Gratings in SOI.

An alternative implementation of Bragg gratings is their incorporation into Silicon waveguide structures. In the published literature relating to Silicon, Bragg Gratings are either configured as high reflectivity periodic structures used to improve Fabry-Perot cavity finesse [76] or as part of a hybrid p-i-n modulator which is used to vary the Bragg wavelength and hence the intensity of the propagating light [73].

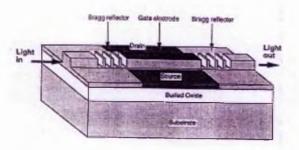

Figure 9 schematic view of the fabry-perot grating waveguide modulator [78].

In figure 9 is shown the classic Fabry-Perot cavity but with Bragg reflectors in the place of conventional mirrors. The application of potentials to the source, gate and drain electrodes will change the cavity characteristics and cause modulation. The authors found that cascading several modulators improved the reflectivity.

As demonstrated by Liu and Chou [78], twelve trenches of Bragg reflectors showed almost unity reflectivity over a 120nm range, centred on 1300nm, for a cavity length of 18.3 micron. The usage of Bragg reflectors to increase the finesse of a Fabry-Perot cavity greatly reduces the modulator size, leading to faster modulator operation. The proposed modulator can also be used as a tuneable spectral filter with a much narrower resonance peak and larger intensity modulation.

Cutolo et al [61] have proposed and modelled a pin diode Bragg reflector integrated into a SOI (Silicon on Insulator) waveguide, with a response time of 12 ns and operating power of 4mW for a 50% modulation depth. Amplitude modulation is achieved by carrier injection changing the refractive index of the guiding layer.

The design of a tuneable filter with the integration of Bragg gratings on a SOI wave guide is very flexible as the reflectivities of the Bragg reflectors can be easily controlled by the number of etch trenches and trench depth [61]. This offers significant advantages over competing technologies such as fibre: facilitating the possibility of mass production and utilising established Silicon technology and has the potential for subsystem integration.

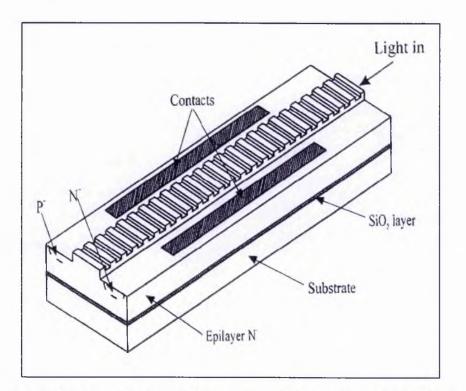

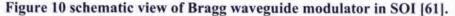

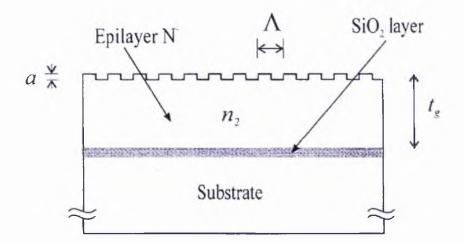

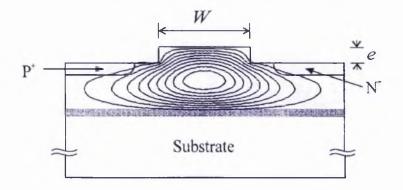

In figure 10 we see the schematic of a Bragg waveguide modulator: when potential is applied to the p and n contacts the refractive index of the guiding layer is changed by way of carrier injection. This then shifts the peak reflectivity of the Bragg mirror to a different wavelength. The longitudinal and transverse sections are shown in figures 11 and 12 and the simulation was run in Medici TM.

Figure 11 Longitudinal section of figure 11 [61].

Figure 12 Transverse section showing contour lines of equal optical field strength [61].

# ARRAYED WAVEGUIDE GRATING TUNEABLE FILTERS

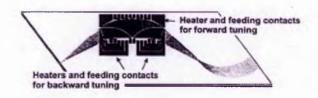

In 1999, Toyoda et al [79] developed a tuneable filter using polymer-Arrayed Waveguide Grating (AWG) demultiplexers with a tuning range of 10nm around 1550nm. Unfortunately the wavelength tuning range is limited and the response is slow due to the slow response time of the Peltier type heater that was used. The same authors improved the tuning range to 20nm and response time of 2-60ms, a cross talk of <-30dB by implementing two different heating structures that allow forward and backward tuning [80]. The structure that they came up with is shown in figure 13.

Figure 13 layout of optical phased array with the heaters on the top [80].

A Thermo-Optic wavelength tuneable filter in Silica on Silicon has been demonstrated using a similar phase shifter [80]. The tuning range was about 6nm because the inherent thermo-optic coefficient of Silica (4.5 x  $10^{-6}$ /K) [81, 82] is smaller than that of polymer  $(-1.6 \times 10^{-4}/\text{K})$  [79]. Trinh et al [83] had demonstrated AWG multi / demultiplexers in SOI. This device has successfully demultiplexed 4 wavelengths centred 1.9nm apart at 1550nm, cross-talk to neighbouring channels was less than -22dB, insertion loss was below 6dB for all channels and a TE-TM shift of less than 0.04nm was demonstrated. Recently, Pearson et al [84] have presented theoretical and experimental results detailing the design and performance of AWG demultiplexers fabricated in SOI. The authors have emphasised that polarisation birefringence can be removed by an appropriate choice of the SOI ridge waveguide width to height ratio [84]. Reactive Ion Etching (RIE) is more a favourable fabrication technique compared to chemical etches because it can produce the precise geometry profiles required for producing a waveguide with zero birefringence. However, ridge waveguides fabricated by RIE may suffer from sidewall roughness if care is not taken. As reported in previous work [85], this sidewall roughness can cause very high losses in small cross section waveguides.

# **ELECTRONICALLY SWITCHABLE BRAGG GRATINGS**

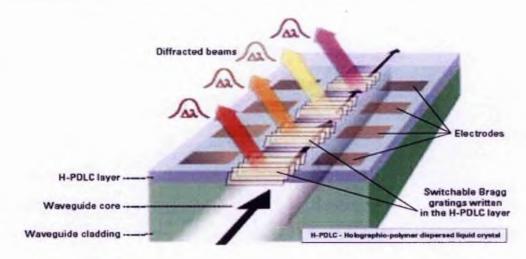

A recent development in the field of Bragg gratings is the Electronically Switchable Bragg Grating [86] this depends on the configuration of a Bragg grating in Holographic Polymer Dispersed Liquid Crystal. A composite electro-optical [87] medium of this nature is called a Holographic Polymer Dispersed Liquid Crystal (H-PDLC). Since H-PDLCs contain liquid crystals exhibiting an electro-optic effect, their periodic structure can be altered or turned on or off by the application of an electrical field. Under these conditions H-PDLCs are generally referred to as Electronically Switchable Bragg Gratings (ESBGs). A schematic of ESBG operation is shown in figure 14 and shows the core, cladding, H-PDLC layer, switchable Bragg gratings, diffracted photon beams and the electrodes used for control.

Figure 14 ESBGs can provide a platform for various WDM functions [86].

ESBGs can be used in grating assisted planar waveguide Mach Zehnder coupled optical add/drop [86] multiplexers / demultiplexers (OADMs). If one has a Mach Zehnder interferometer with ESBGs in both arms then the resonant frequency can be tuned to drop just one channel, if the gratings are electronically erased then the system reverts to an all pass. Due to the symmetry of the device it is correspondingly possible to add as well as drop simultaneously by adding in one arm and dropping in the other providing the full OADM functionality. The placing of additional matched pairs of gratings with different resonant wavelengths would permit the OADM to drop or add several different wavelength channels at once. Channel cross-connecting (i.e. routing signals from individual input ports to one or more selected output ports) is a required function in communication systems. ESBGs allow this function to be implemented in the optical rather than electronic domain, eliminating substantial cost associated with electronic to optical conversion. Optical space switching can be implemented using ESBGs to generate phase delays in phased array planar waveguide structures to build a number of simple switching elements. In summary, liquid crystal replaces fibre cladding, a Bragg grating is recorded on the liquid crystal for each wavelength and the gratings can be switched on and off.

Despite these benefits ESBGs are basically slow, the settling time of 50 microseconds is likely to preclude faster WDM applications and the application is unlikely to be easily compatible with waveguide based integrated optics (a matter of constant concern with optically based SOI is that it should be physically compatible with what the electronics SOI designers are already producing) and this may well limit its usefulness to sensor applications and other fixed device applications where settling time and compatibility were not a matter of the essence. Thus although these devices are very versatile and configurable there must still be a need for fast response variable Bragg Gratings and it would seem as if flat ion implanted Bragg Gratings were becoming one of the major contenders for the solutions to the vacant positions in integrated optics.

### **RECENT DEVELOPMENTS IN BRAGG GRATINGS**

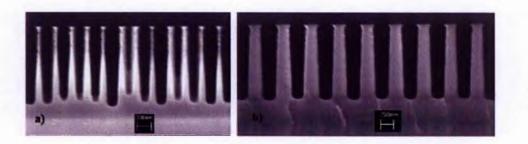

Aalto et al [88] fabricated a corrugated Bragg Grating on a SOI rib and enhanced reflectance by extending the grating to the shoulder of the rib (wide grating structure). Their e-beam writing technique produced some flaws with first order but none with second order gratings and their calculation gave extra reflectance peaks due to higher order propagating modes (see figure 17).

Although they had problems with first order e-beam the technique is promising for higher order gratings in SOI as great quality of documented period is required and quality of maintained periodicity also.

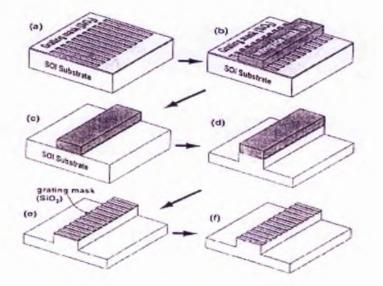

However the gratings are corrugated which limits their application and no experimental results are given. In figure 15 we see the first and second order grating profiles and in figure 16 a schematic of the fabrication.

Figure 15 a) first and b) second order gratings [88].

Figure 16 processing steps in the grating fabrication and the waveguide [88].

Figure 17 Aalto's calculation demonstrated higher order propagating modes i.e. single modality had been lost [88].

Figure 18 wide grating structure [88].

In figure 18 we see the structure of the gratings with the grating extending beyond the top of the rib waveguide and in the simulation (figure17) we see the presence of higher order modes caused by putting a grating on the top of a rib waveguide.

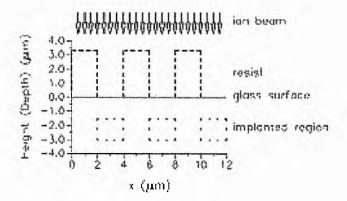

Banyasz et al [89] produced gratings in glass by ion implantation of Helium and Nitrogen. Photo resist was deposited on the glass surface and used as a mask for the implantation as shown in figure 19 in schematic.

Figure 19 schematic of the implantation [89].

Various dose and ion energies were applied and the effective optical path modulation is shown in table 2.

| Number of  | Implanted ion | Energy (keV) | Dose (x 10^15 | D (nm) |

|------------|---------------|--------------|---------------|--------|

| experiment |               |              | ions/cm^2)    |        |

| 1          | Helium        | 500,650,800  | 100           | 120    |

| 2          | Nitrogen      | 500,800,1160 | 15            | 220    |

| 3          | Nitrogen      | 1600         | 40            | 240    |

| 4          | Nitrogen      | 1160         | 10            | 180    |

Table 2 the modulation of the optical path produced by the implantation [89].

These contained gratings caused by index change and by surface relief. The surface relief was estimated from figure 20 to be 300nm for a 2 micron line width. The surface relief was thought to be caused by volumetric changes in the silica or sputtering. The gratings could not be used in SOI firstly as silica would be difficult to transfer to SOI and secondly a 4 micron periodicity implies function outside the telecommunications wavelength range.

Figure 20 scanning electron microscopy of the grating edge [89].

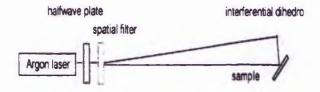

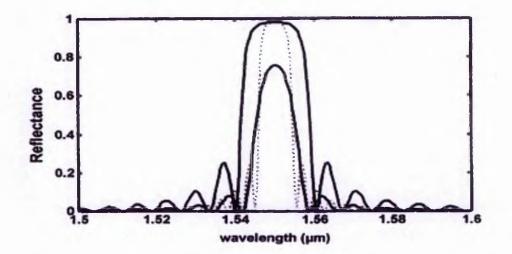

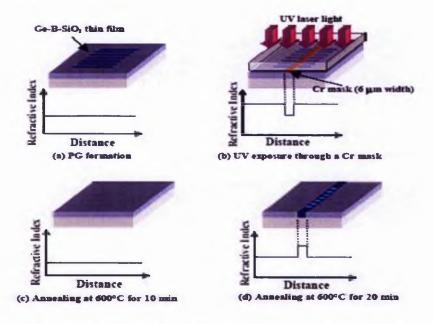

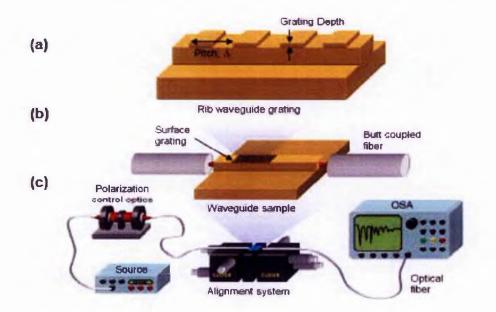

The gratings were not very shallow due to the small changes in refractive index caused by implanting nitrogen into glass. Incorporating into SOI must be a problem since glass was used as the basis for the implantation. Ion implantation into Silicon is better as this can be done straight into SOI and the change in refractive index is about 2 for Silica creation from a Silicon start. Boehme et al [90] presented laser etching of wet Silica to create gratings, again although the fabrication is novel, transfer to SOI is difficult and the gratings are in relief. Ferguson et al [91] present use of Focussed Ion Beam milling to create gratings in fibres; this technique could be modified to create relief gratings in SOI. Florea et al [92] present the interferometric technique using photo-resist for grating manufacture: if this was conjoined with ion implantation rather than etching it could create flat gratings in SOI. Li et al [93] by a two step exposure process created surface gratings in photo-resist obviously this technique could be used to create SOI relief gratings. Moreau et al [94] report the formation of Sol-Gel gratings by holographic interferometry as shown in the schematic of figure 21 where the fringes are caused by recombining the light from an Argon laser onto the sample.