# $\mu {\rm SPIDER}$ CAD TOOL: CASE STUDY OF NOC IP GENERATION FOR FPGA

Samuel Evain, Rachid Dafali, Jean-Philippe Diguet, Yvan Eustache,

Emmanuel Juin

# ► To cite this version:

# HAL Id: hal-00338244 https://hal.archives-ouvertes.fr/hal-00338244

Submitted on 12 Nov 2008

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# $\mu$ SPIDER CAD TOOL: CASE STUDY OF NOC IP GENERATION FOR FPGA

Samuel Evain

CEA LIST CEA Saclay 91191 Gif sur Yvette email: samuel.evain@cea.fr

# ABSTRACT

This paper introduces the  $\mu$ Spider CAD tool for NoC design under latency and bandwidth constraints and describes the different steps of the associated design flow. We show how the tool can be used to automatically generate a NOC IP compliant with Xilinx EDK tool. We present synthesis results and a real implementation of a video application based on a multi-processor architecture. Finally we conclude about research to be done at application/OS levels above current work to achieve a complete and efficient implementation of a multi-processor embedded system.

# 1. INTRODUCTION

The concept of Network On Chip (NoC) has been recently introduced as an alternative to bus in order to solve the tedious issue of emerging system on chip (SoC) interconnect design. Different arguments are commonly forwarded to sustain the interest for NoCs [1] based on packet switching. First the NoC can provide new spatial and time parallelism capabilities to cope with expanding bandwidth requirements and the management of an increasing number of inter IPs communications. It also contributes to raise the abstraction level of design tools for flexibility and productivity improvements. This point is crucial, since the design of complex SoC, implementing tens of processors, IPs and memories, means error prone communication schemes that can be intractable for designers under time to market pressure.

Moreover a NoC is based on physical and logical control flows that offer new opportunities for controlling quality of service including real-time, power and reliability. Finally, NoC intrinsically holds the property of scalability, which is a key point for design reuse and SoC configurability.

Today first industrial solutions [2] are available and ongoing researchs investigate further aspects. One of the research issues in which we particularly focus on is design flow to handle complexity and provide designers with CAD tool. Some equivalent work is proposed in Ætereal [3] for ASIC design. This approach is based on an architecture model and a methodology, which is close to ours but differs at level of mutual exclusions considerations and heuristics choices for path and time slot allocation. There is no real work about a R. Dafali, J-Ph.Diguet, Y. Eustache, E. Juin

Univ. Européenne de Bretagne / CNRS / LESTER lab 56100 Lorient, France email: jean-philippe.diguet@univ-ubs.fr

specific CAD tools for NoC IP generation targeting FPGA. In [4] FPGA are used as a proof of concept independently from any CAD tool. Other work are based on FPGA for emulation purpose in [5] and to speed-up simulation in [6].

To our point of view, the main issue is the productivity gain for implementing complex communication schemes. Our project was, from the beginning, driven by the objective of providing the SoC designer with an ad-hoc component offering services for communication management at application level. To get over this challenge we have designed a CAD tool and a software layer for a simplified access to the communication medium at application level. On the one hand, it is well known that flexibility has a cost. An area overhead mainly due to interface and router FIFOs and an increase of communication latencies due to the path length and packet routing are generally observed. However, the paradigm can take benefit from a rigorous formalization that enables the implementation of efficient automatic methods. We based our framework development on the guaranty of latency and bandwidth requirements at application level while minimizing the resulting NoC cost

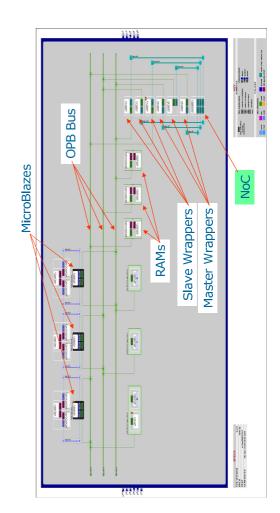

$\mu$ Spider CAD tool for NoC design performs design space exploration and code generation. Design space exploration is implemented in an interactive way based on designer choices for arbiter, routing policies and topology selections. Then automatic procedures are available for time-consuming and error prone tasks such as Time Division Multiplexing (TDM), FIFO sizing and path allocation for guaranteed traffic management. Then based on designer and tool choices, code generation is automatically carried out and can specifically targets Xilinx EDK tool by producing the IP folder including data/IP.mpd and data/IP.pao and /hdl/vhdl/\*.vhd files with the correct format. In this paper we present the  $\mu$ Spider design flow as IP generator for reconfigurable MPSoC implemented on Xilinx FPGA.

#### 2. DESIGN FLOW OVERVIEW

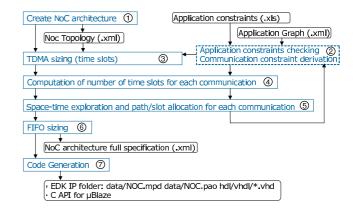

Our NOC model enables the implementation of two kinds of communications: best effort (BE) and guaranteed traffic (GT) based on a TDM technique. Figure 1 gives an overview of the NoC design Flow. An interactive GUI (Fig. 2 helps the designers to easily follow the  $\mu$ Spider design flow.

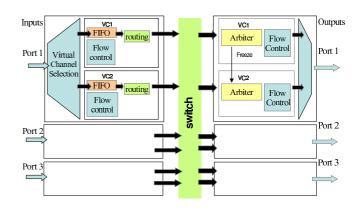

The first step enables the designer to rapidly specify the application and the NOC parameters. The application is specified with a set of characterized communication tasks, with application throughputs (Application Graph.xml) and if necessary with links between mutual exclusive communications (Mutual Exclusion Graph.xml). The NOC knobs are related to the NOC topology which can be ad hoc or automatically generated as 2D Mesh. NoC parameters are specified by the designer, the main ones are: Path bit width (e.g. 32 bits) Router parameters (ports, routing policy, arbiter policy, etc.), Network Interfaces (NI), Flow control policy (with or without End to End flow control) and wrapper (slave, master, bus standard) and the IP mapping namely the IP/NI association. If real-time constraints are required, then related communications are implemented with virtual channel (GT, BE, BE with priority).

The second step deals with derivation of local latency and bandwidth constraints for each unidirectional communication from application I/O throughputs (e.g. telecom chain or image processing). The objective is to extract local latency and bandwidth constraints for each communication task from global I/O application constraints. The important issue, which is usually omitted in NOC design flows, is in practice necessary for applying following steps 3 and 4, which requires constraints for each individual and unidirectional communication. This work is not trivial since firstly different local decisions are possible to meet global constraints and secondly latency, bandwidth and TDM table size are strongly dependent. Moreover read operations imply two types of heterogeneous communications: the read command (request) and the data response for which two distinct set of constraints must be defined. Thus, the second step first transforms communication tasks into unidirectional ones. This aspect is required for read operations that need a lightweight forward communication for sending a read command and a backward communication for receiving data. Then we produce, for each GT communication, the minimum bandwidth and a set of rules for latency/bandwidth checking. Due to space restriction the step is not detailed in this paper but can be found in [7].

The third step computes the minimum TDM table size required for implementing GT communications and a minimum bandwidth for all BE communications. TDM tables are based on integer bandwidth division, so compared to real constraints higher bandwidths are usually obtained, so we first try to solve the TDM size issue while considering absolute lower bounds. Basically our method is based on a heuristic that starts with a minimum size, which is increased until a solution is found. As a result we obtain minimum latencies taken into account within the next step.

The fourth step [8] automates the more tedious task which is the exploration of time (TDM slots)-space (NOC paths) space in order to allocate time slots to each GT communi-

**Fig. 1**.  $\mu$ Spider design flow.

cation. It provides next steps with a complete NOC specification. The exploration / allocation step is based on a two steps heuristic that, for each communication, first evaluates link usage probabilities and then selects a valid path with minimum impact on non allocated paths. The heuristic parameters (cost function, sorting criteria) have been selected for globally minimizing the FIFO costs.

The fifth step is the VHDL code generator, some additional C API codes are also provided for interfacing NOC components with IPs which are compliant with the OPB bus standard.

#### **3. ARCHITECTURE MODEL**

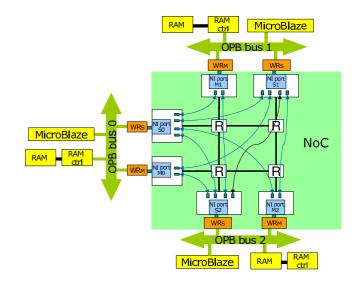

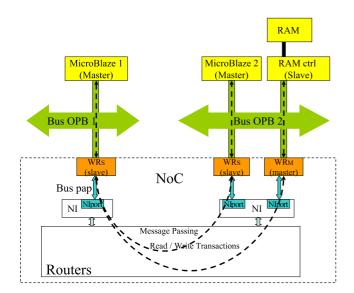

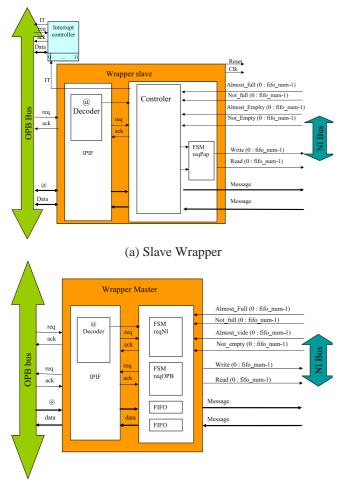

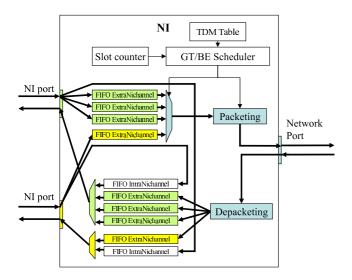

The architecture model is a network of bus-based clusters connected through a NoC. In case of Xilinx targets, we use OPB-based clusters connected to a NoC component instantiated as a traditional IP in an EDK project. As depicted in Fig. 3, typically a cluster is composed of a Microblaze (MB) soft processor that can control one or more local RAM memories connected to its OPB bus. So, the NoC IP is in charge of inter-cluster communications, the interface cluster / NoC is built with two components : a wrapper that adapts OPB and NoC network interface protocols and the Network Interface, which manages NoC accesses and (un)packetise data. Each cluster can integrate masters able to initiate read or write communications and slaves that can respond to read requests. A cluster can communicate with other clusters through dedicated channels, each input or output channel is implemented as a FIFO. Note that the architecture model is based on first designer choices such as topology, routing policies and link bit width for instance.

In the following we present different aspects of the architecture model.

# 3.1. Communication model

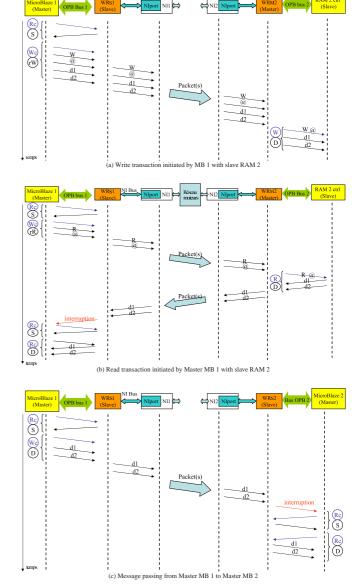

Three kinds of communications are implemented: write, read and message passing. They are depicted in Fig. 4. Fig. 5

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |                                                                                                                                     |                            |           |               |           |        | _0 |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------|---------------|-----------|--------|----|--|

| File Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                | _                                                                                                                                   |                            |           |               |           |        |    |  |

| Graphic Editor Advar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | nced Editor                                                                    |                                                                                                                                     |                            |           |               |           |        |    |  |

| Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                |                                                                                                                                     | Gene                       |           | Load          | Sav       |        |    |  |

| Communication<br>Cluster<br>Unidirect. Comm. In slots unit<br>Mutual Exclusive Comm.<br>Path Exploration<br>Buffer sizing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                |                                                                                                                                     |                            |           |               |           | -      |    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                | VRechercheVAAS\Theses\SEVMicroSpider\project\TurboDecoder\Archi                                                                     |                            |           |               |           |        |    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |                                                                                                                                     |                            |           |               |           |        |    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |                                                                                                                                     |                            |           |               |           |        |    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |                                                                                                                                     |                            |           |               |           |        |    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                | VHDL                                                                                                                                | <u></u>                    |           |               |           |        |    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |                                                                                                                                     |                            |           |               |           |        |    |  |

| Recent comma                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                |                                                                                                                                     |                            |           |               |           |        |    |  |

| _HW D:\Recherche\AAS\"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Theses\SE\                                                                     | MicroSpider\pr                                                                                                                      | oject\Turbol               | Decoder   | Archi_2_3     | xml       |        |    |  |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                | 36 A.C                                                                                                                              | 8                          |           |               |           |        |    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |                                                                                                                                     |                            |           |               |           |        |    |  |

| Reppo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ort:                                                                           |                                                                                                                                     |                            |           |               |           |        |    |  |

| ynthax: -I_HW : [-I_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _HW fileNan                                                                    | ne] Importe so                                                                                                                      | us forme XI                | 1L la des | cription ha   | ardware i | du NoC |    |  |

| ARCHI_~1.XML - XML N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Notepad                                                                        |                                                                                                                                     |                            |           |               |           |        |    |  |

| File Edit View Insert To                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ools Help                                                                      |                                                                                                                                     |                            |           |               |           |        |    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                | 19월 *                                                                                                                               | اهاها                      |           | <b>∓=</b>  I≣ | ۲         |        |    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |                                                                                                                                     |                            |           | 1 +10         | <u></u>   |        |    |  |

| Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •                                                                              | Value                                                                                                                               | s                          |           |               |           |        |    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |                                                                                                                                     |                            |           |               |           |        |    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                | 4                                                                                                                                   |                            |           |               |           |        |    |  |

| architectureName                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                | a                                                                                                                                   |                            |           |               |           |        |    |  |

| architectureName oc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                |                                                                                                                                     | 2DWithEdge                 | opology   | 2linesY       |           |        |    |  |

| architectureName                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                |                                                                                                                                     | 2DWithEdge                 | opology_  | 2linesY       |           |        |    |  |

| architectureName noc nocName version comment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                | mest<br>v00<br>mest                                                                                                                 | 2DWithEdge<br>with 2 lines |           | 3             |           |        |    |  |

| architectureName noc nocName oreversion oreversion odataCodingWi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | idth                                                                           | mesh<br>v00<br>mesh<br>32                                                                                                           |                            |           | 3             |           |        |    |  |

| architectureName noc nocName version comment dataCodingWi pathCodingWi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | idth<br>idth                                                                   | mest<br>v00<br>mest                                                                                                                 |                            |           | 3             |           |        |    |  |

| architecture/Name noc oncName version dataCodingWi pathCodingWi virtualChanne                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | idth<br>idth                                                                   | mest<br>v00<br>mest<br>32<br>16                                                                                                     |                            |           | 3             |           |        |    |  |

| architectureName noc noc ocdame version comment dataCodingWi pathCodingWi vitualChanne vcName vcName                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | idth<br>idth<br>el                                                             | mest<br>v00<br>mest<br>32<br>16                                                                                                     | with 2 lines '             |           | 3             |           |        |    |  |

| architectureName noc roctame version comment dataCodingWi virtualChanne vcName vcName vcName                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | idth<br>idth<br>al                                                             | mesh<br>v00<br>mesh<br>32<br>16<br>VC1<br>stree                                                                                     | with 2 lines '             |           | 3             |           |        |    |  |

| architectureName oc noc nocName version comment dataCodingWi vitualChanne vcName vcName                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | idth<br>idth<br>al                                                             | mesh<br>v00<br>mesh<br>32<br>16<br>VC1<br>stree                                                                                     | with 2 lines '             |           | 3             |           |        |    |  |

| architectureName nocName version comment dataCodingWi pathCodingWi virtualChame vortingTe vortingTe arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | idth<br>idth<br>al                                                             | mest<br>v00<br>mest<br>32<br>16<br>VC1<br>stree<br>rotat                                                                            | with 2 lines '             |           | 3             |           |        |    |  |

| architectureName noc nocVame version comment dataCodingW pathCodingW vcName vcName vcName qos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | idth<br>idth<br>el<br>chnique<br>nTechnique                                    | mest<br>v00<br>mest<br>32<br>16<br>VC1<br>stree<br>rotat                                                                            | with 2 lines '             |           | 3             |           |        |    |  |

| architectureName noc nocName version comment deacodingW virtualCharne virtualCharne virtualCharne virtualCharne virtualCharne virtualCharne voltingTe deacodingW virtualCharne voltingTe component deacodingW reviewSR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | idth<br>idth<br>chnique<br>nTechnique<br>ntName<br>ort                         | mest<br>v00<br>mest<br>32<br>16<br>VC1<br>stree<br>rotat<br>BE<br>R00                                                               | with 2 lines '             |           | 3             |           |        |    |  |

| architectureName nocVame oncVame version comment dataCodngW vituaCharne votName                                                                                                                                   | idth<br>idth<br>el<br>chnique<br>nTechnique<br>nTechnique                      | v00<br>mest<br>32<br>16<br>VC1<br>stree<br>rotat<br>BE                                                                              | with 2 lines '             |           | 3             |           |        |    |  |