# High performance metal-insulator-metal capacitor using a SrTiO(3)/ZrO(2) bilayer

Corentin Jorel, Christophe Vallée, Patrice Gonon, E. Gourvest, Christophe

Dubarry, Emmanuel Defay

### ► To cite this version:

## HAL Id: hal-00633086 https://hal.archives-ouvertes.fr/hal-00633086

Submitted on 17 Oct 2011

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# High performance metal-insulator-metal capacitor using a SrTiO<sub>3</sub>/ZrO<sub>2</sub> bilayer

C. Jorel,<sup>1,a)</sup> C. Vallée,<sup>1</sup> P. Gonon,<sup>1</sup> E. Gourvest,<sup>1</sup> C. Dubarry,<sup>2</sup> and E. Defay<sup>3</sup> <sup>1</sup>*Microelectronics Technology Laboratory (LTM), Joseph Fourier University (UJF), CEA/LETI/D2NT/LTM, 17 Avenue des Martyrs, 38054 Grenoble Cedex 9, France* <sup>2</sup>*CEA/LITEN, MINATEC, 17 Avenue des Martyrs, 38054 Grenoble Cedex 9, France* <sup>3</sup>*CEA/LETI, MINATEC, 17 Avenue des Martyrs, 38054 Grenoble Cedex 9, France*

(Received 20 May 2009; accepted 4 June 2009; published online 23 June 2009)

Future integration of metal-insulator-metal capacitors requires devices with high capacitance density and low quadratic voltage coefficient of capacitance ( $\alpha$ ). A major problem is that the increase in capacitance density is usually accompanied by increased voltage nonlinearities. By combining two high-*k* materials with opposite  $\alpha$ , it is demonstrated that it is possible to obtain capacitors with both high capacitance density and minimal nonlinearity. A SrTiO<sub>3</sub>/ZrO<sub>2</sub> bilayer was used to elaborate capacitors displaying a voltage coefficient of -60 ppm/V<sup>2</sup> associated with a density of 11.5 fF/ $\mu$ m<sup>2</sup>. These devices constitute excellent candidates for the next generation of metal-insulator-metal capacitors. © 2009 American Institute of Physics. [DOI: 10.1063/1.3158951]

Capacitors are key passive components in most of the integrated circuits which are used in analog filtering, dc decoupling, and analog-to-digital conversion. Following the integration and component size reduction efforts, capacitors are meant to be integrated on-chip, within the back-end metallization levels. Getting small size capacitors with high capacitance values requires using dielectrics possessing a high capacitance density per unit area, i.e., high- $\kappa$  dielectrics. Therefore, the traditional dielectrics, SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub>, were forsaken because of their low dielectric constant ( $\kappa$  < 10) and there is a lot of ongoing effort to develop high- $\kappa$  materials ( $\kappa$  > 15) such as Ta<sub>2</sub>O<sub>5</sub>, HfO<sub>2</sub>, and ZrO<sub>2</sub>, to name a few.<sup>1-10</sup>

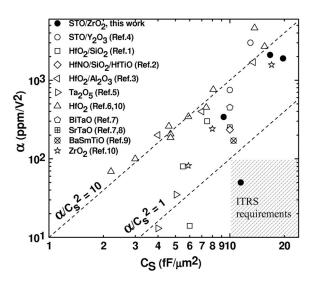

An important issue regarding capacitor performances is the voltage linearity, which shows the dependence of capacitance (C) on the applied bias (V). For high- $\kappa$  oxides it is usual to observe a quadratic voltage dependence of capacitance,  $[C(V)-C_0]/C_0 = \alpha V^2 + \beta V$ , where  $C_0$  is the capacitance at zero bias, and  $\alpha$  and  $\beta$  are the quadratic and linear coefficients. For most of the high- $\kappa$  dielectrics the coefficient  $\alpha$  is in the 100–1000 ppm/ $V^{2}$  range and the coefficient  $\beta$  is in the 100 ppm/V range.<sup>1–11</sup> As a consequence, for usual working voltages (1-3 V) the quadratic contribution prevails  $(\alpha V^2 > \beta V)$  and the most important parameter that must be controlled is the quadratic coefficient  $\alpha$ . Usually  $\alpha$  is observed to increase dramatically with decreasing oxide thickness.<sup>3,7,8,11</sup> Thus, the effort to increase the capacitance density  $(C_S = \kappa \varepsilon_0 / t)$  by decreasing the thickness (t) is always limited by a large increase of  $\alpha$ . The difficulty to obtain both high  $C_s$  and low  $\alpha$  can be quantified by introducing the ratio  $\alpha/C_s^2$ . The reason for introducing  $C_s^2$ , instead of  $C_s$ , is the following. For practical applications the capacitance variation is written as a function of V, but physically  $(C-C_0)/C_0$ should vary with the electric field (E=V/t), i.e., it should be independent of the oxide thickness. Rewriting  $(C-C_0)/C_0$  as a function the electric field,  $[C(E)-C_0]/C_0 = \alpha E^2 t^2 + \beta E t$ , it is seen that the relative capacitance variation does not dependent on the oxide thickness if  $\alpha$  varies with  $1/t^2$ . In that case the ratio  $\alpha/C_s^2$  is also expected to be independent of the oxide thickness.<sup>11</sup> These ideas are summarized in Fig. 1 which shows  $\alpha$  as a function of  $C_s$  for different materials. On this plot the ratio  $\alpha/C_s^2$  appears as a material's figure of merit which varies from 10 (ppm  $\mu$ m<sup>2</sup>/V<sup>2</sup> fF<sup>2</sup>) for materials such as HfO<sub>2</sub>, down to one for oxides such as Ta<sub>2</sub>O<sub>5</sub>. According to the International Technology Roadmap for Semiconductors (ITRS),<sup>12</sup> in a few years application will require  $\alpha < 100$  ppm/V<sup>2</sup> and  $C_s > 10$  fF/ $\mu$ m<sup>2</sup>. This is a difficult challenge which is better seen in Fig. 1 as a more general difficulty to get  $\alpha/C_s^2 < 1$ .

A way to reduce  $\alpha$  was proposed by Kim *et al.*<sup>1</sup> It consists in using a bilayer capacitor where a dielectric (SiO<sub>2</sub>) with a negative  $\alpha$  is used to compensate the oxide (HfO<sub>2</sub>) with a positive  $\alpha$ . By using a 12 nm HfO<sub>2</sub>/4 nm SiO<sub>2</sub> stack, these authors<sup>1</sup> obtained a very low  $\alpha$  value of 14 ppm/V<sup>2</sup> and a  $\alpha/C_s^2$  ratio which is clearly below unity. However, the low  $\kappa$  value of SiO<sub>2</sub> prevented them to get high  $C_s$  values

FIG. 1. Quadratic coefficient  $\alpha$  as a function of capacitance density  $C_S$  for different materials of the literature. The figure of merit  $\alpha/C_S^2$  is expressed in ppm  $\mu$ m<sup>2</sup>/V<sup>2</sup>fF<sup>2</sup>. The shaded area represents long term (2016) ITRS requirements (Ref. 12).

#### 94, 253502-1

### © 2009 American Institute of Physics

Downloaded 25 Jun 2009 to 132.168.24.153. Redistribution subject to AIP license or copyright; see http://apl.aip.org/apl/copyright.jsp

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed. Electronic mail: corentin.jorel@cea.fr.

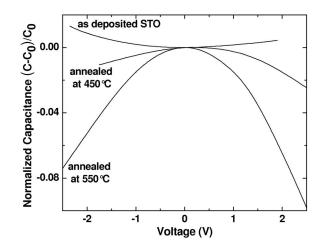

FIG. 2. Normalized capacitance vs bias for a 20 nm STO layer (as-deposited, annealed in air at 450  $^\circ C,$  and annealed in air at 550  $^\circ C).$

(6 fF/ $\mu$ m<sup>2</sup>). Since then, other multilayer structures were investigated, but none of them were successful in getting  $\alpha/C_s^2 < 1$  to fulfill roadmaps requirements (see Fig. 1).<sup>3,4</sup> In the present work we studied SrTiO<sub>3</sub> (STO)/ZrO<sub>2</sub> bilayers. ZrO<sub>2</sub> is a high- $\kappa$  dielectric with positive  $\alpha$  in the 100–1000 ppm/V<sup>2</sup> range<sup>10</sup> (Fig. 1). STO was chosen as a dielectric with a negative  $\alpha$  to compensate for the ZrO<sub>2</sub> positive  $\alpha$  coefficient. Contrary to SiO<sub>2</sub>, STO can reach high- $\kappa$  values (65 in this study) which allows to maintain an overall high capacitance density. By carefully engineering the STO/ZrO<sub>2</sub> thickness ratio it is demonstrated that STO/ZrO<sub>2</sub> capacitors provide  $\alpha/C_s^2 < 1$  and appear as a solution to meet the long-term ITRS roadmap.

STO layers were deposited at room temperature by Pt(100 nm)/ argon ion beam sputtering on  $TiO_2(10 \text{ nm})/SiO_2(500 \text{ nm})/Si \text{ substrates.}^{13}$  STO postannealings (1 h) were performed in air at 450 or 550 °C (as specified in the discussion). ZrO<sub>2</sub> layers were deposited on STO by metal-organic chemical-vapor deposition at 400 °C, in Ar/O<sub>2</sub> mixtures containing Zr(Obut)2(mmp)2 as a Zr precursor. Gold top electrodes were deposited by electron beam evaporation to form metal-insulator-metal (MIM) capacitors. C-V measurements were performed at 100 kHz using a HP4284 capacitance meter.

Figure 2 shows  $[C(V)-C_0]/C_0$  for a 20 nm STO layer in three different states (as-deposited, annealed at 450 °C and annealed at 550 °C). As-deposited STO is in an amorphous state and displays a positive  $\alpha(2200 \text{ ppm/V}^2)$  and a quite low  $\kappa$  value of about 20. An annealing at 450 °C reverses the sign of the voltage coefficient ( $\alpha = -3800 \text{ ppm/V}^2$ ). Still, the  $\kappa$  value of this annealed film remains low (20) indicating that crystallization is partial. Annealing at 550 °C further drives  $\alpha$  toward negative values (-12 800 ppm/V<sup>2</sup>) and allows to reach higher  $\kappa$  values (65). This demonstrates that the  $\alpha$  value of STO layers can be tuned from positive values (as-deposited, amorphous layers) to negative values (air annealed, semicrystalline layers). Crystalline and stoechiometric STO is a paraelectric perovskite material which is known to display negative voltage coefficients.<sup>14</sup> The positive voltage coefficient measured for the amorphous films is probably due to the loss of the crystalline state, as well as oxygen deficiencies. Indeed, amorphous BaTiO<sub>3</sub> also has a positive voltage coefficient which decreases upon oxygen addition

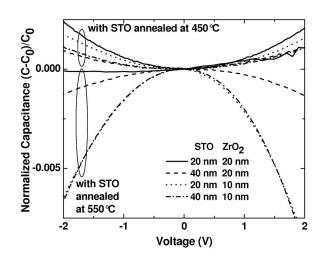

FIG. 3. Normalized capacitance vs bias for  $STO/ZrO_2$  stacks. The stacks make use of STO annealed at 450 °C (upper curves) or at 550 °C (lower curves). Best performances are obtained with  $STO(550 \ ^{\circ}C, 20 \ nm)/ZrO_2(20 \ nm)$ .

during deposition.<sup>15</sup> Moreover, oxygen vacancies are likely defects to be at the origin of nonlinearities observed in MIM capacitors.<sup>16</sup> Therefore, in amorphous dielectrics such as SrTiO<sub>3</sub> or BaTiO<sub>3</sub> (perovskite family) it is thought that oxygen vacancies control nonlinearities. Upon annealing in oxygen (air) the material crystallizes and recovers oxygen stoechiometry, leading to a "normal" negative voltage coefficient.<sup>14</sup>

Starting from STO layers with negative  $\alpha$ , ZrO<sub>2</sub> layers were deposited on top of the STO films. Stacks with different STO and ZrO<sub>2</sub> thicknesses were tested (see Fig. 3 and Table I). The STO(20 nm)/ZrO<sub>2</sub>(20 nm) bilayer is clearly the most interesting one in terms of performances. Corresponding  $\alpha$  and  $C_s$  are -60 ppm/V<sup>2</sup> and 11.5 fF/ $\mu$ m<sup>2</sup> (figure of merit  $\alpha/C_s^2=0.46<1$ ). These characteristics meet long-term ITRS requirements (Fig. 1). The dc leakage current was also measured and the values are shown in Table I. For the 20 nm/20 nm bilayer, the leakage current at 2 V is 3.5  $\times 10^{-8}$  A/cm<sup>2</sup>, close to ITRS specifications ( $< 10^{-8}$  A/cm<sup>2</sup> at 1.8 V). The breakdown field of the 20 nm/20 nm stack was measured around 4 MV/cm (15 V across the capacitor). Since the  $\kappa$  value of ZrO<sub>2</sub> is three times lower than the STO one, most of the electric field is applied to the ZrO<sub>2</sub> layer, which supports higher breakdown electric fields (typically 5 MV/cm compared to 1 MV/cm for STO). It is also noted that the  $(C(V)-C_0)/C_0$  curve is asymmetrical with respect to

TABLE I. Capacitance density, experimental quadratic coefficient, and theoretical quadratic coefficient calculated from Eq. (1), where  $\varepsilon$ (STO)=65,  $\alpha$ (STO)=-12 800 ppm/V<sup>2</sup> (this work),  $\varepsilon$ (ZrO<sub>2</sub>)=20,  $\alpha$ (ZrO<sub>2</sub>)=+250 ppm/V<sup>2</sup> (Ref. 10), and leakage current of STO/ZrO<sub>2</sub> capacitors. STO was postannealed in air at 550 °C during 1 h.

| Layers      |                          |                                                                                       |                                     |                                      |                                      |

|-------------|--------------------------|---------------------------------------------------------------------------------------|-------------------------------------|--------------------------------------|--------------------------------------|

| STO<br>(nm) | ZrO <sub>2</sub><br>(nm) | $\begin{array}{c} C_S ~({\rm fF}/\mu{\rm m}^2) \\ {\rm at}~100~{\rm kHz} \end{array}$ | $\alpha \text{ (ppm/V^2)}$<br>Expt. | $\alpha \text{ (ppm/V^2)}$<br>Theor. | $I_S$ (A/cm <sup>2</sup> )<br>at 2 V |

| 40          | 20                       | 9                                                                                     | -350                                | -644                                 | $2.5 \times 10^{-8}$                 |

| 40          | 10                       | 16.5                                                                                  | -2280                               | -2153                                | $2.7 \times 10^{-8}$                 |

| 20          | 20                       | 11.5                                                                                  | -60                                 | -54                                  | $3.5 \times 10^{-8}$                 |

| 20          | 10                       | 19.5                                                                                  | -1900                               | -644                                 | $3.4 \times 10^{-8}$                 |

| 20          |                          | 29                                                                                    | $-12\ 800$                          |                                      | $1 \times 10^{-7}$                   |

Downloaded 25 Jun 2009 to 132.168.24.153. Redistribution subject to AIP license or copyright; see http://apl.aip.org/apl/copyright.jsp

the sign of V (20 nm/20 nm stack, STO annealed at 550 °C, Fig. 3). This can be explained by the importance of the linear coefficient  $\beta$ (+143 ppm/V) which gives a linear contribution as important as the quadratic one. However, in practice the  $\beta$  coefficient has less importance because it can be more easily compensated by circuit design.<sup>17</sup> At 125 °C the characteristics worsen. The  $\alpha$  coefficient increases to -135 ppm/V<sup>2</sup>. Though the characteristics are good at room temperature, studies are still needed to assess their thermal stability.

Low  $\alpha$  values of the STO/ZrO<sub>2</sub> stacks can be explained as follows. Let us denote by  $C_1$ ,  $t_1$ ,  $\kappa_1$ ,  $\alpha_1$ , and  $\beta_1$ ; the capacitance, the thickness, the dielectric constant, the voltage coefficients of the STO layer, and  $V_1$  the voltage across this layer (correspondingly,  $C_2$ ,  $t_2$ ,  $\kappa_2$ ,  $\alpha_2$ ,  $\beta_2$ , and  $V_2$  for the ZrO<sub>2</sub> layer). The total capacitance C is  $(C_1C_2)/(C_1+C_2)$ and the voltage across the stack is  $V=V_1+V_2$ . Calculation of  $\alpha$  and as a function of  $\alpha_1$ ,  $\alpha_2$ ,  $\beta_1$ , and  $\beta_2$  is made by writing  $(dC/dV) = 2\alpha C_0 V + \beta C_0 = 2\alpha C_0 (V_1 + V_2) + \beta C_0$ . We can also write  $(dC/dV) = (\delta C/\delta C_1)(\delta C_1/\delta V) + (\delta C/\delta C_2)$  $\times (\delta C_2 / \delta V)$ and  $(\delta C_1 / \delta V) = (\delta V_1 / \delta C_1 + \delta V_2 / \delta C_1)^{-1}$ = $(\delta C_1 / \delta V_1)(1 + \delta V_2 / \delta V_1)^{-1}$ . Using  $(\delta C_1 / \delta V_1) = 2\alpha_1 C_{10} V_1$  $+\beta_1 C_{10}$  and the displacement field continuity at the interface  $\kappa_1(V_1/t_1) = \kappa_2(V_2/t_2)$  (dC/dV) can now be expressed as a function of  $\alpha_1$ ,  $\alpha_2$ ,  $\kappa_1$ , and  $\kappa_2$ . Comparing with the expression of (dC/dV) as a function of  $\alpha$  and  $\beta$ , one finds

$$\alpha = \alpha_1 \left( \frac{1}{1 + \frac{\kappa_1 t_2}{\kappa_2 t_1}} \right)^3 + \alpha_2 \left( \frac{1}{1 + \frac{\kappa_2 t_1}{\kappa_1 t_2}} \right)^3, \tag{1}$$

$$\beta = \beta_1 \left( \frac{1}{1 + \frac{\kappa_1 t_2}{\kappa_2 t_1}} \right)^2 + \beta_2 \left( \frac{1}{1 + \frac{\kappa_2 t_1}{\kappa_1 t_2}} \right)^2.$$

(2)

As explained in the introduction, we will focus on the quadratic coefficient  $\alpha$  [Eq. (1)]. In this work we measured  $\kappa_1$ =65 and  $\alpha_1$ =-12 800 ppm/V<sup>2</sup> (see Table I). From Ref. 10 we consider  $\kappa_2$ =20 and  $\alpha_2$ =+250 ppm/V<sup>2</sup>. Reporting these values in Eq. (1) (with  $t_1$ =20 nm and  $t_2$ =20 nm) we get  $\alpha$ =-54 ppm/V<sup>2</sup>, which is very close to the experimental value of -60 ppm/V<sup>2</sup>. The experimental and the theoretical  $\alpha$  also agree very well for the 40 nm/10 nm stack and are of the same order of magnitude for the 40 nm/20 nm and for the

20 nm/10 nm stacks (Table I). Thus, on average, Eq. (1) appears to predict the final voltage coefficient quite well (provided that the characteristics of individual layers are known).

To conclude, high performance MIM capacitors are obtained by combining two high-*k* materials with opposite quadratic voltage coefficient of capacitance. By adjusting the thickness of each layer [Eq. (1)], it is possible to minimize the quadratic voltage coefficient, while maintaining high capacitance density ( $\alpha/C_s^2 < 1$ ). This concept was applied to STO/ZrO<sub>2</sub> stacks, but it can be extended to other couples of dielectrics.

- <sup>1</sup>S. J. Kim, B. J. Cho, M.-F. Li, S.-J. Ding, C. Zhu, M. B. Yu, B. Narayanan, A. Chin, and D.-L. Kwong, IEEE Electron Device Lett. **25**, 538 (2004).

<sup>2</sup>V. Mikhelashvili, P. Thangadurai, W. D. Kaplan, and G. Eisenstein, Appl. Phys. Lett. **92**, 132902 (2008).

- <sup>3</sup>S.-J. Ding, H. Hu, C. Zhu, S. J. Kim, X. Yu, M.-F. Li, B. J. Cho, D. S. H. Chan, M. B. Yu, S. C. Rustagi, A. Chin, and D.-L. Kwong, **IEEE Trans.** Electron Devices **51**, 886 (2004).

- <sup>4</sup>M. Kahn, C. Vallée, E. Defay, C. Dubourdieu, M. Bonvalot, S. Blonkowski, J. R. Plaussu, P. Garrec, and T. Baron, Microelectron. Reliab. 47, 773 (2007).

- <sup>5</sup>E. Deloffre, L. Montès, G. Ghibaudo, S. Bruyère, S. Blonkowski, S. Bécu, M. Gros-Jean, and S. Crémer, Microelectron. Reliab. 45, 925 (2005).

- <sup>6</sup>S. J. Kim, B. J. Cho, M. F. Li, X. Yu, C. Zhu, A. Chin, and D.-L. Kwong, IEEE Electron Device Lett. **24**, 387 (2003).

- <sup>7</sup>L. Goux, H. Vander Meeren, and D. J. Wouters, J. Electrochem. Soc. **153**, F132 (2006).

- <sup>8</sup>M. Lukosius, C. Wenger, S. Pasko, L. Costina, J. Dabrowski, R. Sorge, H. J. Mussig, and C. Lohe, IEEE Trans. Electron Devices **55**, 2273 (2008).

- <sup>9</sup>Y. H. Jeong, J. H. Paik, Y. J. Lee, and S. Nabm, J. Electrochem. Soc. **155**, G214 (2008).

- <sup>10</sup>S. Blonkowski, Appl. Phys. Lett. **91**, 172903 (2007).

- <sup>11</sup>C. Durand, C. Vallée, C. Dubourdieu, M. Kahn, M. Derivaz, S. Blonkowski, D. Jalabert, P. Hollinger, Q. Fang, and I. W. Boyd, J. Vac. Sci. Technol. A 24, 459 (2006).

- <sup>12</sup>The International Technology Roadmap for Semiconductors (ITRS) (Semiconductor Industry Association, 2008), Table RFAMS3 On-Chip Passives Technology Requirements, http://www.itrs.net/Links/2008ITRS/ Home2008.htm.

- <sup>13</sup>E. Defaÿ, B. Andre, F. Baume, G. Tartavel, D. Muyard, and L. Ulmer, Ferroelectrics 288, 121 (2003).

- <sup>14</sup>See, for instance, C. Ang and Z. Yu, Phys. Rev. B **69**, 174109 (2004), and references therein.

- <sup>15</sup>F. El Kamel, P. Gonon, and C. Vallée, Appl. Phys. Lett. **91**, 172909 (2007).

- <sup>16</sup>P. Gonon and C. Vallée, Appl. Phys. Lett. **90**, 142906 (2007).

- <sup>17</sup>D. Dornisch, G. Wilk, G. Li, K. M. Ring, D. J. Howard, and M. Racanelli, ECS Trans. 6, 755 (2007).