# University of South Alabama

# JagWorks@USA

Theses and Dissertations

Graduate School

5-2022

# Circuit-Variant Moving Target Defense for Side-Channel Attacks on Reconfigurable Hardware

Tristen H. Mullins University of South Alabama, tah1323@jagmail.southalabama.edu

Follow this and additional works at: https://jagworks.southalabama.edu/theses\_diss

Part of the Information Security Commons, and the Other Computer Sciences Commons

#### **Recommended Citation**

Mullins, Tristen H., "Circuit-Variant Moving Target Defense for Side-Channel Attacks on Reconfigurable Hardware" (2022). Theses and Dissertations. 54.

https://jagworks.southalabama.edu/theses\_diss/54

This Dissertation is brought to you for free and open access by the Graduate School at JagWorks@USA. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of JagWorks@USA. For more information, please contact jherrmann@southalabama.edu.

# CIRCUIT-VARIANT MOVING TARGET DEFENSE FOR SIDE-CHANNEL ATTACKS ON RECONFIGURABLE HARDWARE

# A Dissertation

Submitted to the Graduate Faculty of the University of South Alabama in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in

Computing

by Tristen H. Mullins B. S., University of South Alabama, 2018 May 2022

#### **ACKNOWLEDGEMENTS**

I would like to express my deepest gratitude to my committee chair, Dr. Todd

Andel for his valued guidance and encouragement throughout my time at South Alabama.

I would also like to thank my committee members Dr. Todd McDonald, Dr. Dimitrios

Damopoulos, and Dr. Samuel Russ for lending their expertise in the completion of this research.

The completion of this dissertation would not have been possible without the unwavering support of my family. I am extremely grateful to my husband and children for the inspiration they provided and sacrifices they made to allow me to pursue this degree.

# TABLE OF CONTENTS

| Page                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LIST OF TABLESvi                                                                                                                                                     |

| LIST OF FIGURESvii                                                                                                                                                   |

| LIST OF ABBREVIATIONSix                                                                                                                                              |

| ABSTRACTx                                                                                                                                                            |

| CHAPTER I INTRODUCTION                                                                                                                                               |

| 1.1 Motivation                                                                                                                                                       |

| CHAPTER II BACKGROUND                                                                                                                                                |

| 2.1 The AES Algorithm                                                                                                                                                |

| 2.1.1 SubBytes       6         2.1.2 ShiftRows       7         2.1.3 MixColumns       7         2.1.4 AddRoundKey       8         2.1.5 Side-Channel Leakage       8 |

| 2.2 Power Analysis                                                                                                                                                   |

| 2.2.1 Simple Power Analysis122.2.2 Differential Power Analysis13                                                                                                     |

| 2.3 Electromagnetic Analysis172.4 Countermeasures19                                                                                                                  |

| 2.4.1 Evaluating Countermeasures202.4.2 Countermeasure Techniques22                                                                                                  |

| 2.5 Circuit Variants                                                                 |

|--------------------------------------------------------------------------------------|

| 2.5.1 Circuit Variant Countermeasures                                                |

| 2.6 Moving Target Defense                                                            |

| 2.6.1 Dynamic Partial Reconfiguration                                                |

| CHAPTER III RESEARCH OBJECTIVE                                                       |

| CHAPTER IV S-BOX CIRCUIT VARIANTS                                                    |

| 4.1 Program Encryption Toolkit394.2 Side-Channel Properties41                        |

| CHAPTER V COUNTERMEASURE DESIGN                                                      |

| 5.1 Equipment and Resources465.2 Countermeasure Design475.3 Control Implementation51 |

| CHAPTER VI SIDE-CHANNEL RESISTANCE                                                   |

| 6.1 Localized EM Analysis                                                            |

| 6.1.1 Results                                                                        |

| 6.2 Power Analysis                                                                   |

| 6.2.1 Results                                                                        |

| 6.3 Performance and Cost                                                             |

| CHAPTER VII CONCLUSIONS AND FUTURE WORK                                              |

| REFERENCES                                                                           |

| APPENDICES                                                                           |

| Appendix A: First Order Analysis of Control Implementation                           |

| BIOGRAPHICAL SKETCH                                                                  |

# LIST OF TABLES

| Table                                                            | Page |

|------------------------------------------------------------------|------|

| 1. S-box Substitution Values for The Hexadecimal Byte xy [27]    | 7    |

| 2. Research Objectives for Circuit Variant Moving Target Defense | 37   |

| 3. Number of Gates for S-Box Circuit Variants                    | 41   |

| 4. Execution Times for AES S-box Variants.                       | 43   |

| 5. LUT Equations for S-boxes 1 and 5.                            | 44   |

| 6. Recovered Key from Control Implementation.                    | 62   |

| 7. Recovered Key from Countermeasure Implementation.             | 62   |

| 8. Utilization of Control Implementation.                        | 67   |

| 9. Utilization of Countermeasure Implementation                  | 67   |

# LIST OF FIGURES

| Figure                                                                     | Page |

|----------------------------------------------------------------------------|------|

| 1. AES Encryption Block Diagram [29].                                      | 6    |

| 2. Pseudo Code for AES Algorithm [33].                                     | 9    |

| 3. Block Diagram of a Typical Measurement Setup for Power Analysis [30]    | 11   |

| 4. Power Trace from AES-128 on a Smart Card by Kocher et al. [35]          | 11   |

| 5. SPA Leaks in RSA Modular Exponentiation by Kocher et al. [35]           | 13   |

| 6. Five Steps of DPA Attack based on Mangard et al. [30]                   | 15   |

| 7. EM XY Scan at External (Left) and Internal Clock Frequency (Right) [45] | 19   |

| 8. Iterative Selection/Replacement                                         | 40   |

| 9. Merged Signature Circuit Generation. 5 Gates with a Max Fan In of 2     | 41   |

| 10. DONT_TOUCH Logic For S-box 1.                                          | 43   |

| 11. EM Trace of S-box 0.                                                   | 43   |

| 12. EM Trace of S-box 5                                                    | 44   |

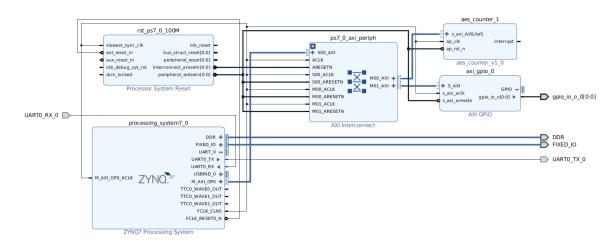

| 13. IP Core Block Diagram                                                  | 48   |

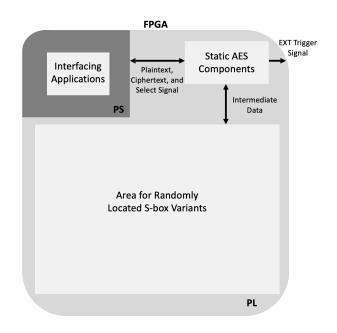

| 14. System Block Diagram.                                                  | 49   |

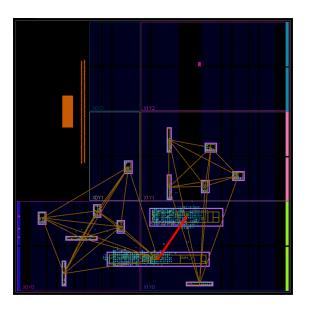

| 15. Countermeasure Device Layout                                           | 50   |

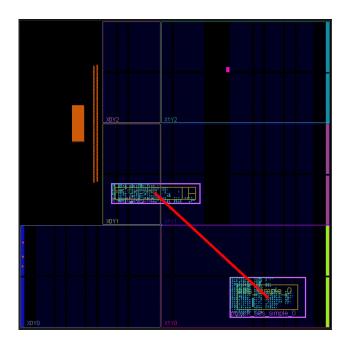

| 16. Control Device Layout                                                  | 51   |

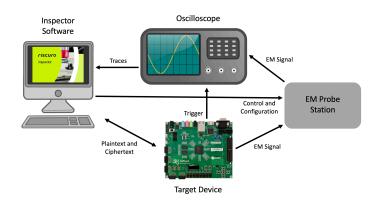

| 17. Electromagnetic Analysis Setup.                                        | 54   |

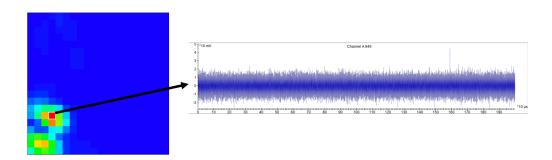

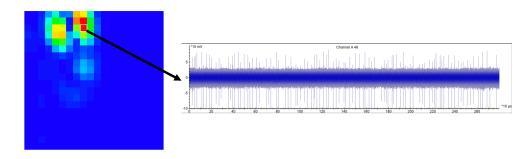

| 18. Control Hotspot A and Corresponding EM Trace.        | . 54 |

|----------------------------------------------------------|------|

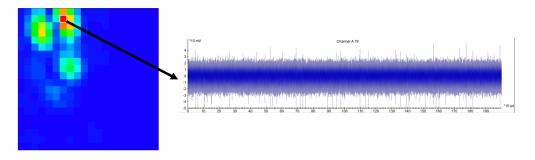

| 19. Control Hotspot B and Corresponding EM Trace.        | . 55 |

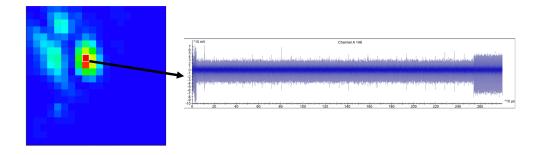

| 20. Control Hotspot C and Corresponding EM Trace.        | . 55 |

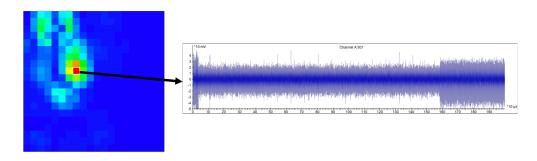

| 21. Countermeasure Hotspot A and Corresponding EM Trace. | . 56 |

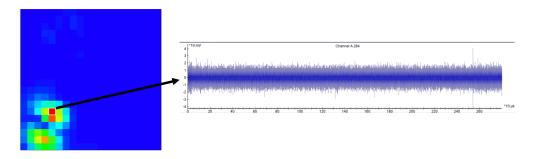

| 22. Countermeasure Hotspot B and Corresponding EM Trace. | . 56 |

| 23. Countermeasure Hotspot C and Corresponding EM Trace. | . 56 |

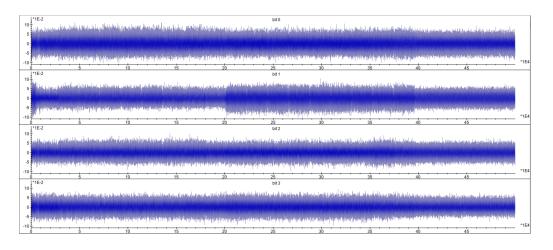

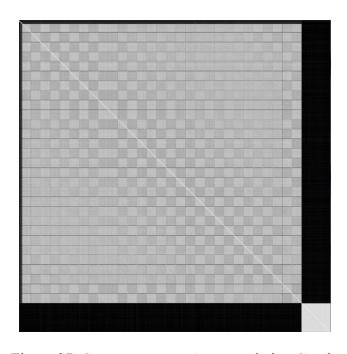

| 24. Control Correlation for Input Bits 0-3.              | . 57 |

| 25. Countermeasure Correlation for Input Bits 0-3.       | . 58 |

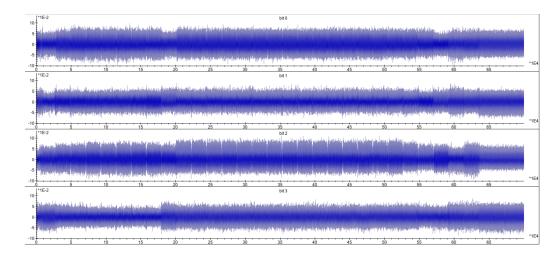

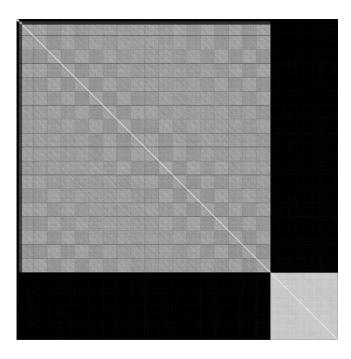

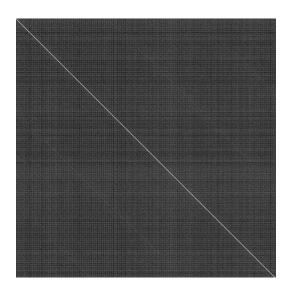

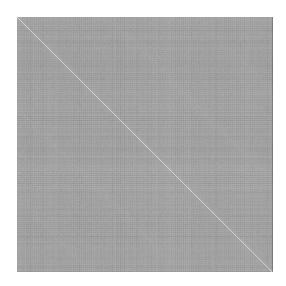

| 26. Control Autocorrelation Graph.                       | . 59 |

| 27. Coutnermeasure Autocorrelation Graph.                | . 59 |

| 28. Control First Order Analysis Examples.               | . 61 |

| 29. Countermeasure First Order Analysis Examples.        | . 62 |

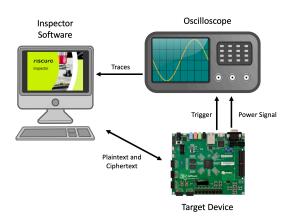

| 30. Power Analysis Setup.                                | . 63 |

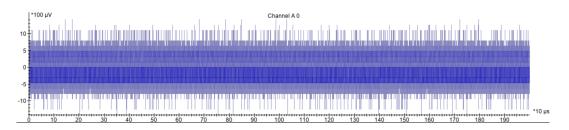

| 31. Control Power Trace.                                 | . 64 |

| 32. Filtered Control Power Trace                         | . 64 |

| 33. Control Power Autocorrelation Graph.                 | . 65 |

| 34. Filtered Control Power Autocorrelation Graph.        | . 66 |

# LIST OF ABBREVIATIONS

AES Advanced Encryption Standard

PA Power Analysis

SCA Side-Channel Analysis

EM Electromagnetic

RDI Random Delay Insertion

EMA Electromagnetic Analysis

SNR Signal-to-Noise Ratio

ECC Elliptic Curve Cryptography

CV Circuit-Variant

CPA Correlation Power Analysis

P&R Placement & Route

PL Programmable Logic

ISR Iterative Selection/Replacement

#### **ABSTRACT**

Mullins, Tristen, H., Ph.D., University of South Alabama, May 2022. Circuit-Variant Moving Target Defense for Side-Channel Attacks on Reconfigurable Hardware. Chair of Committee: Todd R. Andel, Ph.D.

With the emergence of side-channel analysis (SCA) attacks, bits of a secret key may be derived by correlating key values with physical properties of cryptographic process execution. Power and Electromagnetic (EM) analysis attacks are based on the principle that current flow within a cryptographic device is key-dependent and therefore, the resulting power consumption and EM emanations during encryption and/or decryption can be correlated to secret key values. These side-channel attacks require several measurements of the target process in order to amplify the signal of interest, filter out noise, and derive the secret key through statistical analysis methods. Differential power and EM analysis attacks rely on correlating actual side-channel measurements to hypothetical models.

This research proposes increasing resistance to differential power and EM analysis attacks through structural and spatial randomization of an implementation. By introducing randomly located circuit variants of encryption components, the proposed moving target defense aims to disrupt side-channel collection and correlation needed to successfully implement an attack.

#### **CHAPTER I**

#### INTRODUCTION

### 1.1 Motivation

Several factors are considered when deciding on which platform to implement a cryptographic algorithm. There are many trade-offs between software and hardware implementations including cost, speed, and flexibility. While software implementations are often more flexible, easier to update, and have low development costs, they can have greater overhead costs and weaker security than their hardware counterparts.

Reconfigurable hardware devices (e.g., field-programmable gate arrays, or FPGAs) feature characteristics that allow them comparable flexibility to software implementations while incorporating the benefits of hardware realization. Wollinger and Paar [1] list some potential advantages reconfigurable hardware provides for cryptography including algorithm agility, algorithm upload, architecture efficiency, resource efficiency, algorithm modification, throughput, and cost efficiency. Not only do these improve algorithm performance, but they also ensure that the platform resources are used efficiently, and updates are easily made through reconfiguration. However, these advantages can only be exploited if security shortcomings are addressed.

The security of cryptosystems involves preventing an attacker's ability to obtain information about plaintext. Traditionally, this has been done by prioritizing secrecy of

the key through complex key selection and secure key exchange [2]. With the emergence of side-channel analysis (SCA) attacks, bits of a secret key may be derived by correlating key values with physical properties of cryptographic process execution. Information such as timing [3], power [4], and electromagnetic (EM) radiation [5] side-channel properties can all be observed during run-time of a cryptoprocess. These signals reflect datadepended system behaviors that may be analyzed by an attacker to derive secret key values.

The ability to obtain information about the system is dependent on the accessibility of a "usable" side-channel and does not "reflect inherent weaknesses" of the process being examined [6]. Therefore, countermeasures for SCA attacks should focus on reducing trace usability by minimizing behavior-key correlation and information leakage within the signal.

#### 1.2 Problem Statement

Side-channel countermeasures are designed to increase the complexity of SCA attacks. This is often done through hiding and masking techniques such as random delay insertion (RDI) [7]–[9], shuffling [10]–[13], masking [14], [15], dual-rail logic [16]–[19], etc. While increasing attack complexity makes it more difficult for an attacker to successfully obtain the key, it does not make it impossible. Because there is currently no solution that eliminates all side-channel leakage, we must "accept that cryptographic implementations leak a certain amount of information," and avoid allowing the leakages to completely compromise security during use [20].

Many researchers suggest implementing countermeasures in combination to further improve security [12], [21]. Such integration has been used to address the shortcomings of individual countermeasures. For example, masking schemes are often applied in combination with shuffling countermeasures to increase the number of required attack traces [12], [13].

Attackers may also have the ability to perform multiple types of SCA on devices. With physical access to a device, both power and electromagnetic analysis (EMA) attacks may be conducted with simple equipment. Though many power countermeasures are assumed to protect against EMA, it has been shown that power countermeasures may still be vulnerable to localized EMA attacks [22]–[24]. This creates a need for both power and EMA attack prevention methods on a device. To provide sufficient security, designs should include countermeasure combinations that not only protect against single side-channel attacks but alternatives that may be available to an attacker with physical device access.

However, selecting which countermeasures to apply should not be done arbitrarily. Not only is it costly to implement multiple security measures, but some combinations may also add deficiencies to a system. It has been shown that methods used to secure an encryption algorithm against one kind of attack may consequently leave it vulnerable to another [25], [26]. Therefore, it is important to assess the compatibility of countermeasures so that attack vectors are not introduced or aided by their integration.

# 1.3 Research Objective

This research focuses on increasing the complexity of localized EM SCA by introducing structural and spatial randomization of the target hardware. This is done by utilizing randomly placed S-box circuit variants in the programmable logic side of an SOC. A practical countermeasure evaluation is performed by collecting power and localized EM traces, determining which trace sets are usable, and performing first order differential analysis on those traces.

The remainder of this document is organized as follows. Chapter II provides a background on power and EM side-channel analysis as well as countermeasures. This includes literary review of works involving moving target defense, circuit variants, and dynamic partial reconfiguration. Chapter III describes the goals and objectives of this research while Chapter IV details a proposed methodology for developing and assessing the circuit-variant moving target defense countermeasure.

#### **CHAPTER II**

#### BACKGROUND

In this chapter, a background on power and electromagnetic side-channel analysis is provided. This includes an overview of techniques for attacks as well as resistance. A description of the algorithm used in this research, AES, is also provided. Further, methods for quantifying countermeasure effectiveness are also discussed as well as the applicability of power countermeasures as an EM analysis defense. Related works involving circuit variance, moving target defenses, and dynamic partial reconfiguration are discussed.

# 2.1 The AES Algorithm

The Advanced Encryption Standard (AES) is the current standard for encrypting electronic data [27]. This symmetric block cipher is a form of the Rijndael cipher [28] that processes 128-bit blocks with variable key length. Each data block consists of 16 bytes arranged in four rows and four columns. The cipher supports key lengths of 128, 192, and 256 bits which correspond to 10, 12, and 14 rounds, respectively.

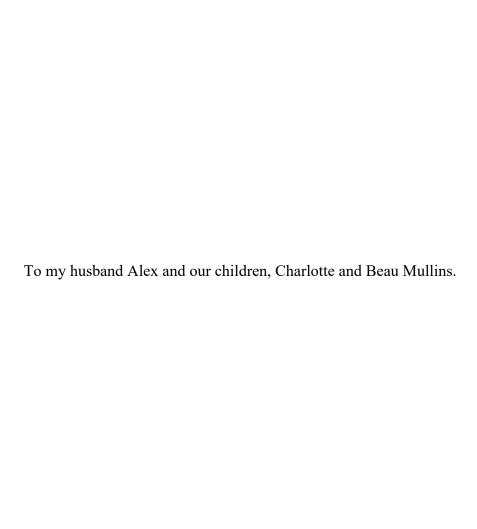

Figure 1 shows a block diagram for AES encryption. After the initial round key addition, a round function is implemented either 10, 12, or 14 times depending on the key length. Each round consists of four transformations: SubBytes, ShiftRows, MixColumns,

and AddRoundKey. The only exception is the final round which does not perform the MixColumns operation.

Figure 1. AES Encryption Block Diagram [29].

# 2.1.1 SubBytes

The SubBytes transformation is a non-linear byte substitution that operates on each byte independently using a substitution table, or S-box. The S-box is constructed by taking the multiplicative inverse in the finite field  $GF(2^8)$  and then applying an affine transformation over GF(2) [27]. An example of a S-box in hexadecimal form is shown in Table 1. An input byte xy results in an output byte that is determined by the value at the intersection of row x and column y. For example, an input byte  $xy = \{b1\}$  would yield the output byte  $\{c8\}$ .

Table 1. S-box Substitution Values for The Hexadecimal Byte xy [27].

|                |   | У  |    |            |    |    |    |    |            |    |            |    |    |    |            |    |    |

|----------------|---|----|----|------------|----|----|----|----|------------|----|------------|----|----|----|------------|----|----|

|                |   | 0  | 1  | 2          | 3  | 4  | 5  | 6  | 7          | 8  | 9          | a  | b  | С  | đ          | е  | f  |

|                | 0 | 63 | 7с | 77         | 7b | £2 | 6b | 6£ | с5         | 30 | 01         | 67 | 2b | fe | d7         | ab | 76 |

|                | 1 | ca | 82 | <b>c</b> 9 | 7d | fa | 59 | 47 | f0         | ad | d4         | a2 | af | 9c | a4         | 72 | c0 |

|                | 2 | b7 | fd | 93         | 26 | 36 | 3£ | £7 | n<br>n     | 34 | a5         | e5 | f1 | 71 | ď8         | 31 | 15 |

|                | 3 | 04 | с7 | 23         | с3 | 18 | 96 | 05 | 9a         | 07 | 12         | 80 | e2 | eb | 27         | b2 | 75 |

|                | 4 | 09 | 83 | 2c         | 1a | 1b | 6e | 5a | a0         | 52 | 3b         | đ6 | b3 | 29 | <b>e</b> 3 | 2f | 84 |

|                | 5 | 53 | d1 | 00         | ed | 20 | fc | b1 | 5b         | 6a | cb         | be | 39 | 4a | 4c         | 58 | cf |

|                | 6 | d0 | ef | aa         | fb | 43 | 4d | 33 | 85         | 45 | £9         | 02 | 7£ | 50 | 3с         | 9£ | a8 |

| $ \mathbf{x} $ | 7 | 51 | a3 | 40         | 8f | 92 | 9d | 38 | £5         | bс | b6         | da | 21 | 10 | ff         | £3 | d2 |

| ^              | 8 | cd | 0  | 13         | ec | 5£ | 97 | 44 | 17         | c4 | <b>a</b> 7 | 7e | 3d | 64 | 5d         | 19 | 73 |

|                | 9 | 60 | 81 | 4 f        | dc | 22 | 2a | 90 | 88         | 46 | ee         | b8 | 14 | de | 5e         | 0b | db |

|                | a | e0 | 32 | 3a         | 0a | 49 | 06 | 24 | 5c         | c2 | d3         | ac | 62 | 91 | 95         | e4 | 79 |

|                | b | e7 | c8 | 37         | 6d | 8d | đ5 | 4e | <b>a</b> 9 | 6c | 56         | £4 | ea | 65 | 7a         | ae | 08 |

|                | С | ba | 78 | 25         | 2e | 1c | a6 | b4 | <b>c</b> 6 | e8 | dd         | 74 | 1f | 4b | bd         | 8b | 8a |

|                | d | 70 | 3e | <b>b</b> 5 | 66 | 48 | 03 | £6 | 0e         | 61 | 35         | 57 | b9 | 86 | c1         | 1d | 9e |

|                | е | e1 | £8 | 98         | 11 | 69 | đ9 | 8e | 94         | 9b | 1e         | 87 | e9 | ce | 55         | 28 | df |

|                | f | 8c | a1 | 89         | 0d | bf | е6 | 42 | 68         | 41 | 99         | 2d | 0f | b0 | 54         | bb | 16 |

# 2.1.2 ShiftRows

In the Shift Rows transformation, bytes in the last three rows of the block are cyclically shifted [27]. The bytes in each row are rotated to the left a certain number of times depending on which row they are in. The first row does not shift, the second shift by one, the third by two, and the fourth by three.

# 2.1.3 MixColumns

The MixColumns transformation operates on each column individually. Each column is treated as a four-term polynomial over GF(2<sup>8</sup>) and is multiplied with a fixed polynomial [27]. The MixColumns transformation is not performed in the final round of AES.

# 2.1.4 AddRoundKey

For the AddRoundKey transformation, a simple bitwise XOR operation is used to add a round key to the data [27]. The round keys are derived from the cipher key using a key schedule that consists of the key expansion and round key selection [28]. The number of round key bits is equal to the block length,  $N_b$ , multiplied by the number of rounds plus one. For example, a 128-bit block length and 10-round implementation would require a round key of 1048 bits. The cipher key is used to generate an expanded key. The first  $N_b$  words of the expanded key are used for the first round key, the second  $N_b$  words for the second round key, etc.

The pseudo code for the AES algorithm is shown in Figure 2.  $N_r$  represents the number of rounds. For 128-bit AES,  $N_r = 10$ . The data block size in words is represented by  $N_b$ . Array w[] contains the key schedule. As shown in Figure 2, all  $N_r$  rounds of the cipher are identical with the exception of the final round. The final round is executed outside of the for loop and does not include the MixColumns transformation.

#### 2.1.5 Side-Channel Leakage

Of the four transformations in the round function, the SubBytes and AddRoundKey operations are the most prone to side-channel leakage. Any operations with output directly related to the secret key are of particular interest to attackers. SubBytes applies a function to each byte of the state. Therefore, each output byte of the SubBytes transformation in the first round can be calculated based on one byte of plaintext and one byte of the key [30]. While simple countermeasures may be used to mask the side-channel leakage of the AddRoundKey function, the non-linearity of the SubBytes transformation makes it difficult to mask [31]. Further, masked S-box

implementations may still leak information via glitches when realized in hardware, requiring the inclusion of additional countermeasures [32].

```

Cypher

INPUT: byte in[4 * N_b], word w[N_b * (N_r + 1)]

OUTPUT: byte out[4 * N_b]

byte state[4, N_b]

state = in;

AddRoundKey(state, w[0, N_b - 1])

for round = 1, step 1 to N_r - 1 do

SubBytes(state)

ShiftRows(state)

MixColumns(state)

AddRoundKey(state, w[round * N_b, (round + 1) * N_b - 1])

end for

SubBytes(state)

ShiftRows(state)

AddRoundKey(state, w[N_r * N_b, (N_r + 1) * N_b - 1])

out = state

```

Figure 2. Pseudo Code for AES Algorithm [33].

# 2.2 Power Analysis

Kocher et al. first introduced power analysis attacks in 1998 [34]. Their work demonstrated that secret keys may be revealed through power consumption measurements of devices. This method of secret key derivation is based on the behavior of semiconductor logic. When charge is applied to or removed from transistors, a current is induced that consumes power and emits EM radiation [34]. This switching activity may vary depending on which operations are being performed on a device as well as the data

being processed. For example, operations that are performed using different circuits would have differing power consumption behavior. Similarly, varying numbers of transistors may experience switching activity depending on the input values being used [35]. These trends in power consumption may be measured by an attacker and used to determine runtime information that may otherwise be assumed to be private. If the device under observation is executing cryptographic processes, the data-dependent power usage may expose the secret key.

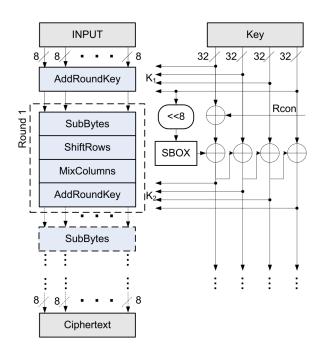

For power analysis attacks, one or more traces must be collected. A trace consists of measurements taken during the execution of the crypto-process being targeted. Mangard et al. [30] presents a block diagram of a typical measurement setup that includes the sequence of interactions for acquiring a power or EM trace. Figure 3 shows this block diagram. In the first step, the cryptographic device is supplied with power and a clock signal. The power measurement circuit or EM probe is also placed during this step while the oscilloscope is initialized in the second. During step 3, commands are sent to the device to start execution. Power consumption is measured at step 4 using the measurement device (i.e., circuit or probe) and oscilloscope set up previously. Power measurement circuits often consist of a small resistor in series with the power supply or ground of the device. The oscilloscope samples the voltage drop across the resistor which is proportional to the power consumption under a constant power supply. EM probes serve as contactless alternatives to power measurement circuits. Using these devices, an oscilloscope measures the output voltage of the probe which is proportional to the device's EM field-inducing power consumption. The PC receives the output of the

cryptographic process in step 5 and the power trace from the oscilloscope in step 6. To collect multiple traces, steps 2 through 6 are repeated as necessary.

Figure 3. Block Diagram of a Typical Measurement Setup for Power Analysis [30].

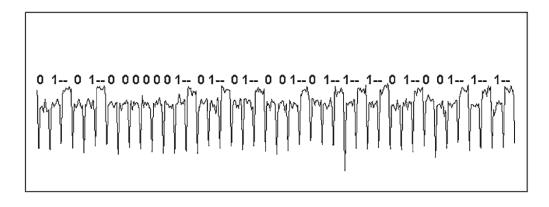

Figure 4 shows an example power trace for AES-128 encryption on a smart card collected by Kocher et al. [35]. The 10 rounds of AES are clearly visible within the trace, a characteristic that can aid an attacker in identifying which encryption algorithm their target is using.

Figure 4. Power Trace from AES-128 on a Smart Card by Kocher et al. [35].

Simple implementations that yield low-noise measurements may be broken with a single trace in a Simple Power Analysis (SPA) attack. The more complex the device, however, the noisier the signal may be. Electronic noise from the power supply and clock generator or switching noise from other components and parallel operations may decrease the signal-to-noise ratio (SNR). A low SNR can be overcome by taking more traces as well as utilizing signal processing methods. Differential Power Analysis (DPA) may be applied in scenarios where SPA falls short. DPA attacks utilize statistical functions that are designed for specific cryptographic algorithms [36].

# 2.2.1 Simple Power Analysis

With simple power analysis attacks [34], the attacker attempts to infer information about a process directly by visually analyzing a single power trace or very few traces. I/O operations and individual rounds have been identified using SPA profiling [35], [37]. Biham and Shamir introduced a profiling method to identify key scheduling [37]. Using their method, data-dependent portions of the trace are found by comparing power traces that process different input data. Key-dependent portions are identified using the traces from multiple devices which each have a unique key. Several models link power consumption to the hamming weight of the processed data or the hamming distance between that data and [38]–[41]. This information leakage that is observable using SPA, can significantly reduce the number of candidates when trying to brute-force search the key [42]. When no countermeasures are implemented, data-dependent instruction sequences may reveal power consumption differences for "0" and "1" key bits. Kocher et al. demonstrates this using a simple implementation of RSA, shown in

Figure 5 [35]. This trace was gathered during the modular exponentiation step of RSA in which squares and multiplies are performed using bits from the decryption key. Per the structure of the algorithm, squares are consumed in each iteration of the loop while multiplications are only performed when the bit of the exponent is equal to 1. This behavior can be directly observed in the power consumption of the unprotected device since the multiplication operation consumes more power than the square, allowing the bits of the decryption key to be identified. In order to find the key, the attacker must have detailed knowledge of the algorithm used by the target. Nevertheless, by revealing data and operation dependent power consumption with minimal traces, SPA techniques may still be leveraged by attackers to aid in more complex SCA attacks against protected implementations.

Figure 5. SPA Leaks in RSA Modular Exponentiation by Kocher et al. [35].

# 2.2.2 Differential Power Analysis

Differential power analysis [34] uses algorithm-specific statistical methods to identify data-dependent correlations in power traces. These attacks differ from SPA

attacks in several ways. Where SPA analyses a single trace over time, DPA requires a large number of traces and is able to find small correlations at specific points [30]. The attacker often does not need to be knowledgeable of details beyond which algorithm is used by the target to perform a DPA attack as opposed to SPA.

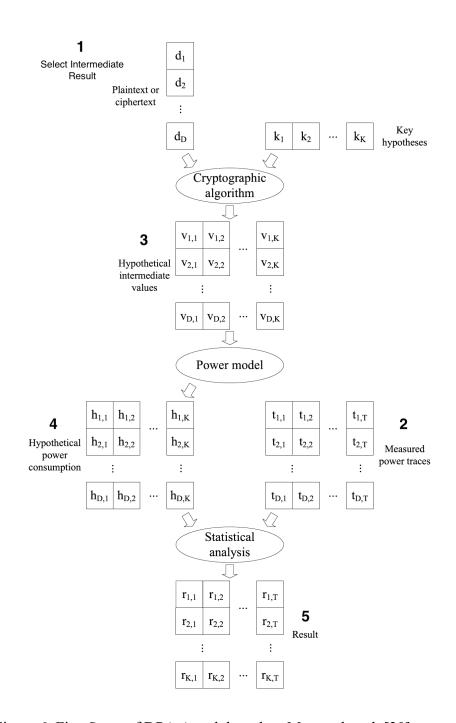

DPA attacks all follow a general procedure. Mangard et al. [30] describe the DPA strategy in 5 steps which are displayed in Figure 6.

**2.2.2.1 Step 1: Select Intermediate Value.** In the first step, the attacker must choose an intermediate result on which to base the attack. This result must be a key-dependent value (e.g., an XOR operation or S-box output for AES) and may be represented as a function of d and k where d corresponds to plaintext or ciphertext and k is the key. **2.2.2.2 Step 2: Collect Traces.** Power consumption measurements are taken in step 2. The attacker must know each data value d that is processed, represented as vector  $\mathbf{d} = (\mathbf{d}_1, \ldots, \mathbf{d}_D)'$ . For each of the D data blocks, a power trace t is taken at each encryption or decryption, t. The power trace for t is t is t in t in t in t is the length of the trace. The resulting power traces for step 2 are shown in Figure 6 as a matrix of size t

**2.2.2.3 Step 3:** Calculate Hypothetical Intermediate Values. The vector  $\mathbf{k} = (k_1, ..., k_K)$  is comprised of all K key hypotheses. Each of these elements are used in the calculation of hypothetical intermediate values f(d, k) in step 3. The results are found in matrix  $\mathbf{V}$  of size  $D \times K$  where  $v_{i,j}$  represents the intermediate value corresponding to  $d_i$  and  $k_j$ . Because  $\mathbf{k}$  includes all possible values for the key, one column in  $\mathbf{V}$  corresponds to the intermediate value that was calculated using the correct key.

T and all use the same secret key.

Figure 6. Five Steps of DPA Attack based on Mangard et al. [30].

# **2.2.2.4 Step 4: Map Hypothetical Power Consumption.** Hypothetical power consumption, matrix **H** in Figure 6, is then obtained for each intermediate value *v* in step

4. This is done using simulation techniques that are based on the attacker's understanding of the target device's behavior. Hamming-distance and Hamming-weight models are the most common power models used in DPA attacks due to their ease of application [30]. Customized power models increase the effectiveness of the attack but are up to the attacker to derive using their knowledge of the device.

Before performing the final step of a DPA attack, the attacker needs to make sure each column  $t_i$  consists of similar operations before calculating the correlation coefficients for matrix **R**. This can be done using a trigger signal to indicate the beginning of a specific operation and initiate measurement with the oscilloscope. In a controlled setting, the attacker would be able to program the device to trigger the oscilloscope consistently before a process. However, an attacker may not have sufficient control over the device for this method. If no other useful signals can be measured from the device, alternatives may be used such as the start signal from the PC to cryptographic device shown in step 3 of Figure 3. Using such asynchronous signals may result in inconsistent delays between the trigger and start of encryption. Attackers must utilize alignment methods when preprocessing their traces to remove these delays and ensure that the power consumption within each column  $t_i$  is dependent on the same operations. 2.2.2.5 Step 5: Comparison of Power Consumption. Finally, in step 5, the hypothetical and actual power consumption for each key hypothesis is compared. That is, the columns of matrix H are compared to the column of matrix T to obtain a matrix of size  $K \times T$ , **R**. Each element  $r_{i,j}$  corresponds to the correlation coefficient of columns  $\mathbf{h}_i$ and  $t_i$  and range in value from -1 to 1. An explanation of the correlation coefficient algorithm can be found in [30]. The attacker assumes that there exists a column  $\mathbf{h}_{ck}$  that

corresponds to the hypothetical power consumption calculated using the correct key. It is also assumed that there exists a column  $\mathbf{t}_{ct}$  that contains power consumption values that depend on the intermediate values selected in step 1. These two columns yield the highest value in matrix  $\mathbf{R}$ ,  $r_{ck,ct}$ . The location of this element in  $\mathbf{R}$  reveals the correct key hypothesis as well the position of the power trace at which intermediate values are processed. If there is no clear maximum value  $r_{ck,ct}$ , more traces may need to be taken to determine the relationship between the columns of  $\mathbf{H}$  and  $\mathbf{T}$ .

# 2.3 Electromagnetic Analysis

While data-dependent current flow serves as the basis for power analysis attacks, it also emits electromagnetic fields that can contain key-revealing information. Simple and Differential Electromagnetic Analysis attacks (SEMA and DEMA, respectively) follow similar statistical analysis methods to SPA and DPA using signals collected from EM field probes [35], [36], [43]. Using EM rather than current-based power measurements for attacks does have its advantages. EM measurements offer a desirable alternative to power consumption when access to the power and ground lines are limited, when the power signal contains too much noise, or when power analysis countermeasures are implemented [43]–[46].

The majority of difference between EMA and power analysis methods are a result of the respective signals' frequency contents. Debeer et al. [45] identify four points of variation: aliasing, alignment, resampling, and probe positioning. Unlike power signals, EM signals maintain their strength at high frequencies. Because of this, samples taken at too low a frequency could misrepresent the original signal, a concept referred to as

aliasing. This may be prevented by excluding high frequencies during trace collection using a low-pass filter between the probe and oscilloscope. Debeer et al. [45] also describe how common techniques for alignment and resampling of power traces are not applicable to unprocessed EM traces due to their lack of low-frequency components, but can be used after some simple preprocessing methods.

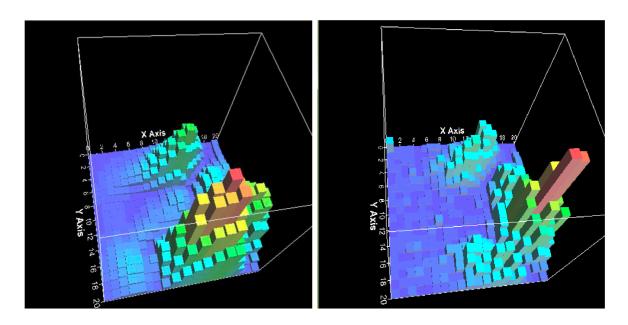

When using a high-resolution EM probe, attackers may perform localized attacks using traces collected from a specific area on the chip [44]. These types of attacks are most successful when the probe is placed above the area of the chip where the sidechannel leakage of interest is strongest [47]. To determine the optimal probe position, measurements are taken across the surface of the chip during the execution of the target process. If the chip hosts a variety of processes with distinct clock frequencies, the EM signal should be filtered to reduce components that are not related to the target operations. Figure 7 shows how the location of the strongest signal is dependent on the clock frequency observed. This XY scan of a smart card by Debeer et al. [45] displays EM signal strengths that indicate the location of the main processor and the cryptoprocessor which run at the external and internal clock frequency, respectively. The location with the strongest signal at the target process's clock frequency indicates the optimal probe position for trace collection. If there are multiple locations that meet this criteria, the position with EM signal behavior that can be related to the target process should be selected [45]. Other works have also identified leakage "hotspots" by performing EM attacks at multiple locations on a chip and plotting the correlation values in a heat map [48], [49].

Figure 7. EM XY Scan at External (Left) and Internal Clock Frequency (Right) [45].

After traces are collected and processed, the statistical analysis for EMA attacks is similar to those of SPA and DPA. In their 2001 work, Quisquater and Samyde [43] attribute this to EM signals containing "at least the same information" as power signals. Agrawal et al. [22] and Gandolfi et al. [44] found that EM emanations contain multiple information leakages that can be used in attacks where SPA/DPA may fall short. Other works comparing leakage models have also found EM signals to contain more information than current-based power signals [50], [51].

# **2.4 Countermeasures**

Side-channel countermeasures aim to minimize information leakage as much as possible. Because leakage cannot be entirely eliminated [20], designers need a method of quantifying how effective their countermeasures are against attacks.

# 2.4.1 Evaluating Countermeasures

Evaluation is an important part of conveying the impacts of countermeasure designs. This is often done using one of two approaches: proving a countermeasure in theory or in practice [52].

Many countermeasures have been shown to be theoretically secure through mathematical proofs [13], [53]–[57]. While leakage may be sufficiently minimized under the assumptions of the proof, the design may still be vulnerable to attacks when realized on a physical device. The models used for these theoretical security evaluations require assumptions that are not able to consider all possible leakage sources. For example, several mathematically secure masking schemes have been found to leak information via logic gate switching activity or hardware glitches [58]–[60]. In their 2012 work [52], Moradi and Mischke further evaluate Prouff and Roche's glitch-free masking scheme [57]. They found that though the scheme was secure under the assumptions of the original article, more realistic analysis revealed exploitable leakages that were out of the scope of the original model. The authors suggest that proposals supported by theoretical security proofs may leverage the real-world perspective of practical analysis to obtain a more thorough security evaluation. Using practical evaluation methods to support the claims of theoretical security proofs has since become more common in the literature [61]–[64].

Practical countermeasure evaluation is done using real side-channel measurement traces. Many researchers quantify the effectiveness of proposed countermeasures using the number of traces needed to break the encryption. This metric provides insight on how much resistance a countermeasure provides against a specific attack. Number of attack

traces may be used to evaluate how a countermeasure compares to an unprotected implementation in a controlled setting. This method may also be used to evaluate incremental changes to schemes such as introducing additional countermeasures for a combined security approach [12], [65], [66]. There are limitations to comparing proposed countermeasures from distinct works using this metric since number of required traces is dependent on several variables including target device, equipment used for trace collection, and analysis methods. Because differential SCA attacks rely on a device-dependent power model, the number of required traces is not necessarily guaranteed for all implementations. It is important that this metric only be used to compare countermeasures that have been implemented on similar devices. Furthermore, a countermeasure that guarantees security within a given number of traces against one attack does not necessarily guarantee the same level of security against other side-channel attack methods [12], [67]. Therefore, it is important for a researcher to make clear the scenarios in which the countermeasure may achieve the presented level of security.

The cost of implementing a countermeasure is another aspect that should be considered by designers. When a user is selecting among effective and usable countermeasures, the security-cost trade-off may be the deciding factor. Many researchers describe countermeasure costs in terms of number of specific logic elements. However, hardware requirements for a given implementation may vary among devices. In [68], Katashita et al. show that the lookup table specifications for two FPGAs result in large resource utilization differences for the same circuit. Similar to the security metrics discussed earlier, resource utilization may be used to describe costs relative to an unprotected implementation but have limitations due to their device-dependency. Other

cost metrics used to evaluate countermeasures include performance and storage overhead [49], [66], [69].

# **2.4.2** Countermeasure Techniques

Side-channel analysis countermeasures focus on minimizing the correlation between key-dependent operations and the data that is leaked. Techniques traditionally fall into one of two categories: hiding and masking. In this section, both categories are discussed as well as methods specific to EMA prevention.

Hiding countermeasures involve decreasing the signal-to-noise ratio for a sidechannel. This is often done through leveling techniques which decrease the signal or randomization techniques that increase noise level [70]. Many leveling techniques have been developed to minimize key-dependent fluctuations in power consumption and execution timing. Some examples include using low-drop-out voltage regulators to maintain a constant voltage across encryption blocks [71], dual-rail pre-charge logic to control the number of observed transitions on a power side-channel [72], and constanttime operation to thwart timing attacks [73], [74]. Some randomization techniques include shuffling operations [75], insertion of dummy rounds [76], and random delay insertion [77] to introduce noise to hinder power and timing attacks. Some reconfigurable hardware has the advantage of being able to implement countermeasures that leverage dynamic reconfiguration capabilities. This feature of the device can be used to introduce randomness in timing, target location [66], and hardware structure [78]. Though all of these countermeasures increase resistance to side-channel attacks, they would need to be implemented in combination with other countermeasures to sufficiently reduce the risk of leaking key-revealing information [12], [65], [76], [79].

One of the most common countermeasures for side-channel attacks is masking. This method involves randomizing intermediate values so that there are no dependencies between side-channel info and the actual secret key. This countermeasure is implemented at the algorithm level and includes methods such as Boolean [56], [78], [80], multiplicative [81], [82], and combinations of the variants [83], [84]. Like hiding schemes, masking countermeasures are also often implemented in combination with other countermeasures to reduce side-channel related risks [10], [12], [85]. When masking schemes are realized in hardware, logic gate switching activity (i.e., glitches) can leak information that could be leveraged by a side-channel attack [58]–[60]. To overcome this risk, masking schemes for hardware should be designed to either work in the presence of glitches [86] or avoid them altogether [18], [87].

Many researchers consider EM analysis a variant of power analysis, grouping methods and countermeasures for both [35], [88]. The similarities between the side-channel types allow for their countermeasures to be inclusive against standard attacks. However, it has been shown that implementations with DPA countermeasures may be vulnerable to more advanced localized EM attacks [23], [24]. In [23], Specht et al. use localized EMA to isolate the leakage from separate shares in a threshold implementation countermeasure. Their attack combines leakage from multiple probes to break the scheme. Another example is dual-rail logic which has been shown to prevent power attacks becomes vulnerable to localized EM attacks due to placement and routing imbalances [24]. The shortcoming of power countermeasures against localized EMA attacks highlights the need for an additional family of countermeasures.

Existing countermeasures against EMA fall into two categories similar to masking and hiding: signal information reduction and signal strength reduction [22]. Signal information reduction involves randomization and refreshing techniques that are also used for power SCA defense (e.g., additional noise, masking). Signal strength reduction includes techniques that are unique to EMA prevention such as spatial randomization and shielding.

In [66], Mentens et al. introduce "spatial jitter" which randomizes the location of functional blocks dynamically to prevent EMA. Li et al. [48] propose a spatial randomization of dataflow in which data bytes are randomly assigned to AES S-boxes that are places throughout the FPGA fabric. By randomizing the location at which the target logic block is placed, EM leakage hotspots are reduced and the optimal probe location for the attack is difficult to determine.

While traditional SCA countermeasures aim to reduce the usability of a captured signal, shielding techniques work to prevent signal capture altogether. In [89], Das et al. propose a Signature aTtenuation Embedded CRYPTO with Low-Level metAl Routing (STELLAR). Their technique prevents leakage through EM radiation by routing the design to low-layer metals as well as including signature attenuation hardware to hide the signal. Shielding designs have been proposed that also include an anti-tampering mechanism [90], [91]. The shield utilizes substrate layers that allow for the conduction of an integrity related signal that is broken when the shield is removed. This method was initially proposed as a method to prevent fault injection attacks but could also be used to prevent an attacker from removing shields intended to block EM radiation if incorporated by vendors as suggested in [92]. Miura et al. [93] propose an EM attack sensor which

detects when a near-field EM probe approaches the chip. This concept is based on previous work which demonstrates that a probe cannot measure the original EM field without disturbing it [94]. Though shielding concepts are effective at limiting EM attacks, they incur high packaging costs. The inclusion of detection mechanisms is also accompanied by additional overhead.

# **2.5 Circuit Variants**

Circuit variants refer to designs that are structurally different but have similar functionality. These designs may be diverse in logic gate types, size, and include redundancies all of which result in variations in path delays and consequentially, sidechannel behavior.

The goal of delay-based countermeasures is to reduce the ability to align traces collected by an attacker [95]. Randomizing the timing behavior of an implementation results in a desynchronization effect that introduces noise within the trace set [7]. The ability to align the portion of the traces being targeted is a crucial step in successfully performing a differential analysis attack. If a trace is unable to be aligned with a selected reference trace within the set, it is discarded. If a large portion of the traces within the set are discarded, the attack cannot be reliably performed. Delay-based countermeasures have been implemented in both software and hardware schemes through random delay insertion, random process interrupts, and temporal jitter [7]–[9], [21], [96].

Delay characterizations may also be observed and exploited at the circuit level of designs. In combinational logic, propagation delay refers to the maximum time it takes for an output to reach its final value after an input switch and is the sum of the delays

trough each element on the critical path [97]. The delay characteristics of logic gates can vary from nanoseconds to the picosecond range depending on the technology being used [98]. Therefore, the timing behavior of a circuit may be directly influenced by the types of gates used to construct it as well as the number of gates. Existing works have shown that variations in gate compositions are translated to the timing behavior of a circuit which may be leveraged in side-channel countermeasures [88].

## 2.5.1 Circuit Variant Countermeasures

In 2003, Benini et al. introduce the concept of mutating a data path using power-masked modules [99]. These scheme combines a fully functional unit A and a smaller block B that implements the most typical behavior of A but consumes less power. By activating block B rather than block A when inputs allow, the same functionality can be obtained with a randomized power profile. This concept was later extended to reconfigurable hardware by Stöttinger et al. to protect AES [100]. Their approach shuffles modules to tamper with correlation between real and estimated power consumption levels, thwarting DPA attacks.

In [88], Bow et al. utilize two methods of circuit variance for their countermeasure: synthesis-directed and circuit-directed. The synthesis-directed technique involves generating netlists for S-boxes based on a behavioral description and a standard cell library. For each netlist, the available logic gates for the standard cell libraries were changed, forcing the synthesis tool to utilize different logic gates for the implementation. In the circuit-directed technique, a clock delay circuit is used to add random delays along paths within the design. Three synthesis-driven implementations with S-boxes at different

locations for each are combined with three circuit-driven implementations to obtain twelve static versions of the AES engine. Correlation power analysis (CPA) attacks are applied to a trace set composed of measurements from all twelve AES versions. The scheme improved resistance to CPA by more than two orders of magnitude over unprotected AES. Leakage present in the circuit-directed variants suggest that this method alone would not provide sufficient protection against power analysis attacks. However, the fully synthesis-directed approach is limited to only three versions.

Hettwer et al. use a similar synthesis-directed technique for generating diversity [49]. For each variant, 80% of the slices for the defined reconfigurable area are prohibited for placement until after the other 20% has been placed. This method is used to create 128 versions of the AES engine that are randomly selected for configuration. The placement and route (P&R) restrictions for the bitstream generation enabled a spatially randomized design that is effective against localized EMA and fault injection. However, resistance to CPA is only improved by a factor of 2-3, requiring additional countermeasures to sufficiently prevent such attacks.

The lack of power resistance of the approach in [49] may be attributed to the method of variant generation. By only implementing P&R specifications, it is likely that there is minimal diversity within the bitstreams in terms of gate composition. A lack of diversity in this context would result in similar power profiles between the implementations even though they are mapped throughout the FPGA fabric. Therefore, extraction of the key is still possible when an attack is performed using the power side-channel rather than localized EM. The SPREAD approach [88] was able to achieve a much higher level of resistance with significantly fewer versions of AES. This may be

attributed to the gate-level adaptations provided by the synthesis- and circuit-driven techniques used. It is possible that the countermeasure presented in [49] could be improved using different circuit variant generation schemes (e.g., those used in [88]), but diversity would be limited by the size of the circuit since the entire AES core is replaced.

# **2.6 Moving Target Defense**

Cyber defense includes three complimentary categories: proactive, active, and regenerative [101]. In this cohesive model, proactive measures harden the system to make it more resilient against attacks, active defenses involve attack detection and real-time responses, and regenerative techniques are used to restore the system after an attack. Each of these techniques are reactive in nature, designed to patch known vulnerabilities of a system or respond to an attack that has been detected [102].

A Moving target defense (MTD) is a more proactive approach. System changes are made over time to create a varying attack surface [103]. Rather than hardening specific aspects of a configuration, MTD enables a complex target that makes attacks more difficult to complete. Modifying characteristics of the system pseudo-randomly disadvantages the attacker in the reconnaissance phase [104]. The time attackers have to discover and exploit vulnerabilities is limited in an MTD system. Persistence is also more difficult for cyber-attacks since any privileges gained may be lost when the system is altered [105]. MTD techniques may also be used to introduce additional protection to systems in which other security mechanisms are already implemented [102].

MTDs have been introduced at many different levels to protect a variety of systems and devices. Address hopping and port hopping may be used to protect networks

[106]–[108]. Address space layout randomization, data space randomization, and instruction set randomization are deployed in most current operating systems [109]–[111]. MTD techniques have also been used to provide low-cost side-channel attack prevention in several contexts including cloud architectures [112], processor caches [113], embedded systems [69], [114], among others [115].

Many cryptographic SCA countermeasures have also incorporated MTD methods through refreshing parameters. Masking schemes, for example, need to implement a sufficient level of refreshing in order to remain effective [62], [116], [117]. Cryptographic targets may also disrupt SCA by updating the secret key. This concept, called key refreshing, involves generating new session keys from a nonce and master key to thwart SCA attacks. The principal behind using re-keying methods is that the burden of protection is shifted from the cryptoprocess to the easier to secure re-keying algorithm [118]. The rate of key-refreshing determines the window in which an attack can occur. While some works propose a new key for each block of plaintext [119], frequent updates can introduce significant costs to the system since the nonce would need to be synchronized across all parties [114]. It is also important that the key update function is secure against SCA to prevent the extraction of the master key [120]. Recent works have proposed securely rekeying at an interval that is based on the number of required traces to complete a power analysis or EMA attack [114], [121]. Similar countermeasures involving register renaming [122], [123] and algorithm-level parameter randomization [26], [124]–[127] have been proposed which pseudo-randomly alter characteristics about the system that are leveraged in side-channel attacks.

Dynamic logic reconfiguration (DLR) has been used to implement FPGA-oriented MTDs in which redundant logic blocks are placed throughout the FPGA fabric and are randomly selected for operation at runtime. This method has been used to hinder hardware trojans [128], [129] and provide dynamic side-channel countermeasures in hardware [48], [69].

In their 2019 work, Li et al. [48] propose a DLR-based spatial randomization technique to minimize leakage that may be exploited through localized EM attacks. In this MTD countermeasure, a permutation network is used to randomly assign data bytes to sixteen AES S-boxes and a second permutation network restores the order of the bytes. By using logic gates rather than look-up tables to synthesize S-boxes, the designer is able to select the location for each S-box, allowing maximum distance between each component. Two attack scenarios are simulated: one where the attacker has full access to the device, enabling a profiling attack, and a second black-box attack. Both attacks perform correlation analysis using EM traces. When determining the optimal location of the probe, the profiling attacker observes no distinct hotspots while the black-box attacker observes one. This hotspot is linked to the state registers' location which is unaffected by the spatial randomization in the S-box layer. The countermeasure increases the number of required attack traces by 150X for the profiled attack and 3.25X for the black-box attack. Further work is needed to determine if a similar countermeasure can be applied to reduce the leakage of the state registers. Implementing another countermeasure in combination with the spatial randomization to further increase the number of attack traces is another open area of research.

The dynamic nature of MTDs enables changes in systems that would otherwise be static. However, there exists a family of devices that allow hardware configurations to be altered and/or placed at runtime. This feature, called dynamic partial reconfiguration, supports the implementation of more complex MTDs in hardware.

# 2.6.1 Dynamic Partial Reconfiguration

Some system-on-a-chip (SoC) and field programmable gate-arrays (FPGA) have the capability to alter portions of their hardware configuration during run-time without interrupting the rest of the chip [130]. This feature, referred to as dynamic partial reconfiguration (DPR) and is different from the previously discussed DLR in that DPR schemes change the placement and routing of functions where DLR functions are static. DPR can be utilized to implement complex moving target defense techniques in hardware designs.

In [66], Mentens et al. propose the first DPR countermeasure to reduce sidechannel leakage. Their approach introduces temporal jitter by randomly adding registers between functional blocks to introduce delays. The countermeasure also increases resistance to fault injection by altering the location of functional blocks which is referred to as spatial jitter.

Stöttinger et al. [131] propose a SPA and DPA countermeasure for elliptic curve cryptography (ECC) that combines the techniques presented in [66] and by Benini et al. in [88]. This countermeasure introduced temporal jitter as well as parallel modules that can be dynamically reconfigured with implementation variants. In a later work, Stöttinger et al. [100] adapted the DPA countermeasure presented in [99] for reconfigurable

platforms. After each encryption, the AES countermeasure uses DPR to reconfigure one of the two S-boxes in the FPGA fabric with a new implementation. Each implementation is functionally the same but have different side-channel behavior, reducing the correlation between real and estimated power consumption values.

Similar to the work presented in [48], Bloom et al. [132] propose a scheme in which spatial randomization is used to protect a device. This countermeasure, however, uses DPR rather than DLR to change the location of IP blocks to prevent design- and fabrication-time trojans from attacking fixed structures in the FPGA. Their hardware abstraction layer decrypts bitstreams for new IP cores, finds an unused random location, completes place and route for the core, and deletes the previous one.

Hettwer et al. [49] propose a countermeasure against physical attacks in which the entire AES core is replaced with a circuit variant implementation over time. Though power SCA resistance was only increased by at most a factor of 3, the random changes to the physical layout of the configurations made this countermeasure especially effective against localized EMA and fault injection. Localized EMA was performed at 135 locations across the chip. The highest correlation value obtained using 5000 traces was 0.1 for the reference implementation and 0.06 for the countermeasure. The probability of injecting a fault is also reduced to less than 1% with the countermeasure implemented. The replacement of the entire AES core results in encryption stalls during reconfiguration as well as a large storage overhead for the bitstreams.

Huss et al. [133] describe a concept for a mutating runtime architecture which combines three countermeasures for AES. Recent work [88] presents a similar approach for side-channel power resistance for encryption algorithms using DPR called SPREAD.

This countermeasure utilizes an extra copy of an AES S-box to allow partial bitstream reprogramming. A customized tool is used to create relocatable bitstreams which will allow the same bitstream to be programmed at different locations by changing a frame address. A multiplexing scheme is used to isolate the redundant S-box so that it can be replaced with a functionally equivalent variant of one of the other sixteen S-box structures and reincluded in the AES engine. Another S-box is then randomly selected to be reprogrammed as the process is repeated. The work published in [88] displays a proof of concept in which 12 versions of an AES engine are tested against DPA and CPA. A fully operational version is needed to determine the actual number of traces required to break the implementation. Further research is also needed to determine how susceptible this countermeasure is to localized EMA.

Besides SCA resistance, an important consideration when designing and selecting DPR-based countermeasures is their cost. Even though DPR schemes may have less inactive logic consuming real-estate than DLR schemes, they can still be expensive which can limit their applicability and usefulness [132]. Storage overhead for reconfiguration bitstreams can significantly increase the requirements for an implementation. For example, a partial bitstream for the scheme proposed in [49] has a size of 616 MB, requiring over 700 MB to store all 128 variants. This requires external flash to be able to implement the countermeasure as it is designed. The authors also suggest implementing additional countermeasures to increase power SCA resistance which would further increase the cost. An alternative is presented in [88] in which only S-boxes are reconfigured, but further research is needed to determine how much diversity is sufficient in a fully dynamic scheme. Further, the timing and throughput overhead

should also be considered in the design process. The setup time for DPR schemes as well as any function stalls for reconfiguration can make the security-efficiency trade-off less desirable. When composing a countermeasure involving DPR, minimizing the number of required bitstreams and reconfiguration frequency may lead to a design that is applicable to a wider variety of reconfigurable devices.

## **CHAPTER III**

## RESEARCH OBJECTIVE

Related works have shown that individually, spatial randomization and implementation diversity may be used to obfuscate optimal EM probe positions and increase resistance to power analysis attacks, respectively. However, countermeasures that have attempted to combine these concepts have yet to display resistance to both power analysis and localized EMA attacks in an efficient manner. A spatially randomized implementation may hinder an attacker using a high-resolution EM probe, but if the power consumption behavior does not vary between implementations, an attacker may still perform a sidechannel attack that is not location-dependent (i.e., a power analysis attack). This scenario is unfavorable since the equipment to perform a power analysis attack is simpler and more affordable than that of a localized EM attack [30], [47]. Therefore, it is in the researcher's best interest to ensure that defenses against localized EM attacks are also resistant to power attacks.

The goal of this research is to increase the complexity of both power and localized EM SCA by introducing structural and spatial randomization of the target hardware. We propose a countermeasure that utilizes randomly located S-box circuit variants in the PL side of an SOC. The focus of this approach is limiting the presence of EM "hotspots" that indicate favorable candidates for high-resolution probe placement as discussed in Section

2.2. One S-box will be selected and used as the output for the encryption run, mimicking the behavior of a MTD, and increasing the number of traces needed to perform a localized EMA attack.

Power analysis resistance will be introduced to the design through the variation in circuit structure and composition of the S-boxes. By diversifying the implementations at the gate-level, we aim to vary the power behavior observed by the attacker and disrupt the correlation between the hypothetical and actual power consumption. For this countermeasure, all circuit variants will be generated using a program encryption toolkit (PET) that allows for multiple criteria to be set including subcircuit selection and replacement size, gate type, and fan-in. The influence the variants have on side-channel behavior will be determined by implementing multiple AES versions, each with a different S-box variant. EM traces will be collected for each and their behavior compared.

A practical countermeasure evaluation will be conducted to determine the implementation's resistance to power and localize EM analysis. Power and EM traces will be collected for both a control and countermeasure implementation. Usable trace sets will be determined by the inclusion of AES artifacts such as repeated round structures visible within the traces. DPA and DEMA attacks will be performed on the usable trace sets using first order analysis. The number of traces needed to obtain sufficient confidence values of key candidates to differentiate between correct and incorrect bytes will be used to quantify the success of the attacks. During the acquisition step of the DEMA attacks, the optimal probe placement will be determined as well as any leakage hotspots identified. These characteristics will be used to investigate the level of hotspot

obfuscation provided by the countermeasure. The objectives of this research are shown in Table 2.

Table 2. Research Objectives for Circuit Variant Moving Target Defense

| Objectives | Description                                                         |

|------------|---------------------------------------------------------------------|

| 1.         | Circuit Variant Side-Channel Behavior Study.                        |

| 1.1        | Generate S-box circuit variants.                                    |

| 1.2        | Design control AES implementation.                                  |

| 1.3        | Collect EM traces for each AES-S-Box version.                       |

| 2.         | Investigate EM Hotspots.                                            |

| 2.1        | Modify AES core to accommodate multiple S-box instances.            |

| 2.2        | Randomly place S-box P-blocks in programmable logic.                |

| 2.3        | Collect EM spectralintensity graphs of both implementations.        |

| 3.         | Assess Trace Sets for Usability.                                    |

| 3.1        | Identify AES artifacts within the trace sets.                       |

| 3.2        | Determine the target window for first order analysis.               |

| 4.         | Differential First Order Analysis Attacks.                          |

| 4.1        | Improve SNR of collected trace sets.                                |

| 4.2        | Evaluate attack success using confidence values for key candidates. |

This research differs from related works in both the circuit variant generation specifications and the increased resistance to localized EM attacks. By limiting the design to only altering S-boxes, we expect to reduce the storage overhead of the scheme proposed in [49]. Another distinction from [49] is the criteria for generating variants which will focus on gate-level diversity and circuit size. This is expected to further increase resistance to power attacks. This design aims to implement a DLR scheme where

the SPREAD scheme in [88] utilizes a custom synthesis tool flow to create relocatable bitstreams. Though this may result in less resource usage for an active implementation in SPREAD, the reconfiguration logic may introduce noise in the side-channel. The lack of a reconfiguration controller in the proposed DLR design leaves more area in the PL for S-box variants. This research will also only utilize a synthesis-driven circuit variant generation method as opposed to SPREAD which also includes additional hardware for a circuit-driven approach. To introduce gate-level diversity, we will use a program encryption toolkit [134] to generate equivalent circuits that vary in size and composition where the method in [88] exclude specific gate types when generating netlists for each version. Lastly, the proposed countermeasure will be not only be assessed for power analysis resistance but for localized EM analysis resistance as well.

## **CHAPTER IV**

## S-BOX CIRCUIT VARIANTS

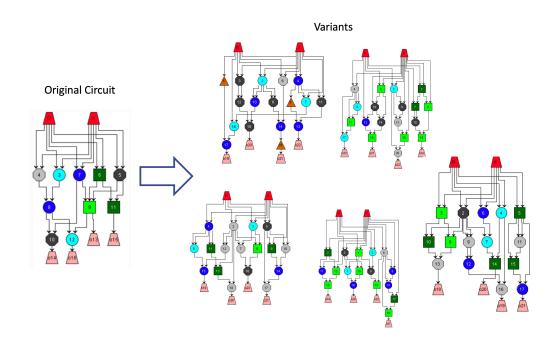

This chapter details the generation of AES S-box circuit variants (CVs) using a Program Encryption Toolkit (PET). In particular, the Iterative Selection/Replacement feature of PET is described. The influence the CVs have on side-channel properties for an AES implementation are also studied.

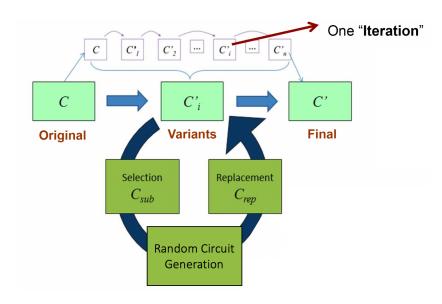

# 4.1 Program Encryption Toolkit

PET is a customized Java application that includes features to generate random equivalent circuits based on an ICAS BENCH format netlist [134], [135]. The netlist used as the reference circuit for our S-box consisted of a gate-level implementation that follows the behavior of the standard AES SubBytes function shown in Table 1. PET's Iterative Selection/Replacement (ISR) feature was used to diversify subcircuits within the S-box structure. In this method of variant generation, shown in Figure 8, a user specifies a size range for randomly selected subcircuits and a number of iterations for the process [136]. For each iteration, a subcircuit is selected and replaced by a randomly generated equivalent circuit. Characteristics of the random circuit may be set by the user including number of gates, max fan-in, as well as gate types. The circuit variants used in this research were generated using replacements with a max fan-in of two, selection size of

two, replacement size of six, and only excluded BUFFER gates. In addition to the original, five variants were used in the study that were generated using 100 iteration intervals ranging from 100 to 500 ISR iterations.

Figure 8. Iterative Selection/Replacement

The total number of gates for each S-box variant are shown in Table 3. Because the configuration for the ISR was to replace two-gate subcircuits with six-gate variants, the increase between each S-box version was expected to be at least 400 gates. However, the results shown in Table 3 reveal the gate increases to be well over that estimate. This is due to PET's Merged Signature circuit generation method, an example of which is shown in Figure 9. In the Merged Signature method, a circuit is generated for each function of the selected subcircuit and then merged to form a single circuit. If the selected subcircuit is composed of two functions, each of those may be replaced in one iteration. This accounts for the increase in gates for each S-Box being much greater than 400.

Table 3. Number of Gates for S-Box Circuit Variants

| Iteration | S-Box | Number of Gates |

|-----------|-------|-----------------|

| Original  | S0    | 1136            |

| 100       | S1    | 1914            |

| 200       | S2    | 2696            |

| 300       | S3    | 3473            |

| 400       | S4    | 4248            |

| 500       | S5    | 5025            |

Figure 9. Merged Signature Circuit Generation. 5 Gates with a Max Fan In of 2.

# **4.2 Side-Channel Properties**

Using PET, a VHDL source for each S-box variant was generated. Each of these VHDL S-boxes were used in their own AES core that was designed using Xilinx Vivado Design Suite 2018.1. By default, Vivado works to optimize designs for timing, power

consumption, and logic resources during synthesis and implementation [137], [138]. Therefore, these setting must be overwritten or bypassed to prevent Vivado from removing redundant logic that may have been added by PET. Custom synthesis strategies and implementation settings may be created, but logic optimization may still be automatically applied, potentially eliminating the intended effects. The best way to prevent logic from being removed is to add a DONT\_TOUCH attribute to items that should not be modified. Because there is not enough available logic on the SOC to set each wire within the S-box source as DONT\_TOUCH, the entire entity was specified as such instead as shown in Figure 10. This still allows Vivado to implement the designs as lookup tables (LUTs) on the device. However, the resulting Boolean logic for the LUTs vary between S-box designs. An example is given in

Table 5. Power consumption estimates were also provided by Vivado in the implemented design. The largest difference in dynamic power consumption was 1 mW. This could be due to the designs being implemented as LUTs rather than the large PET-generated circuits.

```

library IEEE;

use IEEE.std_logic_1164.all;

entity AES_SBOX1 is

inl

in

Std_Logic;

Std_Logic;

in3

in

Std Logic;

Std_Logic;

in5

in

out1199

Std Logic

out1200 :

out1202

out

Std Logic:

out1204

out

Std_Logic;

out1206 :

Std Logic)

attribute dont_touch : string; attribute dont_touch of AES_SBOX1 : entity is "true";

end AES SBOX1:

```

Figure 10. DONT\_TOUCH Logic For S-box 1.

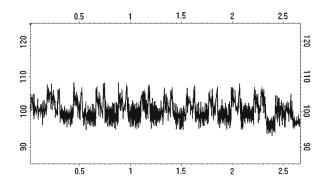

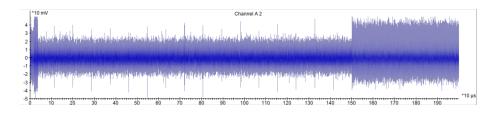

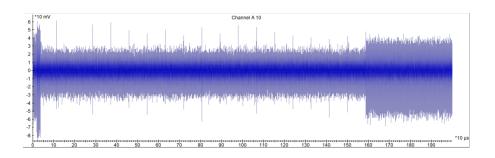

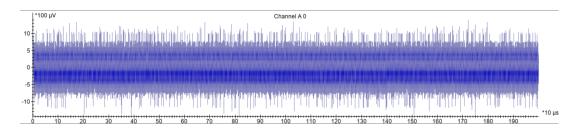

Once placed on the SOC, the execution time for each S-box version was measured. This was done using the trigger signal of the design which is high during the AES encryption. The measurements may be found in Table 4 The differences are on the order of 10 µs but may still be observed in the EM trace. The EM traces for S-box 0 and S-box 5 may be found in Figure 11 and Figure 12, respectively.

Table 4. Execution Times for AES S-box Variants.

| S-Box | Execution Time (ms) |  |

|-------|---------------------|--|

| S0    | 1.579               |  |

| S1    | 1.560               |  |

| S2    | 1.616               |  |

| S3    | 1.631               |  |

| S4    | 1.631               |  |

| S5    | 1.658               |  |

Figure 11. EM Trace of S-box 0.

Figure 12. EM Trace of S-box 5.

Table 5. LUT Equations for S-boxes 1 and 5.