## Design of new SPADIC front-end boards for TRD readout

*M. Krieger*<sup>\*1</sup><sup>1</sup>ZITI, University of Heidelberg, Germany

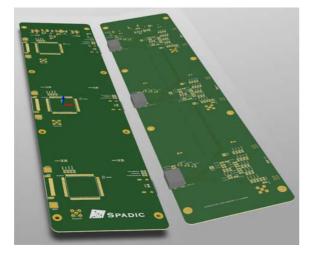

Figure 1: Rendered view (front and back side) of the new FEB for 3 packaged SPADIC 1.0 chips.

The design of the TRD subsystem foresees the use of different types of modules and front-end boards (FEBs). In order to keep the hit rates per channel within controlled limits across the detector, the modules and FEBs cover a range of different channel densities.

This means that between 4 and 10, or even more, SPADIC chips must be assembled on one FEB of approximately 50 cm length. For testing the type of FEB with the lowest SPADIC density, for 2014 a prototype FEB is designed that connects one SPADIC every 114 mm.

As the first prototype of such a multi-chip FEB, a new PCB holding 3 SPADIC chips with this pitch has been designed (Figure 1). It contains voltage regulators and power-on sequencing logic shared by all SPADICs, and for each SPADIC individually a TRD input connector, decoupling capacitors, charge injection, and an HDMI connector for CBMnet data links. Neighboring SPADICs are connected to allow exchange of trigger signals. Additionally, a smaller version of the FEB containing only one SPADIC has been designed (Figure 2b).

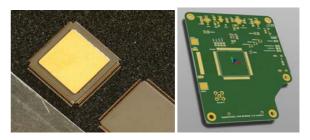

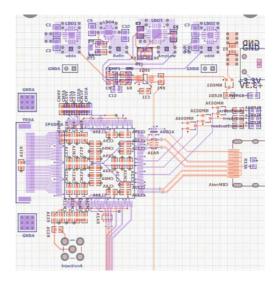

For the evaluation of integration options and a simplified FEB assembly, most of the remaining SPADIC 1.0 chips have been cased into ceramic quad-flat packages with 176 pins (QFP176, Figure 2a) and 23 mm  $\times$  23 mm in size. This allows saving space by placing the decoupling capacitors on the opposite size of the PCB directly beneath the package, as shown in Figure 3.

Figure 2: (a) SPADIC 1.0 chip assembled in QFP176 package. (b) The smaller version of the new FEB for only one SPADIC 1.0 chip allows easier testing.

Figure 3: Layout of the top third of the new PCB, containing the voltage regulators and one of three SPADIC chips.

This new 3-SPADIC FEB has a size of  $83 \text{ mm} \times 339 \text{ mm}$  and requires 4 layers. Using the same layout, the SPADIC pitch could be reduced to approximately 60 mm.

## References

- M. Krieger, P. Fischer, "Commissioning of the SPADIC 1.0 Amplifier/Digitizer Chip", this report.

- [2] D. Emschermann, "Development of the Münster CBM TRD prototypes and update of the TRD geometry to version v13a", CBM Progress Report 2013, p. 53

- [3] F. Lemke et al., "Status of the CBMnet based FEE DAQ readout", this report.

<sup>\*</sup> michael.krieger@ziti.uni-heidelberg.de