**Review Article**

Available online at www.ijournalse.org

**Emerging Science Journal**

(ISSN: 2610-9182)

Vol. 6, No. 1, February, 2022

# A Review on Multilevel Inverter Topologies

# Afshin Balal <sup>1\*</sup>, Saleh Dinkhah <sup>2</sup>, Farzad Shahabi <sup>3</sup>, Miguel Herrera <sup>1</sup>, Yao Lung Chuang <sup>1</sup>

<sup>1</sup> Texas Tech University, 2500 Broadway, 79409, Lubbock, Texas, United States.

<sup>2</sup> Santa Clara University,500 El Camino Real, 95053, Santa Clara, California, United States.

<sup>3</sup> University of South Florida, Fowler Avenue, 4202, Tampa, Florida, United States.

#### Abstract

In this paper, a brief review of the multilevel inverter (MLI) topologies is presented. The two-level Voltage Source Inverter (VSI) requires a suitable filter to produce sinusoidal output waveforms. The high-frequency switching and the PWM method are used to create output waveforms with the least amount of ripples. Due to the switching losses, the traditional two-level inverter has some restrictions when running at high frequencies. For addressing this problem, multilevel inverters (MLI) with lower switching frequencies and reduced total harmonic distortion (THD) are employed, eliminating the requirement for filters and bulky transformers. Furthermore, improved performance at the high switching frequency, higher power quality (near to pure sinusoidal), and fewer switching losses are just a few of the benefits of MLI inverters. However, each switch has to have its own gate driver for implementing MLI, which adds to the system's complexity. Therefore, reducing the number of switches of MLI is necessary. This paper presents a review of some of the different current topologies using a lower number of switches.

#### **Keywords:**

Traditional Two-Level Inverters; Multilevel Inverter (MLI); High Power Application.

#### Article History:

| Received:       | 04 | September | 2021 |

|-----------------|----|-----------|------|

| <b>Revised:</b> | 09 | November  | 2021 |

| Accepted:       | 23 | December  | 2021 |

| Published:      | 01 | February  | 2022 |

### **1- Introduction**

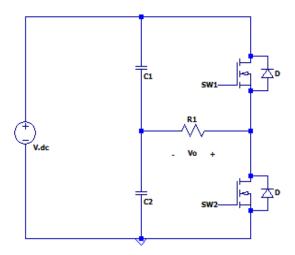

Inverters are used in applications, including air conditioning, uninterruptible power supply (UPS), high-voltage dc power (HVDC) transmission lines, electric cars, battery storage, and solar panels [1, 2]. Inverters are categorized as square-wave inverters, sinusoidal two-level pulse width modulation (PWM) inverters, and multilevel inverters [3, 4]. Power electronics, DC-DC converters, and inverters have seen a surge in the study due to the scarcity of fossil fuels and the diversity of renewable energy sources. The converters must be very dependable, efficient, and offer excellent performance due to the high prices of renewable energy supplies [5]. It must generate sinusoidal output waveforms that are synced with the national power grid [6]. Figure 1 shows the circuit diagram of a two-level inverter.

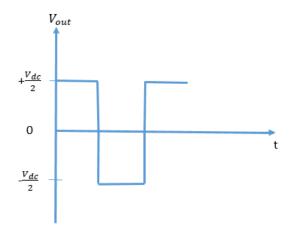

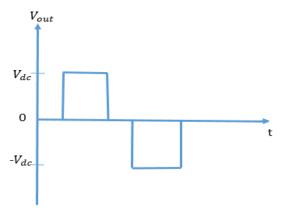

When SW1 is ON, then  $V_0 = +(V_{dc}/2)$ , and when SW2 is ON,  $V_0 = -(V_{dc}/2)$  [7, 8]. No need to mention that the conventional two-level inverters without pulse width modulation (PWM) produce a square wave output voltage of two levels, as depicted in Figure 2.

This traditional inverter runs at a high switching frequency for high-power applications, with significant switching losses [9]. Harmonic distortion and excessive stress on power semiconductors are other issues. Because of these issues, connecting power electronic switches to the high-voltage grid is not feasible [10, 11]. These issues necessitate the use

<sup>\*</sup> CONTACT: afshin.balal@ttu.edu

DOI: http://dx.doi.org/10.28991/ESJ-2022-06-01-014

<sup>© 2022</sup> by the authors. Licensee ESJ, Italy. This is an open access article under the terms and conditions of the Creative Commons Attribution (CC-BY) license (https://creativecommons.org/licenses/by/4.0/).

of MLI inverters with different topologies. Improved performance at the high switching frequency, reduced harmonic distortion, higher power quality (near to pure sinusoidal), and fewer switching losses are just a few of the benefits of MLI inverters [3, 12]. However, each switch has to have its own gate driver for implementing MLI, which adds to the system's complexity. Therefore, reducing the number of switches of MLI is necessary [3, 13, 14]. This paper presents a review of some of the different current topologies using a lower number of switches.

Figure 1. Diagram of a two level inverter

Figure 2. The output voltage of a two-level inverter

# 2- Three Types of Classical MLI

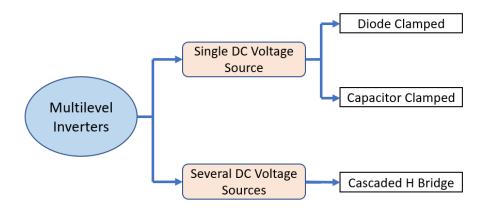

From various dc input sources, a multilevel inverter creates a smooth sinusoidal waveform. In addition, multi-level inverters play an important role in high-power industrial applications [15, 16]. Diode-clamped, flying capacitor (capacitor-clamped), and Cascaded H bridge multilevel inverters are the most common topologies [17]. The scheme of multilayer inverters is shown in Figure 3.

Figure 3. Multilevel inverter scheme

#### 2-1-Diode Clamped Topology

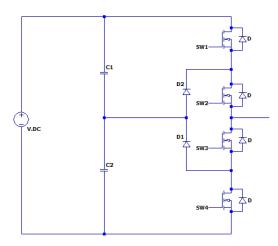

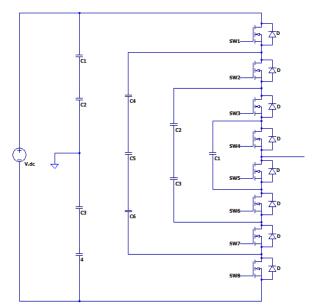

By using diodes, a diode-clamped Multilevel inverter (n level) creates n voltage levels at the output and generally has (n-1) capacitors on the dc-link bus [18, 19]. Figure 4 shows a three-level half-bridge diode clamped multilevel inverter [20]. An n-level inverter requires (n-1) balancing capacitors, 2(n-1) switches and (n-1)(n-2) clamping diodes. Therefore, as shown from Figure 4, the three-level classical diode clamped inverter creates three levels of voltage at the output and has two capacitors at the DC bus and four switches, and two clamping diodes [21, 22].

Figure 4. Three-level diode clamped MLI

According to Figure 5, three-level inverters provide a square wave output voltage of three levels without employing PWM.

Figure 5. The output waveform of three-level diode clamped MLI

The benefits and drawbacks of diode clamped MLI are as follow [23-25]:

Benefits:

- The real and reactive power flow can be controlled.

- Filters are not required to decrease harmonics.

- The voltage of the switch is just half of the voltage of the dc-link.

- The efficiency is high at the fundamental frequency

Drawbacks:

- Clamping diodes are increased when each level is raised.

- Individual converter real power flow management is challenging

#### 2-2-Capacitor Clamped Topology

It is different from the diode-clamped MLI topology because the capacitors are employed to restrict the voltage in this case [26, 27]. The voltage level of a capacitor's clamped inverter is the same as the diode clamped inverter [28, 29].

For an n-level inverter, the dc bus requires (n-1) capacitors,  $\frac{(n-1)(n-2)}{2}$  number of flying capacitors, and the total number of (n-1) switches is required. For instance, based on Figure 6, a five-level flying capacitor MLI creates five voltage levels at the output and has four capacitors at the DC bus and also has eight switches and six clamping capacitors [30, 31].

Figure 6. Five-level flying capacitor MLI

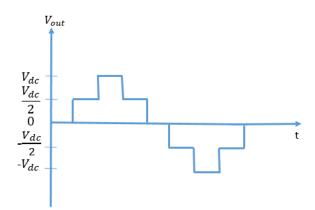

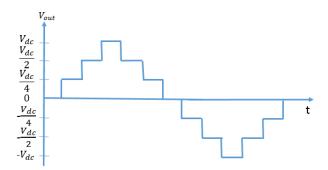

Also, according to Figure 7, the five-level inverters provide a square wave output voltage of five levels without employing PWM.

Figure 7. The output waveform of five-level flying capacitor MLI

The benefits and drawbacks of flying capacitor MLI are as follow [32-34]:

Benefits:

- Get rid of the clamping diode problems.

- Filters are not required to decrease harmonics.

- Reduces the amount of stress on the semiconductor switches.

- It provides the correct switching combination for balancing various voltage levels.

- It is possible to control both real and reactive power flow.

Drawbacks:

- Controlling the voltage across all of the capacitors is hard to achieve.

- A decrease in switching efficiency

- Higher cost because of using more capacitors

#### 2-3-Cascaded H Bridge Topology

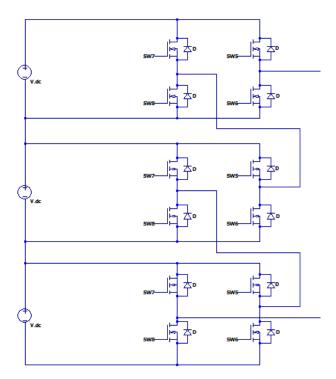

A cascaded MLI consists of succession of H-bridge inverters with independent DC sources [35-37]. In this inverter, the output voltage has a 2s+1 voltage level, and S is the number of DC inputs. Each cell provides three voltage levels, and the cascaded MLI is made up of connected H-bridge cells in series [38-40]. Therefore, the output voltage levels are equal to the total voltages generated by each H Bridge cell [35, 41]. Figure 8 indicates a seven-level cascaded MLI, which has three separate dc sources.

Figure 8. Seven-level H-bridge MLI

Based on Figure 9, the seven-level cascaded inverters provide a square wave output voltage of seven levels without employing PWM.

Figure 9. The output waveform of seven-level cascaded MLI

The benefits and drawbacks of cascaded H bridge MLI are as follow [42-44]: Benefits:

- To decrease switching losses, a soft switching approach can be employed.

- Filters are not required to decrease harmonics.

- THD (total harmonic distortion) is extremely low.

- A lower number of components is used in this MLI.

#### Drawbacks:

• For power conversions, it requires independent dc sources

## **3- Review of New Different MLI Topologies**

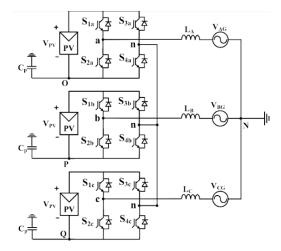

In [45], a new three phases transformer-less inverter design was suggested, which is shown in Figure 10. This suggested MLI has six switches and combines the benefits of dc-bypass and ac-bypass circuit designs.

Figure 10. Proposed novel three-phase transformerless MLI [45]

For the suggested configuration, a new modulation approach based on a sine triangle pulse width modulation technique and specialized logic functions is created. As a consequence, there is less leakage current throughout the inverter's operation and the proposed topology and its modulation method can be utilized to generate more electricity. In [46], a novel MLI topology using fewer components was suggested, as shown in Figure 11. It can also be linked in a cascade to increase the number of levels of voltages at the end.

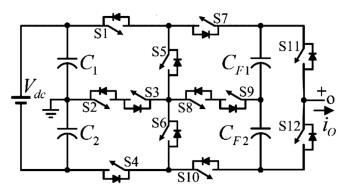

Figure 11. Proposed 15-level MLI [46]

The suggested inverter has the smallest DC-link source and minimal THD at the output voltage and current. In [47], a new MLI was proposed, which consists of series of proposed basic cells shown in Figure 12. Two dc voltage sources, six switches, and an H-bridge make up each basic cell or module

Figure 12. Proposed 9-level cascaded MLI with reducing DC voltage sources [47]

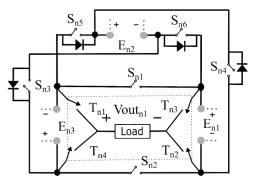

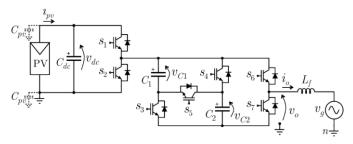

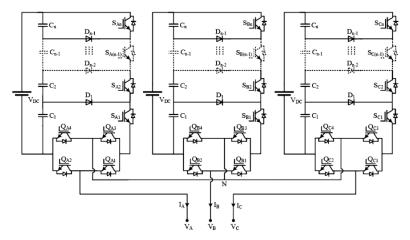

Compared to the standard symmetric multilevel inverter, the suggested topology in Figure 12 uses fewer switches in symmetric conditions. Furthermore, under asymmetric conditions, the magnitude diversity of dc voltage sources is smaller than in conventional conditions. In Grigoletto (2021) [48] study, a novel transformerless multilevel commonground inverter was introduced, as shown in Figure 13. One dc source, seven switches, and three capacitors make up the suggested structure.

Figure 13. Proposed multilevel common-ground topology [48]

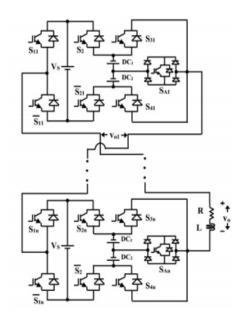

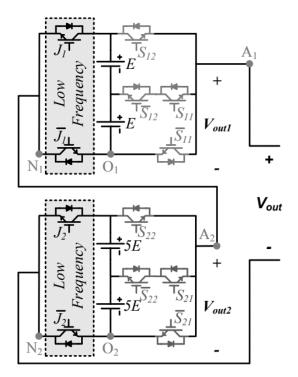

Furthermore, this topology eliminates leakage current. A feedforward modulation method is also presented to isolate the output variables from the voltage–capacitor oscillations. In [49], an improved topology of cascaded MLI was investigated. Each module in this topology consists of a Half-bridge, an H-bridge, two DC inputs, and an extra bidirectional circuit

Figure 14. Proposed cascaded MLI topology with fewer circuit components [49]

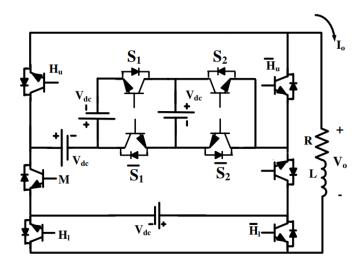

Also, with fewer power circuit components, each module in the proposed MLI can synthesize a maximum of the 9level output voltage waveform. Although the suggested topology may be switched at the fundamental frequency, it is impossible to achieve equitable power-sharing across modules. In [50], the article describes a dual-T-type five-level cascaded MLI topology shown in Figure 15. The Cascaded MLI has a high charging current and operates in a nonuniform manner. The proposed configuration solves these issues while maintaining the desired voltage-boosting characteristic.

Figure 15. Proposed Dual T-type five-level cascaded MLI [50]

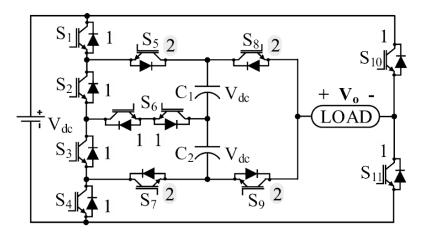

The capacitor boosts the voltage gain, while the dual structure's management of eight power switches allows for the creation of five voltages. In addition, cascaded extensions operate in a consistent manner. In Samsami et al. (2017) [51] study, a new topology was suggested. Figure 16 depicts a topology with three DC inputs and eight switches.

Figure 16. The proposed staircase cascaded MLI [51]

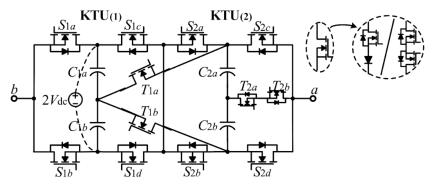

This suggested framework may be in cascade and modularly extended. According to Figure 16, switches of (S1, S2, S3, and S4) should have various voltage ratings and have a lowest blocking voltage capacity corresponding. Also, the suggested MLI reduces the number of switches. In [52], a single-source MLI based on the innovative K-type unit (KTU) was introduced. Due to their symmetric functioning in a cycle, may achieve self voltage balancing, decreasing control complexity compared to traditional MLIs.

Figure 17. Proposed single-source MLI k-type unit [52]

Furthermore, with more KTUs, the output levels climb substantially, and the voltage gain will increase. Also, the benefits of the suggested KTU circuit are demonstrated in terms of decreased components, voltage stress, and total cost. In [53], a different setup MLI has been proposed and has been shown in Figure 18. The suggested topology comprises eight switches, two separate DC voltage sources, and two series capacitors as its fundamental structure.

Figure 18. The proposed cross-connected source-based MLI [53]

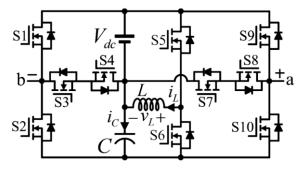

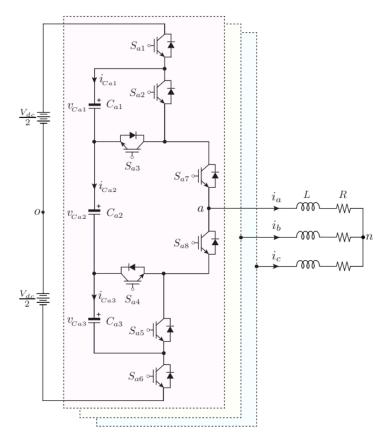

The suggested topology works to reduce the amount of DC inputs, cost, switches, diodes, and so on. In Dekka et al. (2020) [54] study, for high-power applications, a novel five-level voltage source inverter is suggested as shown in Figure 19. The proposed topology consists of eight switches, three capacitors, and two dc sources. In addition, unlike hybrid converters, the suggested inverter has a simple construction.

Figure 19. Proposed novel five-level voltage source inverter [54]

Due to the availability of a common dc-link, the suggested topology may also be linked back-to-back. Furthermore, an isolated dc supply and a complicated transformer are not required. In addition, to regulate the flying capacitor voltages, a simple technique based on pulse width modulation system is presented. In Oskuee et al. (2015) [55] study, 'Cascaded Innovative Cell-based Multilevel Inverter' was proposed as a novel MLI topology. Figure 20 depicts the suggested topology with four sources and ten power switches. This topology is implemented without the usage of any passive components.

Figure 1. Proposed new cell base MLI [55]

This modular configuration uses fewer components, such as power semiconductor switches for gate driver circuits. The multilevel inverter recommended has the least amount of power loss. Also, because all voltage levels for a symmetrical source configuration cannot be synthesized by using all inputs, equitable power-sharing is not possible, and this circuit is appropriate for just symmetrical configuration. In [56], the author offers a novel Active-Neutral-Point-Clamped Inverters ANPC inverter shown in Figure 21, and may generate greater voltage levels while maintaining unity or enhanced voltage gain. By integrating only one more switch, the topology may give a voltage gain of 1.5 and increase the number of voltage levels to seven.

Figure 21. Proposed ANPC inverter [56]

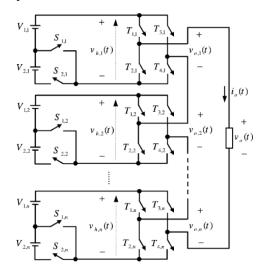

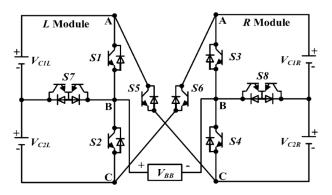

Three switches and one capacitor are added to the design to provide 11 levels with a 2.5 voltage gain. In [57], another cascaded MLI was proposed. Figure 22 indicates the proposed structure with two DC sources and six switches in each modular cell. The structure is suggested for asymmetrical source configurations.

Figure 22. Proposed ANPC inverter [57]

Because of the extremely asymmetric design, the base frequency is not suitable for this case. Also, in the suggested converter, the number of dc links is reduced, decreasing the size and the installation space. In [58], the author proposes a new MLI set up with a small number of high-power electric components, which is indicated in Figure 23. The inverter is made up of two T-type modules coupled by two switches. This inverter may use dc inputs with the varying ratings voltage to function.

Figure 23. Proposed new MLI using two T-type modules [58]

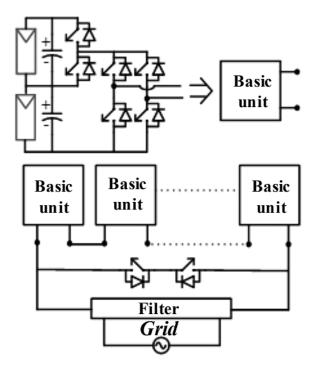

To achieve greater voltage levels, the suggested inverter can be expanded utilizing cascaded connections. The creation of negative voltage levels without an H-bridge circuit is a key characteristic of this MLI. Low total harmonic distortion and excellent output efficiency can also be obtained. Furthermore, the high-quality output voltage is generated using a low-frequency modulation method. In [59], the author suggested an efficient and reliable MLI. Figure 24 shows the suggested configuration, which included a series of base modules and two power switches in parallel to the power grid.

Figure 2. Proposed highly efficient and reliable MLI for solar PV system [59]

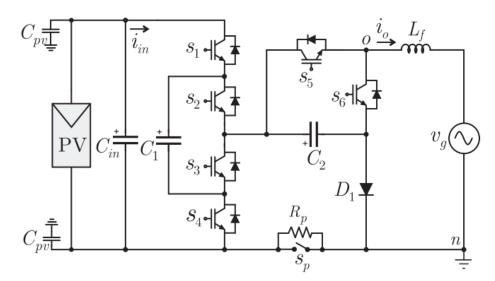

Two dc inputs, two MOSFETs, and an H-bridge make up each basic cell. Each cell can produce bipolar many levels. Also, this topology contains no passive components. The authors suggested this MLI for solar PV applications with the goal of reducing leakage current in the system. In [60] for PV systems, a five-level transformerless inverter with lower THD was proposed which can be seen in Figure 25. This case has six switches and three capacitors with a PV source. In addition, unlike half-bridge-based topologies, the suggested inverter can handle reactive power.

Figure 25. Proposed five-level common ground transformer-less inverter [60]

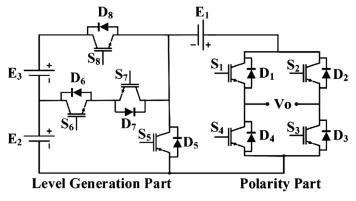

The inverter connects the grid to the PV system, resulting in very low leakage current. Furthermore, a modulation technique for maintaining balanced voltage over the capacitors has been presented, which can be readily implemented using standard PWM modulators. In [61], a new MLI has been proposed. Figure 26 indicates one module of the suggested architecture. For inverting the polarity of the level generator module, the suggested topology necessitates the use of an H-bridge inverter. A level generator is made up of an input, three capacitors, four power switches, and diodes.

Figure 26. One module of the proposed MLI [61]

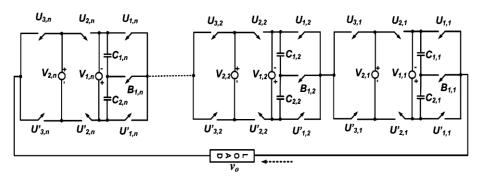

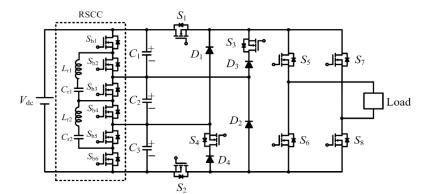

Because this configuration necessitates the use of a capacitor to divide the voltage of the DC bus, it necessitates the need for extra control circuitry to maintain the charge balance of the capacitors. A new converter is used to balance the voltage of the capacitors. The suggested topology also lowers the number of different DC sources, switches, and drivers. In [62], a novel three-phase multilevel inverter with fewer components is suggested, which is shown in Figure 27. This inverter creates several level output voltages from a single DC source.

Figure 27. Proposed novel three-phase MLI [62]

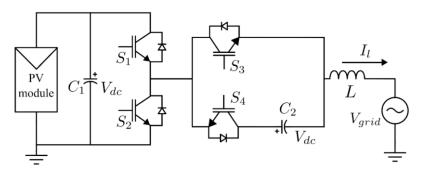

Despite the fact that each element is subjected to voltage stress equal to  $V_{in}$ , the total standing voltage (TSV) is decreased due to the use of a smaller number of components in relation to the number of series linked capacitors. Also, the suggested inverter may operate at a low switching frequency, lowering switching losses. In [63], it was recommended that a transformerless multilevel topology be used, as shown in Figure 28. The suggested configuration included a half-bridge with two switches S1 and S2, a voltage source, as well as a second half-bridge with switches S3 and S4, and a capacitor.

Figure 28. Proposed cascaded half bridge MLI [63]

The MLI described above cannot be used for fundamental switching. The suggested topology's major purpose is to fully remove leakage current in the PV applications by connecting the grid to the PV system, as well as using several levels at the end to ensure minimal filtering needs for the system. In [64], a novel switching capacitor-based multilevel inverter architecture is suggested, which can be seen in Figure 29. Using just one input voltage and two capacitors, the suggested configuration provides seven levels of output voltages.

Figure 29. Proposed switching capacitor-based MLI [64]

In this topology, Vout is three times bigger than  $V_{in}$ . The suggested seven-level inverter, lowering the topology's overall standing voltage.

#### **4-** Conclusion

This paper includes a brief review of classical multilevel inverter topologies and the advantages and disadvantages of each method. In addition, the performance features, switching issues, and technological feasibility of several new multilevel inverter topologies were studied in this paper. These topologies provide a variety of advantages over traditional topologies, including a fewer number of switches, lower harmonics, and lower stresses on the power semiconductors. However, there are some drawbacks, including the necessity for a separate power supply in cascaded MLI, design complexity, and switching control circuits are the primary drawbacks of MLI.

#### **5- Declarations**

#### 5-1-Author Contributions

Conceptualization, A.B. and S.D.; methodology, A.B., S.D., and F.S.; validation, F.S., M.H., and Y.L.C.; formal analysis, A.B. and S.D.; investigation, A.B., S.D., and F.S.; resources, A.B., S.D., and F.S.; writing—original draft preparation, A.B.; writing—review and editing, S.D., F.S., M.H., and Y.L.C.; visualization, S.D. and F.S.; supervision, A.B.; project administration, A.B.; funding acquisition, A.B., S.D., and F.S. All authors have read and agreed to the published version of the manuscript.

#### 5-2-Data Availability Statement

No new data were created or analyzed in this study. Data sharing is not applicable to this article.

#### 5-3-Funding

The authors received no financial support for the research, authorship, and/or publication of this article.

#### 5-4- Conflicts of Interest

The authors declare that there is no conflict of interests regarding the publication of this manuscript. In addition, the ethical issues, including plagiarism, informed consent, misconduct, data fabrication and/or falsification, double publication and/or submission, and redundancies have been completely observed by the authors.

#### **6- References**

- Kjaer, S. B., Pedersen, J. K., & Blaabjerg, F. (2005). A review of single-phase grid-connected inverters for photovoltaic modules. IEEE Transactions on Industry Applications, 41(5), 1292–1306. doi:10.1109/TIA.2005.853371.

- [2] Vázquez, N., & López, J. V. Inverters. (2008). In Power Electronics Handbook (pp. 289–338). Elsevier.

- [3] Malinowski, M., Gopakumar, K., Rodriguez, J., & Perez, M. A. (2009). A survey on cascaded multilevel inverters. IEEE Transactions on Industrial Electronics, 57(7), 2197–2206. doi:10.1109/TIE.2009.2030767.

- [4] Rodriguez, J., Lai, J.-S., & Peng, F. Z. (2002). Multilevel inverters: a survey of topologies, controls, and applications. IEEE Transactions on Industrial Electronics, 49(4), 724–738.

- [5] Mirafzal, B., & Adib, A. (2020). On Grid-Interactive Smart Inverters: Features and Advancements. IEEE Access, 8, 160526– 160536. doi:10.1109/ACCESS.2020.3020965.

- [6] Lasseter, R. H., Chen, Z., & Pattabiraman, D. (2020). Grid-Forming Inverters: A Critical Asset for the Power Grid. IEEE Journal of Emerging and Selected Topics in Power Electronics, 8(2), 925–935. doi:10.1109/JESTPE.2019.2959271.

- [7] Aghazadeh, A., Davari, M., Nafisi, H., & Blaabjerg, F. (2019). Grid integration of a dual two-level voltage-source inverter considering grid impedance and phase-locked loop. IEEE Journal of Emerging and Selected Topics in Power Electronics.

- [8] Aghazadeh, A., Khodabakhshi-Javinani, N., Nafisi, H., Davari, M., & Pouresmaeil, E. (2019). Adapted near-state PWM for dual two-level inverters in order to reduce common-mode voltage and switching losses. IET Power Electronics, 12(4), 676–685. doi:10.1049/iet-pel.2018.5268.

- [9] Aghazadeh, A., Jafari, M., Khodabakhshi-Javinani, N., Nafisi, H., & Namvar, H. J. (2018). Introduction and advantage of space opposite vectors modulation utilized in dual two-level inverters with isolated DC sources. IEEE Transactions on Industrial Electronics, 66(10), 7581-7592. https://doi.org/10.1109/TIE.2018.2880720

- [10] Gupta, K. K., & Bhatnagar, P. (2017). Multilevel inverters: Conventional and emerging topologies and their control. In *Multilevel Inverters: Conventional and Emerging Topologies and Their Control*. Academic Press. doi:10.1016/C2016-0-03360-0.

- [11] Ponraj, R. P., & Sigamani, T. (2021). A novel design and performance improvement of symmetric multilevel inverter with reduced switches using genetic algorithm. Soft Computing, 25(6), 4597–4607. doi:10.1007/s00500-020-05466-7.

- [12] Ali, A. N., Jeyabharath, R., & Udayakumar, M. D. (2016). Cascaded Multilevel Inverters for Reduce Harmonic Distortions in Solar PV Applications. Asian Journal of Research in Social Sciences and Humanities, 6(11), 703. doi:10.5958/2249-7315.2016.01223.5.

- [13] Kouro, S., Rebolledo, J., & Rodríguez, J. (2007). Reduced switching-frequency-modulation algorithm for high-power multilevel inverters. IEEE Transactions on Industrial Electronics, 54(5), 2894–2901. doi:10.1109/TIE.2007.905968.

- [14] Gautam, S. P., Sahu, L. K., & Gupta, S. (2016). Reduction in number of devices for symmetrical and asymmetrical multilevel inverters. IET Power Electronics, 9(4), 698–709. doi:10.1049/iet-pel.2015.0176.

- [15] Nguyen, N. V., Nguyen, T. K. T., & Lee, H. H. (2014). A reduced switching loss PWM strategy to eliminate common-mode voltage in multilevel inverters. IEEE Transactions on Power Electronics, 30(10), 5425-5438. https://doi.org/10.1109/TPEL.2014.2377152.

- [16] Chowdhury, M. R., Rahman, M. A., Islam, M. R., & Mahfuz-Ur-Rahman, A. M. (2021). A New Modulation Technique to Improve the Power Loss Division Performance of the Multilevel Inverters. IEEE Transactions on Industrial Electronics, 68(8), 6828–6839. doi:10.1109/TIE.2020.3001846.

- [17] Keddar, M., Doumbia, M. L., Krachai, M. Della, Belmokhtar, K., & Midoun, A. H. (2019). Interconnection performance analysis of single phase neural network based NPC and CHB multilevel inverters for grid-connected PV systems. International Journal of Renewable Energy Research, 9(3), 1451–1461.

- [18] Hossam-Eldin, A. A., Negm, E., Elgamal, M. S., & AboRas, K. M. (2020). Operation of grid-connected DFIG using SPWMand THIPWM-based diode-clamped multilevel inverters. IET Generation, Transmission and Distribution, 14(8), 1412–1419. doi:10.1049/iet-gtd.2019.0248.

- [19] Wu, B. and M. Narimani, (2016). Diode-Clamped Multilevel Inverters in High-Power Converters and AC Drives, 143–183. doi:10.1002/9781119156079.ch8.

- [20] Choudhury, S., Nayak, S., Dash, T. P., & Rout, P. K. (2018). A comparative analysis of five level diode clamped and cascaded H-bridge multilevel inverter for harmonics reduction. In *International Conference on Technologies for Smart City Energy Security and Power: Smart Solutions for Smart Cities, ICSESP 2018 - Proceedings* (Vols. 2018-January), 1–6. IEEE. doi:10.1109/ICSESP.2018.8376690.

- [21] Narendra Rao, P., & Nakka, J. (2019). A Novel Hybrid Multilevel PWM Technique for Power Rating Enhancement in Improved Hybrid Cascaded Diode Clamped Multilevel Inverter. Electric Power Components and Systems, 47(11–12), 1132–1143. doi:10.1080/15325008.2019.1659455.

- [22] Shi, S., Wang, X., Zheng, S., Zhang, Y., & Lu, D. (2018). A new diode-clamped multilevel inverter with balance voltages of DC capacitors. IEEE Transactions on Energy Conversion, 33(4), 2220–2228. doi:10.1109/TEC.2018.2863561.

- [23] Hassan, P. D. R., & Shyaa, S. S. (2021). Simulink Implementation of Voltage Stability Improvements Using STATCOM based 5-level Diode Clamped Converter. IOP Conference Series: Materials Science and Engineering, 1105(1), 012009. doi:10.1088/1757-899x/1105/1/012009.

- [24] Adam, G. P., Finney, S. J., Massoud, A. M., & Williams, B. W. (2008). Capacitor balance issues of the diode-clamped multilevel inverter operated in a quasi-two-state mode. IEEE Transactions on Industrial Electronics, 55(8), 3088–3099. doi:10.1109/TIE.2008.922607.

- [25] Von Bloh, J., & De Doncker, R. W. (2002). Design rules for diode-clamped multilevel inverters used in medium-voltage applications. International Power Electronics Congress - CIEP, 2002-January, 165–170. doi:10.1109/CIEP.2002.1216654.

- [26] Escalante, M. F., Vannier, J. C., & Arzandé, A. (2002). Flying capacitor multilevel inverters and DTC motor drive applications. IEEE Transactions on Industrial Electronics, 49(4), 809–815. doi:10.1109/TIE.2002.801231.

- [27] Humayun, M., Khan, M. M., Hassan, M. U., & Zhang, W. (2021). Analysis of hybrid switches symmetric flying capacitor multilevel inverter based STATCOM. International Journal of Electrical Power and Energy Systems, 131, 107054. doi:10.1016/j.ijepes.2021.107054.

- [28] Coday, S., Barchowsky, A., & Pilawa-Podgurski, R. C. N. (2021). A 10-level gan-based flying capacitor multilevel boost converter for radiation-hardened operation in space applications. Conference Proceedings - IEEE Applied Power Electronics Conference and Exposition - APEC, 2798–2803. doi:10.1109/APEC42165.2021.9487143.

- [29] Humayun, M., Khan, M. M., Muhammad, A., Xu, J., & Zhang, W. (2020). Evaluation of symmetric flying capacitor multilevel inverter for grid-connected application. International Journal of Electrical Power and Energy Systems, 115, 105430. doi:10.1016/j.ijepes.2019.105430.

- [30] Barth, C. B., Assem, P., Foulkes, T., Chung, W. H., Modeer, T., Lei, Y., & Pilawa-Podgurski, R. C. (2019). Design and control of a GaN-based, 13-level, flying capacitor multilevel inverter. *IEEE Journal of Emerging and Selected Topics in Power Electronics*, 8(3), 2179-2191. https://doi.org/10.1109/JESTPE.2019.2956166.

- [31] Abhilash, T., Annamalai, K., & Tirumala, S. V. (2019). A Seven-Level VSI with a Front-End Cascaded Three-Level Inverter and Flying-Capacitor-Fed H-Bridge. IEEE Transactions on Industry Applications, 55(6), 6073–6088. doi:10.1109/TIA.2019.2933378.

- [32] Amini, J., & Moallem, M. (2017). A Fault-Diagnosis and Fault-Tolerant Control Scheme for Flying Capacitor Multilevel Inverters. IEEE Transactions on Industrial Electronics, 64(3), 1818–1826. doi:10.1109/TIE.2016.2624722.

- [33] Porselvi, T., & Muthu, R. (2011). Comparison of cascaded H-bridge, neutral point clamped and flying capacitor multilevel inverters using multicarrier PWM. Proceedings - 2011 Annual IEEE India Conference: Engineering Sustainable Solutions, INDICON-2011. doi:10.1109/INDCON.2011.6139534.

- [34] Adam, G. P., Anaya-Lara, O., Burt, G., Finney, S. J., & Williams, B. W. (2009). Comparison between flying capacitor and modular multilevel inverters. IECON Proceedings (Industrial Electronics Conference), 271–276. doi:10.1109/IECON.2009.5414934.

- [35] Wu, B., & Narimani, M. (2017). Cascaded H-bridge multilevel inverters.

- [36] Chithra, M., & Dasan, S. G. B. (2011). Analysis of cascaded H bridge multilevel inverters with photovoltaic arrays. 2011 International Conference on Emerging Trends in Electrical and Computer Technology, ICETECT 2011, 442–447. doi:10.1109/ICETECT.2011.5760157.

- [37] Odeh, C. I., Lewicki, A., & Morawiec, M. (2021). A Single-Carrier-Based Pulse-Width Modulation Template for Cascaded H-Bridge Multilevel Inverters. IEEE Access, 9, 42182–42191. doi:10.1109/ACCESS.2021.3065743.

- [38] Memon, M. A., Siddique, M. D., Saad, M., & Mubin, M. (2021). Asynchronous Particle Swarm Optimization-Genetic Algorithm (APSO-GA) based Selective Harmonic Elimination in a Cascaded H-Bridge Multilevel Inverter. IEEE Transactions on Industrial Electronics. doi:10.1109/TIE.2021.3060645.

- [39] Lee, E. J., Kim, S. M., & Lee, K. B. (2020). Modified phase-shifted PWM scheme for reliability improvement in cascaded Hbridge multilevel inverters. IEEE Access, 8, 78130–78139. doi:10.1109/ACCESS.2020.2989694.

- [40] Maurya, S., Mishra, D., Singh, K., Mishra, A. K., & Pandey, Y. (2019). An Efficient Technique to reduce Total Harmonics Distortion in Cascaded H- Bridge Multilevel Inverter. Proceedings of 2019 3rd IEEE International Conference on Electrical, Computer and Communication Technologies, ICECCT 2019. doi:10.1109/ICECCT.2019.8869424.

- [41] Bhatnagar, P., Agrawal, R., & Gupta, K. K. (2019). Reduced device count version of single-stage switched-capacitor module for cascaded multilevel inverters. IET Power Electronics, 12(5), 1079–1086. doi:10.1049/iet-pel.2018.6017.

- [42] Khoucha, F., Ales, A., Khoudiri, A., Marouani, K., Benbouzid, M. E. H., & Kheloui, A. (2010). A 7-level single DC source cascaded H-bridge multilevel inverters control using hybrid modulation. 19th International Conference on Electrical Machines, ICEM 2010. doi:10.1109/ICELMACH.2010.5608179.

- [43] Lee, E. J., & Lee, K. B. (2021). Performance improvement of cascaded H-bridge multilevel inverters with modified modulation scheme. Journal of Power Electronics, 21(3), 541–552. doi:10.1007/s43236-020-00200-w.

- [44] Tackie, S. N., & Babaei, E. (2020). Modified topology for three-phase multilevel inverters based on a developed H-bridge inverter. *Electronics*, 9(11), 1848. https://doi.org/10.3390/electronics9111848.

- [45] Chamarthi, P. K., Al-Durra, A., El-Fouly, T. H. M., & Jaafari, K. Al. (2021). A Novel Three-Phase Transformerless Cascaded Multilevel Inverter Topology for Grid-Connected Solar PV Applications. IEEE Transactions on Industry Applications, 57(3), 2285–2297. doi:10.1109/TIA.2021.3057312.

- [46] Samanbakhsh, R., Ibanez, F. M., Koohi, P., & Martin, F. (2021). A New Asymmetric Cascaded Multilevel Converter Topology with Reduced Voltage Stress and Number of Switches. IEEE Access, 9, 92276–92287. doi:10.1109/ACCESS.2021.3092691.

- [47] Bahravar, S., Babaei, E., & Hosseini, S. H. (2012). New cascaded multilevel inverter topology with reduced variety of magnitudes of dc voltage sources. India International Conference on Power Electronics, IICPE. doi:10.1109/IICPE.2012.6450408.

- [48] Grigoletto, F. B. (2021). Multilevel Common-Ground Transformerless Inverter for Photovoltaic Applications. IEEE Journal of Emerging and Selected Topics in Power Electronics, 9(1), 831–842. doi:10.1109/JESTPE.2020.2979158.

- [49] Odeh, C. I., Obe, E. S., & Ojo, O. (2016). Topology for cascaded multilevel inverter. IET Power Electronics, 9(5), 921–929. doi:10.1049/iet-pel.2015.0375.

- [50] Lee, S. S., Lim, C. S., Siwakoti, Y. P., & Lee, K. B. (2020). Dual-T-Type Five-Level Cascaded Multilevel Inverter with Double Voltage Boosting Gain. IEEE Transactions on Power Electronics, 35(9), 9522–9529. doi:10.1109/TPEL.2020.2973666.

- [51] Samsami, H., Taheri, A., & Samanbakhsh, R. (2017). New bidirectional multilevel inverter topology with staircase cascading for symmetric and asymmetric structures. IET Power Electronics, 10(11), 1315–1323. doi:10.1049/iet-pel.2016.0956.

- [52] Zeng, J., Lin, W., Cen, D., & Liu, J. (2020). Novel k-Type multilevel inverter with reduced components and self-balance. IEEE Journal of Emerging and Selected Topics in Power Electronics, 8(4), 4343–4354. doi:10.1109/JESTPE.2019.2939562.

- [53] Agrawal, R., & Jain, S. (2017). Multilevel inverter for interfacing renewable energy sources with low/medium- and highvoltage grids. IET Renewable Power Generation, 11(14), 1822–1831. doi:10.1049/iet-rpg.2016.1034.

- [54] Dekka, A., Ramezani, A., Ouni, S., & Narimani, M. (2020). A New Five-Level Voltage Source Inverter: Modulation and Control. IEEE Transactions on Industry Applications, 56(5), 5553–5564. doi:10.1109/TIA.2020.3000712.

- [55] Oskuee, M. R. J., Karimi, M., Ravadanegh, S. N., & Gharehpetian, G. B. (2015). An Innovative Scheme of Symmetric Multilevel Voltage Source Inverter with Lower Number of Circuit Devices. IEEE Transactions on Industrial Electronics, 62(11), 6965– 6973. doi:10.1109/TIE.2015.2438059.

- [56] Lee, S. S., Lim, C. S., & Lee, K. B. (2019). Novel active-neutral-point-clamped inverters with improved voltage-boosting capability. IEEE Transactions on Power Electronics, 35(6), 5978-5986. doi:10.1109/TPEL.2019.2951382.

- [57] Khoshkbar Sadigh, A., Abarzadeh, M., Corzine, K. A., & Dargahi, V. (2015). A New Breed of Optimized Symmetrical and Asymmetrical Cascaded Multilevel Power Converters. IEEE Journal of Emerging and Selected Topics in Power Electronics, 3(4), 1160–1170. doi:10.1109/JESTPE.2015.2459011.

- [58] Meraj, S. T., Hasan, K., & Masaoud, A. (2020). A Novel Configuration of Cross-Switched T-Type (CT-Type) Multilevel Inverter. IEEE Transactions on Power Electronics, 35(4), 3688–3696. doi:10.1109/TPEL.2019.2935612.

- [59] Jain, S., & Sonti, V. (2016). A highly efficient and reliable inverter configuration based cascaded multilevel inverter for PV systems. *IEEE transactions on industrial electronics*, 64(4), 2865-2875. doi:10.1109/TIE.2016.2633537.

- [60] Grigoletto, F. B. (2020). Five-Level Transformerless Inverter for Single-Phase Solar Photovoltaic Applications. IEEE Journal of Emerging and Selected Topics in Power Electronics, 8(4), 3411–3422. doi:10.1109/JESTPE.2019.2891937.

- [61] Hsieh, C. H., Liang, T. J., Chen, S. M., & Tsai, S. W. (2016). Design and Implementation of a Novel Multilevel DC-AC Inverter. IEEE Transactions on Industry Applications, 52(3), 2436–2443. doi:10.1109/TIA.2016.2527622.

- [62] Mondol, M. H., Tür, M. R., Biswas, S. P., Hosain, M. K., Shuvo, S., & Hossain, E. (2020). Compact Three Phase Multilevel Inverter for Low and Medium Power Photovoltaic Systems. IEEE Access, 8, 60824–60837. doi:10.1109/ACCESS.2020.2983131.

- [63] Kadam, A., & Shukla, A. (2017). A Multilevel Transformerless Inverter Employing Ground Connection between PV Negative Terminal and Grid Neutral Point. IEEE Transactions on Industrial Electronics, 64(11), 8897–8907. doi:10.1109/TIE.2017.2696460.

- [64] Siddique, M. D., Mekhilef, S., Mekhilef, S., Shah, N. M., Ali, J. S. M., & Blaabjerg, F. (2020). A new switched capacitor 7L inverter with triple voltage gain and low voltage stress. IEEE Transactions on Circuits and Systems II: Express Briefs, 67(7), 1294–1298. doi:10.1109/TCSII.2019.2932480.