Clemson University

### **TigerPrints**

All Dissertations

**Dissertations**

5-2022

# The Development of TIGRA: A Zero Latency Interface For Accelerator Communication in RISC-V Processors

Wesley Brad Green wbgreen@g.clemson.edu

Follow this and additional works at: https://tigerprints.clemson.edu/all\_dissertations

Part of the Computer and Systems Architecture Commons

#### **Recommended Citation**

Green, Wesley Brad, "The Development of TIGRA: A Zero Latency Interface For Accelerator Communication in RISC-V Processors" (2022). *All Dissertations*. 2982. https://tigerprints.clemson.edu/all\_dissertations/2982

This Dissertation is brought to you for free and open access by the Dissertations at TigerPrints. It has been accepted for inclusion in All Dissertations by an authorized administrator of TigerPrints. For more information, please contact kokeefe@clemson.edu.

## THE DEVELOPMENT OF TIGRA: A ZERO LATENCY INTERFACE FOR ACCELERATOR COMMUNICATION IN RISC-V PROCESSORS

A Dissertation Presented to the Graduate School of Clemson University

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy Computer Engineering

> by Wesley Brad Green May 2022

Accepted by: Dr. Melissa C. Smith, Committee Chair Dr. Jon C. Calhoun Dr. Walt Ligon Dr. Rong Ge

### Abstract

Field programmable gate arrays (FPGA) give developers the ability to design application specific hardware by means of software, providing a method of accelerating algorithms with higher power efficiency when compared to CPU or GPU accelerated applications. FPGA accelerated applications tend to follow either a loosely coupled or tightly coupled design. Loosely coupled designs often use OpenCL to utilize the FPGA as an accelerator much like a GPU, which provides a simplifed design flow with the trade-off of increased overhead and latency due to bus communication. Tightly coupled designs modify an existing CPU to introduce instruction set extensions to provide a minimal latency accelerator at the cost of higher programming effort to include the custom design.

This dissertation details the design of the Tightly Integrated, Generic RISC-V Accelerator (TIGRA) interface which provides the benefits of both loosely and tightly coupled accelerator designs. TIGRA enabled designs incur zero latency with a simple-to-use interface that reduces programming effort when implementing custom logic within a processor. This dissertation shows the incorporation of TIGRA into the simple PicoRV32 processor, the highly customizable Rocket Chip generator, and the FPGA optimized Taiga processor. Each processor design is tested with AES 128-bit encryption and posit arithmetic to demonstrate TIGRA functionality.

After a one time programming cost to incorporate a TIGRA interface into an existing processor, new functional units can be added with up to a 75% reduction in the lines of code required when compared to non-TIGRA enabled designs. Additionally, each functional unit created is cocompatible with each processor as the TIGRA interface remains constant between each design. The results prove that using the TIGRA interface introduces no latency and is capable of incorporating existing custom logic designs without modification for all three processors tested. When compared to the PicoRV32 coprocessor interface (PCPI), TIGRA coupled designs complete one clock cycle faster. Similarly, TIGRA outperforms the Rocket Chip custom coprocessor (RoCC) interface by an average of 6.875 clock cycles per instruction. The Taiga processor's decoupled execution units allow for instructions to execute concurrently and uses a tag management system that is similar to out-of-order processors. The inclusion of the TIGRA interface within this processor abstracts the tag management from the user and demonstrates that the TIGRA interface can be applied to out-of-order processors.

When coupled with partial reconfiguration, the flexibility and modularity of TIGRA drastically increases. By creating a reprogrammable region for the custom logic connected via TIGRA, users can swap out the connected design at runtime to customize the processor for a given application. Further, partial reconfiguration allows users to only compile the custom logic design as opposed to the entire CPU, resulting in an 18.1% average reduction of compilation during the design process in the case studies. Paired with the programming effort saved by using TIGRA, partial reconfiguration improves the "time to design" and "test new functionality" timelines for a processor.

## Dedication

I dedicate this Dissertation to my grandfather, Frank Minozzi. The man who taught me the meaning of hard work while never forgetting to have a little bit of fun.

## Acknowledgments

I would first like to acknowledge Dr. Melissa Smith, who has pushed and supported me for too many long years. Without her guidance, mentorship, and friendship I would not have pushed through and completed my PhD.

I want to thank my family and friends who have helped me through some of the toughest times of my life. They all stood by me at the lowest points and helped to lift me up when it was needed the most.

I want to thank my partner, Caitie B. O'Donnell, who helped kick my butt into gear, motivate me, and support me as I pushed toward the completion of this work.

I would specifically like to thank (and congratulate) Dillon Todd and Theresa Lê, who's Master's Theses helped bring the TIGRA concept to life!

## Table of Contents

| Ti            | itle Page                                                                                                                                                                                                                                                                                                                                                                                                 | i                                                                                                                  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| $\mathbf{A}$  | bstract                                                                                                                                                                                                                                                                                                                                                                                                   | ii                                                                                                                 |

| D             | edication                                                                                                                                                                                                                                                                                                                                                                                                 | v                                                                                                                  |

| A             | cknowledgments                                                                                                                                                                                                                                                                                                                                                                                            | v                                                                                                                  |

| $\mathbf{Li}$ | st of Tables                                                                                                                                                                                                                                                                                                                                                                                              | ii                                                                                                                 |

| Li            | st of Figures                                                                                                                                                                                                                                                                                                                                                                                             | x                                                                                                                  |

| $\mathbf{Li}$ | st of Listings                                                                                                                                                                                                                                                                                                                                                                                            | ii                                                                                                                 |

| 1             | Introduction                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                                                                                  |

| 2             | 2.1 AES       2.2 Posits         2.2 Posits       2.3 Loosely Coupled Accelerators         2.3 Loosely Coupled Accelerators       2.4 Tightly Coupled Accelerators         2.4 Tightly Coupled Accelerators       2.5 Partial Reconfiguration         2.5 Partial Reconfiguration       2.6 Summary         2.6 Summary       2.7 Partial Reconfiguration         2.7 Research Design and Methods       7 |                                                                                                                    |

| 4             | Case Studies1'4.1PicoRV321'4.2Rocket Chip Generator24.3Taiga Processor24.4AES 128-bit Custom Logic24.5Posit Arithmetic Custom Logic24.6Built-in Functions Custom Logic34.7Comparing the Programming Effort34.8Summary3                                                                                                                                                                                    | $     \begin{array}{c}       7 \\       1 \\       4 \\       7 \\       8 \\       0 \\       2     \end{array} $ |

| 5             | Simulation Results       3         5.1       PicoRV32 Simulation Results       3         5.2       PicoRV32 Hardware Results       3                                                                                                                                                                                                                                                                      | 5                                                                                                                  |

|    | 5.3   | Rocket Chip Results           | 41        |

|----|-------|-------------------------------|-----------|

|    | 5.4   | Taiga Processor Results       | 46        |

|    | 5.5   | Summary                       | 51        |

| 6  | Part  | tial Reconfiguration          | 53        |

|    | 6.1   | Taiga Partial Reconfiguration | 54        |

|    | 6.2   | Summary                       | 57        |

| 7  | Con   | clusions and Future Work      | 58        |

| Aı | ppen  | dices                         | <b>61</b> |

|    | Α     | Code Listings                 | 62        |

|    | В     | Extended Timing Diagrams      | 76        |

|    | С     | Raw Data from Simulations     | 78        |

| Bi | bliog | graphy                        | 81        |

## List of Tables

| 4.1 | Custom instructions for AES                                                                                                                                                                                   | 28 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2 | Custom instructions for arbitrary Taiga design                                                                                                                                                                | 32 |

| 4.3 | Comparison of the lines of code edited for each design in Chapter 4                                                                                                                                           | 32 |

| 5.1 | Latency of TIGRA enabled Rocket compared to RoCC when executing AES instruc-<br>tions. Each value counts the number of clock cycles between instruction fetch and<br>when the result is stored in a register. | 47 |

| 6.1 | Synthesis and Implementation timing results of the full Taiga processor with each test                                                                                                                        |    |

|     | case connected via TIGRA and the same designs using Xilinx DFX                                                                                                                                                | 55 |

| 6.2 | Comparison of synthesis and implementation times of a complete design compared to                                                                                                                             |    |

|     | the same design using Xilinx DFX                                                                                                                                                                              | 56 |

## List of Figures

| 3.1        | The main RISC-V instruction type opcodes: Register, Immediate, Upper immediate, and Store.                                                                                                                                                                                                                                                                                                                                                                                | 8               |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

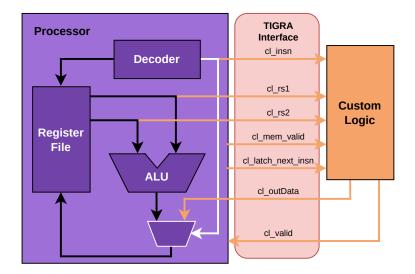

| 3.2        | A processor coupled with custom logic via the TIGRA interface. The signals con-<br>necting the Custom Logic to the processor block (shown in orange) are required to<br>handle communication with the user designed hardware. The multiplexer and the sig-<br>nal connecting it to the decoder (shown in white) represent the minimal logic added<br>to the processor to ensure TIGRA instructions follow the standard ALU flow. Clock<br>and reset signals are not shown | 10              |

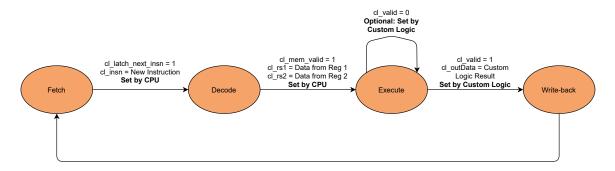

| 3.3        | An example four-stage CPU pipeline, showing how to set each TIGRA control signal                                                                                                                                                                                                                                                                                                                                                                                          |                 |

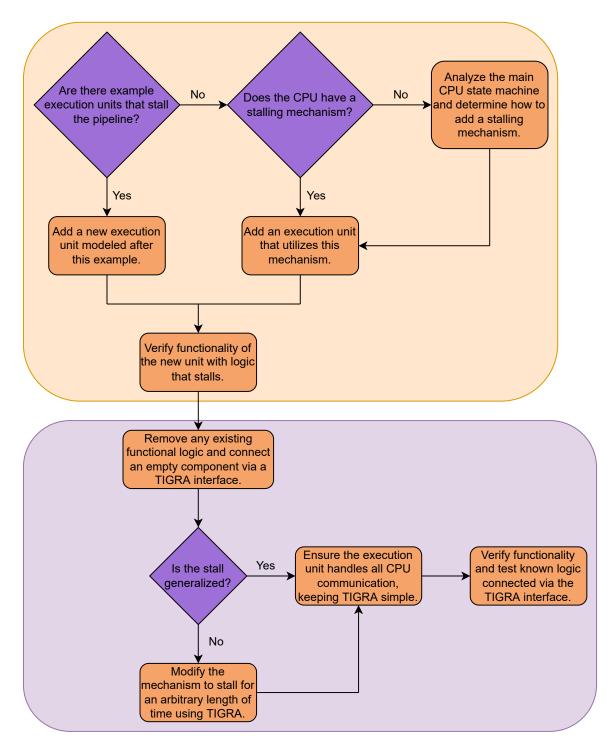

| 3.4        | in the host processor and the custom hardware design                                                                                                                                                                                                                                                                                                                                                                                                                      | 11              |

| 3.5        | represents the unique effort required to generalize the new execution unit for TIGRA.<br>An example custom logic setup implementing many accelerators. The signals external<br>to the custom logic block represent the TIGRA interface. The necessary instruction<br>decoder(s) and other logic is not shown to maintain generality and keep the design<br>readable                                                                                                       | 12<br>14        |

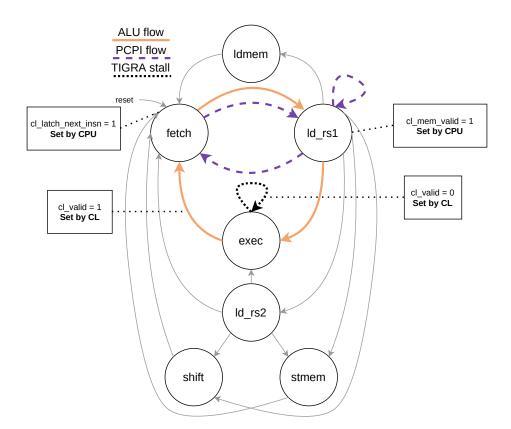

| 4.1        | The PicoRV32 state diagram, emphasising the PCPI and TIGRA flows. The boxes                                                                                                                                                                                                                                                                                                                                                                                               |                 |

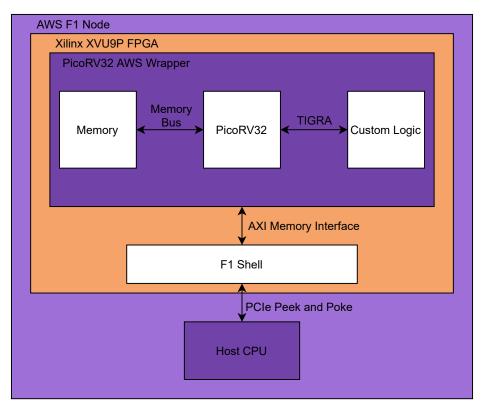

| 4.1        | represent the value and timing of TIGRA control signals during execution The AWS F1 HDK hierarchy when connected with a full PicoRV32 with TIGRA                                                                                                                                                                                                                                                                                                                          | 19              |

|            | enabled and connected to custom logic.                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20              |

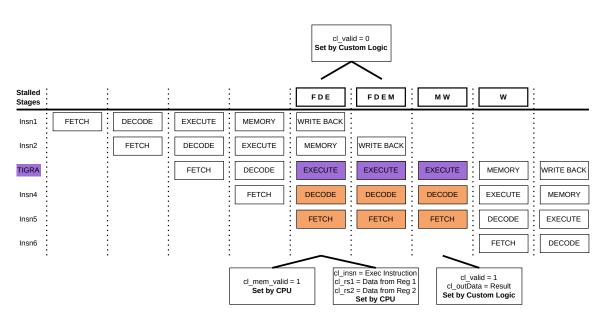

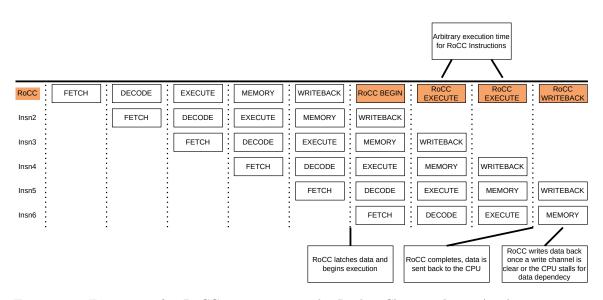

| 4.3<br>4.4 | Example execution stall of a TIGRA instruction in the Rocket pipeline. The purple highlighted instruction (TIGRA) stalls in the execute stage of the pipeline, causing later instructions (Insn4 and Insn5 highlighted in orange) to stall in decode and fetch. Execution of a RoCC instruction in the Rocket Chip pipeline. As shown, custom                                                                                                                             | 23              |

|            | hardware connected to a RoCC interface begins execution as the instruction exits the main Rocket Chip pipeline.                                                                                                                                                                                                                                                                                                                                                           | 25              |

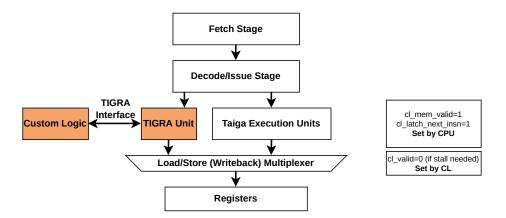

| 4.5        | Taiga's general pipeline flow showing the necessary additions to include a TIGRA in-<br>terface. The added unit is shown separate from the Taiga execution units to represent<br>that each operates independently of each other. Each vertical stage is separated by a                                                                                                                                                                                                    |                 |

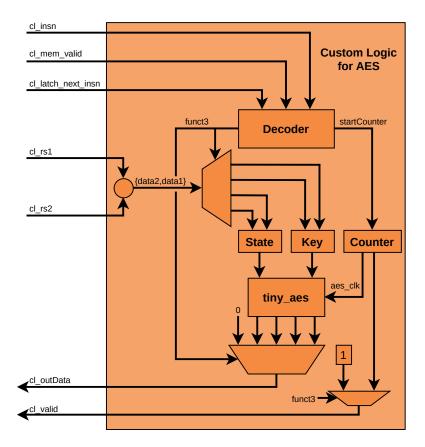

| 4.6        | queue to facilitate the decoupled operation and ensure instructions complete in order.<br>AES-128 Bit custom logic block diagram.                                                                                                                                                                                                                                                                                                                                         | $\frac{26}{29}$ |

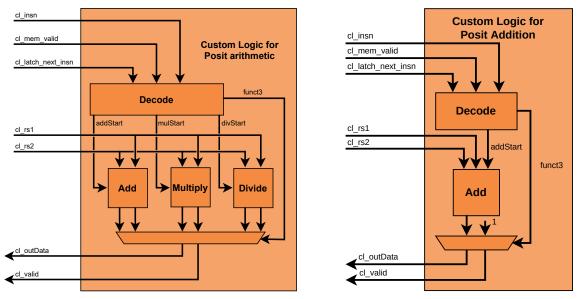

| 4.7        | Posit arithmetic custom logic block diagrams for use with PicoRV32 or hardware                                                                                                                                                                                                                                                                                                                                                                                            |                 |

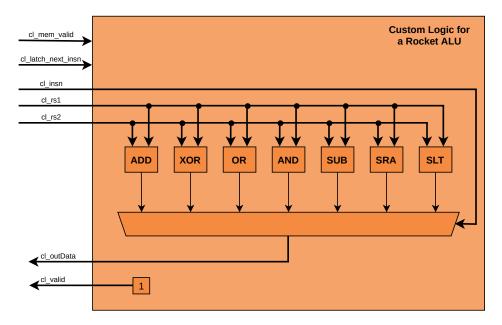

| 4.8        | compilation (a) and for use with the Rocket Chip generator and Taiga simulators (b).<br>Rocket ALU custom logic block diagram.                                                                                                                                                                                                                                                                                                                                            | $\frac{30}{31}$ |

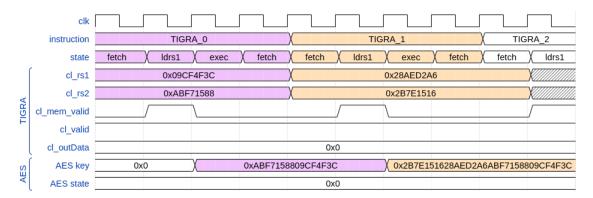

| 5.1        | PicoRV32 with TIGRA and AES: The second two TIGRA instructions which store<br>the AES state in the custom logic and complete the encryption. The break represents<br>15 clock cycles during which none of the shown signals change                                                                                                                                                                                                                                        | 36              |

| 5.2   | PicoRV32 with TIGRA and AES: The first two reads from the AES custom logic,                                                                                             |    |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|       | showing the end of the stall from the last write.                                                                                                                       | 37 |

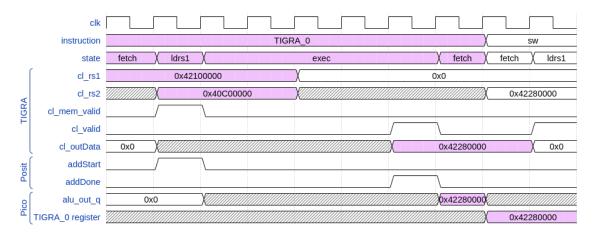

| 5.3   | PicoRV32 with TIGRA and Posit Arithmetic: Posit addition showing the data flow                                                                                          |    |

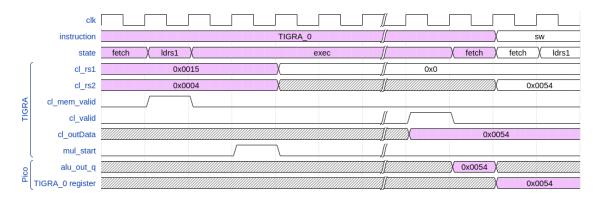

|       | from the custom logic all the way through register write-back                                                                                                           | 37 |

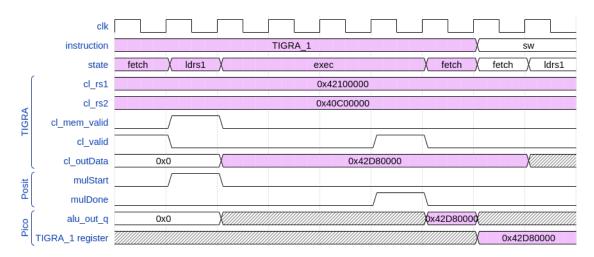

| 5.4   | PicoRV32 with TIGRA and Posit Arithmetic: Posit multiplication showing the data                                                                                         |    |

|       | flow from the custom logic all the way through register write-back.                                                                                                     | 38 |

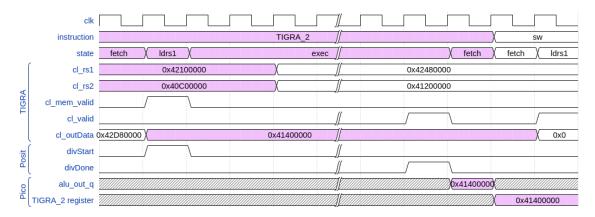

| 5.5   | PicoRV32 with TIGRA and Posit Arithmetic: Posit division showing the data flow                                                                                          |    |

|       | from the custom logic all the way through register write-back. The break represents                                                                                     |    |

|       | 6 clock cycles during which none of the shown signals change                                                                                                            | 38 |

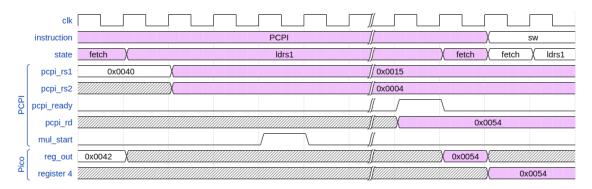

| 5.6   | PicoRV32 with TIGRA and multiplication: Multiplication, the break represents 30                                                                                         |    |

|       | clock cycles                                                                                                                                                            | 40 |

| 5.7   | PicoRV32 with PCPI and multiplication: Multiplication, the break represents 31 clock                                                                                    |    |

|       | cycles                                                                                                                                                                  | 40 |

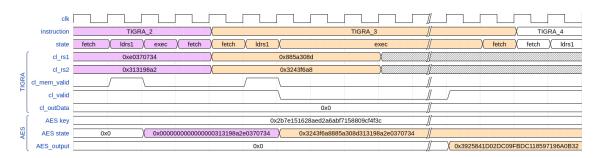

| 5.8   | Rocket Chip with AES via TIGRA: The first three AES writes                                                                                                              | 42 |

| 5.9   | Rocket Chip with TIGRA: The remaining instructions to complete AES encryption                                                                                           |    |

|       | in a Rocket Chip generated processor. The break in the diagram represents 18 clock                                                                                      |    |

|       | cycles during which none of the signals shown change                                                                                                                    | 43 |

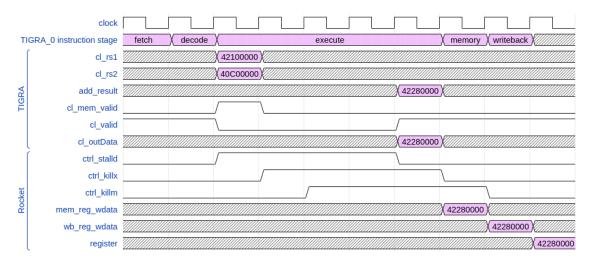

| 5.10  | Rocket Chip with TIGRA: Posit addition of 18 and 3, 0x42100000 and 0x40C00000,                                                                                          |    |

|       | providing the resultant value 21, $0x42280000$                                                                                                                          | 44 |

| 5.11  | Rocket Chip with TIGRA and Rocket Chip ALU. Results from two XOR instructions                                                                                           |    |

|       | executing within the instruction verification environment provided by the RISC-V Tools.                                                                                 | 45 |

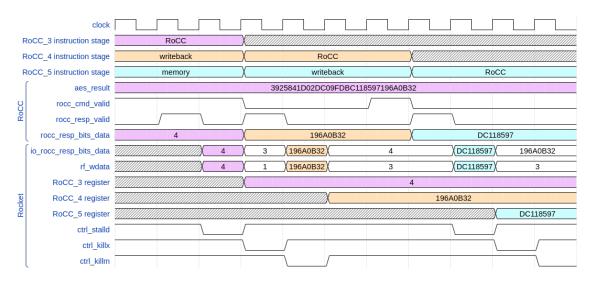

| 5.12  | Rocket Chip with RoCC and AES. The first AES write instruction that writes the                                                                                          |    |

|       | lowest 32-bits of the AES key to the custom logic. The break represents 7 clock cycles                                                                                  |    |

|       | during which none of the shown signals change.                                                                                                                          | 45 |

| 5.13  | Rocket Chip with RoCC and AES. The first two AES read instructions that return                                                                                          |    |

|       | the lowest 64-bits of the encrypted result.                                                                                                                             | 46 |

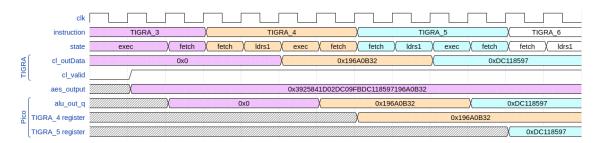

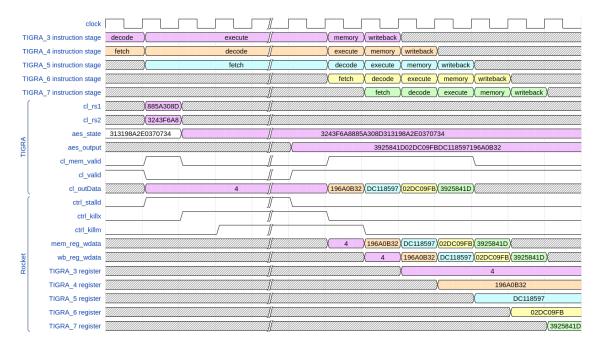

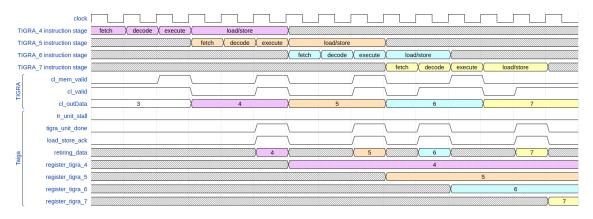

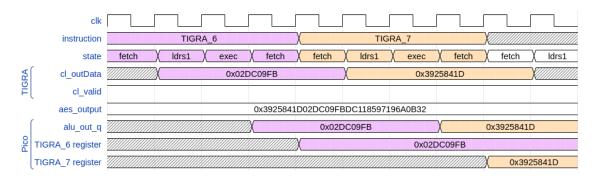

| 5.14  | Simulation of the first two TIGRA instructions when using custom logic with AES.                                                                                        | 40 |

| F 1 F | These instructions both complete within one clock cycle                                                                                                                 | 48 |

| 5.15  | Simulation showing the latter five TIGRA instructions executing on the Taiga pro-                                                                                       |    |

|       | cessor with AES hardware connected. The break represents 18 clock cycles during                                                                                         | 40 |

| F 16  | which none of the shown signals change.                                                                                                                                 | 49 |

| 5.10  | Simulation of two consecutive $tigra_0$ instructions with Posit addition connected via the TIGRA interface on the Taiga processor. Each break represents 2 clock cycles |    |

|       | during which none of the shown signals change                                                                                                                           | 50 |

| 517   | Simulation of the TIGRA instructions 4-7 when using custom logic with arbitrary                                                                                         | 50 |

| 5.17  | return values and stalls. These instructions signal complete at varying times even                                                                                      |    |

|       | though the data is immediately available.                                                                                                                               | 50 |

| 5 18  | Simulation of the first 7 multiplications to test the multiplication custom logic                                                                                       | 51 |

| 0.10  | Simulation of the mist r multipleations to test the multipleation custom logic                                                                                          | 01 |

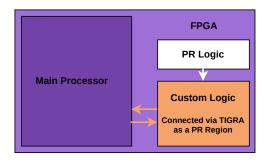

| 6.1   | Abstract block diagram for partial reconfiguration. The Custom Logic block is the                                                                                       |    |

|       | reconfigurable region in orange. The PR logic block, shown in white, represents the                                                                                     |    |

|       | extra logic required to partially reprogram the FPGA.                                                                                                                   | 53 |

| 6.2   | Screenshot showing a portion of the XCVU9P device, including the custom logic block                                                                                     |    |

|       | which is designated as the partially reconfigurable region.                                                                                                             | 55 |

|       |                                                                                                                                                                         |    |

| 1     | Simulation of the first two TIGRA instructions in PicoRV32 with AES via TIGRA.                                                                                          |    |

| _     | These instructions both complete within one clock cycle                                                                                                                 | 76 |

| 2     | Simulation of the last two TIGRA instructions in PicoRV32 with AES via TIGRA.                                                                                           |    |

|       | These instructions all complete within one clock cycle                                                                                                                  | 76 |

| 3 | Simulation of TIGRA instructions 2 and 3 when using custom logic with AES. In-<br>struction 2 completes within one clock cycle, while instruction 3 initiates a stall and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | compress the energy priority is a set of the | 77 |

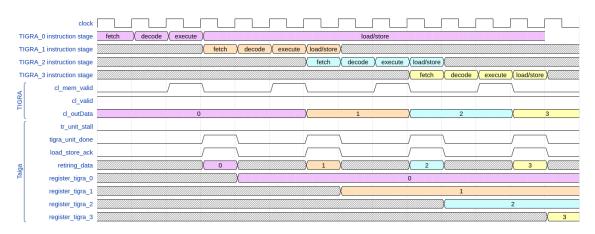

| 4 | Simulation of the first four TIGRA instructions when using custom logic with ar-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|   | bitrary return values and stalls. These instructions all complete within one clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|   | cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 77 |

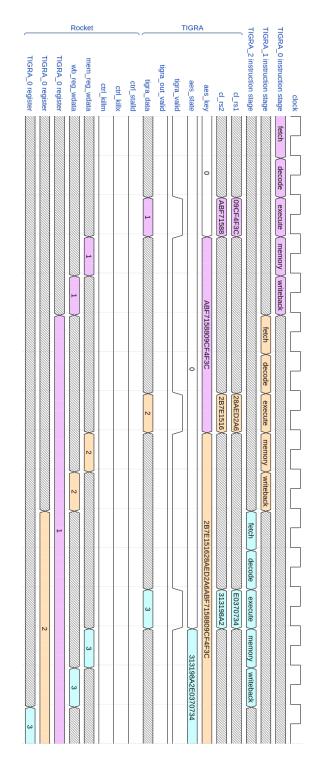

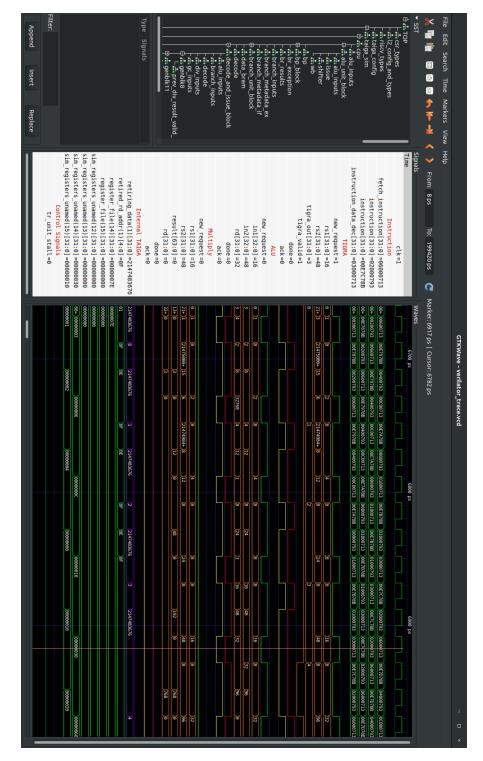

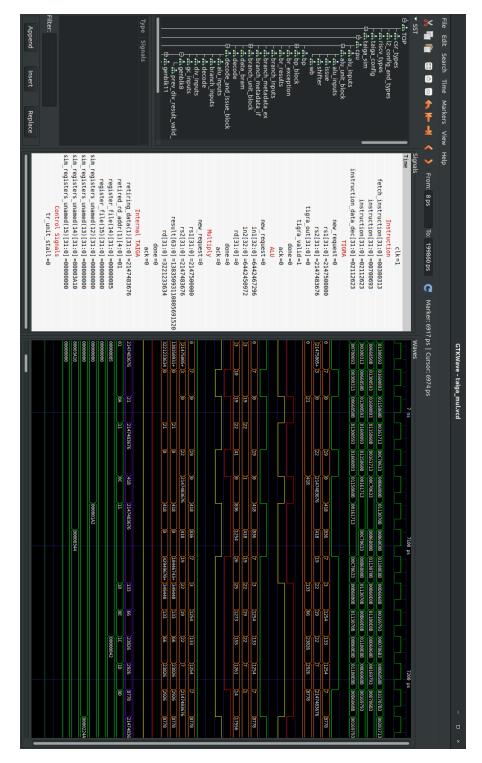

| 5 | Original timing diagram showing six of the eight instructions for custom logic with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|   | arbitrary return values and stall lengths. This diagram shows the difficulty of reading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|   | content in this format compared to the transcribed waveforms shown in the paper.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 79 |

| 6 | Original timing diagram showing the first 7 TIGRA multiplication instructions. This                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|   | diagram shows the compiler reordering commands for the code in Listing 7. Here you                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|   | can see the processor issue 5 TIGRA instructions consecutively, while the code issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|   | at most 3 consecutively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 80 |

|   | v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

## Listings

| 1  | The code required to add a TIGRA enabled PicoRV32 processor to an AWS F1             |    |

|----|--------------------------------------------------------------------------------------|----|

|    | wrapper with posit custom logic.                                                     | 62 |

| 2  | The instructions used to test the Posit custom logic within the PicoRV32 with TIGRA. | 66 |

| 3  | The instructions used to test the AES custom logic within the PicoRV32 with TIGRA.   | 67 |

| 4  | The instructions used to test multiplication within the PicoRV32 with TIGRA          | 68 |

| 5  | The instructions used to test multiplication within the PicoRV32 using PCPI          | 68 |

| 6  | C code used to test AES encryption in the Rocket Chip and Taiga processors via the   |    |

|    | TIGRA interface.                                                                     | 69 |

| 7  | C code used to test multiplication in the Taiga processor via the TIGRA interface    | 70 |

| 8  | C code used to test the arbitrary custom logic in the Taiga processor via the TIGRA  |    |

|    | interface                                                                            | 72 |

| 9  | Module declaration of the TIGRA custom logic in the Taiga processor using a System   |    |

|    | Verilog interface and struct to simplify design                                      | 75 |

| 10 | Flattened module declaration of the TIGRA custom logic for use with Dynamic Func-    |    |

|    | tion eXchange.                                                                       | 75 |

| 11 | Binary object dump of AES test code for the Rocket Chip processor. This shows        |    |

|    | the instructions required to complete the code in Listing 6 and demonstrates the     |    |

|    | instruction reordering completed by the compiler                                     | 78 |

|    |                                                                                      |    |

### Chapter 1

## Introduction

Field-programmable gate arrays (FPGAs) give developers the ability to design application specific hardware by means of software. This enables developers to create custom implementations of existing algorithms that execute with very little latency and with higher power efficiency than the algorithm on CPUs or even GPUs, as shown in [35], [11] and [29]. As a result of this capability, FPGAs uniquely fill a need to combat growing power requirements in high performance computing (HPC) environments [55]. Developers are also designing application specific accelerators, such as Google's TPU [30] and NVIDIA's tensor cores [39] for machine learning, in an attempt to ensure HPC applications continue to scale over time. FPGAs are often used to prototype novel designs before building an application specific integrated circuit (ASIC) such as in [18] where the authors build an FPGA-based accelerator to process data captured by the Square Kilometre Array (SKA) telescope with the intention of taping out to an ASIC. The authors in [36] create a real-time power, temperature and aging monitor system (eTAPMon) used to help predict the ASIC characteristics from FPGA-based prototypes of multi-processor systems-on-chips (MPSoCs) designs.

With the advent of OpenCL for FPGAs [21][53], developers are given a set of tools to simplify FPGA programming that enable acceleration of existing algorithms. OpenCL enables the host computer to use an FPGA as a loosely coupled accelerator, much like when using a general purpose graphics processing unit (GPGPU) for application development. As a loosely coupled accelerator, the device communicates to the CPU over a bus which introduces latency. Further, loosely coupled devices tend to operate on very coarse-grained chunks of an existing application in an attempt to minimize the communication time required and latency introduced. To minimize the latency introduced for applications that require fine-grained computation or to introduce improvements and extensions to an existing architecture, many developers use FPGAs to create tightly coupled accelerators [33][3][42]. These tightly coupled devices require the developer modify the existing CPU pipeline to incorporate the custom logic in the FPGA into design, significantly increasing the programming effort required. Existing within the CPU pipeline, these designs incur very little or no latency penalty and can allow very fine-grained execution. However, without fabricating the corresponding hardware from a tightly coupled design, these architectural improvements are only available for use through simulation or a soft-core CPU running within an FPGA.

Due to the restrictions on tightly coupled accelerators, FPGAs are typically only used for algorithm acceleration within the loosely coupled OpenCL model. While developers may design custom hardware that can complete a design with very low latency, most existing mechanisms do not leverage FPGA custom logic co-processors in real world applications without synthesizing and running the entire processor and custom design on an FPGA. This drawback, coupled with the release of the Intel Xeon Scalable processors [43], motivate the research described in this work.

This dissertation introduces TIGRA [13], a tightly integrated generic RISC-V accelerator interface that provides the benefits of a tightly coupled accelerator without requiring modification of the underlying CPU architecture. With TIGRA, the researcher aims to provide an architecture modification that will allow developers to fully leverage FPGA custom designs on a CPU without the overhead of communication via a standard bus. TIGRA reduces the required programming effort to incorporate fine-grained, tightly coupled accelerators to existing architectures and has implications for many common HPC algorithms, such as encryption or compression. The interface also provides developers with a mechanism for quickly testing proposed extensions to an architecture, such as built in posit arithmetic or improved hardware for existing functionality.

The remainder of this dissertation is organized as follows: Chapter 2 discusses existing work for different FPGA based accelerators, Chapter 3 provides the design of TIGRA and experiments proving the functionality, Chapter 4 explains the design of each case study used to prove TIGRA, Chapter 5 discusses the results and implications of the use of TIGRA, Chapter 6 shows the benefits of using partial reconfiguration, and Chapter 7 concludes the paper with a discussion of future work and summarized results.

### Chapter 2

## **Related Work**

In this section, we discuss the test cases used in Chapter 4 and the motivation behind these choices. We will also describe many different loosely and tightly coupled FPGA accelerators and the improvements they provide over existing architectures and pure software implementations.

#### 2.1 AES

With the rising usage of cloud computing and data transfers via the network, data security concerns have grown, pushing the need for fast encryption in datacenters. Rijndael, the Advanced Encryption Standard (AES) algorithm, is one of the most widely used algorithms for data security in high performance computing [12]. As FPGAs have become more widely used, developers have been targeting these reprogrammable devices in an attempt to include ultra low latency encryption hardware in existing designs. In early 2004, the authors of [15] achieve a 21.54 Gb/s AES design with a clock frequency of only 168.3 Mhz. A more recent design achieves a throughput of 54.52 Gb/s on FPGA hardware using AES-192 [2]. Both of these designs were executed on FPGAs without a host computer, restricting their usage in existing applications or within an HPC environment.

#### 2.2 Posits

Posit numbers are a rising data format intended to operate as a drop in replacement for the floating point number system [14]. Posits are the hardware friendly evolution of Type II Unums, a number format designed to improve upon the floating point system. This newer number system has proven to provide a higher dynamic range, with higher accuracy at a smaller data size than the existing floating point standard. Developers have begun testing posits in deep learning applications, which rely on floating point calculations to achieve high accuracy inference results. The authors in [10] show that an 8-bit posit implementation of Deep Neural Networks achieve the same classification results as the same network running on 32-bit floating point architectures. Further, [37] demonstrates a 51% reduction in power with the same comparison, showing the capabilities of posits. In [26], [25], and [27], the authors create a posit arithmetic generator for FPGAs that is used in Section 4.5 to enable Posit arithmetic via the TIGRA interface for each tested processor.

#### 2.3 Loosely Coupled Accelerators

Loosely coupled accelerators, devices that communicate over a bus to a host computer like a GPU, are very commonly used in HPC applications. OpenCL for FPGAs [21][53] enables the use of application specific hardware as a loosely coupled accelerator, and many developers have begun creating designs to leverage usage of these lower power devices for algorithm acceleration. [46] introduces an OpenCL based AES accelerator that achieves a throughput of 392.173 MB/s. Many other designs leverage the Rocket Custom Coprocessor (ROCC) interface from the Rocket Chip generator [7] to enable loosely coupled accelerators within the RISC-V ISA. The RoCC interface allows developers to more easily include custom logic within a Rocket Chip processor, and the interface also provides access to the floating point unit (FPU) and memory within the processor.

In [56], the authors create a low power YOLO network accelerator via RoCC that achieves 6.36 GOps/W. [9] introduces a DSP accelerator using the RoCC interface that achieves up to 100 times speedup over existing software based algorithms. The authors in [20] create "Centrifuge" to leverage high-level synthesis (HLS) and Fire Sim [32] and enable developers to create the interface for RoCC accelerators without the need to modify RTL directly. And the authors in [47] create *Picos*, a hardware based task-scheduler, and *Phentos*, a full Rocket Chip ecosystem utilizing *Picos*, resulting in a 308 times improvement compared to base designs without the hardware task-scheduler. While these results are promising, loosely coupled accelerators introduce overhead due to the communication latency incurred. [41] and the results in Section 5.3.4 explore the latency incurred when using the RoCC interface.

#### 2.4 Tightly Coupled Accelerators

Tightly coupled accelerators aim to remove the communication overhead incurred from loosely coupled designs, but often require much more programming effort to implement the accelerator. The developers of [24] create a tightly coupled AES system that achieves a 35% performance increase when compared to a loosely coupled implementation using an Avalon interface. In [3], a tightly coupled H.265/HEVC deblocking filter achieves an 11% performance increase when compared to the standard software implementation. Tightly coupled accelerators are also often used to implement extensions to an existing instruction set. The authors of [42] propose an out-of-order floating point extension and [33] introduces ten more bit-manipulation instructions to the RISC-V ISA. In [38], the authors propose a posit extension to RISC-V. In the described work, the authors replace the existing FPU in the Rocket Chip generator with custom logic for posit arithmetic and explain the difficulty in designing custom instructions and adding to an existing Rocket Chip processor. The authors in [31] develop the RISC-V Architecture Extension for the Number Theoretic Transform (RANTT) which incorporates a task scheduler and does not require the use of custom instructions. The RANTT design achieves up to 6x performance over a pure software based design, but pure hardware accelerator implementations out-perform this implementation.

#### 2.5 Partial Reconfiguration

As development tools mature, more researchers have begun to utilize partial reconfiguration (PR) in designs to allow for increased functionality of designs and reduce the area and power requirements when working with FPGAs. The authors of [16] develop a software defined radio (SDR) design that allows users to swap networking protocols within the FPGA at runtime to achieve a reduction of 76.71% power usage compared to a design that implements all required protocols when not using partial reconfiguration. The authors improve upon their own design by optimizing partitioning in [17] to further reduce power and area usage of five different communication protocols. In [1], the authors evaluate using partial reconfiguration within the RoCC interface by implementing the AES and DES encryption algorithms to achieve a speedup of up to 249.91 times when compared to the software implementation. This design enables the user to choose which encryption is required at runtime. PR is also used in video shot boundary detection to allow users to swap between different algorithms in [48], but the authors note the difficulty in improving the partial reconfiguration design

due to limitations within the FPGA development software.

#### 2.6 Summary

The works described here all provide improvements upon existing software based designs. The loosely coupled designs provide ease of programmability through HLS tools but incur a latency penalty due to bus communication. Conversely, tightly coupled designs incur no latency overhead and provide fine-grained control of a design but require much more effort to modify an existing processor. The TIGRA interface provides the ease of programmability given by loosely coupled designs while incurring no latency penalty similar to a tightly coupled design. Further, leveraging partial reconfigurability with the TIGRA interface improves the portability and modularity of custom logic in designs utilizing FPGAs for the custom logic.

### Chapter 3

## **Research Design and Methods**

In this chapter, we discuss the proposed design and usage of the Tightly Integrated Generic RISC-V Accelerator (TIGRA) interface for a generic processor, how to integrate TIGRA into an existing design, the forward-looking goal for TIGRA, and how to use the interface in a development environment.

#### 3.1 TIGRA Design

TIGRA is a tightly integrated, generic RISC-V accelerator interface that aims to bridge the gap between loosely and tightly coupled accelerators. This interface provides a simple interconnect between FPGA custom logic and a CPU pipeline that reduces the programming effort required to incorporate custom hardware with existing processors with no latency. The initial addition of a TIGRA interface incurs a one time programming cost, but reduces the programming effort to add any future custom logic to the processor. The intended design allows for the connected custom logic to exist separately from the CPU, but receive the benefits of an integrated hardware element or instruction set modification.

In this section we describe the design choices made for TIGRA, the minimal signal requirements for the interface, and design guidelines for developing and using TIGRA. Here, we target developers aiming to incorporate a TIGRA interface into RISC-V processors while maintaining simplicity, speed, and flexibility for hardware designs.

| 31 | 25       | 24 20      | 19 15 | 5 14 12 | 11 7     | 6 0    | )      |

|----|----------|------------|-------|---------|----------|--------|--------|

|    | funct7   | rs2        | rs1   | funct3  | rd       | opcode | R-type |

|    |          |            |       | -       | _        |        | _      |

|    | imm[11:  | 0]         | rs1   | funct3  | rd       | opcode | I-type |

|    |          |            |       | -       | _        |        | _      |

|    |          | imm[31:12] | rd    | opcode  | U-type   |        |        |

|    |          |            |       |         |          |        | _      |

| i  | mm[11:5] | rs2        | rs1   | funct3  | imm[4:0] | opcode | S-type |

Figure 3.1: The main RISC-V instruction type opcodes: Register, Immediate, Upper immediate, and Store.

#### 3.1.1 RISC-V ISA

RISC-V is an open-source ISA developed in an effort to provide a standard that drives innovation and enables easy customization and design of different processors [23]. The authors at RISC-V International maintain a database of many available designs for developers to download and test new extensions or designs. The availability and customizability of RISC-V CPUs motivates the choice to model TIGRA for use within this architecture, and the different instruction designs help motivate the interface design. Further, while TIGRA is motivated by RISC-V, the concepts presented are applicable to any existing architecture.

RISC-V is designed with 4 main instruction types, shown in Figure 3.1[50]. As shown, R-type instructions require two source registers and write a result to a destination register. I-type instructions are used for instructions that require immediate input values, such as add immediate or load word instructions, and use one source register and a 12-bit immediate value. As I-type instructions only allow for 12-bit values and most data-types are at minimum 32-bits wide, the RISC-V authors needed to create the U-type instructions. These instructions load the upper 20 bits of a register from an immediate value within the instruction. Used together, I and U-type instructions load a register with a 32-bit value. S-type instructions are used for stores, using one of the source registers as the base memory address and the other as the data to be written to memory. The immediate fields of the S-type instructions are used together as a memory offset. The *opcode* field of each type shown specifies the major opcode of the instruction. The *funct*3 and *funct*7 fields, when present, represent 3 and 7-bit minor opcodes, respectively, to further distinguish between instructions. The rs1, rs2, and rd fields point to locations within the processor register field to specify where to read from and write to as required by each instruction. We choose to model TIGRA using the R-type instruction, as this type provides the most generality and flexibility with data movement between custom logic and the processor. When creating TIGRA designs, we will use the major opcodes 0001011 and 0101011 as these are reserved by the RISC-V authors for custom instructions and guaranteed to not be used by future ISA extensions. As R-type instructions contain both *funct*7 and *funct*3 fields, this enables the creation of 1024 unique instructions per major opcode. Therefore, only one major opcode needs to be used for TIGRA custom instructions.

#### 3.1.2 Interface Requirements

We define a minimum of seven required signals in TIGRA to complete the interface between a processor and an FPGA based custom logic accelerator. Following the format of R-type instructions, two data inputs and one data output are required to meet all specifications. The signals  $cl_rs1$  and  $cl_rs2$  of Figure 3.2 correspond to the rs1 and rs2 fields, respectively, of an R-type instruction. Specifically, the rsX signals should pass the corresponding values from the register file of the CPU to TIGRA, the same data that would be passed to the ALU of the processor. The data output of the custom logic,  $cl_outData$ , corresponds to the rd field of the instruction and will ultimately be written back to this location in the register file. These three signals follow the data-width of registers within the implemented processor.