#### University of Tennessee, Knoxville

## TRACE: Tennessee Research and Creative **Exchange**

**Doctoral Dissertations**

Graduate School

5-2022

# Data Center Power System Emulation and GaN-Based High-**Efficiency Rectifier with Reactive Power Regulation**

Jingjing Sun University of Tennessee, Knoxville, jsun30@vols.utk.edu

Follow this and additional works at: https://trace.tennessee.edu/utk\_graddiss

Part of the Electrical and Electronics Commons, and the Power and Energy Commons

#### **Recommended Citation**

Sun, Jingjing, "Data Center Power System Emulation and GaN-Based High-Efficiency Rectifier with Reactive Power Regulation. " PhD diss., University of Tennessee, 2022. https://trace.tennessee.edu/utk\_graddiss/7200

This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Jingjing Sun entitled "Data Center Power System Emulation and GaN-Based High-Efficiency Rectifier with Reactive Power Regulation." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Leon M. Tolbert, Major Professor

We have read this dissertation and recommend its acceptance:

Leon M. Tolbert, Daniel J. Costinett, Helen Cui, Xueping Li

Accepted for the Council:

<u>Dixie L. Thompson</u>

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

# Data Center Power System Emulation and GaN-Based High-Efficiency Rectifier with Reactive Power Regulation

A Dissertation Presented for the

Doctor of Philosophy

Degree

The University of Tennessee, Knoxville

Jingjing Sun

May 2022

© by Jingjing Sun, 2022 All Rights Reserved. To my Mom

# Acknowledgments

I would like to express my sincere gratitude to my advisor, Dr. Leon M. Tolbert, for his support, guidance, and encouragement through my Ph.D. studies. I want to thank him for guiding me into this research field and teaching me how to do research with his broad vision, profound knowledge, and great patience. His kindness, elegant manners, and optimistic outlook have deeply affected me, which motivates me to refine myself and always be respectful.

I would also like to show my sincere gratitude to my co-advisor Dr. Daniel J. Costinett, who always provides me precious suggestions and inspires new ideas on my research. With his guidance in my Ph.D. studies, I have gained a solid understanding of power electronics. His enthusiasm, self-discipline, and rigorous attitude toward research have influenced me deeply on how to be a qualified researcher and engineer.

I would like to extend my gratitude to Dr. Fred Wang, Dr. Benjamin J. Blalock, Dr. Kevin Bai, and Dr. Helen Cui for their instruction. They help me to broaden my knowledge on power electronics, and are always generous to give me support, suggestions, and encouragement.

I would like to appreciate Dr. Xueping Li for serving on my dissertation committee and giving me good suggestions.

I am also grateful to Dr. Chien-Fei Chen, Dr. Anne Skutnik, Mr. Robert B. Martin, Ms. Wendy Smith, Ms. Dana Bryson, Mr. Ryan Smiley, and all other staff members for their efforts on providing a wonderful and safe educational environment.

Special thanks to all the colleagues in the power electronics labs and EECS department in UTK. I really enjoy working with them and cherish the friendships with them. Particularly, I want to thank Dr. Bo Liu, Dr. Ling Jiang, Dr. Handong Gui, Dr. Shuyao Wang for

their kindness and generous help in both my study and daily life. Their suggestions have helped me solve many problems. Genuine appreciation also goes to the colleagues whom I worked with in different projects, including Dr. Shiqi Ji, Dr. Sheng Zheng, Dr. Xingxuan Huang, Mr. Nathan Strain, Ms. Maeve Lawniczak, Mr. Douglas Bouler, Dr. Chongwen Zhao, Dr. Jie Li, Mr. Ruiyang Qin, Dr. Jingxin Wang, Mr. Peter Pham, Dr. Spencer Cochran. It was a great experience to work with them. I also cherish the help and friendship from other colleagues and alumni in the power electronics labs. They are Dr. Zheyu Zhang, Dr. Xiaojie Shi, Dr. Zhiqiang Wang, Dr. Ren Ren, Dr. RuiRui Chen, Dr. Edward Jones, Dr. Yiwei Ma, Dr. Fei Yang, Dr. Wenchao Cao, Dr. Saeed Anwar, Dr. Shuoting Zhang, Dr. Li Zhang, Mr. Liyan Zhu, Mr. Yang Huang, Mr. Yu Yan, Mr. Ziwei Liang, Dr. Zhe Yang, Mr. Jiahao Niu, Mr. Haiguo Li, Mr. Zhou Dong, Ms. Le Kong, Mr. Dingrui Li, Mr. Kamal Sabi, Mr. Andrew Foote, Mr. Jared Baxter, Dr. Ishita Ray, Ms. Paychuda Kritprajun, Mr. Nattapat Praisuwanna, Ms. Jiu Jia, and Mr. Xingxuan Tian.

I would like to express my deepest gratitude and love to my great Mom Delan Shan, who is the strongest, bravest, and most optimistic person in my mind, and my great Dad Jianguo Sun for their unconditional love and support in my life. I want to give my heartiest thank to my fiance, Mr. Yusen Fan, for his meticulous care and love all the time. His gentle personality and cheerful attitude always encourage me to make progress on research and explore the wonderful world.

This dissertation made use of the Engineering Research Center Shared Facilities supported by the Engineering Research Center Program of the National Science Foundation and the Department of Energy under NSF Award Number EEC-1041877 and the CURENT Industry Partnership Program.

## Abstract

Data centers are indispensable for today's computing and networking society, which has a considerable power consumption and significant impact on power system. Meanwhile, the average energy usage efficiency of data centers is still not high, leading to significant power loss and system cost.

In this dissertation, effective methods are proposed to investigate the data center load characteristics, improve data center power usage efficiency, and reduce the system cost.

First, a dynamic power model of a typical data center ac power system is proposed, which is complete and able to predict the data center's dynamic performance. Also, a converter-based data center power emulator serving as an all-in-one load is developed. The power emulator has been verified experimentally in a regional network in the HTB. Dynamic performances during voltage sag events and server load variations are emulated and discussed.

Then, a gallium nitride (GaN) based critical conduction mode (CRM) totem-pole power factor correction (PFC) rectifier is designed as the single-phase front-end rectifier to improve the data center power distribution efficiency. Zero voltage switching (ZVS) modulation with ZVS time margin is developed, and a digital variable ON-time control is employed. A hardware prototype of the PFC rectifier is built and demonstrated with high efficiency. To achieve low input current total harmonic distortion (iTHD), current distortion mechanisms are analyzed, and effective solutions for mitigating current distortion are proposed and validated with experiments.

The idea of providing reactive power compensation with the rack-level GaN-based frontend rectifiers is proposed for data centers to reduce data center's power loss and system cost. Full-range ZVS modulation is extended into non-unity PF condition and a GaN-based T-type totem-pole rectifier with reactive power control is proposed. A hardware prototype of the proposed rectifier is built and demonstrated experimentally with high power efficiency and flexible reactive power regulation. Experimental emulation of the whole data center system also validates the capability of reactive power compensation by the front-end rectifiers, which can also generate or consume more reactive power to achieve flexible PF regulation and help support the power system.

# Table of Contents

| 1 | Intr | oducti  | ion                                                   | 1  |

|---|------|---------|-------------------------------------------------------|----|

|   | 1.1  | Backg   | round of Data Centers                                 | 1  |

|   |      | 1.1.1   | Load Performance                                      | 1  |

|   |      | 1.1.2   | Energy Efficiency                                     | 3  |

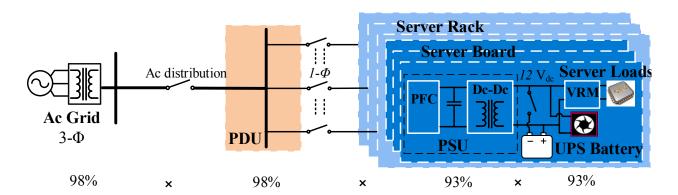

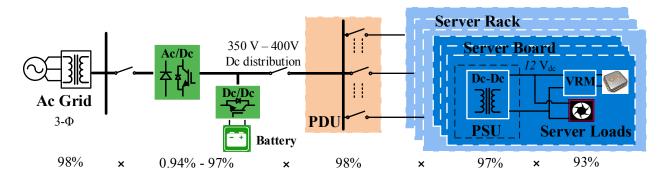

|   |      | 1.1.3   | Power Distribution Architecture                       | 8  |

|   |      | 1.1.4   | Reactive Power                                        | 10 |

|   | 1.2  | Motiva  | ation and Strategy                                    | 14 |

|   |      | 1.2.1   | Motivation                                            | 14 |

|   |      | 1.2.2   | Strategy                                              | 15 |

|   | 1.3  | Disser  | tation Outline                                        | 16 |

| 2 | Lite | erature | e Review                                              | 18 |

|   | 2.1  | Data (  | Center Power Model and Simulator/Emulator             | 18 |

|   |      | 2.1.1   | Data Center Power Model                               | 18 |

|   |      | 2.1.2   | Simulation and Emulation Tools for Power System       | 19 |

|   | 2.2  | Topolo  | ogies of Single-Phase Front-End Rectifier             | 23 |

|   | 2.3  | Soft S  | witching Techniques                                   | 32 |

|   |      | 2.3.1   | Principle of Soft Switching                           | 32 |

|   |      | 2.3.2   | ZVS Realization                                       | 33 |

|   | 2.4  | ZVS (   | Control Strategies of Single-Phase Rectifier          | 36 |

|   | 2.5  | Currei  | nt Distortion and Mitigation                          | 41 |

|   | 2.6  | Reacti  | ive Power Compensation                                | 45 |

|   |      | 2.6.1   | Traditional Techniques of Reactive Power Compensation | 45 |

|   |     | 2.6.2  | Single-Phase Rectifier for Reactive Power Compensation        | 46         |

|---|-----|--------|---------------------------------------------------------------|------------|

|   | 2.7 | Summ   | nary                                                          | 51         |

| 3 | Mo  | deling | and Emulation of Data Center Power Distribution System        | <b>5</b> 4 |

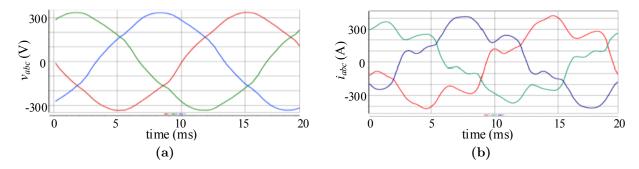

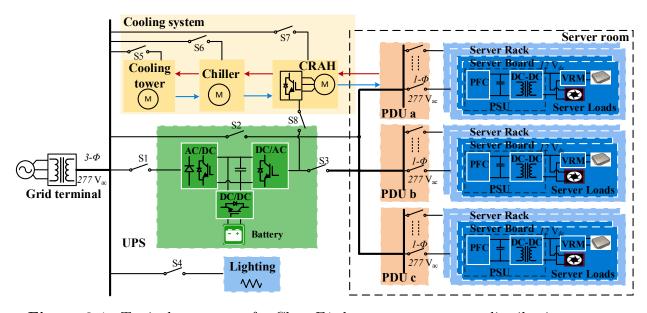

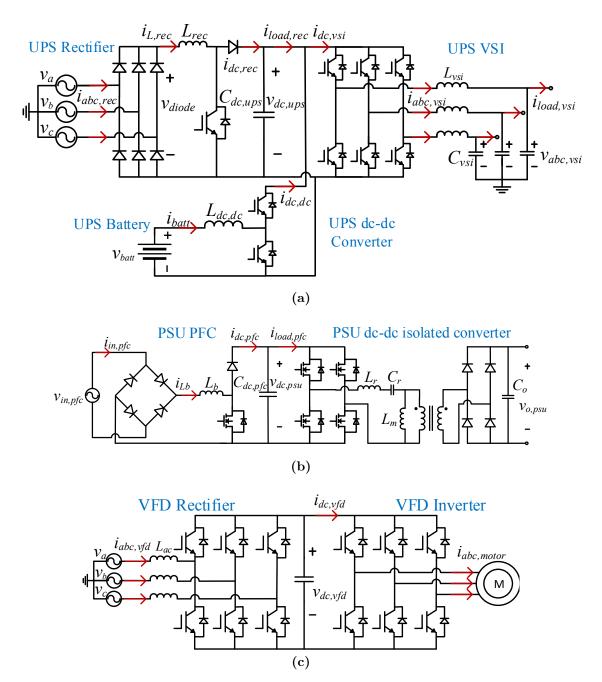

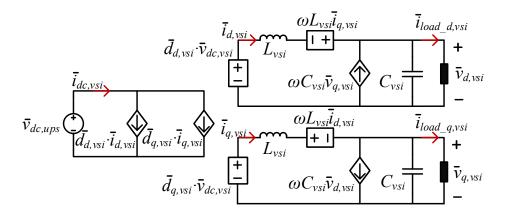

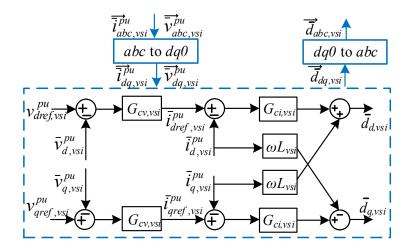

|   | 3.1 | System | m Circuit and Operation Principle                             | 55         |

|   |     | 3.1.1  | Circuit Topology and Control                                  | 55         |

|   |     | 3.1.2  | Operation Principle                                           | 59         |

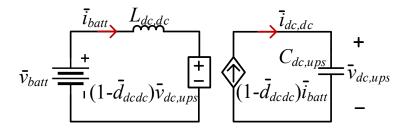

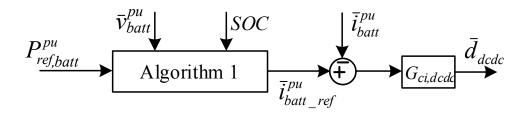

|   | 3.2 | Dynar  | mic Data Center Power Model                                   | 61         |

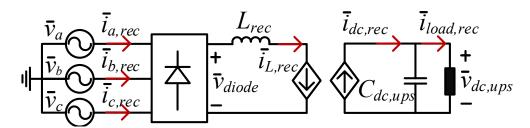

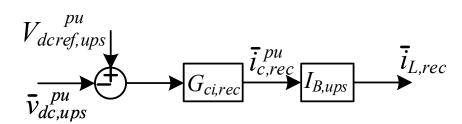

|   |     | 3.2.1  | UPS Model                                                     | 61         |

|   |     | 3.2.2  | PSU Model                                                     | 70         |

|   |     | 3.2.3  | Cooling System Model                                          | 72         |

|   |     | 3.2.4  | Server and Cooling Load Model                                 | 77         |

|   |     | 3.2.5  | Simulation                                                    | 82         |

|   | 3.3 | Data   | Center Power Emulator                                         | 89         |

|   |     | 3.3.1  | Model Digitization and Simplification                         | 89         |

|   |     | 3.3.2  | Generalized System Model                                      | 96         |

|   |     | 3.3.3  | Hardware Implementation                                       | 96         |

|   | 3.4 | Exper  | imental Verification                                          | 100        |

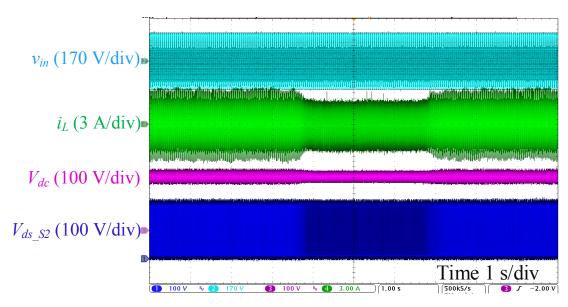

|   |     | 3.4.1  | Experimental Emulation of Voltage Sag Events                  | 100        |

|   |     | 3.4.2  | Experimental Emulation of Server Load Variations              | 102        |

|   | 3.5 | Summ   | nary                                                          | 102        |

| 4 | Gal | N-Base | ed Bridgeless PFC Design                                      | 105        |

|   | 4.1 | Topolo | ogy Selection                                                 | 105        |

|   |     | 4.1.1  | Bridgeless Totem-Pole PFC Design                              | 106        |

|   |     | 4.1.2  | Bridgeless Four-level Flying Capacitor Totem-Pole PFC         | 106        |

|   |     | 4.1.3  | Performance Evaluation and Comparison                         | 109        |

|   | 4.2 | GaN-I  | Based Totem-Pole PFC Rectifier with Full-Range ZVS Modulation | 114        |

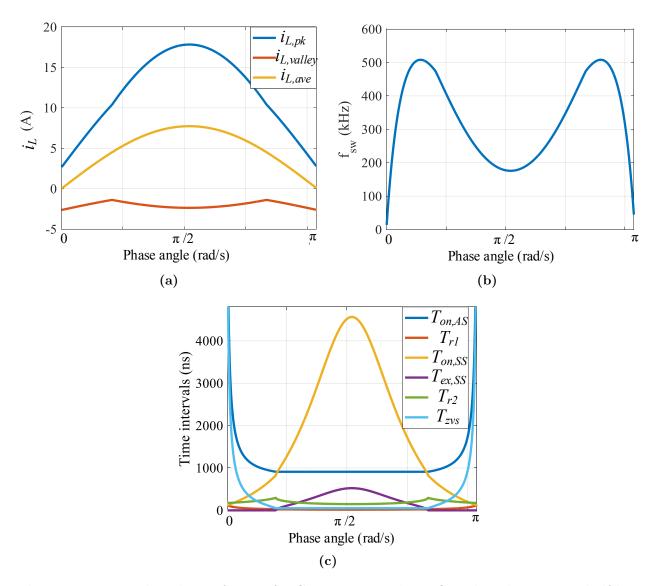

|   |     | 4.2.1  | Operation Principle                                           | 114        |

|   |     | 4.2.2  | Adaptive Analytical Converter Model                           | 119        |

|   | 4.3 | Comp   | onent Selection                                               | 125        |

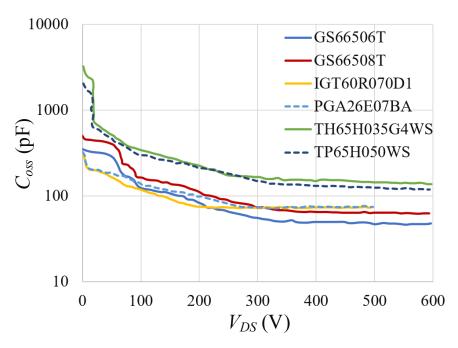

|   |     | 4.3.1   | Device Selection                                                       | 123   |

|---|-----|---------|------------------------------------------------------------------------|-------|

|   |     | 4.3.2   | Dc-Link Capacitor Selection                                            | 125   |

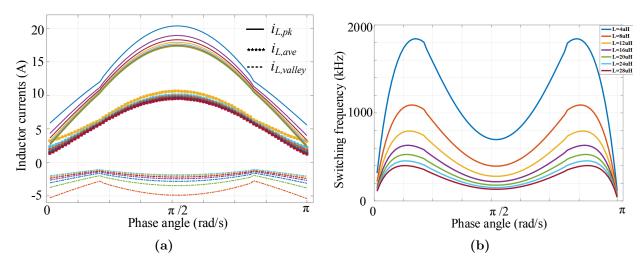

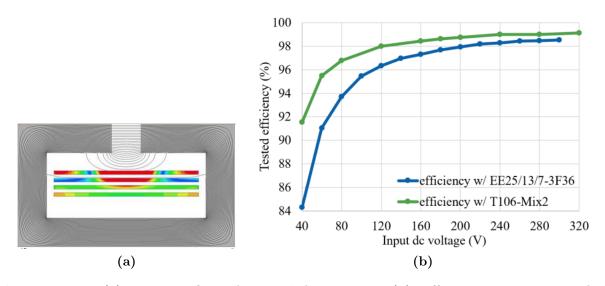

|   |     | 4.3.3   | Boost Inductor Design                                                  | 125   |

|   | 4.4 | Contr   | ol Implementation                                                      | 129   |

|   |     | 4.4.1   | Digital-Based Variable On-time Control                                 | 129   |

|   |     | 4.4.2   | Voltage-Loop Controller Design                                         | 132   |

|   | 4.5 | Exper   | imental Verification                                                   | 134   |

|   | 4.6 | Summ    | nary                                                                   | 134   |

| 5 | Mit | igation | n of Current Distortion for GaN-Based Totem-Pole PFC                   | 138   |

|   | 5.1 | Analy   | sis of Current Distortion Issues                                       | 139   |

|   |     | 5.1.1   | Line-Cycle Current Distortion                                          | 139   |

|   |     | 5.1.2   | Ac Line Zero-Crossing Current Spike                                    | 141   |

|   | 5.2 | Mitiga  | ation Methods for Current Distortion                                   | 148   |

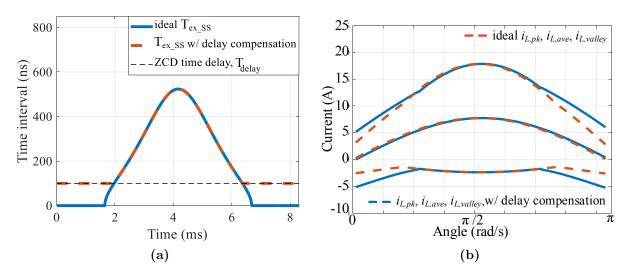

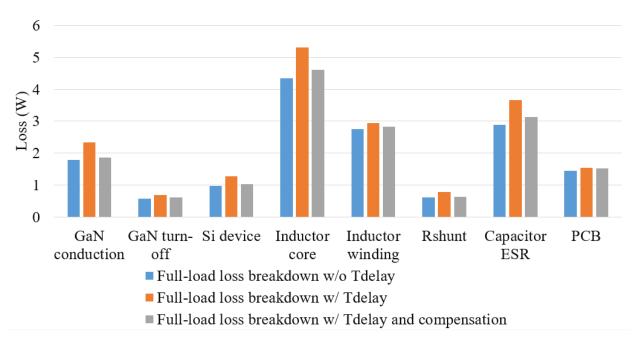

|   |     | 5.2.1   | Delay Compensation for Line-Cycle Current Distortion                   | 148   |

|   |     | 5.2.2   | Methods for Zero-Crossing Current Spike Elimination                    | 151   |

|   | 5.3 | Exper   | imental Verification                                                   | 153   |

|   |     | 5.3.1   | Verification of the Line-Cycle Current Distortion Mitigation           | 153   |

|   |     | 5.3.2   | Verification of the Ac Line Zero-Crossing Current Spike and Mitigation | n 155 |

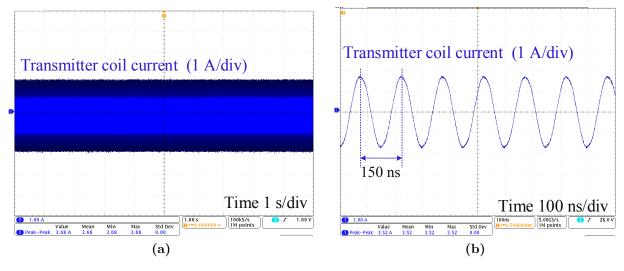

|   | 5.4 | CRM     | Totem-Pole PFC in MHz WPT System                                       | 159   |

|   |     | 5.4.1   | CRM Totem-Pole PFC for a<br>N All-GaN 6.78 MHz WPT System $\ .$        | 159   |

|   |     | 5.4.2   | Noise Impact on Current Distortion                                     | 161   |

|   |     | 5.4.3   | Noise Immunity Approaches                                              | 164   |

|   |     | 5.4.4   | Experimental Verification                                              | 168   |

|   | 5.5 | Summ    | nary                                                                   | 175   |

| 6 | Gal | N-Base  | ed Rectifier with Reactive Power Regulation                            | 179   |

|   | 6.1 | Advar   | ntages of Reactive Power Compensation by Front-End Rectifiers          | 180   |

|   | 6.2 | CRM     | Totem-Pole Rectifier with Reactive Power                               | 186   |

|   |     | 6.2.1   | Effect of Reactive Power on Dc Capacitance                             | 186   |

|   |     | 6.2.2   | ZVS Modulation with Non-Unity PF                                       | 189   |

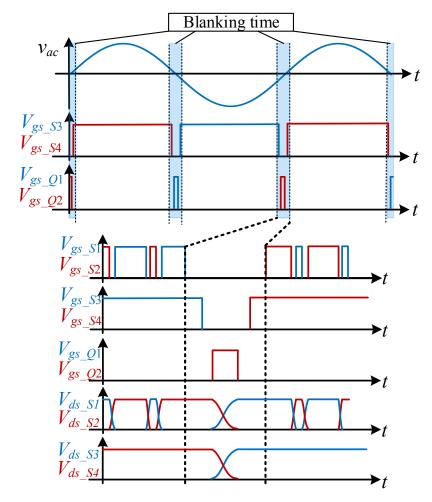

|   |     | 6.2.3     | Ac Line Zero-Crossing Challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 193                     |

|---|-----|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|   | 6.3 | Rectif    | ier Topology Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 198                     |

|   |     | 6.3.1     | Dual Boost Full-Bridge (DBFB) Rectifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 198                     |

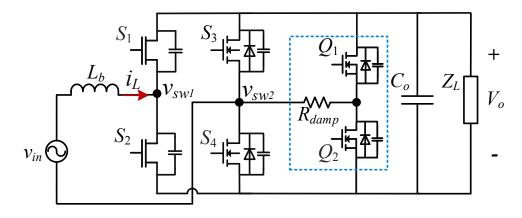

|   |     | 6.3.2     | T-Type Totem-Pole Rectifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 204                     |

|   |     | 6.3.3     | Performance Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 207                     |

|   | 6.4 | Contro    | ol Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 213                     |

|   |     | 6.4.1     | Control Strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 213                     |

|   |     | 6.4.2     | Controller Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 215                     |

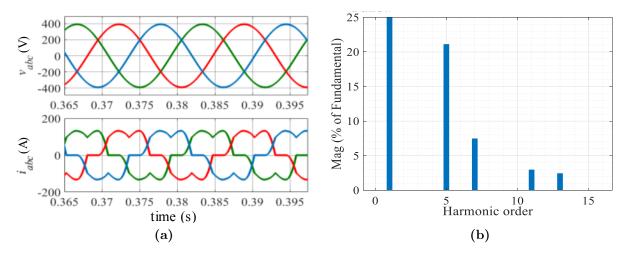

|   |     | 6.4.3     | Simulation Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 217                     |

|   | 6.5 | Summ      | ary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 219                     |

| 7 | Doo | .4:6 on 3 | Varification and Data Contan System Emplotion with Departir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |

| • |     |           | $egin{array}{lll} 	ext{Verification} & 	ext{and} & 	ext{Data} & 	ext{Center System Emulation} & 	ext{with Reactive} \ 	ext{gulation} & 	ext{constant} & 	ext{$ | $rac{\mathbf{e}}{222}$ |

|   | 7.1 |           | eation of the T-type Totem-Pole Rectifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 223                     |

|   | 1.1 | 7.1.1     | Hardware Prototype Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                         |

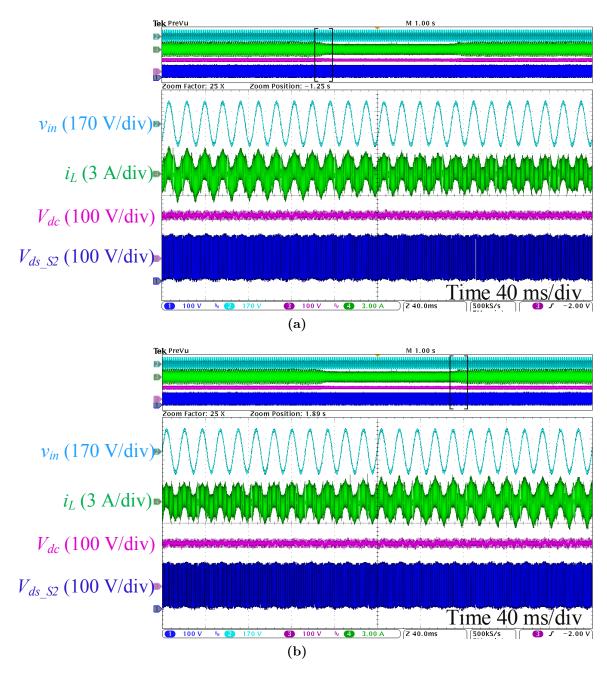

|   |     | 7.1.1     | Experimental Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 223                     |

|   | 7.2 |           | ation of the Data Center Power System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $\frac{225}{235}$       |

|   | 1.4 | 7.2.1     | Data Center Power System with Reactive Power Regulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 235                     |

|   |     | 7.2.1     | Experimental Emulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\frac{230}{238}$       |

|   | 7.3 |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 240                     |

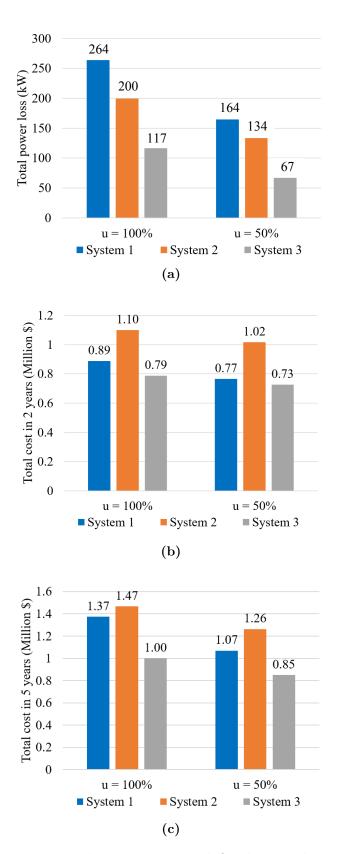

|   |     | •         | n Cost and Loss Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                         |

|   | 7.4 | Summ      | ary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 247                     |

| 8 | Con | clusio    | n and Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 248                     |

|   | 8.1 | Conclu    | usion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 248                     |

|   |     | 8.1.1     | Summary of the Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 248                     |

|   |     | 8.1.2     | Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 250                     |

|   |     | 8.1.3     | Publication List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 251                     |

|   | 8.2 | Future    | e Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 253                     |

|   |     | 8.2.1     | Microgrid Emulation with Data Center Load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 253                     |

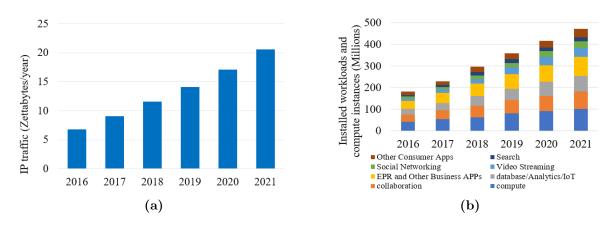

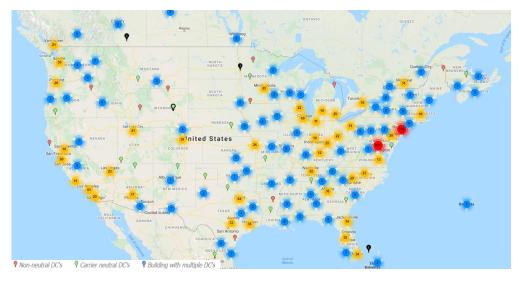

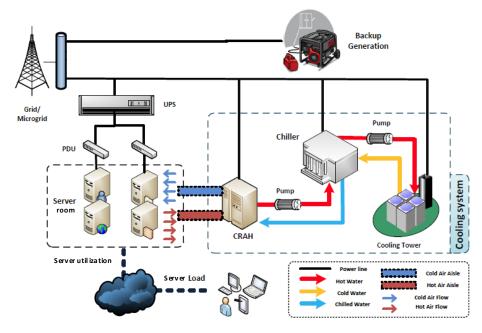

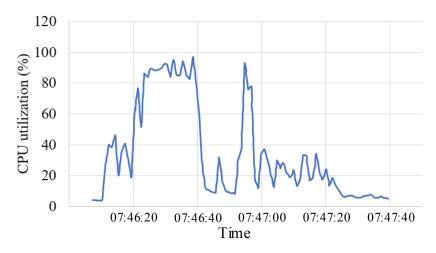

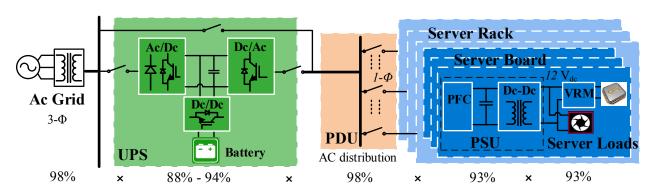

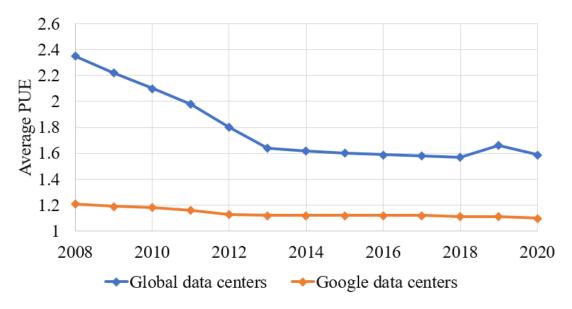

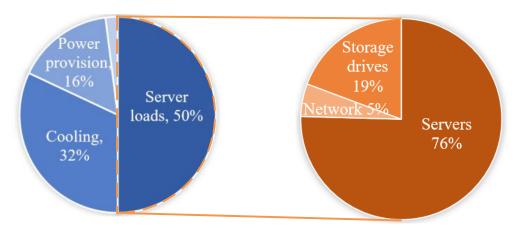

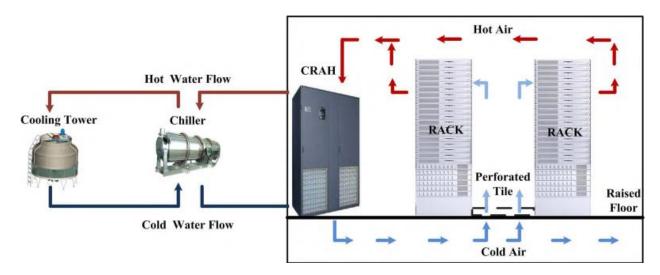

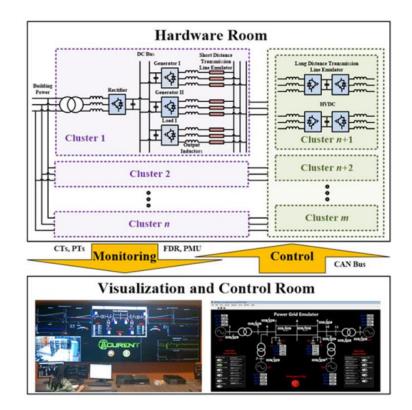

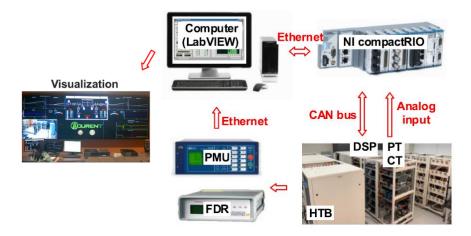

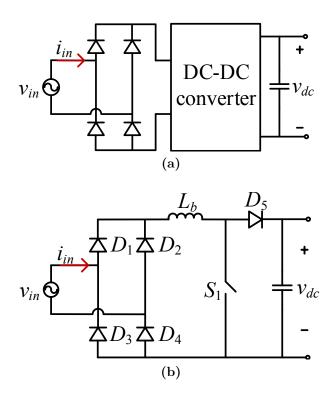

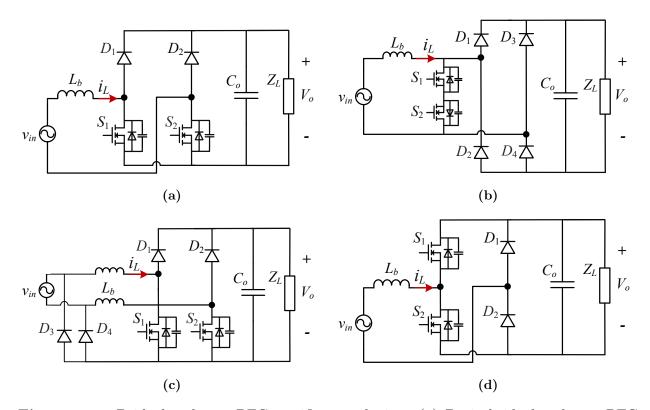

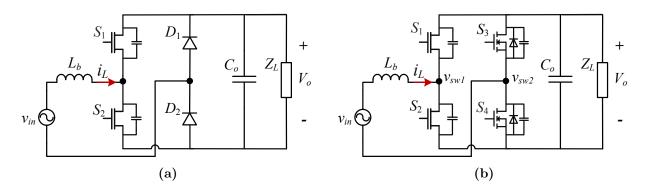

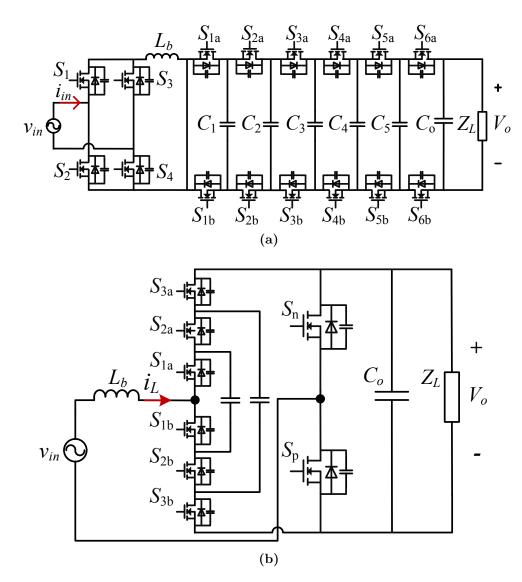

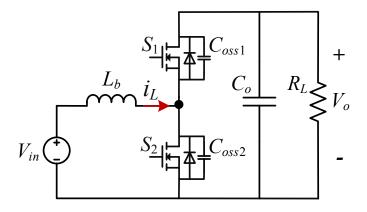

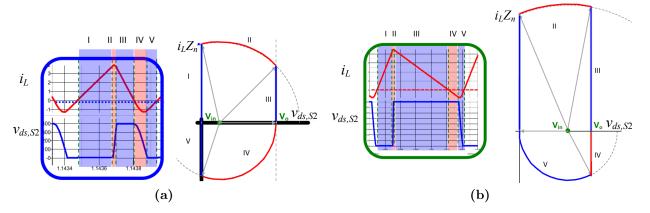

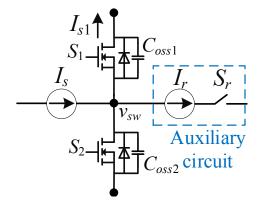

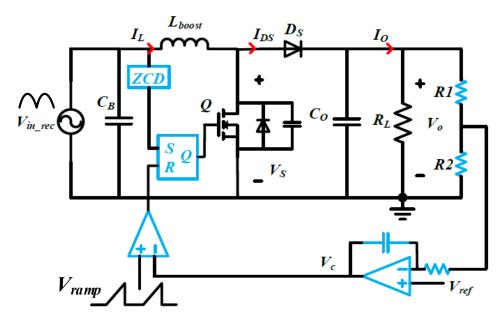

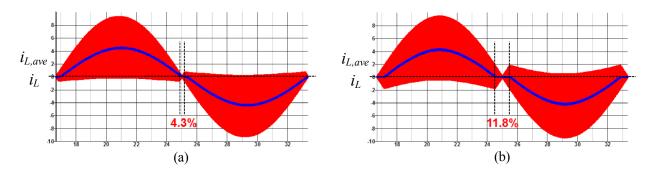

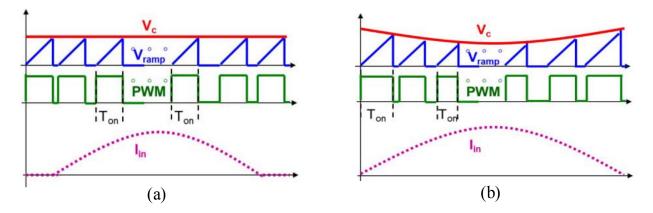

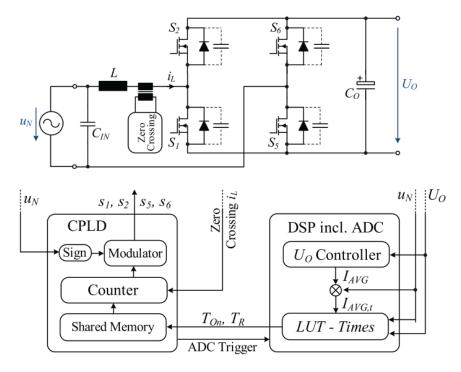

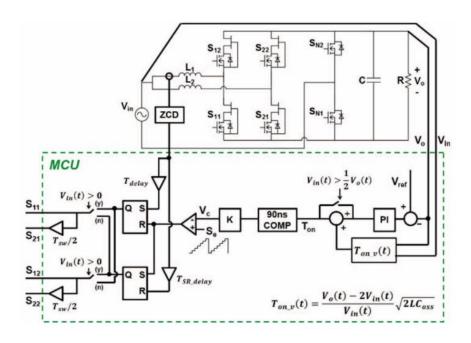

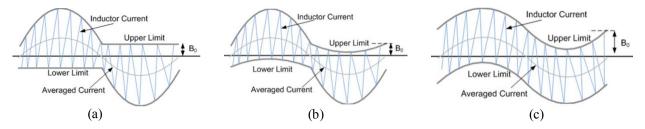

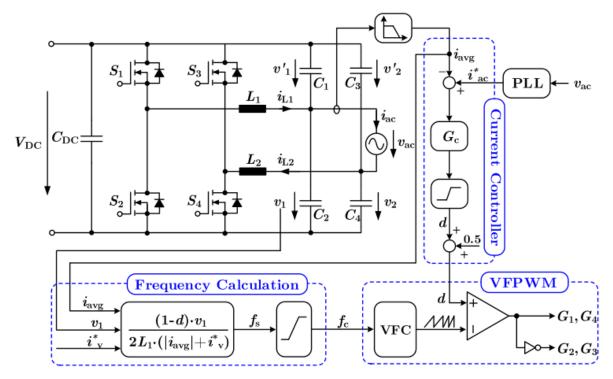

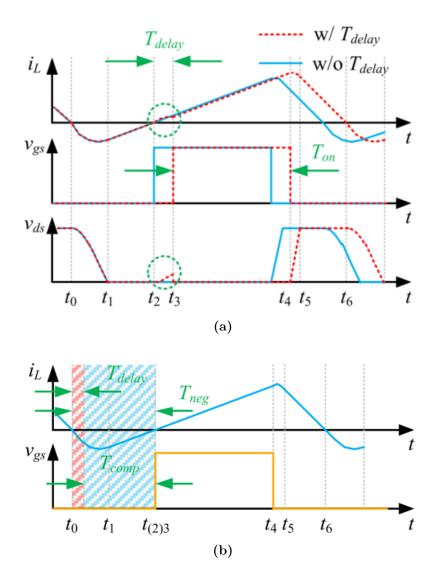

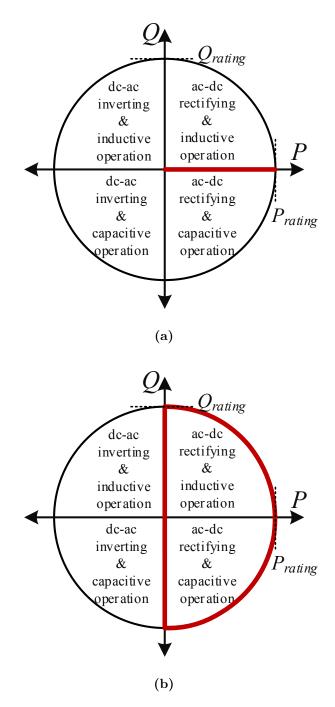

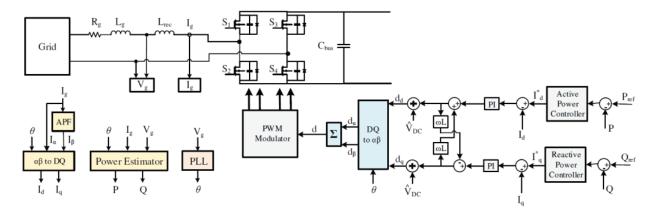

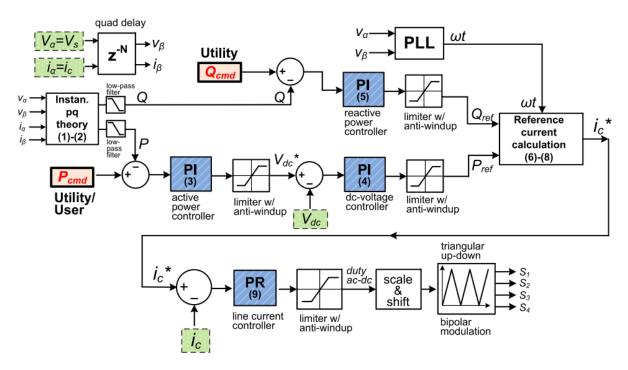

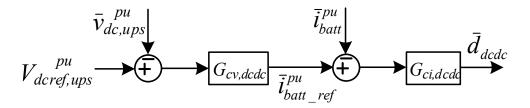

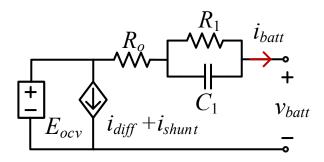

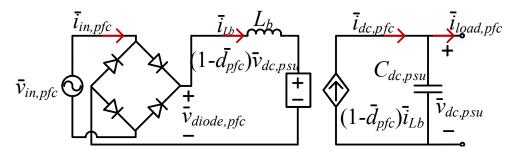

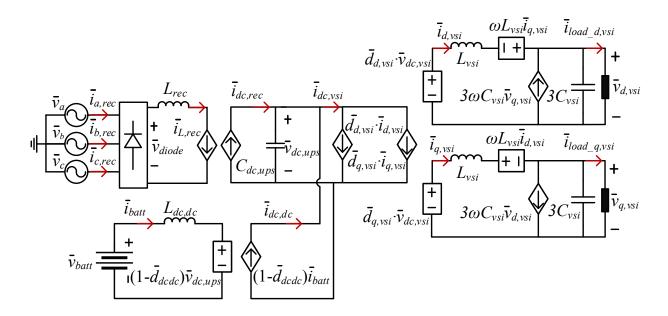

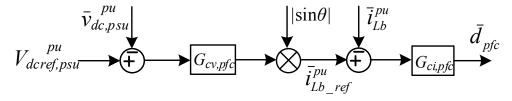

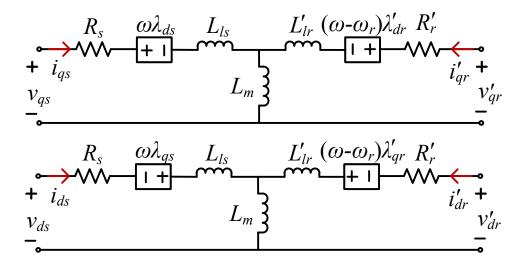

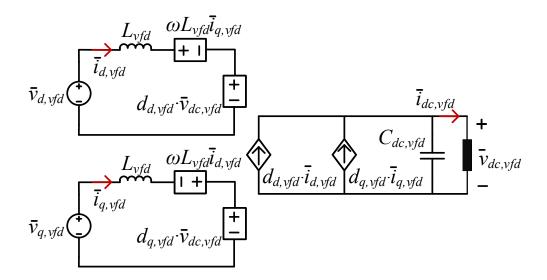

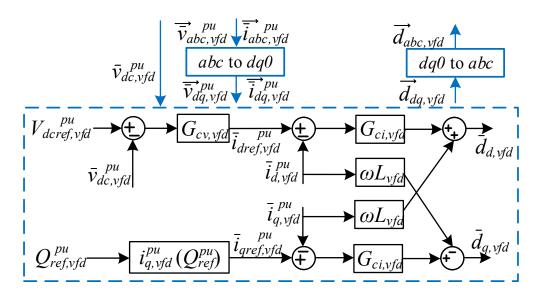

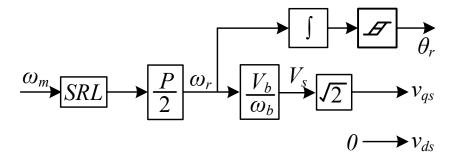

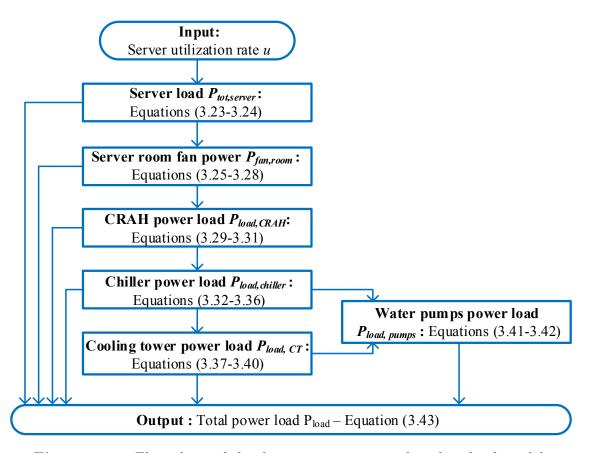

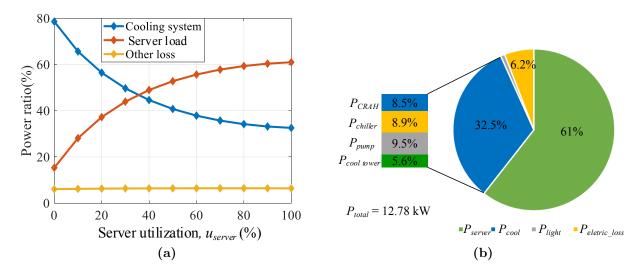

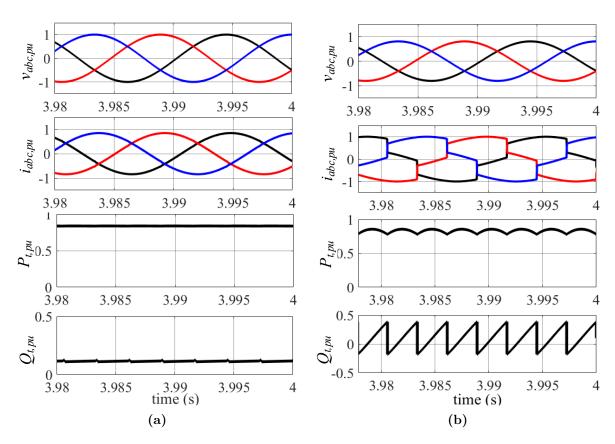

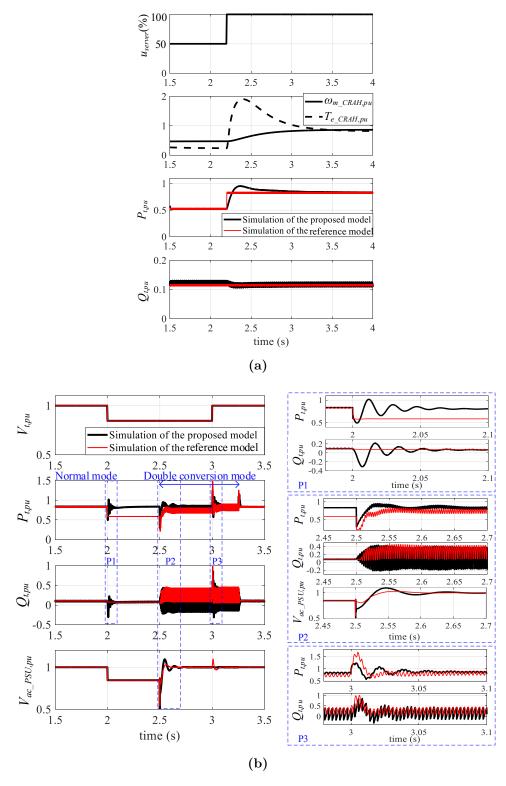

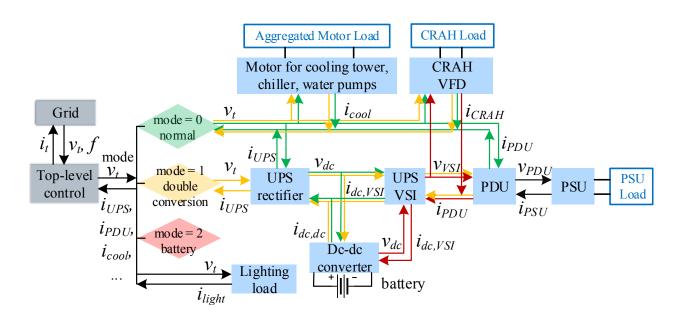

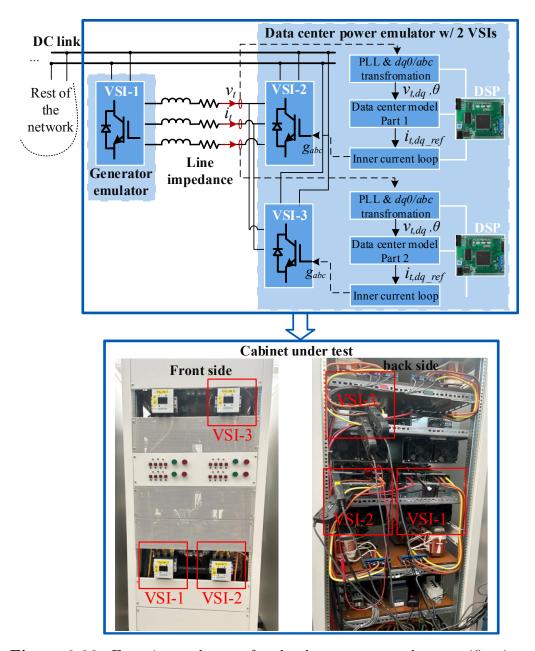

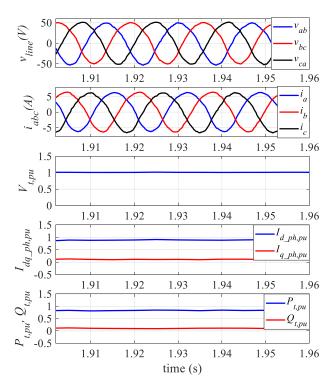

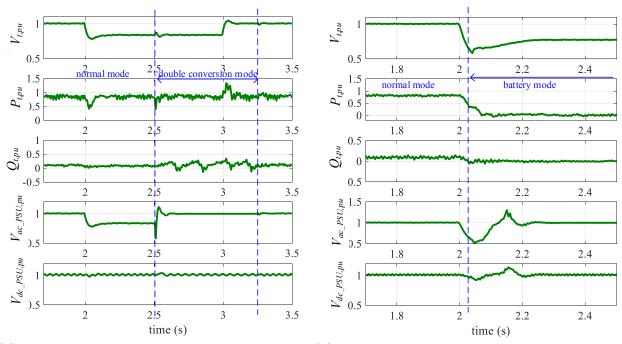

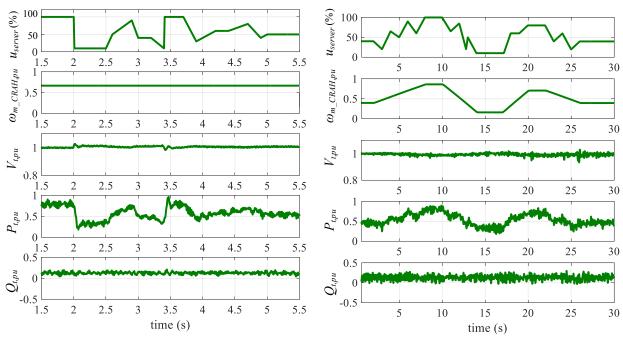

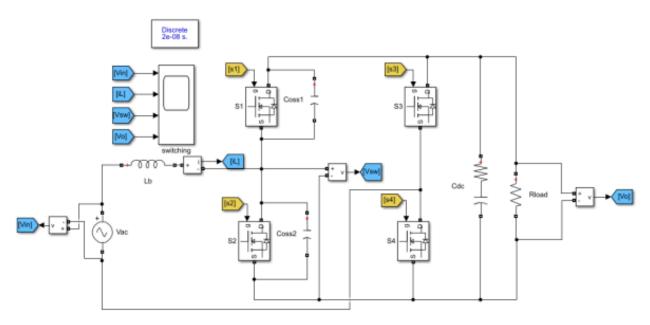

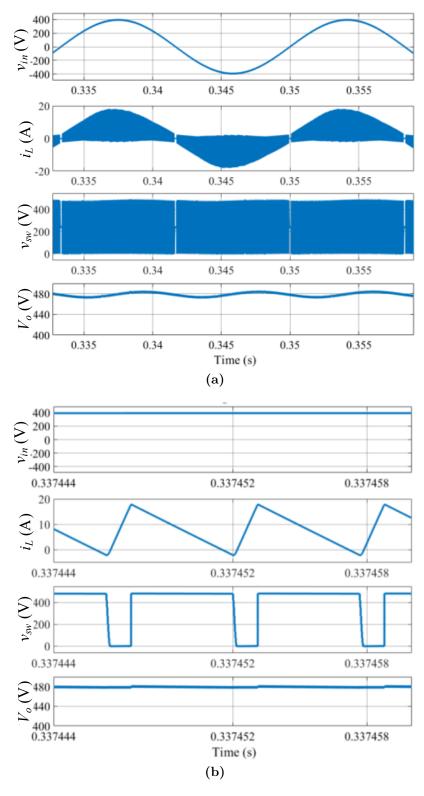

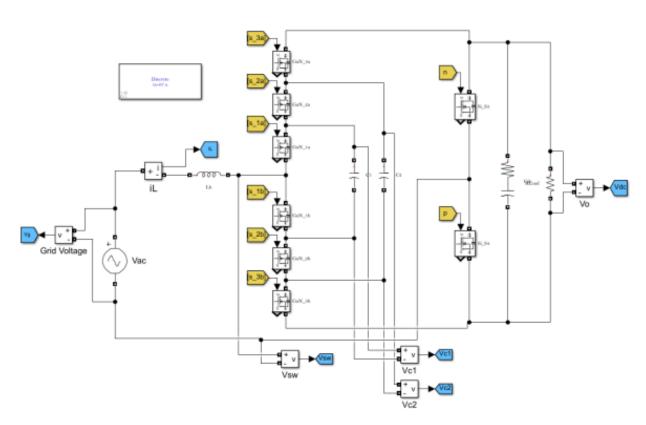

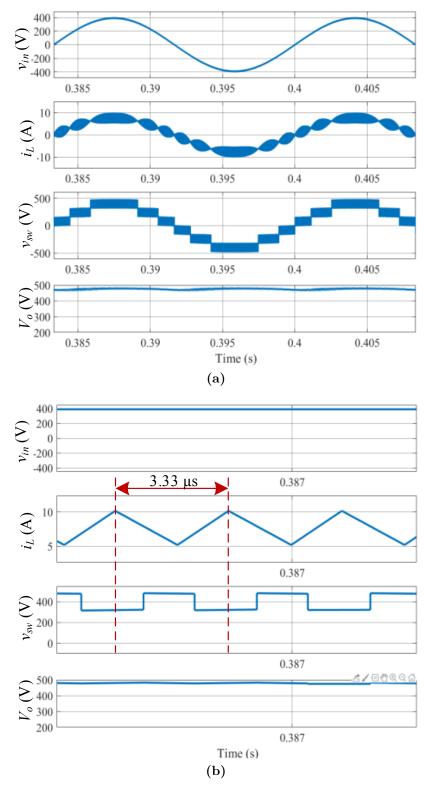

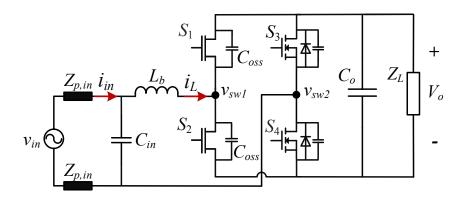

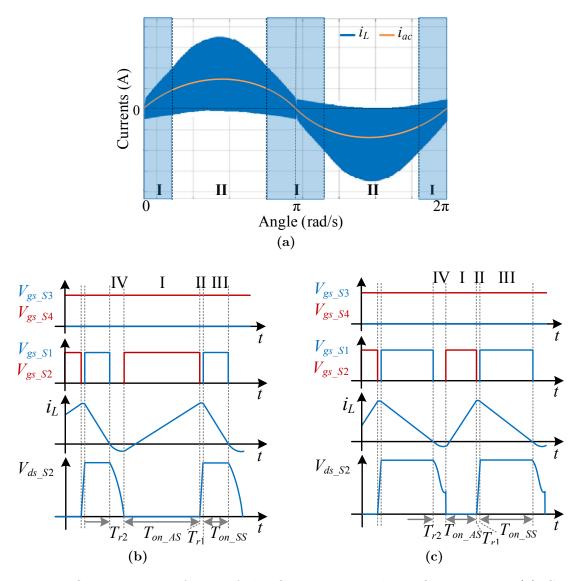

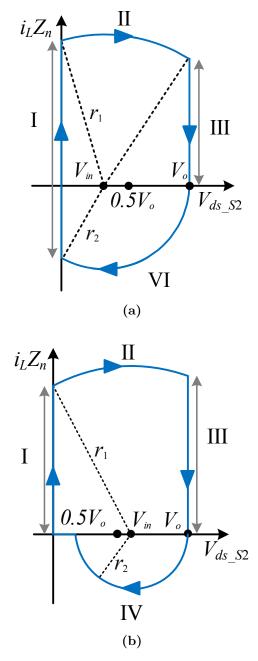

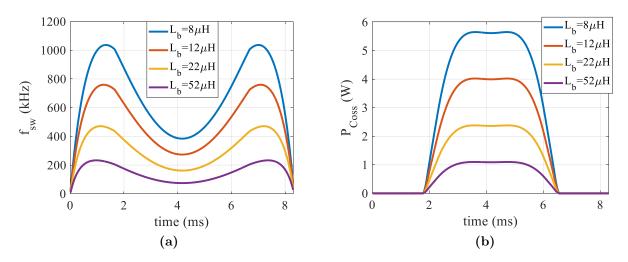

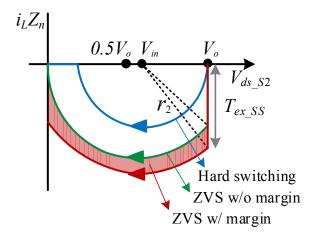

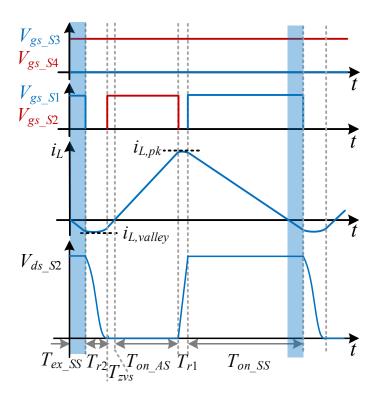

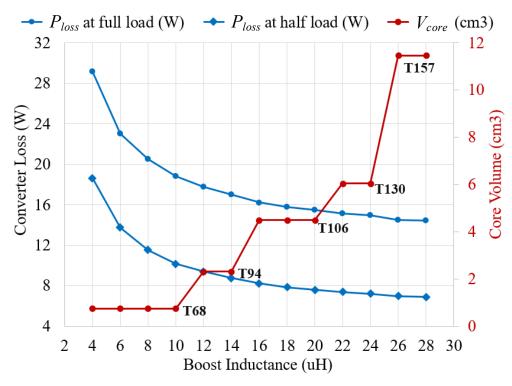

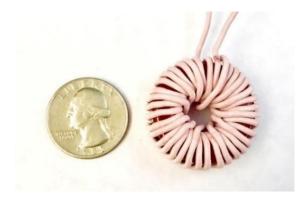

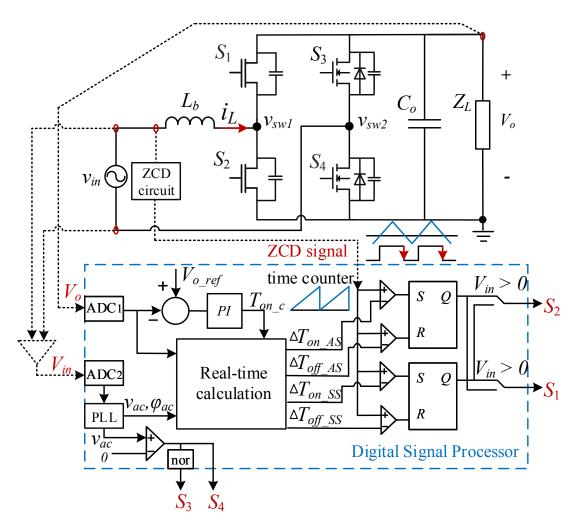

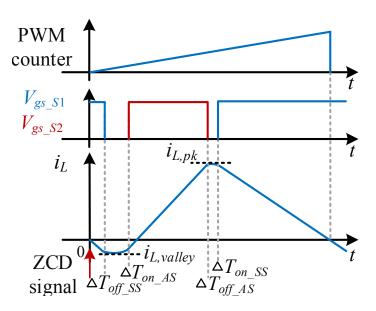

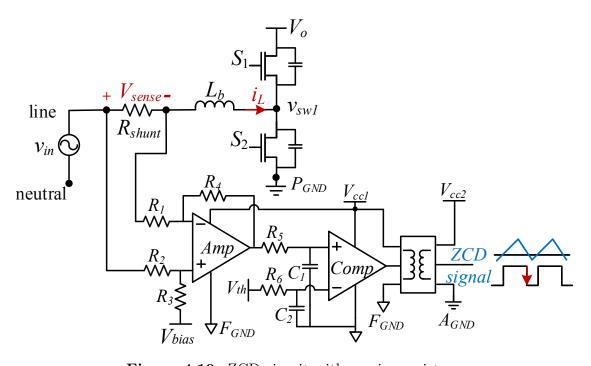

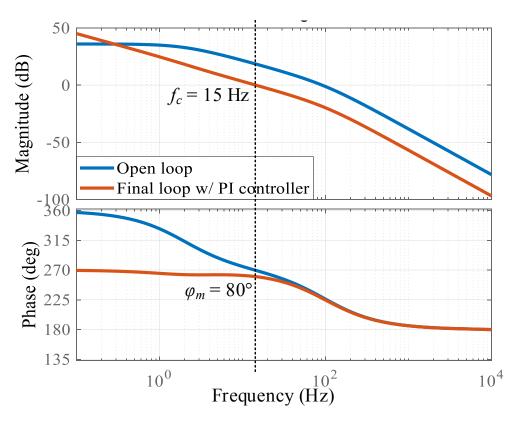

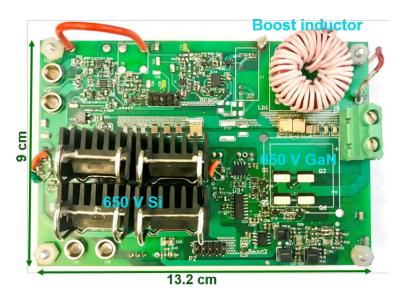

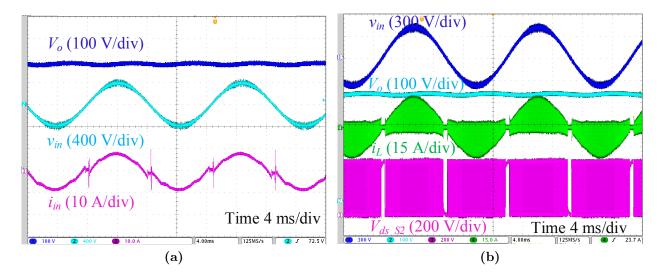

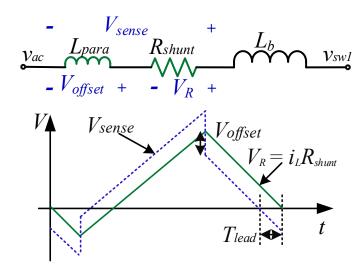

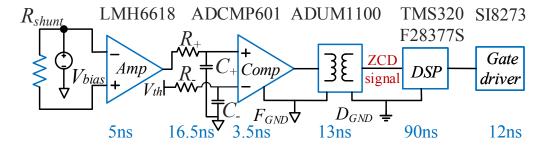

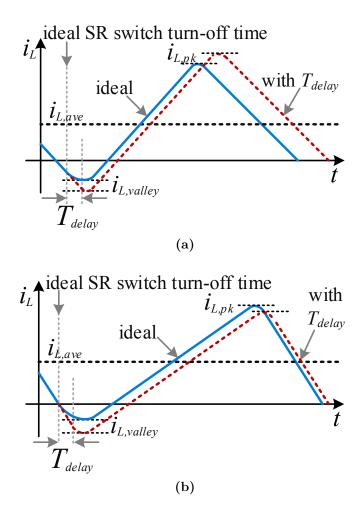

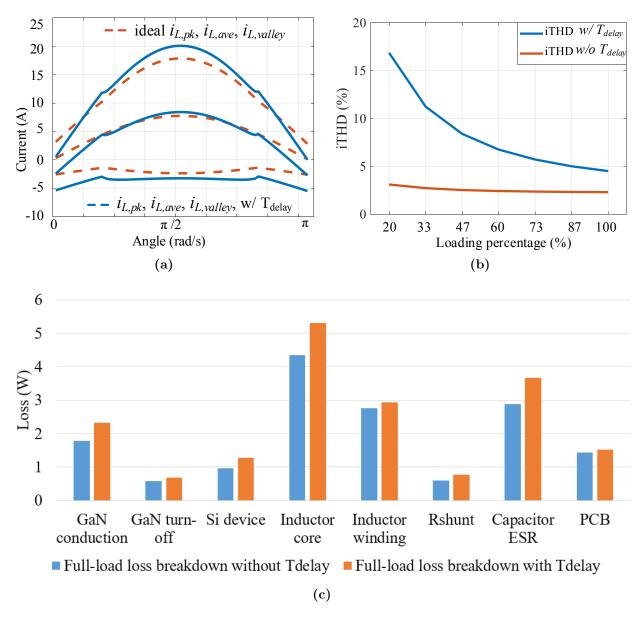

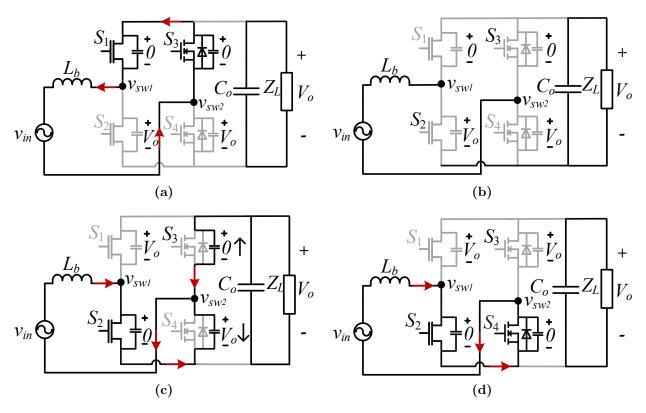

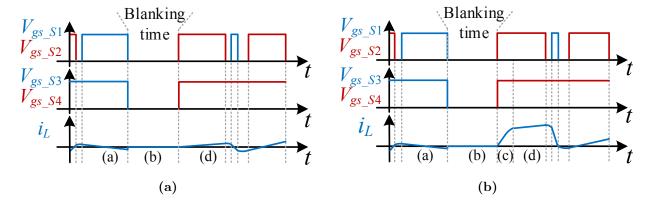

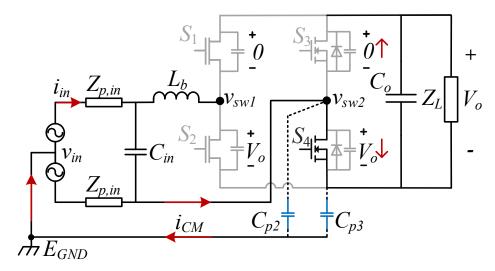

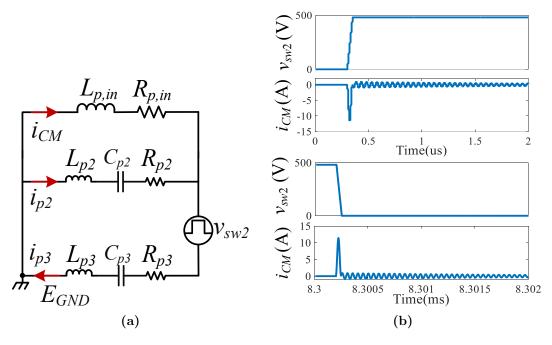

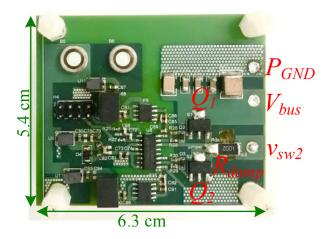

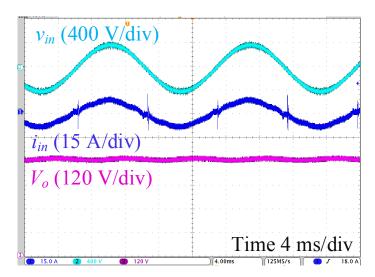

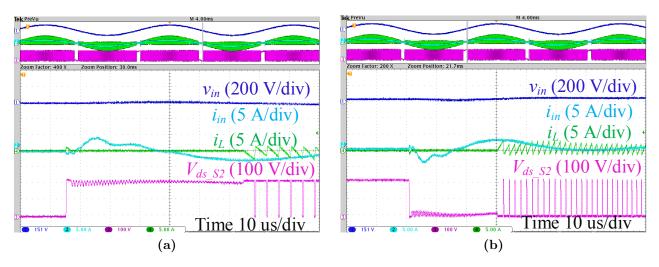

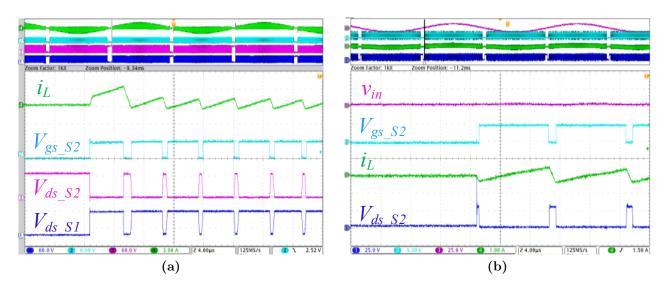

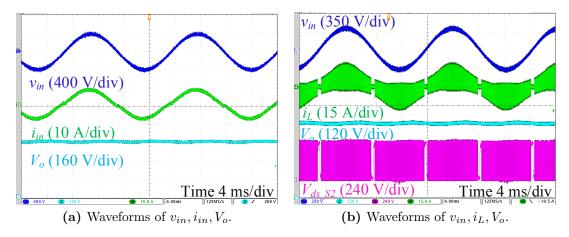

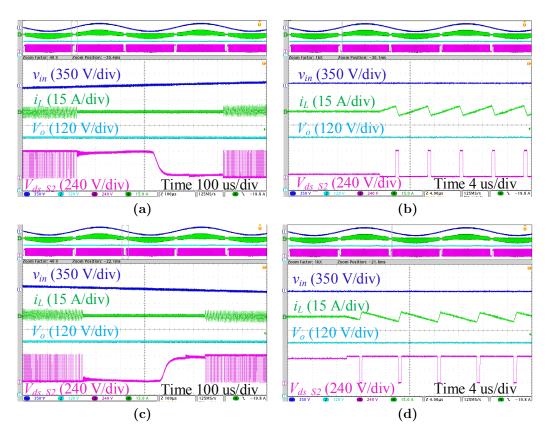

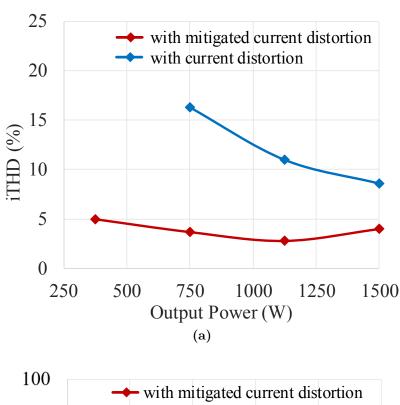

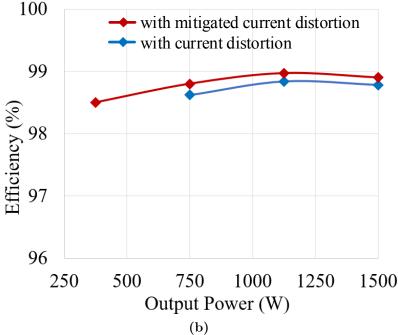

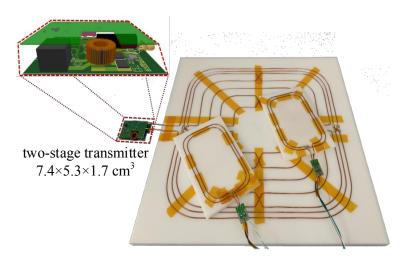

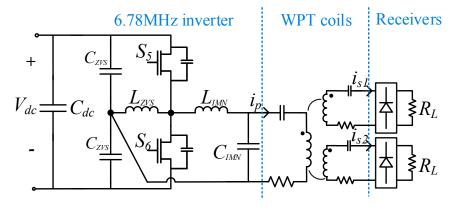

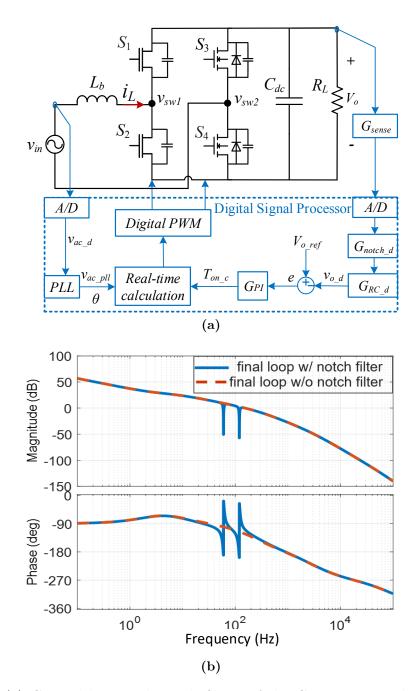

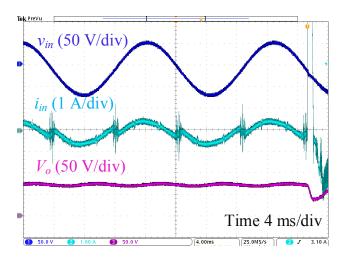

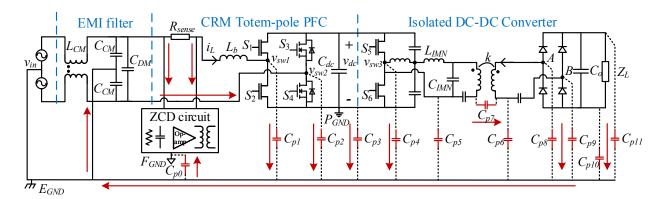

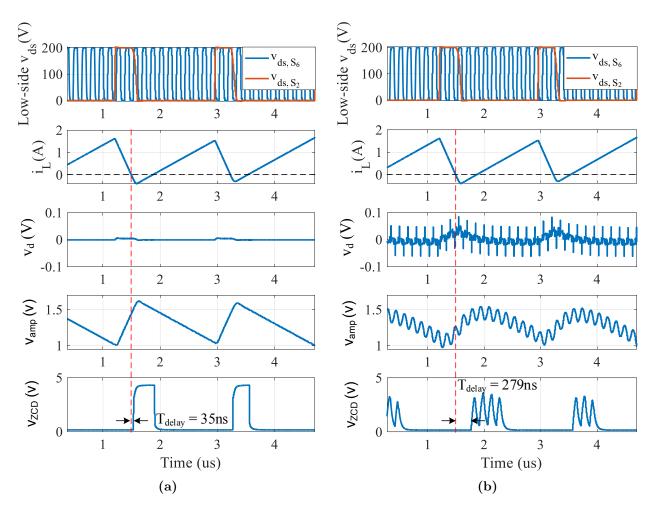

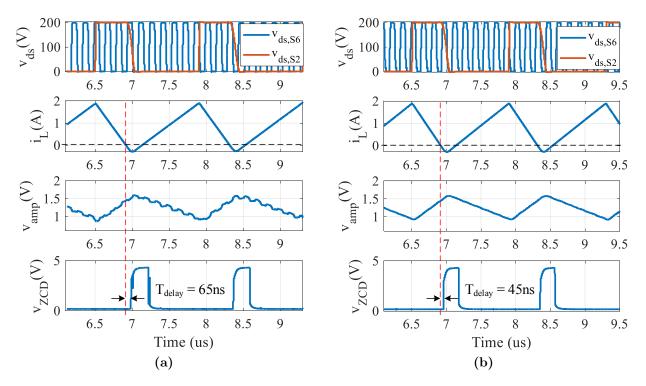

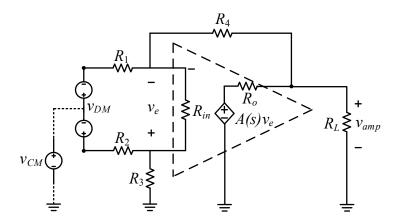

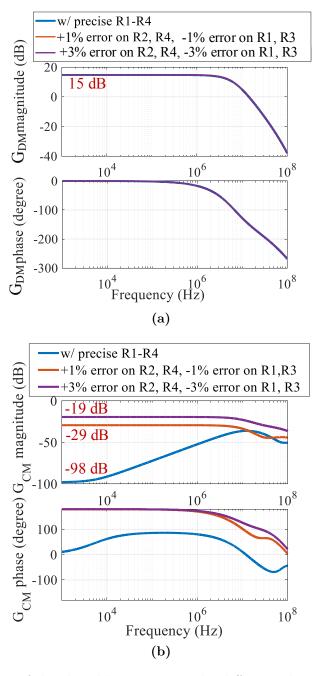

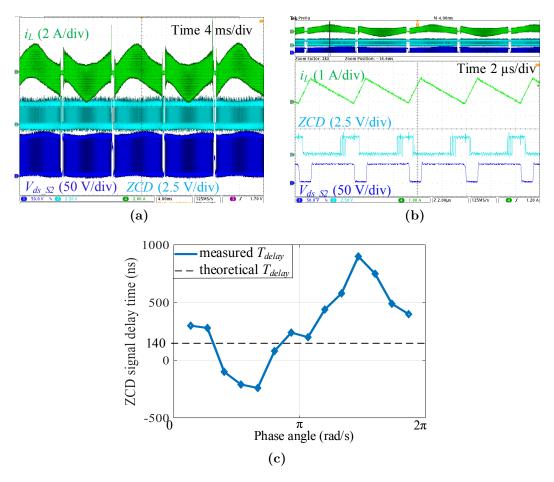

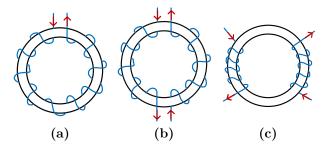

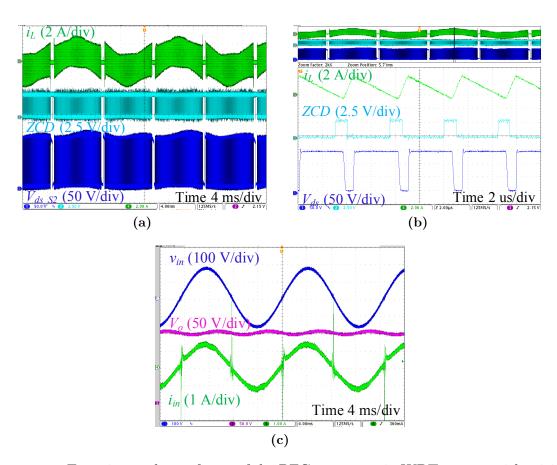

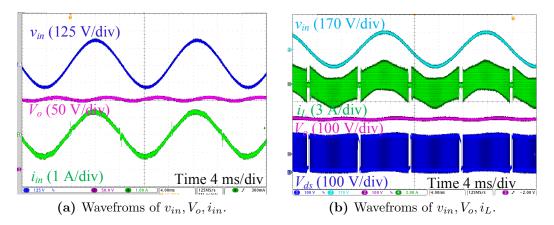

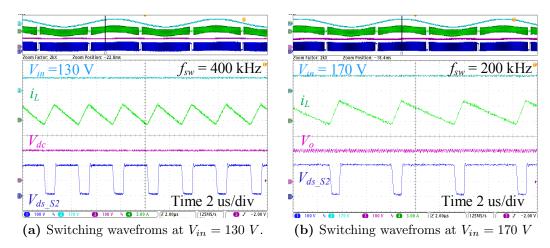

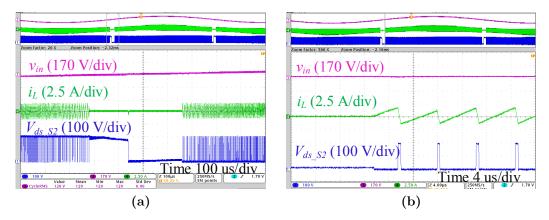

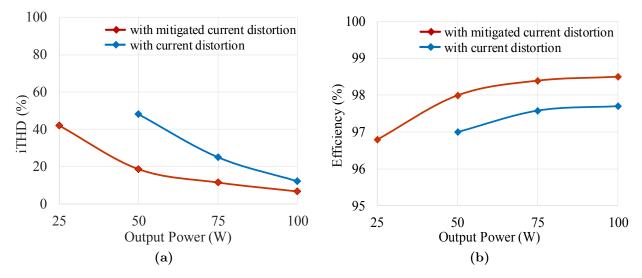

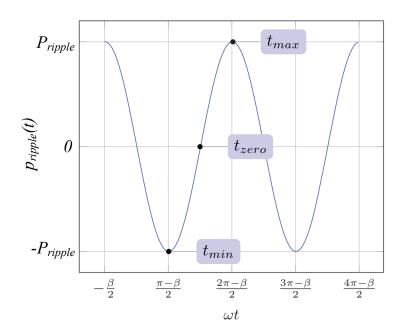

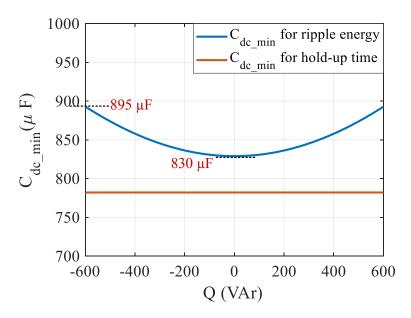

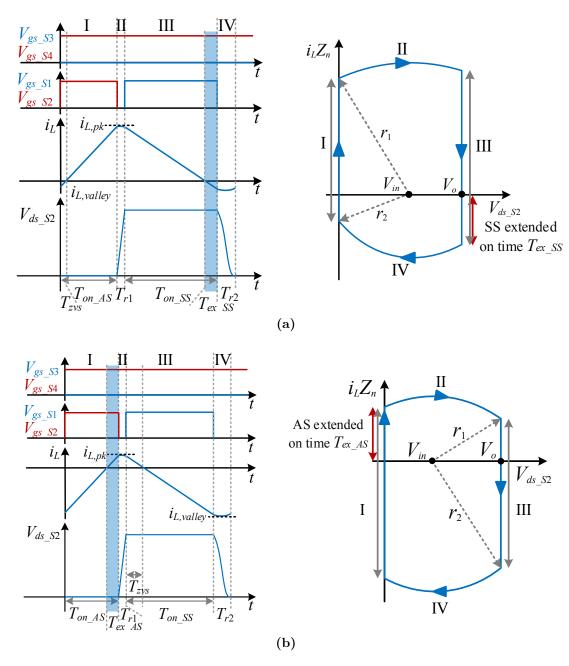

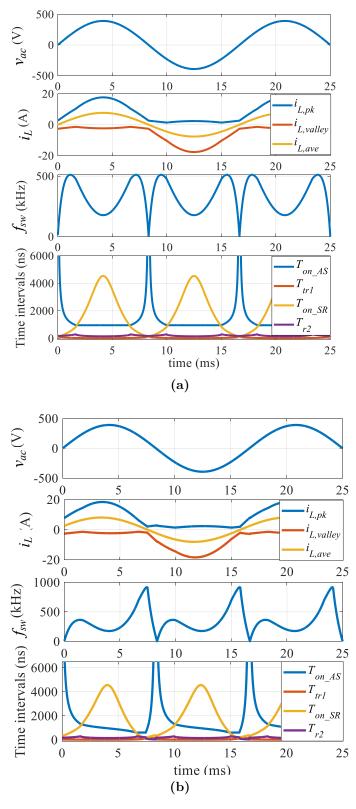

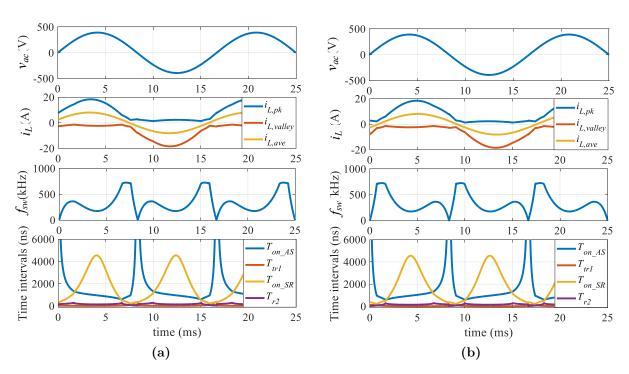

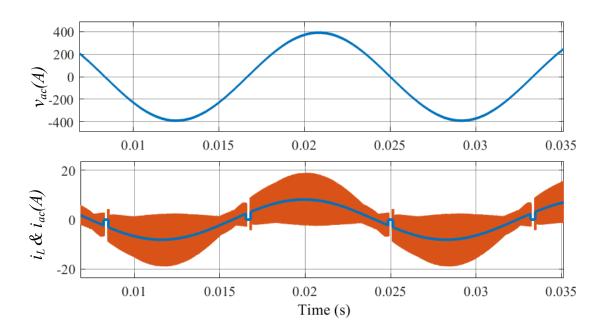

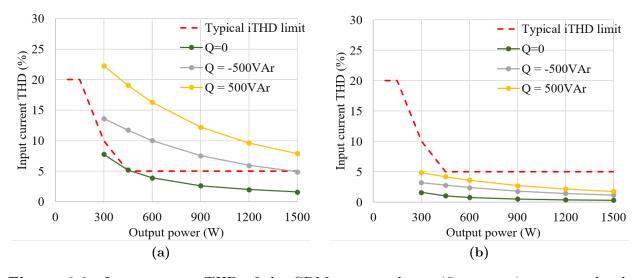

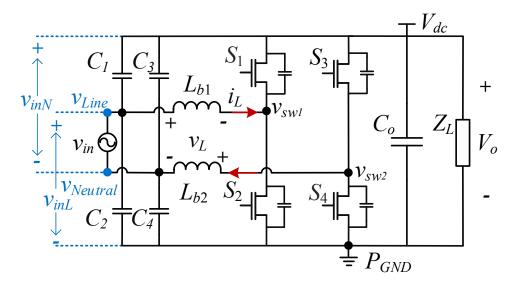

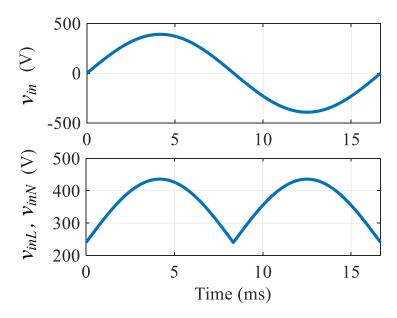

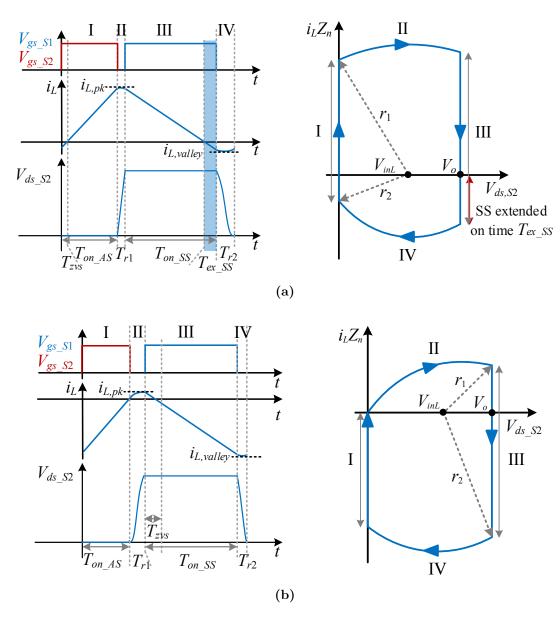

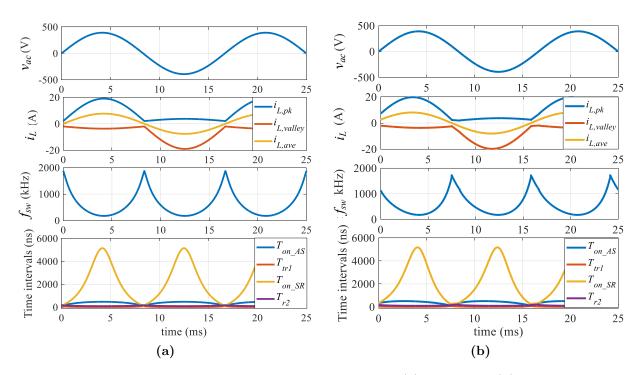

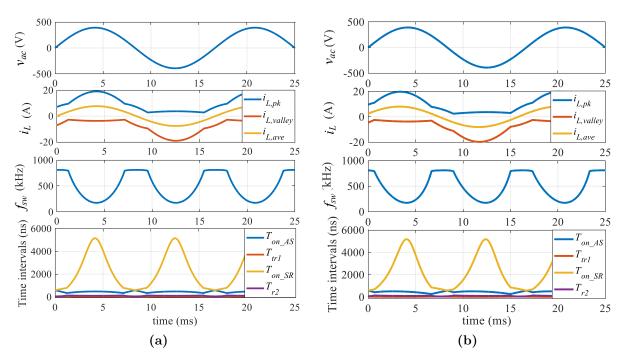

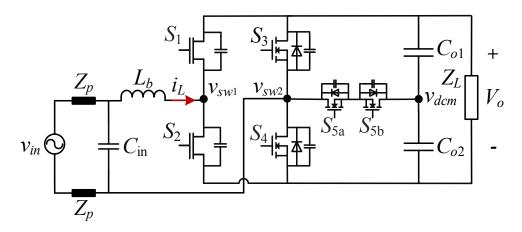

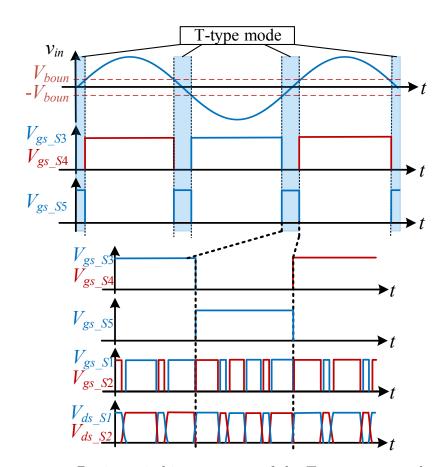

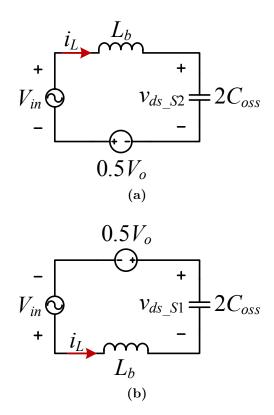

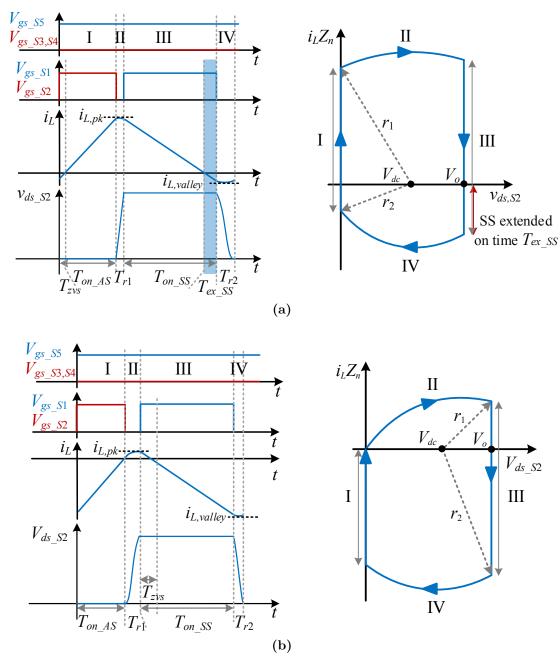

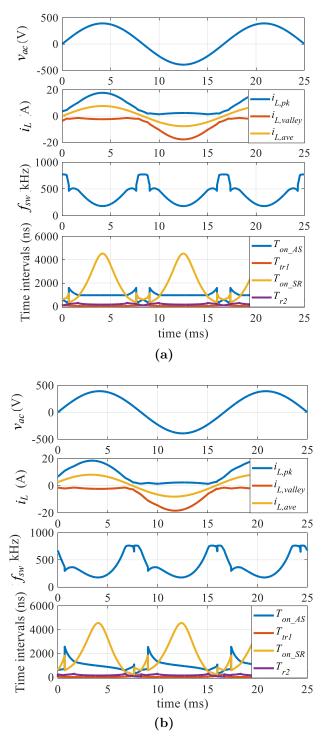

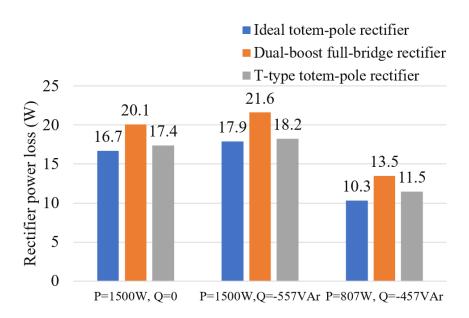

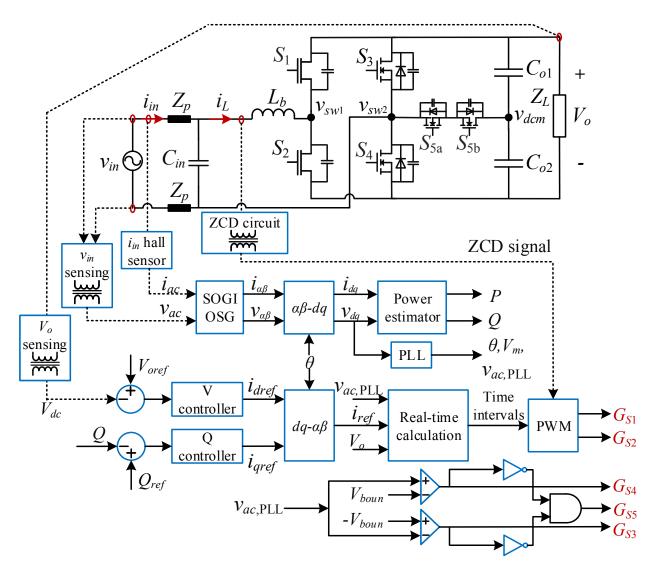

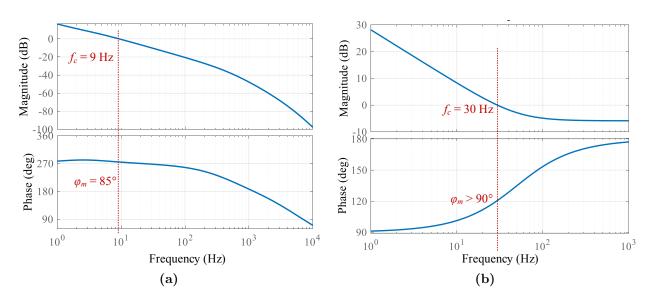

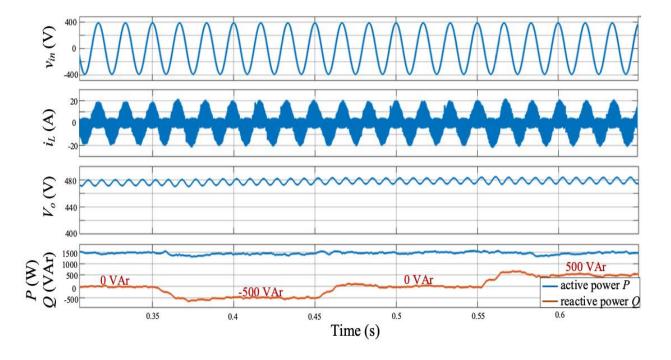

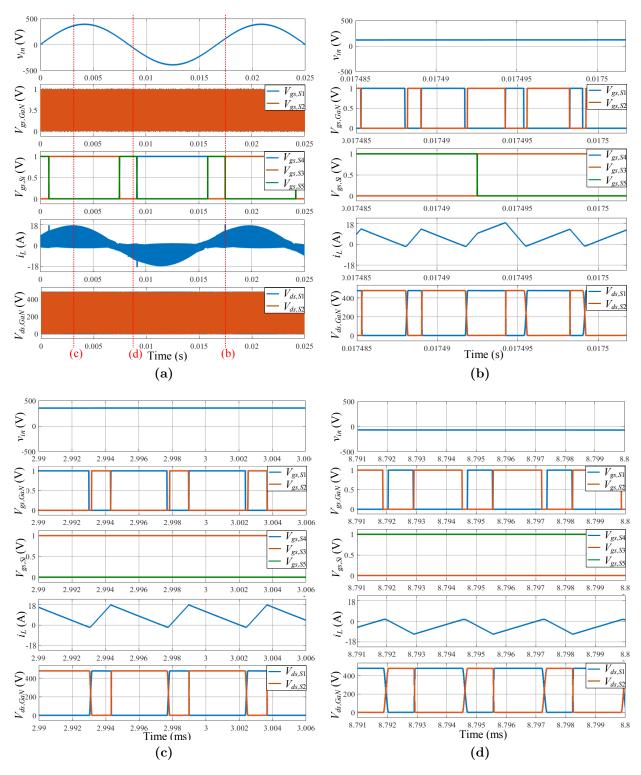

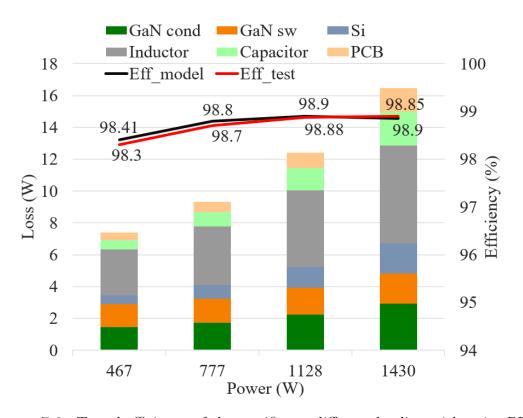

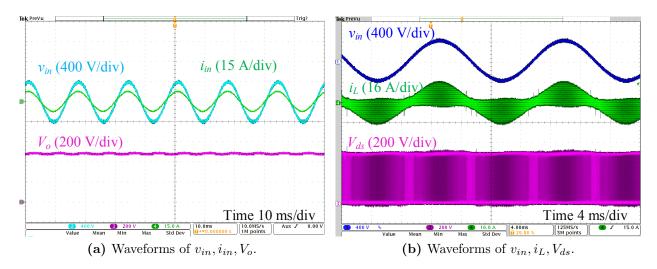

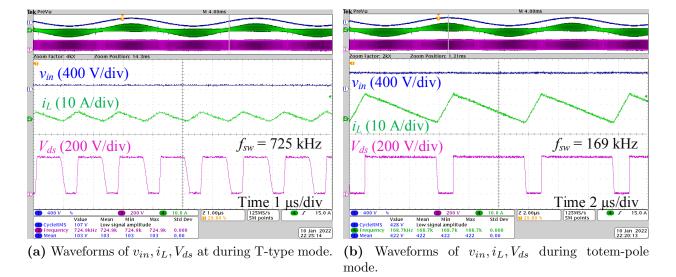

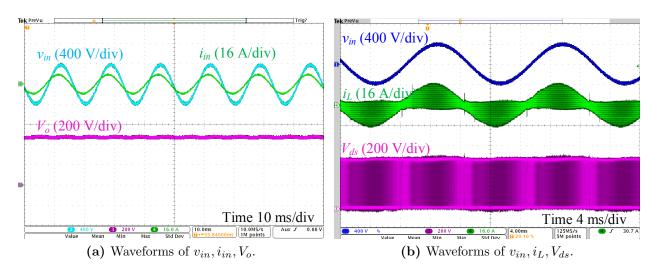

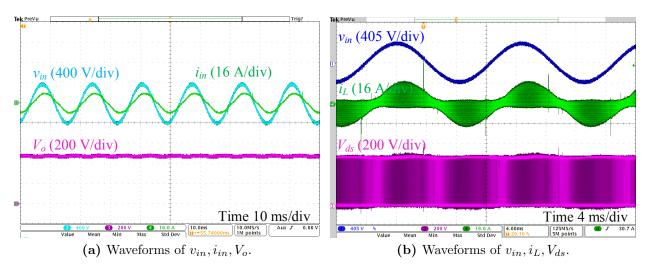

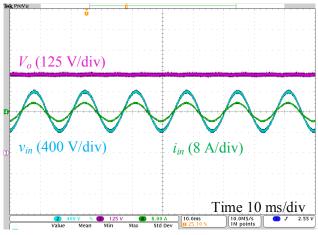

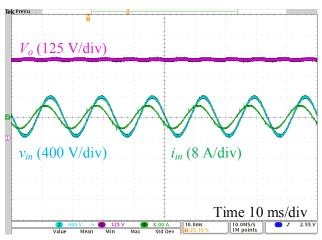

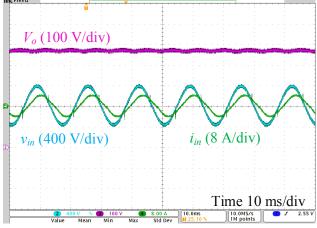

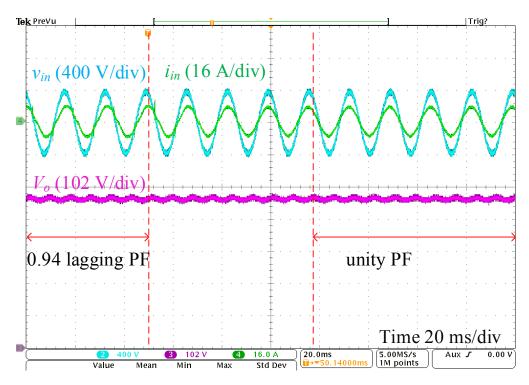

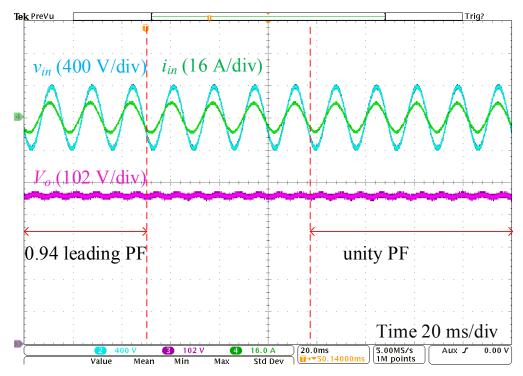

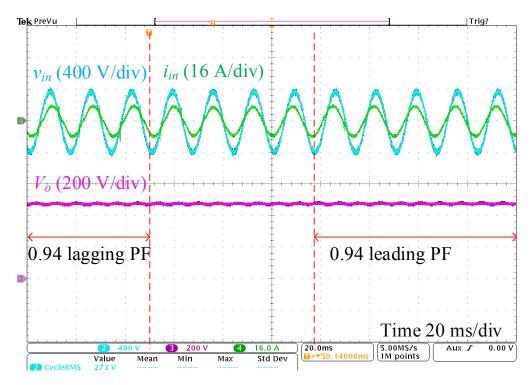

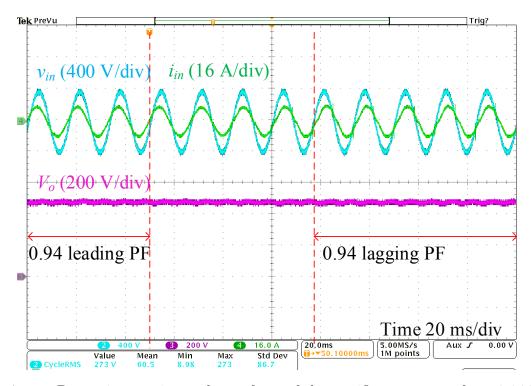

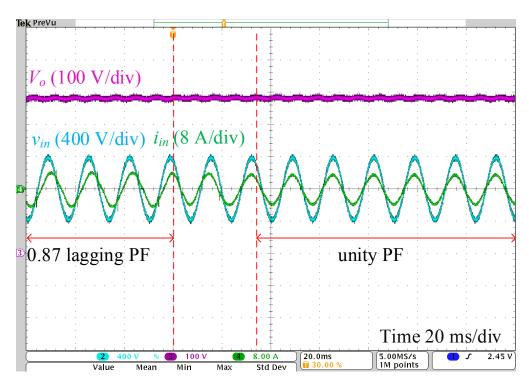

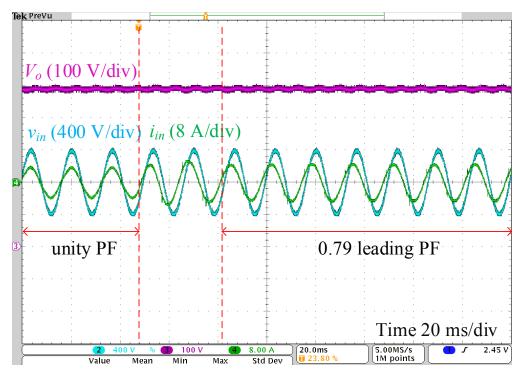

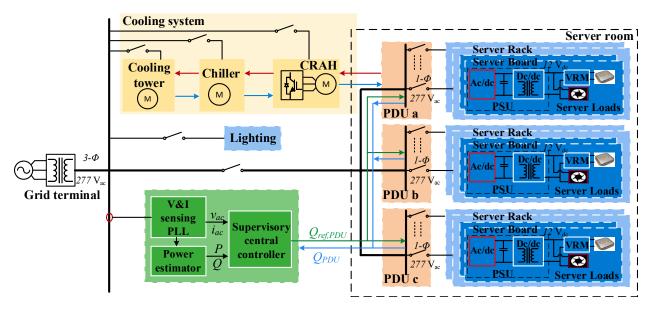

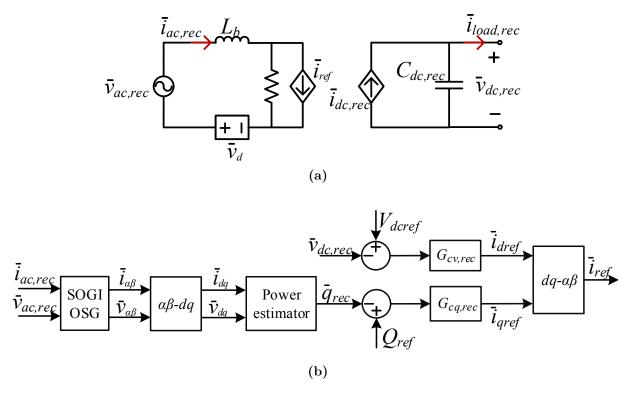

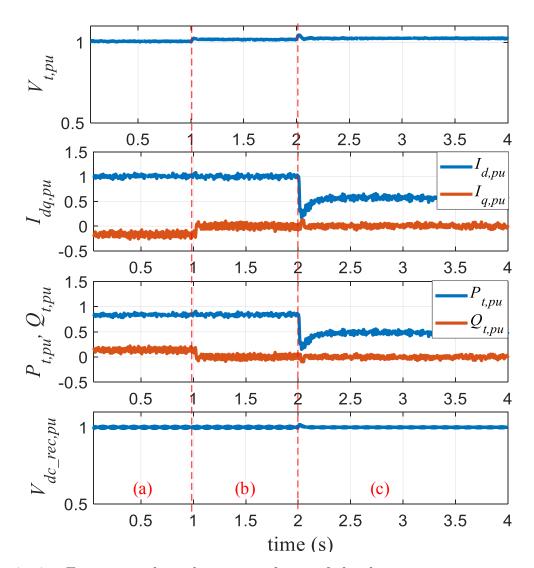

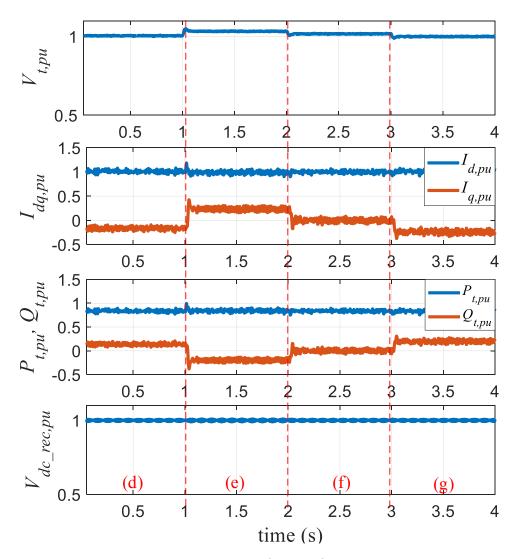

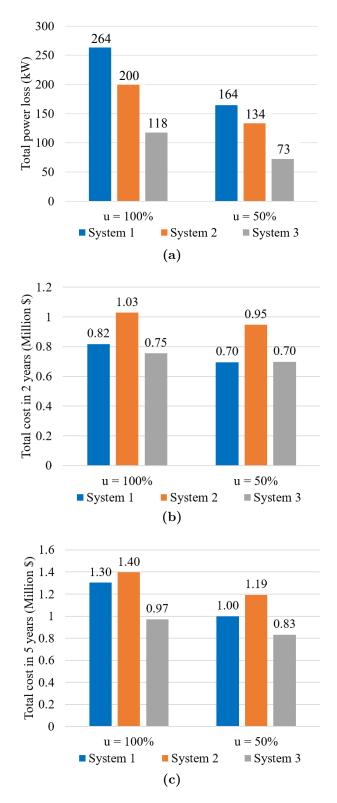

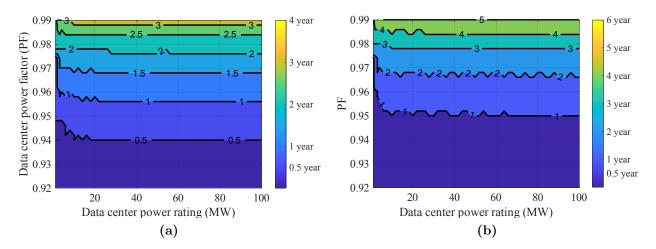

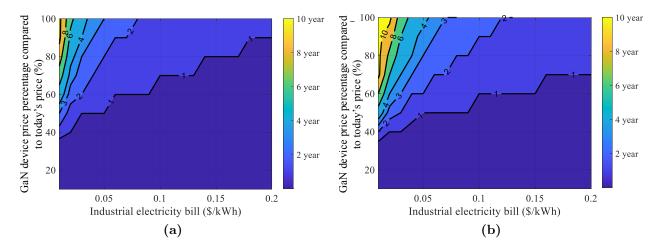

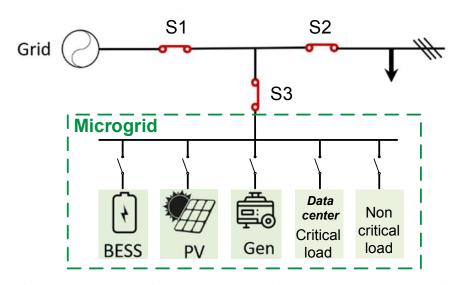

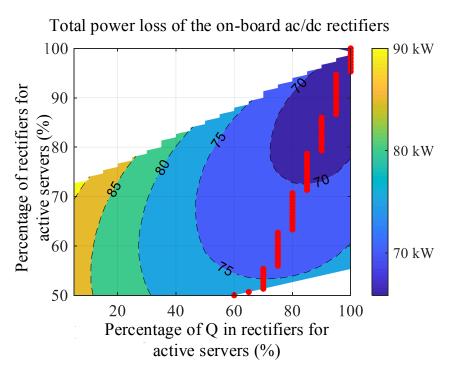

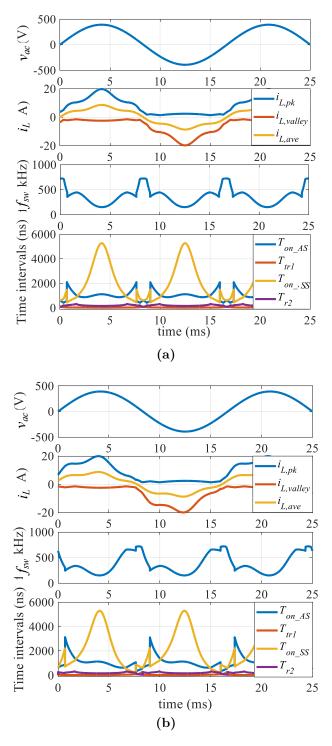

|   |     | 8.2.2     | Data Center Power Management System with Reactive Power Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 255                     |