#### University of Tennessee, Knoxville

# TRACE: Tennessee Research and Creative Exchange

**Doctoral Dissertations**

**Graduate School**

12-2021

# Modeling and Control of a 7-Level Switched Capacitor Rectifier for Wireless Power Transfer Systems

Spencer Cochran *University of Tennessee, Knoxville*, scochra6@vols.utk.edu

Follow this and additional works at: https://trace.tennessee.edu/utk\_graddiss

Part of the Controls and Control Theory Commons, Electrical and Electronics Commons, and the Power and Energy Commons

#### **Recommended Citation**

Cochran, Spencer, "Modeling and Control of a 7-Level Switched Capacitor Rectifier for Wireless Power Transfer Systems." PhD diss., University of Tennessee, 2021. https://trace.tennessee.edu/utk\_graddiss/7057

This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Spencer Cochran entitled "Modeling and Control of a 7-Level Switched Capacitor Rectifier for Wireless Power Transfer Systems." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Daniel J. Costinett, Major Professor

We have read this dissertation and recommend its acceptance:

Leon M. Tolbert, Benjamin J. Blalock, Songnan Yang

Accepted for the Council:

<u>Dixie L. Thompson</u>

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

# Modeling and Control of a 7-Level Switched Capacitor Rectifier for Wireless Power Transfer Systems

A Dissertation Presented for the

Doctor of Philosophy

Degree

The University of Tennessee, Knoxville

Spencer Cochran

December 2021

$\bigodot$  by Spencer Cochran, 2021

All Rights Reserved.

## Acknowledgments

I would like to thank my wife, Blakely, for her unending support during this season of our lives. There is no way I would have completed this race without her. You've sacrificed so much for us, and I just love you, Blake. I would also like to thank Dr. Costinett, whose mentorship has been invaluable over the last few years and has served to shape both the engineer and person I've become. Lastly, I would like to thank my committee: Dr. Tolbert, Dr. Yang, and Dr. Blalock. Without these committee members and the University of Tennessee faculty at large, I would have certainly lacked the guidance to succeed. Their professional expertise and willingness to illuminate the path before me have been essential during my journey in graduate school.

### Abstract

Wireless power continues to increase in popularity for consumer device charging. Rectifier characteristics like efficiency, compactness, impedance tunability, and harmonic content make the multi-level switched capacitor rectifier (MSC) an exceptional candidate for modern WPT systems. The MSC shares the voltage conversion characteristics of a post-rectification buck-boost topology, reduces waveform distortion via its multi-level modulation scheme, demonstrates tank tunability via the phase control inherent to actively switched rectifiers, and accomplishes all this without a bulky filter inductor. In this work, the MSC WPT system operation is explained, and a loss model is constructed. A prototype system is used to validate the models, showing exceptional agreement with the predicted efficiencies. The modeled MSC efficiencies are between 96.1% and 98.0% over the experimental power range up to 20.0 W.

Two significant control loops are required for the MSC to be implemented in a real system. First, the output power is regulated using the modulation of the rectifier's input voltage. Second, the switching frequency of the rectifier must exactly match the WPT carrier frequency set by the inverter on the primary side. Here, a small signal discrete time

model is used to construct four transfer functions relating to the output voltage. Then, four novel time-to-time transfer functions are built on top of the discrete time model to inform the frequency synchronization feedback loop. Both loops are tested and validated in isolation. Finally, the dual-loop control problem is defined, closed form equations that include loop interactions are derived, and stable wide-range dual-loop operation is demonstrated experimentally.

## Table of Contents

| L | Intr               | oduction 1                         |

|---|--------------------|------------------------------------|

|   | 1.1                | Wireless Power                     |

|   | 1.2                | Fundamental Circuit Model          |

|   | 1.3                | The $Qi^{TM}$ Standard             |

|   | 1.4                | Elements of a WPT System           |

|   |                    | 1.4.1 Fundamental Source           |

|   |                    | 1.4.2 WPT Coils                    |

|   |                    | 1.4.3 Tank Tuning                  |

|   |                    | 1.4.4 Rectifier                    |

|   | 1.5                | Practical Rectifier Considerations |

|   |                    | 1.5.1 Compactness                  |

|   |                    | 1.5.2 Harmonic Content             |

|   | 1.6                | Rectifier Metrics                  |

| 2 | ${ m Lit}\epsilon$ | rature Review 31                   |

|   | 2.1                | Diode Rectifiers                   |

|   | 2.2  | Output Regulation                                        | 34  |

|---|------|----------------------------------------------------------|-----|

|   | 2.3  | Diode Emulation Active Rectifiers                        | 37  |

|   | 2.4  | Active Rectifiers                                        | 41  |

|   | 2.5  | Comparison of WPT Rectification Strategies               | 43  |

|   | 2.6  | Control of Active Rectifiers in WPT Systems              | 50  |

|   |      | 2.6.1 Output Regulation                                  | 50  |

|   |      | 2.6.2 Frequency Synchronization                          | 51  |

|   |      | 2.6.3 Dual-Loop Operation and Control Novelty            | 54  |

| 3 | Intr | oduction to the Multi-Level Switched Capacitor Rectifier | 56  |

|   | 3.1  | WPT System and Rectifier Circuit                         | 58  |

|   | 3.2  | Rectifier Loss Mechanisms                                | 64  |

|   |      | 3.2.1 Conduction Loss                                    | 64  |

|   |      | 3.2.2 Switching Loss                                     | 66  |

|   |      | 3.2.3 Charge Sharing Loss                                | 71  |

|   | 3.3  | Stack vs. Queue Modulation                               | 72  |

|   | 3.4  | Impedance Control                                        | 78  |

|   | 3.5  | Switching Limits                                         | 86  |

|   | 3.6  | Fundamental Model vs. Simulation                         | 90  |

| 4 | Stat | te Space Modeling                                        | 96  |

|   | 4.1  | 3-Level, Closed Form                                     | 96  |

|   | 4.2  | 3-Level Circuit Operation                                | 100 |

|   | 4.3  | State Space Representation                  | 103 |

|---|------|---------------------------------------------|-----|

|   | 4.4  | 7-Level, PLECS                              | 106 |

|   | 4.5  | Propagation Through Period and Steady State | 110 |

|   | 4.6  | Example Operating Point                     | 113 |

|   | 4.7  | Additional Implementations                  | 116 |

|   | 4.8  | Model Comparison                            | 117 |

| 5 | Exp  | perimental Platform                         | 123 |

|   | 5.1  | Prototype WPT System                        | 123 |

|   | 5.2  | Experimental Tank Tuning                    | 129 |

|   | 5.3  | Bootstrap Circuit                           | 132 |

|   | 5.4  | Power Stage Layout                          | 136 |

|   | 5.5  | Waveforms                                   | 142 |

|   | 5.6  | Power Sweep - Model Comparison              | 146 |

|   | 5.7  | Component Non-Linearities                   | 149 |

|   | 5.8  | SHE Modulated Experiments                   | 151 |

| 6 | Disc | crete Time Modeling                         | 160 |

|   | 6.1  | Output Transfer Functions                   | 161 |

|   |      | 6.1.1 Example Transfer Function Derivation  | 165 |

|   | 6.2  | Phase Transfer Functions                    | 168 |

|   | 6.3  | MATLAB Implementation                       | 172 |

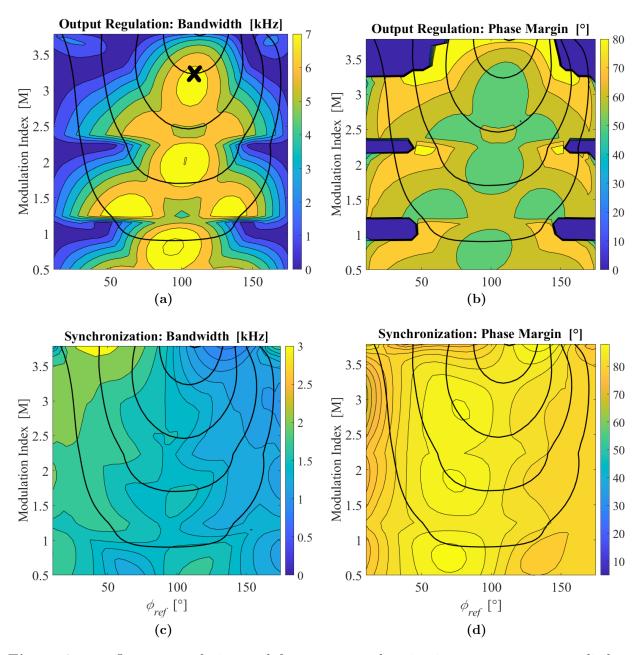

|   | 6.4  | Design of Isolated Control Loops            | 176 |

|   |     | 6.4.1   | Output Voltage Regulation           |   | 179 |

|---|-----|---------|-------------------------------------|---|-----|

|   |     | 6.4.2   | Phase and Frequency Synchronization |   | 182 |

|   | 6.5 | Zero-C  | Crossing Detector                   |   | 185 |

|   |     | 6.5.1   | Prototype Implementation            |   | 185 |

|   |     | 6.5.2   | Small Signal Representation         |   | 188 |

|   | 6.6 | Simula  | ation Platform                      |   | 190 |

|   | 6.7 | Valida  | tion of Isolated Control Loops      |   | 192 |

|   |     | 6.7.1   | Isolated Output Regulation          |   | 193 |

|   |     | 6.7.2   | Isolated Frequency Synchronization  |   | 196 |

| 7 | Dua | al-Loop | o Control                           | : | 202 |

|   | 7.1 | Closed  | l Form Representation               |   | 204 |

|   | 7.2 | Closed  | l Form Equations Applied            |   | 212 |

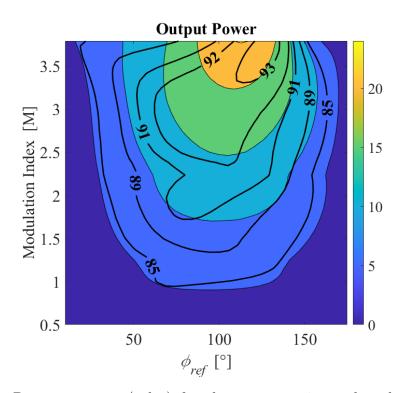

|   | 7.3 | Zero-S  | Slope Power Contours                |   | 221 |

|   | 7.4 | Exper   | imental WPT Tank Retuning           |   | 226 |

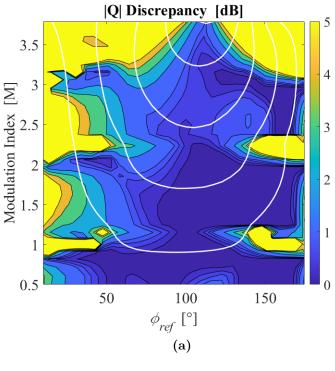

|   | 7.5 | Model   | Deviation and Instability           |   | 229 |

| 8 | WP  | T Sys   | tem Design                          | : | 237 |

|   | 8.1 | Voltag  | ge and Control Optimization         |   | 238 |

|   | 8.2 | Capac   | itance and Footprint Area           |   | 243 |

|   | 8.3 | Capac   | itance and System Efficiency        |   | 244 |

|   | 8.4 | Modul   | lation                              |   | 247 |

|   |     | 8 4 1   | Low THD Modulation                  |   | 248 |

|                           |        | 8.4.2  | Gap Modulation         | 252 |

|---------------------------|--------|--------|------------------------|-----|

|                           |        | 8.4.3  | Parasitics             | 258 |

|                           |        | 8.4.4  | 100 kHz Gap Modulation | 260 |

| 9                         | Fut    | ure Wo | ork: Integration       | 264 |

|                           | 9.1    | Conclu | asions                 | 265 |

| Bi                        | ibliog | graphy |                        | 267 |

| $\mathbf{V}_{\mathbf{i}}$ | ita    |        |                        | 288 |

## List of Tables

| 1.1 | WPT Standards Comparison [1, 2]                                               | 3   |

|-----|-------------------------------------------------------------------------------|-----|

| 1.2 | Operating Point Used to Exemplify Design Space                                | 9   |

| 2.1 | Theoretical Rectifier Impedances                                              | 44  |

| 2.2 | Example Tank Values                                                           | 44  |

| 2.3 | Comparison of Rectification Strategies                                        | 49  |

| 3.1 | Losses Contributed by Low (LS) and High Side (HS) Switches Based on Fig. 3.6  | 69  |

| 3.2 | Summary of Fundamental Rectifier Loss Mechanisms                              | 73  |

| 3.3 | Stack vs. Queue Example Comparison                                            | 77  |

| 3.4 | Fundamental Model vs. LTspice Simulation                                      | 95  |

| 4.1 | 3-Level Circuit Interval Actuation                                            | 101 |

| 4.2 | Example State Space Operating Point                                           | 114 |

| 4.3 | Models Compared with Simulation                                               | .20 |

| 4.4 | Comparison of the Fundamental Harmonic Analysis (FHA) and State Space         |     |

|     | Modeling Approaches for the 7-Level Switched Capacitor Rectifier WPT System 1 | .22 |

| 5.1 | System Specifications of Proposed MSC Rectifier                    | 124 |

|-----|--------------------------------------------------------------------|-----|

| 5.2 | Equivalent Tuned Tank Impedance Comparison with $v_{rec}=0$        | 128 |

| 5.3 | Properties of the Experimental Setup                               | 128 |

| 5.4 | Waveform Distortion in Fig. 5.10                                   | 145 |

| 5.5 | Harmonic ESR Values                                                | 150 |

| 5.6 | Waveform Distortion in Fig. 5.10                                   | 155 |

| 6.1 | Final Small Signal Plant Model Transfer Functions                  | 173 |

| 6.2 | Values of Sensing Circuit                                          | 186 |

| 6.3 | Operating Point Used to Validate Isolated Loop Designs             | 194 |

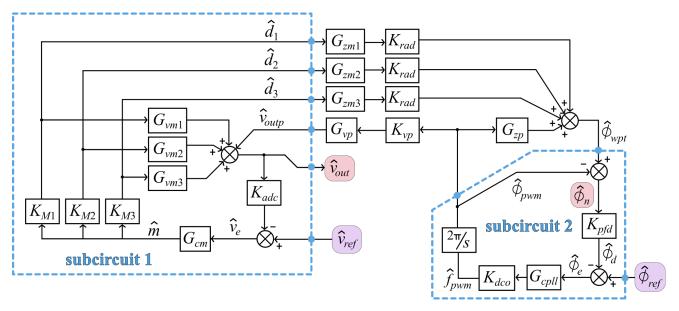

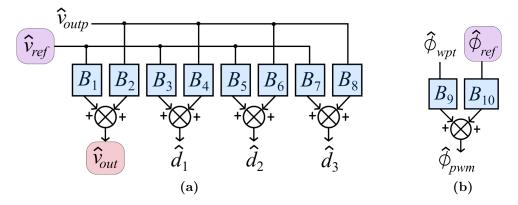

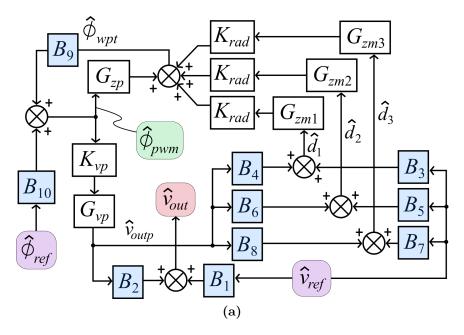

| 7.1 | Subcircuit Equations and Block Diagram Coefficients                | 209 |

| 7.2 | Complete Small Signal Model                                        | 211 |

| 7.3 | Operating Point used to Examine the Closed Form Small Signal Model | 211 |

| 7.4 | New WPT Tank Values                                                | 228 |

| 8.1 | Optimization Capacitance and ESR Values                            | 246 |

# List of Figures

| 1.1 | General form of a WPT system, showing power commutation from $V_{in}$ ,               |    |

|-----|---------------------------------------------------------------------------------------|----|

|     | through $L_{tx}$ and $L_{rx}$ , and to $R_{rec,1}$                                    | 3  |

| 1.2 | Equivalent WPT tank models: (a) $k$ model and (b) T model                             | 5  |

| 1.3 | Efficiency of the WPT system given coupling values of (a) $k = 0.3$ , (b) $k = 0.6$ , |    |

|     | and (c) $k = 0.9$ . The optimal load is shown as a black $x$ , and the optimal        |    |

|     | resistance (Im( $Z_{rec,opt}$ ) = 0) is shown as a black circle (o)                   | 9  |

| 1.4 | Cartesian and polar descriptions of the optimal load $(Z_{rec,opt})$ for different    |    |

|     | values of $k$ using the tank in Table 1.2                                             | 10 |

| 1.5 | Implementation of the (a) fundamental source via a (b) full-bridge [3], (c)           |    |

|     | half-bridge [4], or (d) class-E inverter [5, 6]. Here, $v_p$ is the fundamental       |    |

|     | component of $v_{inv}$                                                                | 15 |

| 1.6 | The WPT coils and their parasitic components as shown in the fundamental              |    |

|     | circuit model                                                                         | 18 |

| 1.7  | The four basic types of WPT compensation: (a) series-series (SS) as snown in                |    |

|------|---------------------------------------------------------------------------------------------|----|

|      | the fundamental model, (b) series-parallel (SP), (c) parallel-series (PS), and              |    |

|      | (d) parallel-parallel (PP)                                                                  | 21 |

| 1.8  | The rectifier is depicted as a load in the fundamental circuit model                        | 23 |

| 1.9  | iPhone 12 (a) breakdown, (b) circuit board, and (c) wireless charging coil [7].             | 25 |

| 1.10 | The quality factor of WPT coil part number 760308101141 verses frequency [8]                | 28 |

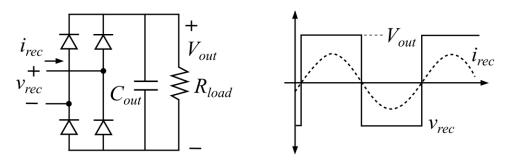

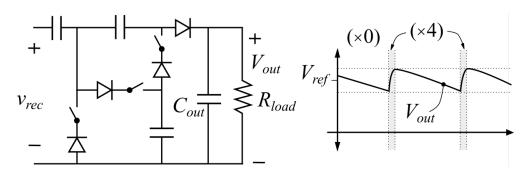

| 2.1  | A diode full bridge rectifier and waveforms [9–11]                                          | 33 |

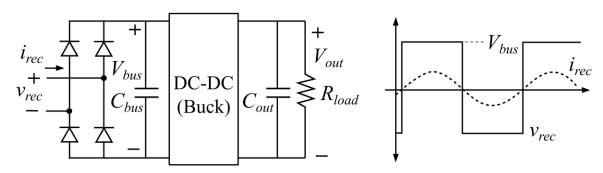

| 2.2  | A diode full bridge rectifier with a DC-DC converter and the accompanying                   |    |

|      | waveforms [12, 13]                                                                          | 36 |

| 2.3  | Resonant regulating rectifier based on a voltage quadrupler that regulates the              |    |

|      | output voltage via simple comparison with a reference value [14]                            | 38 |

| 2.4  | Actively switching rectifier doing diode emulation. A small switching delay                 |    |

|      | results in reverse leakage loss [15–18]                                                     | 40 |

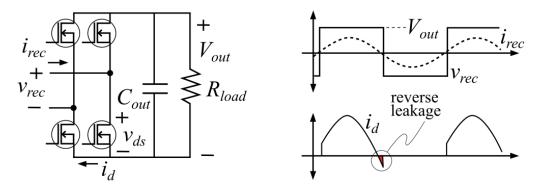

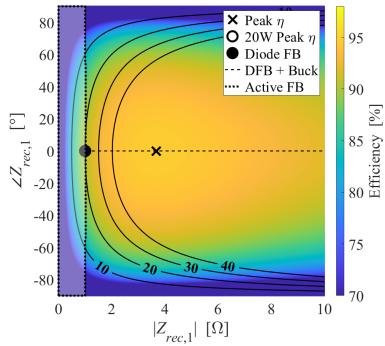

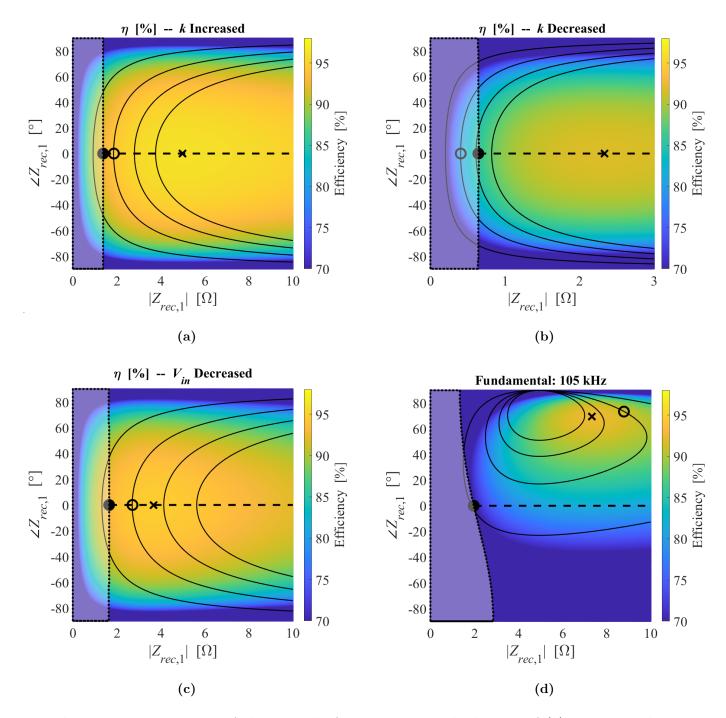

| 2.5  | Example operating point for reference. Both sides of the WPT tank are tuned                 |    |

|      | for resonance, $k = 0.55$ , and $V_{in} = 26 \text{ V} \dots \dots \dots \dots \dots \dots$ | 44 |

| 2.6  | Variations of the example from Fig. 2.5 with changes of (a) increasing $k$ to               |    |

|      | 0.75, (b) decreasing $k$ to 0.35, (c) lowering $V_{in}$ to 16 V, and (d) reducing the       |    |

|      | fundamental frequency to 105 kHz                                                            | 46 |

| 2.7  | A single controller driving both sides of a WPT system                                      | 52 |

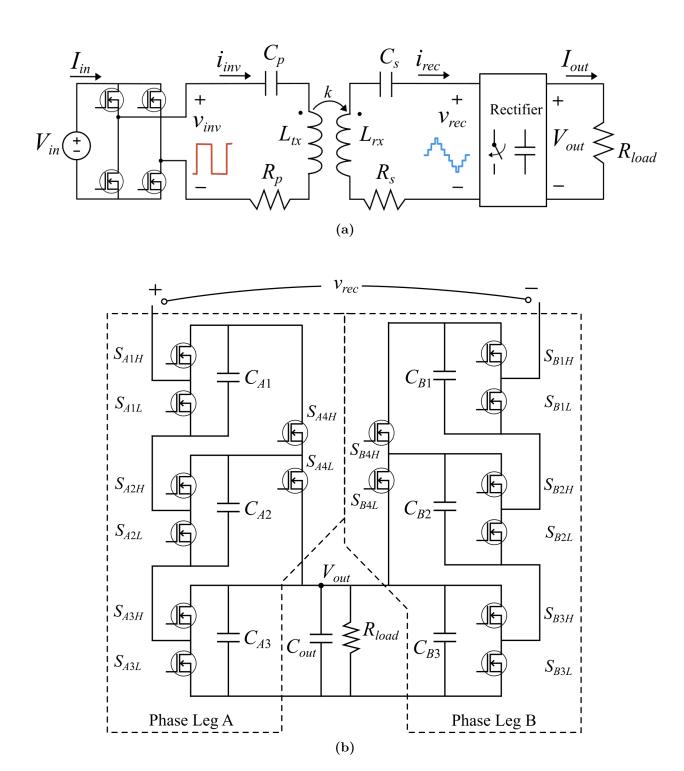

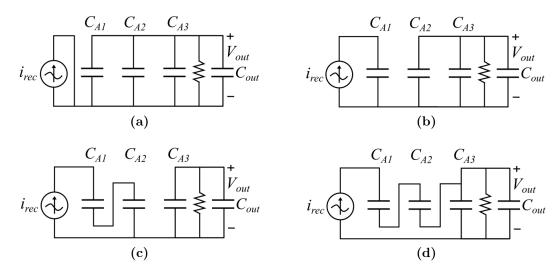

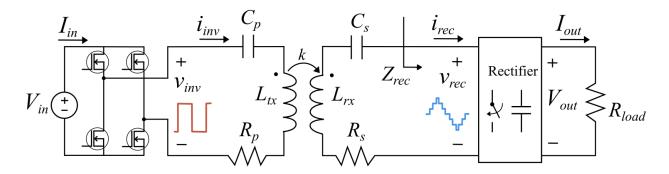

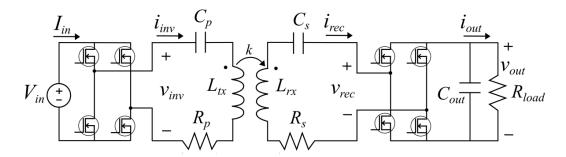

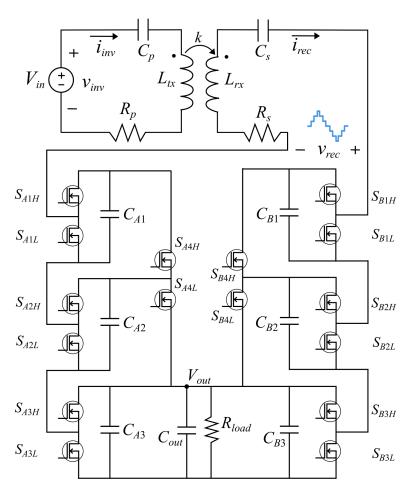

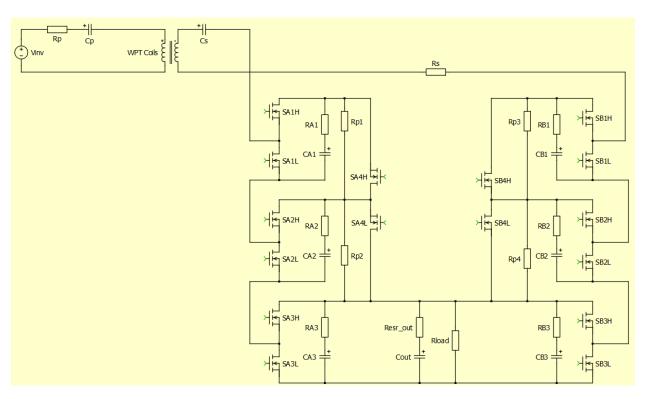

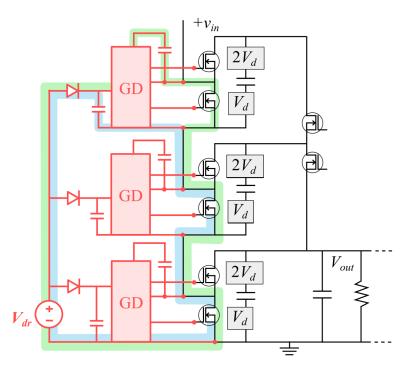

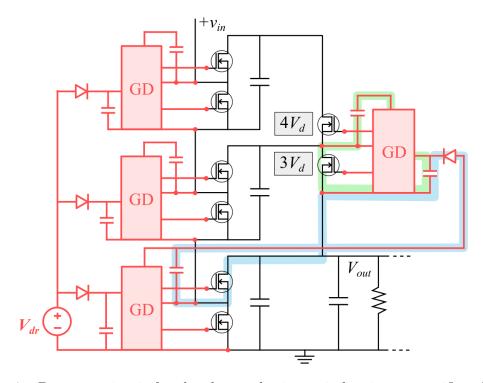

| 3.1  | (a) The complete WPT system and (b) the proposed 7-level rectifier topology.                | 57 |

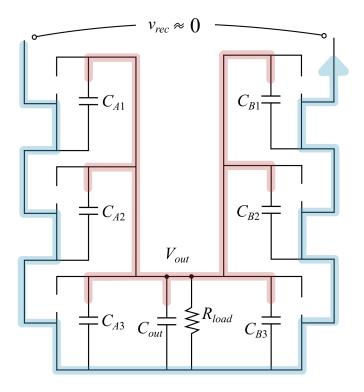

| 3.2  | Example configuration illustrating all capacitors balancing and $v_{rec} = 0$               | 59 |

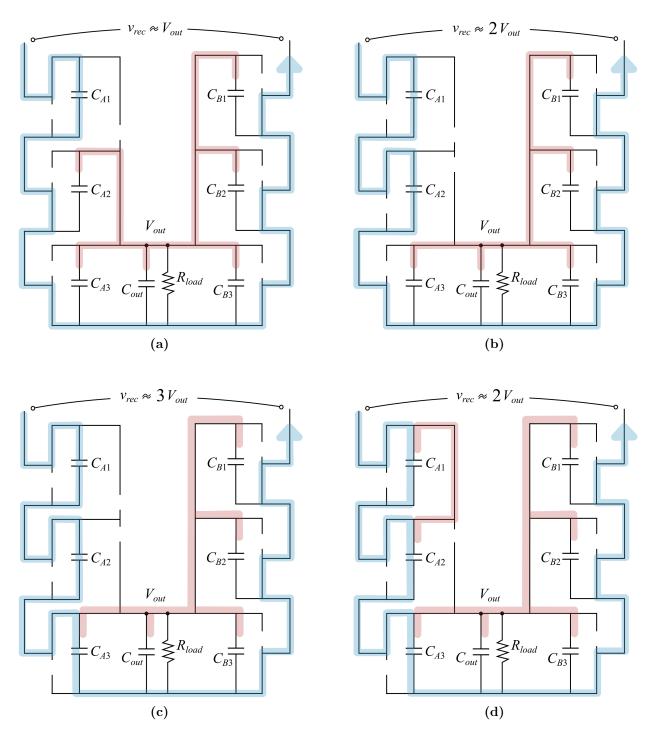

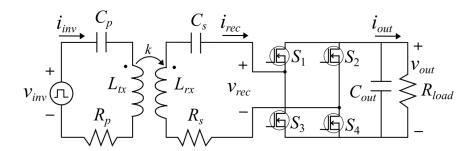

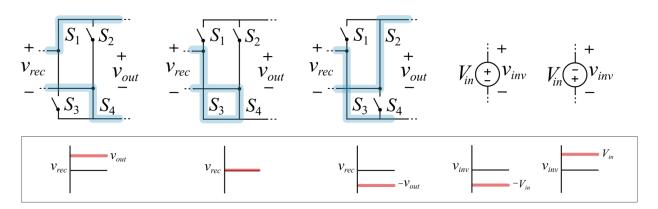

| 3.3  | Example configurations of the 7-level switched capacitor rectifier, showing (a)                                                  |    |

|------|----------------------------------------------------------------------------------------------------------------------------------|----|

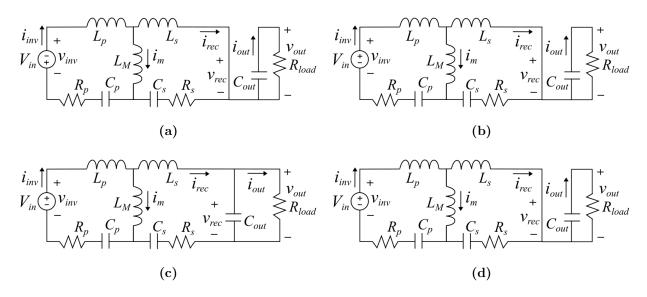

|      | $v_{rec} = 0$ , (b) $v_{rec} = V_{out}$ , (c) $v_{rec} = 2V_{out}$ , and (d) $v_{rec} = 3V_{out}$                                | 60 |

| 3.4  | Example configurations of the 7-level switched capacitor rectifier, showing (a)                                                  |    |

|      | $v_{rec} \approx V_{out}$ , (b) $v_{rec} \approx 2V_{out}$ , (c) $v_{rec} \approx 3V_{out}$ , and (d) $v_{rec} \approx 2V_{out}$ | 63 |

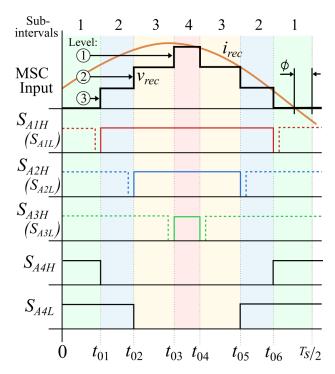

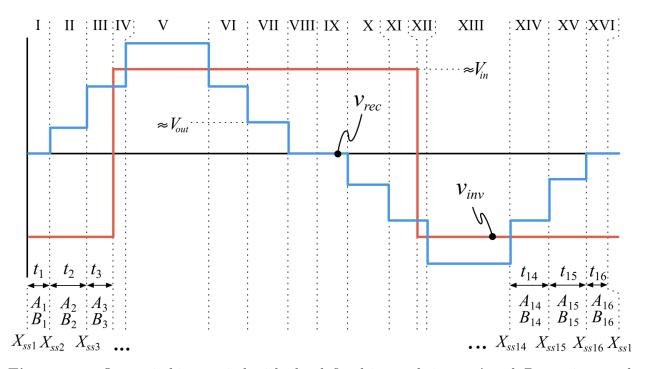

| 3.5  | Basic stack control signal sequence for 7-level SC rectifier in one half-period.                                                 |    |

|      | For each gate signal: Solid line: high side switches and charge sharing switches                                                 |    |

|      | $(S_{A1H}, S_{A2H}, S_{A3H}, S_{A4H}, S_{A4L})$ ; dashed line: low side switches $(S_{A1L}, S_{A2L}, S_{A2L}, S_{A2L})$          |    |

|      | $S_{A3L}$ )                                                                                                                      | 63 |

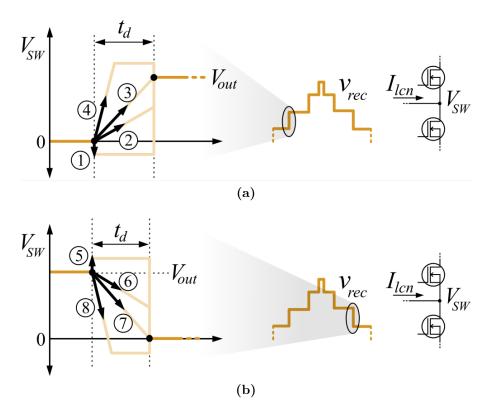

| 3.6  | Linearized dead time for (a) positive level changes and (b) negative level                                                       |    |

|      | changes showing the potential $V_{sw}$ translation cases dependent on $I_{lcn}$                                                  | 68 |

| 3.7  | Charge sharing loss equivalent circuits in MSC rectifier: capacitor to capacitor.                                                | 73 |

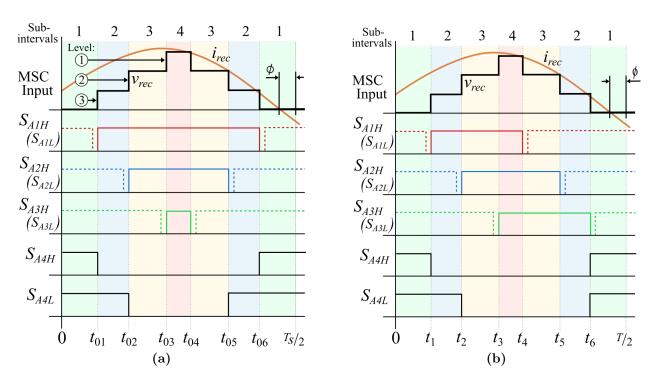

| 3.8  | Two basic control strategies: (a) LIFO, stack modulation and (b) FIFO, queue                                                     |    |

|      | modulation                                                                                                                       | 74 |

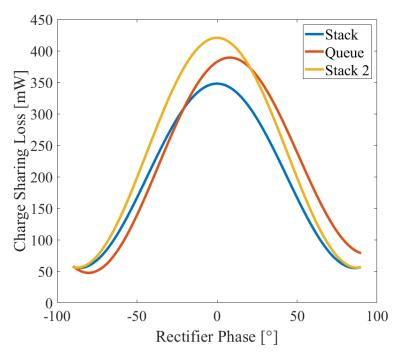

| 3.9  | Half-cycle charge sharing loss as a function of rectifier phase for the stack and                                                |    |

|      | queue modulation strategies. 'Stack 2' results in the same waveform shape,                                                       |    |

|      | but level 1 is on for the longest duration $(t_{01}-t_{06})$ with level 3 on for the                                             |    |

|      | shortest duration $(t_{03}-t_{04})$                                                                                              | 79 |

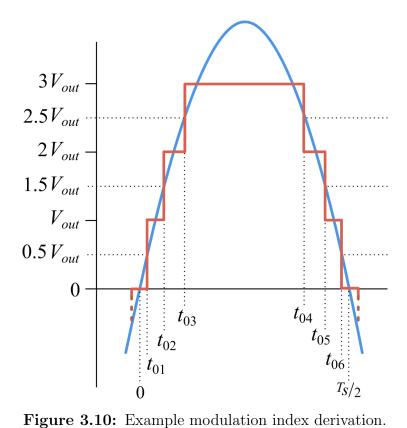

| 3.10 | Example modulation index derivation                                                                                              | 81 |

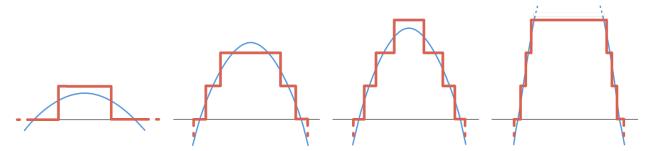

| 3.11 | Illustration of the modulation index range and the underlying sinusoid used                                                      |    |

|      | to generate each modulation index                                                                                                | 82 |

| 3.12 | WPT system showing the rectifier input impedance, $Z_{rec}$                                                                      | 84 |

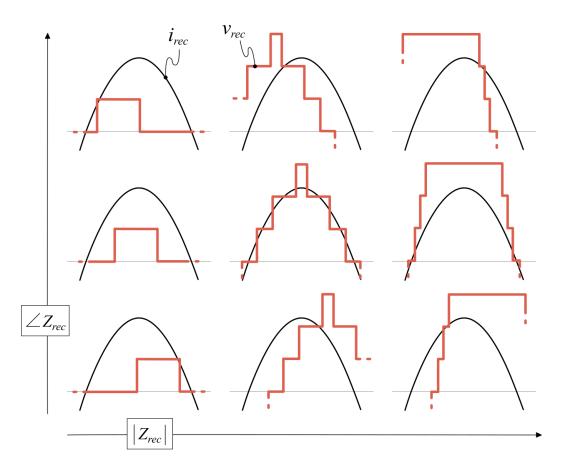

| 3.13 | Example rectifier input impedances. $Z_{rec}$ magnitude increases left to right     |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | with modulation index, and $Z_{rec}$ phase angle increases top to bottom with       |     |

|      | switching time                                                                      | 84  |

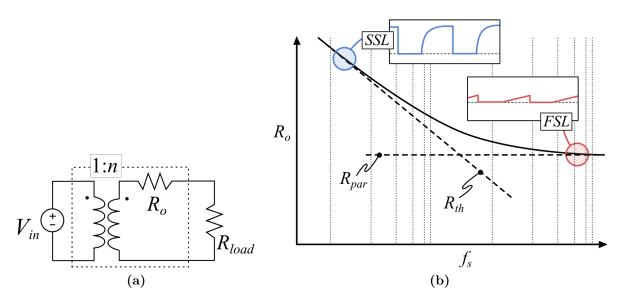

| 3.14 | The (a) idealized switched capacitor converter model and the (b) frequency          |     |

|      | dependence of $R_o$ showing the fast and slow switching limits. Both figures are    |     |

|      | adapted from [19]                                                                   | 88  |

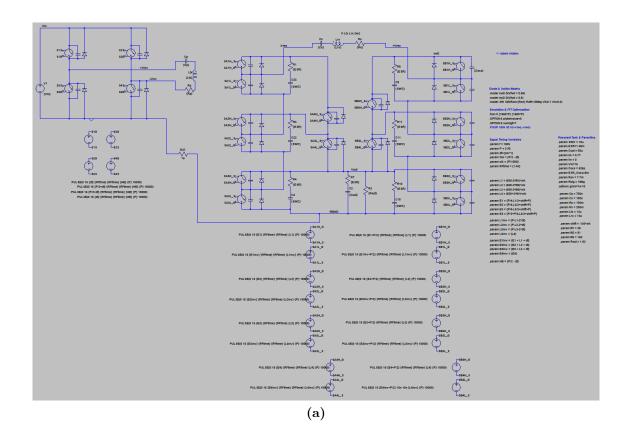

| 3.15 | LT<br>spice simulation of the 7-level switched capacitor WPT system.<br>            | 91  |

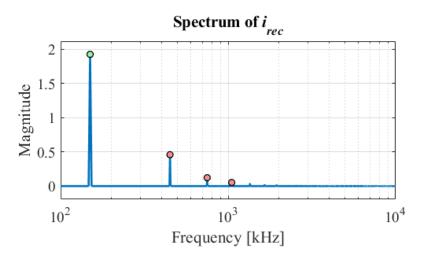

| 3.16 | Spectrum of $i_{rec}$ from the LTspice simulation                                   | 94  |

| 4.1  | Example WPT system with a 3-level (full-bridge) rectifier                           | 98  |

| 4.2  | Equivalent circuit used to model the WPT system with a 3-level rectifier            | 98  |

| 4.3  | Every possible input $(v_{inv})$ and rectifier switch combination $v_{rec}$         | 99  |

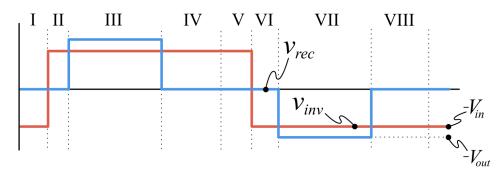

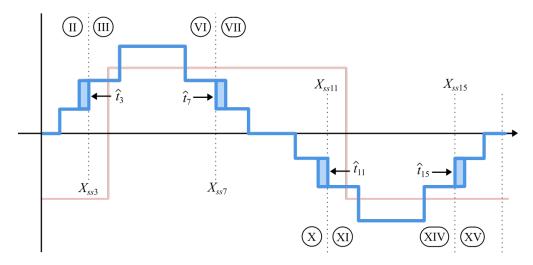

| 4.4  | One period of $v_{inv}$ and $v_{rec}$ waveforms                                     | 101 |

| 4.5  | Equivalent circuits of intervals (a) I, (b) II, (c) III, and (d) IV as described in |     |

|      | Fig. 4.4 and Table 4.1                                                              | 101 |

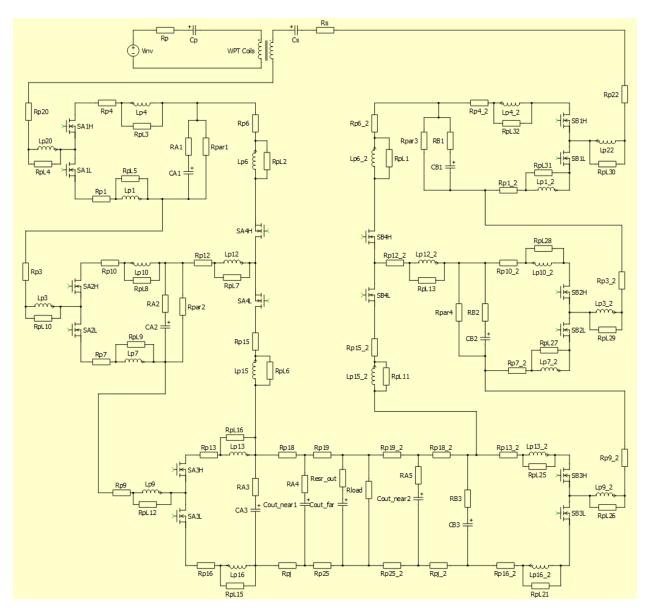

| 4.6  | The proposed circuit as it is modeled in state space                                | 107 |

| 4.7  | Layout of the proposed circuit in PLECS software                                    | 109 |

| 4.8  | One switching period with the defined interval times, $A$ and $B$ matrices, and     |     |

|      | steady state $x(t)$ values                                                          | 114 |

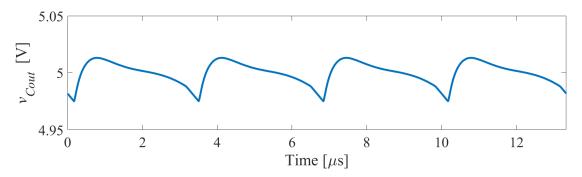

| 4.9  | Voltage on capacitor $C_{out}$ in state space model                                 | 115 |

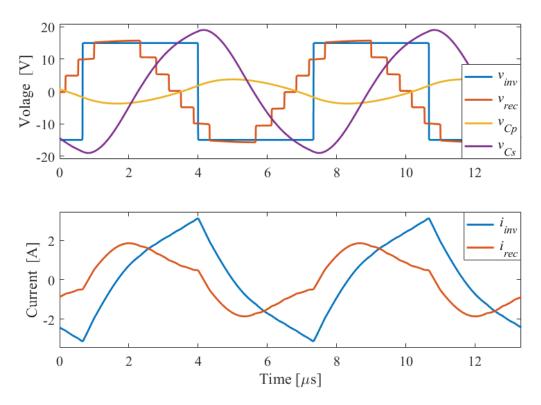

| 4.10 | Waveforms of the state space model for the 7-level WPT system using the             |     |

|      | example operating point outlined in Table 4.2                                       | 115 |

| 4.11 | PLECS circuit layout including parasitic resistance and inductance                  | 118 |

|------|-------------------------------------------------------------------------------------|-----|

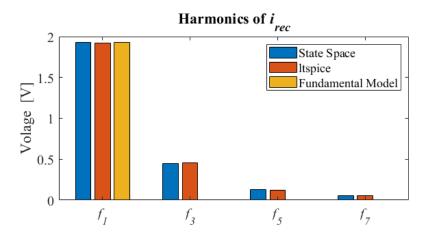

| 4.12 | Harmonic content of $i_{rec}$ for the fundamental model, state space model, and     |     |

|      | ltspice simulation                                                                  | 120 |

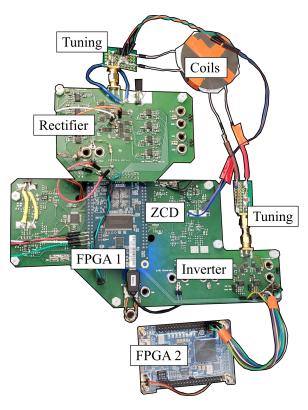

| 5.1  | Experimental setup showing the FPGA controller, inverter, tuned WPT tank,           |     |

|      | and rectifier                                                                       | 124 |

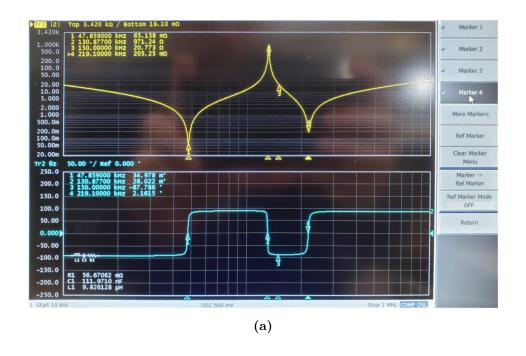

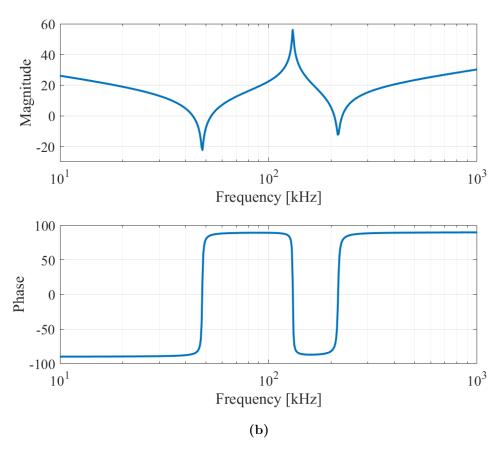

| 5.2  | The tuned tank impedance as (a) measured by the impedance analyzer and              |     |

|      | (b) calculated with the fundamental circuit                                         | 127 |

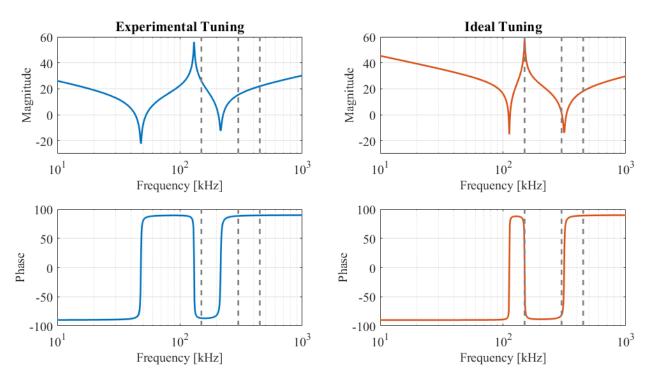

| 5.3  | The impedance presented to the inverter with $Z_{rec} = 0$ , including lines for    |     |

|      | the fundamental (150 kHz), second harmonic (300 kHz), and third harmonic            |     |

|      | (450 kHz). Both the experimental tuning (as implemented in the prototype)           |     |

|      | and the tuning that cancels the reactive component are shown                        | 130 |

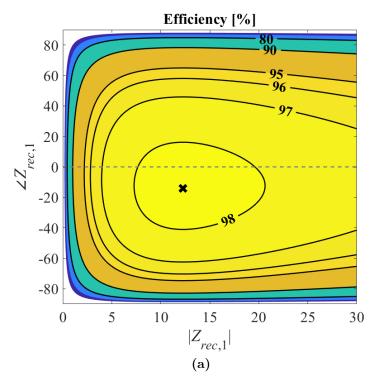

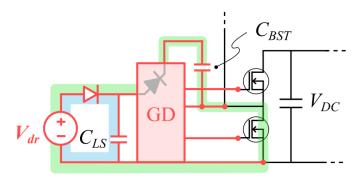

| 5.4  | The tank tuning of the experimental setup showing both (a) efficiency and           |     |

|      | (b) output power given the values in Table 5.3. The black $x$ is the optimal        |     |

|      | efficiency point considering only tank conduction loss                              | 131 |

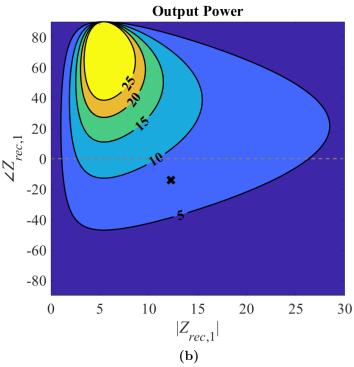

| 5.5  | Basic boostrap circuit structure using a half-bridge gate driver module. The        |     |

|      | blue and green charging paths show how $C_{LS}$ and $C_{BST}$ charge, respectively. | 133 |

| 5.6  | Boostrap circuit for the power switches in one rectifier phase leg. The charging    |     |

|      | paths of the highest level are shown by the blue and green lines                    | 135 |

| 5.7  | Boostrap circuit for the charge sharing switches in one rectifier phase leg         | 135 |

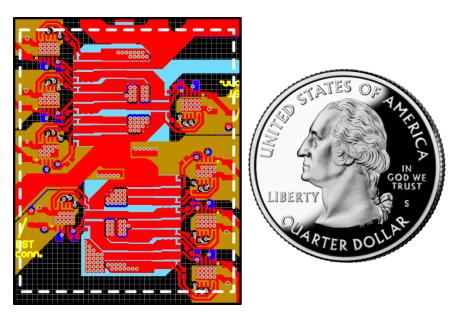

| 5.8  | The PCB layout of the rectifier power stage with a US quarter for size              |     |

|      | reference. The white dotted line measures 31.4 mm x 27.5 mm                         | 138 |

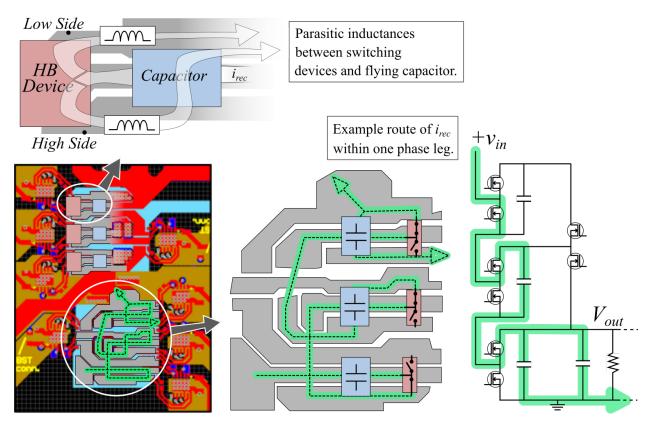

| 5.9  | Example showing the characteristics of the power stage layout. The parasitic                                                                   |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | inductance between the switching devices and their respective flying capacitors                                                                |     |

|      | are visualized in the upper graphic. The rightmost graphic shows an example                                                                    |     |

|      | of how the current path of $i_{rec}$ flows through one phase leg of the PCB layout.                                                            | 140 |

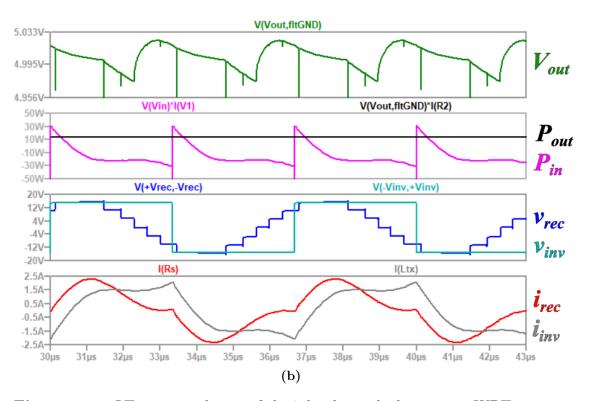

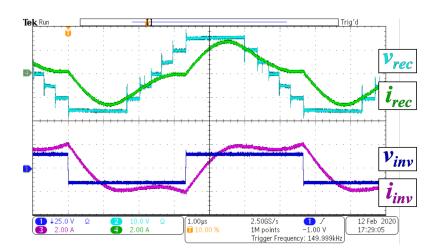

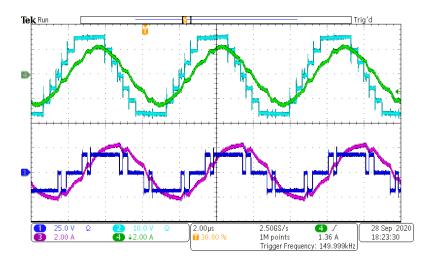

| 5.10 | Waveforms at $P_{out}=16.97$ W, $\angle Z_{rec,1}=25.36^{\circ}$ , and $ Z_{rec,1} =7.66$ $\Omega$                                             | 143 |

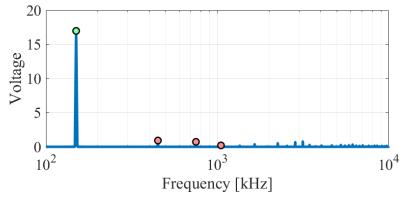

| 5.11 | Low-harmonic spectrum of $v_{rec}$ as pictured in Fig. 5.10. The fundamental                                                                   |     |

|      | component, and $3^{\rm rd}$ , $5^{\rm th}$ , and $7^{\rm th}$ harmonics are marked with colored circles                                        | 145 |

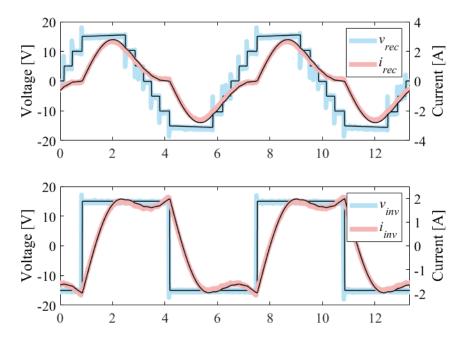

| 5.12 | Experimental waveforms (color) overlaid with modeled waveforms (black) at                                                                      |     |

|      | $P_{out} = 16.97 \text{ W.} \dots \dots$ | 145 |

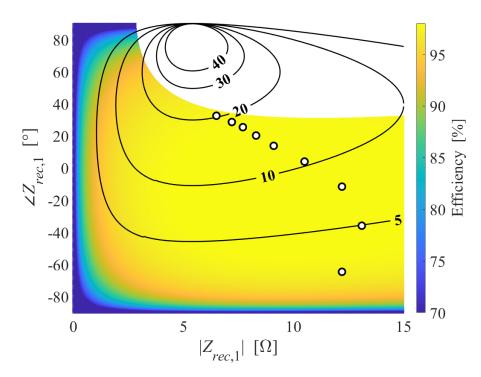

| 5.13 | Experimental data points overlaid on fundamental model in terms of $Z_{rec}$ to                                                                |     |

|      | aid in visualizing how the rectifier is able to traverse the operating region.                                                                 |     |

|      | The white area denotes the space where the MSC cannot operate $(M > 3.81)$ ,                                                                   |     |

|      | and the black lines are output power contours                                                                                                  | 147 |

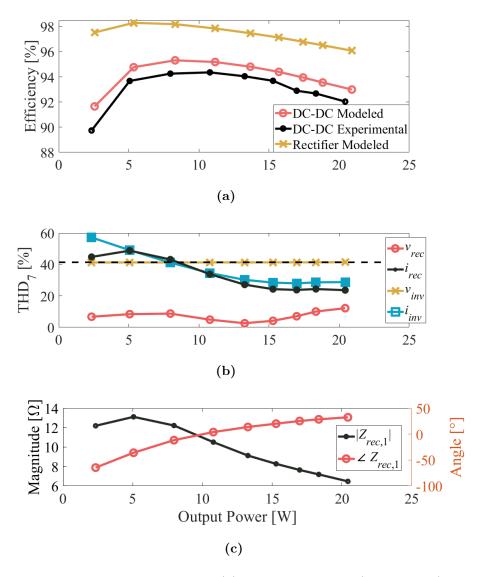

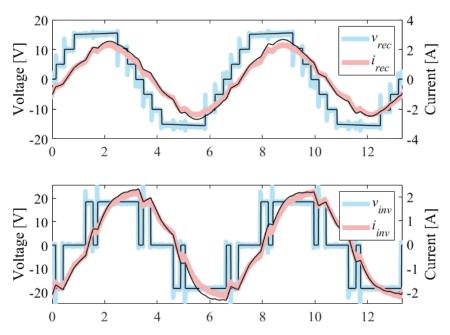

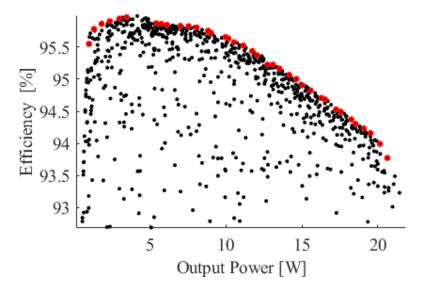

| 5.14 | The experimental data points (a) compared to the (state space) modeled DC-                                                                     |     |

|      | DC efficiency, (b) in terms of distortion, and (c) in terms of the fundamental                                                                 |     |

|      | impedance. The black dashed line in (b) is the THD <sub>7</sub> of a square wave for                                                           |     |

|      | comparison                                                                                                                                     | 148 |

| 5.15 | Loss distribution as predicted by the state-space-based model for the range of                                                                 |     |

|      | output powers from 2.47 W to 20.97 W                                                                                                           | 148 |

| 5.16 | Quality factor of the WPT coils used on the primary and secondary sides [20].                                                                  |     |

|      | The fundamental, $3^{rd}$ , $5^{th}$ , and $7^{th}$ are marked for reference                                                                   | 152 |

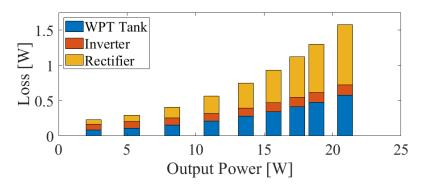

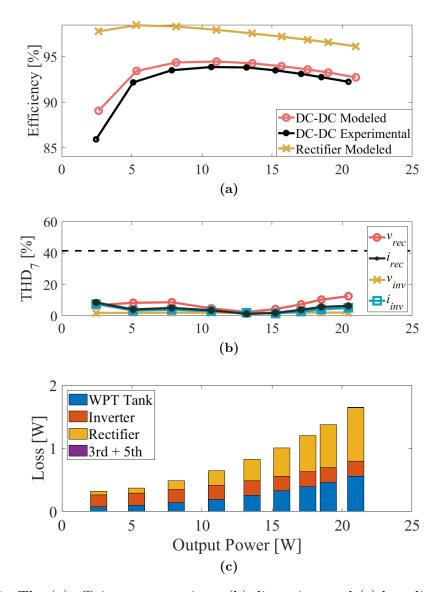

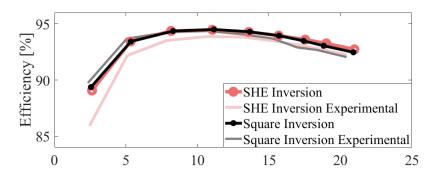

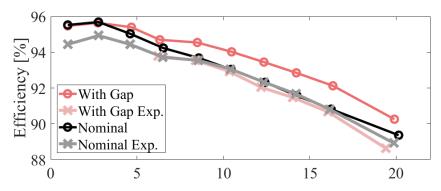

| 5.17 | The (a) efficiency comparison and (b) loss distribution including an adjust-                                                                   |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | ment for additional harmonic loss due to component non-linearities. In                                                                         |     |

|      | Fig. 5.17b, the purple is the additional loss caused by $\mathrm{ESR}_3$ and $\mathrm{ESR}_5$                                                  | 153 |

| 5.18 | Experimental waveforms switched to reduce distortion at $P_{out}=17.1~\mathrm{W}.$                                                             | 155 |

| 5.19 | Experimental waveforms (color) overlaid with modeled waveforms (black) at                                                                      |     |

|      | $P_{out} = 17.07 \text{ W.} \dots \dots$ | 155 |

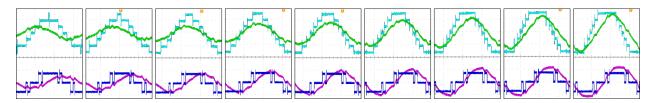

| 5.20 | Waveforms of the low THD power sweep (from low to high power) using SHE                                                                        |     |

|      | modulation at the inverter                                                                                                                     | 157 |

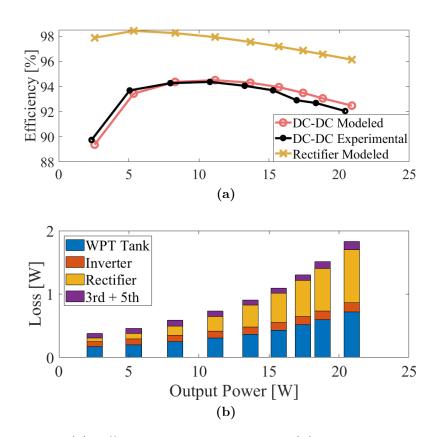

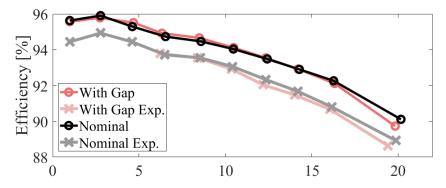

| 5.21 | The (a) efficiency comparison, (b) distortion, and (c) loss distribution for the                                                               |     |

|      | SHE modulated test set                                                                                                                         | 158 |

| 5.22 | Comparison of experimental data sets with (a) inverter square wave modula-                                                                     |     |

|      | tion and (b) inverter SHE modulation                                                                                                           | 159 |

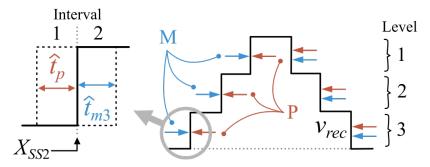

| 6.1  | Modulation (M) and phase (P) type control actions around steady state $v_{rec}$                                                                |     |

|      | resulting in time perturbations $\hat{t}_{mn}$ and $\hat{t}_p$ , respectively                                                                  | 163 |

| 6.2  | Perturbations for an increase in modulation level 2 (increase modulation level                                                                 |     |

|      | duration)                                                                                                                                      | 167 |

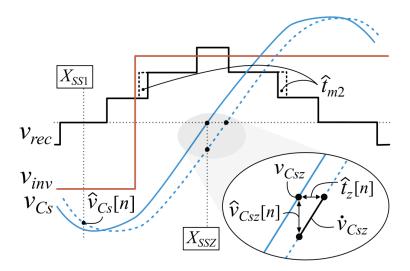

| 6.3  | Steady state waveforms (solid) with a perturbation on level 2 $(\hat{t}_{m2})$ and the                                                         |     |

|      | resulting change in $v_{Csz}$ . The linear projection using the steady state slope,                                                            |     |

|      | $\dot{v}_{Csz}$ , gives the change in zero-crossing, $\hat{t}_z$                                                                               | 171 |

| 6.4  | The (a) natural response matrix $N$ and (b) natural response matrix for the                                                                    |     |

|      | output $H$ as defined in MATLAB                                                                                                                | 175 |

| 6.5  | The (a) forced response matrix $F_{m1}$ and (b) forced response matrix for the                  |       |

|------|-------------------------------------------------------------------------------------------------|-------|

|      | output $J_{m1}$ as defined in MATLAB                                                            | 177   |

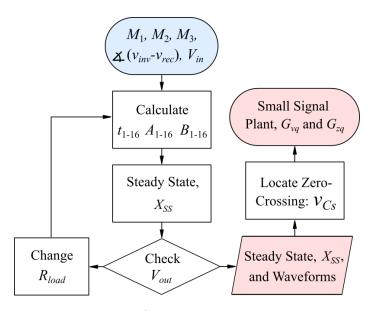

| 6.6  | The high-level overview of how the code base calculates both the steady state                   |       |

|      | power model and the small signal system model. Modulation, phase, and                           |       |

|      | voltage inputs are converted into steady state values, waveforms, and small                     |       |

|      | signal models                                                                                   | 178   |

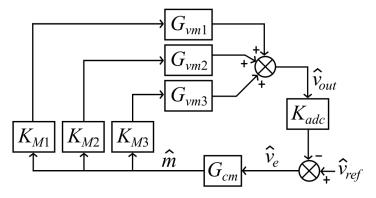

| 6.7  | The control loop for output voltage regulation isolated from the rest of the                    |       |

|      | system                                                                                          | 180   |

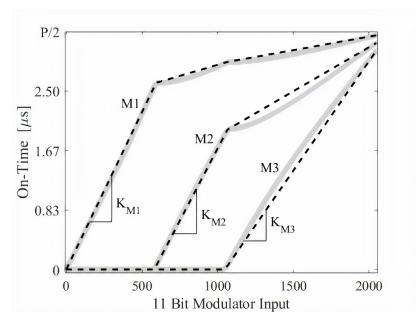

| 6.8  | Modulation scheme of the 7-level switched capacitor rectifier. The input is                     |       |

|      | 11 bit, and the output is the on-time of each level (solid lines) ranging from                  |       |

|      | 0 seconds to half the period $(P/2)$ . The small signal gains of the modulator                  |       |

|      | are approximated using the linear slopes shown by the dotted lines                              | 180   |

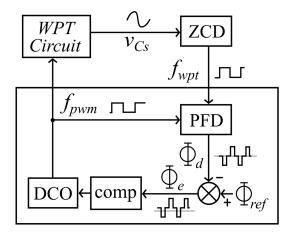

| 6.9  | Block diagram of the control circuitry responsible for synchronizing the                        |       |

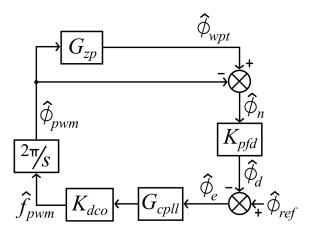

|      | rectifier switching frequency, $f_{pwm}$ , to the WPT carrier frequency, $f_{wpt}$              | 183   |

| 6.10 | Small signal representation of the frequency synchronization control loop                       | 183   |

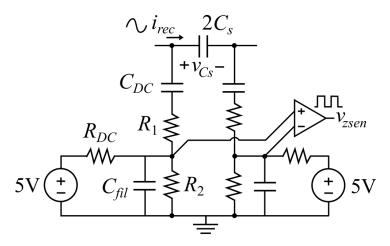

| 6.11 | circuit diagram                                                                                 | 186   |

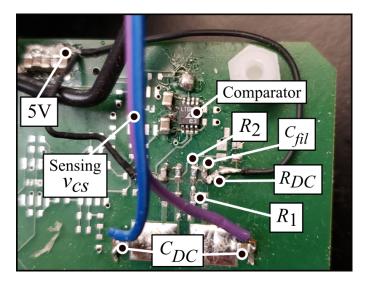

| 6.12 | ZCD as implemented on the prototype PCB                                                         | 187   |

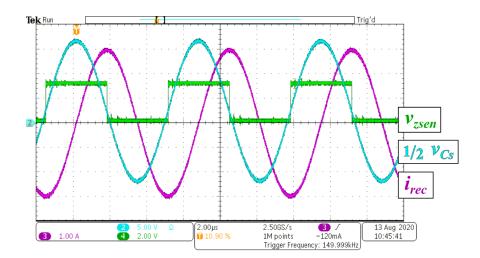

| 6.13 | Example waveforms showing the sensing circuitry function: $v_{Cs}$ , $i_{rec}$ , and $v_{zsen}$ | . 187 |

| 6.14 | Basic frequency synchronization loop with showing the plant model absorbing                     |       |

|      | the zero-crossing detection circuit                                                             | 189   |

| 6.15 | Simulink control simulation. The file can be executed with either loop working       |      |

|------|--------------------------------------------------------------------------------------|------|

|      | in isolation or with dual-loop functionality. The effect of non-linearities          |      |

|      | like clock-edge execution, quantization, and limited control resolution can be       |      |

|      | investigated using this model                                                        | 191  |

| 6.16 | Experimental setup with a different WPT tank than is presented in Chapter 5          | .194 |

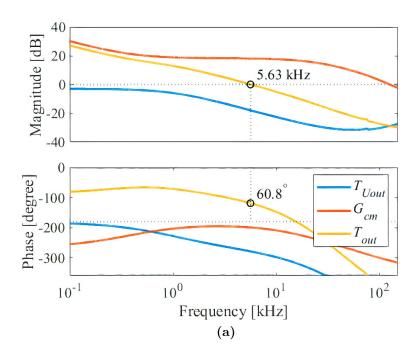

| 6.17 | Plot of the uncompensated loop gain $(T_{Uout})$ , compensator gain $(G_{cm})$ , and |      |

|      | loop gain $(T_{out})$                                                                | 195  |

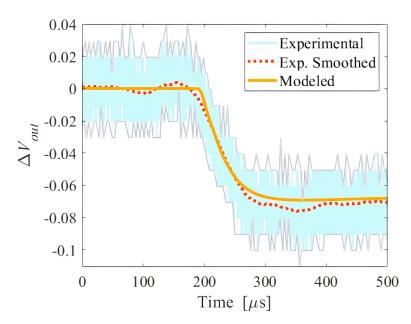

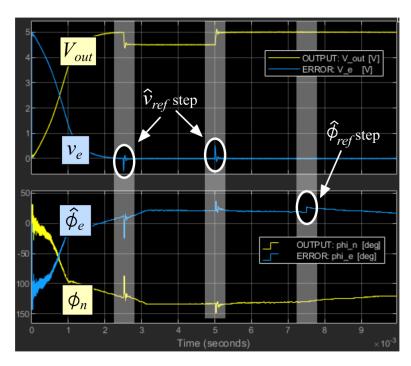

| 6.18 | Experimental vs. modeled response to a step change in $V_{ref}$ for the design in    |      |

|      | Fig. 6.17                                                                            | 197  |

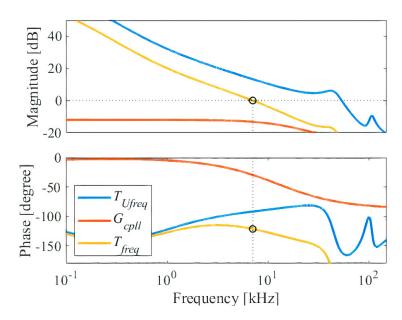

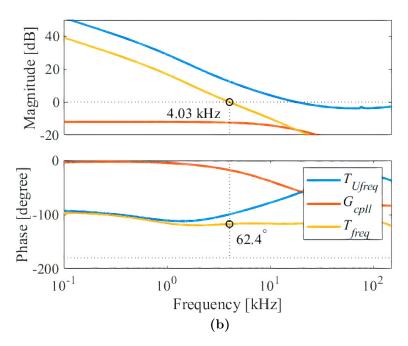

| 6.19 | Frequency synchronization uncompensated loop gain $(T_{Ufreq})$ , compensator        |      |

|      | $(G_{cpll})$ , and final loop gain $(T_{freq})$                                      | 199  |

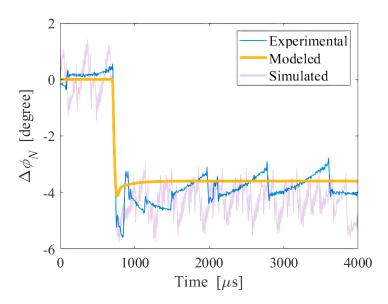

| 6.20 | Experimental vs. modeled vs. simulated response to a step change in $\Phi_{ref}$ for |      |

|      | the design in Fig. 6.19                                                              | 200  |

| 7.1  | The isolated loop designs with the true cross-coupling effects of the power          |      |

|      | stage incorporated                                                                   | 203  |

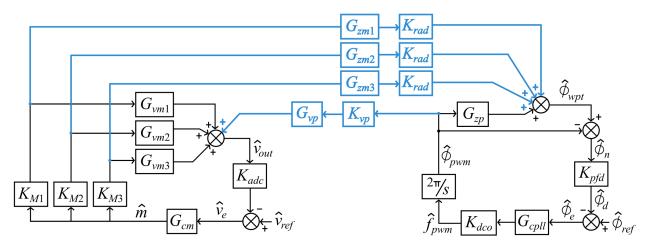

| 7.2  | The full small signal model with blue dotted lines identifying the subcircuits       |      |

|      | used to derive the closed form equations                                             | 205  |

| 7.3  | The simplified versions of (a) subcircuit 1 and (b) subcircuit 2 from Fig. 7.2.      | 207  |

| 7.4  | The simplified small signal model                                                    | 207  |

| 7.5  | Isolated loop designs for both (a) output voltage regulation and (b) frequency       |      |

|      | synchronization                                                                      | 213  |

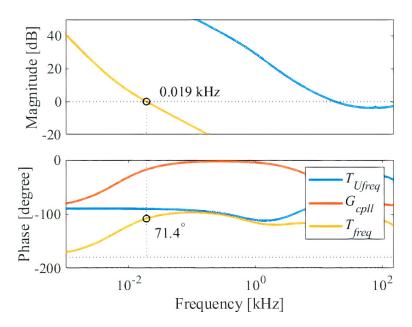

| 7.6  | Lower bandwidth design for the isolated frequency synchronization control loop.215           |      |  |  |  |

|------|----------------------------------------------------------------------------------------------|------|--|--|--|

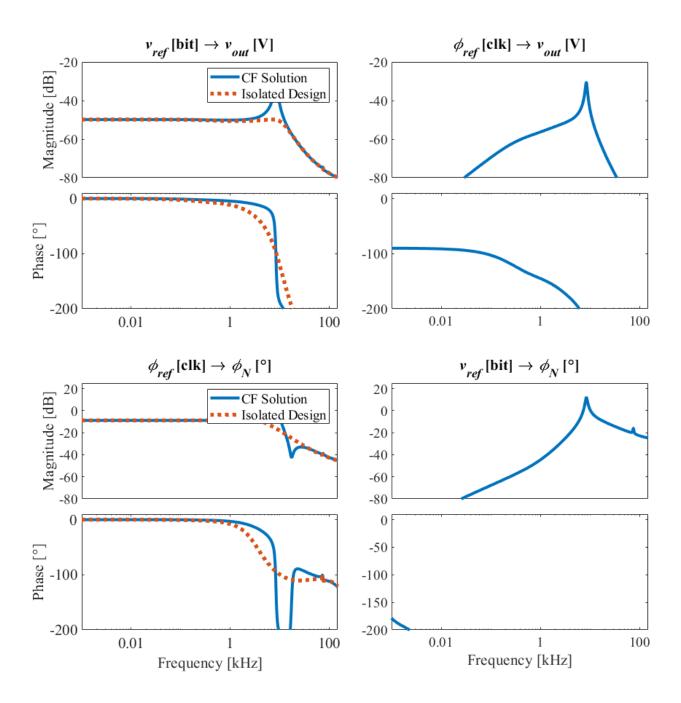

| 7.7  | Initial input-to-output interactions given similar control bandwidths for the                |      |  |  |  |

|      | isolated feedback loop designs                                                               | 216  |  |  |  |

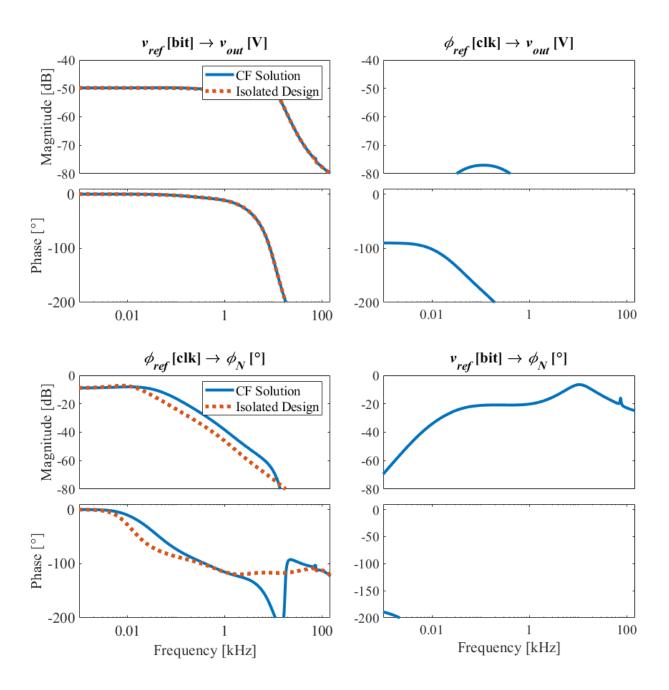

| 7.8  | Input-to-output interactions given a much lower bandwidth design for the                     |      |  |  |  |

|      | isolated frequency synchronization loop                                                      | 218  |  |  |  |

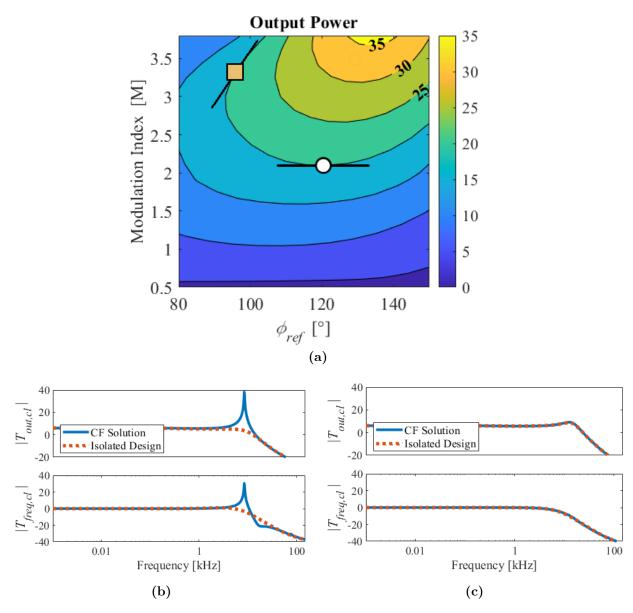

| 7.9  | Simulated result of multiple reference steps for the bandwidth-decoupled design              | .220 |  |  |  |

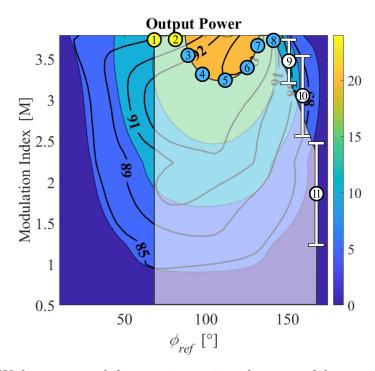

| 7.10 | (a) Modeled output power with two labeled points. Small signal characteristics               |      |  |  |  |

|      | are shown for the (b) orange square and (c) white dot. $\hdots$                              | 222  |  |  |  |

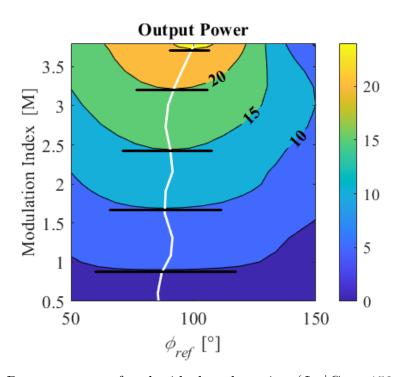

| 7.11 | Power contours for the ideal tank tuning ( $L_{tx} C_p=150$ kHz and $L_{rx} C_s=$            |      |  |  |  |

|      | 150 kHz) accompanied by a white line that denotes $\angle Z_{rec,1} = 0^{\circ}$             | 224  |  |  |  |

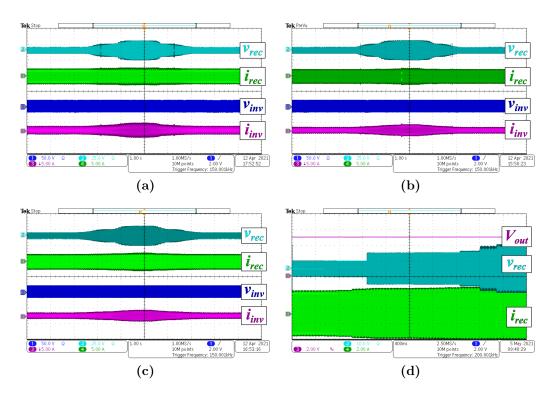

| 7.12 | Low power ( $\approx$ 7 W) to 20 W sweeps under dual-loop operation with a                   |      |  |  |  |

|      | constant value of $\phi_{ref}$ . Primary side tanks tuned with $L_{rx} C_s=150~\mathrm{kHz}$ |      |  |  |  |

|      | and secondary side tanks $(L_{tx} C_p)$ tuned at (a) 180, (b) 120, and (c) 90 kHz            |      |  |  |  |

|      | with a fundamental operating frequency of 150 kHz. (d) Carrier frequency of                  |      |  |  |  |

|      | 200 kHz with tuning of $L_{tx} C_p=131$ kHz and $L_{rx} C_s=150$ kHz                         | 225  |  |  |  |

| 7.13 | Power contours (color) for the new experimental tank tuning $(L_{tx} C_p)$                   |      |  |  |  |

|      | 131.1 kHz and $L_{rx} C_s=151.0$ kHz) accompanied efficiency contours (black)                |      |  |  |  |

|      | at $V_{in} = 19 \text{ V.} \dots \dots \dots \dots$                                          | 228  |  |  |  |

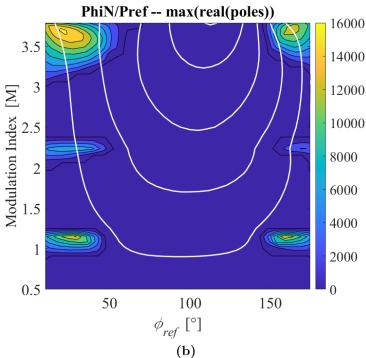

| 7.14 | Output regulation and frequency synchronization compensators applied to                      |      |  |  |  |

|      | the entire operating space, showing output regulation (a) bandwidth and (b)                  |      |  |  |  |

|      | phase margin and frequency synchronization (c) bandwidth and (d) phase                       |      |  |  |  |

|      | margin. The overlaid black lines are the power contours that match Fig. 7.13                 | 230  |  |  |  |

| 7.15 | (a) Absolute value of the sum total difference in dB between the isolated and        |     |  |  |  |

|------|--------------------------------------------------------------------------------------|-----|--|--|--|

|      | closed form small signal representations of the WPT system. The white power          |     |  |  |  |

|      | contours match Fig. 7.13 and are present for reference. (b) Complete system          |     |  |  |  |

|      | model closed loop gain for $V_{out}/V_{ref}$ . The zeros and poles are extracted for |     |  |  |  |

|      | each transfer function, and the plots show the maximum real portion among            |     |  |  |  |

|      | all the pole                                                                         | 232 |  |  |  |

| 7.16 | Wide range stability testing using the control loops outlined in Fig. 7.14. Each     |     |  |  |  |

|      | power range is tested with a constant $\phi_{ref}$ , and points 1-3 saturate before  |     |  |  |  |

|      | 20 W, points 4-8 reach 20 W, and points 9-11 go unstable before 20 W                 | 233 |  |  |  |

| 7.17 | Wide operating range test dynamically moving between operating points                | 235 |  |  |  |

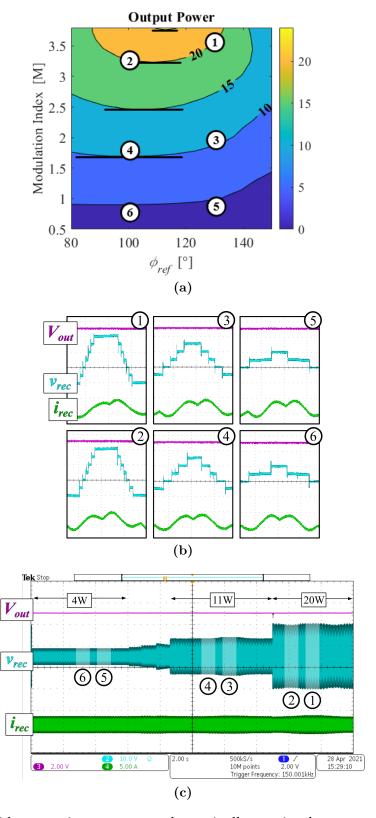

| 8.1  | Optimization of modulation index, control phase, and input voltage for the           |     |  |  |  |

|      | experimental system with 15.66 $\mu$ F                                               | 240 |  |  |  |

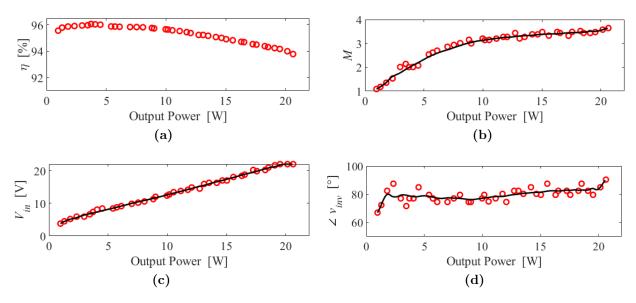

| 8.2  | Results of the optimization. The best data is extract and fit lines are assigned     |     |  |  |  |

|      | for (a) system efficiency, (b) modulation index, (c) rectifier phase, and (d)        |     |  |  |  |

|      | input voltage                                                                        | 240 |  |  |  |

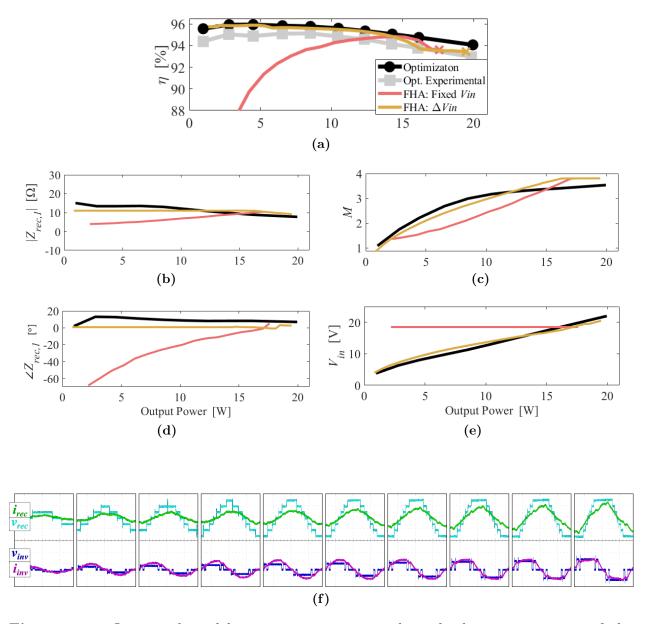

| 8.3 | Optimized model trajectory as compared to the best $\eta$ trajectory of the              |     |

|-----|------------------------------------------------------------------------------------------|-----|

|     | fundamental circuit. The (a) efficiency plot compares the optimal to the                 |     |

|     | first harmonic approximation circuit with $v_{inv}$ both fixed and varied. The           |     |

|     | rectifier impedance (b) magnitude and (c) phase are listed as well as the (c)            |     |

|     | modulation index and (e) DC inverter voltage. The (a) efficiency plot shows              |     |

|     | test results in good agreement with the model. The experimental waveforms                |     |

|     | are given in (f)                                                                         | 242 |

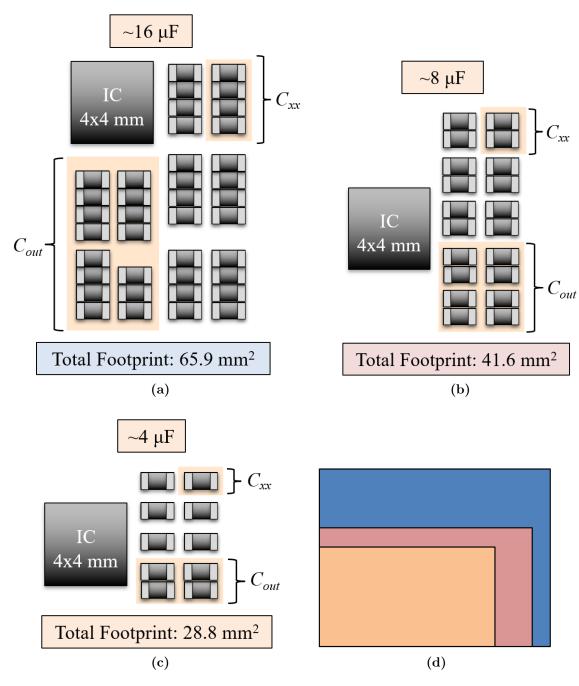

| 8.4 | Assuming a 4 x 4 mm IC design, to scale component sizes for the (a) 16,                  |     |

|     | (b) 8, and (c) 4 $\mu F$ designs are shown. The sum total component areas are            |     |

|     | visualized in (d)                                                                        | 245 |

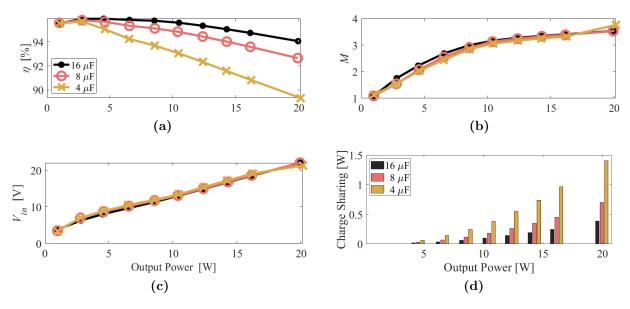

| 8.5 | Comparison of optimized efficiency trajectories for 4, 8, and 16 $\mu \mathrm{F}$ flying |     |

|     | capacitance designs showing (a) efficiency, (b) modulation index, (c) input              |     |

|     | voltage, and (d) charge sharing loss                                                     | 246 |

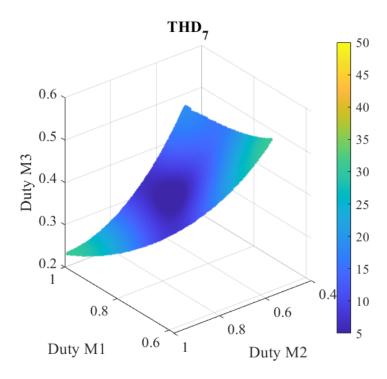

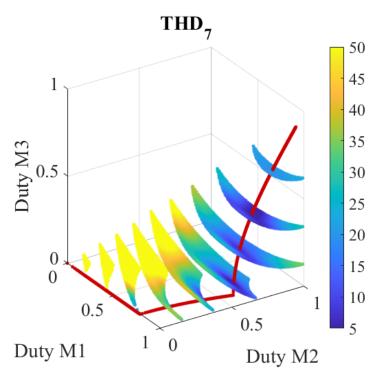

| 8.6 | Every modulation scheme and its accompanying $\mathrm{THD}_7$ that gives a specific      |     |

|     | fundamental component                                                                    | 250 |

| 8.7 | Optimal modulation scheme for harmonic reduction through the $7^{th}$ compo-             |     |

|     | nent: the red line is a digitized sinusoid                                               | 251 |

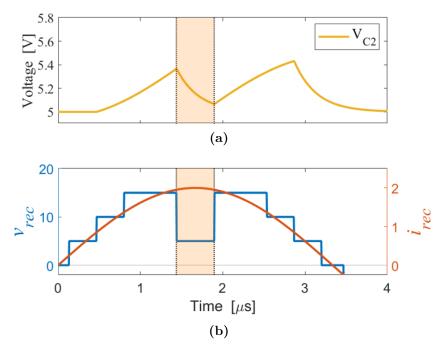

| 8.8 | Example gap modulation showing (a) the voltage ripple on the level two                   |     |

|     | capacitance and (b) the modulation index with a $v_{rec}=1$ interval in the              |     |

|     | middle                                                                                   | 254 |

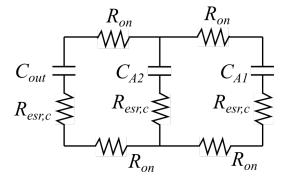

| 8.9 | The equivalent circuit used to calculate the worst case $\tau$ through $C$ .             | 254 |

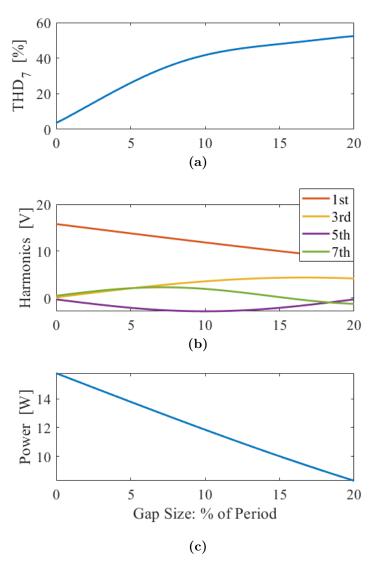

| 8.10 | Assuming a fixed $i_{rec,1} = 2$ A and $Z_{rec} = 0$ , the insertion of various sizes of                 |     |

|------|----------------------------------------------------------------------------------------------------------|-----|

|      | $t_{gap}$ affects both the (a) THD <sub>7</sub> of $v_{rec}$ by changing (b) the components of $v_{rec}$ |     |

|      | and (c) the output power of the system. $\hdots$                                                         | 256 |

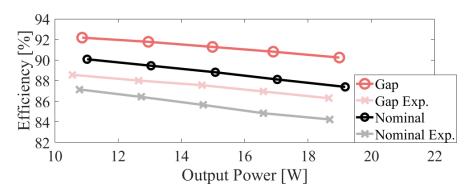

| 8.11 | Comparison of modeled and experimental optimized trajectories for the 4 $\mu \mathrm{F}$                 |     |

|      | rectifier design.                                                                                        | 259 |

| 8.12 | Comparison of modeled and experimental optimized trajectories for the 4 $\mu \mathrm{F}$                 |     |

|      | rectifier design. Here, the model includes individual parasitic elements in the                          |     |

|      | rectifier PCB                                                                                            | 259 |

| 8.13 | Comparison of modeled and experimental optimized trajectories for the 4 $\mu \mathrm{F}$                 |     |

|      | rectifier design at 100 kHz                                                                              | 263 |

### Chapter 1

### Introduction

Consumer device wireless power transfer (WPT) is well established in the market. Annually released flagship smartphones are consistently equipped with the cutting-edge technology, and wireless charging has been included in their hardware suite for the past few years. From laptops and tablets to cellphones and wearables, these handheld electronics are an integral part of daily life. Elimination of charging cables yields significant benefits in terms of convenience, safety, and device longevity. These and other motivating factors have convinced more than 600 international companies to contribute to the development of WPT standards [21], resulting in greater than 3,000 WPT-certified products available on the market today [22].

#### 1.1 Wireless Power

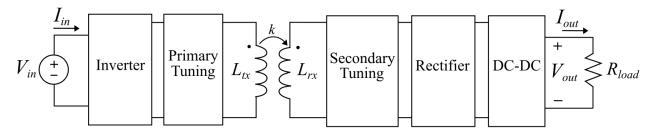

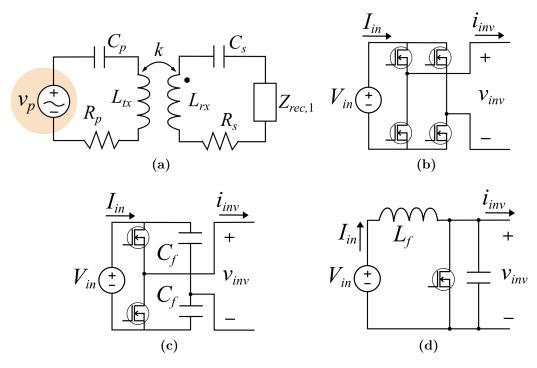

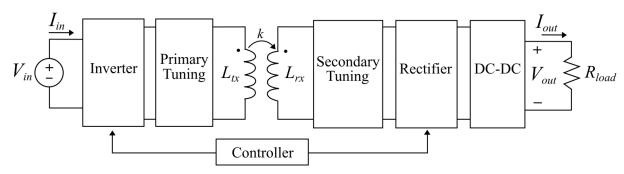

The generalized layout of a wireless power transfer system is shown in Fig. 1.1. Power is transferred from the DC source,  $V_{in}$ , to the load,  $R_{rec,1}$ . All power delivered to the load travels through the transformer comprised of wireless power coils,  $L_{tx}$  and  $L_{rx}$ . Coupling coefficient k denotes the strength of the magnetic coupling between the two inductors in the transformer.

The left and right sides of the circuit in Fig. 1.1 are the transmitter and receiver sides of the WPT system, respectively. In a traditional transformer, ferromagnetic material is generally closed through both indutances in order to amplify the magnetic coupling of the system. Here, the transformer used in wireless power avoids mechanically fastening  $L_{tx}$  to  $L_{rx}$  with core material. Thus, the transmitter (or primary) and receiver (or secondary) sides are both electrically isolated and physically decoupled. This is the fundamental operating principle of WPT systems – transformer design that enables seamless electrical power throughput without restricting the secondary side circuitry to a fixed location in physical space, i.e. a user can charge a device at a charging pad or carry the phone elsewhere without manually changing circuitry or connectors in either case.

There are various approaches when engineering a WPT system. The two most common frameworks for consumer device designs are the AirFuel<sup>TM</sup> and Qi<sup>TM</sup> standards, and while both follow the basic structure shown in Fig. 1.1, there are some notable differences. The AirFuel Resonant standard generally operates with lower coupling values: k is smaller (the system is "loosely coupled"). The fundamental operating frequency for AirFuel is 6.78 MHz,

**Figure 1.1:** General form of a WPT system, showing power commutation from  $V_{in}$ , through  $L_{tx}$  and  $L_{rx}$ , and to  $R_{rec,1}$ .

**Table 1.1:** WPT Standards Comparison [1, 2]

|                           | $\mathbf{Q}\mathbf{i}^{TM}$ | $\mathbf{AirFuel}^{TM}$ Resonant |

|---------------------------|-----------------------------|----------------------------------|

| Carrier Frequency         | 100's kHz                   | 6.78 MHz                         |

| Magnetic Coupling         | Tight, $k \uparrow$         | Loose, $k \downarrow$            |

| Receivers per Transmitter | 1                           | Multiple                         |

| Communication             | In-Band                     | Bluetooth®                       |

| Charging Distance         | ${\rm millimeters}  + $     | centimeters +                    |

multiple devices can charge simultaneously, and the consumer benefits from a longer charging distance [1].

The  $Qi^{TM}$  standard is a "tightly coupled" standard, meaning that the coupling value k tends to be higher. The format allows only one charging coil  $(L_{tx})$  to one receiving coil  $(L_{rx})$ , enables in-band communications between the primary and secondary, and operates in the 100 kHz range. An overview of each standard is given in Table 1.1. Without strict adherence, the research in this thesis is conducted with reference to the Qi standard. Therefore, an overview of the Qi standard is first presented in order to give context to the designs proposed later.

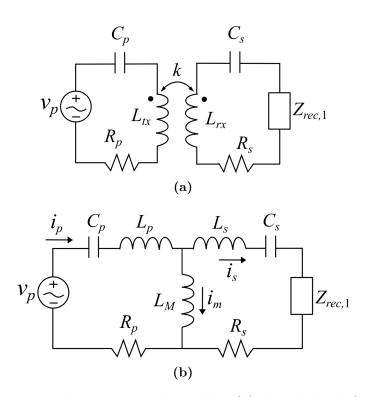

### 1.2 Fundamental Circuit Model

The first harmonic approximation (FHA) is often used to model the primary behavior of the WPT system [23, 24]. Fig. 1.2a shows how the FHA is applied to a basic wireless power transfer system. The output of the inverter is assumed to be sinusoidal and is modeled as voltage source,  $v_p$ . The wireless power coils are again given by  $L_{tx}$  and  $L_{rx}$ , and they are magnetically coupled together by a factor of k. The transmitter and receiver coils are tuned by  $C_p$  and  $C_s$ , respectively. The capacitance values are chosen by the designer to pass power from the source to the load at the fundamental frequency while dampening all other frequencies. The resistances  $R_p$  and  $R_s$  are the equivalent series resistances of the WPT tank at the frequency defined by  $v_p$ , and  $Z_{rec,1}$  is the complex load impedance that receives power.

Figure 1.2: Equivalent WPT tank models: (a) k model and (b) T model.

Given the high likelihood that a user will align the transmitter and receiver coils slightly differently during each charging session, the consequent varying value of k means that a WPT system is operated with a variety of equivalent inductance values. Fig. 1.2b shows an equivalent way of modeling the same circuit, the T model. In the T model, each of the inductance values is a function of the coupling, k, and the energy stored in the magnetic field is modeled by the current flowing through  $L_M$ .

To convert between the two models, inductances  $L_p$ ,  $L_s$ , and  $L_M$  are functions of  $L_{tx}$ ,  $L_{rx}$ , and k. The coupled inductance is

$$L_M = k \cdot \sqrt{L_{tx} L_{rx}},\tag{1.1}$$

and each of the line inductances are

$$L_p = L_{tx} - L_M, \tag{1.2}$$

$$L_s = L_{rx} - L_M. (1.3)$$

When the coupling value is ideal (k = 1), the value of  $L_M$  is large and the amount of circulating magnetizing current is small  $(i_m \approx 0)$ . When k = 0,  $L_M = 0$  and the magnetizing path is shorted, signifying that no power will flow to the output because all current will be circulating through the shorted path  $(i_s \approx 0)$ . In reality, the coupling will fall somewhere between these two extremes, and some current will circulate through the magnetization path

while the rest of the current delivers power to the output. Put simply, the more magnetic field shared between the coils, the greater the magnetic coupling.

The T model provides an insightful framework for understanding system tuning. As an example, take  $L_{tx}=10~\mu\text{H}$ ,  $L_{rx}=10~\mu\text{H}$ , and k=0.4. This means  $L_s$  is equal to 4.0  $\mu\text{H}$  in the T model. If a designer wanted to assign  $C_s$  so that it resonates at 150 kHz with the line inductance ( $L_s=4.0~\mu\text{H}$ ), the equations dictate that  $C_s=1/(4\pi^2 f^2 L_s)=281.5~n\text{F}$ . If the coupling changes from k=0.4 to k=0.2 because a user changes the coil alignment, the resonant frequency also changes to  $f=1/(2\pi\sqrt{L_sC_s})=212.1~\text{kHz}$ .

The specific resonant frequency change in this example may or may not impact the system enough to cause any type of catastrophic failure, but the mechanic illustrated here is one that designers must pay attention to. The fundamental model is predicated on the filtering characteristics of the WPT tank tuning, and if that tuning changes dramatically enough, the underlying assumption that the harmonics are negligible may fail. Furthermore, when the efficiency curves of the inverter, tank, and rectifier are considered, the alteration of k could move the WPT system to an operating point that is significantly less efficient than intended, a byproduct of the spacial freedoms inherent to WPT systems.

Given that the fundamental approximation is valid, the circuit in Fig. 1.2 is used to derive certain loading characteristics for the WPT system. If the secondary side series tuning capacitor is sized to resonate with the receiver coil  $(C_s \text{ with } L_{rx})$ , then  $\text{Im}(Z_{rec,1}) = 0$  and  $Z_{rec,1} = R_{rec,1}$ . Here, equations for maximum power throughput and maximum system efficiency are derived [24]. In general, maximum power is the effect of conjugate matching [24]. For consumer device WPT, the maximum efficiency point is generally more

useful. A closed-form equation for efficiency is derived for the fundamental model, and then the derivative is taken in order to isolate the optimal value of  $R_{rec,1}$  [24]. The work in [24] gives the optimal resistive load

$$R_{rec,opt} = \sqrt{R_s^2 + \frac{R_s}{R_p}(\omega L_M)^2}$$

[24]. (1.4)

The optimal value of  $R_{rec,1}$  is a function of  $L_M$  and, thereby, a function of k. Mathematically, this is why the system efficiency of a WPT link is maximized by changing the load as the magnetic coupling varies. The optimal load often has an imaginary component, however, due to inaccurate matching of the secondary side reactive components. The derivation is expanded to find the complete impedance,  $Z_{rec,1}$ , that optimizes efficiency for the system in Fig. 1.2. This expression is

$$Z_{rec,opt} = \frac{j}{\omega C_s} - j\omega(L_s + L_M) + \sqrt{R_s^2 + \frac{R_s}{R_p}(\omega L_M)^2}$$

[24],

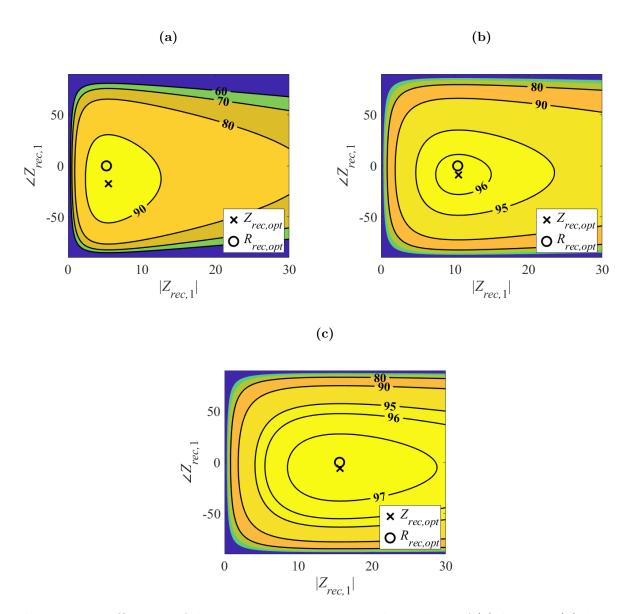

and it returns the complex impedance of  $Z_{rec,opt}$ . To illustrate, Fig. 1.3 shows three different values of k using the tank defined by Table 1.2, where  $C_s$  is not perfectly tuned to  $L_{rx}$ . Each value of coupling results in a different optimal loading, denoted by the black x. Note also the black dot: this is  $R_{rec,opt}$ , the value returned by (1.4) that assumes a perfect secondary tuning. For many tank designs, the efficiency difference between the two operating points is small at high coupling values. But the deviation between  $R_{rec,opt}$  and  $Z_{rec,opt}$  is more significant as coupling reduces because the constant imaginary component of  $Z_{rec,opt}$  becomes more

Table 1.2: Operating Point Used to Exemplify Design Space

| $v_p$  | $L_{tx}$           | $L_{rx}$           | $C_p$             | $C_s$             | $R_p$                  | $R_s$                  |

|--------|--------------------|--------------------|-------------------|-------------------|------------------------|------------------------|

| 19.1 V | $13~\mu\mathrm{H}$ | $13~\mu\mathrm{H}$ | $750~\mathrm{nF}$ | $100~\mathrm{nF}$ | $100~\mathrm{m}\Omega$ | $200~\mathrm{m}\Omega$ |

**Figure 1.3:** Efficiency of the WPT system given coupling values of (a) k = 0.3, (b) k = 0.6, and (c) k = 0.9. The optimal load is shown as a black x, and the optimal resistance  $(\text{Im}(Z_{rec,opt}) = 0)$  is shown as a black circle (o).

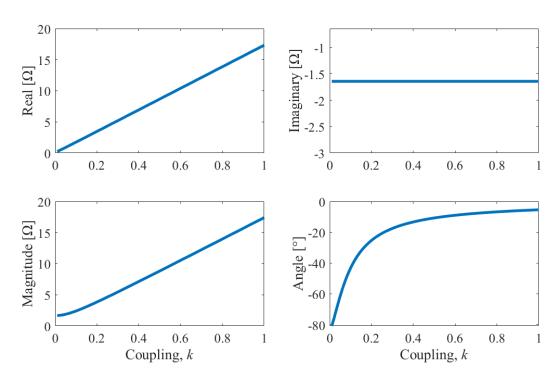

**Figure 1.4:** Cartesian and polar descriptions of the optimal load  $(Z_{rec,opt})$  for different values of k using the tank in Table 1.2.

dominant relative to the impedance's shrinking real component. For the same example, Fig. 1.4 shows how the real and imaginary values of  $Z_{rec,opt}$  vary with coupling factor.

If the WPT receiver tank is tuned perfectly to the fundamental frequency such that  $|Z_{Cs}| = |Z_{Lrx}|$ , then there is no imaginary component necessary to achieve optimal efficiency. In this case, a resistive load is the optimal complex impedance at  $Z_{rec,1}$  [24], and the black x and dot would perfectly align for each coupling value in Fig. 1.3. In practice, perfect tuning is impossible with imperfect component values, and the amount of deviation influences the phase angle required of  $Z_{rec,1}$  for maximum efficiency. Fig. 1.4 exemplifies how an "out-of-tune" tank influences the optimal loading angle of a WPT system by requiring a non-zero imaginary component to return the coils.

# 1.3 The $Qi^{TM}$ Standard

With over 3,700 Qi-certified products available today, the Qi standard dominates the WPT consumer device market [22]. This level of availability means convenience to the end-user, as it is increasingly easy to find a compatible wireless charging location. The market relevance of the standard also means that an understanding of Qi fundamentals is essential for the researcher.

Because the Qi standard is designed to be a near-field, tightly-coupled strategy, k is assumed to be relatively high during the design process. Generally, loosely coupled strategies (like AirFuel Resonant) might operate with  $k \leq \approx 0.25$ , while Qi-type designs will generally

operate with  $k \ge \approx 0.25$  [25–28]. The value of k is affected by the proximity of the WPT coils and the orientation of the two coils relative to one another in space [28].

This is why Qi transmitters and receivers are designed with flat, similarly-sized interfaces. The design allows the  $L_{tx}$  and  $L_{rx}$  coils to share as much magnetic field as possible by ensuring that the wireless power coils are properly oriented and in close proximity. Assuming the coils are then aligned one over the other, k is maximized, and the efficiency of the WPT system is increased. In contrast, if an obstruction creates distance between the coils, they are offset on the z-axis, or if either is rotated, the coupling decreases and the system efficiency likely follows. Power delivery and fundamental frequency are correlated under the Qi standard. Lower power Qi applications can transfer up to 5 W using frequencies from 110 to 205 kHz, while power applications of up to 120 W can leverage the frequency range of 80 to 300 kHz [1]. Because of the space constraints of thin consumer electronics and the orientation constraints of the high coupling requirement, the WPT coils in Qi systems are most often designed with a thin, disc-like shape [29, 30].

The inductances and dimensions necessary for consumer electronic WPT often result in challenges for inductors designed at Qi operating frequencies. In the 100's of kHz frequency range, wireless power coils often exhibit sizeable parasitic equivalent series resistances (ESRs), or equivalently, the coils suffer from a low quality factor, Q. The consequent conduction losses in the WPT tank are significant for Qi designs because of these constraints [31].

Qi systems enable the primary and secondary sides to communicate with one another.

The communication is "in-band," meaning that the information is transmitted from one

unit to another via the same magnetic field that transmits the charging power. The digital communication signal is embedded into the power waveforms and decoded by the message recipient. Communication is useful for both ensuring a safe load is receiving the power and for real-time system-level tuning. Take a transmitter/receiver misalignment for example: k is less than ideal, and the primary side can ping the secondary side, notifying it that the perceived load is not as expected. If the secondary has the means, it can adjust its perceived electrical load to better suit the needs of the transmitter [24, 32, 33]. This type of communication adds robustness and versatility to an already useful platform.

Overall, the Qi standard leverages higher values of k to wirelessly transmit power. The operation frequencies, desired coupling values, and common space constraints tend to push Qi WPT coil designs to lower Q values. Conduction loss tends to dominate switching loss in these systems [31]. Therefore, the Qi protocol is poised to benefit from design approaches that leverage switching actions to reduce WPT coil conduction. The Qi protocol serves as a loose framework for the research in this thesis, but the prototype circuit is not subject to strict adherence to the specific implementation details of the Qi standard.

# 1.4 Elements of a WPT System

A basic understanding of the complete wireless power system is helpful within the discussion and derivation of WPT rectifier topics. As a complement to the rectifier work of this thesis, each segment of the fundamental WPT circuit model is briefly described in this section.

#### 1.4.1 Fundamental Source

The fundamental circuit model is powered by the source  $v_p$ , and in a real circuit this source is an inverter. The inverter takes a DC source voltage and translates it into a periodic waveform by means of switching actions. The inverter sets both the fundamental period and consequent frequency of the entire WPT system. Therefore, an inverter is designed with the entire system in-mind and acts as both the power source and frequency source for the rest of the wireless power system.

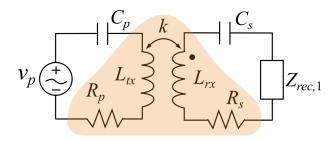

The full-bridge type inverter is a four-switch topology that flips the polarity of a DC voltage  $(V_{in})$  to achieve a square wave output at  $v_{inv}$ . The topology is shown in Fig. 1.5b and is featured in many wireless power works that operate in the kilohertz frequency range [3, 34–37]. The work in [34] showcases a reduction in switch count for a multi-transmitter coil wireless power system. An in-motion secondary side couples to each transmitter as it moves along the coil path, and four inverter switches are used to drive each transmitter coil in the 15.9 kHz system [34]. Another full-bridge approach marries an 85 kHz inductive power inverter with a 1 MHz capacitive power transfer inverter by designing the two supplies to share a half-bridge [36]. Some full-bridge approaches include inductors so that their output manifests as a current source to the rest of the WPT system [35].

A half-bridge is a variation of the full-bridge and only uses two switches to invert a DC source. Fig. 1.5c shows a half-bridge that uses two capacitors across  $V_{in}$ . This topology

**Figure 1.5:** Implementation of the (a) fundamental source via a (b) full-bridge [3], (c) half-bridge [4], or (d) class-E inverter [5, 6]. Here,  $v_p$  is the fundamental component of  $v_{inv}$ .

is used in [4] in a 1 MHz capacitive power transfer system. The work in [35] uses a full-bridge component arrangement, but the two high-side devices are inductors. The current-fed 2,000 W wireless power system operates at 46.8 kHz and is calculated at 92.5 % efficient [35].

The class-E topology is often regarded as a good candidate for megahertz frequency operation due to its ability to achieve zero voltage switching and zero voltage derivative switching (ZVDS or ZDS) [28, 38–43]. Switching at 10's of kHz typically does not incur enough switching loss to dominate the loss profile. However, the class-E inverter in Fig. 1.5d has still been investigated at  $\approx 300$  kHz for inductively coupled wireless power applications [5, 6], and the work in [44] used class-E inversion and rectification in a 200 kHz system. Note that the primary side capacitor,  $C_p$ , and the transmitter coil,  $L_{tx}$ , are not pictured in any inverter topology in Fig. 1.5a, but these elements are a necessary part of the class-E topology in Fig. 1.5d.

While different, each of the inverter topologies serves the same purpose within the fundamental circuit model: power the WPT circuit as a sinusoidal source. In Fig. 1.5, each topology leverages  $V_{in}$  to create  $v_{inv}$ , and the first harmonic of  $v_{inv}$  in Figs. 1.5b-1.5d serves as  $v_p$  in a wireless power system. The inverter provides the input power to and dictates the fundamental frequency of the WPT circuit.

#### 1.4.2 WPT Coils

The coupled coils of the wireless power system are the fundamental technology that makes WPT possible, and given that the full system power flows through the wireless power tank, a significant amount of research goes into both coil design and tuning. However, as illustrated with the fundamental circuit model in Fig. 1.6, the conduction losses associated with  $R_p$  and  $R_s$  are the most basic hindrance to a high-efficiency wireless power setup. Within the tuned WPT tank, these parasitic ESRs are attributed almost entirely to the inductors because low ESR capacitors are relatively easy to purchase for applications near 100 kHz. At the most basic level, more coil turns means a larger inductance, but more turns also means more conduction loss (larger  $R_p$  and  $R_s$ ). Improving coil design is a priority in the research community because it directly affects the viability of the WPT system [29, 30, 45–56].

Many techniques serve to characterize or improve the coils used in today's systems. The relationship between stray magnetic field and coil efficiency is characterized in [29]. The work in [45] solves for an optimal coil design with an analytical process that accounts for both ohmic loss and the skin effect. Bayesian optimization [30], multilayer flat spiral techniques [46], and numerical modeling [47] are applied to wireless power coil designs in attempts to improve the state of the art. Another technique involves leveraging non-uniform wire width in a manner that increases coil inductance more quickly than ESR. The design showcases a 1.21 times increase in quality factor when compared to the traditional approach [54].

Magnetic material is used to increase the efficiency of WPT system by increasing the coupling factor relative to the ESR components. The work in [31] analyzes a wireless power system, concludes that the losses in the WPT tank should be the focus, and then verifies a solution strategy using Litz wire and magnetic materials to improve efficiency. In [49], various types of ferrite structures are compared, and structure 4 is concluded to provide high

Figure 1.6: The WPT coils and their parasitic components as shown in the fundamental circuit model.

quality factor and misalignment tolerance. Soft magnetic composites are also considered for WPT applications [48]. However, much of the work with magnetic material is focused on kilowatt-level WPT [31, 48, 49], and while magnetic material is widely accepted as a useful tool for inductor design, incorporation of magnetic materials into the slim form factors of consumer devices is a non-trivial affair. Using an A10 coil during experimental verification (a coil commercially available for consumer device WPT), a soft magnetic structure is 84 % thinner than a conventional ferrite shield and reduces flux leakage by 20.9 % [57]. Another technique uses an advanced PCB structure with integrated magnetic nanocrystalline sheets, allowing ultra-thin printed coils to use magnetic material [58].

The coil link in Fig. 1.6 is the cornerstone technology that enables wireless power transfer. The coil-centric research work in the field of wireless power ultimately serves to increase the efficiency and viability of modern WPT system. Irrespective of the technological improvements, every WPT coil pair has loss mechanisms and a consequent loss profile. Understanding the loss characteristics of the coils used in a WPT system design is essential for the success of that design.

## 1.4.3 Tank Tuning

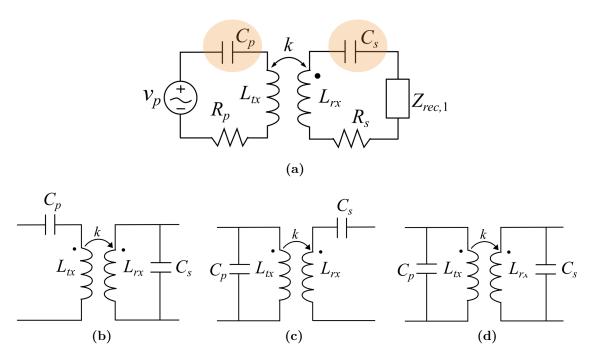

Impedance matching networks (IMNs) describe the topological ways of matching the WPT coils to their resonant capacitors. The compensation scheme of the fundamental circuit in Fig. 1.7a is "series-series". Because  $C_s$  is in series with  $L_{tx}$  and  $C_p$  is in series with  $L_{rx}$ , both the primary and secondary sides are said to be series compensated. There are four

dominate types of compensation: series-series (SS), series-parallel (SP), parallel-series (PS), and parallel-parallel (PP) [59]. The first descriptor always refers to the transmitter side and the second descriptor to the receiver side. For example, a PS compensation would mean that  $C_p$  is in parallel with  $L_{tx}$  and  $C_s$  is in series with  $L_{rx}$ . Fig. 1.7 shows examples of each of the four basic impedance matching network types.

Generally, series-series compensation is the most popular [24, 25, 34, 45, 59–63]. The SS design is shown to provide the lowest copper mass for a given efficiency, while PS provides the lowest operating frequency [60]. A genetic algorithm is used to find which compensation methods create the most robust WPT designs in terms of minimization of the input phase of the primary input impedance. SS and PS are cited as good candidates under this criteria [25]. The work in [59] again points to the SS design after comparing the four IMNs in terms of maximum efficiency, maximum load power transfer, load independence, k independence, and allowance of k = 0. The SS compensation approach to WPT is well documented in literature and serves as a sufficient tuning approach for many wireless power systems [59].

Other types of compensations schemes are sometimes used. The LCC compensation scheme includes an additional inductor and capacitor to tune either of the WPT coils [3, 64]. Combined with the control scheme in [64], the resonant frequency under this tuning is no longer a function of either the coupling coefficient or the load condition. Another approach tunes the primary and secondary sides with different IMNs. Retaining the simple one-capacitor tuning on the secondary side still leaves room for more complex tuning on the primary [35, 37, 65]. An extra capacitor on the primary side is called a CCL tuning [35], and

**Figure 1.7:** The four basic types of WPT compensation: (a) series-series (SS) as shown in the fundamental model, (b) series-parallel (SP), (c) parallel-series (PS), and (d) parallel-parallel (PP).

LCL tuning adds an single inductor [37, 65]. The LCL serves to decouple the transmitter current from the coupling value and load condition [37].

Each of these compensation schemes represents an operating space via the fundamental circuit model. While there are pros and cons to each tuning approach, characterization is possible for any of the impedance matching networks seen in literature. As an example, the series-series compensation style in Fig. 1.2a is characterized in Fig. 1.3. Generally, SS type tuning is sufficient to meet the demands placed on most WPT systems [24, 25, 34, 45, 59–63], but quantification of the design space is the most essential step to ensuring the successful implementation of a wireless charging platform.

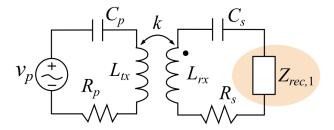

#### 1.4.4 Rectifier

The full wireless power system is comprised of an inverter, coupled coils, a tuning method, and a rectifier. The focus of this thesis is the WPT rectifier, depicted as a load in the fundamental model in Fig. 1.8. In the fundamental model,  $Z_{rec,1}$  is the impedance presented to the WPT circuit by the rectifier. As outlined by the example in Fig. 1.3, there exist an optimal way of loading the WPT system with the rectifier impedance, highlighting the importance of considering  $Z_{rec,1}$  when choosing a WPT rectification topology.

Given that the other elements of a WPT system are chosen (inverter, coils, and tuning), the rectifier is responsible for loading the system appropriately. Ideally, the rectifier presents the optimal  $Z_{rec,1}$  such that the system-wide efficiency is maximized. For this reason, equivalent input impedance is an important metric for analyzing different designs.

Figure 1.8: The rectifier is depicted as a load in the fundamental circuit model.

Likewise, there are other important metrics to consider during the design process. The efficiency metric is a given, as excess loss is not only inelegant but also produces heat, a poor characteristic for handheld devices. Evaluation metrics related to compactness and harmonic content are motivated in the next section.

#### 1.5 Practical Rectifier Considerations

The consumer device architectures currently deployed in the market highlight additional challenges associated with in-device rectification design. As these devices get smaller and more power hungry, the space and loss allowances that constrain engineers get less forgiving. This section references devices currently available in the market in order to define evaluation metrics for comparing the different rectifier design approaches found in literature.

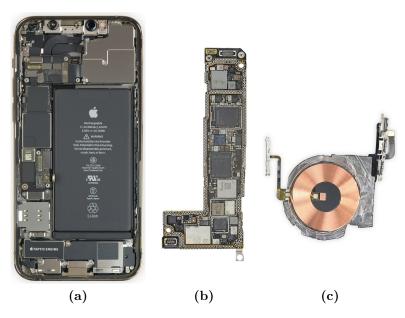

## 1.5.1 Compactness

Fig. 1.9 shows a breakdown of the iPhone 12 by Apple, released in late 2020. The opened cell phone, internal circuit board, and wireless power coil are shown in Figs. 1.9a-1.9c [7]. The tightly packed internal structure of the phone illustrates the density to which the power circuitry design must adhere. Furthermore, the entire iPhone 12 device is only a few millimeters thick and is comprised of multiple part layers (PCB, screen, wireless coil, mechanical case, etc.), meaning that all electrical components used must be very low-profile.

Reviewing the literature for WPT rectifier strategies reveals designs that, if implemented in a real system, likely would not be easy to fit into any form factor similar Fig. 1.9. For

Figure 1.9: iPhone 12 (a) breakdown, (b) circuit board, and (c) wireless charging coil [7].

example, a 11.2 W and 3.8 V wireless power system showcases 77.3% peak efficiency at k=0.6 by leveraging an active rectifier and DC-DC converter [66]. However, the DC-DC converter is designed for a filter inductance of  $L=1~\mu\mathrm{H}$ , a part search for which returns a competitive inductor choice: ASPI-0425-1R0N-T3 by Abracon LLC [67]. This 1  $\mu\mathrm{H}$  inductor has a DCR of 12 mH and a 3A current rating (virtually no safety factor: 2.95 A = 11.2 W / 3.8 V), both of which are sufficient for the application. However, the ASPI-0425-1R0N-T3 is 2.5mm thick and has dimensions of 4mm x 4mm. For a single component, this is a very large area under the circuit density constraints implied by Fig. 1.9.

In general, this qualitative analysis motivates the use of rectification topologies that do not require large filter inductors. While including large inductances is likely possible in today's consumer devices, the size of such components makes them less competitive than other, more power dense components. For the purpose of this thesis, a metric of 'compactness' is introduced as a binary method of evaluating rectification strategies that simply denotes the presence or absence of a filter DC inductor. If a topology has a DC filter inductor, it is said to lack compactness. If a topology does not have a DC filter inductor, it is said to be compact.

#### 1.5.2 Harmonic Content

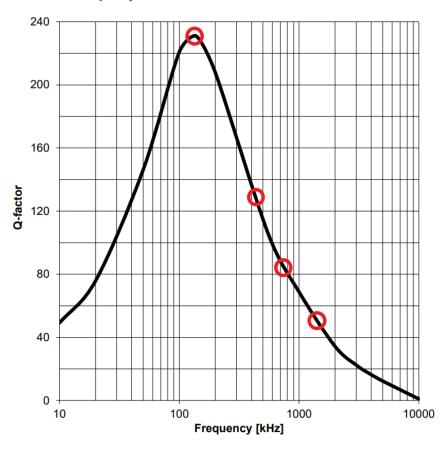

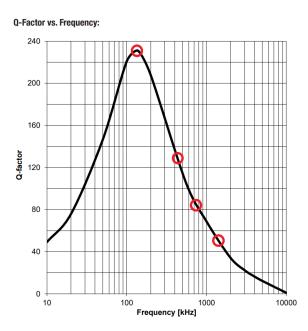

Another circuit element currently available for purchase is the wireless power coil. Part number 760308101141 by Würth Elektronik is a high quality factor, 10  $\mu$ H coil intended for wireless power applications at 150 kHz [8]. The quality factor at 150 kHz is reported at

220, signifying the potential for low-loss WPT system designs. However, the quality factor curve across a range of frequencies is shown in Fig. 1.10, and it shows how the quality factor rapidly drops off after the designed operating frequency.

The fundamental frequency of 150 kHz holds the maximum quality factor at  $\approx$ 220, and the subsequent harmonics at 450 kHz, 750 kHz, and 1050 kHz show quality factors of  $\approx$ 110,  $\approx$ 85, and  $\approx$ 50, respectively. Assuming the datasheet inductance remains constant at 10  $\mu$ H, the equivalent series resistance (ESR) values at the fundamental,  $3^{rd}$ ,  $5^{th}$ , and  $7^{th}$  are 43 m $\Omega$ , 257 m $\Omega$ , 554 m $\Omega$ , and 1,320 m $\Omega$ , respectively. Given any significant amount of harmonic content in the tank currents, these large harmonic ESR values can cause deviation from the fundamental model by adding extraneous loss into the circuit.

A coil design with constant ESR helps to mitigate the potential harmonic losses from significantly influencing the loss profile. However, achieving a constant ESR across any significant frequency band is nearly impossible for WPT coil. Another approach is to eliminate the harmonic content of the power current conducting through the coil. In the absence of waveform distortion, the harmonic ESR values of the tank are irrelevant to the loss within the circuit. This interaction motivates rectification strategies that produce less waveform distortion. The implication of a rectifier that produces lower harmonic content is a higher overall system efficiency due to the  $I^2R$  harmonic interactions with component non-linearities like those in Fig. 1.10.

## Q-Factor vs. Frequency:

Figure 1.10: The quality factor of WPT coil part number 760308101141 verses frequency [8]

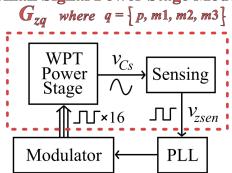

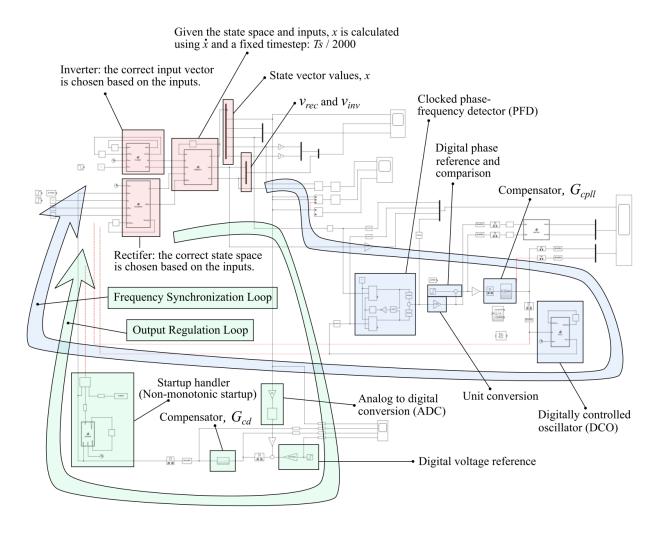

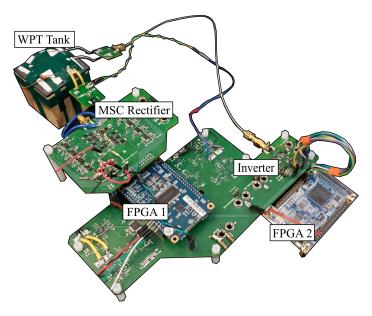

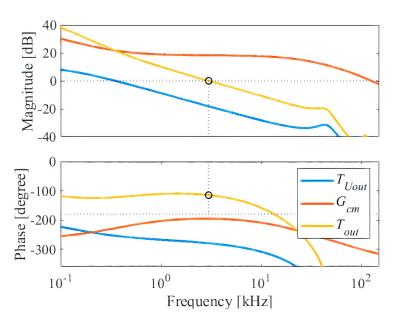

#### 1.6 Rectifier Metrics