# University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange

**Doctoral Dissertations**

**Graduate School**

12-2021

# Switching Performance Evaluation, Design, and Test of a Robust 10 kV SiC MOSFET Based Phase Leg for Modular Medium Voltage Converters

Xingxuan Huang xhuang36@vols.utk.edu

Follow this and additional works at: https://trace.tennessee.edu/utk\_graddiss

Part of the Power and Energy Commons

### **Recommended Citation**

Huang, Xingxuan, "Switching Performance Evaluation, Design, and Test of a Robust 10 kV SiC MOSFET Based Phase Leg for Modular Medium Voltage Converters. " PhD diss., University of Tennessee, 2021. https://trace.tennessee.edu/utk\_graddiss/6954

This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Xingxuan Huang entitled "Switching Performance Evaluation, Design, and Test of a Robust 10 kV SiC MOSFET Based Phase Leg for Modular Medium Voltage Converters." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Leon M. Tolbert, Major Professor

We have read this dissertation and recommend its acceptance:

Fei (Fred) Wang, Hua Bai, Brian Rowden

Accepted for the Council:

Dixie L. Thompson

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

Switching Performance Evaluation, Design, and Test of a Robust 10 kV SiC MOSFET Based Phase Leg for Modular Medium Voltage Converters

> A Dissertation Presented for the Doctor of Philosophy Degree The University of Tennessee, Knoxville

> > Xingxuan Huang December 2021

Dedicated to my parents, Rigao Huang and Xiaoqing Yang.

#### ACKNOWLEDGEMENTS

First, I would like to acknowledge my supervisor Dr. Leon Tolbert. I really appreciate him for offering me this fabulous opportunity and his continuous, patient, and valuable guidance in my research and dissertation. His honesty, thoughtfulness, and education philosophy have inspired me to become a better person, for which I am always grateful. I am grateful to Dr. Wang for supervising my research projects and offering valuable insights and suggestions in my research. I want to thank Dr. Bai and Dr. Rowden for serving in the committee and their suggestions in improving my dissertation and research. I also appreciate Dr. Daniel Costinett and Dr. Zheyu Zhang for their generous help and feedback when I study for my PhD degree in UTK and CURENT center.

Especially I want to thank Dr. Shiqi Ji and Mr. William Giewont with great personality and knowledge in medium voltage power electronics. I was able to learn from them in many aspects, through a lot of discussion and hands-on experiments. I am fortunate and grateful to work in research projects with so many incredible researchers in CURENT. In addition to Dr. Shiqi Ji and Mr. William Giewont, they are Dingrui Li, Dr. Ruirui Chen, Dr. Cheng Nie, James Palmer, Jingjing Sun, Shida Gu, Dr. Sheng Zheng, Min Lin, John Meadors, and Dr. Li Zhang. I also acknowledge Mr. Marko Laitinen from Danfoss for his generous and continuous help in my research projects.

Also I want to thank my fellow UTK students and my officemates for help, friendship, and valuable discussions in my research. Particularly, I would like to thank Jie Li, Dr. Ren Ren, Dr. Ling Jiang, Ziming Wang, William Norton, Yang Huang, Liyan Zhu, Zhou Dong, Craig Timms, Dr. Shuyao Wang, Dr. Chongwen Zhao, Haiguo Li, Dr. Wen Zhang, Paxton Wills, Kamal Sabi, Dr. Bo Liu, Dr. Handong Gui, Ruiyang Qin, Haoyuan Sun, Ziwei Liang, Jiahao Niu, and Montie Smith. Also, I am grateful to my officemates, Daniel Merced, Zhe Yang, Paige Williford, and Mark Nakmali, from whom I was able to get a lot of help and support in my daily life and research in Knoxville.

I sincerely acknowledge PowerAmeirca, Advanced Research Projects Agency (ARPA-E) and Advanced Manufacturing Office (AMO) of U.S. Department of Energy, and Danfoss for funding my research. I also want to express my appreciation to Wolfspeed and Powerex for manufacturing and packaging the 10 kV SiC MOSFETs used in my research. My study at UTK is supported by the staff of EECS department and CURENT center, to whom I am really grateful, especially Mr. Robert Martin and Mr. Ryan Smiley. The work in this dissertation made use of the Engineering Research Center Shared Facilities supported by the Engineering Research Center Program of the National Science Foundation and DOE under NSF award number EEC-1041877 and the CURENT Industry Partnership Program.

Last but not least, I want to thank my families for their endless love and support throughout my life, especially my parents and my grandparents. Their love and support are particularly important during the pandemic. Without them, I could not finish this dissertation.

Per aspera ad astra.

#### ABSTRACT

10 kV SiC MOSFETs are one of the most promising power semiconductor devices for next-generation high-performance modular medium voltage (MV) converters. With extraordinary device characteristics, 10 kV SiC MOSFETs also bring a variety of challenges in the design and test of MV converters. To tackle these inherent challenges, this dissertation focuses on a robust half bridge (HB) phase leg based on 10 kV SiC MOSFETs for modular MV converters. A baseline design and test of the phase leg is established first as the foundation of the research in this dissertation.

Thorough evaluation of 10 kV SiC MOSFETs' switching performance in a phase leg is necessary before applying them in MV converters. The impact of parasitic capacitances and the freewheeling diode is investigated to understand the switching performance more extensively and guide the converter design.

One non-negligible challenge is the flashover fault resulting from the premature insulation breakdown, a short circuit fault with extremely fast transients. A device model is established to thoroughly analyze the behavior of 10 kV SiC MOSFETs when the fault occurs in a phase leg. Subsequently, the gate driver and protection design considerations are summarized to achieve lower short circuit current and overvoltage and ensure the survival of the MOSFET that is in ON state when the fault happens.

Furthermore, it is challenging to design the overcurrent/short circuit protection with fast response and strong noise immunity under fast switching transients for 10 kV SiC MOSFETs. The noise immunity of the desaturation (desat) protection is studied quantitatively to provide design guidelines for noise immunity enhancement. Then, an

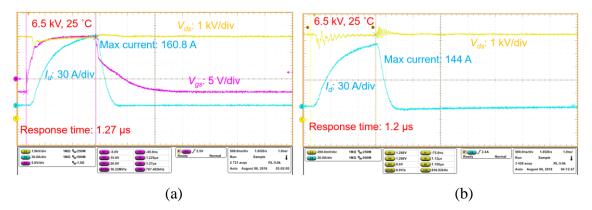

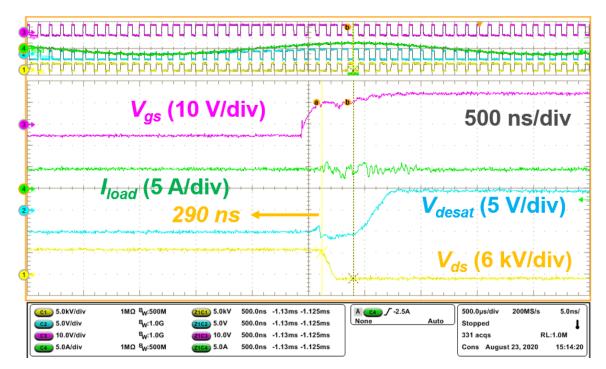

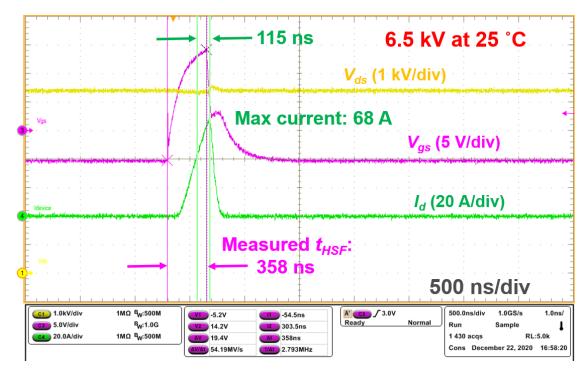

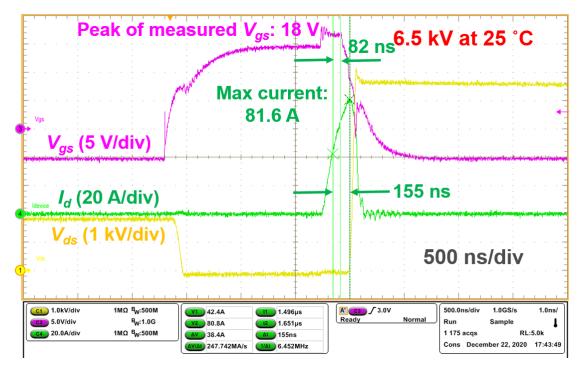

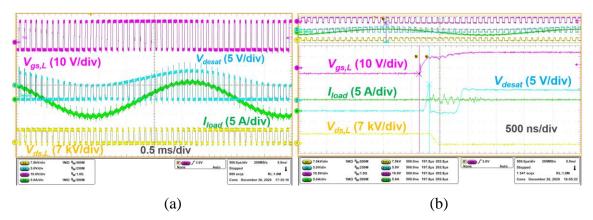

improved desat protection scheme with digital blanking time is developed with <350 ns response time, which is validated with short circuit tests at 6.5 kV. Based on the investigation results of the noise immunity, the strong noise immunity of the developed protection is also successfully validated. A desat protection scheme with ultrafast response is also proposed after considering the high negative dv/dt during the turn-on transient of 10 kV SiC MOSFETs. The ultrafast response (<160 ns response time) and the strong noise immunity are validated with short circuit tests and ac-dc continuous test at 6.5 kV.

In addition, a simple test scheme is proposed and validated experimentally, in order to qualify the HB phase leg based on the 10 kV SiC MOSFET comprehensively for the modular MV converter applications. The test scheme includes the ac-dc continuous test with two phase legs in series to create the testing condition similar to what is generated in a modular MV converter, especially the high dv/dt. The test scheme can fully test the capability of the phase leg to withstand high dv/dt and its resulting noise.

# TABLE OF CONTENTS

| CHAPTER 1. Introduction                                                                                                                                                                                              | 1                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 1.1 Modular Medium Voltage Converters                                                                                                                                                                                | 1                                                  |

| 1.2 10 kV SiC MOSFETs for MV Applications                                                                                                                                                                            | 5                                                  |

| 1.3 Motivation and Objective                                                                                                                                                                                         | 11                                                 |

| 1.4 Dissertation Outline                                                                                                                                                                                             | 14                                                 |

| CHAPTER 2. Literature Review                                                                                                                                                                                         | 17                                                 |

| 2.1 Switching Performance Evaluation                                                                                                                                                                                 | 17                                                 |

| 2.1.1 Characterization and Influencing Factors of Switching Performance                                                                                                                                              | 18                                                 |

| 2.1.2 Impact of Freewheeling Diode on Switching Performance                                                                                                                                                          | 25                                                 |

| 2.2 Design of 10 kV SiC MOSFET Based Phase Leg                                                                                                                                                                       | 29                                                 |

| 2.2.1 Gate Driver Design                                                                                                                                                                                             | 29                                                 |

| 2.2.2 Overcurrent Protection Design                                                                                                                                                                                  | 34                                                 |

| 2.2.3 Impact of Flashover Fault on Gate Driver Design                                                                                                                                                                | 39                                                 |

| 2.3 Testing of 10 kV SiC MOSFET Based Phase Leg                                                                                                                                                                      | 41                                                 |

| 2.4 Summary                                                                                                                                                                                                          | 44                                                 |

|                                                                                                                                                                                                                      |                                                    |

| CHAPTER 3. Baseline Design and Test of a 10 kV SiC MOSFET Based Phase Leg                                                                                                                                            | 46                                                 |

| CHAPTER 3. Baseline Design and Test of a 10 kV SiC MOSFET Based Phase Leg<br>3.1 Overview of the Phase Leg                                                                                                           |                                                    |

|                                                                                                                                                                                                                      | 46                                                 |

| 3.1 Overview of the Phase Leg                                                                                                                                                                                        | 46<br>46                                           |

| 3.1 Overview of the Phase Leg                                                                                                                                                                                        | 46<br>46<br>47                                     |

| <ul> <li>3.1 Overview of the Phase Leg</li> <li>3.1.1 10 kV SiC MOSFET</li> <li>3.1.2 Architecture of the Phase Leg</li> </ul>                                                                                       | 46<br>46<br>47<br>49                               |

| <ul> <li>3.1 Overview of the Phase Leg.</li> <li>3.1.1 10 kV SiC MOSFET</li> <li>3.1.2 Architecture of the Phase Leg.</li> <li>3.2 Gate Driver Design</li></ul>                                                      | 46<br>46<br>47<br>49<br>51                         |

| <ul> <li>3.1 Overview of the Phase Leg.</li> <li>3.1.1 10 kV SiC MOSFET.</li> <li>3.1.2 Architecture of the Phase Leg.</li> <li>3.2 Gate Driver Design</li> <li>3.2.1 Signal Transfer and Feedback Stage.</li> </ul> | 46<br>46<br>47<br>49<br>51<br>54                   |

| <ul> <li>3.1 Overview of the Phase Leg.</li> <li>3.1.1 10 kV SiC MOSFET.</li> <li>3.1.2 Architecture of the Phase Leg.</li> <li>3.2 Gate Driver Design</li></ul>                                                     | 46<br>46<br>47<br>49<br>51<br>54<br>56             |

| <ul> <li>3.1 Overview of the Phase Leg.</li> <li>3.1.1 10 kV SiC MOSFET.</li> <li>3.1.2 Architecture of the Phase Leg.</li> <li>3.2 Gate Driver Design</li></ul>                                                     | 46<br>46<br>47<br>51<br>54<br>56<br>64             |

| <ul> <li>3.1 Overview of the Phase Leg.</li> <li>3.1.1 10 kV SiC MOSFET.</li> <li>3.1.2 Architecture of the Phase Leg.</li> <li>3.2 Gate Driver Design</li></ul>                                                     | 46<br>46<br>47<br>51<br>54<br>56<br>64<br>64       |

| <ul> <li>3.1 Overview of the Phase Leg.</li> <li>3.1.1 10 kV SiC MOSFET.</li> <li>3.1.2 Architecture of the Phase Leg.</li> <li>3.2 Gate Driver Design</li></ul>                                                     | 46<br>46<br>47<br>51<br>54<br>56<br>64<br>64<br>69 |

| 4.1 Impact of Parasitic Capacitance in Load Inductor                    | 76       |

|-------------------------------------------------------------------------|----------|

| 4.2 Impact of Parasitic Capacitances Due to Heatsink                    | 85       |

| 4.3 Impact of Body Diode and Anti-parallel JBS Diode                    |          |

| 4.3.1 Device under Test and Experimental Setup                          |          |

| 4.3.3 Impact of Anti-parallel JBS Diode                                 | 100      |

| 4.4 Summary                                                             | 103      |

| CHAPTER 5. Analysis and Gate Driver Considerations of 10 kV SiC MOSFE   | Ts under |

| Flashover Fault                                                         | 105      |

| 5.1 Model of 10 kV SiC MOSFET                                           | 106      |

| 5.2 10 kV SiC MOSFET under Flashover Fault                              | 110      |

| 5.2.1 Flashover Fault and Simulation Model                              | 110      |

| 5.2.2 10 kV SiC MOSFET without Kelvin Source                            |          |

| 5.2.3 10 kV SiC MOSFET with Kelvin Source                               | 114      |

| 5.3 Gate Driver Design Considerations                                   | 116      |

| 5.3.1 10 kV SiC MOSFET without Kelvin Source                            | 117      |

| 5.3.2 10 kV SiC MOSFET with Kelvin Source                               | 119      |

| 5.3.3 Summary                                                           | 121      |

| 5.4 Short Circuit Energy Loss and Protection Design                     | 121      |

| 5.4.1 Simulation of FUL and HSF                                         | 121      |

| 5.4.2 Comparison between Flashover and FUL Fault                        | 123      |

| 5.4.3 Comparison between Flashover Fault and HSF Fault                  | 127      |

| 5.5 Summary                                                             | 129      |

| CHAPTER 6. Overcurrent Protection Design with Strong Noise Immunity and | l Fast   |

| Response                                                                | 130      |

| 6.1 Noise Immunity Analysis and Enhancement of Desat Protection         |          |

| 6.1.1. Overview of Desat Protection Circuitry                           | 131      |

| 6.1.2 Noise Immunity Analysis                                           | 133      |

| 6.1.3 Noise Immunity Improvement                                        | 152      |

| 6.1.4 Summary                                                           |          |

| 6.2 Improved Desat Protection with Digital Blanking Time                | 169      |

|                                                                         |          |

| 6.2.1 Working Principles                                         |           |

|------------------------------------------------------------------|-----------|

| 6.2.2 Implementation                                             | 172       |

| 6.2.3 Discussions of Response Time                               | 176       |

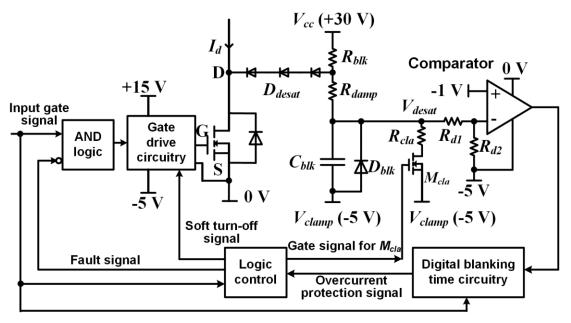

| 6.2.4 Experimental Results                                       | 178       |

| 6.3 Desat Protection with Ultrafast Response                     | 181       |

| 6.3.1 Working Principles                                         |           |

| 6.3.2 Design Details                                             |           |

| 6.3.3 Experimental Results                                       | 199       |

| 6.3.4 Discussion                                                 | 207       |

| 6.3.5 Summary                                                    | 210       |

| 6.4 Summary                                                      | 211       |

| CHAPTER 7. Comprehensive Test Scheme of a 10 kV SiC MOSFET Based | Phase Leg |

|                                                                  | 213       |

| 7.1 Overview of Test Scheme                                      | 213       |

| 7.1.1 Overview of ac-dc Continuous Test                          |           |

| 7.1.2 Modulation Scheme                                          |           |

| 7.2 Open-loop Voltage Balancing Scheme                           |           |

| 7.3 Simulation Results                                           | 222       |

| 7.4 Experimental Setup and Results                               | 224       |

| 7.5 Summary                                                      |           |

| CHAPTER 8. Conclusions and Future Work                           |           |

| 8.1 Conclusions                                                  |           |

| 8.2 Future Work                                                  | 236       |

| References                                                       |           |

| Vita                                                             | 250       |

# LIST OF TABLES

| Table 1. Material properties of Si and SiC for power electronic applications            | . 6 |

|-----------------------------------------------------------------------------------------|-----|

| Table 2. Specifications of the designed gate driver.                                    | 50  |

| Table 3. Specifications of the designed desat overcurrent protection.                   | 58  |

| Table 4. Distribution of the total response time in one gate driver prototype           | 63  |

| Table 5. Details of four steps in the systematic testing of the phase leg               | 65  |

| Table 6. Summary of the selected measurement setup for the DPT.                         | 77  |

| Table 7. Switching performance of Configuration A and B at 3 kV, 125 °C.                | 98  |

| Table 8. Measured resistance of body diode at different temperatures                    | 99  |

| Table 9. Switching performance comparison between Configuration B and Configuration     | m   |

| C at 3 kV/20 A                                                                          | 01  |

| Table 10. Gate driver design considerations from the standpoint of flashover fault 12   | 22  |

| Table 11. Summary of design guidelines to improve noise immunity of desat protection    |     |

| realized by a gate driver IC1                                                           | 53  |

| Table 12. Summary of selection and design guidelines for the comparator for noise       |     |

| immunity improvement1                                                                   | 56  |

| Table 13. Summary of design guidelines to improve noise immunity of desat protection    |     |

| based on discrete components10                                                          | 67  |

| Table 14. Summary of parameters of two desat protection designs with ultrafast response | se  |

|                                                                                         | 97  |

# LIST OF FIGURES

| Fig. 1- 1. Physical structure and current flow of IGBT and power MOSFET [1], [17] 4                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 1- 2. Device-level and converter-level benefits of 10 kV SiC MOSFETs [1]8                                                                         |

| Fig. 1- 3. Specific on-resistance vs. breakdown voltage for Si and SiC [30]                                                                            |

| Fig. 1- 4. Summary of challenges brought by 10 kV SiC MOSFETs 12                                                                                       |

| Fig. 2-1. Two circuit configurations used in DPT: (a) phase leg configuration; (b)                                                                     |

| switch/diode pair                                                                                                                                      |

| Fig. 2- 2. Switching energy loss as a function of external gate resistance (left) and drain                                                            |

| current (right) for the 3rd generation 10 kV SiC MOSFET at 150 °C [29] 21                                                                              |

| Fig. 2- 3. Detailed device model of 10 kV SiC MOSFET [44]                                                                                              |

| Fig. 2- 4. Turn-on and turn-off waveforms of the 10 kV SiC MOSFET at 25 $^\circ C$ [44] 23                                                             |

| Fig. 2- 5. Turn-on and turn-off waveforms of the 10 kV SiC MOSFET at 125 $^\circ C$ [44] 24                                                            |

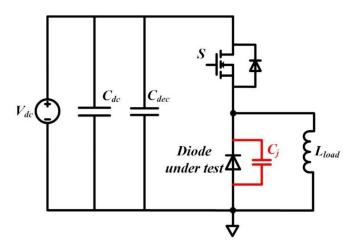

| Fig. 2- 6. Circuit diagram of DPT for diode reverse recovery characterization                                                                          |

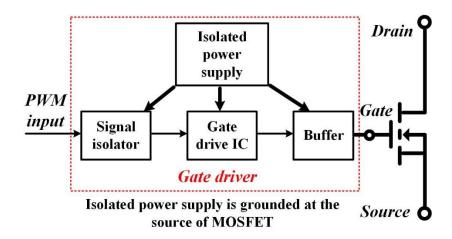

| Fig. 2-7. Basic function diagram of a gate driver for a power MOSFET [1]                                                                               |

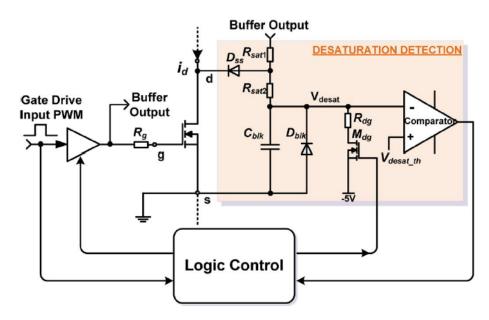

| Fig. 2- 8. Implementation of desat protection for SiC MOSFETs [66]                                                                                     |

|                                                                                                                                                        |

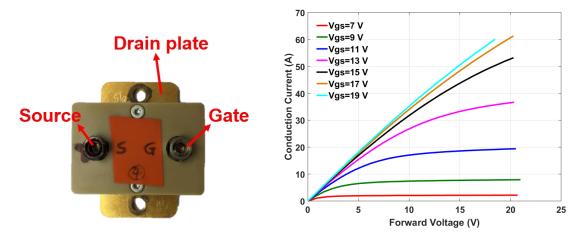

| Fig. 3- 1. Discrete 10 kV SiC MOSFET in the half bridge phase leg (left) and its forward                                                               |

|                                                                                                                                                        |

| Fig. 3- 1. Discrete 10 kV SiC MOSFET in the half bridge phase leg (left) and its forward                                                               |

| Fig. 3- 1. Discrete 10 kV SiC MOSFET in the half bridge phase leg (left) and its forward characteristic at room temperature (right)                    |

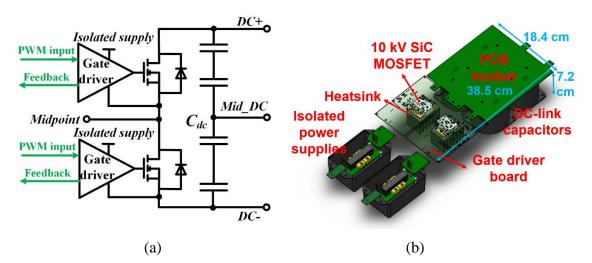

| <ul> <li>Fig. 3- 1. Discrete 10 kV SiC MOSFET in the half bridge phase leg (left) and its forward characteristic at room temperature (right)</li></ul> |

| <ul> <li>Fig. 3- 1. Discrete 10 kV SiC MOSFET in the half bridge phase leg (left) and its forward characteristic at room temperature (right)</li></ul> |

| <ul> <li>Fig. 3- 1. Discrete 10 kV SiC MOSFET in the half bridge phase leg (left) and its forward characteristic at room temperature (right)</li></ul> |

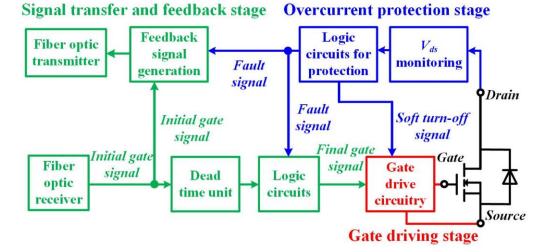

| <ul> <li>Fig. 3- 1. Discrete 10 kV SiC MOSFET in the half bridge phase leg (left) and its forward characteristic at room temperature (right)</li></ul> |

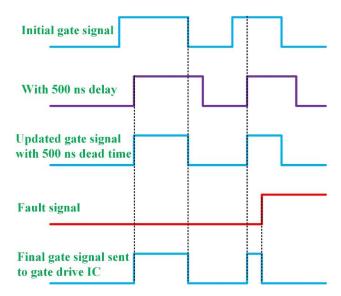

| <ul> <li>Fig. 3- 1. Discrete 10 kV SiC MOSFET in the half bridge phase leg (left) and its forward characteristic at room temperature (right)</li></ul> |

| <ul> <li>Fig. 3- 1. Discrete 10 kV SiC MOSFET in the half bridge phase leg (left) and its forward characteristic at room temperature (right)</li></ul> |

| <ul> <li>Fig. 3- 1. Discrete 10 kV SiC MOSFET in the half bridge phase leg (left) and its forward characteristic at room temperature (right)</li></ul> |

| Fig. 3- 8. Output characteristic of the 10 kV /20 A SiC MOSFET under different              |

|---------------------------------------------------------------------------------------------|

| temperatures                                                                                |

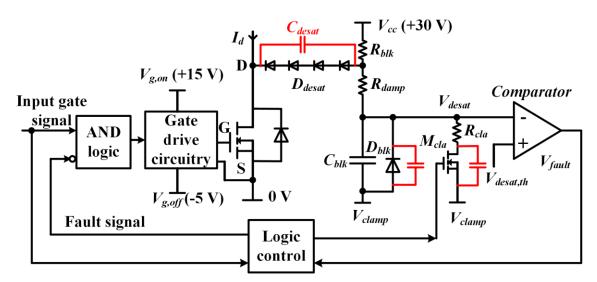

| Fig. 3- 9. Implementation of desat protection in the gate driver for 10 kV SiC MOSFETs.     |

|                                                                                             |

| Fig. 3- 10. Turn-on transient of the 10 kV SiC MOSFET at 6.25 kV/20 A                       |

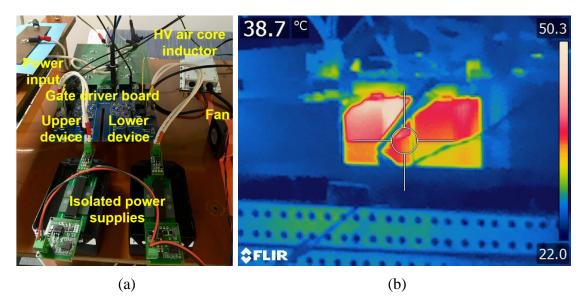

| Fig. 3- 11. Circuit diagram of the continuous test of the designed phase leg                |

| Fig. 3- 12. (a) Phase leg prototype in the high voltage test platform; (b) Thermal image of |

| the phase leg prototype during 6 kV ac-dc continuous test                                   |

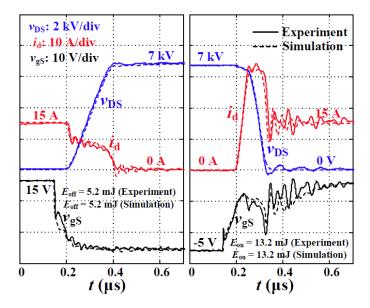

| Fig. 3- 13. HSF short circuit test waveforms: (a) Lower device in the phase leg; (b) Upper  |

| device in the phase leg                                                                     |

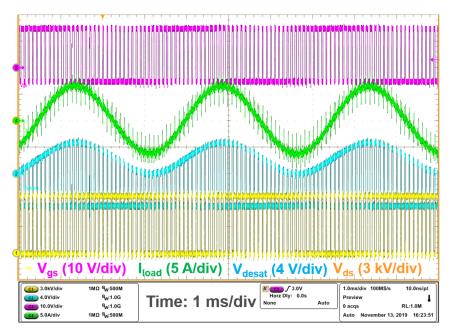

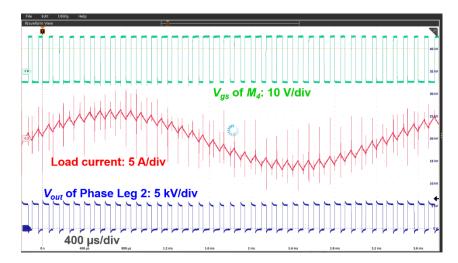

| Fig. 3- 14. Zoom-in waveform of the continuous test of the phase leg at 6.5 kV              |

|                                                                                             |

| Fig. 4-1. Three major sources of the parasitic capacitance in the power stage [1]75         |

| Fig. 4- 2. Circuit diagram of the DPT based on the designed half bridge phase leg 75        |

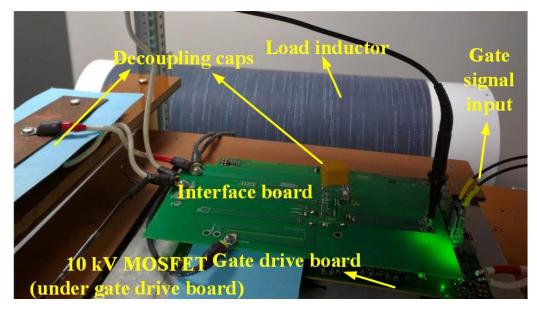

| Fig. 4- 3. DPT test setup based on the designed half bridge phase leg together with         |

| measurement setup77                                                                         |

| Fig. 4- 4. High voltage load inductor with external capacitor to increase its EPC79         |

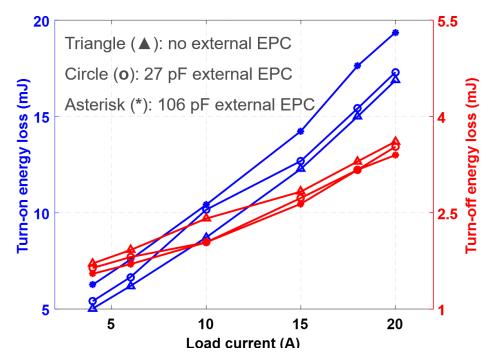

| Fig. 4- 5. Turn-on and turn-off energy loss at 6.25 kV when load inductor has different     |

| EPCs                                                                                        |

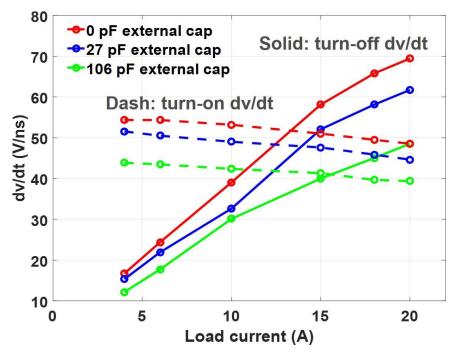

| Fig. 4- 6. Turn-on and turn-off $dv/dt$ at 6.25 kV when the load inductor has different     |

| EPCs                                                                                        |

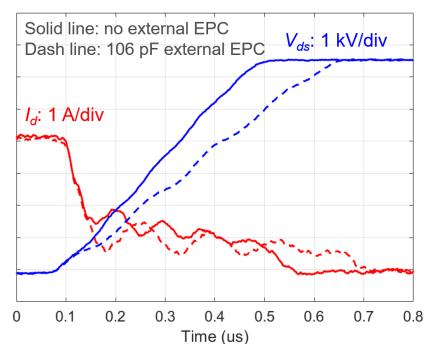

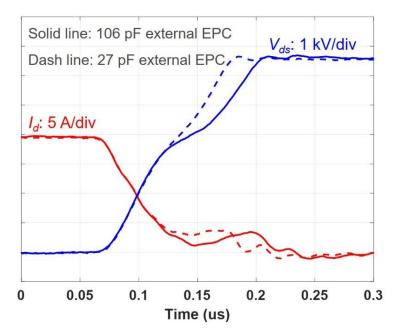

| Fig. 4- 7. Turn-off transient waveform at 6.25 kV when load inductor has different EPCs.    |

|                                                                                             |

| Fig. 4- 8. Turn-off transient waveform at 6.25 kV/20 A when the load inductor has           |

| different EPCs                                                                              |

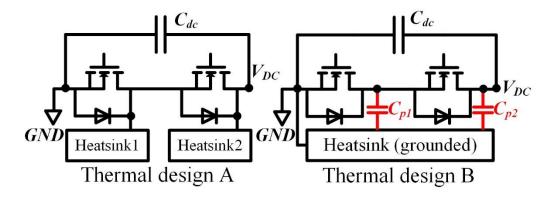

| Fig. 4- 9. Two thermal designs implemented in the half bridge phase leg                     |

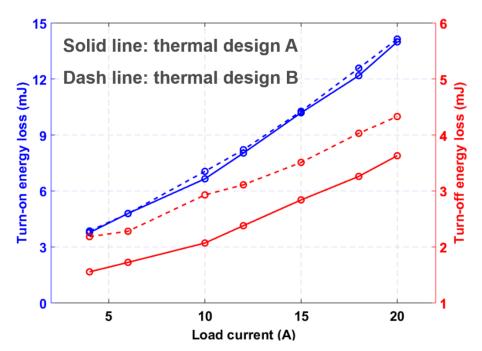

| Fig. 4- 10. Comparison of turn-on and turn-off energy loss between the thermal design A     |

| and B at 6.25 kV                                                                            |

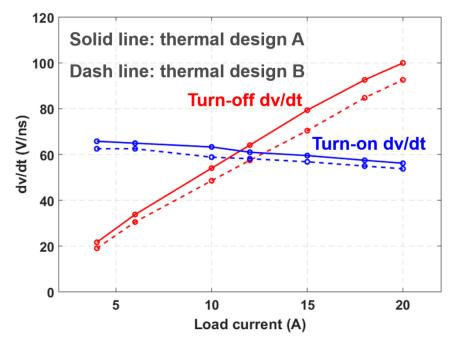

| Fig. 4- 11. Comparison of turn-on and turn-off $dv/dt$ between thermal design A and B at    |

| 6.25 kV                                                                                     |

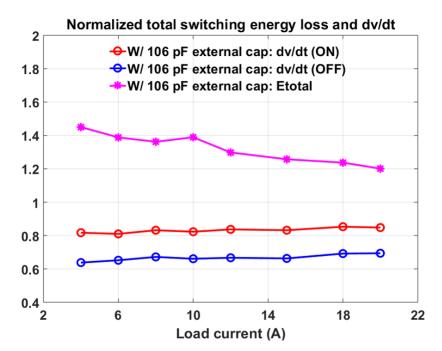

| Fig. 4- 12. Impact of the 106 pF parasitic capacitance due to heatsink on the switching                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| energy loss and $dv/dt$ (Normalized based on data from thermal design A)                                                                     |

| Fig. 4- 13. 10 kV SiC MOSFET module (H-bridge) packaged by Danfoss                                                                           |

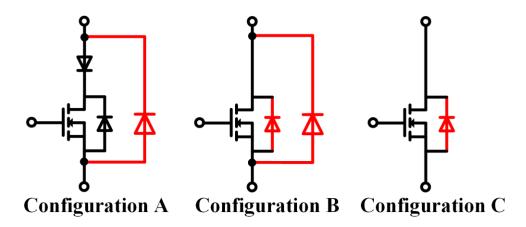

| Fig. 4- 14. Three device configurations for one switch available in the 10 kV SiC                                                            |

| MOSFET module                                                                                                                                |

| Fig. 4- 15. Picture of DPT setup to evaluate the impact of body diode and anti-parallel                                                      |

| JBS diode95                                                                                                                                  |

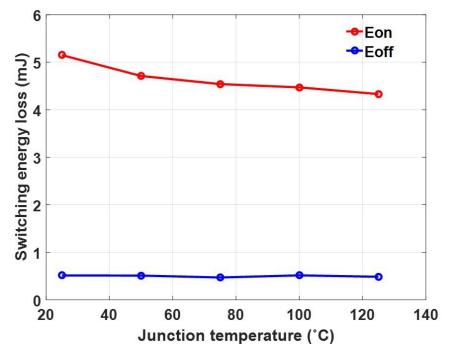

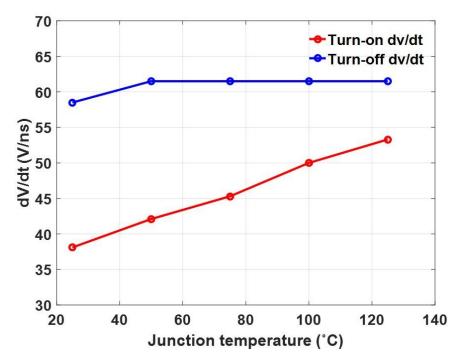

| Fig. 4- 16. Switching energy loss vs. temperature (Configuration C, 3 kV/20 A)                                                               |

| Fig. 4- 17. Turn-on and turn-off <i>dv/dt</i> vs. temperature (Configuration C, 3 kV/20 A) 96                                                |

| Fig. 4- 18. Switching transient waveforms of Configuration A and B at 75 °C (3 kV, 10                                                        |

| A)                                                                                                                                           |

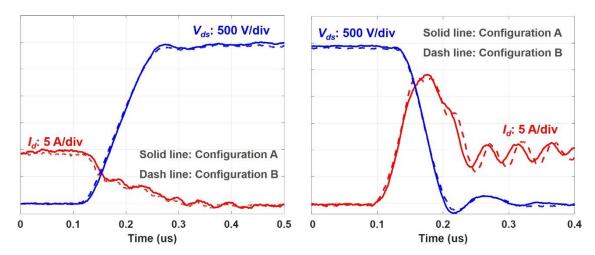

| Fig. 4- 19. Switching transient waveforms of Configuration B and C at 125 °C 101                                                             |

|                                                                                                                                              |

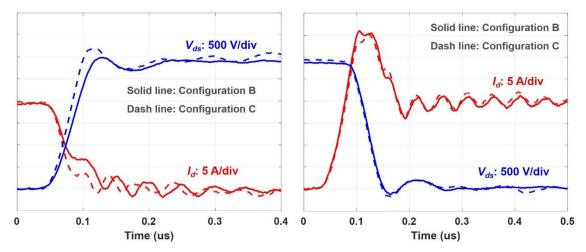

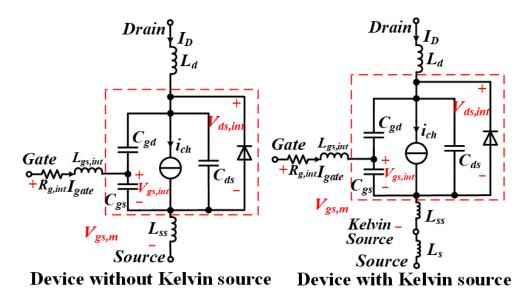

| Fig. 5-1. Equivalent circuit of the established 10 kV SiC MOSFET model 107                                                                   |

| Fig. 5- 2. Circuit model of the 10 kV SiC MOSFET in ON state under flashover fault                                                           |

| modeled by closing an ideal switch                                                                                                           |

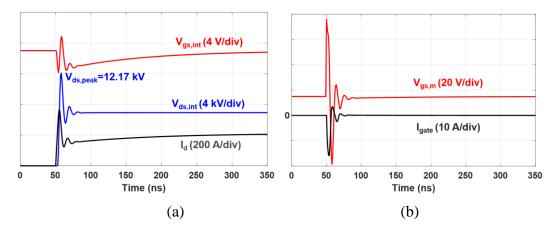

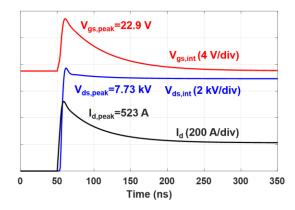

| Fig. 5- 3. Simulation waveforms of flashover fault at 7 kV with 1 nH common source                                                           |

| inductance $L_{ss}$ , 15 $\Omega$ $R_{g,on}$ , and 2.5 $\Omega$ $R_{g,off}$ : (a) Waveforms of $V_{ds,int}$ , $I_d$ , and $V_{gs,int}$ ; (b) |

| Waveforms of $V_{gs,m}$ and gate current $I_{gate}$                                                                                          |

| Fig. 5- 4. Flashover fault simulation results at 7 kV with 1 nH $L_{ss}$ , 15 $\Omega R_{g,on}$ , and 0 $\Omega$                             |

| $R_{g,off}$ : (a) Waveforms of $V_{ds,int}$ , $I_d$ , and $V_{gs,int}$ ; (b) Waveforms of $V_{gs,m}$ and $I_{gate}$ 115                      |

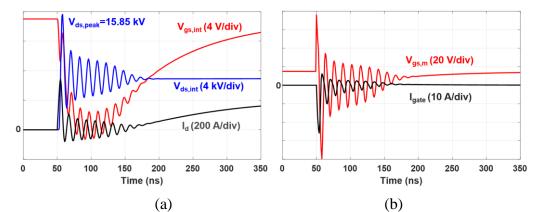

| Fig. 5- 5. Simulation waveforms of flashover fault at 7 kV with 0.15 nH $L_{ss}$ and 15 $\Omega$                                             |

| $R_{g,on}$ : (a) 0 $\Omega$ $R_{g,off}$ . (b) 2.5 $\Omega$ $R_{g,off}$                                                                       |

| Fig. 5- 6. Simulation waveforms of flashover fault at 7 kV with 1 nH $L_{ss}$ : (a) 15 $\Omega R_{g,on}$                                     |

| and 7.5 $\Omega R_{g,off}$ , (b) 15 $\Omega R_{g,on}$ and 2.5 $\Omega R_{g,off}$ as well as a 500 pF external capacitor.                     |

|                                                                                                                                              |

| Fig. 5-7. Simulation waveforms of flashover fault at 7 kV with 0.15 nH $L_{ss}$ , 15 $\Omega R_{g,on}$                                       |

| and 7.5 $\Omega R_{g,off.}$                                                                                                                  |

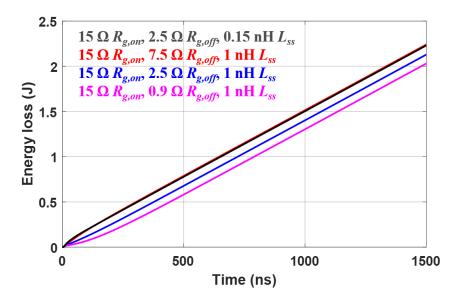

| Fig. 5-8. Short circuit energy loss under flashover fault at 7 kV with different gate                                                        |

| resistances and common source inductance                                                                                                     |

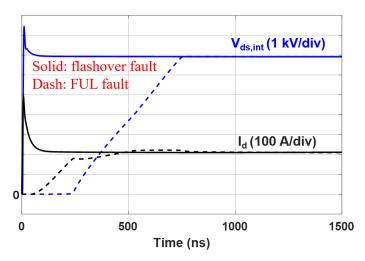

| Fig. 5-9. Simulation waveforms of FUL and flashover fault at 7 kV with 0.15 nH L <sub>ss</sub> , 15    |

|--------------------------------------------------------------------------------------------------------|

| $\Omega R_{g,on}$ , and 2.5 $\Omega R_{g,off}$                                                         |

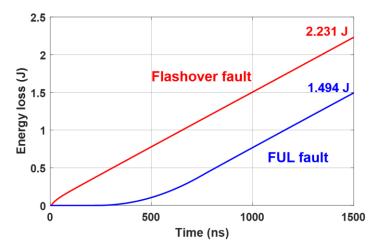

| Fig. 5- 10. Short circuit energy loss comparison between FUL and flashover fault at 7 $\rm kV$         |

| with 0.15 nH $L_{ss}$ , 15 $\Omega$ $R_{g,on}$ , and 2.5 $\Omega$ $R_{g,off}$                          |

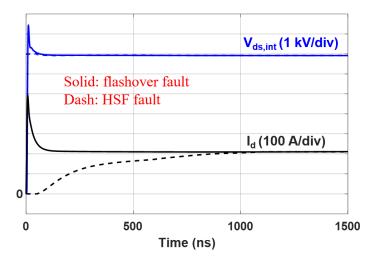

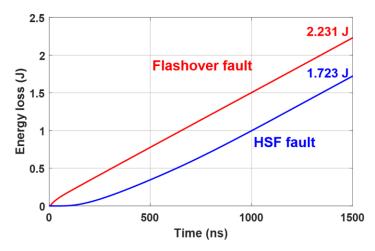

| Fig. 5-11. Simulation waveforms of HSF and flashover fault at 7 kV with 0.15 nH L <sub>ss</sub> , 15   |

| $\Omega R_{g,on}$ , and 2.5 $\Omega R_{g,off}$                                                         |

| Fig. 5-12. Short circuit energy loss comparison between HSF fault and flashover fault at               |

| 7 kV with 0.15 nH $L_{ss}$ , 15 $\Omega$ $R_{g,on}$ , and 2.5 $\Omega$ $R_{g,off}$                     |

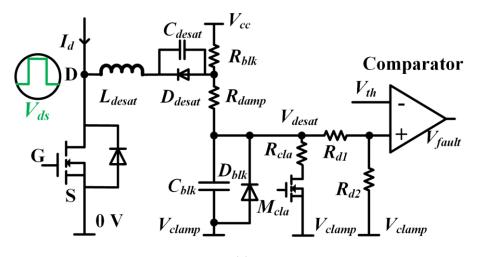

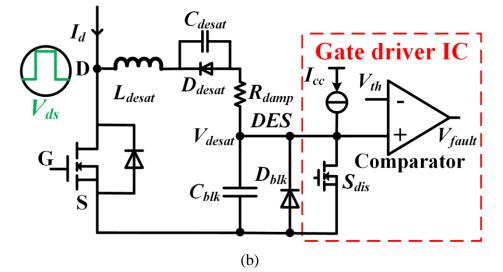

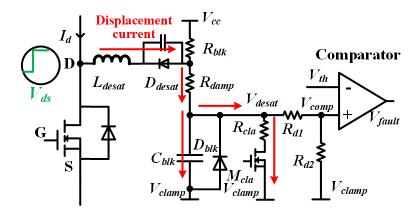

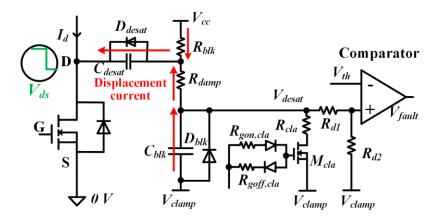

| Fig. 6-1. Two implementations of desat protection for high voltage SiC MOSFETs: (a)                    |

| Based on discrete components; (b) Realized with gate driver IC 132                                     |

| Fig. 6- 2. Displacement current due to $C_{desat}$ and positive $dv_{ds}/dt$ in desat protection       |

| circuitry                                                                                              |

| Fig. 6-3. Displacement current caused by $C_{desat}$ and negative $dv_{ds}/dt$ in desat protection     |

| circuitry                                                                                              |

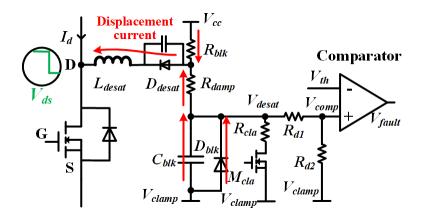

| Fig. 6- 4. Desat protection for 10 kV/20 A SiC MOSFET from Wolfspeed 136                               |

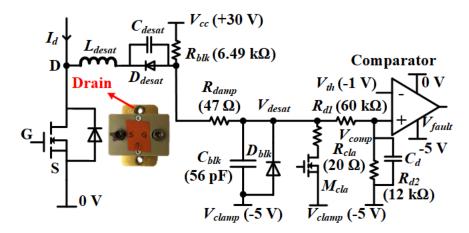

| Fig. 6- 5. Simulation waveforms of desat protection for $10 \text{ kV}/20 \text{ A SiC MOSFETs}$ : (a) |

| $C_{blk}$ =56 pF; (b) $C_{blk}$ =20 pF                                                                 |

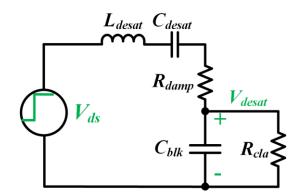

| Fig. 6- 6. Simplified circuit model for the analysis of V <sub>desat</sub>                             |

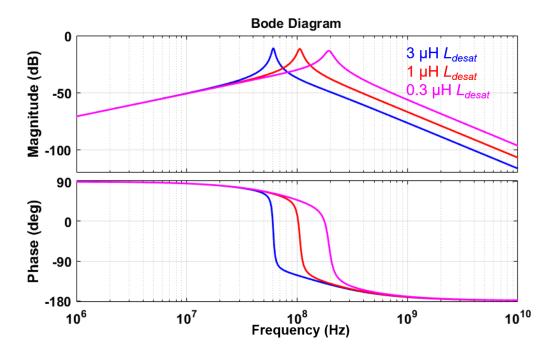

| Fig. 6-7. Bode plot of $V_{desat}(s)/V_{ds}(s)$ as $L_{desat}$ increases (parameters in Fig. 6-4)      |

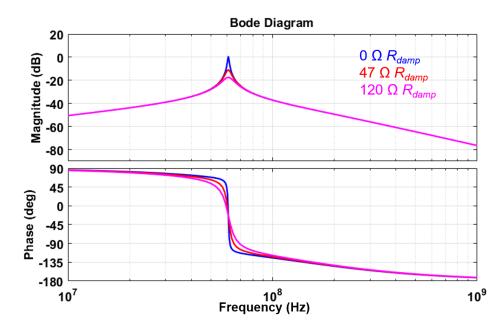

| Fig. 6-8. Bode plot of $V_{desat}(s)/V_{ds}(s)$ as $R_{damp}$ increases ( $L_{desat}=3 \mu H$ )        |

| Fig. 6-9. Desat protection circuitry considering parasitic capacitances between drain and              |

| protection circuitry144                                                                                |

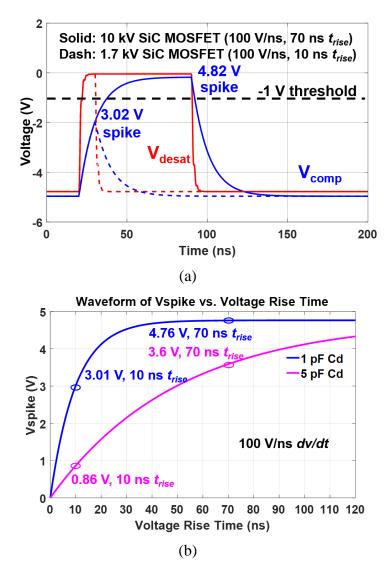

| Fig. 6-10. (a) Simulation results of $V_{desat}$ and $V_{comp}$ with 0.004 pF $C_{p3}$ and 1 pF $C_d$  |

| considered for 10 kV and 1.7 kV SiC MOSFETs with 100 V/ns dv/dt; (b)                                   |

| Calculation result of $V_{spike}$ as a function of $t_{rise}$                                          |

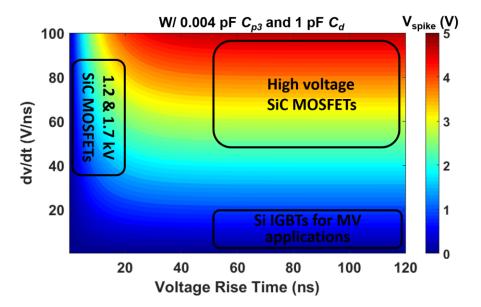

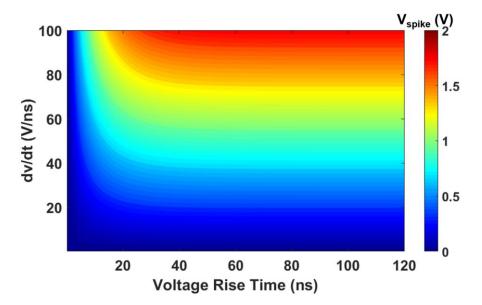

| Fig. 6-11. Contour plot of $V_{spike}$ as a function of $dv/dt$ and voltage rise time $t_{rise}$       |

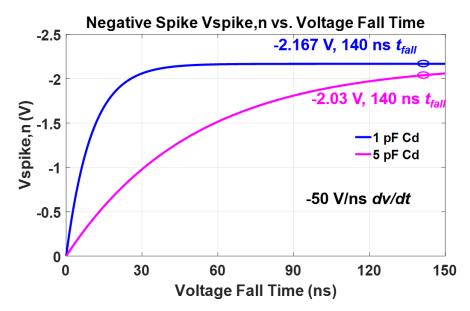

| Fig. 6-12. Calculation result of $V_{spike,n}$ under the negative $dv/dt$ (-50 V/ns)                   |

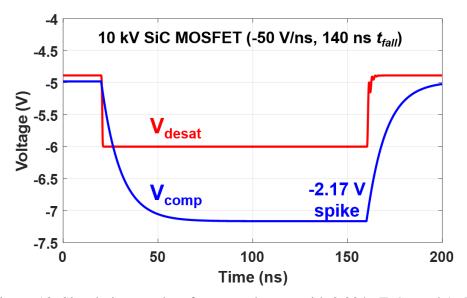

| Fig. 6-13. Simulation results of $V_{desat}$ and $V_{comp}$ with 0.004 pF $C_{p3}$ and 1 pF $C_{d}$    |

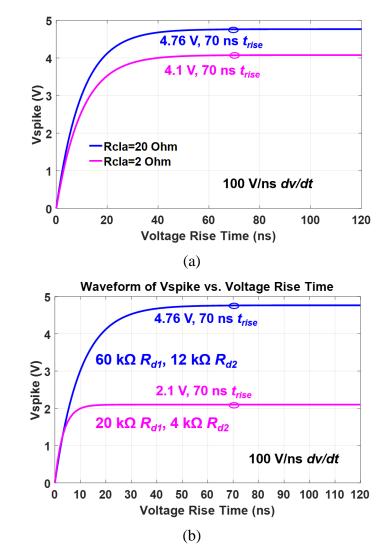

| Fig. 6- 14. Calculation result of $V_{spike}$ as a function of $t_{rise}$ : (a) Impact of $R_{cla}$ ; (b) Impact |

|------------------------------------------------------------------------------------------------------------------|

| of voltage divider impedance                                                                                     |

| Fig. 6-15. Contour plot of $V_{spike}$ as a function of $dv/dt$ and $t_{rise}$ (0.001 pF $C_{p3}$ )              |

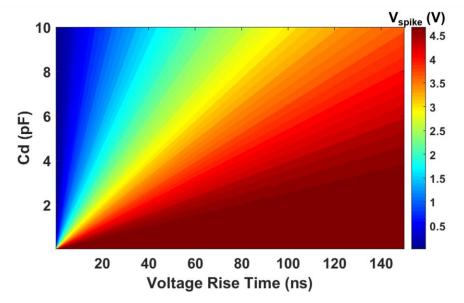

| Fig. 6- 16. Contour plot of $V_{spike}$ as a function of $C_d$ and $t_{rise}$ (0.004 pF $C_{p3}$ ; 100 V/ns      |

| <i>dv/dt</i> )                                                                                                   |

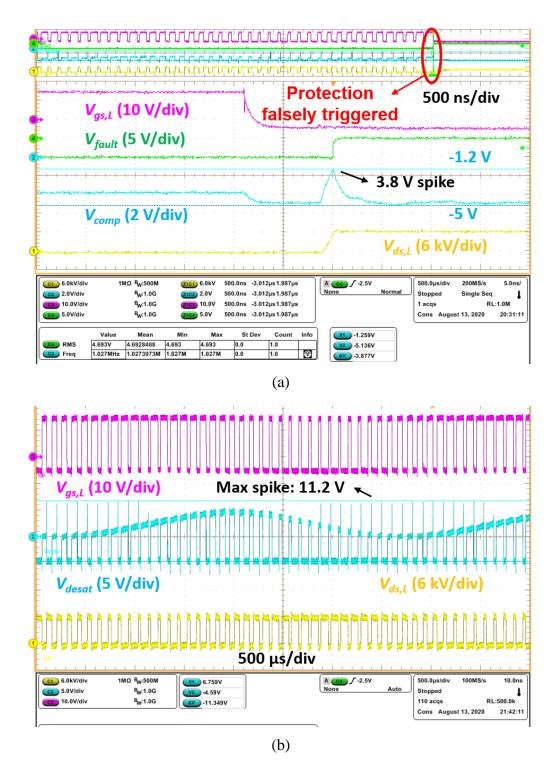

| Fig. 6- 17. Waveforms of 6 kV continuous ac-dc test of a phase leg based on 10 kV SiC                            |

| MOSFETs with desat protection in Fig. 6-4160                                                                     |

| Fig. 6- 18.Waveforms of 6 kV continuous ac-dc test of a phase leg based on 10 kV SiC                             |

| MOSFETs with 90 $\Omega R_{cla}$ . (a) Waveform of $V_{comp}$ when desat protection is falsely                   |

| triggered. (b) Waveform of $V_{desat}$                                                                           |

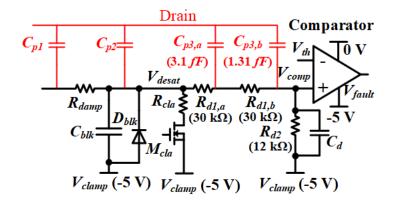

| Fig. 6- 19. Details of capacitive coupling between the voltage divider in the desat                              |

| protection circuitry and the drain terminal of the 10 kV SiC MOSFET 163                                          |

| Fig. 6- 20. Waveforms of 6 kV continuous ac-dc test of a phase leg with 90 $\Omega R_{cla}$ and an               |

| external shielding layer installed                                                                               |

| Fig. 6-21. Waveforms of $V_{comp}$ of new desat protection board with improved noise                             |

| immunity: (a) 6 kV ac-dc continuous test; (b) 7 kV ac-dc continuous test                                         |

| Fig. 6- 22. Improved desat protection in the gate driver for 10 kV SiC MOSFETs 170                               |

| Fig. 6-23. Implementation details of 600 ns digital blanking time                                                |

| Fig. 6- 24. (a) Detailed 3D design of the phase leg. (b) Prototype of half bridge phase leg                      |

| with improved desat protection in high voltage test platform                                                     |

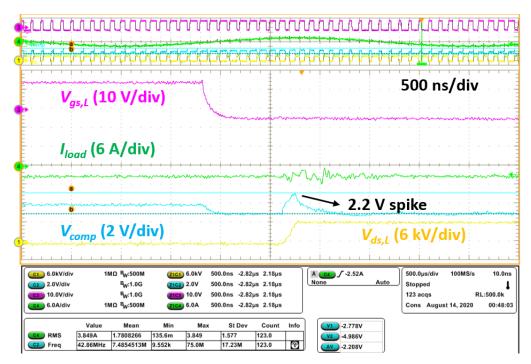

| Fig. 6- 25. HSF short circuit test waveform of lower MOSFET in the phase leg 179                                 |

| Fig. 6- 26. FUL short circuit test waveform of lower MOSFET in the phase leg 179                                 |

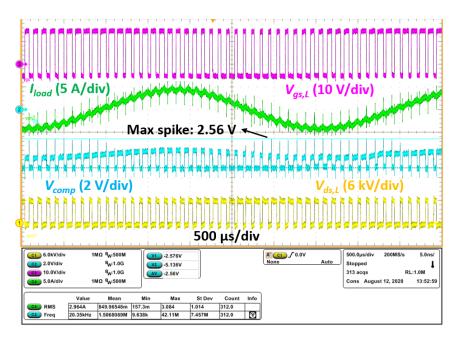

| Fig. 6- 27. Waveforms of ac-dc continuous test at 6.5 kV                                                         |

| Fig. 6- 28. Circuit diagram of desat protection with ultrafast response for 10 kV/20 A SiC                       |

| MOSFET                                                                                                           |

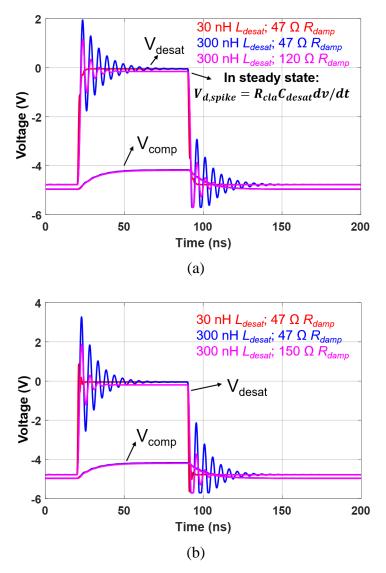

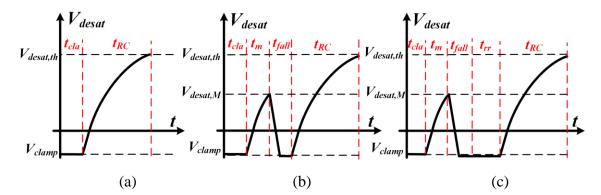

| Fig. 6- 29. Waveforms of $V_{desat}$ during blanking time: (a) impact of high $dv/dt$ neglected;                 |

| (b) reverse recovery process neglected; (c) both high $dv/dt$ and reverse recovery                               |

| considered                                                                                                       |

| Fig. 6- 30. Waveform of $V_{desat}$ during 6 kV ac-dc continuous test (with $D_{blk}$ , 56 pF $C_{blk}$ ,        |

| $6.5 \text{ k}\Omega R_{blk}, 470 \Omega R_{goff,cla}).$                                                         |

|                                                                                                                  |

| Fig. 6- 31. Waveform of V <sub>desat</sub> during 6 kV ac-dc continuous test (without D <sub>blk</sub> , 56 pF |

|----------------------------------------------------------------------------------------------------------------|

| $C_{blk}$ , 6.5 k $\Omega$ $R_{blk}$ , 470 $\Omega$ $R_{goff,cla}$ )                                           |

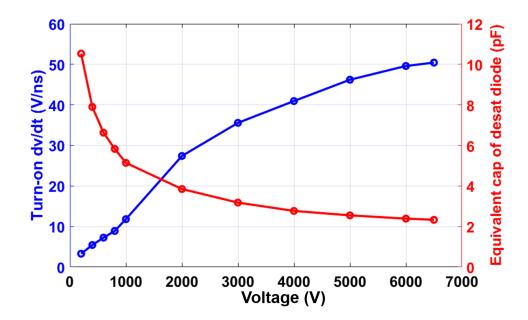

| Fig. 6- 32. Turn-on <i>dv/dt</i> (at 5 A and 25 °C) of 10 kV/20 A SiC MOSFETs and equivalent                   |

| capacitance of desat diode at different voltage levels                                                         |

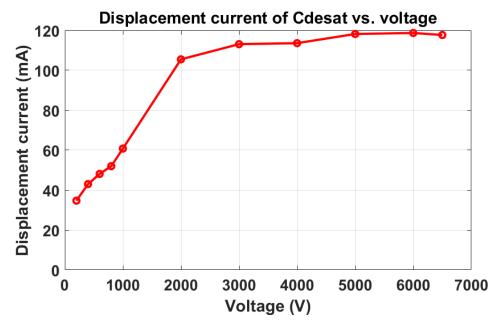

| Fig. 6- 33. Displacement current flowing through desat diode ( $C_{desat}dv/dt$ , calculated                   |

| based on data in Fig. 6-32) at different voltage levels                                                        |

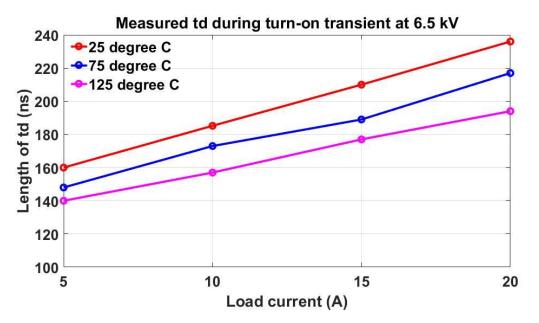

| Fig. 6- 34. Measured $t_d$ during the turn-on transient of the 10 kV/20 A SiC MOSFET at                        |

| 6.5 kV dc bus voltage                                                                                          |

| Fig. 6- 35. Waveforms of $V_{ds}$ during the turn-on transient of the 10 kV/20 A SiC                           |

| MOSFET at different dc voltage levels (at 10 A and 25 °C) 195                                                  |

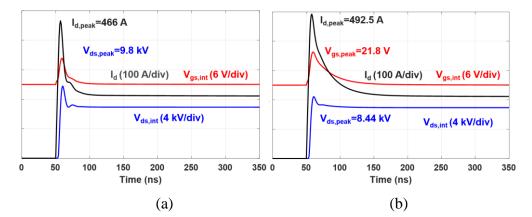

| Fig. 6- 36. HSF short circuit test waveform of 10 kV SiC MOSFET with desat protection                          |

| design 1 with ultrafast response                                                                               |

| Fig. 6- 37. FUL short circuit test waveform of 10 kV SiC MOSFET with desat protection                          |

| design 1 with ultrafast response                                                                               |

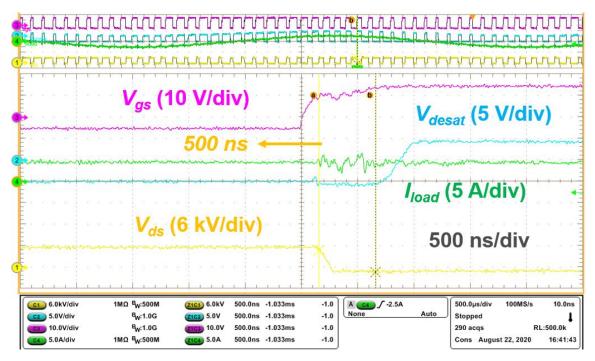

| Fig. 6- 38. Waveforms captured during 6.6 kV ac-dc continuous test with desat protection                       |

| design 1 with ultrafast response                                                                               |

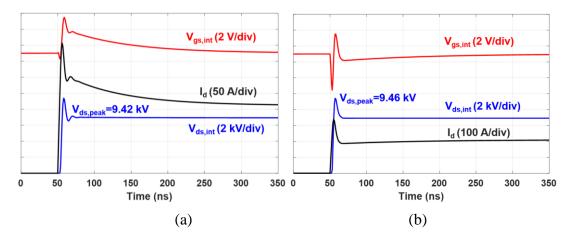

| Fig. 6- 39. HSF short circuit test waveform of 10 kV SiC MOSFET with desat protection                          |

| design 2 with ultrafast response                                                                               |

| Fig. 6- 40. FUL short circuit test waveform of 10 kV SiC MOSFET with desat protection                          |

| design 2 with ultrafast response                                                                               |

| Fig. 6- 41. Waveforms captured during 6.6 kV ac-dc continuous power test with desat                            |

| protection design 2 with ultrafast response                                                                    |

| Fig. 6- 42. Typical waveforms of $V_{ds}$ under HSF, FUL, and flashover fault                                  |

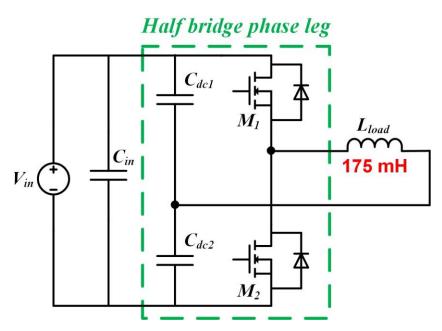

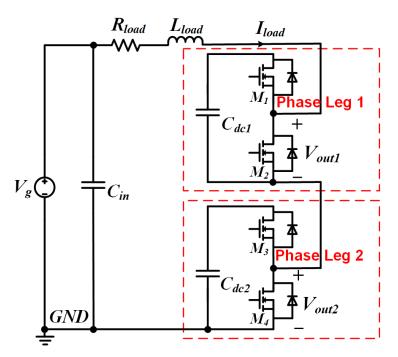

| Fig. 7-1. Circuit diagram of the proposed ac-dc continuous test circuit for the                                |

| qualification of half bridge phase legs                                                                        |

| Fig. 7- 2. (a) DC circuit model of the two phase legs used to study $V_{offset}$ . (b) DC circuit              |

| model of the two phase legs after adding a resistor in parallel with the capacitor. 221                        |

|                                                                                                                |

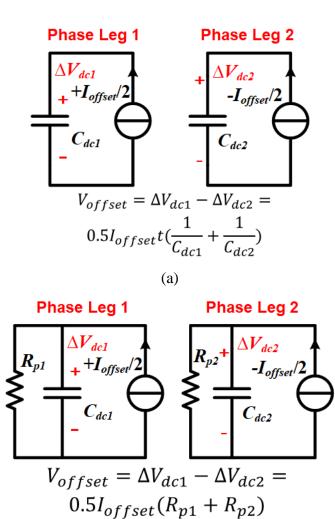

| Fig. | 7-3. Simulated waveforms of load voltage and load current at 6 kV dc-link voltage                             |

|------|---------------------------------------------------------------------------------------------------------------|

|      | (modulation index <i>m</i> =0.25, $R_{load} = 1 \Omega$ , $L_{load} = 175$ mH): (a) Overview ( $V_g$ ramps up |

|      | from 0 to 6 kV within 0.15 s); (b) Zoom-in waveforms                                                          |

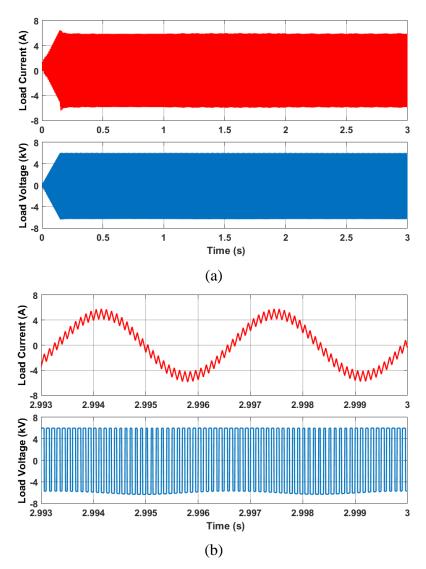

| Fig. | 7-4. Simulated phase leg voltage waveforms (modulation index $m=0.25$ , $V_g=6$ kV,                           |

|      | $R_{load} = 1 \Omega$ , $L_{load} = 175$ mH): (a) Without parallel resistor for voltage balancing; (b)        |

|      | With a 100 k $\Omega$ parallel resistor for voltage balancing                                                 |

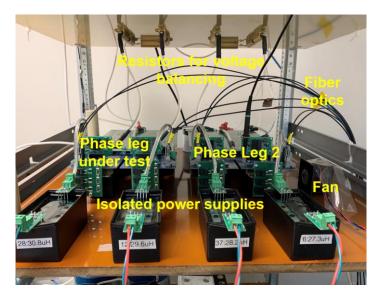

| Fig. | 7-5. Experimental setup of the ac-dc continuous test circuit: (a) Zoom-in view of the                         |

|      | two cascaded phase legs; (b) Overview of the whole test setup (the load inductor is                           |

|      | not visible)                                                                                                  |

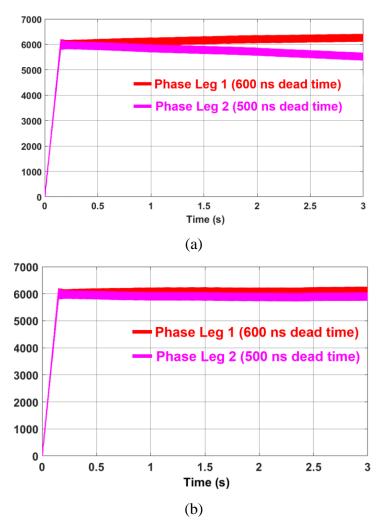

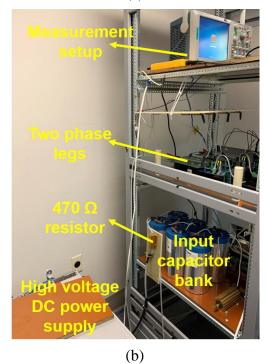

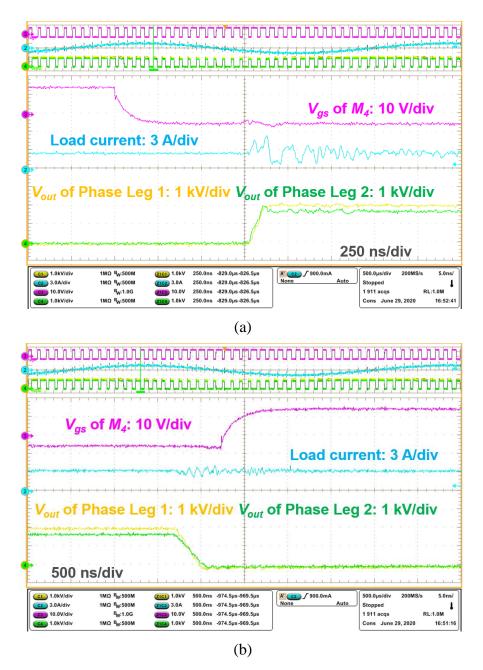

| Fig. | 7-6. Waveforms of the continuous test with the proposed ac-dc continuous test                                 |

|      | circuit at 2.1 kV                                                                                             |

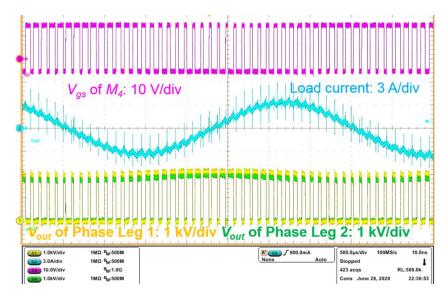

| Fig. | 7-7: Zoom-in waveforms of the continuous test with the proposed ac-dc continuous                              |

|      | test circuit at 2.1 kV: (a) Phase leg output voltage rises; (b) Phase leg output voltage                      |

|      | decreases                                                                                                     |

| Fig. | 7-8: Waveforms of the continuous test with the proposed ac-dc continuous test                                 |

|      | circuit at 6 kV                                                                                               |

### **CHAPTER 1. INTRODUCTION**

This chapter provides an overview of the research presented in this dissertation, including the background, motivations, objectives, and outline of this dissertation. It should be noted that part of the content in this chapter is from the author's Master's thesis titled *Design and Switching Performance Evaluation of a 10 kV SiC MOSFET Based Phase Leg for Medium Voltage Applications* [1].

#### **1.1 Modular Medium Voltage Converters**

Nowadays, power electronics converters with high power conversion efficiency are playing an indispensable part as the essential infrastructure for our society. Particularly, medium voltage (MV, from 1 to 35 kV AC) power converters with high power rating are required to support numerous critical and fundamental applications, including MV motor drives [2] and the modern grid.

MV motor drives are indispensable driving forces in industrial, transportation, and military applications. With the same power rating, MV motor drives achieve lower losses and higher power density compared to low voltage drives [3]. Motors and their drives consume a large percentage of electricity supplied to the industry, hence MV drives with higher efficiency and better performance are promising to make a profound difference in terms of reducing the manufacturing cost and accelerating decarbonization of the industry all over the world.

MV power converters have a wide range of applications in the modern power grid. Various MV converters are needed to support grid operation, such as solid state circuit breaker and fault current limiter for protection [4], [5], active power filter (APF) for improved power quality [6], static synchronous compensator (STATCOM), and unified power flow controller [7]. New MV converters for grid applications have also been developed to achieve more advanced functions, such as solid-state transformer [8] and continuously variable series reactor [9]. MV converters can interface renewable energy sources with the grid efficiently due to fewer stages and less complicated structure, hence drawing increasing attention as the capacity of the installed renewable energy sources keeps soaring. MV dc transmission system enabled by MV converters is promising in interfacing utility-level solar farms and offshore wind farms to the grid with lower cost and higher efficiency [1], [10]. MV power conditioning system (PCS) is essential to realize novel system configurations in distribution grids, including working as the interface of a microgrid to form an asynchronous microgrid, which benefits the microgrid on dynamic decoupling, resilience promotion, and other aspects [11]-[13]. Besides asynchronous microgrids, the MV PCS can be applied in combined heat and power system, flexible manufacturing plants to improve the system flexibility and assist renewable energy integration [14].

Among various MV converters, modular MV converters with modular topology stand out due to reduced complexity in converter design and debugging and easy extension to higher voltage level. Modular multi-level converter (MMC), cascaded H-bridge converter, and other modular topologies composed of many identical modules, have been gaining increasing popularity in MV converters [11], [15]. In MV applications with relatively high voltage and high power rating, topologies which are not modular, such as flying capacitor multi-level converter and neutral point clamped multilevel converter, are less competitive compared to modular MV converters. With reduced complexity and inherent scalability, modular MV converters have extraordinary potential to benefit a great variety of MV applications at different voltage levels [16].

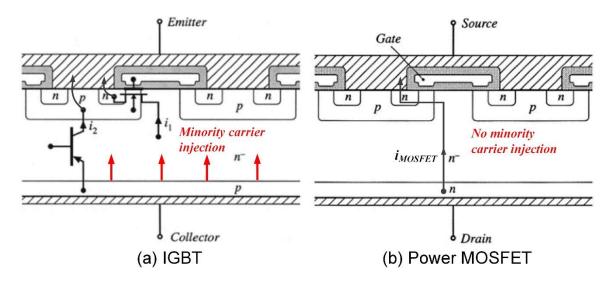

Si-based power semiconductor devices dominate in current MV converters, including IGBTs, thyristors, integrated gate-commutated thyristors (IGCTs), and gate turn-off thyristors (GTOs) [1]. The Si IGBT shown in Fig. 1-1 is prevalent in MV converters because of simple gate driver design and relatively high switching frequency. Thyristors, GTOs, and IGCTs are usually only considered for extremely high power applications, due to their low conduction loss at large current. Si MOSFETs shown in Fig.1-1, typically with lower switching loss than Si IGBTs, are not suitable in MV converters, suffering from exceptionally large conduction loss [1], [17].

However, Si IGBTs have gradually become the bottleneck in the development of high-performance MV converters [1]. The limitations of Si IGBTs for MV applications include relatively low blocking voltage, high switching loss, and low switching frequency [1]. The design and fabrication process of Si IGBTs are mature and approaching the limit of Si material. Power semiconductor devices with higher blocking voltage are highly desirable, yet the voltage rating of Si IGBTs commercially available for MV applications is limited to 6.5 kV, due to the conduction loss. Also, because of current  $i_2$  in Fig. 1-1(a) that cannot be actively shut down and the resulting tail current, it is difficult to further reduce the switching loss of Si IGBTs [17]. Therefore, the switching frequency of MV converters based on 6.5 kV Si IGBTs is usually limited to 1 kHz. In summary, Si IGBTs

Fig. 1- 1. Physical structure and current flow of IGBT and power MOSFET [1], [17].

with limited blocking voltage and low switching frequency are not suitable for future highperformance MV converters [1].

Recently, the rapid development of silicon carbide (SiC) material for power electronics applications has laid a solid foundation for better power semiconductor devices for MV applications. As displayed in Table 1, with much wider bandgap than Si, SiC has superior material properties relevant to power electronics applications, such as electric breakdown field, saturated electron drift velocity, and thermal conductivity [1], [18], [19]. SiC has several different polymorphic crystalline structures, and only 4H-SiC is considered and discussed in this dissertation because it has the best prospect in practical power electronics applications [20].

Excellent material properties of SiC bring the SiC power semiconductor devices higher blocking voltage, higher operation temperature, and potential for higher switching frequency. Tremendous progress has been made in SiC power semiconductor devices, resulting in a wide range of high voltage (>3.3 kV) SiC power semiconductor devices designed and produced for MV applications, including junction barrier Schottky (JBS) diode, MOSFET, IGBT, thyristor, etc [1], [21]-[25]. Due to the ten times higher critical electric field of SiC material, high voltage SiC devices can achieve much higher voltage rating than their Si counterparts [23]. With rated voltage ranging from 6.5 kV to 20 kV, these emerging SiC devices leveraging the superior characteristics of SiC material provide an unprecedented opportunity to expand what can be accomplished with MV converters.

### 1.2 10 kV SiC MOSFETs for MV Applications

The 10 kV SiC MOSFET is one of the most promising high voltage SiC power

| Properties                        | Silicon (Si)                       | Silicon Carbide (SiC)                                                               |

|-----------------------------------|------------------------------------|-------------------------------------------------------------------------------------|

| Bandgap                           | 1.12 eV                            | 3.26 eV                                                                             |

| Electric breakdown field          | 0.3 MV/cm                          | 2.0 MV/cm                                                                           |

| Thermal conductivity              | 1.5 W/cm-K                         | 4.9 W/cm-K                                                                          |

| Electron mobility                 | 1500 cm <sup>2</sup> /V-s          | 950 cm <sup>2</sup> /V-s (along a-axis)<br>1190 cm <sup>2</sup> /V-s (along c-axis) |

| Saturated electron drift velocity | $1.0 \text{ x } 10^7 \text{ cm/s}$ | $1.0 \text{ x } 10^7 \text{ cm/s}$                                                  |

| Dielectric constant               | 11.8                               | 10.0                                                                                |

Table 1. Material properties of Si and SiC for power electronic applications.

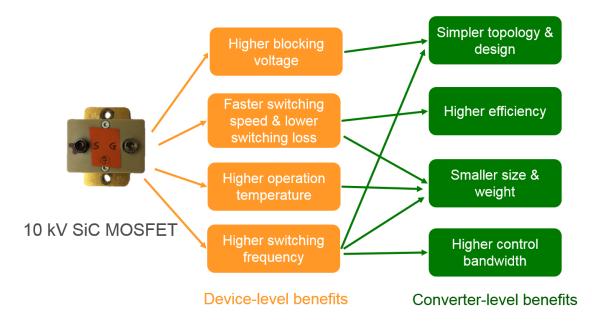

semiconductor devices to replace Si IGBTs in MV applications [1], [26]-[29]. As the leader in SiC power semiconductor devices, Wolfspeed has designed and fabricated three generations of 10 kV SiC MOSFETs, with the specific on-resistance reduced from 160  $m\Omega$ -cm<sup>2</sup> to 100 m\Omega-cm<sup>2</sup> at room temperature [26]-[29]. Compared to Si IGBTs for MV applications, 10 kV SiC MOSFETs have higher voltage rating and operation temperature, lower switching loss, and faster switching speed, as shown in Fig. 1-2 [1]. These benefits at the device level further facilitate comprehensive benefits at the converter level, such as simpler converter topology and design, higher efficiency, smaller size and weight, and higher control bandwidth [1]. Therefore, 10 kV SiC MOSFETs are one of the prospective building blocks of the future high-performance MV converters.

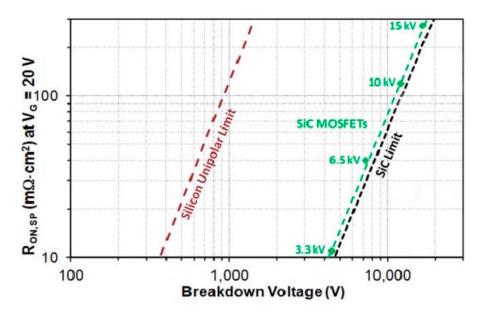

10 kV SiC MOSFETs have relatively low on-resistance because of low specific onstate resistance of SiC unipolar devices [30]. To achieve the same blocking voltage level, much thinner drift layer and much higher doping density can be used if Si wafer is replaced by SiC wafer [1]. Therefore, the on-resistance of SiC majority carrier devices is tremendously reduced compared to their Si-based counterparts at the same voltage level. Fig. 1-3 shows the comparison of the specific on-resistance and its theoretical limit of SiC and Si majority carrier devices [30]. The newest generation of 10 kV SiC MOSFETs has specific on-resistance close to its theoretical limit.

Furthermore, 10 kV SiC MOSFETs have faster switching speed, >20X lower switching losses, and hence are able to switch at much higher frequency than 6.5 kV Si IGBTs with similar current rating [22], [29]. Due to the lower specific on-resistance shown in Fig. 1-3, SiC MOSFETs typically have small die size, including 10 kV SiC MOSFETs.

Fig. 1- 2. Device-level and converter-level benefits of 10 kV SiC MOSFETs [1].

Fig. 1- 3. Specific on-resistance vs. breakdown voltage for Si and SiC [30].

As a result, the parasitic capacitances are smaller, contributing to the faster switching speed. The high saturated electron velocity of SiC material reinforces the fast switching speed of 10 kV SiC MOSFETs. From a fundamental standpoint, the 10 kV SiC MOSFET as a majority carrier device, has faster switching transients by eliminating the injection of minority charges and hence the turn-off tail current, as illustrated in Fig. 1 [17]. Because of the shorter minority carrier lifetime of SiC material [20], the body diode of 10 kV SiC MOSFETs also has much lower reverse recovery loss than Si-based PiN diodes, which also supports high switching frequency capability of 10 kV SiC MOSFETs.

MV converters benefit from the superior performance of 10 kV SiC MOSFETs in numerous aspects [27], [31]. The fast switching speed and low switching energy loss give rise to the low converter switching loss and reduced volume and weight of the cooling system. The switching frequency can be increased to tens of kilohertz to achieve smaller size of passive components and higher power density. The high blocking voltage of 10 kV SiC MOSFETs decreases the number of required power semiconductor devices and simplifies the converter topology and design [11]. With 10 kV SiC MOSFETs, two-level topologies can be adopted for MV drives with 4.16 kV line-to-line voltage.

High switching frequency enabled by 10 kV SiC MOSFETs can support the highspeed direct motor drives without the gearbox, leading to MV drives with smaller footprint and higher system density [32], [33]. Simpler multi-level topologies can be used to directly interface the distribution grid by using 10 kV SiC MOSFETs, without the series connection of switching devices. Moreover, high control bandwidth enabled by 10 kV SiC MOSFETs is capable of supporting more advanced control functions for grid-connected MV converters. For instance, the transformerless PCS based on 10 kV SiC MOSFETs designed for 13.8 kV asynchronous microgrid can achieve APF function to filter 19<sup>th</sup> order harmonics (1140 Hz) in the distribution grid [13]. These benefits from 10 kV SiC MOSFETs are also of great significance in some emerging critical applications, such as electric vehicle (EV) fast charger and data center power supply [31], [34]-[36].

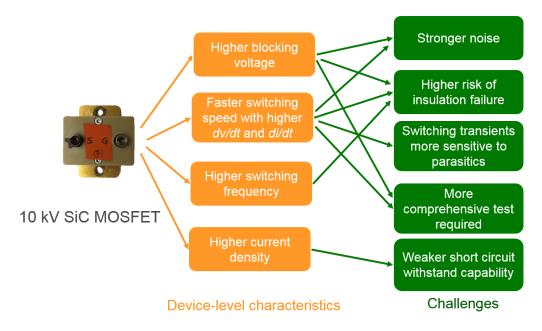

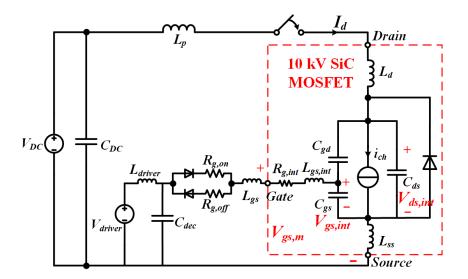

In addition to benefits, superior device-level characteristics of 10 kV SiC MOSFETs bring new challenges. For instance, the drain-to-source voltage  $V_{ds}$  of the 10 kV SiC MOSFET typically falls from 6 kV to nearly 0 V within 100 ns during the turn-on transient. Because of high blocking voltage, the high dv/dt lasts for much longer time than the high dv/dt generated by low voltage (<3.3 kV) SiC MOSFETs. It is challenging to design MV power conversion systems based on the 10 kV SiC MOSFET while fully utilizing its device-level benefits. The gate driver should isolate high voltage with high dv/dt in power and signal transmission. The common-mode (CM) current caused by high dv/dt should be tackled, and the cross-talk issue should be evaluated and addressed [24]. Not only can the high PWM voltage coupled with high dv/dt and switching frequency lead to accelerated insulation degradation, but also the premature insulation failure hence becomes a more serious issue which should be taken into consideration in MV converter design based on 10 kV SiC MOSFETs [37]-[39]. Moreover, the fast switching speed makes the switching transients of 10 kV SiC MOSFETs more sensitive to the parasitics in the power stage, especially parasitic capacitances. It is important to address these challenges in order to fully leverage the comprehensive benefits of 10 kV SiC MOSFETs.

### **1.3 Motivation and Objective**

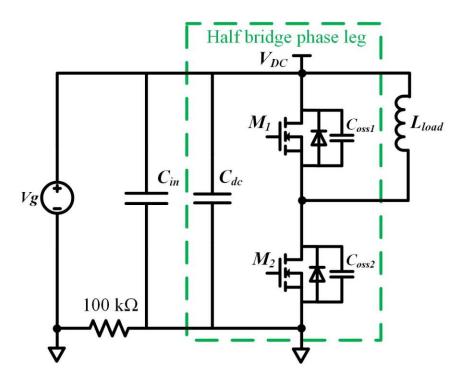

The half bridge (HB) phase leg is one of the most fundamental building blocks for modular MV converters [1]. It can function as the basic building block of MMCs and other topologies based on MMC. Two HB phase legs can form a full bridge or H-bridge, the fundamental building block of various MV converters, such as the cascaded H-bridge converter. The investigation results of the HB phase leg based on 10 kV SiC MOSFETs are the foundation for the study and design of modular MV converters. The device's switching performance in a HB phase leg is also widely accepted to guide the converter loss estimation and design. Hence, this dissertation concentrates on the study of the HB phase leg based on 10 kV SiC MOSFETs. In this dissertation, the phase leg is defined as the HB phase leg with two identical switches allowing bi-directional current. To support the bi-directional current flow, each switching device should have a freewheeling diode.

The premier motivation of this work is to design and build a robust 10 kV SiC MOSFET based HB phase leg for modular MV converters and tackle the challenges brought by the intrinsic characteristics of 10 kV SiC MOSFETs. The challenges are summarized in Fig. 1-4.

With much faster switching speed than Si IGBTs, switching transients of 10 kV SiC MOSFETs are more sensitive to the parasitics in the converter. Particularly, parasitic capacitances in the MV converter heavily influence the switching energy loss and dv/dt [31]. Nonetheless, the test setup used to test 10 kV SiC MOSFETs is often designed and built to minimize the parasitics in the power stage, and hence have different characteristics from MV converters. As a result, the previous study is unable to identify and investigate

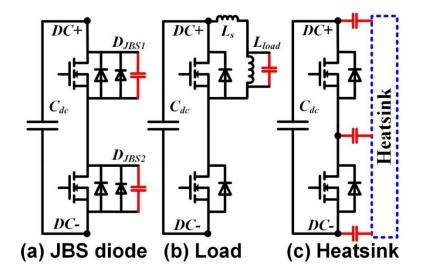

Fig. 1- 4. Summary of challenges brought by 10 kV SiC MOSFETs.

the impact of parasitic capacitances in the power stage on the switching performance, leading to inaccurate switching performance evaluation results. The freewheeling diode also impacts the switching performance of the 10 kV SiC MOSFET in the phase leg, which can be implemented with body diode and an external anti-parallel JBS diode. Adding the external anti-parallel JBS diode also introduces additional parasitic capacitance. Therefore, this dissertation aims to investigate how switching transients and performance of 10 kV SiC MOSFETs are impacted by the parasitic capacitances and the freewheeling diode.

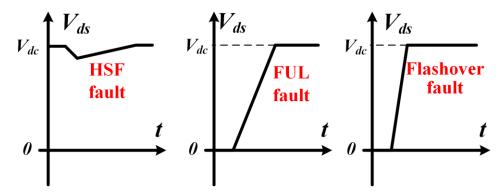

10 kV SiC MOSFETs can generate PWM voltage with high magnitude, switching frequency, and dv/dt. As a result, insulation design is more difficult and challenging in the phase leg, and there is higher risk of premature insulation failure [39]. The insulation failure can generate a flashover fault, the most serious type of short circuit fault in MV converters [37]. In this dissertation, it is defined that the flashover fault happens because protective insulation fails resulting in a shorted component, such as the MOSFET package, the isolated power supply, or the voltage sensor. Thereby, this dissertation aims to take the flashover fault into account and endeavor to reduce the damage if a flashover fault happens in the phase leg design.

With small chip area and high current density, 10 kV SiC MOSFETs possess worse short-circuit ruggedness than Si IGBTs. It is hence challenging to design the protection which is required to have faster response to turn off the MOSFET safely under short circuit/overcurrent conditions. Now that the flashover fault is one type of short circuit fault that should be considered in the phase leg based on 10 kV SiC MOSFETs, the requirement for the overcurrent/short circuit protection becomes even stricter.

The high *dv/dt* and *di/dt* generated by 10 kV SiC MOSFETs also result in stronger noise which disturbs the normal operation of the phase leg. Particularly, the overcurrent/short circuit protection with fast response could be falsely triggered due to the strong noise interference. It is of profound significance to analyze the interference mechanism of the noise and address the noise immunity problem of the overcurrent/short circuit protection. Hence, one objective of this dissertation is to design the overcurrent/short circuit protection with fast response and strong immunity simultaneously after fully understanding how the noise interferes with the protection.

The comprehensive testing and qualification of the HB phase leg based on 10 kV SiC MOSFETs are necessary to ensure robust operation of the modular MV converter. It is desirable to test the phase leg comprehensively so that problems can be found at the phase leg level before assembling and testing the full converter, which is much more complex than one phase leg. The qualification of phase legs based on 10 kV SiC MOSFETs is more crucial and challenging compared to their counterparts based on Si IGBTs, considering the higher dc voltage and much higher dv/dt and hence much more challenging insulation and noise immunity design. Meanwhile, the qualification should not be too complicated and time-consuming. One target of this dissertation is to develop a simple and comprehensive test scheme to fully qualify the HB phase leg based on 10 kV SiC MOSFETs.

### **1.4 Dissertation Outline**

The focus of this dissertation is a robust 10 kV SiC MOSFET based phase leg which can function as a building block of a modular MV converter. The robust phase leg should be able to make full use of the benefits of fast-switching 10 kV SiC MOSFETS and realize normal long-term operation without any insulation and noise issue under the high dv/dtgenerated by 10 kV SiC MOSFETs. Moreover, the robust phase leg should be able to safely protect 10 kV SiC MOSFETs in the phase leg from various overcurrent and short circuit faults, including the worst type of short circuit fault, the flashover fault.

To address these challenges summarized in Fig. 1-4, the research of the phase leg in this dissertation is conducted from three perspectives: switching performance investigation, design, and testing. A detailed outline of this dissertation is as follows.

Chapter 2 reviews the previous switching performance investigation of 10 kV SiC MOSFETs. The previous study about the design and testing of the 10 kV SiC MOSFET based phase leg is also reviewed.

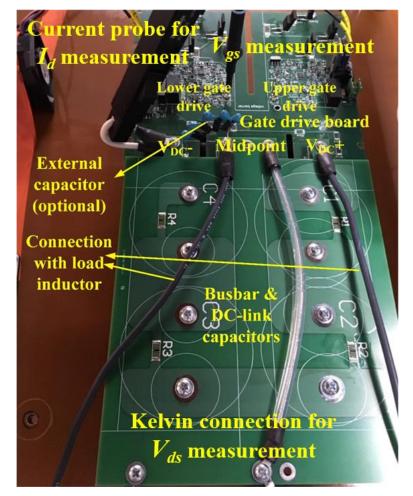

Chapter 3 introduces the baseline design and testing of the 6.5 kV HB phase leg based on the discrete 10 kV/20 A SiC MOSFETs.

Chapter 4 investigates the impact of parasitic capacitances in the MV converter on the switching performance of the 10 kV SiC MOSFET. How the added anti-parallel SiC JBS diode and the body diode impact switching transients and losses is also studied in depth. The switching performance with and without the anti-parallel JBS diode is compared quantitatively to demonstrate the different that the added JBS diode can make.

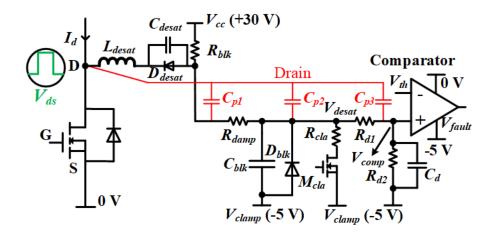

Chapter 5 studies the behavior of the 10 kV SiC MOSFET under a flashover fault due to insulation failure, the worst short circuit fault in MV converters with extremely fast transients. Gate driver design considerations are discussed from the standpoint of a flashover fault. Chapter 6 focuses on the desat protection designed to protect 10 kV SiC MOSFETs from short circuit/overcurrent conditions with fast response and strong noise immunity simultaneously. Noise immunity of the desat protection for high voltage SiC MOSFETs is analyzed thoroughly to support the noise immunity improvement under high dv/dt. A desat protection scheme with ultrafast protection response is also proposed for 10 kV SiC MOSFETs, which can also be adopted for other high voltage SiC MOSFETs.

Chapter 7 introduces a simple test scheme to test the HB phase leg based on 10 kV SiC MOSFETs comprehensively, which in particular can fully test the phase leg's capability of operating under high dv/dt and the resulting noise.

Chapter 8 concludes the research presented in this dissertation, and the future work about the phase leg design and the switching performance investigation is presented in detail.

#### **CHAPTER 2. LITERATURE REVIEW**

Numerous efforts have been spent on the HB phase leg based on 10 kV SiC MOSFETs recently in order to apply the 10 kV SiC MOSFET in high-performance MV power conversion systems in the future. In this chapter, the previous research efforts with 10 kV SiC MOSFETs will be summarized, including switching performance evaluation, phase leg design, and comprehensive test and assessment. Since the literature about 10 kV SiC MOSFETs is still limited, the research about other high voltage SiC devices will also be reviewed. It should also be noted that part of the content in Chapter 2 is from the author's Master's thesis [1].

### 2.1 Switching Performance Evaluation

With fast switching speed, the switching performance of 10 kV SiC MOSFETs is sensitive to numerous influencing factors. Switching performance evaluation should be conducted in detail in order to understand how to control the switching transients and improve the switching performance. The switching performance essential to the MV converter design is the research focus, especially the switching energy loss and dv/dt. Switching loss contributes to a large portion of the total converter loss in converters based on SiC power semiconductor devices with high switching frequency, and it has profound influence on the switching frequency selection and passive component design. The noise caused by the high dv/dt generated by 10 kV SiC MOSFETs poses great challenge to the gate driver design with an isolated power supply, its associated control circuits and signals as well as the protection design with strong noise immunity [23], [24].

## 2.1.1 Characterization and Influencing Factors of Switching Performance

The most common method used to characterize the switching performance of a power semiconductor device is DPT with the clamped inductive load circuit [18], [40]. The basic operation principle of DPT is that the gate-to-source voltage  $V_{gs}$  of the device under test (DUT) has two short pulses for the characterization of both turn-on and turn-off transient in hard switching condition. Detailed working principles of DPT will not be covered in this dissertation. The essential aspects of DPT include the control signal for the DUT, the load inductor, the freewheeling path, and the measurement setup.

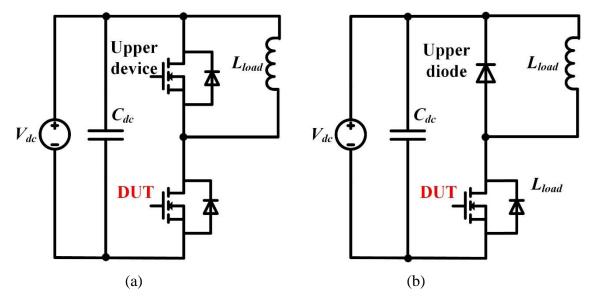

Two circuit configurations are usually used in DPT for the switching performance characterization, depending on the complementary switch which conducts the load current when the DUT is OFF. As shown in Fig. 2-1, the phase leg configuration is one of them, in which the upper device is always OFF. Yet the body diode of the upper device can provide the current path when the DUT is turned off. The other circuit configuration is the switch/diode pair, where a discrete diode with similar current and voltage rating to the DUT is used as the freewheeling diode. The DUT is usually the lower device because of its grounded source and the convenience in measurement. With a hotplate or oven, the junction temperature of the DUT can be regulated.

The HB phase leg can be easily reconfigured as a phase leg configuration for DPT with the purpose of switching performance evaluation. Although the data obtained in DPT with switch/diode pair are not accurate to indicate the dv/dt and switching loss of a phase leg applied in a converter, DPT with switch/diode pair is helpful in understanding the turn-on and turn-off transient and the influence of temperature and gate driver on the switching performance. Therefore, the switching performance evaluation with the switch/diode pair

Fig. 2- 1. Two circuit configurations used in DPT: (a) phase leg configuration; (b) switch/diode pair.

will also be reviewed.

Numerous researchers have used DPT to evaluate the switching performance of high voltage SiC devices. The switching behavior and the impact of some factors have been revealed by analyzing the switching waveforms and data. In [41], the DPT setup with switch/diode pair is built to investigate the switching performance of the 15 kV SiC MOSFET under different gate resistances and junction temperatures. It is found that adopting a smaller turn-on gate resistance leads to faster turn-on transient with higher dv/dt and lower energy loss. The turn-on process can also be accelerated with lower turn-on loss and faster transients by increasing the junction temperature. The turn-off transient is mainly dominated by capacitive charging process and hence is less dependent on gate driver parameters and the junction temperature. The switching performance of 15 kV SiC IGBTs has also been characterized with the switch/diode pair [41], [42], with both switching energy loss and dv/dt analyzed in detail.

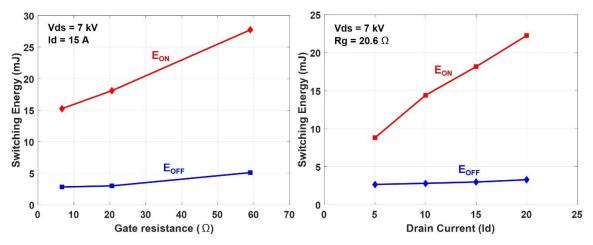

The 3<sup>rd</sup> generation 10 kV SiC MOSFET from Wolfspeed has been first characterized by Wolfspeed researchers with DPT in phase leg configuration [29], [43]. The influence of the gate resistance and the drain current on the switching performance is investigated in detail, as shown in Fig. 2-2, while the detailed analysis of the impact of the junction temperature is not provided. The large gate resistance slows down both turn-on and turn-off transient. Especially, the larger gate resistance leads to a substantial increase in the measured turn-on energy loss. Turn-on energy loss dominates the total switching energy loss. The investigation results coincide well with the conclusions in the investigation of 15 kV SiC MOSFETs with switch/diode pair in [41].

Fig. 2- 2. Switching energy loss as a function of external gate resistance (left) and drain current (right) for the 3rd generation 10 kV SiC MOSFET at 150 °C [29].

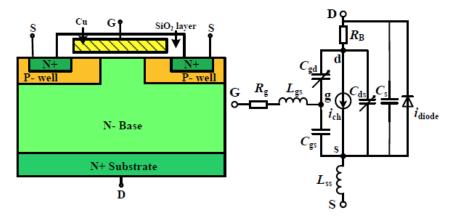

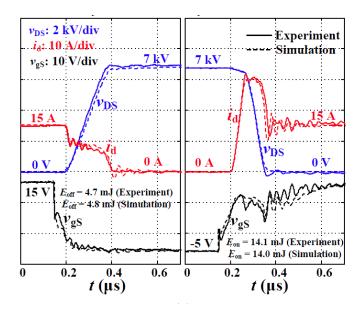

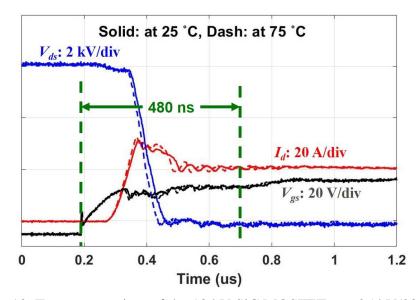

The temperature-dependent switching performance of the 3<sup>rd</sup> generation 10 kV SiC MOSFET is systematically studied in [44] in a HB phase leg. A detailed device model in Fig. 2-3 is built to perform the systematic study of the switching behavior and performance. Temperature has slight impact on the turn-on transient and negligible effect on the turn-off transient, as indicated in the switching waveforms in Fig. 2-4 and Fig. 2-5 ( $R_{g,off} = 3 \Omega$ ,  $R_{g,on} = 15 \Omega$ ). During the turn-off transient, the channel current drops to zero quickly due to low channel current (< 20 A) and high dv/dt. The turn-off process is thereby mainly the charging/discharging process of parasitic output capacitances of the MOSFETs, and dv/dt is higher at higher load current. The parasitic capacitances are independent of temperature. The junction temperature has little influence on the turn-off transient, and the measured turn-off loss is mainly the energy stored in the output capacitance of the DUT [44], [45].

Turn-on transient is slightly impacted by the temperature. The turn-on dv/dt is higher at higher junction temperature due to the lower gate threshold voltage. Meanwhile, the overshoot in drain current  $I_d$  increases because of the increased displacement current in the parasitic capacitances. The turn-on loss reduces slightly at higher temperature. Generally, junction temperature only slightly impacts the switching transients of the 3<sup>rd</sup> generation 10 kV SiC MOSFET, and higher junction temperature makes the turn-on transient faster. Such temperature-dependent switching behaviors of 15 kV SiC MOSFETs have also been reported [46], [47].

In summary, characterization results show that the junction temperature only has slight influence on the switching performance. The turn-on transient of 10 kV SiC MOSFETs is mainly controlled by the gate driver parameters, while the turn-off transient

Fig. 2- 3. Detailed device model of 10 kV SiC MOSFET [44].

Fig. 2- 4. Turn-on and turn-off waveforms of the 10 kV SiC MOSFET at 25 °C [44].

Fig. 2- 5. Turn-on and turn-off waveforms of the 10 kV SiC MOSFET at 125 °C [44].

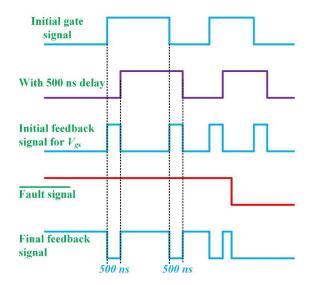

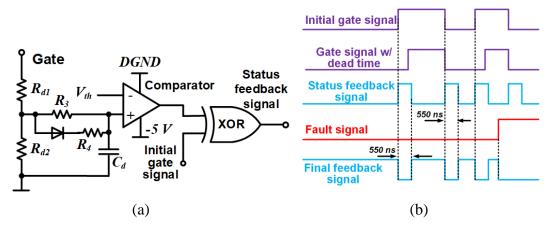

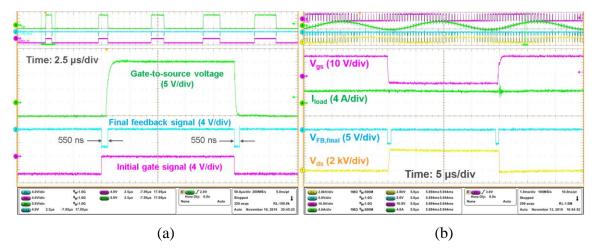

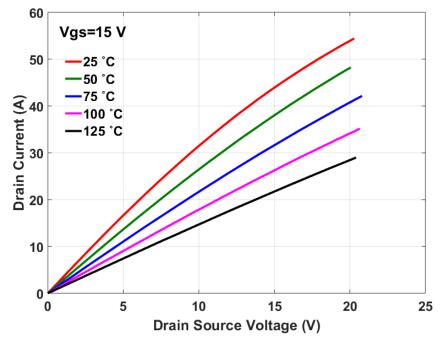

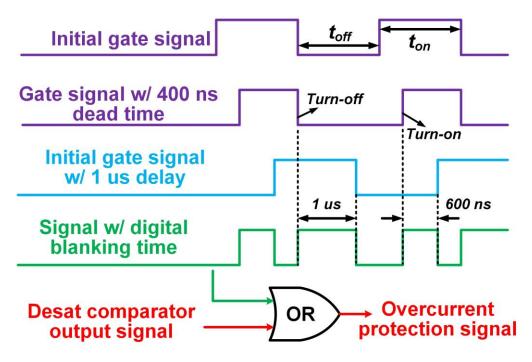

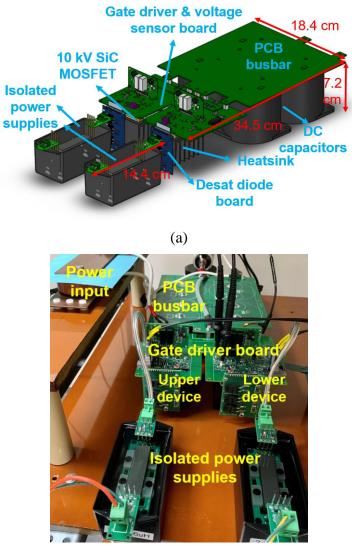

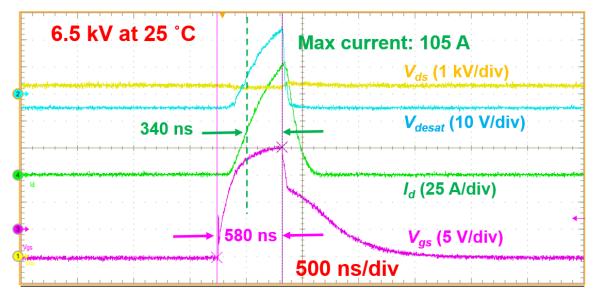

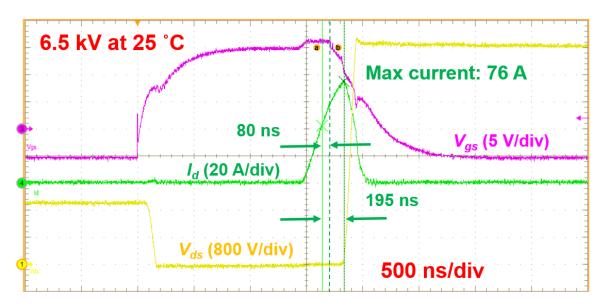

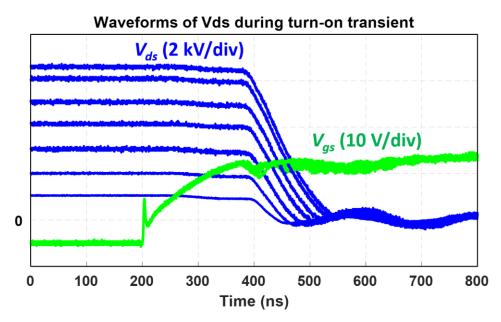

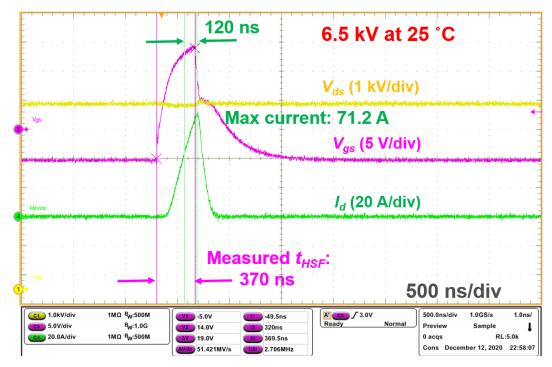

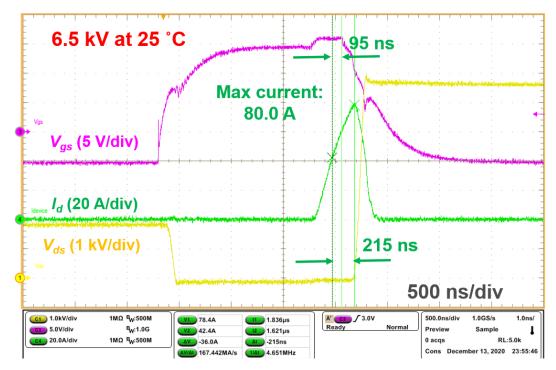

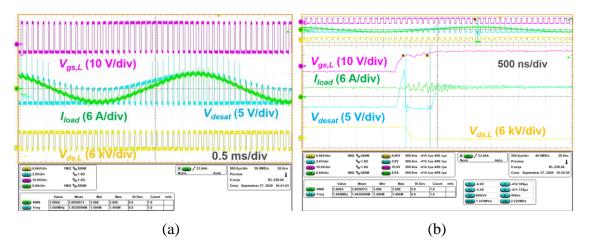

is mainly determined by the parasitic capacitances and the load current since the channel current decreases to zero quickly.