Electronic Theses and Dissertations, 2020-

2021

# Synthesis Methodologies for Robust and Reconfigurable Clock Networks

Necati Uysal University of Central Florida

Part of the Computer and Systems Architecture Commons

Find similar works at: https://stars.library.ucf.edu/etd2020

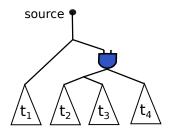

University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2020- by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Uysal, Necati, "Synthesis Methodologies for Robust and Reconfigurable Clock Networks" (2021). *Electronic Theses and Dissertations, 2020-.* 941.

https://stars.library.ucf.edu/etd2020/941

# SYNTHESIS METHODOLOGIES FOR ROBUST AND RECONFIGURABLE CLOCK NETWORKS

by

# NECATI UYSAL M.S. University of Central Florida, 2017 B.S. University of Gaziantep, 2013

A dissertation submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Fall Term 2021

Major Professor: Rickard Ewetz

© 2021 Necati Uysal

#### **ABSTRACT**

In today's aggressively scaled technology nodes, billions of transistors are packaged into a single integrated circuit. Electronic Design Automation (EDA) tools are needed to automatically assemble the transistors into a functioning system. One of the most important design steps in the physical synthesis is the design of the clock network. The clock network delivers a synchronizing clock signal to each sequential element. The clock signal is required to be delivered meeting timing constraints under variations and in multiple operating modes. Synthesizing such clock networks is becoming increasingly difficult with the complex power management methodologies and severe manufacturing variations. Clock network synthesis is an important problem because it has a direct impact on the functional correctness, the maximum operating frequency, and the overall power consumption of each synchronous integrated circuit.

In this dissertation, we proposed synthesis methodologies for robust and reconfigurable clock networks. We have made three contributions to this topic. First, we have proposed a clock network optimization framework that can achieve better timing quality than previous frameworks. Our proposed framework improves timing quality by reducing the propagation delay on critical paths in a clock network using buffer sizing and layer assignment. Second, we have proposed a clock tree synthesis methodology that integrates the clock tree synthesis with the clock tree optimization. The methodology improves timing quality by avoiding to synthesize clock trees with topologies that are sensitive to variations. Third, we have proposed a clock network that can reconfigure the topology based on the active mode of operation. Lastly, we conclude the dissertation with future research directions.

| This dissertation is first dedicated to my family and then to Bekir Yilmaz, a senior member of family whom I have lost during my Ph.D. studies. | my |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                                                                 |    |

|                                                                                                                                                 |    |

|                                                                                                                                                 |    |

|                                                                                                                                                 |    |

## **ACKNOWLEDGMENTS**

I would like to express my gratitude to my advisor, Dr. Rickard Ewetz. His guidance through my research journey with his expertise and knowledge was invaluable. In addition, I am grateful for his assistance and patience when I encounter difficulties. I would also like to extend my gratitude to Dr. Ronald F. DeMara, Dr. Mingjie Lin, Dr. Murat Yuksel, and Dr. Damian Dechev for their support, feedback, and their time to serve in my doctoral committee.

I would like to thank my friend, Baogang Zhang for his support during my PhD studies. Baogang was always there for me when I needed help. It was a great pleasure for me to work with him in the same research lab.

I would like to thank my dear friends, Ahmet Uzun, Ender Egri, Nazar Emirov, and Yunus Uzun. Without their support and advice, it would be really difficult for me to tackle many problems that I have faced in my life.

I would like to express my endless love to my parents, Turgut and Ayse Uysal. I am grateful to them for their devotion and sacrifices in providing a good life for me. I would also like to thank my dear sister and brother, Ayse Gul and Huseyin, for their continuous support and encouragement throughout my entire life.

I would like to thank the ECE department at UCF and NSF (CCF-1755825, CNS-1908471, and CNS-2008339 grants) for providing financial support during my Ph.D. studies.

# TABLE OF CONTENTS

| LIST ( | OF FIGURES                                                          | xi |

|--------|---------------------------------------------------------------------|----|

| LIST C | OF TABLES                                                           | XV |

| СНАР   | TER 1: INTRODUCTION                                                 | 1  |

| СНАР   | TER 2: PRELIMINARIES                                                | 3  |

| 2.1    | Timing constraints                                                  | 3  |

| 2.2    | Variations in the timing                                            | 4  |

| 2.3    | Clock networks with different topologies                            | 5  |

| СНАР   | TER 3: REVIEW OF PREVIOUS WORKS                                     | 7  |

| 3.1    | Elmore delay model                                                  | 7  |

| 3.2    | Clock tree synthesis                                                | 9  |

|        | 3.2.1 Construction of clock trees using the Elmore delay model [26] | 10 |

|        | 3.2.2 Deferred merge embedding (DME) Algorithm                      | 12 |

| 3.3    | Clock tree optimization                                             | 13 |

|        | 3.3.1 Timing slacks under OCVs                                      | 14 |

|      | 3.3.2 Predicted timing quality and CTO                                                                    | 15 |

|------|-----------------------------------------------------------------------------------------------------------|----|

| 3.4  | Gate sizing and layer assignment                                                                          | 16 |

|      | 3.4.1 Van Ginneken's algorithm                                                                            | 16 |

| 3.5  | Techniques of handling OCVs                                                                               | 18 |

| 3.6  | Clock network synthesis for multiple modes of operations                                                  | 19 |

| СНАР | TER 4: LATENCY CONSTRAINT GUIDED BUFFER SIZING AND LAYER AS-<br>SIGNMENT FOR CLOCK TREES WITH USEFUL SKEW | 21 |

| 4.1  | Introduction                                                                                              | 21 |

|      | 4.1.1 Motivation and the overview of the BLU framework                                                    | 21 |

|      | 4.1.2 Proposed framework                                                                                  | 23 |

| 4.2  | The BLU framework                                                                                         | 23 |

|      | 4.2.1 Baseline of the BLU framework                                                                       | 24 |

|      | 4.2.2 Relaxing the latency constraints                                                                    | 25 |

|      | 4.2.3 Tightening the latency constraints                                                                  | 26 |

| 4.3  | Methodology                                                                                               | 28 |

| 4.4  | Experimental evaluation                                                                                   | 29 |

|      | 4.4.1 Evaluation of positive delay adjustments                                                            | 32 |

|      | 4.4.2   | Evaluation of negative delay adjustments      | 33 |

|------|---------|-----------------------------------------------|----|

| 4.5  | Summ    | ary and conclusion                            | 34 |

| СНАР | TER 5:  | AN OCV-AWARE CLOCK TREE SYNTHESIS METHODOLOGY | 36 |

| 5.1  | Introdu | action                                        | 36 |

| 5.2  | Motiva  | ation                                         | 37 |

|      | 5.2.1   | Limitations of previous works                 | 37 |

|      | 5.2.2   | Proposed methodology                          | 37 |

| 5.3  | Metho   | dology                                        | 40 |

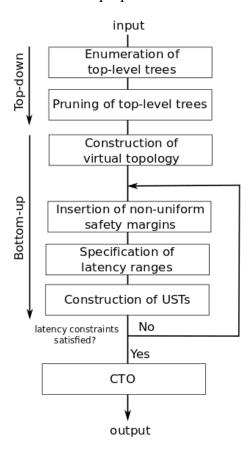

|      | 5.3.1   | The overview of the framework                 | 40 |

|      | 5.3.2   | Enumeration of top-level trees                | 42 |

|      | 5.3.3   | Pruning of top-level trees                    | 43 |

|      | 5.3.4   | Construction of virtual topology              | 44 |

|      | 5.3.5   | Insertion of non-uniform safety margins       | 44 |

|      | 5.3.6   | Specification of latency ranges               | 46 |

|      | 5.3.7   | Construction of USTs                          | 47 |

| 5.4  | Experi  | mental Evaluations                            | 48 |

|      | 5.4.1   | Evaluation of framework configurations        | 49 |

|       | 5.4.2  | Comparisons with state-of-the-art                     | 52 |

|-------|--------|-------------------------------------------------------|----|

| 5.5   | Sumn   | nary and conclusion                                   | 54 |

| CHAP' | ΓER 6: | SYNTHESIS OF CLOCK NETWORKS WITH A MODE RECONFIGURABL |    |

|       |        | TOPOLOGY                                              | 55 |

| 6.1   | Introd | luction                                               | 55 |

| 6.2   | Prelin | ninaries                                              | 56 |

| 6.3   | Proble | em formulation                                        | 58 |

| 6.4   | The li | mitations of the previous studies                     | 59 |

| 6.5   | Propo  | sed MRT Structure                                     | 61 |

|       | 6.5.1  | Overview of the MRT structure                         | 61 |

|       | 6.5.2  | Improving the robustness in high performance modes    | 62 |

|       | 6.5.3  | Reducing power in low performance modes               | 64 |

| 6.6   | Metho  | odology                                               | 66 |

|       | 6.6.1  | Insertion of OR-gates                                 | 67 |

|       | 6.6.2  | Construction of top-level clock trees                 | 68 |

|       |        | 6.6.2.1 Construction of Topology Relation Graph       | 69 |

|       |        | 6.6.2.2 Edge pruning                                  | 70 |

|         |                    | 6.6.2.3 TRG guided Tree construction                                |

|---------|--------------------|---------------------------------------------------------------------|

|         | 6.6.3              | Construction of the reconfigurable topology                         |

|         | 6.6.4              | Clock network optimization                                          |

|         | 6.6.5              | Supply voltage selection                                            |

| 6.7     | Experi             | mental Results                                                      |

|         | 6.7.1              | Evaluation of MRT design configurations                             |

|         |                    | 6.7.1.1 Selection of the number of top-level trees                  |

|         |                    | 6.7.1.2 Evaluation of the TRG guided top-level tree construction 78 |

|         |                    | 6.7.1.3 Evaluation of topology reconfiguration                      |

|         |                    | 6.7.1.4 Evaluation of the negative-edge of the clock signal 81      |

|         | 6.7.2              | Evaluation of MRT structures                                        |

| 6.8     | Summa              | ary and conclusion                                                  |

| СНАР    | TER 7:             | FUTURE WORKS                                                        |

| I IST ( | LIST OF DEFEDENCES |                                                                     |

# LIST OF FIGURES

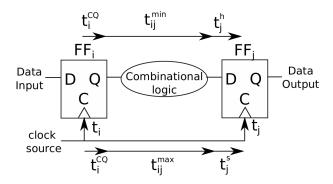

| Figure 2.1: Setup and hold time constraints between a pair of flip-flops                              | 4  |

|-------------------------------------------------------------------------------------------------------|----|

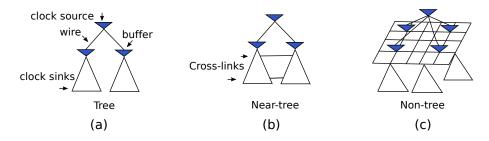

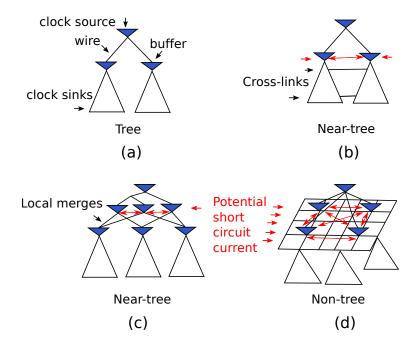

| Figure 2.2: Clock networks with a) tree, b) near-tree and c) non-tree topology                        | 5  |

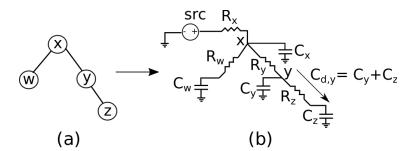

| Figure 3.1: a) A clock tree topology and b) The RC representation of the clock tree topol-            |    |

| ogy in (a)                                                                                            | 7  |

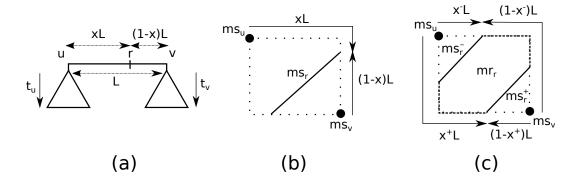

| Figure 3.2: a) A pair of subtrees and the embedding location are illustrated. b) The illus-           |    |

| tration of embedding locations as merging segments (ms) of the correspond-                            |    |

| ing nodes in (a) for a zero skew merge. c) The illustration of embedding                              |    |

| locations as merging regions (mr) of the corresponding nodes in (a) for a                             |    |

| non-zero skew merge.                                                                                  | 12 |

| Figure 3.3: The illustration of the path that introduces OCV into the timing constraints              |    |

| between $FF_i$ and $FF_j$                                                                             | 14 |

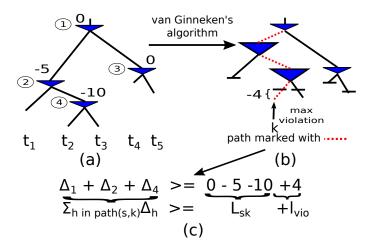

| Figure 3.4: Extension of van Ginneken's algorithm [36]                                                | 17 |

| Figure 4.1: (a) A specified delay adjustment. (b) Delay adjustment realized by buffer                 |    |

| insertion. (c) Proposed realization of delay adjustments using buffer sizing                          |    |

| and layer assignment                                                                                  | 22 |

| Figure 4.2: (a) SG. (b) $P_{tns}$ and $P_{wns}$ and delay adjustments. (c) latency constraints. (d)   |    |

| offsets. (e) van Ginneken's algorithm. (f) selected candidate solution                                | 24 |

| Figure 4.3: (a) Latency constraints (b) Relayed latency constraints (c) Method to find 1 <sup>r</sup> | 25 |

| Figure 4.4: (a) Delay adjustments specified by Eq (3.9). (b) Clock tree after van Gin-    |    |

|-------------------------------------------------------------------------------------------|----|

| neken's algorithm. $l_{max}$ is violated by the path marked with a red dashed line.       |    |

| (c) Generation of a delay adjustment constraint                                           | 26 |

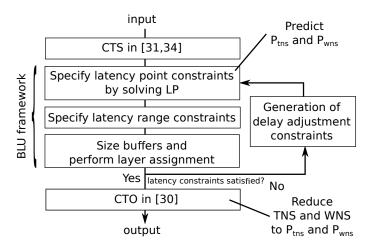

| Figure 4.5: Proposed flow for the BLU framework                                           | 28 |

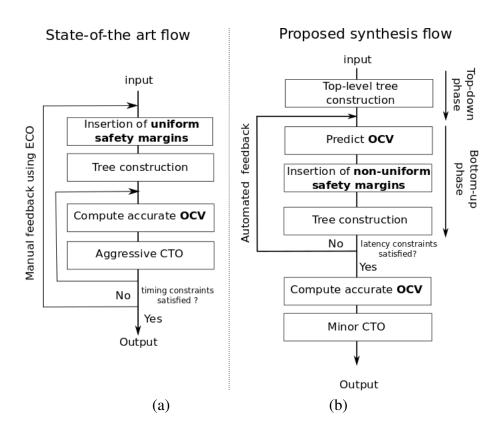

| Figure 5.1: (a) State-of-the-art CTS+CTO based synthesis flow. (b) Proposed OCV-          |    |

| aware clock tree synthesis flow                                                           | 38 |

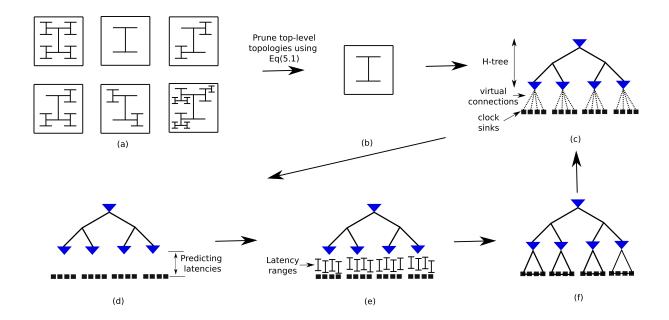

| Figure 5.2: Detailed flow of proposed OCV-aware synthesis methodology                     | 40 |

| Figure 5.3: (a) Multiple candidate top-level topologies are enumerated. (b) The top-level |    |

| topology is determined after pruning the candidate topologies. (c) The top-               |    |

| level clock tree and the virtual topology are constructed. (d) The latencies              |    |

| to the clock sinks are estimated using the virtual topology. (e) Non-uniform              |    |

| safety margins are inserted in the skew constraints and a latency range is                |    |

| specified for each clock sinks. (f) Bottom-level subtrees are iteratively con-            |    |

| structed by inserting safety margins that are tailored to the topology. If the            |    |

| latency constraints are not satisfied, the construction process returns to (c)            |    |

| with improved timing predictions                                                          | 41 |

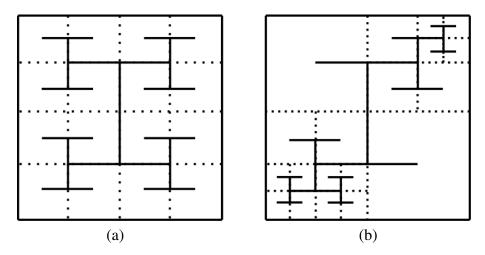

| Figure 5.4: The illustration of (a) Uniform H-tree and (b) Non-uniform H-tree             | 42 |

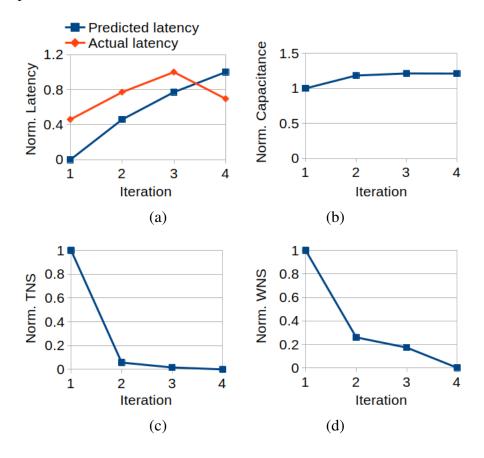

| Figure 5.5: Evaluation of the framework in terms of (a) Latency. (b) Capacitance. (c)     |    |

| TNS. (d) WNS                                                                              | 49 |

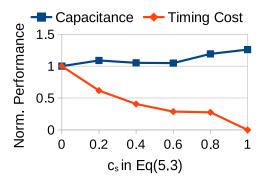

| Figure 5.6: Sensitivity to scaling parameter $c_s$ on $ecg$                               | 50 |

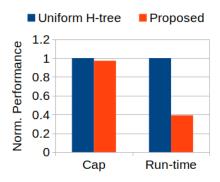

| Figure 5.7: Evaluation of top-level tree construction using uniform H-tree vs. non-uniform |    |

|--------------------------------------------------------------------------------------------|----|

| H-tree                                                                                     | 51 |

| Figure 6.1: Clock networks with different topologies and the illustration of short circuit |    |

| current on each topology                                                                   | 59 |

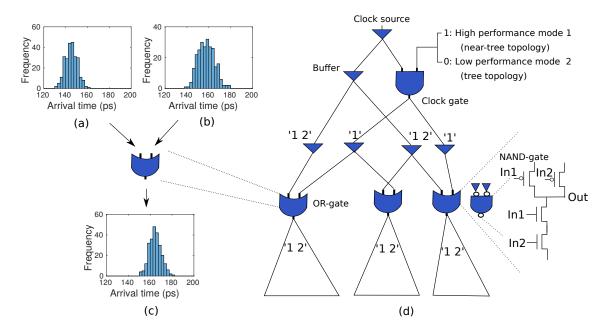

| Figure 6.2: The arrival time distributions (for the positive-edge of the clock signal) at  |    |

| different points with respect to an OR-gate are shown in (a), (b) and (c).                 |    |

| The variance of the arrival time distribution at the output of the OR-gate is              |    |

| tighter than that of the variance at the inputs, which demonstrates that OR-               |    |

| gates improve the robustness to variations. (d) The proposed MRT structure                 |    |

| is constructed using OR-gates to provide robustness to variations                          | 62 |

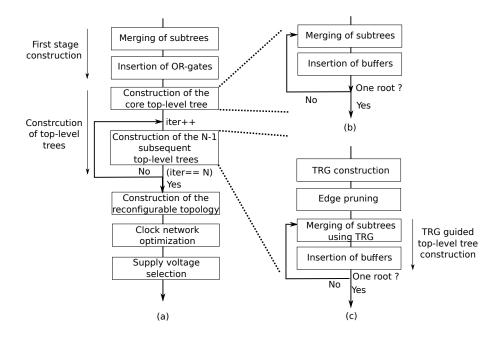

| Figure 6.3: (a) Flow for constructing MRT structures. (b) Flow for construction of the     |    |

| core top-level tree. (c) Flow for construction of the $N-1$ subsequent top-                |    |

| level trees                                                                                | 66 |

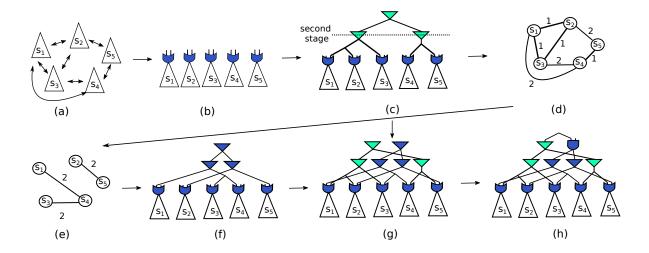

| Figure 6.4: Example flow for the construction of an MRT structure when $N = 2$ . (a) First |    |

| stage subtrees. (b) Driver devices are inserted. (c) Core top-level clock tree             |    |

| is constructed. The driver devices used to construct the core-top level tree               |    |

| are colored in green. (d) The Topology Relation Graph (TRG) is constructed                 |    |

| with respect to the topology. (e) The TRG after edge pruning is applied.                   |    |

| (f) The second top-level clock tree is constructed using TRG. (g) The clock                |    |

| network after the construction of top-level trees shown in (c) and (f). (h) The            |    |

| clock network after constructing the reconfigurable topology.                              | 68 |

| Figure 6.5: The reconfigurable topology                                                    | 73 |

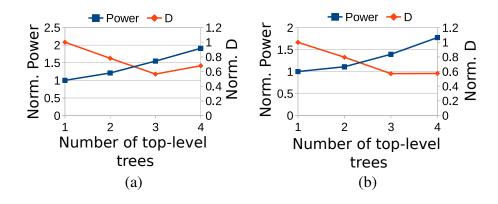

| Figure 6.6: Evaluation of MRT structures with different number of top-level trees on the    |

|---------------------------------------------------------------------------------------------|

| circuits (a) dma and (b) aes. The performance is evaluated in terms of power                |

| and robustness to variations. The clock network structure with 1 top-level                  |

| tree is equivalent to the traditional clock tree                                            |

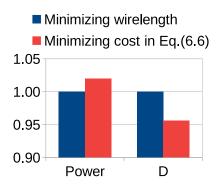

| Figure 6.7: Evaluation of guiding the top-level tree construction using different cost met- |

| rics. The evaluation is performed in terms of normalized power and normal-                  |

| ized robustness ( $D$ )                                                                     |

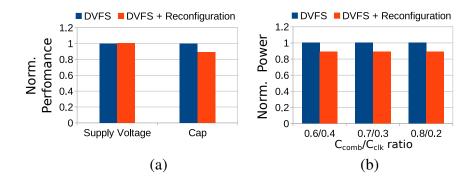

| Figure 6.8: Evaluation of DVFS vs reconfiguration combined with DVFS in terms of            |

| average (a) supply voltage and switching capacitance and (b) total circuit                  |

| power for different ratios of $C_{comb}$ and $C_{clk}$ . The experimental results shown     |

| in the figure are the average values for the benchmarks in Table 6.3 80                     |

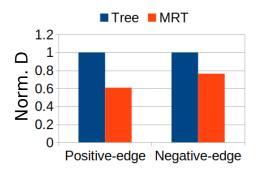

| Figure 6.9: Evaluation of the MRT structure for the negative-edge and the positive-edge     |

| of the clock signal                                                                         |

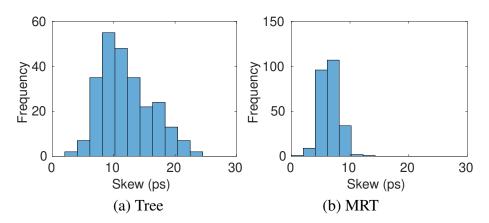

| Figure 6.10: Histogram of skews from Monte Carlo simulations of (a) Tree and (b) MRT        |

| structures on $usbf$                                                                        |

# LIST OF TABLES

| Table 4.1: | Circuits in [31]                                                                          | 29 |

|------------|-------------------------------------------------------------------------------------------|----|

| Table 4.2: | Evaluation of various tree structures in terms of total capacitance                       | 31 |

| Table 4.3: | Evaluation of various tree structures in terms of runtime                                 | 31 |

| Table 4.4: | Evaluation of negative delay adjustments                                                  | 35 |

| Table 5.1: | Holistic guidelines and objectives for different parts of a clock tree                    | 39 |

| Table 5.2: | Evaluation of the clock tree structures in terms of performance and synthesis time        | 52 |

| Table 6.1: | Comparison between clock networks with tree, near-tree, and non-tree topologies           | 60 |

| Table 6.2: | Comparison between DVFS and topology reconfiguration combined with DVFS                   | 64 |

| Table 6.3: | Benchmarks in [7]                                                                         | 75 |

| Table 6.4: | The properties of the structures                                                          | 75 |

| Table 6.5: | Evaluation of structures in terms of power consumption, supply voltage and timing quality | 82 |

# **CHAPTER 1: INTRODUCTION**

Sequential VLSI circuits consist of combinational logic and sequential elements. The sequential elements such as registers and flip-flops require a synchronization signal to capture and propagate the correct data signal. The synchronization is facilitated using a clock network that delivers a clock signal from a clock source to all sequential elements. There exists timing constraints between each sequential element that are separated by combinational logic in the data and control paths. For the functional correctness of the circuit, the clock signal must be delivered meeting the timing constraints.

Clock skew is the difference in the arrival time between a pair of flip-flops. Ideally, the clock signal is required to be delivered to the flip-flops at the same time to meet the timing constraints. Therefore, early studies focused on synthesizing clock networks to meet zero-skew [1, 3–5, 23, 41] or bounded-skew [6, 51, 52] constraints in order to achieve minimum possible clock skew. However, this may not be necessary because the timing constraints imposed by the combinational logic between certain pairs of clock sinks may actually be looser. In such cases, the timing margins can be allowed to be utilized by the clock skew. This is advantageous because there is a trade-off between the clock skew and the hardware cost of a clock network. Consequently, lower cost clock networks can be synthesized by utilizing available timing margins, which can be achieved by constructing useful skew trees (USTs) [22, 31, 34, 53, 70].

Modern VLSI circuits are required to meet tight timing constraints under variations while operating at high clock frequencies. Constructing clock networks with small nominal skews is not too difficult [1, 3, 22, 23]. However, it is very challenging to meet tight skew constraints while a clock network is under the influence of process, voltage and temperature (PVT) variations [2, 20, 21, 64, 65, 68]. The main reason is that the variations result in deterioration in the timing of

the clock network, which introduces timing violations. To meet the timing constraints, the effects of variations must be accurately accounted when synthesizing clock networks.

When the clock signal propagates through the interconnects of a clock network, the transition time of the clock signal may severely degrade. To preserve the functionality of a circuit, the clock signal must be delivered with a sharp transition. This can be ensured by meeting a maximum transition time constraint when delivering the clock signal. To achieve this, typically clock buffers and clock inverters are required to be inserted at the appropriate locations when constructing the clock networks.

In today's advanced technology nodes, modern VLSI circuits are required to operate in low and high performance modes to cater to variable frequency and power requirements. Consequently, the clock networks for such circuits must be synthesized meeting drastically different timing constraints in the different modes. This is particularly more challenging under the influence of variations. To meet both the timing constraints and the power budgets, advanced structures and synthesis methodologies are required.

This dissertation focuses on techniques and methodologies to construct robust clock networks that achieve high timing quality under the influence of variations. Clock network construction problems are formulated and solved using various algorithms, clock network structures, and optimization techniques. In this dissertation, an overview of the backgrounds and the previous works on the construction of clock networks are reviewed in Chapter 2 and Chapter 3, respectively. In Chapter 4, a buffer sizing and layer assignment framework is proposed to improve the timing quality of a constructed clock tree. In Chapter 5, an On-chip variation-aware clock tree synthesis methodology is proposed. Finally, a methodology to construct clock networks that can reconfigure its topology based on the active mode of operation is proposed. The dissertation is concluded with the future research directions in Chapter 7.

#### **CHAPTER 2: PRELIMINARIES**

In this chapter, the preliminaries are reviewed.

#### 2.1 Timing constraints

Synchronous circuits are synchronized by delivering a clock signal from the clock source to flip-flops (or clock sinks). There is a setup and hold time constraint between any pair of flip-flops (FFs) that are only separated by combinational logic in the data and control paths, which is shown in Figure 2.1. The clock signal must be delivered meeting setup and hold time constraints for the functional correctness of the circuit. The setup and hold time constraints between the launching flip-flop  $FF_i$  and the capturing flip-flop  $FF_i$  are formulated, as follows [26]:

$$t_i + t_i^{CQ} + t_{ij}^{max} + t_j^S \le t_j + T,$$

(2.1)

$$t_i + t_i^{CQ} + t_{ij}^{min} \ge t_j + t_j^H,$$

(2.2)

where  $t_i$  and  $t_j$  are the arrival times of the clock signal to the  $FF_i$  and  $FF_j$ , respectively.  $t_i^{CQ}$  is the clock to output delay of the capturing flip-flop; T is the clock period;  $t_j^S$  and  $t_j^H$  are the setup time and hold time of  $FF_j$ , respectively.  $t_{ij}^{max}$  ( $t_{ij}^{min}$ ) is the maximum (minimum) delay through the combinational logic between  $FF_i$  and  $FF_j$ . The clock skew between the pair of clock sinks is defined to be equal to  $skew_{ij} = t_i - t_j$ . Using  $ub_{ij} = T - t_i^{CQ} - t_{ij}^{max} - t_j^S$  and  $l_{ij} = t_i^{CQ} + t_{ij}^{min} - t_j^H$ , the setup and hold time constraints in Eq (2.1) and Eq (2.2) can be respectively reformulated as explicit skew constraints, as follows:

$$lb_{ij} \le skew_{ij} \le ub_{ij} \tag{2.3}$$

Figure 2.1: Setup and hold time constraints between a pair of flip-flops.

## 2.2 Variations in the timing

The intrinsic variability in the semiconductor fabrication and fluctuations in the environmental operating conditions introduces variations in the timing. The clock network that synchronizes each circuit is naturally vulnerable to these variations because it spans across each chip. Consequently, the variations in the timing must be accounted for when constructing clock networks.

The variations are introduced by the variability in the manufacturing process such as differences in the channel lengths, wire widths, and oxide thickness; and the changes in the environmental conditions such as temperature, supply voltage, and cross-talk noise.

The variations within a single die are spatially correlated and commonly referred to as On-Chip variations (OCV). However, the variations between each die are directly dependent on the parameters of the process at the time of manufacturing. These process parameters are captured using process corners. To account for the OCVs at a process corner, spatially correlated variations are applied to the process parameters across the chip. Consequently, the timing quality of a clock network can be evaluated by performing simulations for each corner using the process parameters that are obtained after applying OCVs.

Clock networks can easily be constructed to meet the timing constraints under the nominal conditions. However, it is challenging to meet the timing constraints under variations because variations may severely shrink the timing margins. The variations in the timing can be integrated into the explicit skew constraints in Eq (2.3), as follows:

$$lb_{ij} + (\delta_i + \delta_j) \le skew_{ij} \le ub_{ij} - (\delta_i + \delta_j)$$

(2.4)

where  $\delta_i$  and  $\delta_j$  are the timing deteriorates at  $FF_i$  and  $FF_j$ , respectively. The timing deteriorates are directly correlated with the distance between  $FF_i$  and  $FF_j$  in the topology of the clock network [17, 35].

Figure 2.2: Clock networks with a) tree, b) near-tree and c) non-tree topology.

# 2.3 Clock networks with different topologies

The overall power consumption and robustness to variations of a clock network is determined by the topology, which can be in the form of a tree, near-tree, or non-tree, which are illustrated in Figure 2.2. Clock trees consume the least power but are vulnerable to variations. Clock networks with a non-tree or near-tree topology have multiple paths from the clock source to the clock sinks. When inserted appropriately, the alternative paths neutralize the negative impact of variations. However, clock networks with a non-tree topology (as clock meshes) may consume 3X-5X more

power than a clock tree [19, 25, 27]. Near-tree structures provide high robustness to variations, while power consumption is only slightly higher than the power consumption of a clock tree. Therefore, clock network structures in the form of a near-tree topology [9, 13, 15, 16, 24, 35, 69] has been the focus of many recent studies. More details about the properties of the clock network topologies are provided in Chapter 6.

# **CHAPTER 3: REVIEW OF PREVIOUS WORKS**

In this chapter, we present an overview of the backgrounds and the previous works.

#### 3.1 Elmore delay model

The clock network synthesis process requires a delay model to propagate the clock signal in order to evaluate the timing performance of a clock network. The interconnects of a clock network can be represented as a lumped Resistor-Capacitor (RC) network. The delay of any node in an RC network can be obtained by formulating and solving differential equation problems. In general, Elmore delay model [50] is extensively used to obtain the delay in an RC network, which is based on the first order approximation of the delay. There exists complex delay models that are used to more accurately compute the delay in an RC network [14, 44–47, 60]. However, these techniques are computationally expensive compared to the Elmore delay model.

Figure 3.1: a) A clock tree topology and b) The RC representation of the clock tree topology in (a).

A clock network with a tree topology and its equivalent RC representation is illustrated in (a) and (b) of Figure 3.1, respectively. The delay of a specific node in the RC network shown in Figure 3.1(a) can be computed using the equation, as follows [50]:

$$t_{v_s,v_i} = \sum_{\forall j \in path(v_s,v_i)} R_j \cdot C_{d,j}$$

(3.1)

where  $v_i$  is a node in the topology;  $t_{v_s,v_i}$  is the propagation delay from the clock source  $(v_s)$  to  $v_i$ ;  $path(v_s,v_i)$  is the path from  $v_s$  to  $v_i$ ;  $R_j$  is the total resistance of a wire segment that connects two nodes on the  $path(v_s,v_i)$ ;  $C_{d,j}$  is the total downstream capacitance on  $v_j$ , i.e., the total capacitance of the subtree rooted at  $v_j$ .

The voltage at a certain time (t) on each node in the RC network can be computed using the equation as follows:

$$V_i(t) = V_{dd} \cdot (1 - e^{-t/t_{v_s, v_i}})$$

(3.2)

where  $V_i(t)$  is the voltage at node i;  $V_{dd}$  is the supply voltage. The delay is generally defined as the duration for the output capacitance to be charged from 0V to  $V_{dd}/2$ . Using the Eq (3.2), the total elapsed time until the voltage reaches to  $V_{dd}/2$  can be derived, as follows:

$$t_{d,\nu_i} = \ln(2) \cdot t_{\nu_s,\nu_i} \tag{3.3}$$

where  $t_{d,v_i}$  is the delay of the clock signal that propagates from  $v_s$  to  $v_i$ . The switching performance of the interconnects can be evaluated using the transition time at each node. The transition time at a certain node is the elapsed time that the voltage changes between  $0.1V_{dd}$  and  $0.9V_{dd}$  [26]. The transition time at any internal node in an RC network can be formulated using Eq (3.2), as follows [54]:

$$t_{tr,v_i} = ln(9) \cdot t_{v_s,v_i} \tag{3.4}$$

where  $t_{tr,v_i}$  is the transition time of the clock signal at  $v_i$ . Using the Eq (3.3) and Eq (3.4), the delay and the transition time of the clock signal can be respectively computed to evaluate the timing of the clock network.

#### 3.2 Clock tree synthesis

Clock tree synthesis (CTS) is a process that is performed to construct a clock tree that delivers a clock signal from a clock source to each clock sinks. The inputs to this process are x-y coordinates of clock sinks and a technology library. Given these inputs, a clock tree is constructed to connect the clock source to the clock sinks using wires and devices from the technology library. Moreover, the clock signal must be delivered meeting the skew constraints in Eq (2.3) for the functional correctness of the circuits.

Early studies on CTS focused on the construction of zero skew trees (ZSTs) [5, 23, 56] and bounded skew trees (BSTs) [6]. Later, the construction of useful skew trees (USTs) [22, 28, 32, 34] was explored to meet the explicit (arbitrary) skew constraints imposed between each pair of sequential elements (or clock sinks) that are only separated by combinational logic in the control logic and data paths.

In the remaining of this section, the backgrounds for the clock tree synthesis process is presented. We mainly focused on explaining the construction of the ZSTs. However, the details of the modifications required to synthesize BSTs and USTs are provided for different steps of the CTS process.

## 3.2.1 Construction of clock trees using the Elmore delay model [26]

In this section, it is explained how clock trees can be constructed using the Elmore delay model in Section 3.1, which is described more detailed in [26]. Zero skew tree construction is proposed in [5, 23, 56]. The construction is based on iteratively merging two subtrees (or clock sinks) into a large subtree such that a target skew constraint is guaranteed to be satisfied under the Elmore delay model. This is achieved by propagating the downstream delay of each subtree and finding a tapping point where two subtrees are required to be merged to meet the skew constraint.

Let u and v be the two subtrees; r be the newly formed subtree that is constructed after merging subtrees u and v;  $t_{u,r}^{max}$  ( $t_{v,r}^{max}$ ) be the maximum downstream delay through the path from r to u (v).  $t_{u,r}^{max}$  and  $t_{v,r}^{max}$  can be respectively computed, as follows:

$$t_{u,r}^{max} = t_u^{max} + x \cdot L \cdot R_{wire} \cdot (x \cdot L \cdot C_{wire} + C_u)$$

$$t_{v,r}^{max} = t_v^{max} + (1 - x) \cdot L \cdot R_{wire} \cdot ((1 - x) \cdot L \cdot C_{wire} + C_v)$$

(3.5)

where  $t_u^{max}$  and  $t_v^{max}$  are the maximum downstream delay of subtrees u and v, respectively; L is the shortest manhattan distance between u and v; x is the ratio of the wirelength between u and tapping point r to the L.  $C_u$  and  $C_v$  are the downstream capacitance at u and v, respectively.  $R_{wire}$  and  $C_{wire}$  are the resistance and capacitance per unit distance, respectively.

To construct zero skew trees, two subtrees are required to be merged such that  $t_{u,r}^{max} = t_{v,r}^{max}$  is satisfied. Consequently, a zero skew merge can be achieved by solving the following equation to find the required x, as follows [23, 26]:

$$x = \frac{t_v^{max} - t_u^{max} + R_{wire} \cdot L \cdot (C_{wire} \cdot L + C_v)}{R_{wire} \cdot L \cdot (C_{wire} \cdot L + C_v + C_v)}$$

(3.6)

After finding x for a zero skew merge using Eq (3.6), the distance from u to the tapping point can be computed as xL, which is shown in Figure 3.2(a). The embedding locations for a zero skew merge can be represented as merging segments (ms), which is shown in Figure 3.2(b). Note that a detour wire is required to be inserted to balance the delay of the subtrees when x < 0 or x > 1 conditions are obtained. Next, the maximum propagation delay of the subtree r is updated to be the maximum of  $t_{u,r}^{max}$  and  $t_{v,r}^{max}$ , i.e.,  $t_r^{max} = \max\{t_{u,r}^{max}, t_{v,r}^{max}\}$ . Consequently, a zero skew clock tree can be constructed by iteratively performing a zero-skew merge on a pair of subtrees until a single subtree is obtained.

Similar to the zero skew merges, merges for non-zero skew constraints can be performed to construct BSTs and USTs under the Elmore delay model. This can be achieved by propagating both the maximum and minimum downstream delay of the subtrees as in Eq (3.5). Let  $t_{u,r}^{min}$  and  $t_{v,r}^{min}$  be the minimum downstream delay through the path from r to u and v, respectively. Using the maximum and minimum downstream delay of subtrees, multiple equations as in Eq (3.6) can be formulated and solved to determine the possible embedding locations that ensure to meet  $|t_{u,r}^{max} - t_{v,r}^{min}| < skew_{u,v}$  and  $|t_{v,r}^{max} - t_{u,r}^{min}| < skew_{v,u}$ . Let  $x^+$  and  $x^-$  be the maximum and minimum possible x value that meets the skew constraints. While performing merge operations in the construction of BSTs and USTs, there exists a range of possible x values instead of a single x value due to that a non-zero skew is allowed to be utilized. Therefore, the skew constraints are guaranteed to be satisfied by selecting any x in the range of  $[x^-, x^+]$ . The embedding locations for a non-zero skew merge are represented using merging regions (mr), which is shown in Figure 3.2(c).

In the next section, we review a well-known algorithm to construct clock trees with buffers, which guarantees to meet both the skew constraints and the transition time constraint under the Elmore delay model.

Figure 3.2: a) A pair of subtrees and the embedding location are illustrated. b) The illustration of embedding locations as merging segments (ms) of the corresponding nodes in (a) for a zero skew merge. c) The illustration of embedding locations as merging regions (mr) of the corresponding nodes in (a) for a non-zero skew merge.

#### 3.2.2 Deferred merge embedding (DME) Algorithm

In [1, 4, 23], DME algorithm is proposed to construct ZSTs. The DME algorithm is extended to construct BSTs [6] and USTs [22]. Given a clock tree topology and a set of clock sinks, the DME algorithm constructs a clock tree while ensuring to meet the skew constraints under the Elmore delay model. The algorithm is based on first iteratively performing a bottom-up merging of subtrees phase and insertion of buffers phase. Next, a top-down embedding phase is performed to determine the exact locations of the internal nodes in each subtree.

Merging of subtrees: The bottom-up merging of subtrees phase is based on iteratively merging the pair of subtree (or clock sinks) that requires minimum wirelength to be joined while meeting the skew constraint under the Elmore delay model. The embedding locations for each pair of subtree is determined using the procedure explained in Section 3.2.1 and the corresponding pair of subtree is merged at the embedding location. The merging process is facilitated by a nearest neighbour graph (NNG) [5]. An NNG is used to capture the subtrees and the wirelength distances between the pairs of subtrees. Iteratively, the pair of subtrees that require minimum amount of wirelength

to be joined is selected to be merged. The transition time is evaluated after each pair of subtrees have been merged. If the transition time constraint is violated, subtrees are unmerged and locked for further merging operations. Merging operations are performed until all the subtrees are locked.

**Insertion of buffers:** The input to the insertion of buffers step is a set of locked subtrees from the merging of subtrees step. For each subtree, a minimum sized buffer that can drive the locked subtree (without violating the transition time constraint) is inserted at the root. Next, a stem wire is inserted between the buffer and the subtree [4].

The merging of subtrees and the insertion of buffers steps are repeated until there is one single subtree left. Finally, a top-down embedding phase is performed to determine the exact locations (x-y coordinates) of each internal node within each subtree. More details about the DME algorithm and its variants are in [1, 4, 6, 22, 23, 26].

## 3.3 Clock tree optimization

Clock tree optimization (CTO) is a process that is performed to eliminate the timing violations that are obtained after the CTS process. State-of-the-art CTO techniques are based on specifying and realizing delay adjustments using buffers and detour wires to remove the timing violations [30, 38, 39]. In this section, we first present how the slacks in the timing constraints are captured (see Section 3.3.1). Next, we explain how delay adjustments are specified to remove the timing violations (see Section 3.3.2).

# 3.3.1 Timing slacks under OCVs

After a clock tree has been constructed, the slack in the constraints can be computed, as follows:

$$setup\_slack_{ij} = t_j - t_i + T - t_j^S - t_{ij}^{CQ} - t_{ij}^{max} - \delta_i - \delta_j,$$

$$(3.7)$$

$$hold\_slack_{ij} = t_i - t_j + t_{ij}^{CQ} + t_{ij}^{min} - t_j^H - \delta_j - \delta_i,$$

$$(3.8)$$

where  $setup\_slack_{ij}$  and  $hold\_slack_{ij}$  are respectively the slacks in the setup and hold time constraints in Eq (2.1) and Eq (2.2). A negative slack implies a violation of a timing constraint while a positive slack implies available margins in a timing constraint.  $\delta_i$  and  $\delta_j$  are the timing deteriorates that are introduced by OCV.

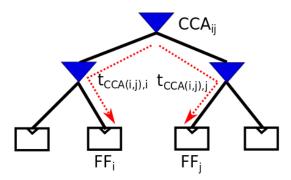

Figure 3.3: The illustration of the path that introduces OCV into the timing constraints between  $FF_i$  and  $FF_j$ .

The timing deteriorates  $\delta_i$  and  $\delta_j$  are dependent on the distance between FF<sub>i</sub> and FF<sub>j</sub> in the clock tree topology. A clock tree containing the flip-flops FF<sub>i</sub> and FF<sub>j</sub> is illustrated in Figure 3.3. Let the closest common ancestor (CCA) between FF<sub>i</sub> and FF<sub>j</sub> in the clock tree be denoted CCA(i,j) [35]. Based on the model in [39],  $\delta_i$  and  $\delta_j$  are equal to  $c_{ocv} \cdot t_{CCA(i,j),i}$  and  $c_{ocv} \cdot t_{CCA(i,j),j}$ , respectively.  $t_{CCA(i,j),i}$  and  $t_{CCA(i,j),j}$  are the propagation delays from the CCA(i,j) to FF<sub>i</sub> and FF<sub>j</sub>, respectively.  $c_{ocv}$  is a parameter determined by circuit simulations.

The slack in the timing constraints can be captured in a slack graph (SG) [30]. In an SG G = (V, E), the vertices V represent clock sinks and the edge weights E represent the slack in the timing constraints. An edge  $e_{ij}$  with weight  $w_{ij} = setup\_slack_{ij}$  is added for each setup time constraint. An edge  $e_{ji}$  with weight  $w_{ji} = hold\_slack_{ij}$  is added for each hold time constraint. The timing quality of a clock tree is measured in total negative slack (TNS) and worst negative slack (WNS), i.e., the sum and the maximum of the negative timing slacks in Eq (3.7) and Eq (3.8).

#### 3.3.2 Predicted timing quality and CTO

Timing violations in constructed clock trees are typically eliminated by realizing non-negative delay adjustments [12, 30, 38, 39]. A delay adjustment is a change of the propagation delay through a branch in the clock tree. Note that the use of delay adjustments is equivalent to specifying latency constraints in the form of points [38, 39] or ranges [30] for the clock sinks.

Let  $\triangle_k \ge 0$  be a delay adjustment at a location k in a clock tree. Delay adjustments are typically restricted to locations where buffers are placed in the topology to avoid disrupting the overall timing [39]. Next, the final timing quality is predicted by specifying a set of delay adjustments using an LP formulation, as follows [30, 39]:

$$\min \quad c_t \sum_{k \in B} \triangle_k + c_{wns} P_{wns} + c_{tns} P_{tns}$$

$$s.t. \sum_{k \in path(CCA(i,j),i)} (1 + c_{ocv}) \triangle_k - \sum_{k \in path(CCA(i,j),j)} (1 - c_{ocv}) \triangle_h - s_{ij} \le w_{ij},$$

$$s_{ij} \le P_{wns}, \quad (i,j) \in E,$$

$$\sum_{(i,j) \in E} s_{ij} = P_{tns},$$

$$(3.9)$$

where path(i, CCA(i, j)) and path(j, CCA(i, j)) respectively denote the buffers on the paths from

CCA(i,j) to FF<sub>i</sub> and FF<sub>j</sub>.  $w_{ij}$  is the weight of an edge in the SG.  $s_{ij} \ge 0$  is a timing violation that is not eliminated by realizing the specified delay adjustments.  $P_{tns}$  and  $P_{wns}$  are respectively the predicted TNS and WNS that is achieved by realizing the specified delay adjustments. The  $c_t$ ,  $c_{wns}$  and  $c_{tns}$  parameters are used to balance the different terms in the objective function. The  $(1+c_{ocv})$  and  $(1-c_{ocv})$  factors account for the timing deteriorates introduced by the specified delay adjustments.

## 3.4 Gate sizing and layer assignment

Gate sizing and layer assignment can be performed to save power while meeting constraints on the maximum latency (or propagation delay). Buffer sizing and layer assignment for zero skew and bounded skew clock trees has been studied in [29, 37, 41, 48]. Buffer sizing for USTs was performed using a Taylor expansion and sequential linear programming in [33, 48]. Nevertheless, it is difficult to handle discrete buffer sizes and layer assignments using linearization. In Section 3.4.1, we explain an algorithm that is commonly used to perform discrete gate sizing and layer assignment.

#### 3.4.1 Van Ginneken's algorithm

Van Ginneken's algorithm is a well known dynamic programming algorithm that minimizes the latency of an RC tree using buffer sizing and layer assignment under the Elmore delay model [43]. In [36], the algorithm was extended to find all Pareto optimal solutions in terms of power consumption and latency while considering slew propagation. Moreover, it is straightforward to set different latency constraints for different clock sinks.

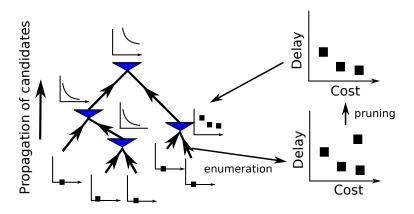

The algorithm solves the problem of selecting a buffer size for each buffer and a layer assignment

for each wire in a clock tree by propagating candidate solutions from the leaf nodes to the source node, which is illustrated in Figure 3.4. Each candidate  $c_k$  stores the maximal downstream delay  $d_k$ , non-shielded downstream capacitance  $cap_k$ , and cost in terms of total capacitance  $cost_k$ , i.e.,  $c_k = (d_k, cap_k, cost_k)$  [36]. First, a candidate solution with zero maximum downstream delay is created at each clock sink. Both the non-shielded capacitance and the cost are set equal to the sink capacitance, which is illustrated in the bottom-left of Figure 3.4.

Figure 3.4: Extension of van Ginneken's algorithm [36].

The candidate solutions at the sinks are then propagated up towards the root of the tree. When a candidate solution is propagated through an edge (buffer or wire), all possible realizations (buffer sizes or layer assignments) are enumerated as candidates to realize the edge, shown in the bottom-right of Figure 3.4. New candidates are also formed when two branches in the clock tree are joined. Pruning is applied to eliminate non-Pareto optimal solutions, which is shown in the top-right of Figure 3.4. Next, the minimum cost candidate solution that meets a defined latency requirement is selected at the root. Lastly, the size for each buffer and the layer assignment for each wire is determined based on the selected candidate.

## 3.5 Techniques of handling OCVs

In this section, an overview of previous works on the construction of clock trees under the influence of OCVs is presented. Most common approaches to handle the OCVs in the literature are: i) inserting safety margins into the timing constraints before (or during) the clock tree synthesis, ii) applying a clock tree optimization phase to an initially constructed clock tree in order to eliminate the timing violations, and iii) reconstructing the topology of a clock tree to reduce the effects of OCVs.

Techniques of handling OCVs by inserting safety margins before (or during) the clock tree synthesis process have been explored in [22, 32, 58]. The insertion of uniform safety margins was investigated in [22, 32]. The limitation of that approach is that the required safety margins depend on the clock tree topology and are therefore non-uniform. Consequently, the use of non-uniform safety margins results in that many timing constraints will have excessive (or inadequate) timing margins inserted, which translates into substantial hardware overheads (or timing violations). To reduce the overheads, the magnitude of the safety margins can be tailored to the clock tree topology during the synthesis process [31, 58]. Unfortunately, these techniques still result in clock trees with timing violations [58] or unacceptable overheads [31].

The state-of-the-art methodology for synthesizing clock networks consists of a CTS phase and a CTO phase, which are detailed in Section 3.2 and Section 3.3, respectively. In the CTS phase, an initial clock tree is first constructed. Next, the impact of the OCVs and the associated timing violations are determined, which is explained in Section 3.3.1. An aggressive CTO phase is subsequently applied to eliminate all timing violations [12, 30], which is based on specifying and realizing delay insertions as explained in Section 3.3.2. The delay insertions improve timing by redistributing timing margins from satisfied to unsatisfied timing constraints. While CTO is capable of significantly improving the timing quality of most clock trees, there is no guarantee that

the optimization process will converge to a solution without timing violations. In particular, it may be impossible to close timing if the quality of the initial clock tree is poor. Advanced CTO techniques have recently been investigated to solve this challenge. The reconstruction of the clock tree topology with the objective of minimizing latency or placing certain clock sinks close in the topology was explored in [39, 42, 55]. Nevertheless, CTO flows are still time consuming and often require costly manual intervention. This stems from that the state-of-the-art design flows consider the impact of OCVs too late in the synthesis process.

In Chapter 4, a framework that can realize both positive and negative delay adjustments using buffer sizing and layer assignment is proposed. In addition, a clock tree synthesis methodology that can account for the effects of OCVs early in the synthesis flow is proposed in Chapter 5.

#### 3.6 Clock network synthesis for multiple modes of operations

Meeting tight skew constraints under the influence of PVT variations is particularly challenging for circuits that are required to operate in low and high performance modes. In each mode, the timing constraints are drastically different. For the functional correctness of the circuit, clock networks must be synthesized such that the clock signal is delivered meeting timing constraints in both modes of operation under variations.

Many recent studies are focused on constructing clock trees that utilize a combination of guard-bands and useful skew to satisfy timing constraints under the variations in multiple modes [34]. However, for circuits with strict requirements on the clock frequency (in the high performance modes), it may be impossible to satisfy the timing constraints using a clock network with a tree topology.

As described in Section 2.2, the robustness to variations of a clock network is highly dependent on

the topology. The clock networks with a near-tree structure provides robustness to variations while the power consumption is similar to that of a clock tree. In the past decade, clock networks with near-tree topologies have been investigated, which promise significant improvements in robustness while the power consumption is similar to that of a clock tree [9, 13, 15, 16, 24, 35]. In [13, 15, 24], near-tree structures were constructed by inserting cross-links. In [35], multiple tree structures were fused together in order to create a multilevel fusion tree. In [9], a locally-merged structure was formed by fusing subtrees at internal nodes of a clock tree. The fusion was performed at internal nodes instead of at the clock sinks to reduce hardware overheads. A drawback of all near-tree structures is that there are multiple gates driving the same net of wires, which may result in short circuit current. Moreover, the same topology is used in every operational mode, despite that the robustness provided by a near-tree is only required in the high performance modes. It is easy to understand that a clock network with a tree topology could easily meet the timing constraints with much smaller power in the low performance modes.

In this dissertation, we addressed the problem of constructing clock networks for multiple modes of operations under variations, and proposed a new synthesis methodology to solve this problem in Chapter 6.

# CHAPTER 4: LATENCY CONSTRAINT GUIDED BUFFER SIZING AND LAYER ASSIGNMENT FOR CLOCK TREES WITH USEFUL SKEW

#### 4.1 Introduction

Closing timing using CTO is a tremendously challenging problem that may require designer intervention. The timing constraints must be satisfied even while the circuit is under the influence of OCVs. In addition, power consumption is a key design constraint in the advanced technology nodes. To meet both timing constraints and power constraints, it is essential to utilize every available timing margin by exploiting useful skew. In this chapter, we present a latency constraint guided buffer sizing and layer assignment framework for clock trees with useful skew, called the (BLU) framework. The proposed framework is applied after an initial clock tree has been constructed, and before traditional CTO is applied. The key idea is to perform a CTO by realizing delay adjustments using buffer sizing and layer assignment. The proposed framework can realize negative delay adjustments and handle discrete buffer sizes.

#### 4.1.1 Motivation and the overview of the BLU framework

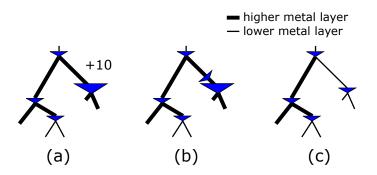

A delay adjustment is illustrated in Figure 4.1(a). The specified delay adjustments are traditionally realized by inserting delay buffers (see Section 3.3), which is shown in Figure 4.1(b). In contrast, this chapter proposes to realize delay adjustments using buffer sizing and layer assignment, which is illustrated in Figure 4.1(c). Compared with buffer insertion, layer assignment is a more gentle method of realizing delay adjustments that may result in lower power consumption.

This chapter is based on the paper that is published at 2019 Asia and South Pacific Design Automation Conference [59] © 2019 ACM.

Figure 4.1: (a) A specified delay adjustment. (b) Delay adjustment realized by buffer insertion. (c) Proposed realization of delay adjustments using buffer sizing and layer assignment.

The BLU framework specifies a set of delay adjustments and predicts the final timing quality ( $P_{tns}$ ,  $P_{wns}$ ) that would be achieved using traditional CTO.  $P_{tns}$  and  $P_{wns}$  are respectively the predicted TNS and WNS. Next, the delay adjustments are translated into latency constraints without degrading  $P_{tns}$  and  $P_{wns}$ . Using the specified latency constraints, buffer sizing and layer assignment is conducted using an extension of van Ginneken's algorithm, i.e., delay adjustments are realized while reducing the total capacitive cost. To further reduce power consumption, the BLU framework attempts to relax each point constraint into a latency range without degrading  $P_{tns}$  and  $P_{wns}$ . Moreover, a method of improving  $P_{tns}$  and  $P_{wns}$  by specifying tight latency constraints using negative delay adjustments is proposed. Lastly, traditional CTO is applied to realize remaining delay adjustments such that TNS and WNS are reduced to  $P_{tns}$  and  $P_{wns}$ .

Compared with in [33, 48], the BLU framework allows buffer sizing and layer assignment to be performed while utilizing discrete buffer and interconnect libraries. We consider the BLU framework to be orthogonal to the techniques of realizing negative delay adjustments by reconstructing the topology of a clock tree in [39, 42].

The experimental results demonstrate that the BLU framework is capable of reducing total capacitance, TNS and WNS with 13%, 58%, and 20%, respectively.

#### 4.1.2 Proposed framework

Non-negative delay adjustments are realized by inserting buffers and detour wires during CTO, which translates into overhead in terms of total capacitance. In contrast, van Ginneken's algorithm (with the extension in [36]) is capable of trading-off maximum delay for total capacitive cost. The key idea of the BLU framework is to use buffer sizing and layer assignment to realize delay adjustments. Consequently, the proposed framework has the potential to improve power consumption while reducing TNS and WNS to  $P_{tns}$  and  $P_{wns}$ , respectively. Extensions to further improve performance are presented in Section 4.2.

Van Ginneken's algorithm requires maximum delay (or latency) constraints. The latency constraints are obtained from the delay adjustments specified using Eq (3.9). The obtained constraints are in the form of points. Therefore, each delay adjustment is required to be realized exactly. Let  $l_i$  denote the upper bound of the latency constraint to sink i. The constraints requires each arrival time  $t_i$  to be equal to the latency constraint  $l_i$ . However, van Ginneken's algorithm only ensures that  $t_i \leq l_i$ . Nevertheless, it is expected that the arrival times  $t_i$  will be close to  $l_i$ , as increasing the arrival time (or delay) typically results in a reduction of total capacitive cost. Moreover, the difference between  $t_i$  and  $l_i$  can be realized through traditional CTO after the proposed framework has been applied.

#### 4.2 The BLU framework

The baseline of the BLU framework is presented in Section 4.2.1. In Section 4.2.2, point constraints are relaxed into range constraints to save capacitive cost. In Section 4.2.3, the latency constraints are tightened to improve  $P_{tns}$  and  $P_{wns}$ .

## 4.2.1 Baseline of the BLU framework

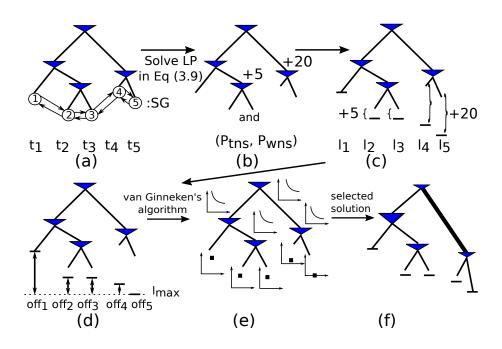

Figure 4.2: (a) SG. (b)  $P_{tns}$  and  $P_{wns}$  and delay adjustments. (c) latency constraints. (d) offsets. (e) van Ginneken's algorithm. (f) selected candidate solution.

The BLU framework is illustrated with an example in Figure 4.2. First, an SG is formed based on the timing and the topology of the initial clock tree, as illustrated in Figure 4.2(a). Next, the LP formulation in Eq (3.9) is solved to specify delay adjustments and to predict  $P_{tns}$  and  $P_{wns}$ , which is illustrated in Figure 4.2(b). The latency constraint  $l_i$  for each clock sink i is obtained by floating down each delay adjustments to the clock sinks and combining the adjustments with the current arrival time of the clock signal, which is shown in Figure 4.2(c). The maximum latency constraint is denoted  $l_{max}$ . Next, an offset  $off_i$  equal to,  $l_{max} - l_i$ , is introduced for each clock sink, as illustrated in Figure 4.2(d). A candidate solution  $c_i$  (in van Ginneken's algorithm) is created at each clock sink i with a maximum downstream delay equal to  $off_i$ , which is illustrated in Figure 4.2(e). Subsequently, van Ginneken's algorithm is applied and the minimum cost candidate solution that satisfies  $l_{max}$  is selected at the root. The latency constraint  $l_{max}$  at the root ensures that

each arrival time  $t_i$  is smaller than  $l_i$ . Moreover, it is guaranteed that at least one candidate solution will satisfy  $l_{max}$  at the root of the clock tree, i.e., the initial clock tree. Figure 4.2(f) shows the clock tree after buffer sizing and layer assignment has been performed with respect to the selected candidate solution. Compared with the clock tree in 4.2(a), the clock tree in Figure 4.2(f) will have the same predicted timing quality but smaller capacitive cost.

## 4.2.2 Relaxing the latency constraints

In this section, the BLU framework is extended to enable further savings in capacitive cost by relaxing the point constraints into latency range constraints. The latency constraints specified by Eq (3.9) are shown in Figure 4.3(a). The relaxed latency range constraints are shown in Figure 4.3(b). The BLU framework specifies the range constraints while guaranteeing that  $P_{tns}$  and  $P_{wns}$  are not degraded if every arrival time  $t_i$  is within the respective latency range.  $l_i^r$  is the relaxed latency constraint for clock sink i and  $l_i \leq l_i^r$ .

Figure 4.3: (a) Latency constraints. (b) Relaxed latency constraints. (c) Method to find  $l_i^r$ .

The method used to find the latency range constraint is illustrated in Figure 4.3(c). First, a predicted slack graph (pSG) is formed [42]. A pSG, captures the predicted slacks in the timing constraints after the delay adjustments specified by Eq (3.9) are realized. Moreover, the predicted slack violations  $s_{ij}$  are added to the respective edges in the pSG such that all edges in the pSG are

non-negative. Next, a relaxed latency constraint  $l_i^r$  is found, as follows:

$$l_i^r = l_i + \frac{w_{ki}^{min}}{(1 + c_{ocv})},\tag{4.1}$$

where  $w_{ki}^{min}$  is the edge with the minimum weight of all the fan-in edges of node i in the pSG, i.e.,  $e_{ki} \in E$ . The  $(1 + c_{ocv})$  factor used to compensate for the increased timing deteriorates  $\delta_i$  and  $\delta_j$ .

#### 4.2.3 Tightening the latency constraints

In this section, the BLU framework is extended by allowing negative delay adjustments to be specified in the clock tree, which may improve  $P_{wns}$  and  $P_{tns}$ , as illustrated in Figure 4.4.

Figure 4.4: (a) Delay adjustments specified by Eq (3.9). (b) Clock tree after van Ginneken's algorithm.  $l_{max}$  is violated by the path marked with a red dashed line. (c) Generation of a delay adjustment constraint.

Compared with non-negative delay adjustments that are relatively easy to realize, it may be impossible to physically realize negative adjustments [39]. Consequently, it may be impossible to satisfy the latency constraint  $l_{max}$  using Van Ginneken's algorithm, which results in that TNS and

WNS cannot be reduced to the predicted  $P_{tns}$  and  $P_{wns}$  using traditional CTO. The BLU framework solves this challenge by generating *delay adjustment constraints* to the LP formulation in Eq (3.9), which ensures that only negative delay adjustments that can be realized are specified.

First, Eq (3.9) is solved while allowing both non-negative and negative delay adjustments, which is shown in Figure 4.4(a). Negative delay adjustments are facilitated by replacing the expression  $c_t \sum_{k \in B} \triangle_k$  with  $c_p \sum_{k \in B} \triangle^+ - c_n \sum_{k \in B} \triangle^-$  in Eq (3.9), where  $\triangle^+ \ge 0$  and  $\triangle^- \ge 0$  are non-negative and negative delay adjustments, respectively.  $c_p$  and  $c_n$  are user defined parameters. Next, the remainder of the BLU framework is applied and the resulting clock tree is shown in Figure 4.4(b). If any candidate solution satisfies the latency constraint  $l_{max}$  at the root, the same flow as for non-negative delay adjustments is applied (see Section 4.2.1).

If no candidate solution meets the latency constraint  $l_{max}$ , the BLU framework selects the candidate solution that is closest to satisfying the latency constraint. Let  $l_{vio}$  be the violation of the latency constraint and let path(s,k) be the path from the source to clock sink k that created the largest latency violation, which is illustrated with a dashed red line in Figure 4.4(b). It is straightforward to find the path based on backtracking the candidate solutions generated by van Ginneken's algorithm. Next, a delay adjustment constraint is generated to force the delay adjustments on the path(s,k) to be  $l_{vio}$  larger than currently specified, as follows:

$$\sum_{h \in path(s,k)} \triangle_h \ge L_{sk} + l_{vio},\tag{4.2}$$

where  $L_{sk}$  is the sum of the delay adjustments on the path from the source to sink k in the current solution of Eq (3.9).  $\triangle_h$  are variables in Eq (3.9).

A new set of latency constraints are specified by solving the LP formulation in Eq (3.9) in combination with the delay adjustment constraints in Eq (4.2), which is shown in Figure 4.4(c). The

process is iteratively repeated until the latency constraint  $l_{max}$  is satisfied.  $P_{tns}$  and  $P_{wns}$  are increased in each iteration as additional constraints are introduced to the LP formulation. Latency constraints are also introduced at internal nodes to speed up the convergence process. Violations of latency constraints at internal nodes are accounted for by modifying the  $cost_k$  of a candidate to be equal to  $cost_i = cap^{tot} + c_{vio} \cdot l_{vio}^{tot}$ , where  $l_{vio}^{tot}$  is the sum of the violations in the downstream subtree and  $c_{vio}$  is a user specified parameter.

## 4.3 Methodology

The flow of the framework is illustrated in Figure 4.5. First, an initial clock tree is constructed using CTS [30, 34], which is the input to the BLU framework. Next, the BLU framework is performed, as described in Section 4.2. Lastly, CTO is performed to reduce TNS and WNS to  $P_{tns}$  and  $P_{wns}$  using the techniques in [30]. The high level flow for the BLU framework is outlined below.

Figure 4.5: Proposed flow for the BLU framework.

A specify latency point constraints step is performed to predict  $P_{tns}$  and  $P_{wns}$  and to specify a set of latency constraints in the form of points. The point constraints are extended into latency ranges

in a *specify latency range constraints* step. Next, *buffer sizing and layer assignment* step is performed using an extension of van Ginneken's algorithm that utilizes three-dimensional sampling and transition time constraints [40]. If the latency constraints are satisfied, buffer sizing and layer assignment is performed. If the latency constraints are not satisfied, a *generation of delay adjustment constraints* step is performed to introduce delay adjustment constraints. Next, the framework returns to the specify point constraints step. The process is iteratively repeated until all the latency constraints are satisfied.

#### 4.4 Experimental evaluation

The experimental evaluation is performed on a quad core 3.4 GHz Linux machine with 32GB of memory. The proposed algorithms are implemented in C++. IBM ILOG CPLEX is used to solve the LP formulations in the framework [66].

Table 4.1: Circuits in [31].

| Circuit      | Sinks | Skew constraints |

|--------------|-------|------------------|

| (name)       | (num) | (num)            |

| s1423        | 74    | 78               |

| s5378        | 179   | 175              |

| s15850       | 597   | 318              |

| msp          | 683   | 44990            |

| fpu          | 715   | 16263            |

| usbf         | 1765  | 33438            |

| dma          | 2092  | 132834           |

| pci bridge32 | 3578  | 141074           |

| ecg          | 7674  | 63440            |

| des peft     | 8808  | 17152            |

| eht          | 10544 | 450762           |

| aes          | 13216 | 53382            |

The evaluation is performed using the framework proposed in [31], which is an extension of the problem formulation used in the ISPD 2010 contest [20]. The properties of the buffers and the

wires are obtained from the 45 nm technology used in the ISPD 2010 contest. The non-uniform skew constraints and the sink locations are generated using Synopsys DC and ICC. Moreover, there is a transition time constraint at each buffer and clock sink. A summary of the circuits is shown in Table 4.1. We construct and compare eight different tree structures to evaluate the BLU framework.

(1) The UST structure is a clock tree constructed using the CTS engine provided by the authors in [31]. (2) The UST-CTO structure is the structure obtained by applying the CTO in [30] to the UST structure. (3) The UST-P structure is obtained by applying the BLU framework to the UST structure using point constraints, i.e., the framework presented in Section 4.2.1. (4) The UST-P-CTO is the structure obtained by applying CTO to the UST-P structure. (5) The UST-R structure is the UST-P structure obtained by relaxing the point constraints into latency ranges, i.e., the method described in Section 4.2.2. (6) The UST-R-CTO structure is the structure obtained by applying CTO to the UST-R structure. (7) The UST-RT structure is the UST-R structure combined with the technique of tightening the constraints proposed in Section 4.2.3. (8) The UST-RT-CTO structure is obtained by applying CTO to the UST-RT structure.

We evaluate the tree structures in terms of total capacitance, timing performance and run-time. It is well known that the power consumption of a clock tree is highly correlated with the total capacitance. The timing quality is evaluated using TNS and WNS, which are computed using Eq (3.7) and Eq (3.8);  $P_{tns}$  and  $P_{wns}$  are obtained from solving the Eq (3.9). The arrival times  $t_i$  and  $t_j$  are obtained using NGSPICE simulations. All tree structures in the experimental results satisfy the same transition time constraints as in [31]. In Section 4.4.1, we evaluate the BLU framework on the clock trees in [31], which only requires non-negative delay adjustments. In Section 4.4.2, we evaluate the BLU framework on the clock trees with strict timing constraints, which utilizes both non-negative and negative delay adjustments.

Table 4.2: Evaluation of various tree structures in terms of total capacitance.

| Circuit | Capacitance (pF) |              |        |           |        |           |  |  |  |  |

|---------|------------------|--------------|--------|-----------|--------|-----------|--|--|--|--|

| (name)  | UST [31]         | UST-CTO [31] | UST-P  | UST-P-CTO | UST-R  | UST-R-CTO |  |  |  |  |

| s1423   | 3.43             | 3.43         | 3.02   | 3.02      | 2.96   | 2.96      |  |  |  |  |

| s5378   | 5.65             | 5.65         | 5.04   | 5.04      | 4.87   | 4.87      |  |  |  |  |

| s15850  | 18.09            | 18.85        | 15.84  | 16.86     | 15.77  | 16.62     |  |  |  |  |

| msp     | 1.41             | 1.41         | 1.35   | 1.35      | 1.20   | 1.20      |  |  |  |  |

| fpu     | 1.60             | 1.60         | 1.52   | 1.52      | 1.35   | 1.35      |  |  |  |  |

| usbf    | 4.55             | 4.55         | 4.14   | 4.14      | 4.07   | 4.07      |  |  |  |  |

| dma     | 5.06             | 5.17         | 4.49   | 4.65      | 4.44   | 4.56      |  |  |  |  |

| pci     | 7.65             | 7.65         | 7.02   | 7.06      | 6.71   | 6.71      |  |  |  |  |

| ecg     | 23.44            | 23.66        | 20.39  | 20.96     | 20.54  | 20.84     |  |  |  |  |

| des     | 18.82            | 18.84        | 16.58  | 16.62     | 16.62  | 16.64     |  |  |  |  |

| eht     | 20.14            | 20.14        | 17.85  | 17.85     | 17.62  | 17.62     |  |  |  |  |

| aes     | 151.70           | 152.91       | 132.91 | 135.28    | 132.91 | 135.60    |  |  |  |  |

| Norm.   | 0.99             | 1.00         | 0.89   | 0.90      | 0.87   | 0.87      |  |  |  |  |

Table 4.3: Evaluation of various tree structures in terms of runtime.

| Circuit | Runtime (mins) |              |       |           |       |           |  |  |  |  |

|---------|----------------|--------------|-------|-----------|-------|-----------|--|--|--|--|

| (name)  | UST [31]       | UST-CTO [31] | UST-P | UST-P-CTO | UST-R | UST-R-CTO |  |  |  |  |

| s1423   | 0.0            | 0.1          | 0.0   | 0.1       | 0.1   | 0.1       |  |  |  |  |

| s5378   | 0.0            | 0.1          | 0.1   | 0.1       | 0.1   | 0.1       |  |  |  |  |

| s15850  | 0.2            | 2.3          | 0.3   | 14.7      | 0.2   | 2.0       |  |  |  |  |

| msp     | 0.0            | 0.0          | 0.5   | 0.0       | 3.7   | 0.1       |  |  |  |  |

| fpu     | 0.0            | 0.2          | 0.7   | 0.0       | 1.2   | 0.0       |  |  |  |  |

| usbf    | 1.0            | 0.2          | 0.4   | 0.2       | 2.4   | 0.2       |  |  |  |  |

| dma     | 1.0            | 2.1          | 1.1   | 2.5       | 10.3  | 2.1       |  |  |  |  |

| pci     | 2.0            | 0.2          | 2.3   | 0.8       | 15.8  | 0.2       |  |  |  |  |

| ecg     | 8.0            | 11.3         | 1.7   | 15.5      | 5.0   | 12.8      |  |  |  |  |

| des     | 4.0            | 1.1          | 1.3   | 0.9       | 3.9   | 0.4       |  |  |  |  |

| eht     | 8.0            | 0.6          | 28.6  | 0.4       | 107.2 | 0.4       |  |  |  |  |

| aes     | 45.0           | 110.5        | 7.2   | 65.7      | 15.4  | 84.3      |  |  |  |  |

| Norm.   | 0.30           | 1.00         | 0.60  | 1.10      | 1.20  | 1.70      |  |  |  |  |

## 4.4.1 Evaluation of positive delay adjustments

The total capacitance and the runtime of each structure are shown in Table 4.2 and Table 4.3, respectively. The normalized performances with respect to the UST-CTO structures are shown in the row labeled as 'Norm'. The run-times in Table 4.3 are the run-times of individual synthesis steps. The normalized run-times are the cumulative run-times. The timing performance is not shown because there are no timing violations after CTO.

First, we apply traditional CTO to the UST structures. All timing violations are eliminated at the expense of an average 1% increase in capacitive cost. Compared with the UST structures, the UST-P structures have 10% lower capacitance. The capacitance reduction stems from that van Ginneken's algorithm assigns interconnects to lower metal layers and that buffers are downsized while still meeting the transition time constraints. Next, CTO is applied to the UST-P structures. The UST-P-CTO structures have 10% lower capacitance than the UST-CTO structures, as the CTO phase only resulted in a small increase in total capacitance. The capacitive improvements come at an expense of a 10% increase in run-time.

Next, we compare UST-R structures with UST-P structures. The table shows that the UST-R structures have 2% lower capacitance than the UST-P structures. The improvement in capacitance is a result of the relaxation of point constraints into range constraints. Ideally, the UST-R structures should have better capacitive performance than the UST-P structures on all circuits. However, the sampling in van Ginneken's algorithm may result in minor capacitance fluctuations (see circuits des and aes). After CTO is applied, it can be observed that the UST-R-CTO structures have 3% lower total capacitance than the UST-P-CTO structures. The average run-time of the UST-R-CTO structures is 1.5X higher than the UST-P-CTO structures. The UST-R structures demonstrate that the BLU framework is capable of performing buffer sizing and layer assignment to reduce capacitive cost without degrading timing performance. The improvements are achieved at the

expense of overhead in run-time.

#### 4.4.2 Evaluation of negative delay adjustments