# STARS

University of Central Florida

Electronic Theses and Dissertations, 2020-

2021

# Study of MoS2/high-k Interface and Implementation of MoS2 Based Memristor for Neuromorphic Computing Applications

Durjoy Dev University of Central Florida

Part of the Electrical and Computer Engineering Commons Find similar works at: https://stars.library.ucf.edu/etd2020 University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2020- by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Dev, Durjoy, "Study of MoS2/high-k Interface and Implementation of MoS2 Based Memristor for Neuromorphic Computing Applications" (2021). *Electronic Theses and Dissertations, 2020-.* 852. https://stars.library.ucf.edu/etd2020/852

#### STUDY OF MoS<sub>2</sub>/HIGH-*k* INTERFACE & IMPLEMENTATION OF MoS<sub>2</sub> BASED MEMRISTOR FOR NEUROMORPHIC COMPUTING APPLICATIONS

by

DURJOY DEV B.Sc. Eng. (EEE) Khulna University of Engineering & Technology, 2013 M.S. North Carolina A&T State University, 2017

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the College of Engineering & Computer Science at the University of Central Florida Orlando, Florida

Fall Term 2021

Major Professor: Tania Roy

© 2021 Durjoy Dev

#### ABSTRACT

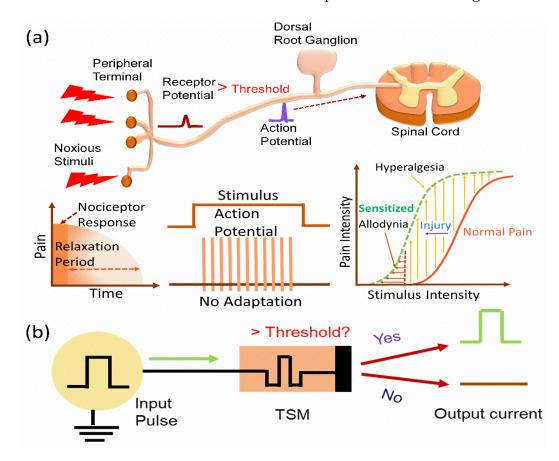

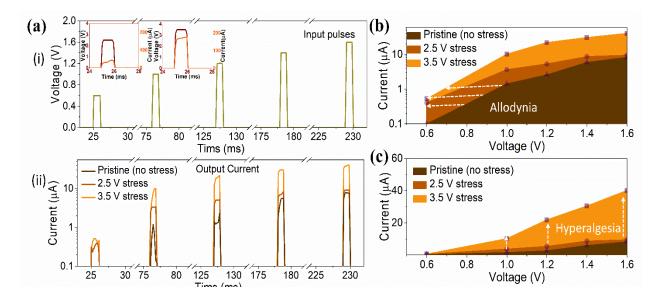

The scientific world is witnessing an unprecedented triumph of artificial neural network (ANN)- a computing system inspired by the biological neural network. With the enthralling quest for Internet of Everything (IoE), it is expected to have an unparalleled dominance of ANN in our day-to-day life. In recent times, memristor has come as an emerging candidate to realize ANN through emulating biological synapse and neuron behavior. Molybdenum disulfide (MoS<sub>2</sub>), one well-known two-dimensional (2D) transition metal dichalcogenides (TMDCs), has drawn interest for high speed, flexible, low power electronic devices since it has a tunable bandgap, reasonable carrier mobility, high Young's modulus, and large surface to volume ratio. Hence, in this work, 2D  $MoS_2$  based field effect transistor (FET) and memristor devices have been developed to evaluate the performance for advanced logic and neuromorphic computing applications. We probe the superior quality of 2D/high-κ dielectric interfaces by fabricating MoS<sub>2</sub> based FET transistors with different gate dielectrics. This low interface trap density of  $\sim 7 \times 10^{10}$  states/cm<sup>2</sup>-eV at the MoS<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> interface establishes the case for van der Waals systems where the superior quality of 2D/high-k dielectric interfaces can produce high performance electronic and optoelectronic devices. This work also demonstrates Au/MoS<sub>2</sub>/Ag threshold switching memristor (TSM) device with low threshold voltage, sharp switching, high ON-OFF ratio and endurance. A leaky integration-and-firing (LIF) neuron is implemented with this TSM. It successfully emulates the key characteristics of a biological neuron. The LIF neuron is monolithically integrated with the  $MoS_2$  based synapse device to realize a single layer perceptron operation and Boolean logic gates. The Au/MoS<sub>2</sub>/Ag TSM device also imitates a nociceptor, the single device exhibits all the key features of nociceptors including threshold, relaxation, "no adaptation" and sensitization

phenomena of allodynia and hyperalgesia. This work indicates applicability of this device in artificial intelligence systems-based neuromorphic hardware applications and artificial sensory alarm system.

To my family

#### ACKNOWLEDGEMENTS

Standing at the marginal distance from achieving the highest educational degree, I find myself indebted to so many good souls who made my PhD journey smooth and blissful. Firstly, I would like to express my sincere appreciation to my advisor Dr. Tania Roy for her continuous guidance, mentorship, encouragement, and patience throughout my PhD program. Dr. Roy has kept faith in my ability and extended her unconditional support and guidance to achieve my research goals. Her mentorship has helped me to nurture the qualities and skillsets of a competent researcher. I would like to extend my gratitude to my dissertation committee members Dr. Kalpathy B. Sundaram, Dr. Jiann-Shiun, Dr. Yeonwoong Jung and Dr. Kristopher Davis for their valuable suggestions and guidance during my dissertation.

I want to thank Dr. Sonali Das and Dr. Nitin Choudhary for providing training on different instruments and guiding me with their valuable opinions. My sincere gratitude to my present and past lab mates- Hirokjyoti Kalita, Adithi Krishnaprasad, Molla Manjurul Islam, Ricardo Martinez Martinez, , Victor Rodriguez, Karl Mama, Madison Manley, Anya Lenox, Victor Okonkwo, Haley Heldmyer for their supports, shrewd suggestions and collaborative works. I am grateful to Mashiyat Sumaiya Shawkat, Jeya Prakash Ganesan, Zhezhi He and Jean Calderon Flores for their unwavering support during our collaborative projects. I am also thankful to the collaborators Dr. Yeonwoong Jung, Dr. Parag Banerjee, Dr. Lei Zhai, Dr. Deliang Fan and Dr. Hee-Suk Chung for their support for material growth and characterizations. My heartfelt thanks to Nathan Aultman, Maria Real-Robert and Ernie Gemeinhart for their indispensable technical support. My sincere appreciation for Diana Poulalion for keeping me on the track by continuously guiding me with the requirements and deadlines to achieve the degree. I would like to thank all the staffs, faculty members of Department of Electrical and Computer Engineering and NanoScience Technology Center for being supportive and cooperative during my stay here.

I acknowledge the support from the Funding agency- National Science Foundation (Grant: NSF-ECCS-1845331) & BAE Systems: (Award no. 1020180) for this work.

Finally, I want to express my utmost gratitude to my family members for their ineffable sacrifice for me. The continuous mental support, inspiration, and appreciation from my parents even at their hardest time were my strengths and motivations during my PhD journey. My sisters and brother in laws have extended their support at all extent to keep me focused throughout my stay at abroad for the higher study. The birth of my daughter Prahi at the first year of my PhD program made me more responsible and disciplined. Last but not the least, no words can be enough to elucidate the sacrifice of my beloved wife Sutripta for my PhD. She was always there for me both at the time difficulties and success. I am blessed to have her in my life and sincerely hope to accomplish more together in future.

## **TABLE OF CONTENTS**

| LIST OF FIGURES xii                                                  |

|----------------------------------------------------------------------|

| LIST OF ACRONYMS (or) ABBREVIATIONS xxi                              |

| CHAPTER 1 INTRODUCTION                                               |

| 1.1 Two Dimensional (2D) Materials                                   |

| 1.1.1 Transition Metal Dichalcogenides (TMDCs)                       |

| 1.1.2 MoS <sub>2</sub> for post Si electronics                       |

| 1.2 Motivation                                                       |

| 1.3 Objectives                                                       |

| 1.4 Dissertation Overview                                            |

| CHAPTER 2 INTERFACE TRAP DENSITY $(D_{it})$ EXTRACTION TECHNIQUES 10 |

| 2.1 Introduction                                                     |

| 2.2 Interface Trap States                                            |

| 2.3 Interface Trap Density $(D_{it})$ Extraction Techniques          |

| 2.3.1 Low Frequency (Quasi-static) Methods 11                        |

| 2.3.2 Terman Method 12                                               |

| 2.3.3 Subthreshold Swing Method                                      |

| 2.3.4 Conductance Method14                                           |

| 2.4 MoS <sub>2</sub> /High κ Interface17                             |

| 2.4.1 High-κ Gate Dielectric                                       | 17 |

|--------------------------------------------------------------------|----|

| 2.4.2 Sources of interface traps at $MoS_2/high \kappa$ interface  | 18 |

| 2.5 Literature on MOS <sub>2</sub> Interface Trap Density          | 19 |

| 2.6 Conclusion                                                     | 22 |

| CHAPTER 3 MoS <sub>2</sub> /HIGH-κ DIELECTRIC INTERFACE EXTRACTION | 23 |

| 3.1 Introduction                                                   | 23 |

| 3.2 Device Fabrication and Characterization Techniques             | 23 |

| 3.2.1 MoS <sub>2</sub> FET Device Fabrication                      | 23 |

| 3.2.2 Electrical Characterization                                  | 25 |

| 3.3 Results & Discussions                                          | 26 |

| 3.3.1 Transfer Characteristics of MoS <sub>2</sub> FET             | 26 |

| 3.3.2 Subthreshold Swing Method for $D_{it}$ Extraction            | 26 |

| 3.3.3 Capacitance and Conductance Measurement                      | 28 |

| 3.3.4 Conductance Method for <i>D<sub>it</sub></i> Extraction      | 31 |

| 3.4 Conclusion                                                     | 35 |

| CHAPTER 4 NEUROMORPHIC COMPUTING DEVICES                           | 36 |

| 4.1 Introduction                                                   | 36 |

| 4.2 Spiking Neural Network (SNN)                                   | 37 |

| 4.3 Artificial Neuron for SNN                                      | 38 |

| 4.3.1 Leaky Integrate-and-Fire Model                          | 39  |

|---------------------------------------------------------------|-----|

| 4.4 Literature Review on 2D Materials Based Artificial Neuron | 42  |

| 4.5 Conclusion                                                | 46  |

| CHAPTER 5 ARTIFICIAL NEURON                                   | 48  |

| 5.1 Introduction                                              | 48  |

| 5.2 Device Fabrication and Characterization Techniques        | 48  |

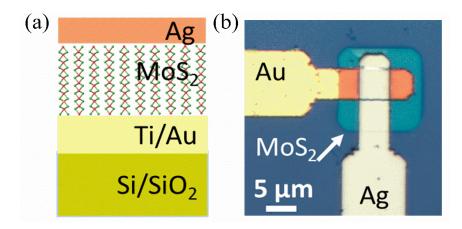

| 5.2.1 Au/MoS <sub>2</sub> /Ag Memristor Device Fabrication    | 48  |

| 5.2.2 Material Characterization                               | 50  |

| 5.2.3 Electrical Characterization                             | 50  |

| 5.3 Results and Discussion                                    | 50  |

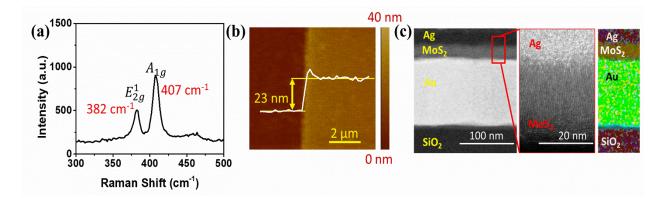

| 5.3.1 Material Characterization                               | 50  |

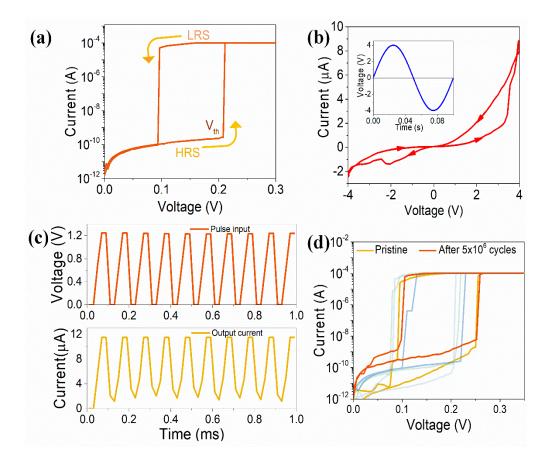

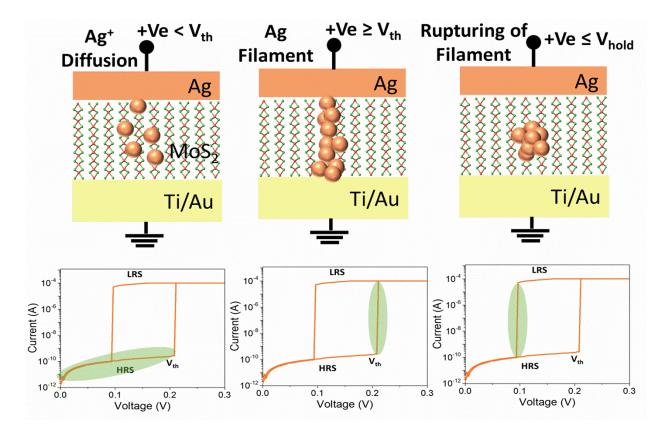

| 5.3.2 Electrical Characterization and Switching Mechanism     | 51  |

| 5.3.3 Realization of Artificial Neuron                        | 56  |

| 5.4 Conclusion                                                | 62  |

| CHAPTER 6 MONOLITHIC INTEGRATION OF ARTIFICIAL NEURON         | í & |

| SYNAPSE                                                       | 63  |

| 6.1 Introduction                                              | 63  |

| 6.2 Artificial Synapse Device                                 | 64  |

| 6.2.1 MoS <sub>2</sub> /graphene Synapse Device               | 64  |

| 6.2.2 Au/MoS <sub>2</sub> /Ti/Au Synapse Device               | 65  |

| 6.3 Electrical Characterization Techniques                       |

|------------------------------------------------------------------|

| 6.4 Results and Discussion                                       |

| 6.4.1 Single Layer Perceptron Realization67                      |

| 6.4.2 Logic Gate Realizations                                    |

| 6.5 Conclusion70                                                 |

| CHAPTER 7 ARTIFICIAL NOCICEPTOR                                  |

| 7.1 Introduction                                                 |

| 7.1.1 Literature Review on Memristor Based Artificial Nociceptor |

| 7.2 Results & Discussion                                         |

| 7.2.1 Artificial Nociceptor Realization                          |

| 7.3 Conclusion                                                   |

| CHAPTER 8 SUMMARY AND FUTURE PERSPECTIVES                        |

| 8.1 Summary                                                      |

| 8.2 Future Perspectives                                          |

| APPENDIX: COPYRIGHT PERMISSIONS                                  |

| LIST OF REFERENCES                                               |

#### LIST OF FIGURES

Figure 1: The 2D material family. Adopted with permission from the reference [18]©2018 IEEE Figure 2: The highlighted transition metals and chalcogens in the periodic table predominantly crystallize to form the 2D layered structure. Adopted with permission from the reference [25] ... 4 Figure 3: (a) Band alignment of monolayer 2D TMDCs compared with the Si and III-V materials. Adopted with permission from the reference [26] ©2015, *IEEE* (b) Chemical structure of 2 layer MoS2; thickness of monolayer MoS2 is 0.65 nm, (c) Polytypes of monolayer MoS<sub>2</sub>; trigonal prismatic (2H) and Octahedral (1T). Adopted with permission from reference [38]......5 Figure 4: (a)The position of the interface trap states in the bandgap of the semiconductor. (b) Figure 5: Equivalent circuits for conductance method (a) MOS-C with interface trap time constant  $R_{it}C_{it}$ . (b) simplified circuit of (a), (c) measured circuit (d) considering series resistance and Figure 6: (a) Device schematic – the channel is underlapped by the gate. (b) Optical microscope image; scale bar: 4  $\mu$ m.(c) The MoS<sub>2</sub>/High  $\kappa$  interface combinations for two different (AlO<sub>x</sub> and Figure 8: Transfer characteristics of the MoS<sub>2</sub> based FET (a) AlO<sub>x</sub> nucleation layer i) ZrO<sub>2</sub> gated  $MoS_2$  FET i)  $Al_2O_3$  gated  $MoS_2$  FET (b)  $SiO_x$  nucleation layer i)  $ZrO_2$  gated  $MoS_2$  FET i)  $Al_2O_3$

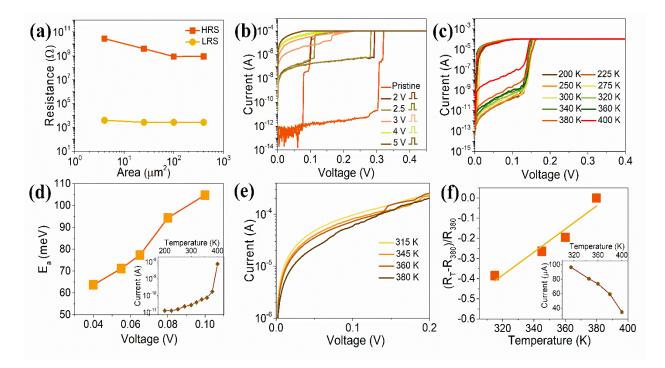

Figure 21: (a) Area dependence of LRS and HRS of Au/MoS<sub>2</sub>/Ag TSM device. (b) *I-V* characteristics of the device in pristine condition and after subjecting the device with pulses of varying voltage amplitudes of 2 V, 2.5 V, 3 V, 4 V and 5 V for 1 ms. OFF current of the device increases compared to pristine condition after pulsing the device. At 5 V device is fully formed and device remains in ON state. (c) Temperature dependent *I-V* characteristics of the pristine TSM device. (d) The activation energy at different voltages extracted from OFF-state of temperature

dependent *I-V* curves. Inset shows increasing trend of OFF-state current with increasing temperature. (e) Temperature dependent *I-V* characteristics of the TSM device at fully formed condition. (f)  $(R_T - R_{380})/R_{380}$  vs. *T* graph extracted from temperature dependent *I-V* characteristics of fully formed TSM device. At fully formed condition, current decreases with increasing temperature (inset).

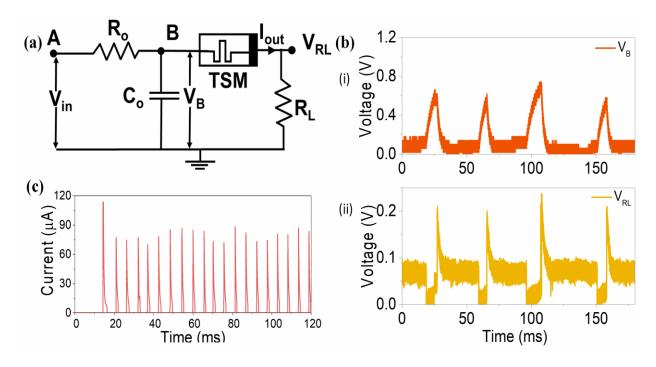

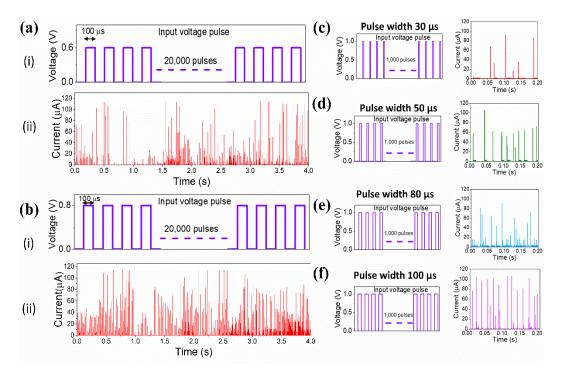

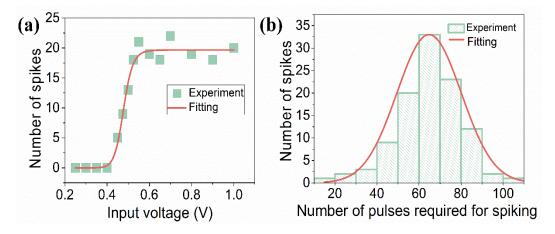

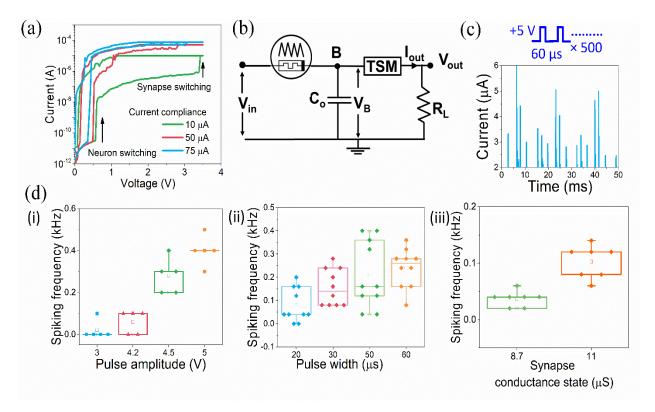

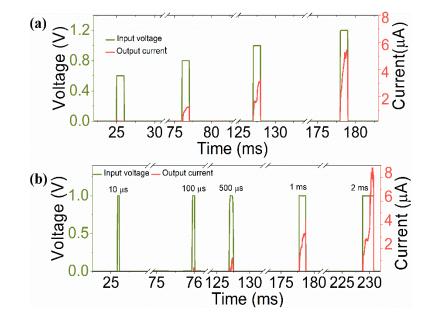

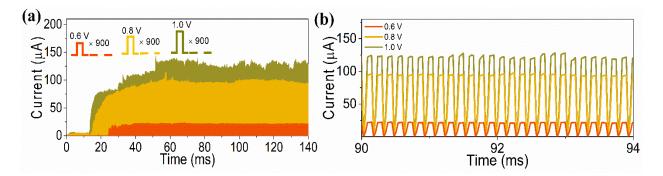

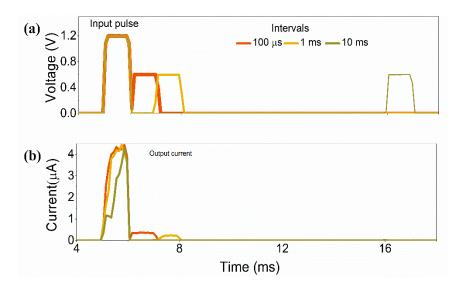

Figure 22: Realization of artificial neuron with Au/MoS<sub>2</sub>/Ag TSM device. (a) Circuit diagram for realization of artificial neuron with Au/MoS<sub>2</sub>/Ag neuron. (b) i) Voltage at node B ( $V_B$ ). With incoming pulses, capacitor accumulate charges at node B till it reaches the threshold voltage of connected TSM device. ii) Voltage across load resistor  $R_L(V_{RL})$ . As soon as potential at node B reaches the threshold value, TSM switches from HRS to LRS and capacitor discharges through TSM device and  $R_L$  to produce the output spikes. (c) Continuous output current spikes for input Figure 23: Stimulus strength-based frequency response of artificial neuron for pulse amplitude variation (a) i) Schematic of input voltage pulse train of 0.6 V. ii) Output current spikes for 0.6 V input pulse train. (b) i) Schematic of input voltage pulse train of 0.8 V. ii) Output current spikes for 0.8 V input pulse train. Stimulus strength-based frequency response of artificial neuron for pulse width variation. Input pulse scheme and output current spikes for (c) 30 µs pulse width. (d) Figure 24: Activation function and stochastic nature of Au/MoS<sub>2</sub>/Ag artificial neuron (a) The variation of number of output spikes for a given time period with increasing input pulse amplitude replicates a sigmoid activation function. (b) The variation in the number of pulses required for

generating an output spike. The variation follows a normal distribution. ...... 59

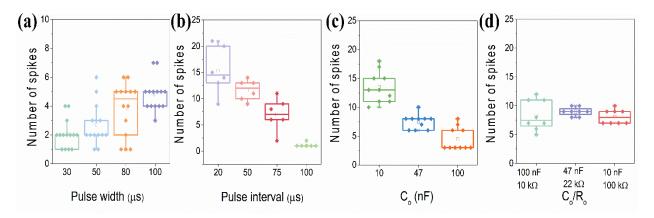

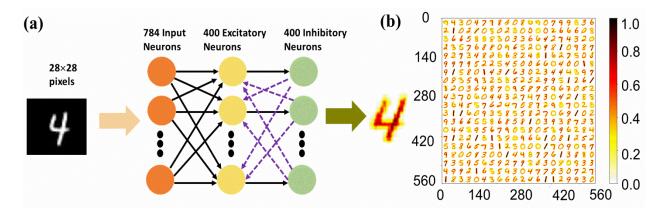

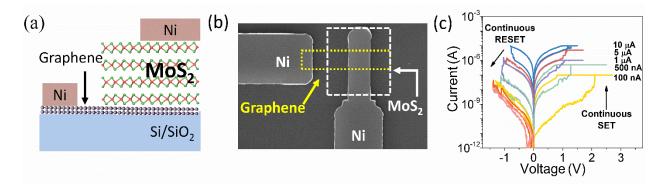

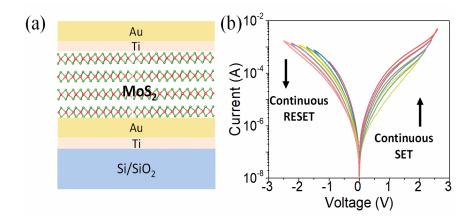

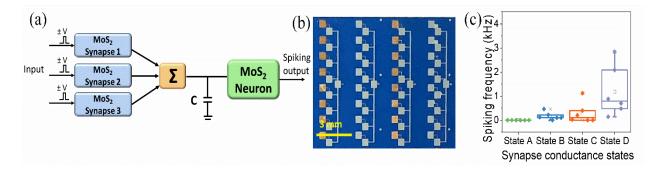

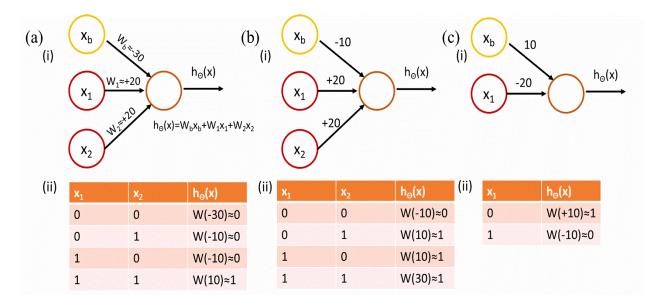

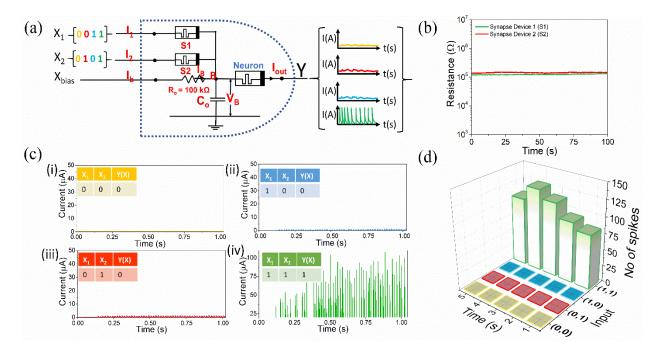

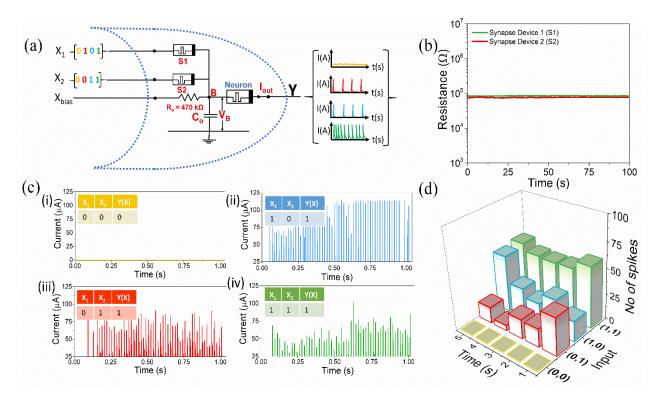

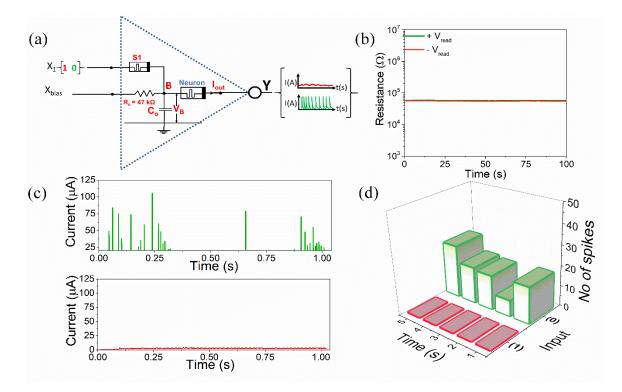

Figure 25: Controllable neuron firing for varying input pulse and circuit parameters. (a) Increasing pulse width with constant pulse interval and pulse amplitude leads increasing spiking frequency. (b) Increasing pulse interval with constant pulse amplitude and width results in decreasing spiking frequency. (c) Lower capacitance ( $C_0$ ) increases the spiking frequency. (d) Variation of both  $R_0$ Figure 26: (a) Block diagram of network architecture adopted to classify MNIST dataset with unsupervised learning technique. (b) The trained weight connections between  $28 \times 28$  input and Figure 27: (a) Device schematic of the graphene/MoS2 memristor device (b) SEM image of the fabricated graphene/MoS<sub>2</sub> memristor device (c) DC *I-V* characteristics of the graphene/MoS<sub>2</sub> Figure 28: (a) Device schematic of the Au/MoS<sub>2</sub>/Ti/Au memristor device (b) DC I-V characteristics of the Au/MoS<sub>2</sub>/Ti/Au memristor device; continuous SET-RESET process shows Figure 29: Monolithic integration of graphene/MoS<sub>2</sub> synapse and Au/MoS<sub>2</sub>/Ag neuron device (a)

### LIST OF TABLES

| Table 1: $D_{it}$ values for MoS <sub>2</sub> -based devices reported in literature                                   |

|-----------------------------------------------------------------------------------------------------------------------|

| Table 2: Interface trap density $(D_{it})$ of MoS <sub>2</sub> FET for different high gate dielectric extracted using |

| subthreshold swing (SS) method                                                                                        |

# LIST OF ACRONYMS (or) ABBREVIATIONS

| 2D              | Two-Dimensional                         |

|-----------------|-----------------------------------------|

| AFM             | Atomic Force Microscopy                 |

| ALD             | Atomic Layer Deposition                 |

| ANN             | Artificial Neural Network               |

| CMOS            | complementary Metal-Oxide-Semiconductor |

| CVD             | Chemical Vapor Deposition               |

| D <sub>it</sub> | Interface Trap Density                  |

| E-beam          | Electron-beam                           |

| EDS             | Energy-Dispersive X-Ray Spectroscopy    |

| ЕОТ             | Equivalent Oxide Thickness              |

| FET             | Field Effect Transistor                 |

| h-BN            | Hexagonal Boron Nitride                 |

| HCS             | High Conductance State                  |

| нн              | Hodgkin–Huxley                          |

| HRS             | High Resistance State                   |

| HRTEM           | High Resolution TEM                     |

| IF              | Integrate-and-Fire                      |

| ІоТ             | Integrate of Things                     |

| IQHE            | Integer Quantum Hall Effect             |

| IR              | Inhibition Ratio                        |

| ITD             | Interaural Time Difference              |

| LCS    | Low Conductance State                     |

|--------|-------------------------------------------|

| LIF    | Leaky Integrate-and-Fire                  |

| LRS    | Low Resistance State                      |

| LTD    | Long Term Depression                      |

| LTP    | Long Term Potentiation                    |

| MOS-C  | Metal Oxide Semiconductor Capacitor       |

| MOSFET | Metal Oxide Semiconductor FET             |

| PCM    | Phase Change Materials                    |

| RT     | Room Temperature                          |

| SNN    | Spiking Neural Network                    |

| SS     | Subthreshold Swing                        |

| STDP   | Spike Timing Dependent Plasticity         |

| STEM   | scanning Transmission Electron Microscopy |

| STP    | Short Term Potentiation                   |

| TCR    | Temperature Coefficient of Resistance     |

| TEM    | Transmission Electron Microscopy          |

| TEMAZ  | Tetrakis(ethylmethylamino)zirconium       |

| TMA    | Trimethylaluminium                        |

| TMDC   | Transition Metal Dichalcogenides          |

| TSM    | Threshold Switching Memristor             |

| WGFMU  | Waveform Generator/Fast Measurement Unit  |

#### CHAPTER 1 INTRODUCTION

The semiconductor industry has experienced an unprecedented growth for the last five decades. The continuous shrinking of the geometrical dimensions along with the rapid evolution of the performances, the silicon-based field effect transistor (FET) has played the central role for this enormous expansion of the semiconductor field. The tremendous evolution like the shifting from the planner FET to FinFET, scaling down from the µm gate length to few nm gate lengths, introduction of high- $\kappa$  gate dielectric etc. has kept the FET technology in line with the Moore's law and enabled to keep pace with the ever-increasing demand of super-fast and low power electronic and optoelectronic devices. [1-4] The technology has been reached to a critical point where the challenges like gate leakage current, high static power dissipation, mobility degradation are getting prominent with the scaling down process. [3, 5, 6] To sustain the Moore's law, implementation of new device geometry and utilization of the new material is getting inevitable.[7, 8] Along with the miniaturization of the electronic devices, there is increasing trend of shifting from rigid substrate to the flexible and wearable platform for electronic devices.[9, 10] With the tremendous technological development, we are getting more dependent on the electronic devices in our day-to-day life. Most of these devices travel with us and are connected to the network for communicating, providing service, and transferring information. Flexible or wearable platform for these devices is in high demand as it provides better durability, space efficiency and comfort compare to the rigid substrate. The coexistence of the bendability, flexibility and stretchability with the preservation of electronic properties even at maximum deformation are the unique requirement for the flexible and wearable electronics.[11] These exceptional properties are not readily available with the traditional electronic materials, hence, there is also ongoing quest for

new materials for future flexible and wearable electronic devices. The isolation of the graphene in 2004 and subsequent rediscovery of other two-dimensional (2D) materials like transition metal dichalcogenides (TMDCs), Bi<sub>2</sub>Se<sub>3</sub>, Bi<sub>2</sub>Te<sub>3</sub>, hexagonal boron nitride (h-BN), black phosphorus has set a new direction for the expedition of next generation electronic materials.[12-15] The layered structure and high carrier mobility along with other exceptional thermal, chemical, mechanical, and electrical properties initiates the opportunity of getting ultimate "thin" devices with the faster speed and low leakage current. The exceptional tensile strength with high Young's modulus and spring constant of the 2D materials also made it a very promising candidate for the next generation flexible and wearable electronics.

#### 1.1 <u>Two Dimensional (2D) Materials</u>

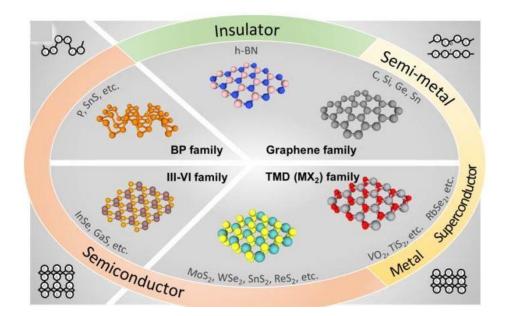

2D materials are solid crystalline having single or few layers of atoms with very large lateral dimension as compared to their thickness.[16] The high aspect ratio enables the 2D materials to attain complete unique properties compare to its bulk counterpart. Recent report showed, in nature there are around 1800 layered structures that can be thinned down to 1 layer or multilayer (<10 nm) and termed as 2D material.[17] This large family encompasses materials with all different kind of conduction mechanisms (metal, semimetal, semiconductor, insulator, superconductor) as shown in **Figure 1**.[18] Out of this large number of materials, graphene is the most popular and most studied 2D material. Graphene is the single layer of  $sp^2$  hybridized carbon atoms with 2D hexagonal (honeycomb) lattice structure. [12] Graphene shows ambipolar characteristics with exceptionally high carrier mobility ( $10^5 \text{ cm}^2/\text{V.s}$ ) due to the ballistic transport.[19] The exceptional behavior of Dirac fermions in presence of the magnetic field enables graphene to show integer quantum hall effect (IQHE) at room temperature.[20] Graphene also has astounding material properties like very high Young's modulus (~0.5–1 TPa), spring constant of ~1-5 N/m and tensile strength of ~130 GPa. [21-24]This noble material also covers the wide range of optical absorption spectrum (300-1400 nm) and shows transparency of 97% at the visible wavelength. Along with the high thermal and chemical stability, it offers other materials large specific surface area for conformal adhesion.[19] Due to all these extraordinary material, electrical, thermal and chemical properties graphene has been extensively explored for wide range of electronic-optoelectronic applications. Despite of having a significant number of tunable properties the zero bandgap of graphene limits its operation for logic devices.

Figure 1: The 2D material family. Adopted with permission from the reference [18]©2018 IEEE

#### **1.1.1** Transition Metal Dichalcogenides (TMDCs)

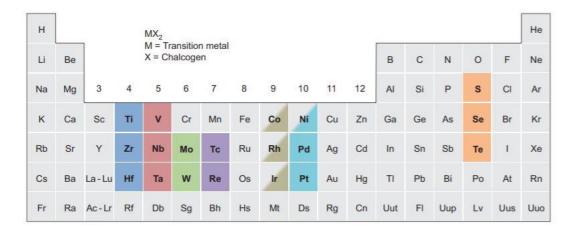

The wide range of tunable bandgap with the inherent noble properties of 2D materials TMDCs have garnered huge interests in the recent times. TMDCs consist of two types of atoms M and X where M represents transition metals like Mo, W, Pt, Pd and X stands for chalcogens such as S, O, Se, Te etc. The M and X atoms are arranged in 2D honeycomb array where M atoms are stacked between X atoms to form X-M-X sandwiched layer, hence the general chemical formula of TMDCs is MX<sub>2</sub>. The periodic table shown in the **Figure 2** demonstrates the possible combination of transition metal and chalcogen to form the TMDCs.

Figure 2: The highlighted transition metals and chalcogens in the periodic table predominantly crystallize to form the 2D layered structure. Adopted with permission from the reference [25]

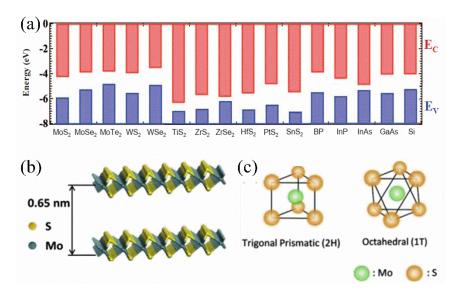

The spatial confinement along the thickness direction during the bulk to monolayer scaling down causes indirect to direct bandgap transition of the TMDCs. **Figure 3a** shows the bandgap alignment for different TMDCs and compared with black phosphorus, III-V materials, and Si. The wide range of the tunability of the bandgap enables to design optimal strain free and atomically sharp heterostructures for electronic devices like diodes, transistors and tunneling devices.[26] For the multilayer TMDCs, different properties like bandgap, phonon vibration and magnetism can be altered by adopting different interlayer stacking strategy like 2H and 3R configurations [27]. The ultra-thin structure, absence of dangling bonds, tunable bandgap, strong spin-orbit coupling with other tunable electrical and material properties, TMDCs has become an exceptional choice in the research field of emerging technologies like sensors for internet of things (IoT) devices,

neuromorphic computing, biomimetic devices, optoelectronics, spintronics and energy harvesting

Figure 3: (a) Band alignment of monolayer 2D TMDCs compared with the Si and III-V materials. Adopted with permission from the reference [26] ©2015, *IEEE* (b) Chemical structure of 2 layer MoS2; thickness of monolayer MoS2 is 0.65 nm, (c) Polytypes of monolayer MoS<sub>2</sub>; trigonal prismatic (2H) and Octahedral (1T). Adopted with permission from reference [38]

#### 1.1.2 MoS<sub>2</sub> for post Si electronics

Among all the 2D materials,  $MoS_2$  is considered as the most promising candidate for the post silicon electronics, mainly because of its indirect bandgap of ~1.2 eV to direct bandgap of ~1.8 eV transition, high ON-OFF current ratio of  $10^8$  at room temperature and carrier mobility of 200 cm<sup>2</sup>/V.s. [39] These features are super critical for future transistor and other electronic devices Another fundamental reason for considering the MoS<sub>2</sub> as the future replacement of the Si is the abundance and innoxious nature of its constituent elements. Like other TMDCs, in MoS<sub>2</sub>, transition metal Molybdenum (Mo) sandwiched between the chalcogen Sulfur (S) to form the single layer of 0.65 nm thickness as shown in **Figure 3b**. The atoms are bonded by strong covalent bond within the layer and weak vdW exists between the layers.[38] **Figure 3c** demonstrates the

monolayer with trigonal prismatic poly type crystal (2H) configuration which depicts semiconducting nature. The octahedra crystal symmetry (1T) shows the metallic behavior.[40] The high Young's modulus of ~ $0.33 \pm 0.07$  TPa makes MoS<sub>2</sub> an exceptional choice for flexible and wearable electronics.

#### 1.2 Motivation

In electronics, the primary reason for the success of silicon among all the semiconductors lies in the superior quality of the interface between silicon and silicon dioxide. Typical production quality SiO<sub>2</sub> gate dielectrics have a mid-gap interface trap density of only ~10<sup>10</sup> states/cm<sup>2</sup>-eV. At a silicon/high- $\kappa$  dielectric interface, the trap densities range from 10<sup>11</sup>–10<sup>12</sup> states/cm<sup>2</sup>-eV.[41] The clear goal of any potential semiconductor system is to possess an interface as close to that of Si/SiO<sub>2</sub>, since a high-quality interface is critical for all imaginable electronic and optoelectronic devices. Two-dimensional materials, by virtue of their layered structure, do not have out-of-plane bonds.[42] Thus, they have been predicted to bear pristine interfaces and surfaces, backed by experimental support. For the efficient and successful implementation of MoS<sub>2</sub> as channel material for transistors it is very critical to investigate the interface quality of MoS<sub>2</sub> with different gate dielectric material. Hence, this dissertation is aiming to study the interface quality of 2D MoS<sub>2</sub> with different high- $\kappa$  gate dielectric to predict the viability of the MoS<sub>2</sub> material system for future electronic devices.

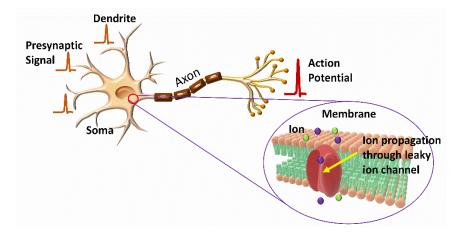

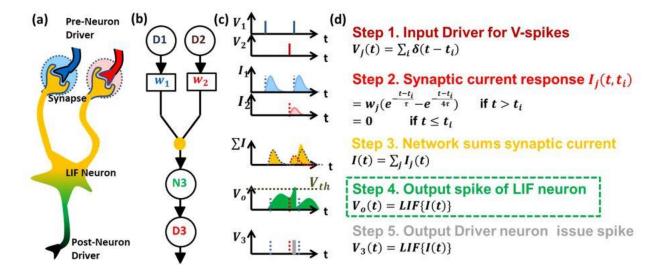

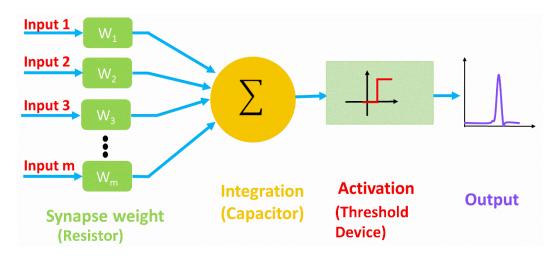

The phenomenal evolution of information and communication has driven us to envision the future technologies that demand faster, highly parallel, low power, and self-learning information processing system like human brain. The limitation of the current state of the art like von Neumann architectures to meet these criteria has paved the way for artificial neural network (ANN). Specially, for solving the probabilistic and unstructured complex computation tasks like face and speech recognition, medical diagnostics, autonomous driving and high-speed data analysis; ANN showed superiority over the digital computer.[43-46]. Spiking neural network (SNN), an advanced technology of ANN is expected to minimize the gap between the machine learning and the neuroscience by emulating the cognitive process of human brain more efficiently. Artificial neuron and artificial synapse are the building blocks of SNN. Revival of memristor devices has opened the opportunity of realizing artificial neuron and synapse with single memristor device. Demonstration of artificial neuron and artificial synapses based on two dimensional (2D) TMDC single memristor device enables the realization of highly scalable, stackable, energy efficient, flexible, wearable and reliable neuromorphic hardware. Moreover, the implementation of both artificial neuron and synapse with the same material system would not make the process limited to the thermal budget and substrate incompatibility due to heterogeneous integration. Therefore, the dissertation also aims to the development and monolithic integration of the MoS<sub>2</sub> based neuromorphic computing devices for future computing technology.

#### 1.3 <u>Objectives</u>

The main objectives of this dissertation are as follows:

- 1. To fabricate the  $MoS_2$  based FET for different high- $\kappa$  gate dielectric.

- 2. To study the MoS<sub>2</sub>/high- $\kappa$  interface quality by adopting the subthreshold swing and conductance method of interface trap density ( $D_{it}$ ) extraction.

- 3. To develop a MoS<sub>2</sub> based reliable threshold switching memristor (TSM) device with the low threshold voltage, high ON-OFF ratio, sharp switching, and high endurance.

- 4. To study the switching mechanism of the TSM device.

- 5. To develop the artificial leaky integrate-and-fire (LIF) neuron circuit and implement the MoS<sub>2</sub> based TSM device for the LIF neuron circuit.

- 6. To study the different feature and performance of the developed LIF neuron

- To do the monolithic integration of the MoS<sub>2</sub> based artificial neuron and synapse device for realizing single layer perceptron and different Boolean logic gates.

- 8. To implement the MoS<sub>2</sub> based TSM for realizing a robust artificial nociceptor which can efficiently emulates the key features of the biological nociceptor.

#### 1.4 <u>Dissertation Overview</u>

Chapter 2 gives an overview of the different interface trap density ( $D_{it}$ ) extraction techniques. The mathematical models, advantages, and disadvantages for different *Dit* extraction techniques are discussed in this chapter. This chapter also gives a brief introduction about the High- $\kappa$  materials and the nucleation layer. The sources of interface traps for MoS<sub>2</sub>/High- $\kappa$  are also discussed in this chapter. The chapter explores the relevant literatures on the  $D_{it}$  of the MoS<sub>2</sub>/dielectric interface.

Chapter 3 presents the experimental methodology and results for the  $D_{it}$  extraction of the different MoS<sub>2</sub>/High- $\kappa$  interface. The MoS<sub>2</sub> FET fabrication steps and electrical characterization techniques are discussed in detail in this chapter. In the result and discussion section, the experimental transfer characteristics of the MoS<sub>2</sub> FET, capacitance-voltage, conductance-voltage,

and conductance-frequency curves shown and explained. The chapter includes the comparative study of the  $D_{it}$  values extracted from the different interface.

Chapter 4 covers the brief introduction about the neuromorphic computing system and spiking neural network (SNN). The necessity of realizing a single device artificial neuron is highlighted in this chapter. This chapter explores the different neuron models also. The chapter includes a literature survey on the 2D materials based artificial neuron.

Chapter 5 presents the fabrication steps for the  $MoS_2$  based TSM device and its implementation as a LIF neuron. The chapter also reveals the switching mechanism of the TSM device. The chapter demonstrates the ability of the LIF neuron to emulates the key features of the biological neuron.

Chapter 6 explores the monolithic integration of the  $MoS_2$  based artificial neuron and synapse devices. The chapter demonstrates the experimental results obtained from the monolithically integrated single layer perceptron. The chapter also presents the successful implementation of AND, OR and NOT logic gates with the single layer perceptron.

Chapter 7 demonstrates the successful implementation of the  $MOS_2$  based TSM device as artificial nociceptor. The chapter delineates the ability of the artificial nociceptor to emulate the complex functionality of the biological nociceptor .

Chapter 8 draws the conclusion of the dissertation and discusses the future directions and challenges to realize neuromorphic computing hardware on complete 2D platform.

# CHAPTER 2 INTERFACE TRAP DENSITY (*D<sub>it</sub>*) EXTRACTION TECHNIQUES

#### 2.1 Introduction

The performance of the semiconductor based electronic devices is greatly influenced by the presence of the interface trap states. Therefore, it is very crucial to precisely quantify the parameters like interface trap density, capture cross-sections, trap time constant for any potential material system prior to the implementation. The comprehensive knowledge about the trap states at any interface facilitates to design and develop high performance devices. Over the years, a good number of interface trap density extraction techniques have been proposed. In this chapter, we will define the interface trap states and explore the mathematical models, advantages, and disadvantages of the different  $D_{it}$  extraction techniques. The chapter also gives a brief introduction on the high- $\kappa$  dielectrics and the possible sources of the interface traps for MoS<sub>2</sub>/high- $\kappa$  interface.

#### 2.2 Interface Trap States

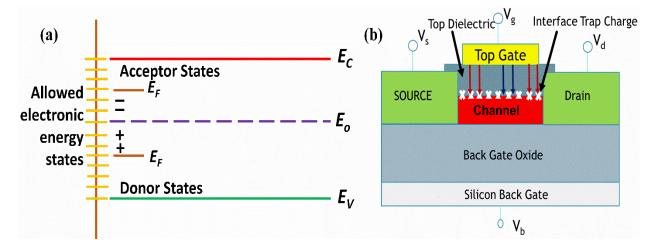

At the oxide-semiconductor interface, the abrupt termination of the periodic nature of the semiconductor initiates electronic energy states within the forbidden bandgap. These energy states are termed as the interface trap states. Interface trap states are very crucial for the device performance because charge can flow between the semiconductor and the interface trap states. The net charge in the interface trap states is dominated by the position of the Fermi level of the semiconductor. The interface trap is considered as acceptor while it is neutral but can accept electron to get negatively charged. At neutral condition it remains above the Fermi level but at negatively charged condition it stays below the Fermi level as shown in the **Figure 4a**. On the

contrary, the donor type interface trap stays below the Fermi level at neutral condition and goes above the Fermi level while it becomes positively charged by donating the electron.[47] Hence for the metal oxide semiconductor FET (MOSFET) or MOS capacitor (MOS-C), the charge in the interface trap states is dependent on the applied gate voltage. The presence of interface traps adversely affects the MOSFET by shifting the threshold voltage, lowering the subthreshold swing, reducing the channel mobility and conductivity.

Figure 4: (a)The position of the interface trap states in the bandgap of the semiconductor. (b) physical location of the interface trap states in the MOSFET device.

#### 2.3 Interface Trap Density (*D<sub>it</sub>*) Extraction Techniques

#### 2.3.1 Low Frequency (Quasi-static) Methods

Low frequency method also known as Quasi-static method is the most common technique of interface trap density ( $D_{it}$ ) measurement. The method only can quantify the  $D_{it}$  but does not provide any information regarding their capture cross-sections.[47] During the low frequency C-V measurements, the interface traps respond to the lower probe frequency. In this condition, the C-V curve gets distorted as interface traps capacitance  $C_{it}$  adds up with the oxide capacitance. At higher frequency, interface traps cannot follow the probe frequency and do not contribute to the overall capacitance. Hence, the *C*-*V* curves come out like an ideal *C*-*V* curve. This feature is utilized in the low frequency method. The low frequency *C*-*V* curve is compared with the high frequency *C*-*V* curve to extract the  $D_{it}$ . The low frequency capacitance ( $C_{lf}$ ) is given by

$$C_{lf} = \left(\frac{1}{C_{0x}} + \frac{1}{C_S + C_{it}}\right)^{-1} \tag{1}$$

Here  $C_{ox}$  is the oxide capacitance,  $C_s$  denotes semiconductor capacitance. The  $D_{it}$  can be extracted using following equations

$$D_{it} = \frac{c_{it}}{a^2} \tag{2}$$

$$D_{it} = \frac{1}{q^2} \left( \frac{c_{ox} c_{lf}}{c_{0x} - c_{lf}} - C_S \right)$$

(3)

The low-frequency method can extract interface density over the entire bandgap. The perfect estimation of the ideal C-V curve or high frequency C-V curve is always challenging for this measurement. This measurement is also found difficult for the very thin oxide layer due to the comparatively higher leakage current.[48]

#### 2.3.2 Terman Method

Terman method is a high frequency capacitance method of  $D_{it}$  extraction. The method relies on the *C-V* measurement at a sufficiently high frequency where the interface traps are unresponsive to the probe frequency. [47] Though the interface traps do not respond to the high probe frequency, the net interface charges change with the slowly varying gate voltage. This variation of interface charge causes the stretching of the *C-V* curve along the gate voltage axis. For the calculation of the *D<sub>it</sub>* with this method, first semiconductor work function ( $\Phi_s$ ) for a given high frequency capacitance  $C_{hf}$  is determined from the ideal MOS-C *C*-*V* curve. Next, the  $V_G$  is extracted from the experimental *C*-*V* curve for the same *Chf*. This step is repeated to obtain a satisfactory  $\Phi_s$  vs VG curve. The  $D_{it}$  can be extracted from this curve using following equation.

$$D_{it} = \frac{c_{ox}}{q^2} \left(\frac{dV_G}{d\Phi_s} - 1\right) - \frac{c_s}{q^2} = \frac{c_{ox}}{q^2} \frac{\Delta V_G}{d\Phi_s}$$

(4)

Where  $\Delta V_G = V_G \cdot V_G$  (ideal), the gate voltage shift from the ideal condition. This method is applicable for the  $D_{it}$  equal or above  $10^{10}$  cm<sup>-2</sup>eV<sup>-1</sup>. The method is not well-accepted due to the inaccurate capacitance measurement. Moreover, with the thinner oxide or increasing capacitance the voltage shift become insignificant and the  $D_{it}$  extraction become difficult.[47]

#### 2.3.3 Subthreshold Swing Method

Subthreshold swing (SS) method is one of the simplest and direct methods of  $D_{it}$  extraction. The  $D_{it}$  can be calculated analytically using the experimentally extracted SS from  $I_D$ - $V_G$  graph of the MOSFET. [49, 50] The following analytical expression is used to extract  $D_{it}$ ,

$$SS = \frac{2.3KT}{q} \left( 1 + \frac{C_{it}}{C_{tg}} + \frac{C_S}{C_{tg}} - \frac{\frac{C_S^2}{C_{tg}C_{sio_2}}}{1 + \frac{C_{it}}{C_{sio_2}} + \frac{C_S}{C_{sio_2}}} \right)$$

(5)

Here,  $C_{tg}$  is the capacitance of the top gate dielectric, given by  $C_{tg} = \epsilon_{tg}/t_{tg}$ , where  $\epsilon_{tg}$  is the dielectric constant and  $t_{tg}$  is the thickness of the top gate dielectric. This method is mostly dependent on the theoretical estimation of the capacitance value, which make it difficult to accurate estimation of the interface traps. Moreover, this method does not give the information about the capture cross section and the defect location. Despite of these limitations, SS method is frequently adopted to get a rough estimation of the interface traps for the MOSFET devices.

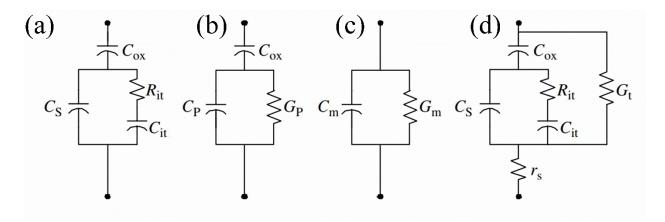

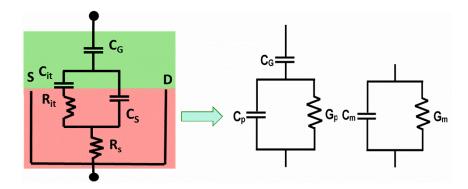

## 2.3.4 Conductance Method

The conductance method developed by Nicollian and Goetzberger is considered as one of the most complete and sensitive methods of  $D_{it}$  extraction.[47, 48, 51] Also, the capture cross sections of the traps and the interface trap time constant  $\tau_{it}$  can be extracted using this method.[47] For a conventional metal oxide semiconductor FET (MOSFET), this method yields  $D_{it}$  in both depletion and weak inversion regions. The technique utilizes the equivalent parallel conductance  $G_P vs$  gate voltage ( $V_G$ ) and  $G_P vs$  frequency (f) measurement of a MOS-C or MOSFET for the accurate estimation of the interface trap density. The conductance incorporates the loss mechanism due to the interface trap capture and emission of carriers and thus infer the interface trap density. **Figure 5** shows the equivalent circuit model of a MOS-C for the explanation of the conductance method. The basic circuit model at **Figure 5a** includes the  $C_{ox}$ ,  $C_S$  and  $C_{it}$ . The loss due to captureemission of carriers is represented by the  $R_{it}$  in the circuit. The circuit is further simplified at **Figure 5b** by replacing circuit element with parallel capacitance  $C_P$  and parallel conductance  $G_P$ . The  $C_P$ and  $G_P$  are defined as following

$$C_p = C_S + \frac{C_{it}}{1 + \left(\omega_{\tau_{it}}\right)^2} \tag{6}$$

$$\frac{G_p}{\omega} = \frac{q\omega\tau_{it}D_{it}}{1+\left(\omega_{\tau_{it}}\right)^2}$$

(7)

Here  $C_{it}=q^2D_{it}$ ,  $\omega=2\pi f$  (*f=measurement* frequency), the interface trap time constant  $\tau_{it}=R_{it}C_{it}$ . It is clear from the Equation 6 and 7 that, the conductance method is simplified compare to the traditional capacitance method because it does not require  $C_S$  for the  $D_{it}$  interpretation. Equation 6 and 7 consider the interface traps with a single energy level within the bandgap. Practically, the interface traps are continuously distributed in energy over the entire bandgap of

the semiconductor. The interface traps located within the few  $\pm \frac{KT}{q}$  of the Fermi level are primarily contributes to the capture and emission of the carriers and causes the time constant dispersion. To incorporates this phenomenon the following normalized conductance is considered for the model.

$$\frac{G_p}{\omega} = \frac{qD_{it}}{2\omega_{it}} \tag{8}$$

Experimentally, the conductance  $G_P$  measured as a function of frequency and GP/ $\omega$  is plotted against  $\omega$ . The peak position of  $G_P / \omega$  at  $\omega = 1/\tau_{it}$  is determined which gives the maximum  $D_{it}=2G_P/q\omega$ . Experimentally obtained  $G_P / \omega$  vs  $\omega$  curve is generally broader compared to the predicted curve considering Equation 8. The anomaly is attributed to the surface potential fluctuations originates from the oxide charge, interface traps nonuniformity and doping density. The equation for  $D_{it}$  is rectified as following equation considering the effect of surface potential fluctuations.

$$D_{it} \approx \frac{2.5}{q} \left( \frac{G_p}{\omega_{max}} \right) \tag{9}$$

The capacitance measuring unit (CMU) generally considers the parallel  $C_m$ - $G_m$  combination of the device under test (DUT) as shown in the **Figure 5c**. The following equation is used to calculate the  $G_P/\omega$  from the measured parallel capacitance and conductance.

$$\frac{G_p}{\omega} = \frac{\omega G_m C_{ox}^2}{G_m^2 + \omega^2 (C_{ox} - C_m)^2} \tag{10}$$

The equation neglects the series resistance of the device, but **Figure 5d** is the modified circuit which incorporates the series resistance  $r_s$  and the tunneling conductance  $G_t$ . The following equation gives the  $G_p/\omega$  value considering the effect of series resistance.

$$\frac{G_p}{\omega} = \frac{\omega(G_c - G_t)C_{0x}^2}{G_c^2 + \omega^2(C_{0x} - C_c)^2}$$

(11)

Where  $G_c$  and  $C_c$  is the corrected conductance and capacitance respectively for the series resistance. Equations are developed to measure  $G_c$  and  $C_c$  from the measured conductance and capacitance.

Figure 5: Equivalent circuits for conductance method (a) MOS-C with interface trap time constant  $R_{it}C_{it}$ . (b) simplified circuit of (a), (c) measured circuit (d) considering series resistance and tunneling conductance  $G_t$ , adopted with permission from the reference [47]

For this measurement the frequency should be precisely determined, and it is suggested to conduct the measurement for the wide range of frequency. The ac signal amplitude should be kept in the range of 50 mV to avoid the spurious conductance arise from the signal harmonics. [47]

The conductance method is recognized as complete method because it yields  $D_{it}$ , capture cross section for the majority carriers, and surface potential fluctuations in the depletion to weak inversion region of the bandgap. The method is viable for the high gate leakage current unlike the capacitance method and can measure  $D_{it}$  even lower than 10<sup>9</sup> cm<sup>-2</sup>eV<sup>-1</sup>. Capacitance based  $D_{it}$ extraction techniques demand the accurate measurement of oxide capacitance, semiconductor capacitance and the interface trap capacitance which increases the complexity and results erroneous estimation. On the other hand, for the conductance method, the measured conductance is directly convertible to the response of interface traps as a function of gate voltage and frequency.[52] In this method all the mathematical calculations are based on the experimentally obtained value, no assumptions are made for the quantification. Moreover, this method is readily applicable to the MOSFET structure which reduce the complexity of fabricating separate MOS-C devices.

## 2.4 <u>MoS<sub>2</sub>/High κ Interface</u>

## 2.4.1 High-κ Gate Dielectric

The dielectric insulator is one of the main components of the electronic logic devices. The enhancement of the metal-semiconductor capacitive coupling and suppressing the leakage current is the main function of the dielectric insulator in the electronic devices. In the past decades,  $SiO_2$  was the only choice as dielectric insulator for the microelectronic devices mainly due its defect free uniform growth. With the scaling down process, the  $SiO_2$  was also thinned down proportionally. The industry faced the major challenge while  $SiO_2$  needed to scale down below 1 nm. At this thickness, the leakage current due to the quantum tunneling became inevitable and also the uniform growth of  $SiO_2$  all over 12-inch wafer also became challenging. At this scenario, scientists gave a breakthrough by replacing  $SiO_2$  by the high- $\kappa$  dielectric materials.

The high- $\kappa$  materials are defined as the dielectric materials with the higher dielectric constant ( $\kappa$ ) compare to the SiO<sub>2</sub>. HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, ZrSiO<sub>4</sub>, HfSiO<sub>4</sub> are some of the common high- $\kappa$  dielectric materials.

The capacitance of the parallel plate capacitor is given by

$$C = \frac{\kappa \varepsilon_{0A}}{t} \tag{12}$$

Where,  $\kappa$  represents dielectric constant,  $\varepsilon_0$  is the permittivity of the free space, *A* denotes the capacitor area and *t* represent the thickness of the capacitor insulator. Equation 12 clearly indicates that, the dielectric materials with higher  $\kappa$  value offers larger capacitance for the same thickness of the material with lower  $\kappa$ . Therefore, high dielectric constant of the high- $\kappa$  dielectric material allows to use a gate with higher physical thickness while achieving the same capacitance obtained for much thinner SiO<sub>2</sub>. The equivalent oxide thickness (EOT) is the required thickness of the SiO<sub>2</sub> to achieve the same capacitance value for the high  $\kappa$  dielectric. EOT is defined by the following equation

$$EOT = t_{high-\kappa} \left( \frac{\kappa_{SiO_2}}{k_{high-\kappa}} \right)$$

(13)

Here,  $t_{high-\kappa}$  is the thickness of the high- $\kappa$  dielectric material. So, the high  $\kappa$  dielectric facilitates the implementation of the thicker gate dielectric to reduce the leakage current while maintaining the required capacitance for the efficient device performance.

## 2.4.2 Sources of interface traps at MoS<sub>2</sub>/high κ interface

### 2.4.2.1 Defects in $MoS_2$

Though it is expected to have very low interface trap density for  $MoS_2$  and other 2D materials because of absence of the out of plane dangling bonds, the experimental studies showed significant trap density at  $MoS_2/oxide$  interface. The intrinsic defects in the geological  $MoS_2$  are the main reason for the performance degradation of the  $MoS_2$  based devices. The variation in the stoichiometry within the same layer as sulfur rich and sulfur deficient region, presence of impurities, structural defects etc. play key role for the high interface trap density at  $MoS_2/oxide$  interface. The polycrystalline  $MoS_2$  layer obtained by CVD, thermal evaporation, hydrothermal

synthesis, electrochemical lithiation etc. process generally contains more defect compare to the exfoliated MOS<sub>2</sub>.

#### 2.4.2.2 Nucleation layer

The atomic layer deposition (ALD) of the high  $\kappa$  gate dielectric requires initial precursor at the growth surface to initiate the self-limiting chemical reaction. The chemically inert basal plane of MoS<sub>2</sub> does not provide that precursor, hence for the thin layer growth of the high  $\kappa$  gate dielectric, the growth takes place only at the defect site or. only the physical adsorption happens. To obtain the high quality growth of the high  $\kappa$  gate dielectric, the functionalization of the surface of the 2D material or deposition of additional buffer layer is required.[53] The functionalization process includes O<sub>2</sub> plasma or Ozone treatment. Both processes improve the ALD nucleation but the O<sub>2</sub> plasma treatment causes an interfacial layer of MoO<sub>3</sub> while Ozone treatment requires thicker deposition of dielectric material for leakage free gate. Another approach is to initiate a buffer layer in between the 2D material and the high  $\kappa$  gate dielectric. Titanyl phthalocyanine and metal oxides are generally used as the buffer layer. Thermal or E-beam evaporation of very thin layer of the buffer layer offer favorable surface for the uniform growth for the high  $\kappa$  gate dielectric. At the same time this buffer or nucleation layer initiate trap states and carrier scattering effects. Hence, the nucleation layer is another major source of the interface traps of Oxide-MoS<sub>2</sub> interface.

## 2.5 Literature on MOS<sub>2</sub> Interface Trap Density

Different  $D_{it}$  extraction techniques are adopted to quantify the interface traps for MOS<sub>2</sub> based FET with different gate dielectrics. Since surface roughness scattering at high electric fields

is absent in an all-two-dimensional  $MoS_2$  transistor with h-BN top gate, it can be argued that there are few interface traps due to the absence of dangling bonds.[54] However, contrary to these speculations, a trap density between mid-10<sup>11</sup> and 10<sup>14</sup> states/cm<sup>2</sup>-eV was reported for monolayer MoS<sub>2</sub> grown by chemical vapor deposition, with a top gate of AlO<sub>x</sub> (2 nm)/HfO<sub>2</sub> (30 nm).[55] Exfoliated monolayer and tri-layer MoS<sub>2</sub> on a local bottom gate with h-BN as the dielectric exhibits an interface trap density  $(D_{it})$  of ~10<sup>12</sup> states/cm<sup>2</sup>-eV.[56] A peak  $D_{it}$  of 10<sup>13</sup> states/cm<sup>2</sup>eV was reported at 0.35–0.4 eV from midgap in MoS<sub>2</sub> regardless of the gate dielectrics.[57] A constant  $D_{it}$  of  $10^{12}$  states/cm<sup>2</sup>-eV at a MoS<sub>2</sub>/dielectric interface is revealed using the Terman method, when sulfur vacancies are absent in MoS<sub>2</sub>.[57] Due to the absence of dangling bonds in 2D materials, it is difficult to deposit high quality dielectrics on them using atomic layer deposition (ALD). By functionalizing the surface of MoS<sub>2</sub> using UV-ozone, researchers have been able to deposit high quality HfO<sub>2</sub> by ALD on MoS<sub>2</sub>.[58] However, the interface trap density between fewlayer MoS<sub>2</sub> channel and 8-13 nm HfO<sub>2</sub> thus deposited is 10<sup>12</sup>-10<sup>13</sup> states/cm<sup>2</sup>-eV.[59] Other researchers advocate the use of a nucleation layer for facilitating the ALD of dielectrics.[60-62] The introduction of a nucleation layer by physical vapor deposition or by functionalization of the 2D surface increases the interface traps. There are very few conclusive reports on trap density lower than  $10^{11}$  states/cm<sup>2</sup>-eV at a 2D semiconductor/gate dielectric interface.  $D_{it}$  extracted for MoS<sub>2</sub>-based field effect transistors (FETs) with various dielectrics are tabulated in Table 1.

| Device Structure                                          | Thickness                                                                                                                                 | Type of<br>MoS <sub>2</sub>      | Method of Dit<br>Extraction                            | Dit Value<br>(cm <sup>2</sup> /eV)                                    |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------|

|                                                           | 7 layer MoS <sub>2</sub><br>13 nm HfO <sub>2</sub>                                                                                        | 11002                            | High low                                               | $1.2 \times 10^{13}$                                                  |

| MoS <sub>2</sub> / HfO <sub>2</sub> [59]                  | 4 layer MoS <sub>2</sub><br>8 nm HfO <sub>2</sub>                                                                                         | CVD grown                        | frequency<br>method and<br>multi-frequency             | $\begin{array}{c} 2 \times 10^{11} - 2 \times \\ 10^{13} \end{array}$ |

| MoS <sub>2</sub> / HfTiO[63]                              | 50 layers (32.5 nm) MoS <sub>2</sub><br>39.65nm HfTiO                                                                                     | Transferred<br>by scotch<br>tape | From SS                                                | 5.58×10 <sup>12</sup>                                                 |

| $MoS_2/Al_2O_3[64]$                                       | 1 layer (0.85 nm) MoS <sub>2</sub><br>1nm Al <sub>2</sub> O <sub>3</sub> seeding layer<br>15 nm Al <sub>2</sub> O <sub>3</sub> dielectric | CVD                              |                                                        | 1.6×10 <sup>13</sup>                                                  |

| MoS <sub>2</sub> /h-BN[65]                                | Single or bilayer MoS <sub>2</sub>                                                                                                        | Exfoliated<br>by scotch<br>tape  | observed noise<br>magnitude                            | 6×10 <sup>10</sup> -1×10 <sup>1</sup>                                 |

| MoS <sub>2</sub> /h-BN[66]                                | Trilayer MoS <sub>2</sub>                                                                                                                 | Exfoliated                       | High low<br>frequency<br>method and<br>multi-frequency | ~10 <sup>12</sup>                                                     |

| $MoS_2/ZrO_2[67]$                                         | Few layers MoS <sub>2</sub><br>5.8nm ZrO <sub>2</sub>                                                                                     | Transferred                      | From SS                                                | $1.7 \times 10^{12}$                                                  |

| MoS <sub>2</sub> / HfO <sub>2</sub> [68]                  | Monolayer to trilayer<br>(0.7nm to 2.1nm) MoS <sub>2</sub><br>10nm HfO <sub>2</sub>                                                       | Exfoliated                       | From SS                                                | 5×10 <sup>12</sup>                                                    |

| MoS <sub>2</sub> / Al2O <sub>3</sub> [69]                 | 30nm MoS <sub>2</sub><br>50nm Al <sub>2</sub> O <sub>3</sub>                                                                              | Exfoliated                       | From SS                                                | $2.6 	imes 10^{11}$                                                   |

| $MoS_2/SiN_x[70]$                                         | 140 layers MoS <sub>2</sub><br>250nm SiN <sub>x</sub>                                                                                     | Exfoliated                       | From SS                                                | 1.14×10 <sup>13</sup>                                                 |

| MoS <sub>2</sub> /SiO <sub>x</sub> /SiN <sub>x</sub> [70] | 125 layers MoS <sub>2</sub><br>50nm SiO <sub>x</sub><br>200nm SiN <sub>x</sub>                                                            | Exfoliated                       | From SS                                                | 2.13×10 <sup>12</sup>                                                 |

| MoS <sub>2</sub> /thermal SiO <sub>2</sub> [70]           | $154 \text{ layers MoS}_2$ $100 \text{ nm SiO}_2$                                                                                         | Exfoliated                       | From SS                                                | 3.32×10 <sup>12</sup>                                                 |

| $MoS_2/Al_2O_3[71]$                                       | 7 – 8 nm MoS <sub>2</sub><br>10 nm Al <sub>2</sub> O <sub>3</sub>                                                                         | Exfoliated                       | Terman                                                 | 1×10 <sup>12</sup>                                                    |

| $MoS_2/HfO_2[71]$                                         | 7 – 8 nm MoS <sub>2</sub><br>10 nm HfO <sub>2</sub>                                                                                       | Exfoliated                       | Terman                                                 | 2×10 <sup>12</sup>                                                    |

| $MoS_2/HfO_2[55]$                                         | Monolayer MoS <sub>2</sub><br>30 nm HfO <sub>2</sub>                                                                                      | CVD                              | Conduction                                             | 3.3×10 <sup>14</sup>                                                  |

| $MoS_2/HfO_2[72]$                                         | Monolayer MoS <sub>2</sub><br>5 nm HfO <sub>2</sub>                                                                                       | CVD                              | High-low<br>frequency<br>method<br>Low Frequency       | 7.03×10 <sup>11</sup>                                                 |

| $MoS_2/Al_2O_3[73]$                                       | 11.3 nm MoS <sub>2</sub><br>30 nm Al <sub>2</sub> O <sub>3</sub>                                                                          | Exfoliated                       | Noise<br>characterization<br>using CNF<br>Model        | 1.8×10 <sup>12</sup>                                                  |

| $MoS_2/Al_2O_3[74]$                                       | 15nm MoS <sub>2</sub><br>16nm Al <sub>2</sub> O <sub>3</sub>                                                                              |                                  | Exfoliated                                             | 2.4×10 <sup>12</sup>                                                  |

Table 1:  $D_{it}$  values for MoS<sub>2</sub>-based devices reported in literature

# 2.6 <u>Conclusion</u>

The exploration for the high quality MoS<sub>2</sub>/high  $\kappa$  gate dielectric interface is crucial prior to its implementation for the next generation electronics. Owing to the importance of nucleation layer for the uniform growth of the high  $\kappa$  gate dielectric, it is also vital to find out the best combination of the nucleation layer and the gate dielectric. Conduction method of  $D_{it}$  extraction is considered as the most accurate and comprehensive method for the  $D_{it}$  extraction. Hence, in this work, the conductance method is adopted to determine the best possible interface of MoS<sub>2</sub> among the different combinations of the nucleation layer-high  $\kappa$  gate dielectric layers.

# CHAPTER 3 MoS<sub>2</sub>/HIGH-к DIELECTRIC INTERFACE EXTRACTION

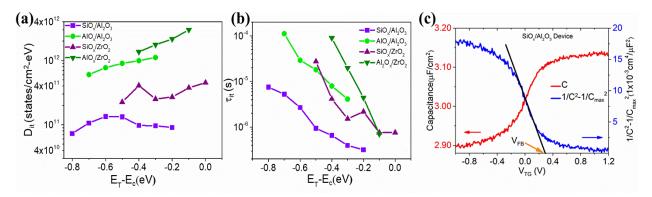

The contents of this chapter have been published in: Dev, D., Krishnaprasad, A., Kalita, H., Das, S., Rodriguez, V., Calderon Flores, J., Zhai, L. and Roy, T., 2018. High quality gate dielectric/MoS<sub>2</sub> interfaces probed by the conductance method. Applied Physics Letters, 112(23), p.232101.

## 3.1 Introduction

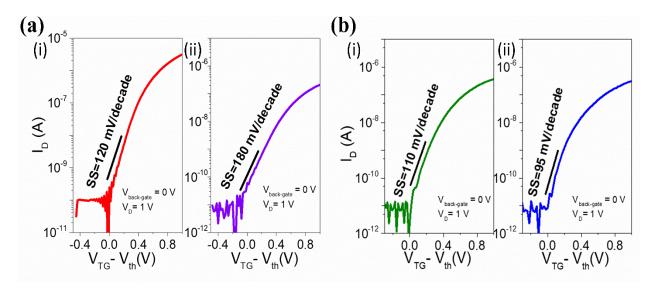

In this chapter, we are going to investigate the interface quality of the MoS<sub>2</sub>/high  $\kappa$  interfaces by developing MoS<sub>2</sub> based field effect transistors (FET) having high- $\kappa$  top gate dielectrics (Al<sub>2</sub>O<sub>3</sub> and ZrO<sub>2</sub>). Two different nucleation layers SiO<sub>x</sub> and AlO<sub>x</sub> are used for this study. Primarily, the  $D_{it}$  is calculated using simple SS method based on  $I_D$ - $V_G$  measurement. Next, the most sensitive method named conductance method is adopted for the precise extraction of the  $D_{it}$  and its location in the bandgap. The extracted results are compared to determine the best possible MoS<sub>2</sub>/nucleation layer/high  $\kappa$  gate dielectric interface for the advanced electronic devices.

# 3.2 Device Fabrication and Characterization Techniques

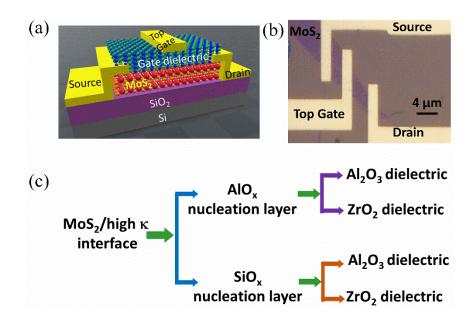

## 3.2.1 MoS<sub>2</sub> FET Device Fabrication

**Figure 6a** and **6b** shows the device schematic and optical image respectively of a top-gated  $MoS_2$  transistor. The first step of the fabrication is the mechanical exfoliation of the  $MoS_2$ . In this step, Scotch-tape method is used to cleave the few layers of the  $MoS_2$  from the bulk  $MoS_2$  source

and then transferred on the patterned p+ Si substrate with 260 nm of thermally grown SiO<sub>2</sub>. The thickness of the exfoliated MoS<sub>2</sub> flakes can be confirmed from the optical contrast of the micrograph. For this work, four-layer MoS<sub>2</sub> flakes are used as the channel material of the FET devices. The precise locations of the flakes on the patterned substrate are determined and NPGS DesginCAD layout editor is used to design the mask according to the location of the flakes. NPGS e-beam lithography system integrated with Zeiss ULTRA-55 FEG SEM is used for the patterning the source/drain contact. E-beam evaporator is used to deposit 60 nm of Ni. Finally, the lift-off process results the patterned source/drain contact. To obtain different combination of nucleation layer and top gate dielectric, four different kinds of devices are fabricated.as shown in the **Figure 6c**.

Figure 6: (a) Device schematic – the channel is underlapped by the gate. (b) Optical microscope image; scale bar: 4  $\mu$ m.(c) The MoS<sub>2</sub>/High  $\kappa$  interface combinations for two different (AlO<sub>x</sub> and SiO<sub>x</sub>) nucleation layers with two different high  $\kappa$  gate dielectrics (Al<sub>2</sub>O<sub>3</sub> and ZrO<sub>2</sub>).

The nucleation layers used are  $AlO_x$  and  $SiO_x$ . For  $AlO_x$  nucleation layer, 1.5 nm of Al was e-beam operated and kept in ambient condition to transform Al to  $AlO_x$ . The  $SiO_x$  seed layer was obtained by directly depositing 1.5 nm of  $SiO_x$  using E-beam evaporator. The top gate

dielectric consisting of 9.5 nm of  $Al_2O_3$  was deposited by atomic layer deposition (ALD) at 250  $^{0}$ C using Trimethylaluminium (TMA) and H<sub>2</sub>O precursors. ZrO<sub>2</sub> top gate dielectric was also deposited by ALD at 150  $^{0}$ C, while the precursor tetrakis(ethylmethylamino)zirconium (TEMAZ) and H<sub>2</sub>O was kept at 110  $^{0}$ C. The top gate contact was patterned using e-beam lithography, and 60 nm Ni was deposited and lifted off to form the electrode. The top gate contact was designed such that there are underlapped regions near the source and drain, as shown in **Figure 6b**. The devices were annealed in forming gas (120  $^{\circ}$ C for 0.5 h on Al<sub>2</sub>O<sub>3</sub> device). A lower annealing temperature and duration was chosen for the devices since they showed increased gate leakage for higher annealing temperatures and durations.

## 3.2.2 Electrical Characterization

Electrical measurements are performed on the devices. The transfer characteristics are measured, followed by capacitance vs. voltage and capacitance vs. frequency measurements, using a Keysight B1500A Semiconductor Device Analyzer and Room temperature (RT) probe-station.

Figure 7: Circuit diagram for capacitance and conductance measurement

During the measurements, we shorted the source and drain and connected them to one terminal of the capacitance measurement unit. We modified the bias on the other terminal of the capacitance measurement unit that was connected to the top gate electrode as shown in **Figure 7**. The back gate ( $V_{BG}$ ) was grounded at 0 V, since in our depletion mode MoS<sub>2</sub> FET, the channel is quite populated with electrons at  $V_{BG} = 0$  V, keeping the underlapped channel regions conductive.

#### 3.3 <u>Results & Discussions</u>

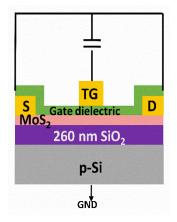

#### 3.3.1 Transfer Characteristics of MoS<sub>2</sub> FET

**Figure 8** shows the transfer characteristics of MoS<sub>2</sub> based FET for different high- $\kappa$  dielectric material as top gate dielectric. **Figure 8a** depicts the  $I_D$ - $V_G$  curve of MOS<sub>2</sub> FET for AlO<sub>x</sub> nucleation layer. The subthreshold swing (*SS*) of the device with ZrO<sub>2</sub> gate dielectric is 120 mV/decade (**Figure 8a(i)**), while it is 180 mV/decade for Al<sub>2</sub>O<sub>3</sub> gate (**Figure 8a(ii**)).  $I_D$ - $V_G$  curve for MOS<sub>2</sub> FET with SiO<sub>x</sub> nucleation layer shown in **Figure 8b** indicates the better *SS* compare to the AlO<sub>x</sub> nucleation layer. With SiO<sub>x</sub> nucleation layer, *SS* of 110 mV/decade (**Figure 8b(i**)) and 95 mV/decade (**Figure 8b(i**)) obtained for ZrO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> gate dielectric respectively.

#### **3.3.2** Subthreshold Swing Method for *D<sub>it</sub>* Extraction

The  $D_{it}$  at the interface of MoS<sub>2</sub> channel and different high- $\kappa$  gate dielectric can be calculated analytically using the Equation 5. SS values obtained from the transfer characteristics are used to calculate the  $D_{it}$ . For the calculation,  $C_{SiO_2} = \epsilon_{SiO_2}/t_{SiO_2} = 0.013 \,\mu\text{F/cm}^2$ , given  $\epsilon_{SiO_2} =$ 3.9, and 260 nm thickness of SiO<sub>2</sub>,  $C_S = C_{MOS_2} = \epsilon_{MOS_2}/t_{MOS_2} = 1.26 \,\mu\text{F/cm}^2$ , using  $\epsilon_{MOS_2} = 4$ ,<sup>16</sup> and 2.8 nm thickness of 4-layer MoS<sub>2</sub> flake are considered. With the AlO<sub>x</sub> nucleation layer, for ZrO<sub>2</sub>,  $C_{tg} = 1.56 \ \mu\text{F/cm}^2$ , considering the gate dielectric stack thickness  $t_{zrO_2} = 9.5 \text{ nm}$  and a nucleation layer  $t_{AlO_x} = 1.5 \text{ nm}$ , with  $\epsilon_{ZrO_2} = 25$  and assuming  $\epsilon_{Al_2O_3} = 5$  (experimental), For AlO<sub>x</sub>/Al<sub>2</sub>O<sub>3</sub> combination,  $C_{tg} = 0.402 \ \mu\text{F/cm}^2$ , considering the gate dielectric stack thickness  $t_{Al_2O_3} = 9.5 \text{ nm}$  With the SiO<sub>x</sub> nucleation layer, for ZrO<sub>2</sub>,  $C_{tg} = 1.15 \ \mu\text{F/cm}^2$  considering a nucleation layer  $t_{SiO_x} = 1.5 \text{ nm}$ , with assuming  $\epsilon_{SiO_x} = 3.9 \text{ The SiO}_x/Al_2O_3$  combination results  $C_{tg} = 0.387 \ \mu\text{F/cm}^2$ .

Figure 8: Transfer characteristics of the  $MoS_2$  based FET (a)  $AlO_x$  nucleation layer i)  $ZrO_2$  gated  $MoS_2$  FET i)  $Al_2O_3$  gated  $MoS_2$  FET (b)  $SiO_x$  nucleation layer i)  $ZrO_2$  gated  $MoS_2$  FET i)  $Al_2O_3$  gated  $MoS_3$  FET i)  $Al_3O_3$  FET i i)  $Al_3O_3O_3$  FET i i)  $Al_3O_3O_$

Obtained SS value and calculated capacitance are utilized to extract the  $D_{it}$  for different combinations of nucleation layer and gate dielectric, the resultant  $D_{it}$  values are tabulated in the Table 2. The interface trap density obtained for MoS<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> interface is impressive and can be compared with the highest reported quality of Si/high- $\kappa$  dielectric interfaces. [75-77]

| Nucleation Layer | Top Gate Dielectric            | <i>D<sub>it</sub></i> (states/cm <sup>2</sup> -ev) |

|------------------|--------------------------------|----------------------------------------------------|

| AlOx             | ZrO <sub>2</sub>               | 5.2×10 <sup>12</sup>                               |

|                  | Al <sub>2</sub> O <sub>3</sub> | 3.0×10 <sup>12</sup>                               |

| SiOx             | ZrO <sub>2</sub>               | 3.7×10 <sup>12</sup>                               |

|                  | Al <sub>2</sub> O <sub>3</sub> | 6.0×10 <sup>11</sup>                               |

Table 2: Interface trap density  $(D_{it})$  of MoS<sub>2</sub> FET for different high gate dielectric extracted using subthreshold swing (SS) method.

## 3.3.3 Capacitance and Conductance Measurement

The conductance method demands the capacitance and conductance measurement of the FET device. All the capacitance and resistance sources contribute to the measured capacitance and conductance are shown in the equivalent circuit model at **Figure 9**.

Figure 9: Equivalent circuit model for MoS<sub>2</sub> FET on Si/SiO<sub>2</sub> substrate with top gate.

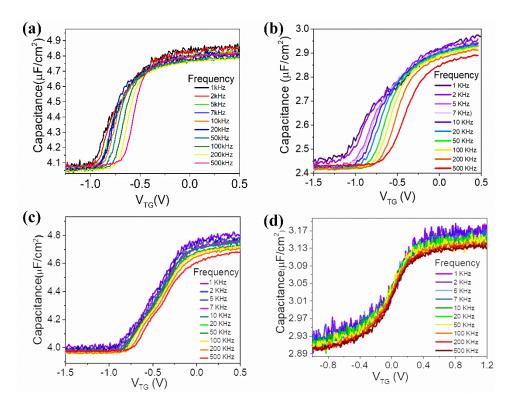

**Figure 10** shows the capacitance-voltage characteristics as a function of frequency for  $MoS_2$  for the different gate dielectrics. **Figure 10a** shows *C-V* curves of the  $MoS_2$  FET with the  $ZrO_2$  gate dielectric and  $AlO_x$  nucleation layer. The *C-V* curve contains significant frequency dispersion at the depletion region. Similar trend is observed for the  $Al_2O_3$  gate dielectric with  $AlO_x$  nucleation layer as shown in **Figure 10b**. The dispersion in the depletion region is a clear signature of the presence of interface traps. The different response of the traps at the different frequency

causes the dispersion in the depletion region of the *C*-*V* curve.[51, 78] On the other hand, with  $SiO_x$  nucleation layer devices show little hump for  $ZrO_2$  top gate dielectric and no dispersion for  $Al_2O_3$  gate dielectric. The presence of little hump in the **Figure 10c** for  $ZrO_2$  gate dielectric is also indicative of trap states. [78] In the **Figure. 10d**, the *C*-*V* curves do not show any significant frequency dependence in the depletion region from 1 kHz to 500 kHz, indicating the presence of few interface traps. Similar observations of dispersion-less *C*-*V* characteristics were made by Chen et al., in an MoS<sub>2</sub> metal-insulator-semiconductor capacitor with h-BN bottom gate.[56] The high capacitance in the accumulation region is attributed to parasitic capacitances due to the ungated regions adjacent to the source and drain. The frequency dispersion in the accumulation region for all the devices is attributed to border traps.[72, 79]

Figure 10: Frequency dependence of capacitance-voltage curve of the MoS<sub>2</sub> FET with (a)  $AlO_x/ZrO_2$  gate dielectric (b)  $AlO_x/Al_2O_3$  gate dielectric (c)  $SiO_x/ZrO_2$  gate dielectric (d)  $SiO_x/Al_2O_3$  gate dielectric.

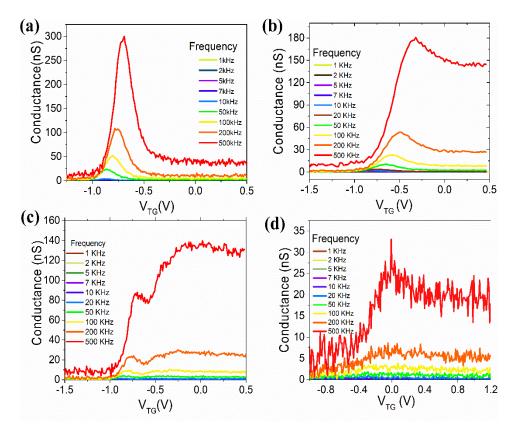

Figure 11 delineates the parallel conductance *vs.* top gate voltages of the MoS<sub>2</sub> FET for different gate dielectrics. Parallel conductance curve with the sharp peak is another indication of the interface traps. [80, 81]The parallel conductance curves shown in the Figure 11a and 11b for  $AlO_x/ZrO_2$  and  $AlO_x/Al_2O_3$  gate dielectric respectively have prominent peaks and support our results obtained from the SS method and findings from the capacitance-voltage measurement. The absence of sharp peaks for both gate dielectric material with SiO<sub>x</sub> nucleation layer (Figure 11c and 11d) denote the better-quality interface for the SiO<sub>x</sub> nucleation layer compare to the AlO<sub>x</sub> nucleation layer.

Figure 11: Conductance-voltage curve of the  $MoS_2$  FET with (a)  $AlO_x/ZrO_2$  gate dielectric (b)  $AlO_x/Al_2O_3$  gate dielectric (c)  $SiO_x/ZrO_2$  gate dielectric (d)  $SiO_x/Al_2O_3$  gate dielectric

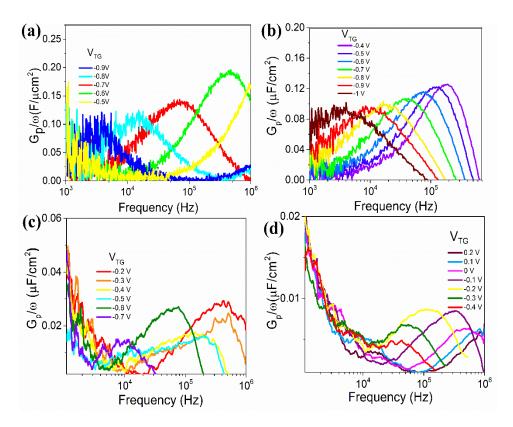

## **3.3.4** Conductance Method for *D<sub>it</sub>* Extraction

The interface trap densities are now extracted more rigorously, using the conductance method. In the case of an  $MoS_2$  FET, the channel is populated with electrons when gate voltage is 0 V, and as the gate voltage is swept to negative, the channel is depleted of electrons. Thus, the interface trap profile at depletion and deep depletion can be obtained in these devices. The technique for the conductance method relies on measuring the equivalent parallel capacitance of a MOS-Capacitor as a function of bias voltage and frequency. The conductance gives an idea of the interface trap density as it fluctuates with the capture and emission of carriers by the traps at the interface between the channel and the dielectric.

The conductance method was implemented at room temperature, in air. Since the device possesses series resistances from the ungated regions and from the contacts, the corrected capacitance  $C_c$  and conductance  $G_c$  need to be extracted first from the measured capacitance and conductance. First, the series resistance  $R_s$  is obtained by biasing the device in accumulation, and then the following expression is applied

$$R_S = \frac{G_{ma}}{G_{ma}^2 + \omega^2 C_{ma}^2} \tag{14}$$

where  $G_{ma}$  and  $C_{ma}$  are the measured conductance and capacitance, respectively, in the accumulation region, and  $\omega = 2\pi \times$  frequency. Now, the series resistance factor is calculated as  $a = G_m - (G_m^2 + \omega^2 C_m^2)R_s$ , where  $G_m$  and  $C_m$  are the measured conductance and capacitance, respectively. The corrected  $G_c$  and  $C_c$  can be then calculated as:

$$G_{C} = \frac{(G_{m}^{2} + \omega^{2} C_{m}^{2})a}{a^{2} + \omega^{2} C_{m}^{2}}$$

(15)

$$C_{C} = \frac{(G_{m}^{2} + \omega^{2} C_{m}^{2})C_{m}}{a^{2} + \omega^{2} C_{m}^{2}}$$

(16).

Now  $G_p/\omega$  is calculated as:

$$\frac{G_p}{\omega} = \frac{\omega G_C C_G^2}{G_C^2 + \omega^2 (C_G - C_C)^2} \tag{17}$$