#### POLITECNICO DI TORINO Repository ISTITUZIONALE

#### A novel fully depleted monolithic active CMOS microstrip sensor

| Original A novel fully depleted monolithic active CMOS microstrip sensor / Giampaolo, RAFFAELE AARON (2022 Mar 08), pp. 1-134.          |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| Availability: This version is available at: 11583/2959959 since: 2022-03-29T16:59:31Z                                                   |

| Publisher: Politecnico di Torino                                                                                                        |

| Published DOI:                                                                                                                          |

| Terms of use: Altro tipo di accesso                                                                                                     |

| This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository |

|                                                                                                                                         |

| Publisher copyright                                                                                                                     |

|                                                                                                                                         |

|                                                                                                                                         |

|                                                                                                                                         |

(Article begins on next page)

####

# A novel fully depleted monolithic active CMOS microstrip sensor

#### Raffaele Aaron Giampaolo

\* \* \* \* \* \*

#### Supervisors

Prof. A. Rivetti, Supervisor Doc. M.D. Rolo, Co-supervisor

#### **Doctoral Examination Committee:**

Prof. R. Aloisio, Referee, GSSI

Prof. L. Gonella, Referee, University of Birmingham

Politecnico di Torino December 25, 2021

| This thesis is licensed under a Creative Commons License, Attribution - Non commercial - No Derivative Works 4.0 International: see www.creativecommons.org. The text may be reproduced for non-commercial purposes, provided that credit is given to the original author. |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I hereby declare that the contents and organisation of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.                                        |

|                                                                                                                                                                                                                                                                            |

| Raffaele Aaron Giampaolo Turin, December 25, 2021                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                            |

### Summary

Romantically speaking, sensors are the way experiments see the universe while, the electronics, the way they can process and understand it. In recent years the complexity and performance of integrated circuits adopted for sensing purposes has increased at an amazing pace. The commercial adoption of monolithic and hybrid pixels has led the scientific community to always find new solutions to improve the design of sensors and electronics while keeping the costs and power dissipation of the devices under control.

Monolithic devices, differently from traditional sensor/electronics couples are the perfect candidates for experiments requiring large area detectors while keeping production costs to a bare minimum. This is due to their intrinsically low material budget and to a decreased number of steps required for production compared to conventional or hybrid sensors.

This thesis presents the research and development of a custom fully depleted monolithic active CMOS sensor produced within the ARCADIA collaboration. In particular, through a close contact between Italian Universities and the INFN (Istituto Nazionale di Fisica Nucleare), the design, simulation and production of a novel active monolithic microstrip detector has been possible.

A set of evaluation structures, both passive and active, has been experimentally tested via electrical, radiation and particle characterization. The results are shown within this thesis proving full device depletion and a correct sensor to electronics monolithic coupling.

The electronics schematic and layout design of a configurable readout IC chip, ASTRA, are discussed. ASTRA (Adapatable Space sTrips Readout ASIC) features configurable gain, peaking time and readout architecture. This configurability makes it a good candidate for readout of commercially available microstrip sensors and also for adoption with active monolithic strip sensors.

Concluding, theoretical studies of the input capacitance and electronic simulation results are shown in the final chapter proving a correct channel functionality and programmability.

# Dedicated to my family and friends

# Contents

| Li | st of          | Table   | $\mathbf{s}$                                                                        | V     |

|----|----------------|---------|-------------------------------------------------------------------------------------|-------|

| Li | st of          | Figur   | es                                                                                  | VI    |

| 1  | Mo             | nolithi | ic active sensors                                                                   |       |

|    | 1.1            | State   | of the art technologies                                                             |       |

|    |                | 1.1.1   | HV and HR CMOS MAPS sensors                                                         |       |

|    |                | 1.1.2   | SOI sensors                                                                         |       |

|    |                | 1.1.3   | ALPIDE                                                                              | 1     |

|    |                | 1.1.4   | DEPFET Pixels                                                                       | 1     |

|    |                | 1.1.5   | 3D CMOS and hybrid pixel sensors                                                    | 1     |

|    | 1.2            | MAPS    | S Recap                                                                             | 1     |

|    | 1.3            | Micro   | strips                                                                              | 1     |

|    |                | 1.3.1   | Depletion voltage and strip capacitance                                             | 1     |

|    |                | 1.3.2   | Microstrips in Space Applications                                                   | 1     |

|    |                | 1.3.3   | Monolithic Microstrips                                                              | 2     |

| 2  | <b>The</b> 2.1 |         | D and ARCADIA monolithic sensor technology ARCADIA Sensor                           | 2 2 2 |

|    |                | 2.1.2   | Backside processing                                                                 | 3     |

|    |                | 2.1.3   | Pixel radiation tolerance                                                           | 3     |

|    | 2.2            | ARCA    | ADIA test structures                                                                | 3     |

|    |                | 2.2.1   | Passive Test Structures                                                             | 3     |

|    |                | 2.2.2   | Active Test Structures                                                              | 3     |

| 3  | Exp            | erime   | ntal Campaigns                                                                      | 4     |

|    | 3.1            | I-V cu  | irves                                                                               | 4     |

|    |                | 3.1.1   | Test Setup                                                                          | 4     |

|    |                | 3.1.2   | Test Results                                                                        | 4     |

|    | 3.2            | Light   | irradiation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 5     |

|    |                | 3.2.1   | Test Setup                                                                          | 5     |

|    |       | 3.2.2 Test Results                             | 2 |

|----|-------|------------------------------------------------|---|

|    | 3.3   | Proton beam                                    | 5 |

|    |       | 3.3.1 Test Setup                               | 6 |

|    |       | 3.3.2 Test Results                             | 7 |

|    | 3.4   | MATISSE tests                                  | 0 |

|    |       | 3.4.1 Sensor characterization                  | 0 |

|    |       | 3.4.2 Electronic characterization 6            | 0 |

|    |       | 3.4.3 Electronic and sensor characterization 6 | 1 |

|    |       | 3.4.4 Fe55 Characterization                    | 5 |

| 4  | Mo    | nolithic Space Strips 69                       | 9 |

|    | 4.1   | Sensor Design                                  | 0 |

|    |       | 4.1.1 In-Pixel Metal Density                   | 1 |

|    | 4.2   | Electronics Enclosure                          | 2 |

|    | 4.3   | Top-Side Biasing                               | 3 |

|    | The   | e ASTRA ASIC 7                                 | 5 |

|    | 5.1   | ASTRA Building Blocks                          |   |

|    | 5.2   | Front-End Design                               |   |

|    | 5.3   | CR-RC Shaper Design                            |   |

|    |       | 5.3.1 Input capacitance study                  |   |

|    |       | 5.3.2 Fast-OR Architecture                     |   |

|    |       | 5.3.3 Sample and Hold circuit                  |   |

|    | 5.4   | Analog Readout                                 |   |

|    |       | 5.4.1 Multiplexer                              |   |

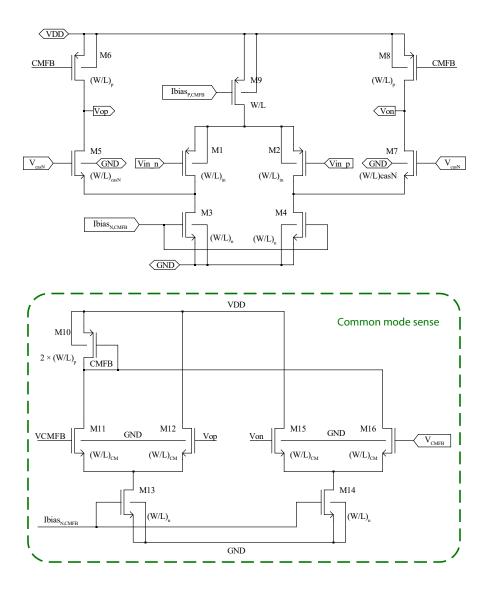

|    |       | 5.4.2 Single ended to Differential Amplifier   |   |

|    |       | 5.4.3 Large Output Buffers                     | 2 |

|    | 5.5   | Digital Readout                                | 9 |

|    | 5.6   | General ASTRA features                         | 4 |

|    |       | 5.6.1 Power Consumption                        | 4 |

|    |       | 5.6.2 CMOS Switches                            | 5 |

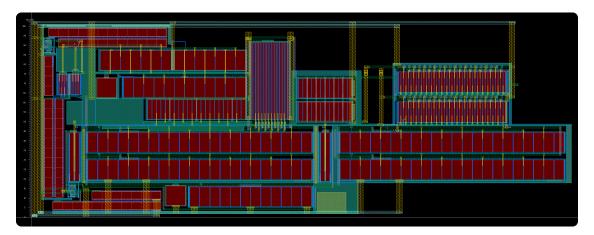

|    |       | 5.6.3 Layout Features                          |   |

|    |       | 5.6.4 Biasing Scheme                           |   |

| 6  | Cor   | nclusions and future research 109              | 9 |

| -  | 6.1   | List of PhD Publications                       |   |

| Bi | bliog | graphy 11:                                     | 3 |

|    |       |                                                |   |

# List of Tables

| 1.1 | Comparison of most advanced MAPS designs |

|-----|------------------------------------------|

| 2.1 | Pseudo-matrices electrode geometries     |

| 3.1 | TCT Parameters                           |

| 3.2 | Tested Sensor samples                    |

| 5.1 | ASTRA Peaking time configuration bits    |

| 5.2 | Analog chain transistor sizes            |

| 5.3 | Wilkinson ADC configuration bits         |

| 5.4 | ASTRA Power Consumption                  |

# List of Figures

| 1.1  | Reduction of transistor nodes                            | 1 |

|------|----------------------------------------------------------|---|

| 1.2  | ±                                                        | 2 |

| 1.3  | O                                                        | 4 |

| 1.4  | Illustration of HV-CMOS MAPS design                      | 7 |

| 1.5  |                                                          | 8 |

| 1.6  | Illustration of SOI MAPS design                          | 9 |

| 1.7  | Illustration of the ALPIDE MAPS                          | 0 |

| 1.8  | Illustration of the DEPFET                               | 1 |

| 1.9  | Illustration of a bump bonding                           | 2 |

| 1.10 | Illustration of a three layered CIS                      | 3 |

| 1.11 | Illustration of a microstrip detector                    | 6 |

| 1.12 | Illustration and photograph of the AMS detector          | 8 |

|      | Illustration of HERD detector                            | 9 |

| 1.14 | First Monolithic Microstrip front-end                    | 0 |

| 1.15 | First Monolithic Microstrip Microphotograph              | 2 |

| 2.1  | Illustration of the ARCADIA MAPS                         | 5 |

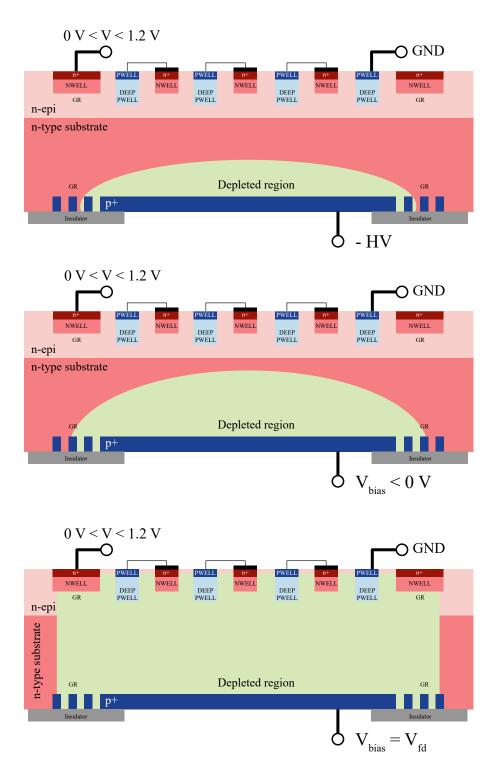

| 2.2  | Illustration of the ARCADIA depletion                    | 7 |

| 2.3  | Single pixel simulation domain                           | 8 |

| 2.4  | Single pixel current with varying electrode bias voltage | 9 |

| 2.5  | Single pixel simulated current                           | 0 |

| 2.6  | Backside guard ring illustration                         | 1 |

| 2.7  | Guard ring study                                         | 2 |

| 2.8  | Pixel current radiation damage effects                   | 3 |

| 2.9  | Test structures backside                                 | 5 |

| 2.10 | Test structures layout                                   | 6 |

| 2.11 | ARCADIA main demonstrator                                | 8 |

| 2.12 | MATISSE Layout and Read-Out logic                        | 9 |

| 2.13 | Monolithic Strips Illustration                           | 0 |

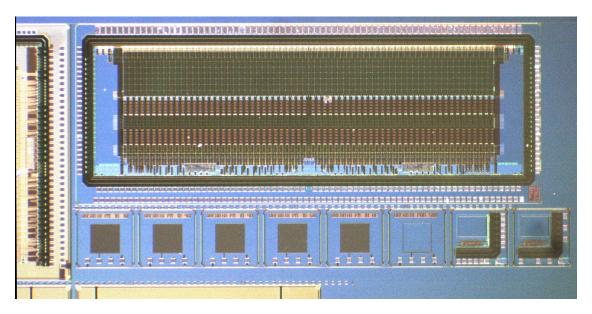

| 2.14 | New Test Structures Microphotograph 4                    | 1 |

| 3.1  | Diode GRN and GRP test results                           | 4 |

| 3.2  | Punch-through voltage I-V curves                         | 5 |

| 3.3  | Full depletion I-V Curves                                | 7 |

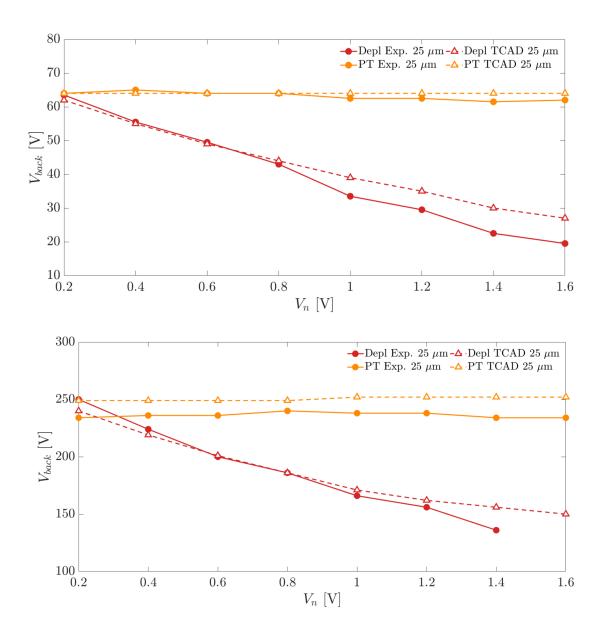

| 3.4  | Operation region to V <sub>n</sub> correlation for different thicknesses . |  |  | 48 |

|------|----------------------------------------------------------------------------|--|--|----|

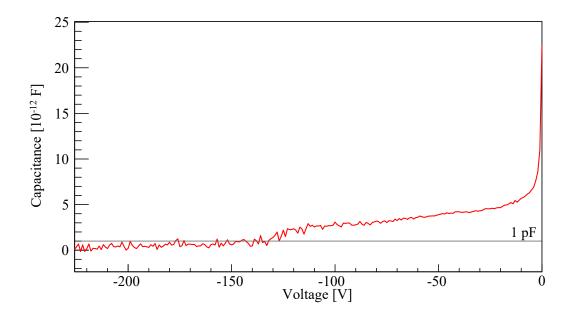

| 3.5  | PM50 C-V curve                                                             |  |  | 49 |

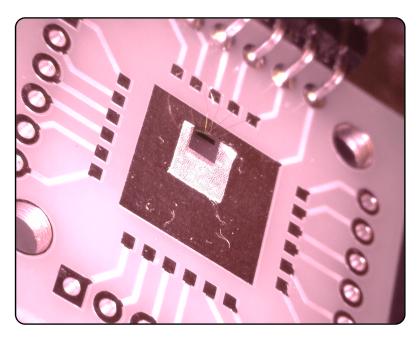

| 3.6  | Test structures image                                                      |  |  | 50 |

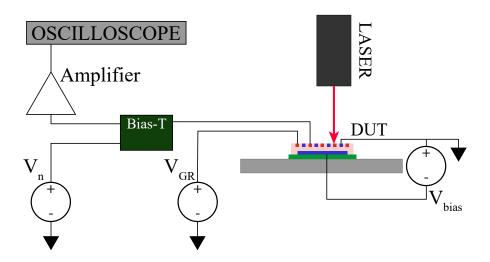

| 3.7  | LASER Setup                                                                |  |  | 51 |

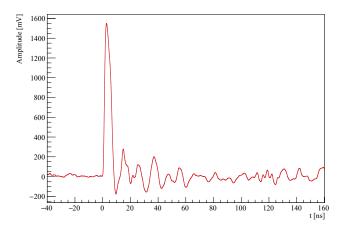

| 3.8  | TCT waveform with $\lambda_{IR}$                                           |  |  | 52 |

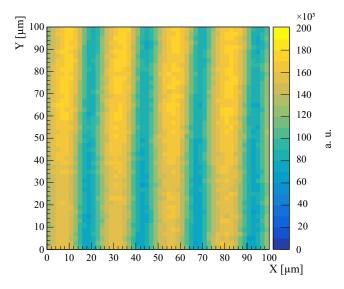

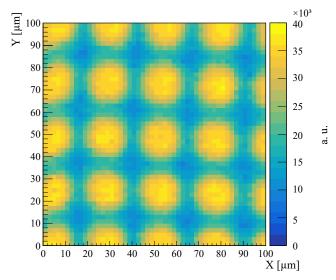

| 3.9  | TCT area scan with $\lambda_{IR}$                                          |  |  | 54 |

| 3.10 | TCT area scan with $\lambda_{red}$                                         |  |  | 54 |

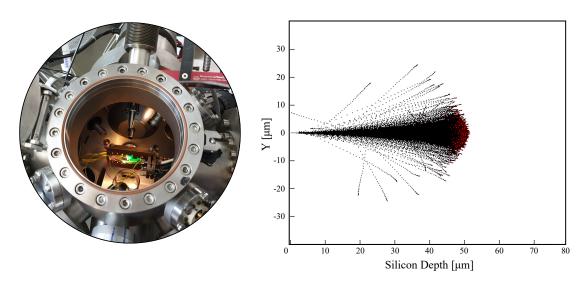

| 3.11 | 2 MeV proton penetration depth in Si                                       |  |  | 55 |

| 3.12 | Proton microbeam test setup illustration                                   |  |  | 56 |

| 3.13 | 3D plot showing a $100\mu m$ thick sensor PM25 edge                        |  |  | 57 |

| 3.14 | 2D comparison of PM25 and PM50                                             |  |  | 59 |

|      | MATISSE IV curves                                                          |  |  | 60 |

| 3.16 | MATISSE Injection Circuit and CSA                                          |  |  | 61 |

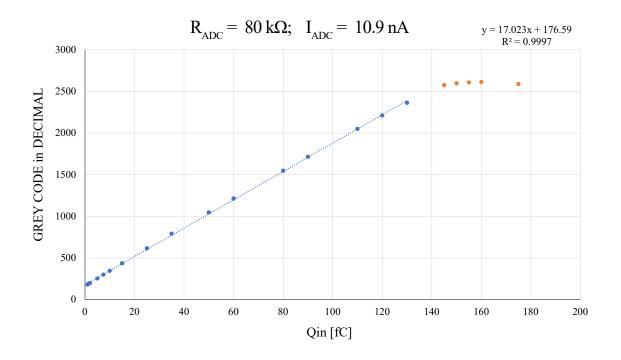

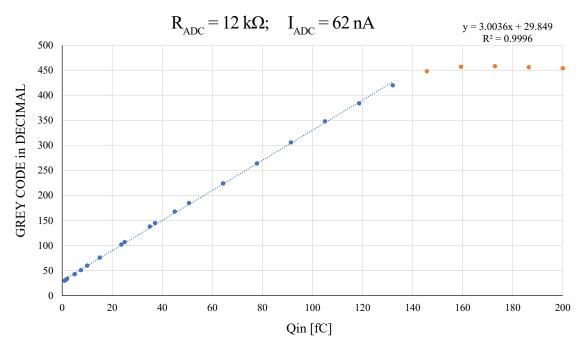

| 3.17 | MATISSE Linearity                                                          |  |  | 62 |

| 3.18 | MATISSE depletion extraction                                               |  |  | 63 |

|      | MATISSE LASER tracking                                                     |  |  | 64 |

|      | MATISSE Fe55 Results                                                       |  |  | 66 |

| 3.21 | MATISSE Fe55 Cluster Shape                                                 |  |  | 67 |

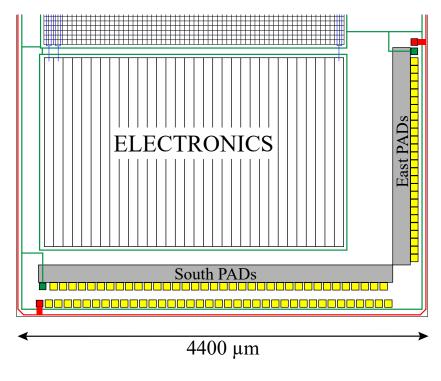

| 4.1  | Layout of the monolithic active microstrip sensor                          |  |  | 69 |

| 4.2  | FE to Strip interconnection layout                                         |  |  | 71 |

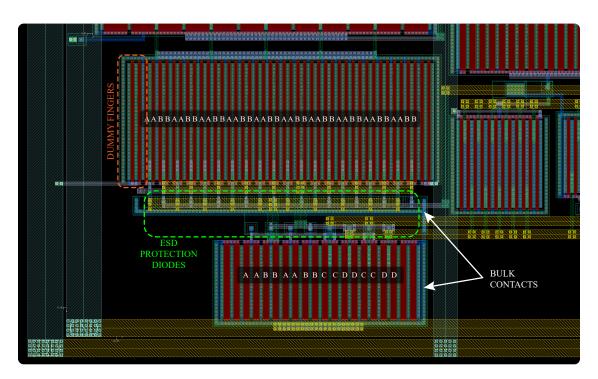

| 4.3  | Electronics enclosure layout                                               |  |  | 72 |

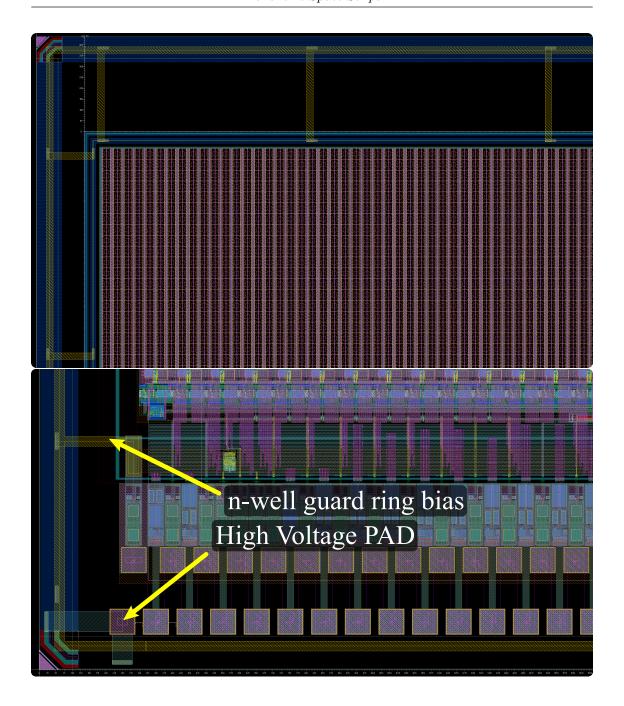

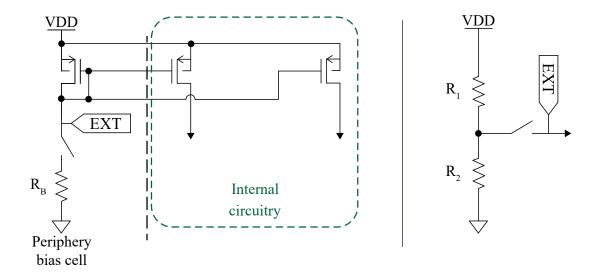

| 4.4  | Top bias illustration                                                      |  |  | 73 |

| 4.5  | Top bias and guard ring layout                                             |  |  | 74 |

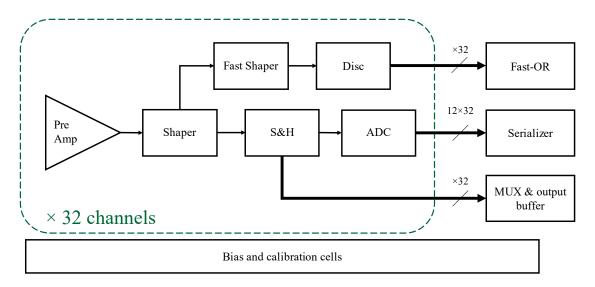

| 5.1  | ASTRA Building Blocks                                                      |  |  | 76 |

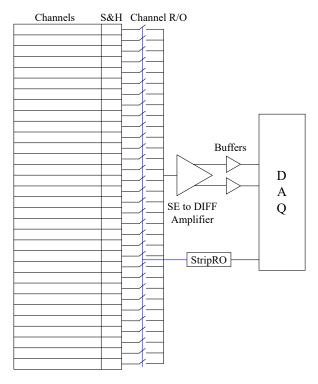

| 5.2  | ASTRA Analog Readout Scheme                                                |  |  | 77 |

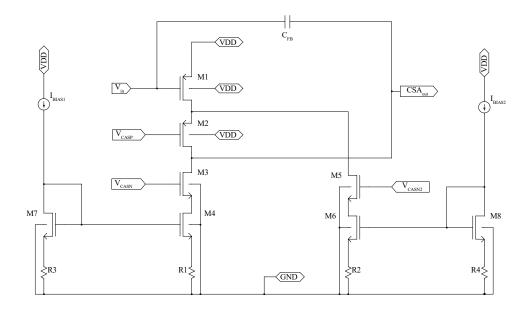

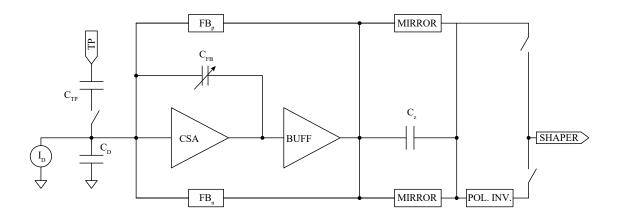

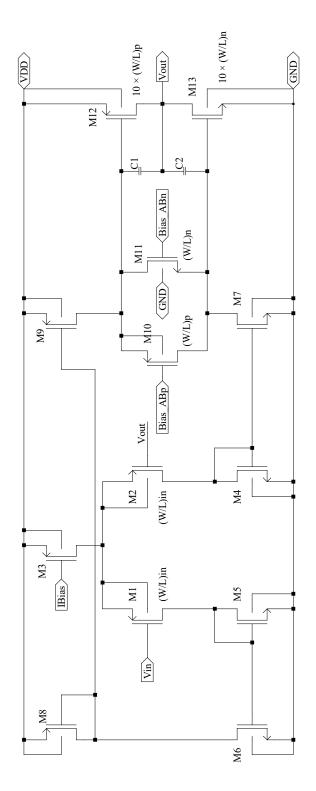

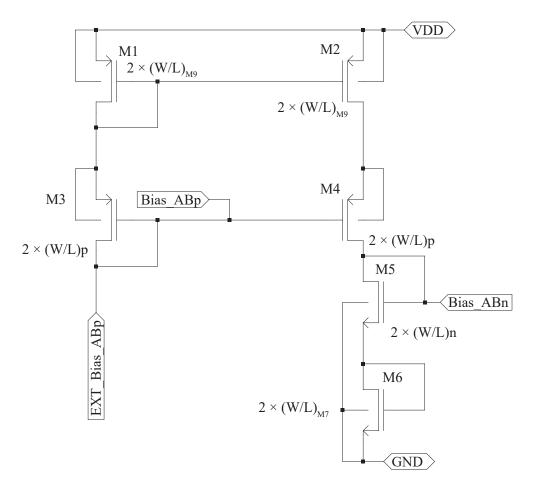

| 5.3  | ASTRA CSA                                                                  |  |  | 78 |

| 5.4  | ASTRA VFE                                                                  |  |  | 79 |

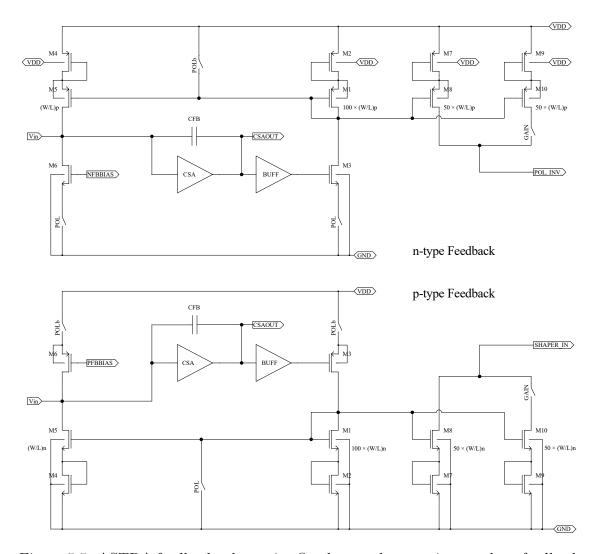

| 5.5  | ASTRA Feedback                                                             |  |  | 81 |

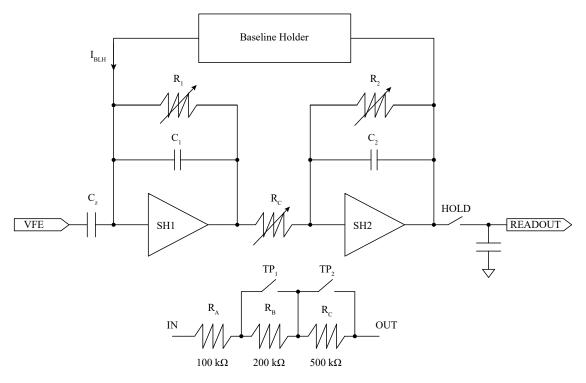

| 5.6  | ASTRA Shaper Block design                                                  |  |  | 82 |

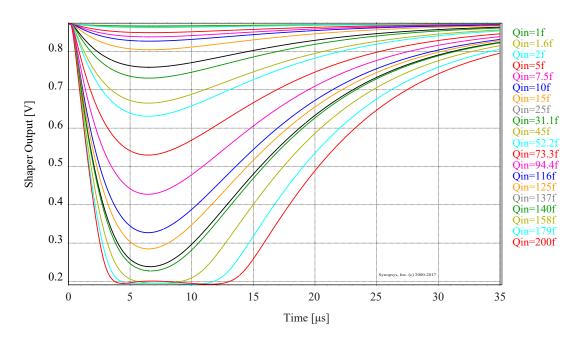

| 5.7  | ASTRA Shaper Output Waveform                                               |  |  | 84 |

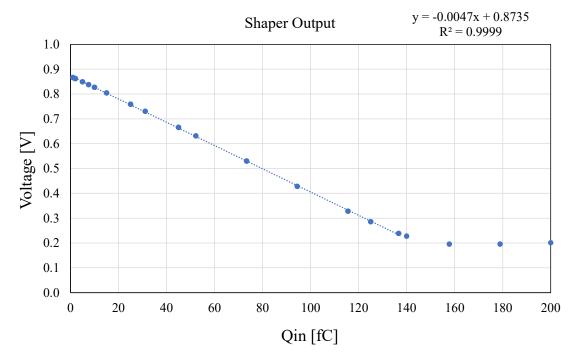

| 5.8  | ASTRA Shaper Linearity                                                     |  |  | 84 |

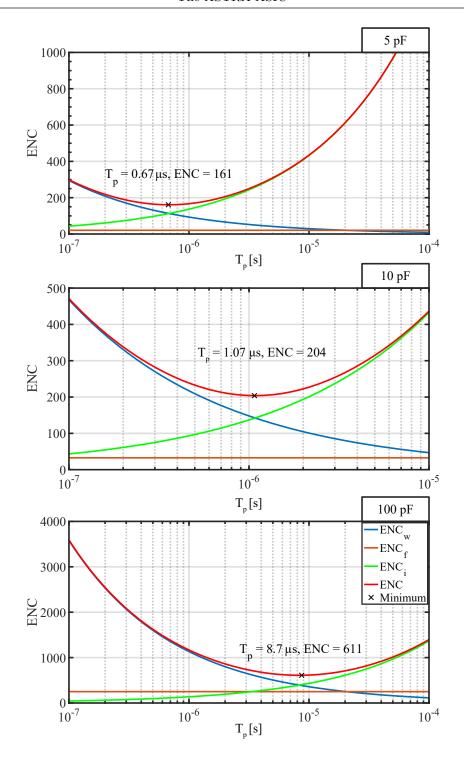

| 5.9  | ASTRA Noise minimization study                                             |  |  | 86 |

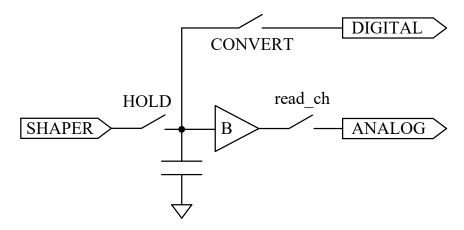

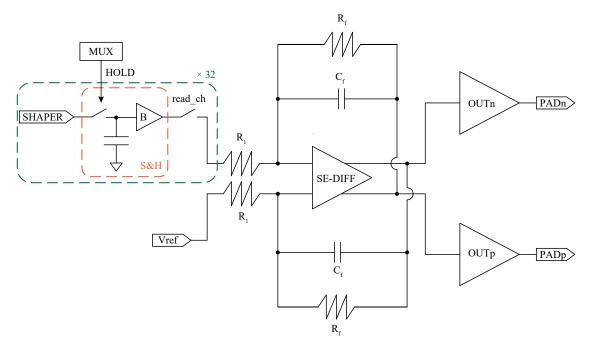

| 5.10 | ASTRA Sample and Hold                                                      |  |  | 87 |

| 5.11 | ASTRA Analog Output                                                        |  |  | 88 |

| 5.12 | ASTRA SE-to-DIFF Amplifier Layout                                          |  |  | 90 |

|      | ASTRA SE-to-DIFF Amplifier Schematic                                       |  |  | 91 |

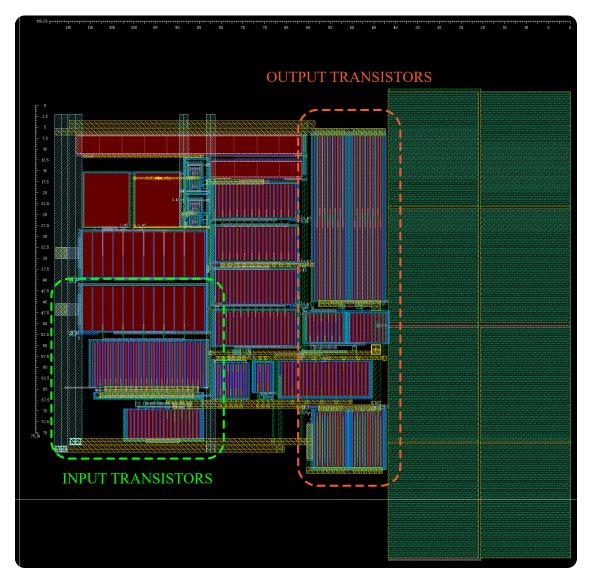

| 5.14 | ASTRA Output Buffer Layout                                                 |  |  | 92 |

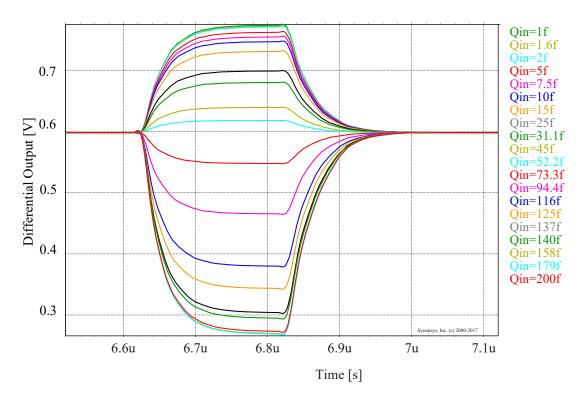

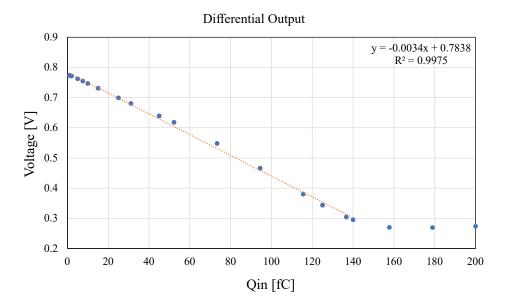

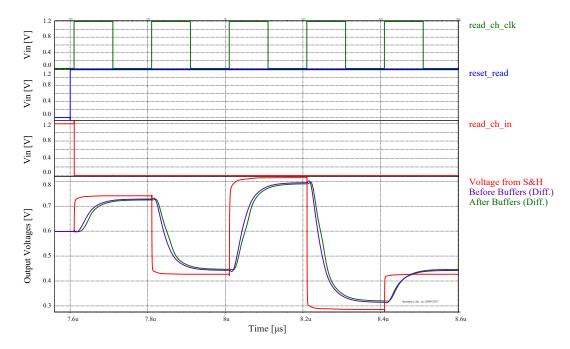

|      | ASTRA Readout Simulation                                                   |  |  | 93 |

|      | ASTRA Readout Linearity                                                    |  |  | 94 |

|      | ASTRA Readout With Digital Control Signals                                 |  |  | 95 |

| 5.18 | ASTRA Output Buffer Schematic                                              |  |  | 96 |

|      | ASTRA Buffer Bias Circuitry                                                |  |  | 97 |

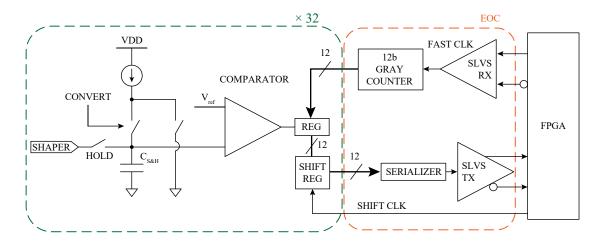

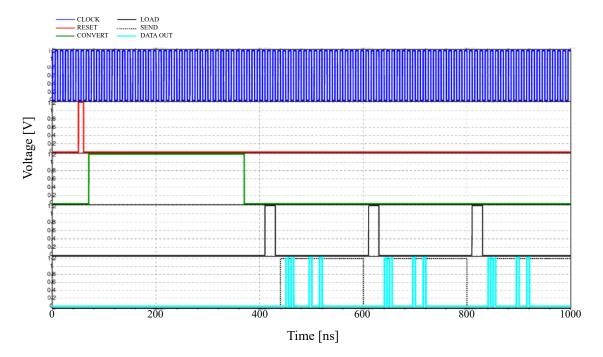

| 5.20 | ASTRA Digital readout blocks      | 99  |

|------|-----------------------------------|-----|

| 5.21 | ASTRA Digital Readout Simulation  | 102 |

| 5.22 | Wilkinson ADC Linearity           | 103 |

| 5.23 | ASTRA Inter-digitized Transistors | 106 |

| 5.24 | ASTRA Bias Circuitry              | 107 |

| 5.25 | ASTRA Microphotograph             | 108 |

## Chapter 1

### Monolithic active sensors

Great advances in the electronics field have increased the adoption of silicon detectors in High Energy Physics (HEP) experiments. In particular, Complementary Metal-Oxide Semiconductors (CMOS) have seen a great shrinkage in size and, in turn, an increase in complexity per unit area.

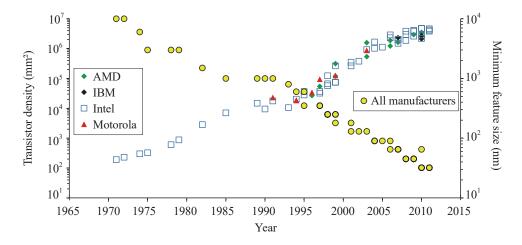

An implication of smaller size is the production of detectors with higher granularity and more complexity in signal processing in smaller areas. Furthermore, following Moore's law, the cost per transistor, which is proportional to the transistor node (figure 1.1), has greatly decreased in the last few decades rendering silicon detectors extremely convenient also for large area detectors. [52, 69, 53] This is of paramount importance for future particle detectors which will require a great surface coverage with a high granularity for vertex reconstruction [18, 80].

Figure 1.1: Reduction of transistor node (gate length) and increase in transistor density in microprocessors over time [28].

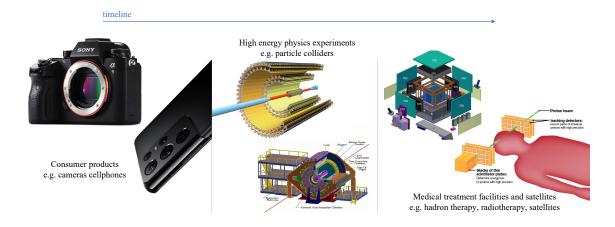

Figure 1.2: Timeline of future MAPS developments. In the past MAPS have been adopted mainly in CMOS image sensors in the commercial field. Presently, MAPS have been mounted on the STAR and ALICE vertex detectors and are being used in favor of hybrid active pixel sensors thanks to their low material budget. In the future we can envision micro-satellites and detectors for space applications adopting MAPS in order to reduce possible mechanical faults and the payload for space exploration. Also, remaining on Earth, radio- and hadron therapy will embrace the adoption of MAPS thanks to the possibility of having extra thin active sensor layers for beam localization.

In order to address the need for high granularity, two different technologies can be adopted. The first one adopts hybrid pixels, where a device comprises two different layers, one to detect and one to amplify the signal from radiation or impinging particles. The first layer is a silicon sensor used as sensitive volume while the second layer includes the CMOS electronics for the signal processing and readout. The separation between the sensor and the ASIC (Application Specific Integrated Circuit) implies the possibility of developing the layers using different technologies and materials. This leads to a good degree of device optimization [10]. The second technology adopts one single substrate for both the sensor and the electronics. Devices produced with this technique are called Monolithic Active Pixel Sensors (MAPS) [73, 75].

Considering the adoption of a single substrate to fabricate the detector, MAPS are much cheaper than hybrid pixels implying a great interest for HEP applications requiring large active areas. Nonetheless, hybrid active pixels sensors (HAPS) have been historically preferred due to their higher degree of customization and inherited performance. To reduce the performance gap, various R&D companies and laboratories are working on improving MAPS technologies to make them the mainstream devices adopted in future experiments. A timeline showing the progress

of MAPS is shown in figure 1.2. The greatest focus is on enabling full thickness (epitaxial layer or bulk) depletion. The ability to fully deplete the sensor would lead to a high radiation hardness, a higher signal to noise ratio per power dissipated and drift charge collection. Furthermore, the adoption of thick depleted substrates can be of great interest in X-ray imaging for medical purposes.

In cases where an extremely low power budget is fundamental, microstrips are adopted in place of pixels. Microstrips can either be a set of single strips of collecting electrodes or an arrangement of pixels connected along a single direction. This arrangement implies a one-dimensional particle localization, but with a lower processing complexity. Nevertheless, a set of thin microstrips planes can yield a precise x-y particle localization while keeping power consumption below the corresponding power dissipated by pixel arrays of the same pitch. Historically, a drive to reduce stray capacitances has led to the inclusion of parts of the front-end electronics onto the microstrip sensor wafer.

This chapter includes an overview of the state of the art in monolithic sensors and monolithic microstrips.

#### 1.1 State of the art technologies

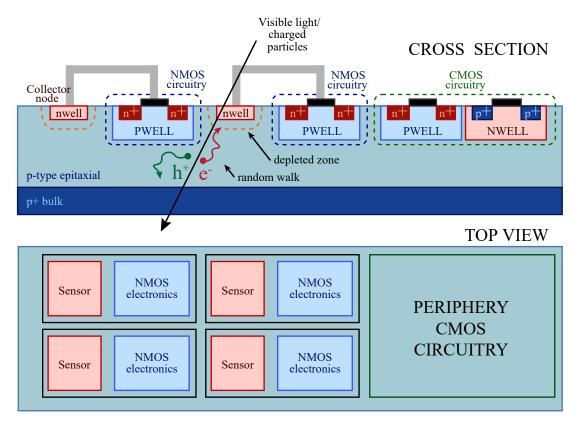

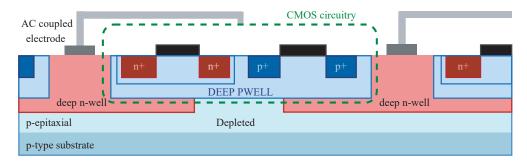

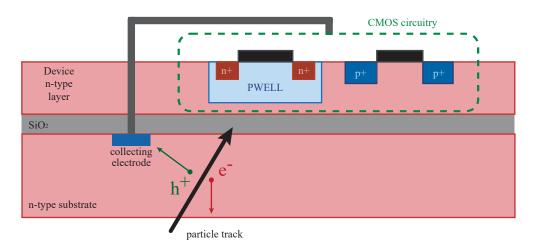

Figure 1.3: Illustration of conventional MAPS design. Visible light or charged particles cross the sensing volume generating charged couples of electrons and holes which are collected by the top electrodes. In conventional MAPS most circuitry is designed adopting N-JFET or NMOS technology with the complementary devices located at the edge of the device.

Conventional MAPS are detectors which adopt a single silicon wafer layer capable of particle or radiation detection and signal processing as seen in figure 1.3. These detectors are widely adopted in industrial applications and are now being focused on by the scientific community.

Historically, most experiments have adopted HAPS (section 1.1.5) rather than MAPS due to their high customizability, resulting from the independent fabrication of the electronics and sensor layers. Nevertheless, in HEP experiments, careful attention is focused on costs and the material budget of the sensing devices. In fact, it is of paramount importance to reduce the quantity of materials adopted for particle tracking in order to reconstruct the trajectory with high precision near the vertex. In addition to the sensing devices, also cooling and holding structures are

found in the detecting layers which lead to a higher material budget. Considering the sensor to electronics volume ratio, MAPS have an advantage over HAPS when pushing the material budget to its lower limits. Moreover, since the electronics are directly connected to the small collecting electrodes, the analog power required for a high SNR decreases. The decrease in power consumption also leads to smaller cooling systems.

Moreover, HAPS have been historically favored in high-rate experiments where faster electronics were required, while MAPS were adopted mainly in low-rate detectors due to the adoption of less scaled technologies. Nevertheless, the decreasing transistor size and small electrodes increase the granularity of the sensor. By adopting, in recent years, smaller technology nodes, MAPS are narrowing the gap with HAPS in rate capability. Nevertheless, the increase in transistor density and rate capability will drive up digital power density in MAPS. The narrowing performance gap and lower material budget are favoring the development of MAPS in place of HAPS for high-rate vertex detectors [76].

Furthermore, a higher number of interconnections, and, in turn, points of structural weakness are found in HAPS due to the extreme precision required for the sensor-to-electronics connection. This issue is non-present in modern MAPS due to having, at least, the very front end (VFE) with some sort of low level communication protocol with the outside world to reduce the number of interconnections and their parasitics. Moreover, the precise bump bonding (typically adopting PbSn) required for connecting pixels with a pitch below 50µm can be realized only by a few companies worldwide. The adoption of extra production steps and precise bump bonding techniques leads to a final fabrication cost, for a large area detector, much higher than that of MAPS produced with standard CMOS technologies.

As aforementioned, sensor and CMOS wafers are very different. In particular, the main difference is in the silicon crystalline purity which affects the minority carrier lifetime. This parameter is important in sensors where a longer lifetime implies that the recombination of the radiation generated electron-hole pairs is less likely, thus it is easier to collect the generated charge. The reticle optimization is done by using float-zone silicon which is dislocation-free and with a low density of impurities. This production method enables the fabrication of high resistivity wafers which, coincidentally, also favors the full depletion of the sensor. In fact, the full depletion depth can be expressed as:

$$x_{dep} \approx \sqrt{\frac{2\varepsilon_0 \varepsilon_{\rm Si} V_{\rm bias}}{q N_{\rm eff}}} = \sqrt{2\varepsilon_0 \varepsilon_{\rm Si} \rho \mu V_{\rm bias}}$$

(1.1)

where  $V_{\rm bias}$  is the reverse bias biasing voltage,  $N_{\rm eff}$  the effective doping, q the electron charge,  $\varepsilon_0$  and  $\varepsilon_{\rm Si}$  are, respectively, the free space permittivity and the dielectric constant of silicon.  $\rho$  is the resistivity and  $\mu$  the carrier mobility.

On the other hand, CMOS electronics do not require substrate optimization,

thus the substrate is grown with the Czochralski method which decreases carrier lifetime through the impurities. Once the substrate is produced, IC are UV printed on a thin layer grown epitaxially on the substrate. The epi-layer is lightly doped and exhibits a low resistivity  $1-10\,\Omega\,\mathrm{cm}$ . This implies that sensors built with these characteristics would exhibit an early breakdown and a small depletion depth.

The different requirements for the two detector components required smart engineering to merge the possibility of maintaining a high production yield and collection efficiency. Various designs have been proposed for monolithic sensors. The first proposal for sensors with embedded processing electronics dates back to the first 1990s where pin collecting electrodes generate signals processed by PMOS-only electronics. The amplified signal was then processed in the matrix periphery where CMOS readout and control electronics were harbored [71, 73]. Various interesting technological breakthroughs have led to different flavors of MAPS, each with their strengths and issues.

The first MAPS adopted in HEP are in the STAR experiment at the RHIC (Relativistic Heavy Ion Collider) of the Brookhaven National Laboratory [33, 23, 26]. Now many experiments adopt MAPS in their tracking detectors, this section gives an overview of modern monolithic active pixel sensors and also includes an overview of the latest hybrid active pixel sensors.

#### 1.1.1 HV and HR CMOS MAPS sensors

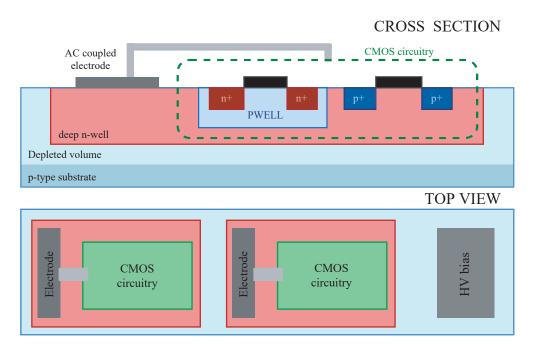

Figure 1.4: Illustration of HV-CMOS MAPS design. A large deep n-well in a p-type epitaxial layer is adopted to collect charges. The large n-well also acts as the CMOS electronics host.

High voltage MAPS (Fig. 1.4) employ low-voltage CMOS transistors within structures capable of sustaining high voltages. The first HV-MAPS inherit HV-CMOS technologies which are adopted by automotive and industrial devices meant to sustain voltages above typical low-voltage CMOS chips. The technology includes a large area deep n-well featuring a high breakdown voltage thanks to the low doping values. The n-well is repurposed, in radiation and particle detectors, as the cathode in a depleted p-type substrate. The front-end electronics is embedded within the n-well collecting electrode with the positive power supply latched to it in order to reverse bias the source and drain diodes of the PMOS transistors [65].

The sensor design leads to a few design problems that must be solved. Firstly, considering that the whole processing chain is contained in each pixel, the size of the electrode cannot be arbitrarily small. Furthermore, the shorted n-well requires a large value resistor per each pixel (in the  $G\Omega$  order of magnitude) to prevent the signal loss through the power net. In addition, the p-well and PMOS p+ diffusions are capacitively coupled to the cathode implying that a small crosstalk signal (due to the bulk effect) between transistors can lead to an output response similar to that of an impinging particle. Thus, a larger adoption of NMOS transistors, in

Figure 1.5: Illustration of HR-CMOS MAPS design. The design issues of the HV-CMOS are fixed by adopting a deep p-well which hosts the CMOS electronics, while a deep n-well is adopted as a collecting electrode within the p-type epitaxial layer.

spite of PMOS ones, is found within the pixel circuitry.

The typical depletion depth within an HV-CMOS sensor is  $x_{dep} \approx 30 \,\mu\text{m}$  which makes the technology a good candidate in vertex detectors requiring a very low material budget sensor such as in the Mu3e experiment [9, 70]. Here a biasing voltage between 30 and 70 V is adopted. On the other hand, the depletion region is not sufficient in cases where a larger sensitive volume is required such as X-ray imaging. In these cases a depletion region larger than 200  $\mu$ m is preferred which implies a modification of the substrate resistivity.

To overcome these issues, the ATLAS collaboration has developed a process variation adopting  $1 \,\mathrm{k}\Omega$  cm resistivity epitaxial layers to increase the depletion region while keeping the biasing voltage below 150V. Preliminary results with high resistivity substrates a depletion region of  $\approx 80\,\mathrm{\mu m}$  can be achieved with 120 V biasing voltage [27].

High Resistivity CMOS MAPS, illustration shown in figure 1.5, are being studied in the CLIC (Compact Linear Collider) collaboration. In this case  $300 \times 30 \mu m^2$  cells include eight small n-type collecting electrodes each connected to their own analog and digital electronics. The cells are arranged in a  $16 \times 128$  matrix and are independently shielded by a deep p-well implant. The small electrode ensures a low parasitic capacitance while keeping a high fill factor and a fine segmentation [55, 45, 44].

#### 1.1.2 SOI sensors

Figure 1.6: Illustration of SOI MAPS design. A buried oxide divides the CMOS electronics layer from the sensing substrate.

Silicon On Insulator (SOI) CMOS electronics (Fig. 1.6) have been in the engineering world for quite some time and are often found in consumer devices thanks to their transistor isolation technique. In fact, in the SOI technology each transistor resides on its own island and there is no connection to the bulk. This isolation is made possible through the adoption of a buried oxide (BOX) which separates the CMOS layer from the mechanical support wafer bulk. Clearly, the intrinsic separation between the CMOS epi-layer and the possibility of using a high resistivity bulk wafer would be the monolithic dream [46, 57]. Nevertheless, the usage as sensors in HEP experiments has not been prolific. This is due to two reasons. Firstly, the high resistivity bulk couples with the transistor channel acting as a secondary gate. This is because the BOX effectively acts as a capacitor accumulating charge at the bottom Si-SiO<sub>2</sub> interface giving rise to the back-gate effect. The most noticeable result of this effect is the threshold shift in the CMOS electronics. Secondly, the main weakness of the SOI sensors is their radiation hardness. In fact, total ionizing dose effects (TID) are harmful due to the buried oxide which, when hit by radiation, is actively filled with positive charges further varying the transistor threshold voltages. Clearly, a solution to the BOX effects on SOI devices is required for HEP experiments. Various R&D groups are working on this issue proposing various solutions. In particular, the adoption of p+ implants below the electronics and the design of a thicker or double BOX have been proposed to increase the radiation hardness to 500 kGy and will also mitigate the back-gate effect [40, 19, 76, 35, 34].

#### 1.1.3 **ALPIDE**

Figure 1.7: Illustration of the ALPIDE MAPS. Similar to HR-CMOS, the CMOS electronics are harbored within a deep p-well in a p-type epitaxial layer. The depleted volume is limited to the first tens of microns leading to diffusion charge collection in areas away from the collecting electrodes.

The increase of luminosity within the HEP experiments has led scientists to researching better ways to detect particles with MAPS. In particular, researchers at CERN have designed MAPS capable of fulfilling the harsh requirements needed for operation in the future high luminosity large hadron collider (LHC) experiments (up to  $6 \times 10^{27} \,\mathrm{cm}^2\mathrm{s}^{-1}$ ).

The ALICE experiment Inner Tracking System (ITS) is being updated during the second long shutdown with ALPIDE (ALICE PIxel DEtector) [67, 48]. The MAPS, shown in figure 1.7, feature a small pixel pitch of  $27 \times 29 \,\mu\text{m}^2$  with 4 small n-well collecting electrodes yielding a small detector capacitance and a high SNR. The CMOS processing electronics, designed in Towerjazz 0.18  $\mu$ m CIS technology, are built in deep p-wells within a thick 25  $\mu$ m epi-layer. The substrate, where the biasing voltage is applied, features a p++ doping and a reverse bias up to  $-6 \,\text{V}$  is possible. The pixel hit-map is generated on chip and sent out through priority encoding [78, 4].

Due to the adoption of standard CIS technology on a p-type epi-layer, the depletion region does not reach the p++ back. This implies the separation of the active sensor in areas with drift charge collection and areas where charges move by diffusion. Clearly, in the depleted areas the charge collection is quick, but, in the non-depleted areas the diffusion of carriers generated by the impinging radiation leads to longer signal acquisition times and charge spreading to neighboring pixels. Investigator chips and new designs have been developed at CERN to solve these issues [5, 37, 72].

#### 1.1.4 DEPFET Pixels

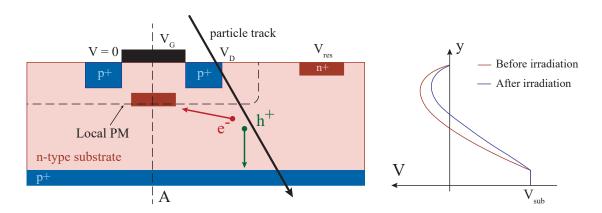

Figure 1.8: Illustration of the DEPFET. On the right is the voltage profile along the cut line A. The potential variation is shown which generates a threshold change in the mosfet characteristics [42].

DEPMOS (depleted MOSFET) and DEPFET (depleted field effect transistor) refer to an interesting variation in standard MOSFET and JFET technologies. Based on semiconductor drift chambers (SDC), DEPMOS technologies (figure 1.8) adopt a tapered potential in the bulk to convey the collected charge (e) in a small n-doped area below a PMOS transistor. Here, this charge actively varies the threshold voltage of the transistor modifying, in turn, its source-drain characteristic current. This location coincides with the local potential maximum (PM), thus, the carriers will be slowly discharged by the PMOS current until a reset signal is sent through an n+ electrode on the top to remove the remaining charge stored in the potential pocket [42].

The n-deposition below the gate can thus be effectively considered a second gate for the transistor. These double gate transistors can then be arranged in matrices and readout in a rolling shutter method or can be coupled with a secondary charge transfer gate in order to enable correlated double sampling on pixel.

Nevertheless, the DEPFET technology does not have in-pixel electronics or digitization due to its extremely customized bulk potentials. This implies that the pixel currents are either amplified on a separated chip or in the matrix periphery not making it yet a viable option for experiments where an extremely low material budget is required [47, 49].

#### 1.1.5 3D CMOS and hybrid pixel sensors

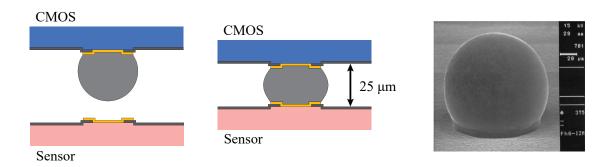

Figure 1.9: *left* Illustration of the bump bonding process. The *orange* layer is an Under Bump Metallization (UBM) which is adopted to improve the yield of the bump bonding process and facilitates the interconnection between the layers by providing a solder wettable surface. On the *right*, a SEM micrograph of a SnAg bump [29].

Differently from the sensors previously described, hybrid active pixel sensors are not monolithic sensors. Nevertheless, the impressive consumer adoption and evolution of this sensor-electronics couple requires an inclusion within the state-of-the-art chapter.

HAPS, illustrated in figure 1.9, are composed of two stacked layers of detecting and processing CMOS wafers. The independent processing of the layers implies the possibility of customizing the detector for each experiment [66].

HAPS, which are widely adopted in HEP experiments, such as Timepix3, adopt the bump bonding technique to connect the sensor to the CMOS readout chip. The technique adopts solder spheres precisely located between the two layers. Depending on the adopted materials the diameter of the bonding contacts ranges from 25 to 50µm. On the other hand, the most common bump bonding pitches found in HEP detectors are  $50\,\mu\mathrm{m}$  wide, while the ultimate pitch could be around  $5-10\,\mu\mathrm{m}$  [29]. Nevertheless, presently, small pitches below  $30\,\mu\mathrm{m}$  can hardly be achieved with a high yield, thus are not yet the HEP HAPS standard.

Furthermore, considering, as explained in the chapter's preamble, the high costs for small production volumes (compared to consumer devices) required for building large detecting surface detectors with customized HAPS, the future adoption of these sensors becomes less appealing compared to MAPS.

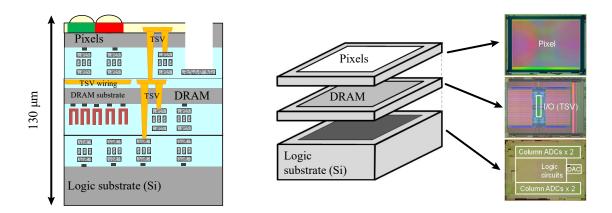

A large R&D effort in HAPS is found in modern consumer cameras and cell phones which require a transistor count that cannot be fitted onto a single substrate. This R&D has led to the adoption of through silicon vias (TSV) for the connection

Figure 1.10: Illustration and layout of a three layered HAPS designed for visible light detection [74].

of the various layers, which can be more than 2, creating a new branch of detectors categorized as 3D CMOS detectors. Until now, due to the consumer application scope and much higher non-recurrent engineering costs, they have been adopted in visible light detection rather than particle or high energy radiation detection. The specific visible light application implies the possibility to have extremely small pixel pitches down to 0.8 µm [62].

Concluding, in cases where the detecting areas are not too large (e.g. medical X-ray imagers and hadron therapy) and advanced on-chip digital signal processing (DSP) is required, HAPS are a highly competitive option. Moreover, the adoption in HEP detectors of the state-of-the-art 3D CMOS developments found in consumer cameras (figure 1.10), such as TSV and direct wafer bonding, could improve the manufacturability yield and final costs for very large productions [10].

#### 1.2 MAPS Recap

Considering the great number of MAPS flavors, an overview of all the previously explained technologies is required.

Various proposals have been brought up for MAPS each with their positive features and drawback. Due to the high speed at which MAPS technologies are evolving it is difficult to categorize each one in a single snapshot. Nevertheless, in table 1.1 a categorization of the most prominent advantages and issues of each technology is given. In order to have a simple reference, the characteristics of each technology are taken from the experimental designs of some the most prominent collaborations in HEP experiments.

The expected total ionizing dose is referred to the experiment in which the MAPS will be used, thus they are not the maximum achievable doses before failure. In particular, when considering SOI-MAPS, the maximum achievable TID should be above 500 kGy with double-BOX technology [35], in the table the column refers to the adoption of SOI-MAPS in the FORCE (Focusing On the Relativistic universe and Cosmic Evolution) satellite. Thus, a high radiation hardness is not required.

Concluding, a great benefit in pixel size and power density can be expected by the custom design of fully depleted monolithic pixel sensors. However, most technologies require a custom processing of the device wafer and, thus, a higher production chain load for a standard CMOS foundry. In the following chapters the design of the novel FD-MAPS will be introduced and explained in a detailed manner.

|                              | HV-CMOS            | HR-CMOS          | SOI            | ALPIDE         | DEPFET         | HAPS           |

|------------------------------|--------------------|------------------|----------------|----------------|----------------|----------------|

| Experiment                   | STAR               | CLIC             | FORCE          | ALICE          | Belle II       | Timepix 3      |

| Standard CMOS                | Yes                | Yes              | $N_{0}$        | Yes            | $N_{\rm o}$    | Yes            |

| Tech node $[nm]$             | 350                | 180              | 200            | 180  TJ CIS    | custom         | 130            |

| Pixel Size $[\mu m^2]$       | $20.7 \times 20.7$ | $37.5 \times 30$ | $30 \times 30$ | $27 \times 29$ | $50 \times 50$ | $55 \times 55$ |

| Sensor Thickness [µm]        | 20                 | 200              | 300 - 500      | 20             | 75             | 700            |

| Material Budget [% $X_0$ ]   | 0.3                | 1 - 1.5          | N. A.          | <1 %           | 0.2            | few $\%$       |

| Spatial Resolution [µm]      | $\sim$ 3.7 - 6     | ~2               | 1.5 - 3        | $\sim$ 5       | 10             | 5              |

| Time Resolution [µs]         | $\sim 186$         | 0.156            | 65             | 30             | 20             | 0.0016         |

| Power Density $[mW cm^{-2}]$ | 150                | 100              | N. A.          | 300  to  100   | N. A.          | 225            |

| Expected TID $[kGy y^{-1}]$  | 6.0                | 1                | 0.001          | 4.5            | 15             | N. A.          |

| Reference                    | [23]               | [44]             | [34]           | [48]           | [51]           | [23]           |

Table 1.1: Comparison of most advanced MAPS designs. Full description in section 1.1.5.

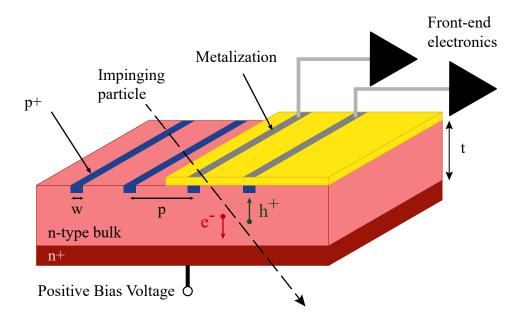

Figure 1.11: Illustration of a microstrip detector. The main geometrical parameters are indicated.

#### 1.3 Microstrips

In various experimental applications the adoption of microstrips is advantageous compared to the usage of pixelated sensors. In particular, when the particle flux is below tens of kHz using microstrips arranged in a perpendicular or slightly slanted formation yields good track reconstruction while keeping the dissipated power lower than pixel detectors. This particle flux is found in aero-spatial applications and satellite detectors which aim at achieving a particle hit-rate in the order of 1 kHz.

Furthermore, in order to reduce the dissipated power in MAPS a trade-off is required between the pixel area and number of processing transistors. Thus, most MAPS with pixel pitches below 30 µm do not measure the particle's energy, but a binary hitmap coupled with the hit timestamp [48].

The illustration of a common AC coupled p-in-n microstrip section is in figure 1.11. Here, the main parameters are depicted: w, strip electrode width; p, strip pitch; t, sensor thickness. Common pitch values range from 25 to 280  $\mu$ m. A key parameter in the design of microstrips is the width-to-pitch ratio w/p. A compromise must be found between the minimization of the strip capacitance and a high voltage stability, respectively solved designing a microstrip sensor with a small or a large w/p ratio.

#### 1.3.1 Depletion voltage and strip capacitance

Approximating a microstrip sensor to a planar diode of thickness t and width p, the thickness of the depleted layer is, remembering equation 1.1:

$$t_{dep} = \sqrt{\frac{2\varepsilon_0 \varepsilon_{\rm Si} V_{\rm bias}}{q N_{\rm eff}}}.$$

(1.2)

Thus, rearranging the terms, the full depletion voltage,  $V_{\rm fd,diode}$ , for a given thickness is:

$$V_{\text{fd,diode}} = \frac{q N_{\text{eff}}}{2\varepsilon_0 \varepsilon_{\text{Si}}} t^2. \tag{1.3}$$

Considering the back-plane capacitance per unit length at full depletion:

$$C_{\text{B,diode}} = \varepsilon_0 \varepsilon_{\text{Si}} \frac{p}{t}.$$

(1.4)

When considering the finite pitch and width of the microstrip detector two main effects arise [16, 39]. The first is an increase of the required voltage to reach full depletion. This effect can be understood considering the modification of the equipotential lines with the variation of w. In particular, when the width decreases, the equi-potential lines will curve near the collecting electrode requiring an increase in voltage to be straightened near it. A more realistic depletion voltage equation is thus:

$$V_{\rm FD} = V_{\rm fd,diode} \left[ 1 + 2 \frac{p}{t} f\left(\frac{w}{p}\right) \right] \tag{1.5}$$

where f(w/p) is a universal function depending on the width over pitch ratio. In the range 0.1 < w/p < 0.6 the function f monotonically decreases from 0.65 to 0.10. [11]

The second effect arising from the finite pitch and width is the decrease in the back-plane capacitance:

$$C_{\rm B} = C_{\rm B,diode} \frac{1}{1 + \frac{p}{t} f\left(\frac{W}{p}\right)}.$$

(1.6)

Considering also the interstrip capacitance, a total capacitance for a detector thickness  $t = 300 \,\mu\text{m}$ , standard pitch  $p = 100 \,\mu\text{m}$  and a ratio 0.1 < w/p < 0.55:

$$C_{\text{tot}} = \left(0.8 + 1.6 \, \frac{w}{p}\right) \frac{\text{pF}}{\text{cm}}.\tag{1.7}$$

The total capacitance of a microstrip is one of the most important parameters a front end electronics designer must consider. In particular, by reducing the

input capacitance to the electronics the equivalent noise charge figure can be reduced without increasing the dissipated power as will be discussed in the electronics chapter 5.

#### 1.3.2 Microstrips in Space Applications

Figure 1.12: *left* Photograph taken from the Russian Mir space station while Space Shuttle Discovery passes below it. In the cargo bay the AMS-01 detector can be noticed near the aft firewall (circled in orange) [3]; *right* illustration of the updated AMS-02 detector aboard the ISS.

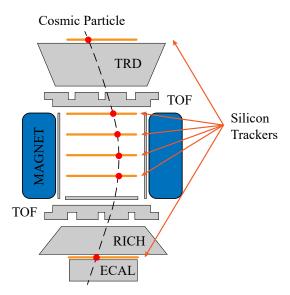

The most common application for silicon strips is in high energy physics experiments, but they are also often found in satellite particle detectors. Cosmic ray detectors, found in orbit, adopt silicon microstrips as particle trackers in order to evaluate the particle's charge, energy and interaction points within the detectors.

An interesting example is the AMS-02 detector deployed onto the ISS (International Space Station). Precursor detectors such as the AMS-01 and the PAMELA experiments also used microstrips sensors [8, 64, 15]. The detector employs a total of 2264,  $41.360 \times 72.045 \times 0.300 \text{mm}^3$ , double-sided Si microstrip sensors. In particular, the two sides of the microstrips have n and p doping profiles arranged in a perpendicular direction which collect, respectively, the generated electrons and holes [12]. The collecting electrode regions are AC coupled to low power external ASIC chips. Most detecting layers, as illustrated in figure 1.12, are located within a large permanent magnet which deviates the charged particles crossing the detector. The silicon trackers measure, with a location standard deviation below  $10\mu\text{m}$ , the

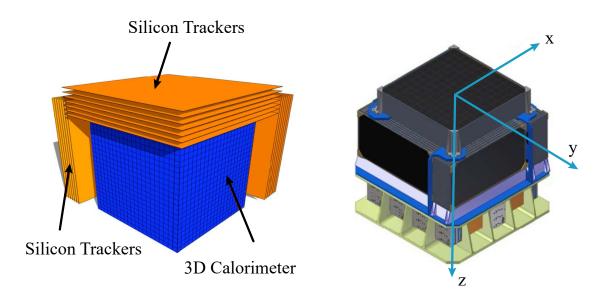

Figure 1.13: *left* illustration of HERD's internal detectors; *right* realistic rendering of the HERD detector

interaction coordinates of the impinging particles with the active layers and extract information regarding the particle's charge and energy.

An example of future adoption of microstrips is in the HERD (High Energy cosmic-Radiation Detection) experiment [30, 77]. The illustration of the detector and a realistic rendering are in figure 1.13. The detector will be hosted in 2025 by the Chinese space station and study cosmic rays and, through indirect detection, look for dark matter.

The silicon trackers are designed for a precise cosmic ray trajectory tracking, gamma ray conversion and tracking and complementary charge measurements (up to Z=26). While the central detector volume will use  $\approx 7500$  LYSO crystals for novel 3D energy studies with a large acceptance.

#### 1.3.3 Monolithic Microstrips

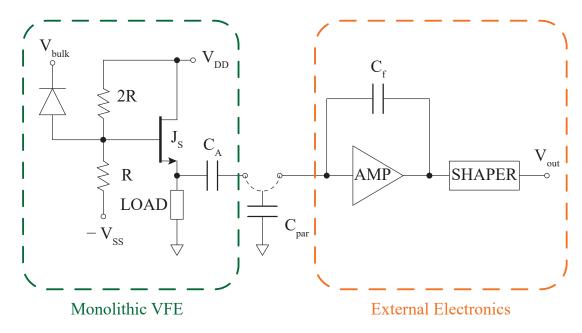

Figure 1.14: First Monolithic Microstrip front-end [14]. On the *left* side the internal monolithic circuitry is shown, while on the *right* the external electronics. Between the two parts, a bond wire is shown with its parasitic capacitance,  $C_{par}$ .

The harsh environment and stringent specifications required in space have led to the research and development of methods to include a very front-end onto the silicon sensor substrate.

Many issues surface when sending electronics to space. On take-off the strong acceleration and the random and sinusoidal vibrations felt by the payload can break the metal bondings between the electronics and the sensors. In particular, the pyroshock due to the rocket stage separation can influence the equipment even before deployment. When deployed, the orbiting electronics must be able to withstand thermal stresses due to sun light (seasonal and day/night effects) and also be able to cool down in space vacuum.

To mitigate the first issue, a reduction of the total number of bondings and interconnections is favorable, making MAPS or monolithic microstrips appealing to the space community. For the second issue, a reduction of the power dissipated implies a lower temperature increase of the electronics due to its operation. In this case, the adoption of microstrips with integrated electronics also implies a reduction of required dissipated power thanks to the higher signal-to-noise (SNR) achievable with monolithic CMOS sensors.

Silicon sensor grade substrates differ from standard CMOS ones because of their

high resistivity  $(4-6 \text{ k}\Omega \text{ cm})$  and pureness. In fact, sensor grade substrates require purification techniques in order to remove contaminants which would act as particle traps within the active volume.

The different steps required for higher silicon pureness found in sensor grade wafers implies a customization of the production chain to also include a very front end within the detector.

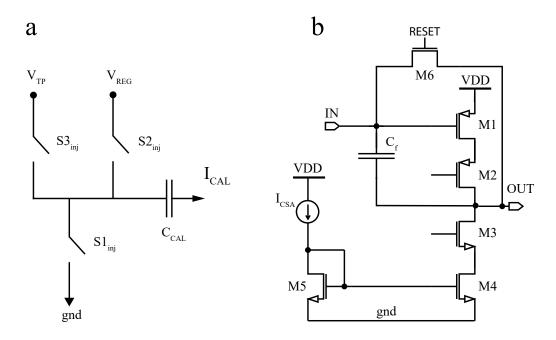

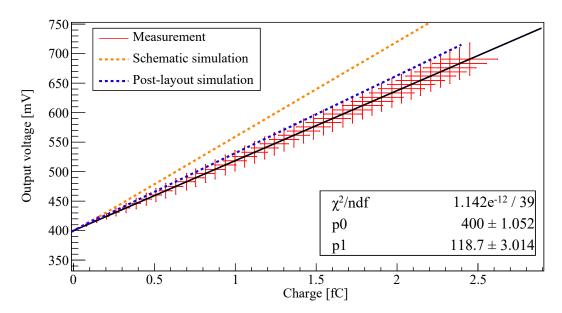

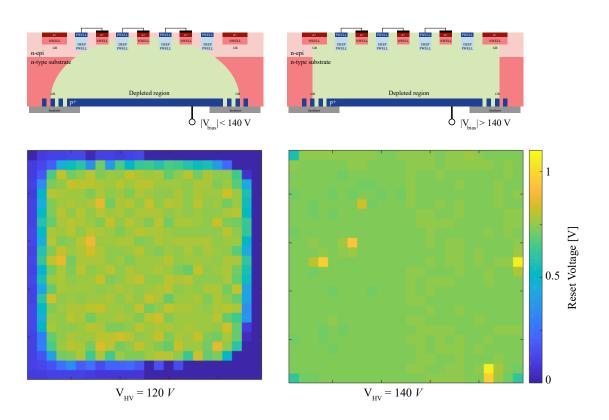

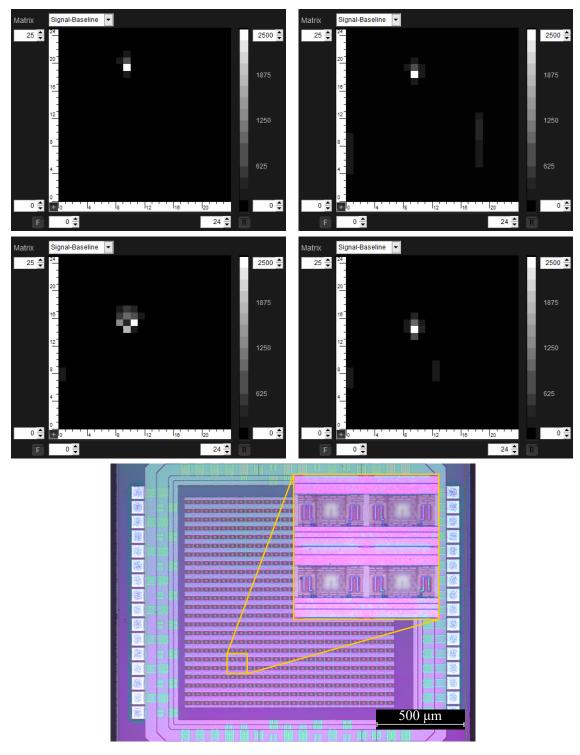

Nevertheless, microstrips including the first electronic amplification stages have been designed to prove monolithic microstrips feasibility [14, 25]. A schematic and a microphotograph of the monolithic structures are in figures 1.14 and 1.15. The first amplifying stage, composed of a common source N-JFET with a diode connected load transistor, is monolithically designed on chip and AC coupled to a charge sensitive amplifier (CSA) through an internal coupling capacitor, C<sub>A</sub>.

By the inclusion of a simple source follower amplifier the signal loss due to the parasitic capacitance due to the bonding and pad is avoided and a higher SNR per dissipated power can be achieved. The monolithic array, thus enables the possibility of moving the external electronics further away from the microstrip sensor and improve the experimental flexibility.

Concluding, various studies have been published on fully integrated preamplifiers onto high resistivity sensor grade wafers proving the clear advantage in including the front end electronics onto the detecting sensor chip [50]. However, these new devices are only adopting NMOS or N-JFET technology in the electronics, leading to a non-complementary and a less complex analog and digital design.

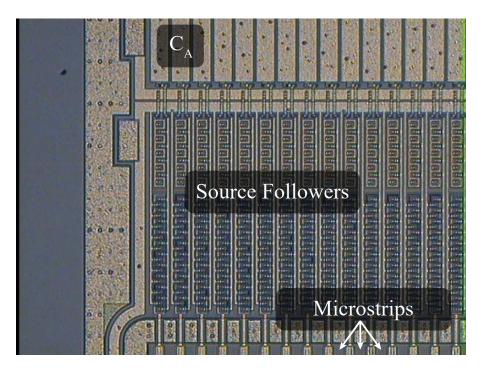

Figure 1.15: Microphotograph of one of the first monolithic microstrip very frontends [25]. On the top the internal to external electronics coupling capacitor,  $C_A$ , is visible, while, at the center the internal source follower topology N-JFET are pictured. At the bottom the connection between the gate of  $J_S$  and the microstrip top metal plate can be seen.

## Chapter 2

# The SEED and ARCADIA monolithic sensor technology

The INFN (*Istituto Nazionale di Fisica Nucleare*) has proposed a new monolithic technology within the ARCADIA collaboration.

ARCADIA's (Advanced Readout CMOS Architectures with Depleted Integrated sensor Arrays) objective is to manufacture fully depleted MAPS for HEP experiments adopting commercial CMOS image sensing technologies.

An Italian collaboration started at INFN Torino has been signed enabling a competitive research and development aimed at optimizing both the substrate and CMOS characteristics. The collaboration started in December 2013 with a shared vision between physicists and engineers with a broad background in image sensors and radiation detectors. At the time, a Sensor with Embedded Electronics Development (SEED) was the primary objective, proving the possibility of including transistors on a fully depleted substrate ranging from 100 to 300  $\mu$ m. In 2016, the prototypes have been submitted in different flavors. A set of 2 × 2 mm<sup>2</sup> ASICs designed in a 6 metal-layer 110 nm BSI (Back-Side Illumination) CMOS technology have been produced. In particular, a set of passive test-structures providing insights in substrate depletion regions and sensor capacitance are the first step for the characterization of sensor. A second test chip, with active pixel amplification and readout, has been produced proving the functionality of the sensor-electronics ensemble.

Since 2018, ARCADIA, relying on the positive results of SEED, has continued the development creating a variety of new large area test structures and continuing the evaluation of the test-structures developed in the SEED time-frame.

The ARCADIA collaboration is currently working on a series of large-area prototypes. The main demonstrator for the technology is a FD-MAPS enclosing an active matrix of  $512 \times 512$  pixels with a 25µm pitch implying a total active area of  $1.3 \times 1.3 \text{cm}^2$ . Additional test structures designed to test the manufacturability

and characteristics of pixels with pitches ranging from 10 to 50  $\mu$ m and total thicknesses from 50 to 200  $\mu$ m have been produced. In particular, the test structures designed are both passive and active sensors for the detailed study of the sensor to electronics couplings and the study of different pixel geometries.

Furthermore, various strip-like sensors have been designed on the ARCADIA reticle in order to test the sensor efficiency also for strip sensors. Moreover, an active monolithic sensor has been included which chapter 4 and 5 will focus on.

In this chapter, an overview of the sensor characteristics and simulations is given. The sensors, designed at the University of Trento have been simulated using advanced CAD (Computer Aided Design) software. On the other hand, the electronic design and validation steps have been done with advanced integrated circuit simulators adopting the commercial CMOS foundry PDK (Process Design Kit).

## 2.1 The ARCADIA Sensor

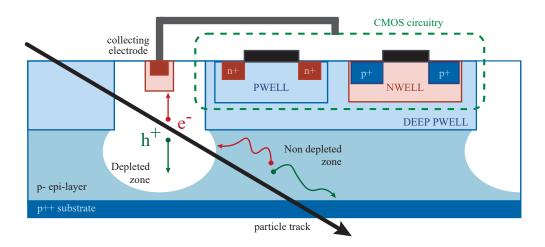

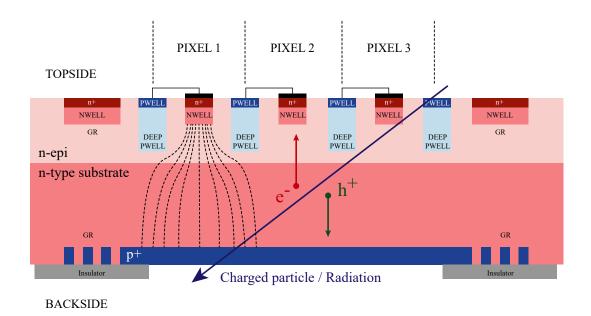

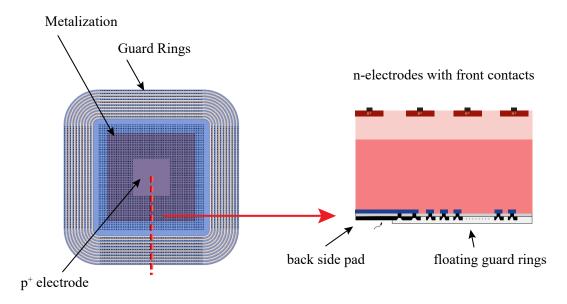

Figure 2.1: Illustration of the ARCADIA FD-MAPS.

The novel sensor developed within the ARCADIA collaboration, in figure 2.1, aims at mitigating the issues present in the state-of-the-art technologies adopting a fully-depleted substrate, a small collecting electrode and shielded CMOS electronics.

Full depletion implies the possibility of collecting carriers by drift throughout the sensor thickness, increasing the signal response speed. As aforementioned, a fully depleted bulk, having a larger detecting volume, leads to a larger amount of charges generated by the impinging radiation, thus generating a larger signal output. On the other hand, drift collection implies a higher spatial resolution due to a lower horizontal charge spread within the active area. Furthermore, the strong electric field produced within the substrate increases the charge collection efficiency (CCE) in two ways. Firstly, the recombination probability decreases noticeably increasing the probability of collection of a generated carrier. Secondly, it increases the radiation hardness of the bulk. In fact, when high energy particles or radiation impinge onto the crystalline lattice of the device their interaction through strong or electromagnetic force can result in atoms being displaced. The displacement leaves behind a vacancy or can effectively lead to an interstitial atom within the lattice. These defects can, through various capture mechanisms, actively generate new energy levels within the silicon band gap trapping the charge carriers and reducing the CCE.

The small collection electrode implies a low capacitance seen by the front-end electronics which improves the SNR. This also implies, differently from HV-CMOS MAPS and HAPS, the possibility of reducing the size of the pixels to pitches below 50 µm.

In most MAPS technologies, it is complicated to fully deplete the sensor due to the voltages in play being too high for the electronics, the substrate resistivity too low for full depletion or because the n-wells including the PMOS transistors compete with the electrode for the charge collection. In ARCADIA, this is not the case due to a few design characteristics developed to increase the high voltage while keeping the CMOS electronics decoupled from the collecting electrodes.

Firstly, the sensor bulk is a lightly n-doped substrate with a small n-type epitaxial layer above it. The low doping implies the possibility, remembering equation 1.2, of adopting a lower voltage to increase the depletion region within the sensor thickness. This is, in general, the reason why sensor substrates have high resistivity. The epi-layer harbors the electronics and the n-type collecting electrodes. On the back, a p+ region is implanted after the completion of the BEOL (Back End Of Line) layers. The choice of adopting a p+ back implant electrode has been designed to start the depletion from the back rather than from the front as illustrated in figure 2.2. In fact, to bias the sensor, the high voltage can be negative and provided from the back implying that the biasing voltages of the electronics and top electrodes are well within the low voltage CMOS standard.

Secondly, the CMOS electronics are harbored within deep p-wells. The adoption of deep p-wells leads to the isolation of the PMOS n-wells and n+ collecting electrodes. Thus, complete CMOS designs are possible within the pixel area.

Figure 2.2: Illustration of the ARCADIA depletion. The p-n junction is at the back, thus the depletion region extends towards the front side as the negative back voltage increases in absolute value.

## 2.1.1 Pixel optimization

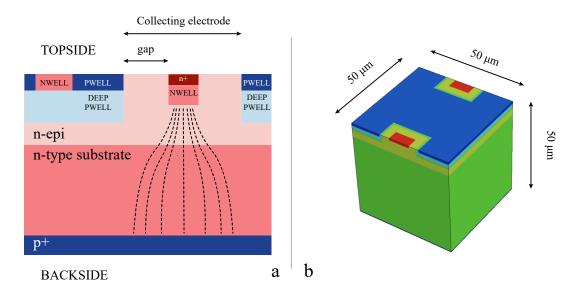

Figure 2.3: Single pixel simulation domain. *left* single pixel parameters illustration. right 3D simulation domain, the cell size is  $50 \times 50 \times 50 \mu m^3$  and the cuts are performed along the collecting electrode center. The color scale represents the doping concentration.

In order to maximize the efficiency of the charge collection and the available area for the CMOS circuitry within a pixel, various TCAD simulations have been done varying sizes and doping parameters.

The simulations parameters do not take into account the n-wells required for the PMOS transistors and are all performed at 300 K.

In figure 2.3, a single pixel and its 3D pixel simulation domain are illustrated. For illustration purposes a 50  $\mu$ m thick domain has been selected, but the final production flavors start from 50 and reach 400  $\mu$ m. For the simulations, the collection electrode is biased at a voltage  $V_{c.e.}=0.8\,V$  this voltage is picked because this way a small portion of the n-well-to-n-epi interface results depleted. In fact, increasing the n-well voltage with respect to the deep p-wells leads to a lower punch-through probability (this effect will be discussed later in the section) and decreases the voltage at which full depletion occurs. This last effect is important to increase the operating region of the sensor as can be seen in figure 2.4. Furthermore, this voltage is near the maximum supply voltage for the CMOS electronics and is, coincidentally, a good biasing voltage for the front-end input PMOS transistor.

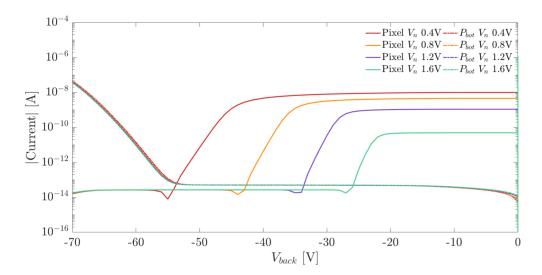

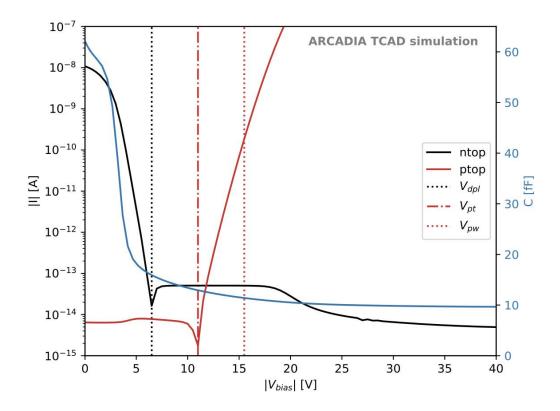

In order to evaluate the electrical characteristics of a single pixel, the results of the simulations focus on capacitance-to-voltage (C-V) and current-to-voltage (I-V) curves. The results of the simulation for the pixel domain in figure 2.3b are plotted

Figure 2.4: Single pixel simulated currents at varying  $V_{c.e.}$ . As the electrode voltage increases the voltage required for full-depletion decreases widening the operating region. Simulation run with a sensor thickness of 100  $\mu$ m.

in figure 2.5. The currents from the top the electrodes are illustrated in black. The depletion voltage,  $V_{\rm dpl}$ , is marked with a vertical black dotted line. The onset of depletion is easily identifiable because the current changes polarity due to the depletion region reaching the top and effectively removing cross pixel currents. The cross pixel current is present mainly due to the fact that the two half electrodes are, in this kind of simulations, biased with a small voltage difference  $\Delta V = 10\,\rm mV$ . Nevertheless, this would not explain the value if not considering that, due to the electrode biasing voltage being positive (standard  $V_{\rm c.e.} = 0.8\,\rm V$ ), the region below the p-wells results un-depleted connecting the two electrodes.

The red curve follows the current flowing through the grounded p-well. Similarly to the n-well current, the current changes polarity, but in this case it is due to the onset of the punch-through. The punch-though voltage,  $V_{\rm p.t.}$ , identifies the value at which the front p-wells and the p<sup>+</sup> back deposition become electrically connected. Once the biasing voltage reaches  $V_{\rm p.t.}$  the current sunk from the p-wells increases exponentially and, if not carefully taken care of, could harm the sensor. Nevertheless, the onset of punch-through is not the limiting factor when depleting the sensor. In fact, the sensor still works beyond  $V_{\rm p.t.}$ , but the currents in play are much higher than normal. Thus, to limit the power consumption to  $0.1\,\rm mWcm^{-2}$ ,  $V_{\rm pw}$  is marked as the ultimate voltage adoptable for normal usage.

Lastly, the blue curve indicates the capacitance of the single pixel at varying back bias voltage. The curve is simulated in AC (Alternated Current) with a frequency of 10 kHz. As the depletion region reaches the top side a sharp capacitance

decrease is noticeable. Nevertheless, the minimum capacitance is only reached at higher voltages due to the lightly doped epi-layer, which is more difficult to deplete compared to the high resistivity substrate.

Figure 2.5: Single pixel simulated current and capacitance curves [56]. The *black* curve shows the pixel current. Here the full depletion voltage is marked with a vertical dotted black line. The *red* curve shows the current passing through the p-well. The punch-through voltage and the voltage where the maximum available power is dissipated are marked with, respectively, a dot-dash red line and a dotted red line. The *blue* curve represents the capacitance of the electrode with varying voltage.

## 2.1.2 Backside processing

Following the BEOL step on the front side of the sensor, the back side must be processed. The layout view of a test diode and an illustration of the back structures are shown in figure 2.6. In order to bias the back side at the high voltages required for full depletion of the sensor, a few steps must be taken care of.

Firstly, the backside p<sup>+</sup> junction must be wide enough to cover the whole active

Figure 2.6: Backside guard ring layout of a diode test structure with GRN = 10 and a vertical cut of the test structure.

area. This is done to ensure that the electric field lines are identical in all the pixels in the matrix. Furthermore, a metallization is required to bias the whole junction with low resistivity to reduce voltage drops throughout the electrode. Unfortunately, if the whole surface is covered in metal the sensor would become blind to light. Thus, a window is designed in order to only have a metallic frame for the biasing of the back electrode.

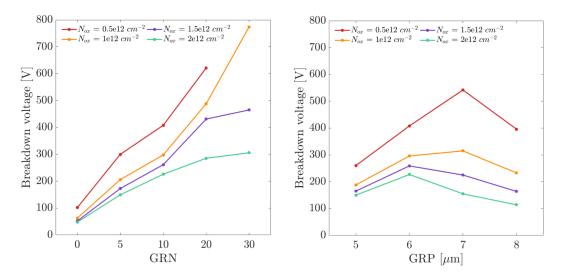

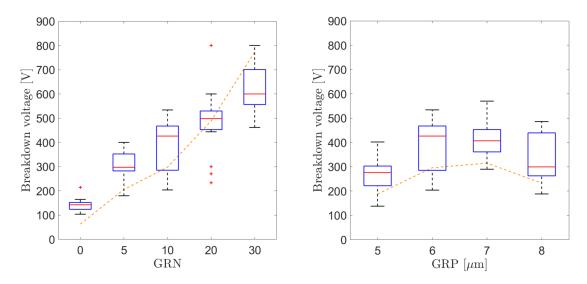

Secondly, a set of guard rings around the p<sup>+</sup> electrode is necessary. In fact, it is well known that the performance and stability of a silicon sensor can be improved by adopting guard ring structures around the electrodes [13]. In particular, various studies have been done via TCAD simulations to select the best performing geometries for these termination structures.

Clearly, in the simulations the objective is to increase the operating region which is limited by the full-depletion voltage and the onset of punch-through and breakdown of the p<sup>+</sup>-n diode.

The customization of the guard rings leads to a variation of the punch-through voltage and is, thus, fundamental to increase the sensor's performance.

The guard rings share the p+ doping with the p+ junction and have been simulated varying number and geometrical parameters. Another important factor is the number of surface traps at the backside interface,  $N_{ox}$ . These traps are generated during the manufacturing process due to the silicon to passivation interface creation technique. In particular, due to the low temperature oxide deposition, in place of thermal oxidation, a varying number of traps at the interface is produced. Thus,

the simulations also vary the trap density within the silicon near the guard rings.

As can be seen in figure 2.7, the breakdown voltage, defined as the voltage at which the backside current exceeds the value of  $1\,\mu\text{A}$ , increases with number of guard rings. This simulation has been evaluated on a domain similar to that in figure 2.3b, but with a 100  $\mu$ m thickness. On the right hand side of figure 2.7, the pitch optimum value results to be between 6 and  $7\,\mu$ m.

The adoption of a current threshold for the definition of the breakdown voltage is a conservative method to identify the breakdown voltage of devices where an abrupt variation of the current is not present [24].

Figure 2.7: Study of the variation of the breakdown voltage with varying number of traps and on the *left* number of guard rings (GRN) and on the *right* pitch between the guard rings (GRP). The simulations have been done on a 100 µm thick domain. More information in [24].

### 2.1.3 Pixel radiation tolerance

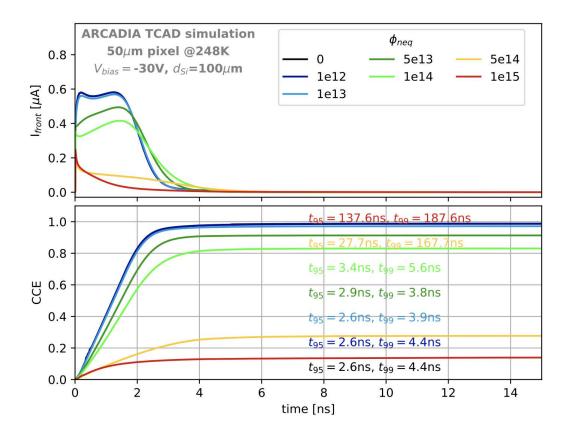

In order to predict the radiation tolerance of the ARCADIA sensors a set of simulations have been done varying the sensor geometry a doping profiles.

In particular, ionizing and non-ionizing radiation can damage various parts of the sensor both on the surface and in the bulk. On the surface, the damage, due to ionizing radiation, takes form of oxide charge build-up at the interface between the Si and Si<sub>2</sub> surfaces. On the other hand, considering also the device bulk, impinging non-ionizing radiation can create silicon crystal lattice defects which actively create new energy levels within the semiconductor band gap. These extra energy levels act as traps within the bulk and lead to a variation of the electrical properties of the

device by changing the depletion voltage (due to the effective doping concentration variation) and the leakage current of the sensor.

In order to predict the sensor damage in the most realistic manner as possible the new Perugia model has been adopted [54, 63].

An example of the effects of radiation damage is shown in figure 2.8. Here, the variation of the signal from a single pixel is shown. The results show a good response to incoming radiation up to  $10^14$  neq/cm<sup>2</sup>. Furthermore, the CCE timings are shown in the bottom plot showing the time required for integrating 95% and 99% of the total generated charge.

Figure 2.8: Pixel current radiation damage effects [56]. On *top* the currents simulated in a single  $50 \times 50 \,\mu\text{m}^2$  pixel at a temeprature of 248 K. At the *bottom* the total collection times are shown. The simulated fluxes range from 0 to  $10^{15} \, \text{neq/cm}^2$ .

## 2.2 ARCADIA test structures

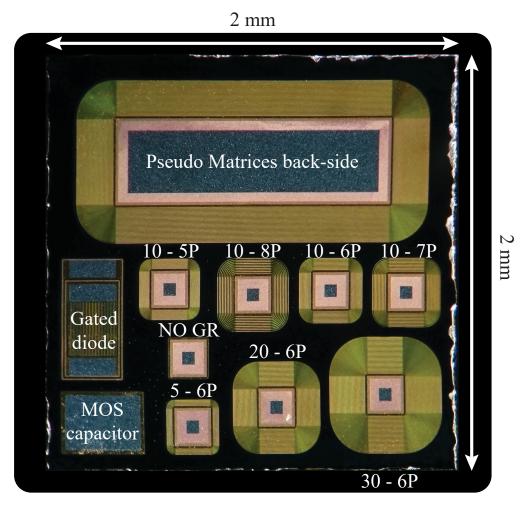

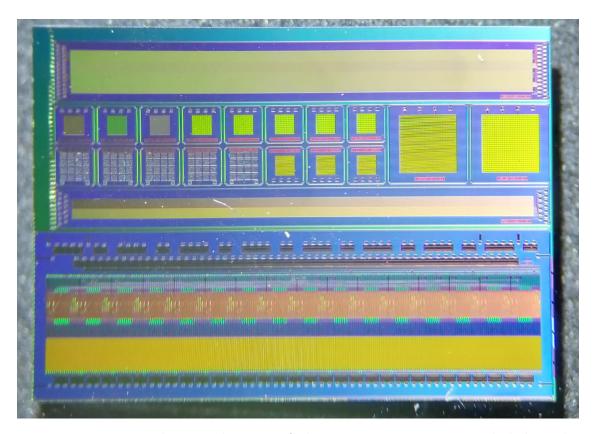

In order to test the concept and functionality of the simulated sensors, a set of test structures has been designed and produced. At the end of the section. in figure 2.14, a photograph showing part of the produced test structures can be found. In chapter 3 the most significant results of the test structures described in this section will be shown.

## 2.2.1 Passive Test Structures

In the first engineering run, within the SEED project, a set of passive test structures has been produced. The test structures have been fitted in a  $2 \times 2 \,\mathrm{mm^2}$  area chip and designed in 110 nm CIS process. The structures were laid out with simplicity in mind making the test procedures as easy as possible. Nevertheless, these structures have been produced with the same double side process adopted for the fully depleted MAPS. This implies that the test chip has different testable structures on the two sides. The scope of these structures is to study the sensor properties like depletion, leakage, breakdown and radiation tolerance.

The passive structures include:

- Set of 8 diodes;

- A gated diode;

- MOS capacitance;

- Pseudo-matrices.

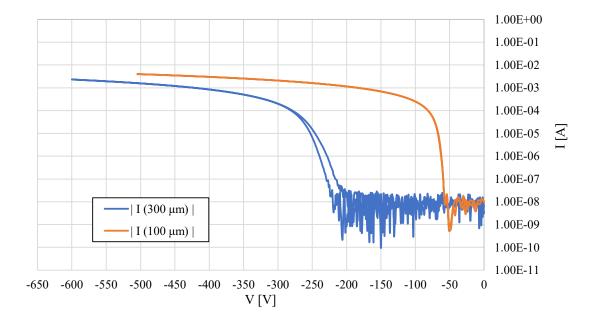

The chips have been produced in 3 different thicknesses:  $100\,\mu\text{m}$ ,  $300\,\mu\text{m}$  and  $400\,\mu\text{m}$ . Each thickness is expected, following the simulation results, to have different operating regions and, obviously, different full-depletion voltages. The diodes and the MOS capacitor are testable from the backside which is visible in figure 2.9, while the pseudo-matrices must be tested from the front as will be explained in the next subsections.

Figure 2.9: Photograph of the back side of the produced test structures. The pseudo-matrices backside  $p^+$  implant is visible on the top, while on the bottom left the MOS capacitor and gated diode are shown. A large area of the chip is dedicated to the study of the  $p^+$ -n-substrate diodes and the number of guard rings adopted. The first number indicates the GR number, while the second indicates the pitch in  $\mu m$ .

#### Test diodes

Within the test structures chip there are 8 diodes. A layout example of the backside of the diodes is on the left in figure 2.6. The number of  $p^+$  guard rings varies from 0 to 30, while the pitch varies from 5 to 8  $\mu$ m. Since the depletion volume starts from the back  $p^+$ -n-sub junction it's extension is not influenced by the top p-wells. Thus, the diodes exhibit a set of collecting  $n^+$  electrodes on the

top which can all be biased at the same time in order to study the variability of their characteristics with varying number of guard rings or their pitch.

The area of each diode is  $200 \times 200 \,\mu\text{m}^2$ . The biasing of each one can be done through a metallization frame surrounding the p<sup>+</sup> implant. As expected, and simulated in figure 2.7, an increase in number of guard rings and a small pitch between them increase the stability of the structures leading to a higher breakdown voltage. Nevertheless, when increasing the number of guard rings also the area required for their proper design increases decreasing that available for the sensor back electrode. For this reason, a trade-off between the area for the guard rings and the minimum acceptable breakdown voltage has to be weighed.

The backside structures and the designed test diodes are photographed in figure 2.9. The diode performance can be evaluated by studying their I-V curves.

On the chip, two study sets can be identified. The first set of diodes adopts a pitch of  $6\,\mu m$  with three different GRN = 5, 20 and 30 guard rings. The second set includes 4 diodes each with 10 rings, but varying pitch of 5, 6, 7 and 8  $\mu m$ . Lastly, a diode without guard rings and a gated diode have been included. The latter can be tested to study the surface generation velocity, while, the former, shows the early breakdown effect due to no GR adoption.

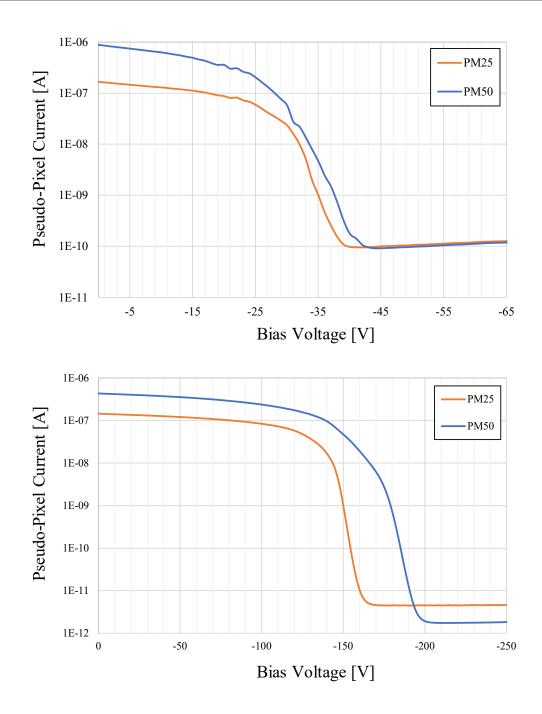

#### Pseudo-matrices

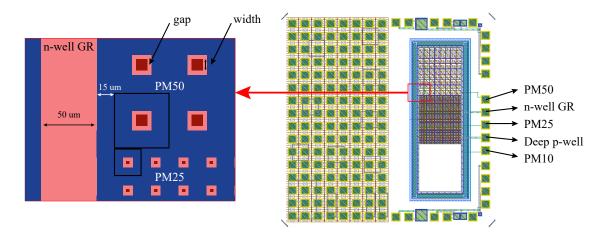

Figure 2.10: Test structures layout. *left* An illustration of the area between PM50 and PM25 is zoomed into. *right* The layout of the front-side of the test structures. All the yellow squares represent the metal pads for external contact. On the left side of the chip an  $8 \times 16$  array of pads is found which can be used to bias the collecting electrodes above the test structure's diodes.

A pseudo-matrix (PM) is a set of passive collecting electrodes connected in parallel. In particular, the chip includes three sets of electrode arrays with varying electrode pitches. The pitches chosen for production are  $50\,\mu\text{m}$ ,  $25\,\mu\text{m}$  and  $10\,\mu\text{m}$ . The matrices are arranged in a set of  $8\times 9$ ,  $16\times 18$  and  $40\times 45$  pixels. The three arrays are surrounded by a single  $50\,\mu\text{m}$  wide n-well guard ring on the front side in order to collect stray carriers generated outside the active volume. The GR-to-pixel-border distance is  $15\,\mu\text{m}$  and it includes both a p-well and a deep p-well. On the back side of the PMs a structure similar to that seen in the diode is present. In fact, a p<sup>+</sup> implant covering the whole area of the arrays framed by a metallic plate used to bias the diode has been designed on the back. In order to stabilize the sensor depletion, a set of 10 floating guard rings has been implemented surrounding the back side p<sup>+</sup> electrode.

Differently from the diodes, these test structures must be tested from the front side of the chip. In fact, as can be seen in figure 2.10 *right* there are 5 dedicated pads designed for the biasing of the pseudo-matrices, p-wells and the n-well guard ring.

| Pitch [µm]          | 50 | 25 | 10   |

|---------------------|----|----|------|

| Gap [μm]            | 5  | 5  | 3.75 |

| Electrode size [µm] | 10 | 5  | 2.5  |

Table 2.1: Pseudo-matrices electrode geometries.

### 2.2.2 Active Test Structures

Within the ARCADIA engineering run wafers, also a set of active test structures are present. In particular, the wafers, with an 8-inch diameter, include 3 important test structures:

- The ARCADIA main demonstrator;

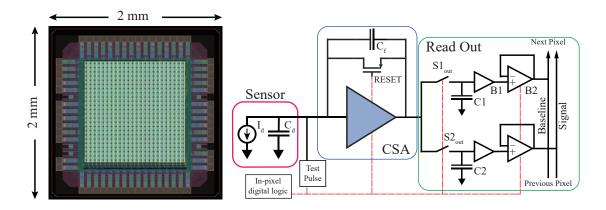

- A process evaluation FD-MAPS named MATISSE;

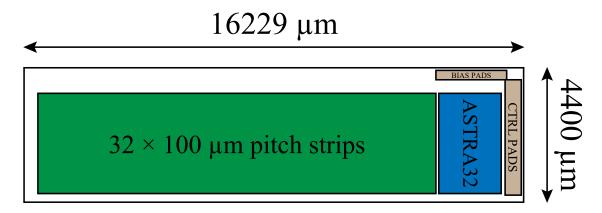

- A fully depleted monolithic strip detector.

### **ARCADIA Main Demonstrator**

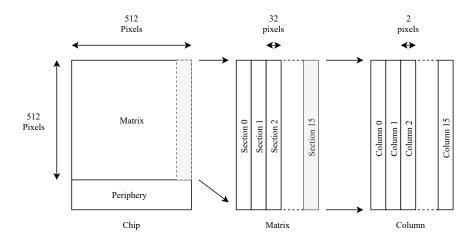

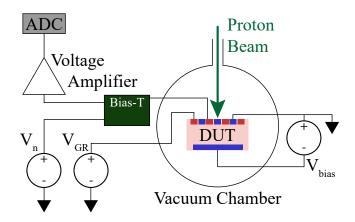

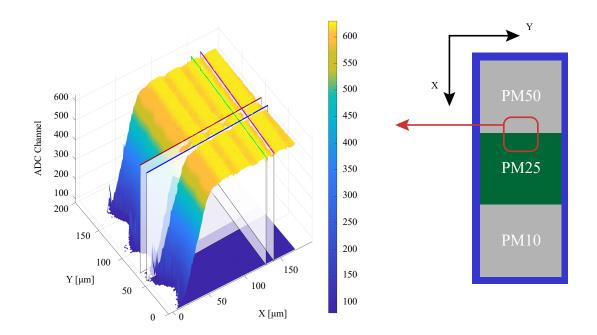

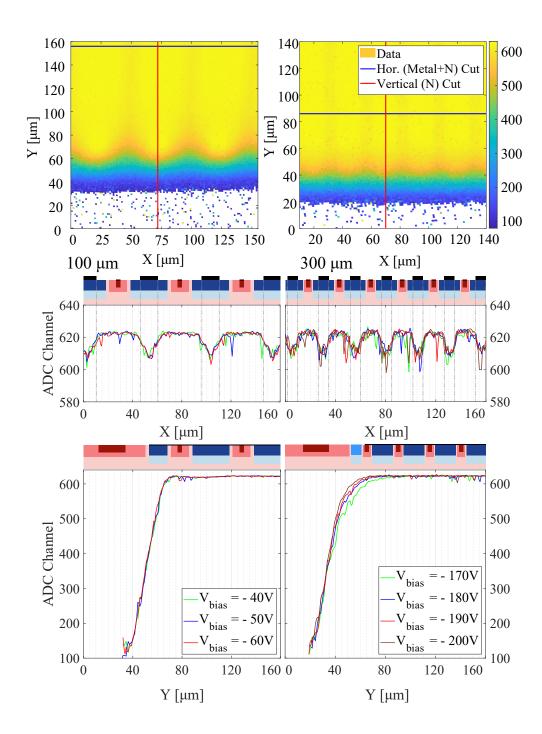

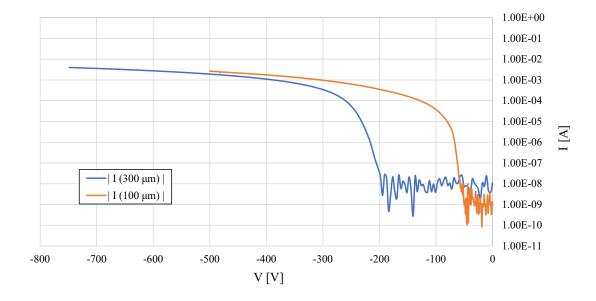

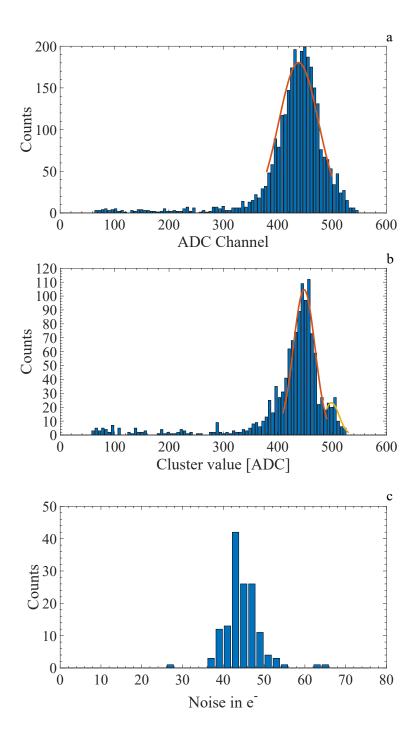

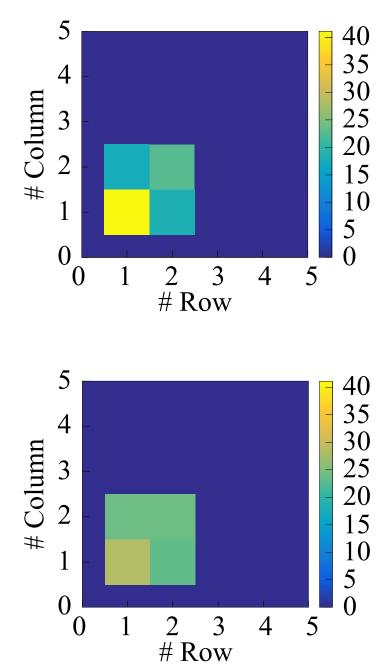

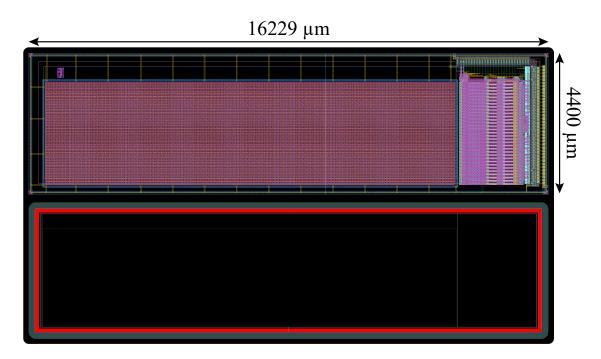

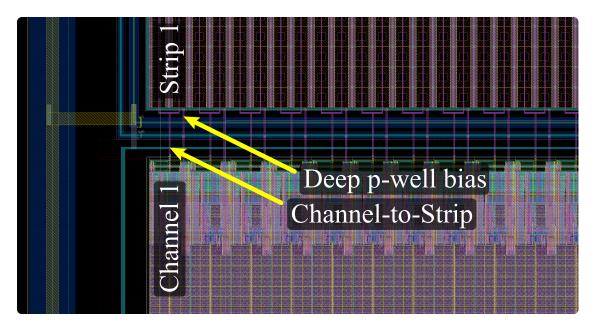

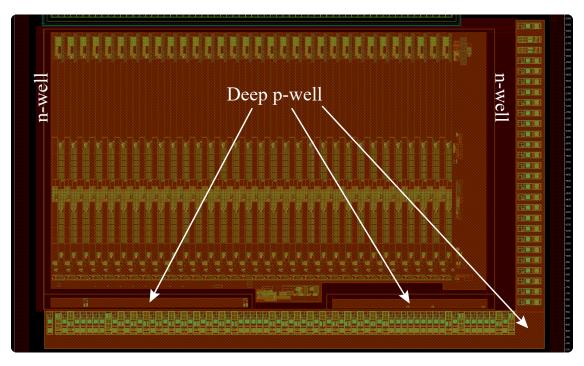

Figure 2.11: Illustration of the ARCADIA Main Demonstrator pixel matrix organization.