# POLITECNICO DI TORINO Repository ISTITUZIONALE

## The IEEE EPS Packaging Benchmark Suite

Original

The IEEE EPS Packaging Benchmark Suite / Guo, Fei; Aygun, Kemal; Becker, W. Dale; Grivet Talocia, Stefano; Hejase, Jose A.; Wong, Wui-Weng; Zhou, Tingdong; Barnes, Heidi; Peng, Zhen; Pelger, Alexander; Sahouli, Mohamed; Schutt-Aine, Jose; Ling, Feng; Griese, Elmar; Paladhi, Pavel Roy; Sharma, Rohit; Pham, Nam; Winkel, Thomas-Michael; Fledell, Evan; Hill, Michael J.; Silva, Benjamin; Hu, Kaisheng; Aronsson, Jonatan; Liu, Chang; Jeong, Yiru; Yilmaz, Ali E.. - ELETTRONICO. - (2021), pp. 1-4. ((Intervento presentato al convegno 2021 IEEE 30th Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS) tenutosi a Austin, TX, USA nel 17-20 Oct. 2021 [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100] [100]

Publisher: IEEE

Published DOI:10.1109/EPEPS51341.2021.9609142

Terms of use: openAccess

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright

IEEE postprint/Author's Accepted Manuscript

©2021 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

# The IEEE EPS Packaging Benchmark Suite

Fei Guo Advanced Micro Devices Markham, Ontario, Canada fei.guo@amd.com

> Jose A. Hejase Nvidia Austin, TX, USA jhejase@nvidia.com

Zhen Peng Univ. Illinois Urbana-Champagin Urbana, IL, USA <u>zvpeng@illinois.edu</u>

> Feng Ling Xpeedic Bellevue, WA, USA feng.ling@xpeedic.com

Nam Pham IBM Poughkeepsie, NY, USA <u>npham@us.ibm.com</u>

Benjamin Silva Intel Corporation Chandler, AZ, USA benjamin.p.silva@intel.com

Yiru Jeong Altair Seongnam, South Korea <u>yiruj@altair.com</u> Kemal Aygün Intel Corporation Chandler, AZ, USA kemal.aygun@intel.com

Wui-Weng Wong Advanced Micro Devices Singapore wui-weng.wong@amd.com

> Alexander Pelger IBM Germany apelger@de.ibm.com

Elmar Griese University of Siegen Germany elmar.griese@uni-siegen.de

Thomas-Michael Winkel IBM Germany winkel@de.ibm.com

> Kaisheng Hu Ciena Canada <u>khu@ciena.com</u>

Ali E. Yilmaz University of Texas at Austin Austin, TX, USA <u>ayilmaz@mail.utexas.edu</u>

*Abstract*—The current state of the Packaging Benchmark Suite being developed by the IEEE EPS technical committee on electrical design, modeling, and simulation (TC-EDMS) is reviewed. The history and goals of the effort to establish the Suite, the key requirements from benchmarks that can support advances in simulation tools and computational methods, and the process being followed by the volunteer committee formed by the authors to produce the Suite are described. The first three benchmarks in the Suite and the steps that were taken to elevate them from potential candidates to effective benchmarks are presented.

Keywords—benchmarking, scientific method, technical collaboration, validation, verification, computer-aided design

#### I. INTRODUCTION

The remarkable advances in computational science and engineering (CSE) fueled in part by the persistent increases in the capabilities of computer hardware and software have produced a large and expanding set of computational methods to quantify the electrical performance of electronic packages. While various commercial, academic, freeware, or proprietary simulation tools that rely on these methods are currently being developed, refined, marketed, and applied in order to support the electromagnetic analysis and design of packages, the expectations from these simulation tools continue to escalate

W. Dale Becker IBM Poughkeepsie, NY, USA wbecker@us.ibm.com

> Tingdong Zhou NXP Canada

tingdong.zhou@nxp.com

Mohamed Sahouli University of Western Ontario London, ON, Canada <u>msahouli@uwo.ca</u>

Pavel Roy Paladhi IBM Austin, TX, USA <u>pavel.roy.paladhi@ibm.com</u>

Evan Fledell Intel Corporation Hillsboro, OR, USA evan.m.fledell@intel.com

Jonatan Aronsson CEM Works Canada aronsson@cemworks.com Stefano Grivet-Talocia Politecnico di Torino Torino, Italy stefano.grivet@polito.it

Heidi Barnes Keysight Technologies Santa Rosa, CA, USA <u>heidi\_barnes@keysight.com</u>

Jose Schutt-Aine Univ. Illinois Urbana-Champaign Urbana, IL, USA jesa@illinois.edu

Rohit Sharma Indian Institute of Tech. Ropar Rupnagar, Punjab, India <u>rohit@iitrpr.ac.in</u>

Michael J. Hill Intel Corporation Chandler, AZ, USA michael.j.hill@intel.com

Chang Liu Cadence Design Systems San Jose, CA, USA <u>changliu@cadence.com</u>

partly because the requirements from and complexity of electronic packages continue to increase. Recognizing

- the importance of simulation tools and computational methods to the development of electronic packages,

- the necessity of verification, validation, and objective comparison to the proper use and further advancement of these tools and methods,

- the obstacles that potential and actual users, developers, and researchers of such tools and methods encounter, and

- the dearth of benchmarks to evaluate the performance of existing and novel tools and methods,

the IEEE Electrical Packaging Society (EPS) technical committee on electrical design, modeling, and simulation (TC-EDMS) initiated a joint industrial-academic effort in late 2018 to assemble a set of modern benchmarks. This article reviews the goals of this effort, the progress made in the last three years, and the current state of the Packaging Benchmark Suite.

#### II. SCIENTIFIC BENCHMARKS AND BENCHMARKING

The Merriam-Webster dictionary defines *benchmark* as "a standardized problem or test that serves as a basis for evaluation

or comparison". In science and engineering, *benchmarking* something of interest is to subject it to a process that invites the participants to collect specific data (using benchmarks), identify similarities and differences relative to reference data, make objective comparisons, and deduce facts about the thing of interest. This process has all the hallmarks of the scientific method and requires the release of sufficient information to (present and future) scientists and engineers to independently and empirically corroborate, reproduce, vary, replicate, or repeat it [1], ultimately enabling them to verify or falsify the deductions and claims of others. Benchmarks and the benchmarking they enable "have a lasting positive impact on a scientific discipline" when they "emerge through a synergistic process of technical knowledge and social consensus proceeding in tandem" [2].

#### A. Physical Benchmarks for CSE

Physical benchmarks serve numerous purposes in measurement campaigns; they are used to, e.g., calibrate equipment, train personnel, verify protocols, or quantify measurement uncertainties. Physical benchmarks—*together with their digital models/ representations*—are used in CSE to also compare different theoretical/computational methods (particularly in terms of their predictive power, accuracy, and cost), reveal their strengths and weaknesses, and provide information for their appropriate use and further development. To be utilized for these purposes, benchmarks must have certain features [3]:

- 1. A carefully selected set. The selected benchmarks should be relevant to and represent a broader set of important problems in the field. They should span difficulty levels [3], e.g., ranging from basic to challenging, from tolerant to highly sensitive to small variations/errors in manufacturing, measurement, and simulation. They should be logically organized, evolving with technology, and version controlled.

- 2. Precise and highly reproducible physical definition. A few drawings, pictures, or equations can be used to specify basic benchmarks, but reproducing more complex benchmarks requires geometrical layouts, stackups, and material properties to be specified via digital models, computer-aided design data, or meshes [4].

- 3. Clearly defined quantities of interest with reliable reference data. Frequency-domain network parameters or time-domain waveforms are common quantities of interest in packaging that require ports, reference impedances, or pulse shapes to be clearly defined. Reliable references include data from meticulous simulations and measurements that are accurate and strongly correlated.

- 4. *Neutral to simulation tools and computational methods.* The benchmarks should not have any *a priori* bias toward or against particular tools or methods, e.g., they should not use proprietary file formats that only certain tools can process.

- 5. *Broad availability and easy access*. The barriers to the use of the benchmarks should be minimized to encourage their use by beginners as well as experts.

Compared to typical case studies used in publications to test simulation tools and computational methods, benchmarks must include significantly more information and clear a higher bar of precision, reliability, and independent reproducibility.

#### III. THE PACKAGING BENCHMARKS COMMITTEE

Section II highlighted the importance of physical benchmarks and key features needed to maximize their utility for CSE. This Section describes the steps the authors took to produce such benchmarks in the IEEE EPS Packaging Benchmark Suite.

#### A. Formation and Composition

Throughout 2019, about 15 experts in industry and academia led by Drs. K. Aygün and W. D. Becker held monthly virtual meetings to discuss the effort initiated by IEEE EPS TC-EDMS, its scope, challenges, and potential approaches to produce a set of modern benchmarks. These meetings culminated in a call to action in the 2019 IEEE EPEPS conference, the formation of the Packaging Benchmarks Committee under the IEEE EPS TC-EDMS umbrella, and the identification of several potential benchmark candidates. Drs. F. Guo and A. E. Yilmaz were elected as inaugural co-chairs of the Committee for two years starting in 2020.

#### B. Mission

The mission of the Packaging Benchmarks Committee is to produce a Packaging Benchmark Suite that will encourage research & development by providing information about the electromagnetic, electrical, and circuit modeling and simulation problems encountered and the state-of-the-art solution methods used when analyzing and designing electronic packages.

#### C. Committee Structure

In Jan. 2020, the co-chairs invited fifty experts with interest and expertise in packaging, EDMS, CSE, and benchmarking to serve in the newly formed committee for a two-year term. Volunteers were selected initially to serve as technical reviewers, aiming for an enthusiastic, productive, and balanced committee. In particular, the selectees included both developers and users of simulation tools in academia and industry. Starting in Mar. 2020, the committee held bi-weekly virtual meetings. In 2020, as the tasks grew, more volunteers joined the committee (three ended their terms early). After a new invitation in Jan. 2021, additional volunteers were selected as new members. The Committee currently consists of 23 members in 3 subcommittees:

- *Technical review* (chaired by Dr. A. E. Yilmaz): 16 voting reviewers critically evaluate benchmark candidates, judge if/ why a candidate should be part of the Suite, identify missing necessary/desirable technical features, help construct data/ documents to support benchmarking, and provide constructive criticism to improve candidate problems.

- *Electrical characterization and measurement* (chaired by H. Barnes): 7 sub-committee members help to identify best practices for measurement characterization of benchmark candidates and methods for assessing errors and uncertainties due to measurement setups (e.g., deembedding and calibration in high-frequency measurements).

- *Website support* (chaired by Dr. J. Schutt-Aine): 3 subcommittee members release new benchmarks to the public [5], maintain the database and website, ensure the Suite is accessible to qualified users, and keep a record of website users who have access to the Suite.

#### D. From Candidate Problem to Benchmark

To evaluate and improve candidate problems, the volunteers adopted an iterative review process that gradually builds consensus. During this process, the committee members work together with the submitters to ensure the quality of the resulting benchmark.

Step 1: Submitters prepare materials for a candidate problem and present these to the Packaging Benchmarks Committee in virtual meetings to gather informal feedback. During this step, the electrical characterization and measurement sub-committee may be tasked with engaging the submitters further and providing technical support, in particular to help optimize measurement setups and reduce uncertainty and errors in measured data. The submitters then submit a packet of technical material—e.g., a digital model, measurement/simulation data, text, figures, tables—and legal approvals that ensure intellectual property rights are respected when the packet is released to the reviewers and potentially to the public as part of the Suite.

Step 2: The submitted packet is formally evaluated by the technical reviewers who provide individual anonymous written comments. These comments are discussed in a regular committee meeting also attended by the submitters. Then, a new time window is opened to the submitters, who respond with written comments, update the packet, and initiate a new evaluation. At each iteration, the reviewers are polled anonymously: their votes are set to "no, the candidate does not yet qualify" by default. The iterations continue until a supermajority of the reviewers vote "yes, the candidate qualifies as a benchmark".

*Step 3:* The approved candidate is added to the Suite, labeled as version 1.0, and published online [5]. As the benchmarks and the technology to share them evolve, various updates to the Suite, modifying the benchmarks' versions, are likely.

A private online repository to view the submitted packets and edit the written feedback has been critical to committee productivity. The committee used a Box repository of the University of Texas at Austin for its activities in 2020-2021.

#### IV. STATE OF THE SUITE

As of Aug. 2021, the Packaging Benchmarks Committee elevated 3 benchmarks into the Suite (Fig. 1); 3 other benchmark candidates are currently in various stages of development.

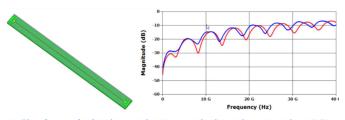

#### A. Benchmark I: Single-ended Microstrip Transmission Line

Benchmark I contains measurement and representative modeling data for a microstrip package transmission line test structure. Over the last decade, this particular problem has been shared with various research groups as a test example; e.g., see [6],[7]. This is a *basic* benchmark that can serve as a suitable entry problem for CSE researchers new to the area of electronic packaging. Furthermore, even though the physical structure is relatively simple by today's EDMS standards, i.e., "a single package transmission line", an accurate electromagnetic analysis of it requires tackling some of the fundamental ingredients common to many other packaging problems. These include multiple lossy dielectric layers with different electrical properties, metal layers with finite thicknesses and rough surfaces, and vias. As a result, the Committee decided that this

I. Single-ended Microstrip Transmission Line (version 1.0)

Single-ended Microstrip Transmission Line Benchmark Problem

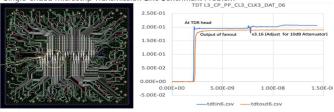

### II. Plasma Package (version 1.0)

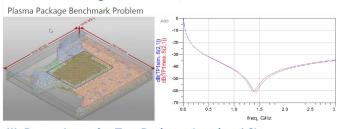

III. Power-Integrity Test Package (version 1.0) Package Power Integrity Benchmarking Problem

Fig. 1: The Packaging Benchmark Suite includes 3 benchmarks that are available online [5] as of Aug. 2021.

test structure would make a good first benchmark for the Packaging Benchmark Suite. One somewhat inevitable shortcoming of using an older example is the inability to collect additional data and perform additional experiments as the physical measurement parts are no longer available. Some of the recent EDMS research has focused on systematic measurement and modeling uncertainty quantification to improve the overall measurement-to-modeling correlation process [8]. This, together with the frequency range of interest (currently limited to 40 GHz), are two potential areas of improvement that can be addressed by a future benchmark submission.

#### B. Benchmark II: Plasma Package

Plasma is the name given to an eight-metal-layer laminate substrate in a so-called 3-2-3 construction which has three buildup layers on top and bottom of a two-metal-layer core. Plasma is a fully wired design that was originally offered as a challenge problem for an EPEP 2006 special session [9] because the design data volume was beyond the capability of computer resources available at that time. Benchmark II provides the full Plasma design file and identifies four traces for extraction and time-domain simulation that includes the full path of pads, vias, traces, and the reference return paths from the pad on the top for die attach to the die on the bottom for BGA attach. The measured waveforms of reflection and transmission delay of a trace are provided along with the near-end and far-end crosstalk observed from three adjacent traces. This gives a benchmark problem for modeling these quantities in an actual design.

#### C. Benchmark III: Power-Integrity Test Package

Benchmark III is about impedance characterization and modeling of a power plane VDD/VSS test structure in a flip chip package. Transfer impedance converted from S-parameters collected using conventional 2-port shunt through characterization is introduced on this test structure with thousands of power and ground bumps. Qualitatively good correlation between simulation and measurement data has sufficiently validated the models developed using realistic dimensions from cross-sectional analysis along with the removal of residual measurement parasitics.

#### V. ONGOING ACTIVITES

The IEEE EPS TC-EDMS Packaging Benchmark Suite is currently available online [5]. As of Aug. 2021, 41 users have registered to download the benchmarks. Their stated purposes include evaluation of industry simulation tools, dissertation research on parallel computational electromagnetics methods, and training machine-learning models.

The Packaging Benchmarks Committee continues to meet regularly, evaluate candidate problems, and give presentations on the effort to develop modern benchmarks at various conferences and seminars. Because the Packaging Benchmark Suite should evolve to remain relevant to the latest problems and solution approaches in the field, the committee members are actively seeking new submissions.

#### A. Recommendations for Future Benchmark Candidates

The existing benchmarks in the Suite provide a foundation for judging any new candidate problems. Potential submitters and future reviewers are expected to study these benchmarks, identify important packaging problems that are not covered by them, evaluate the candidate problem's overlap with the existing benchmarks, and justify how a new benchmark can add value to the Suite.

Potential submitters are also advised to download and study the existing benchmarks [5] in order to understand the information that will be requested from them during the technical review. These include:

- several pages of documentation that describes the electronic package and details all measurements and simulations performed to collect and validate the reference data being made available,

- pictures showing the stack-up, top-down view, and 3D view of the package layout and tables listing layer thicknesses, other key dimensions, and electromagnetic material properties—this data should ideally be submitted for both the digital package models and their physical realizations; e.g., using electromagnetic material and cross-sectional geometry measurements,

- plots of measured and simulated network parameters and/or time-domain waveforms and the corresponding data in standard file formats (e.g., SnP, CSV),

- license statements,

- digital model of the package in a standard file format (e.g., SAB, ODB++).

#### VI. CONCLUSION AND FUTURE WORK

The joint industrial-academic effort initiated by the IEEE EPS TC-EDMS has attracted a large number of expert volunteers, who have formed the Packaging Benchmarks Committee and collaborated over the last three years to establish and publicly release a modern Packaging Benchmark Suite. The committee continues to develop the Suite, which currently consists of 3 publicly available benchmarks [5].

The Packaging Benchmarks Committee also established processes to review candidate problems, help submitters improve the packet of technical materials, and publicly release the resulting benchmarks. These processes would have been infeasible until very recently, but thanks to advances in version control, virtual meeting, and online publication tools that make it significantly easier to visualize, share, and preserve large and complex data, the effort started yielding results in a reasonable time frame. The adopted processes and the overall effort to establish the Packaging Benchmark Suite can inform efforts to develop other scientific benchmarks.

Various scientists and engineers, including some of the committee members, have already started using the benchmarks in the Suite to evaluate existing simulation tools and support the development of novel computational methods for electronic packaging. The Packaging Benchmark Suite is expected to advance scientific benchmarking of simulation tools and computational methods and ultimately lead to advances in CSE and EDMS of electronic packages. To support and reflect these advances, the Suite should continue to be maintained, updated, and enriched with new benchmarks.

#### REFERENCES

- D. G. Feitelson, "From repeatability to reproducibility and corroboration," ACM SIGOPS Oper. Sys. Rev., vol. 49, no. 1, pp. 3-11, Jan. 2015.

- [2] S. E. Sim, S. Easterbrook, and R. C. Holt, "Using benchmarking to advance research: A challenge to software engineering," in *Proc. IEEE* 25<sup>th</sup> Int. Conf. Software Eng., pp. 74-83, May 2003.

- [3] J. W. Massey, C. Liu, and A. E. Yilmaz, "Benchmarking to close the credibility gap: A computational bioEM benchmark suite," in *Proc. URSI Int. Symp. Electromagn. Theory (EMTS)*, Aug. 2016.

- [4] J. T. Kelley *et al.*, "Adding a reproducible airplane model to the Austin RCS benchmark suite," in *Proc. ACES Symp.*, July 2020.

- [5] IEEE EPS TC-EDMS Packaging Benchmark Suite, 2021. [Online]. Available: <u>https://packaging-benchmarks.org</u>

- [6] C. Liu, K. Aygün, and A. E. Yılmaz, "A parallel FFT-accelerated layeredmedium integral equation solver for electronic packages," *Int. J. Num. Model.: Electron. Net., Devices Fields*, vol. 33, no. 2, Mar./Apr. 2020.

- [7] B. Zhou, H. Liu, and D. Jiao, "A direct finite element solver of linear complexity for large-scale 3-d circuit extraction in multiple dielectrics," in *Proc. 50th Design Automation Conf. (DAC)*, June 2013.

- [8] C. S. Geyik *et al.*, "Measurement uncertainty propagation in the validation of high-speed interconnects," in *Proc. IEEE EPEPS*, Oct. 2020.

- [9] Special Session, 2006 IEEE Electrical Performance of Electronic Packaging, 2006, pp. 286-310.