POLITECNICO DI TORINO

Repository ISTITUZIONALE

Integrated cryogenic electronics to readout large areas SiPMs

*Original*

Integrated cryogenic electronics to readout large areas SiPMs / MARTINEZ ROJAS, ALEJANDRO DAVID. - (2021 Jun 09), pp. 1-155.

*Availability:*

This version is available at: 11583/2907032 since: 2021-06-15T17:02:19Z

*Publisher:*

Politecnico di Torino

*Published*

DOI:

*Terms of use:*

Altro tipo di accesso

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

*Publisher copyright*

(Article begins on next page)

Doctoral Dissertation

Doctoral Program in Electrical, electronics and communications Engineering (33<sup>th</sup> cycle)

# Integrated cryogenic electronics to readout large areas SiPMs

DarkSide 20K Experiment

**Alejandro D. Martinez Rojas**

\* \* \* \* \*

## Supervisor

Prof. Angelo Rivetti , Supervisor

### Doctoral Examination Committee:

Prof. Thanushan Kugathasan , Referee, University of Trento

Prof. Lucio Pancheri, Referee, CERN

Politecnico di Torino

March, 2021

This thesis is licensed under a Creative Commons License, Attribution - Noncommercial-NoDerivative Works 4.0 International: see [www.creativecommons.org](http://www.creativecommons.org). The text may be reproduced for non-commercial purposes, provided that credit is given to the original author.

I hereby declare that, the contents and organisation of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.

.....

Alejandro D. Martinez Rojas

Turin, March, 2021

# Summary

The current underground astroparticle experiments of looking for rare events, such as Deep Underground Neutrino and DarkSide-20K, are implementing structures to work in cryogenic temperatures. Cryogenic structures require a robust system capable of readout the generated photo-electrons (PEs) in a cryogenic environment.

In the astroparticle experiments, the electronics readout is mainly structured by a front-end circuit. Hitherto, most readout electronics consist of discrete electronics for general-purpose. Discrete electronics must implement additional filters to achieve the desired bandwidth. Furthermore, it requires an off-line digital signal processing to supply the minimum requirement of signal to noise ratio (SNR). Otherwise, the noise level makes the photo-electron reading a complex process due to the large detector capacitor ( $> 10 \text{ nF}$ )

This research activity deals with the modeling and design aspects of the integrated cryogenic electronics in CMOS technology for fast amplification. An integrated electronics might achieves better performance in terms of SNR and cost. The SNR assumption is done due to the improvement of capacitive matching between sensor and electronic, something hard to realize in general-purpose electronics. Also, the integrated electronics becomes a much cheaper option for mass production than discrete electronics. Furthermore, thank to the robust structure of CMOS technology, front-end electronics can be designed with a lifetime longer than 20 years. It is enough time for an experiment such as an underground astroparticle.

The study of front-end electronics in CMOS technology for SiPM readout at cryogenic condition implies a long-term RD on the technology and circuit design. As a result, few structures of a single transistor were tested and analyzed at a cryogenic temperature of 77 K. The results describe the behavior of the main internal parameters, such as low-field mobility, threshold voltage, transconductance, and so on. The extraction parameter outcomes develop into a key to design the complete integrated electronics architecture precisely.

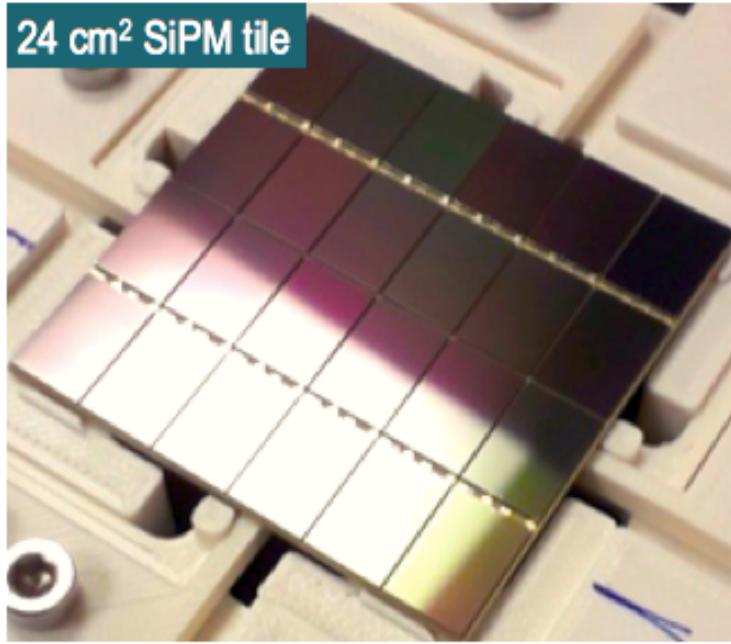

Besides, the cryogenic operation causes a substantial reduction of the failure mechanisms in MOS structures, such as electromigration, stress migration, time-dependent dielectric breakdown, and thermal cycling. However, the most attractive advantage becomes with a consistent reduction of thermal noise, making the readout of a SiPM area of  $24 \text{ cm}^2$  viable. In this experiment, a large area detector is required for a low cabling

and electronic mass, and thus low radioactivity background requirement.

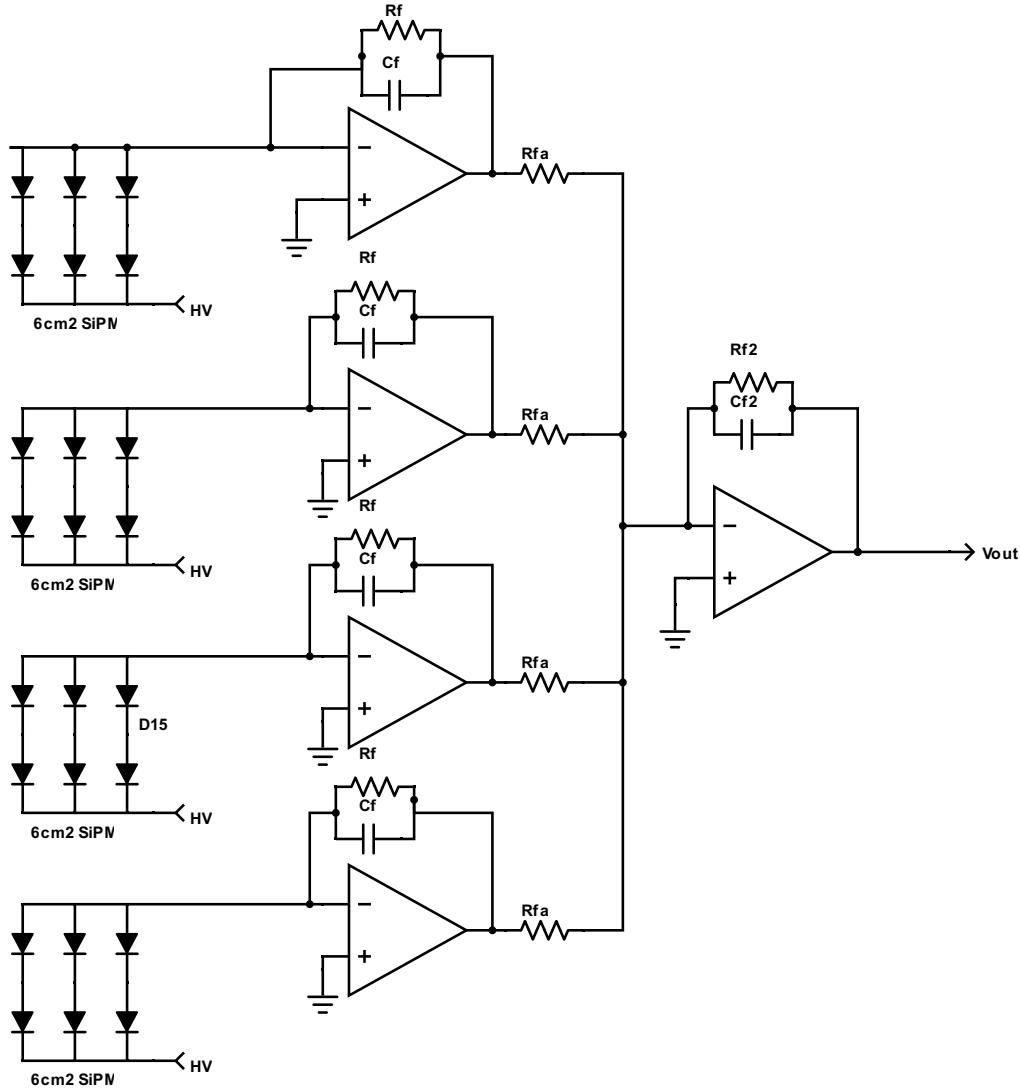

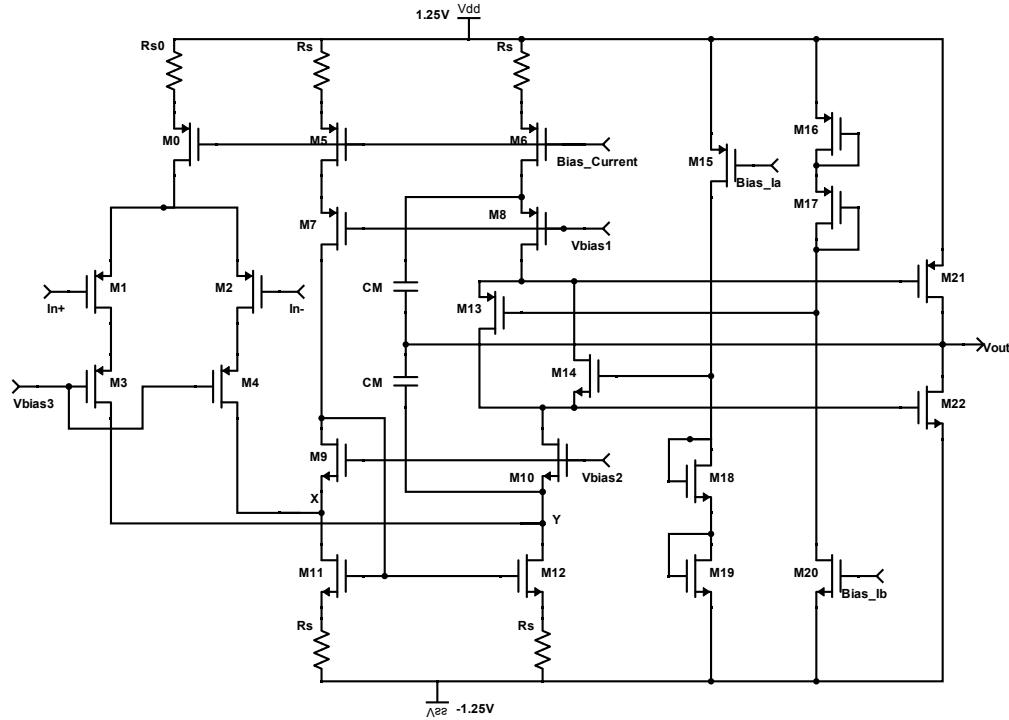

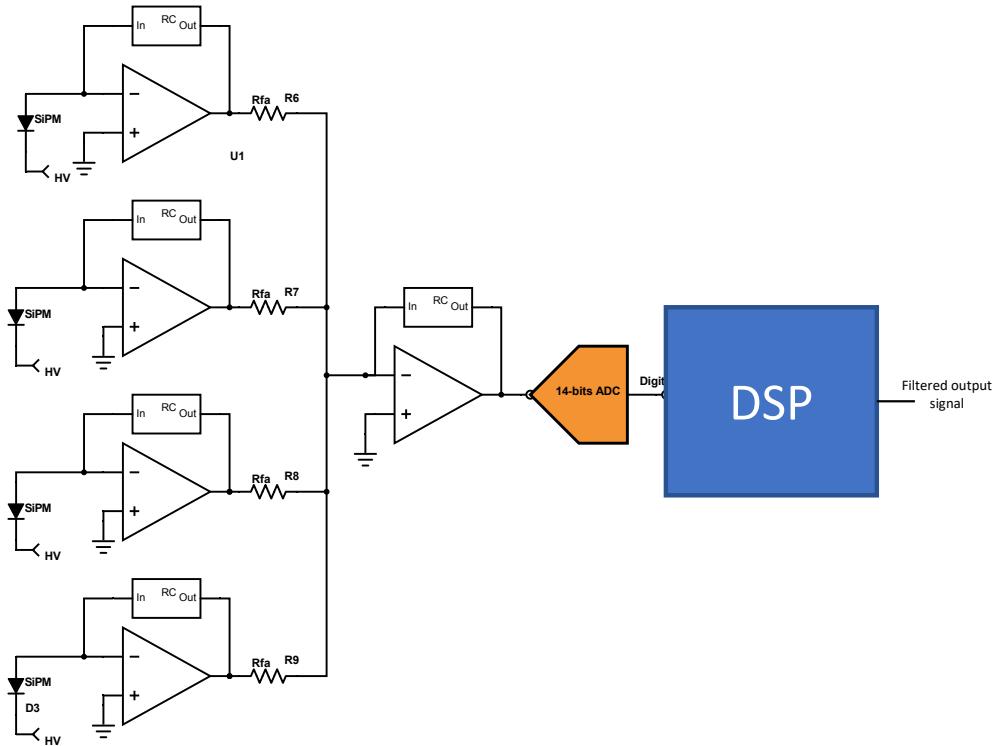

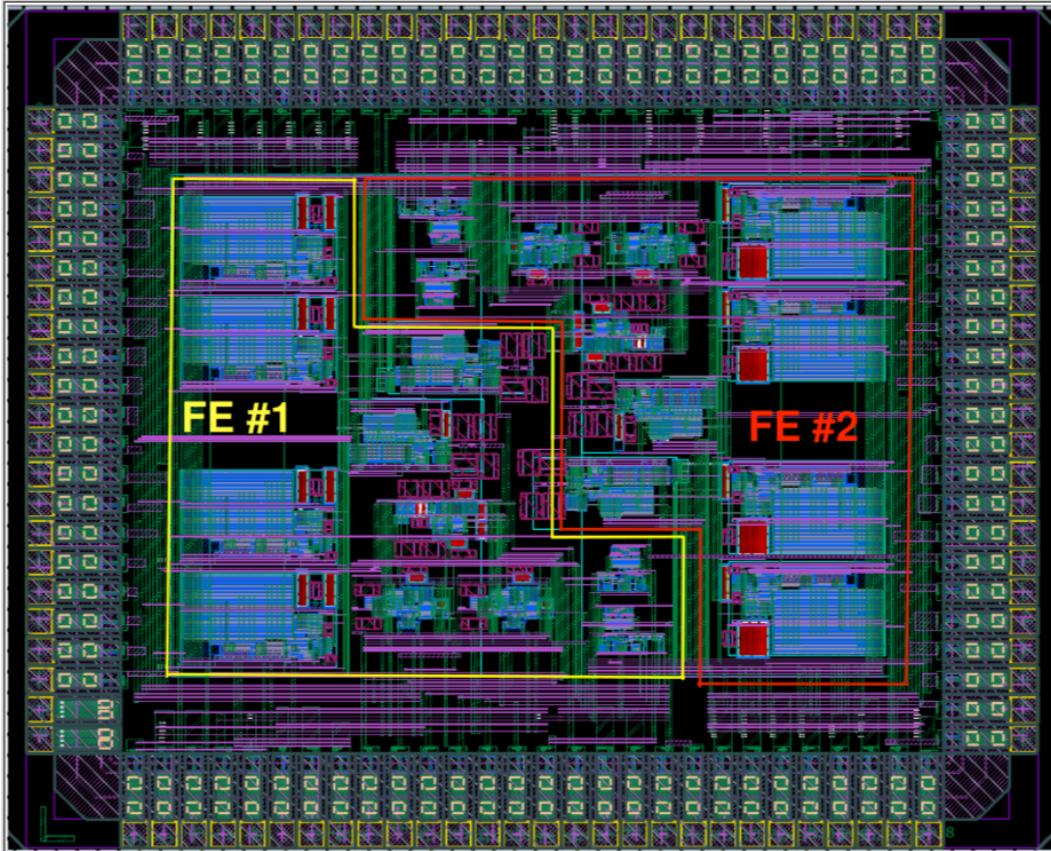

The cryogenic electronics implement a 110 nm CMOS technology. The front-end prototype was developed in two tape-outs. Primarily, the cryogenic electronics (ASIC v1) features 4 fast and low-noise (LN) amplifiers based on Folded Cascode topology with a Class AB amplifier on the output stage. Each low-noise amplifier readout a SiPM quadrant of  $6 \text{ cm}^2$ . The sensor capacitance presents a value of around 10 nF, which highly depends on the bias voltage of the sensor. The 4-LN amplifiers are connected to a summing amplifier to generate a single-end signal from  $24 \text{ cm}^2$  SiPM.

The second tapeout realizes an identical 4-LN and summing amplifier architecture. However, the ASIC v2 incorporates a single-ended to the differential converter. The conversion stage is performed by a fully differential folded cascode structure with common-mode feedback. Besides, the ASIC v2 allows the output signal of cryogenic electronics to be established, as a single-ended or differential signal due to their dedicated power domain. Differential signaling provides the advantage to transport the information from the cryogenic environment to warm data acquisition system by cabling, instead of optical fiber.

# **Acknowledgements**

*I would like to dedicate

this thesis to Istituto

Nazionale di Fisica

Nucleare and Ufficio

VLSI, which allow the

research project to be

developed successfully.

Furthermore, I want to

show a special dedication

to my fiancee for her

support along my Ph.D.

study.*

# Contents

|                                                                               |             |

|-------------------------------------------------------------------------------|-------------|

| <b>List of Tables</b>                                                         | <b>xiii</b> |

| <b>List of Figures</b>                                                        | <b>xiv</b>  |

| <b>1 Introduction</b>                                                         | <b>1</b>    |

| 1.1 Need for Underground Astroparticle experiment . . . . .                   | 2           |

| <b>2 Key developments in cryogenic electronics</b>                            | <b>3</b>    |

| 2.1 Cryogenic electronics for general purposes . . . . .                      | 4           |

| 2.2 Cryogenic electronics for underground astroparticle experiments . . . . . | 9           |

| 2.2.1 Deep Underground Neutrino Experiment . . . . .                          | 9           |

| 2.2.2 Enriched Xenon Observatory . . . . .                                    | 10          |

| 2.2.3 XENON . . . . .                                                         | 12          |

| 2.2.4 DarkSide 50 . . . . .                                                   | 13          |

| 2.3 Cryogenic electronics for DarkSide-20K experiment . . . . .               | 15          |

| 2.3.1 Conclusion . . . . .                                                    | 18          |

| <b>3 Cryogenic CMOS electronics</b>                                           | <b>19</b>   |

| 3.1 Advantages of CMOS electronic at 77 K . . . . .                           | 20          |

| 3.1.1 Carrier mobility . . . . .                                              | 20          |

| 3.1.2 Thermal and low frequency noise . . . . .                               | 24          |

| 3.1.3 Transit Frequency and Power consumption . . . . .                       | 25          |

| 3.1.4 Electromigration and series resistance . . . . .                        | 27          |

| 3.1.5 Interconnect resistance . . . . .                                       | 27          |

| 3.2 Drawbacks of CMOS electronic at 77 K . . . . .                            | 28          |

| 3.2.1 Hot carrier degradation . . . . .                                       | 28          |

| 3.2.2 Threshold voltage . . . . .                                             | 29          |

| 3.3 Key parameters extraction of 110 nm CMOS technology at 300 K and 77 K     | 31          |

| 3.3.1 Threshold voltage extraction . . . . .                                  | 31          |

| 3.3.2 Low field mobility . . . . .                                            | 32          |

| 3.3.3 Series resistances . . . . .                                            | 35          |

| 3.3.4 Mobility attenuation . . . . .                                          | 37          |

|          |                                                                                  |           |

|----------|----------------------------------------------------------------------------------|-----------|

| 3.3.5    | Sub-threshold swing and slope factor . . . . .                                   | 38        |

| 3.3.6    | Normalized trans-conductance for weak and strong inversion regime . . . . .      | 39        |

| 3.3.7    | Mismatch paramaters . . . . .                                                    | 40        |

| 3.3.8    | CMOS electronics at 4.2 K . . . . .                                              | 42        |

| <b>4</b> | <b>Design of a cryogenic front-end electronics for large area SiPM (ASIC v1)</b> | <b>45</b> |

| 4.1      | Photo-detection system . . . . .                                                 | 46        |

| 4.2      | CMOS Front-end integrated electronics . . . . .                                  | 52        |

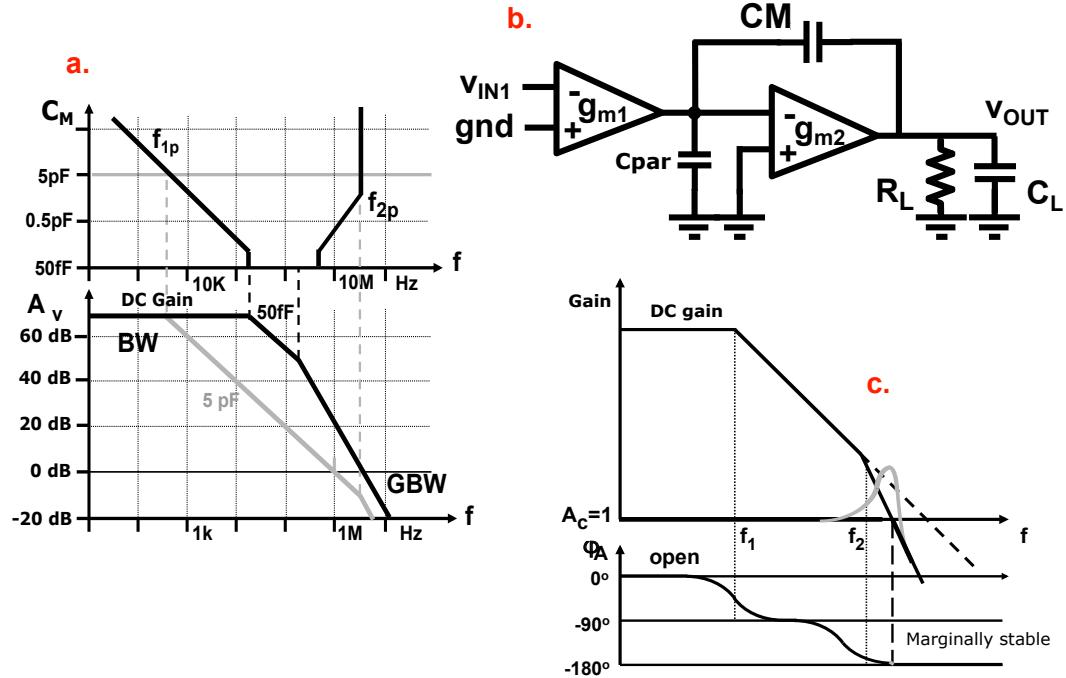

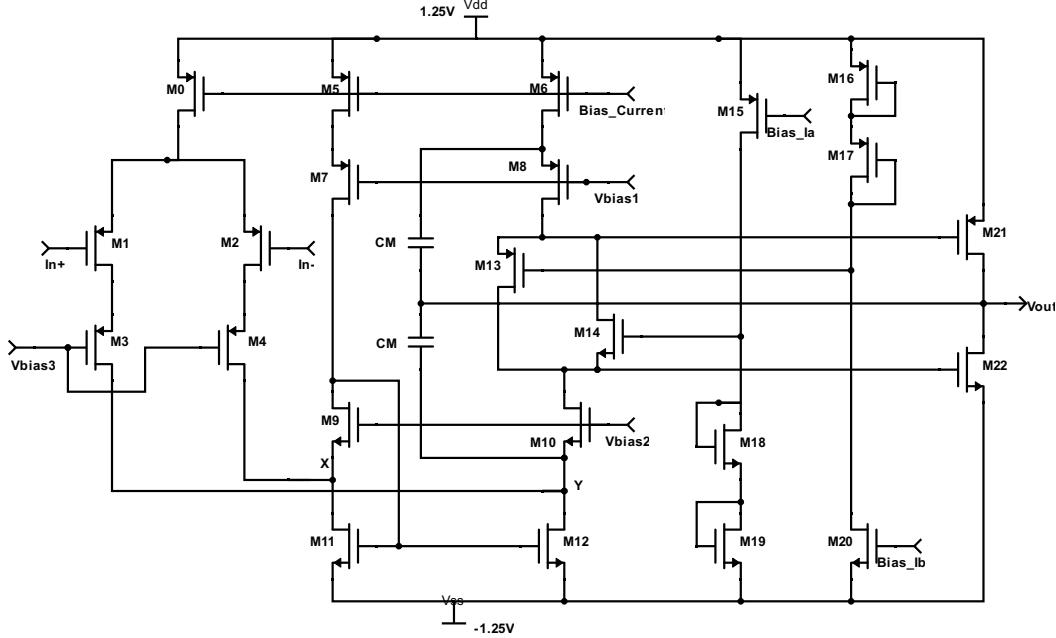

| 4.3      | Transistor-level design of operation amplifier circuits . . . . .                | 53        |

| 4.4      | CMOS electronics post-layout simulations . . . . .                               | 62        |

| 4.4.1    | Monte Carlo simulation . . . . .                                                 | 66        |

| <b>5</b> | <b>Experimental results of cryogenic ASIC v1</b>                                 | <b>71</b> |

| 5.1      | Experimental setup for cryogenic electronics . . . . .                           | 72        |

| 5.2      | Key parameters of the photon-electron signal . . . . .                           | 75        |

| 5.2.1    | RMS noise . . . . .                                                              | 75        |

| 5.2.2    | Signal to noise ratio (SNR) . . . . .                                            | 76        |

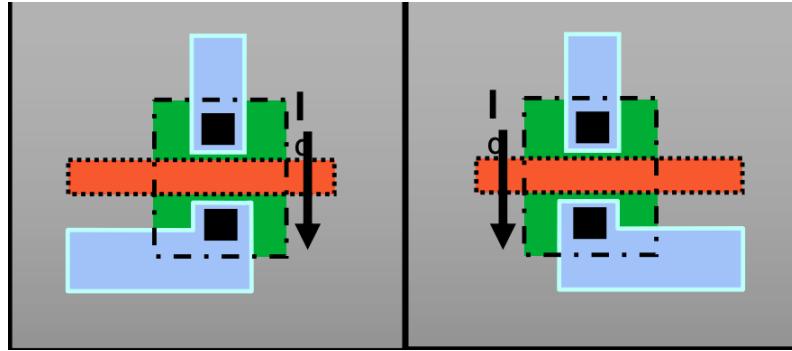

| 5.2.3    | Rising time . . . . .                                                            | 78        |

| 5.2.4    | Linearity . . . . .                                                              | 78        |

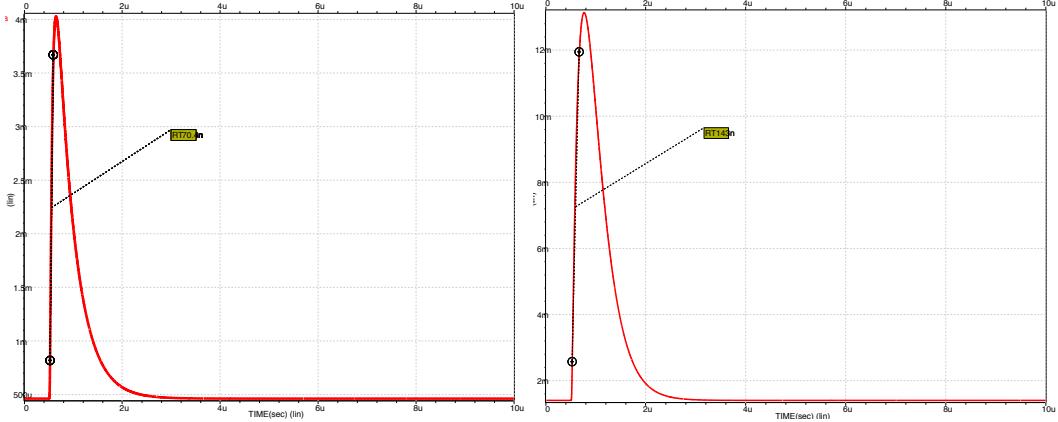

| 5.2.5    | Dynamic range . . . . .                                                          | 80        |

| 5.2.6    | Experimental and simulation results . . . . .                                    | 81        |

| 5.3      | Output voltage histogram at different SiPM bias voltages . . . . .               | 83        |

| 5.4      | Digital filtering for dark matter measurements . . . . .                         | 86        |

| 5.4.1    | Digital trapezoidal pulse-shaper . . . . .                                       | 88        |

| 5.4.2    | Simulation and implementation tool . . . . .                                     | 90        |

| 5.4.3    | Filtering post-implementation results . . . . .                                  | 92        |

| <b>6</b> | <b>Circuit design of cryogenic ASIC v2</b>                                       | <b>95</b> |

| 6.1      | ASIC v2 architecture and floorplan . . . . .                                     | 96        |

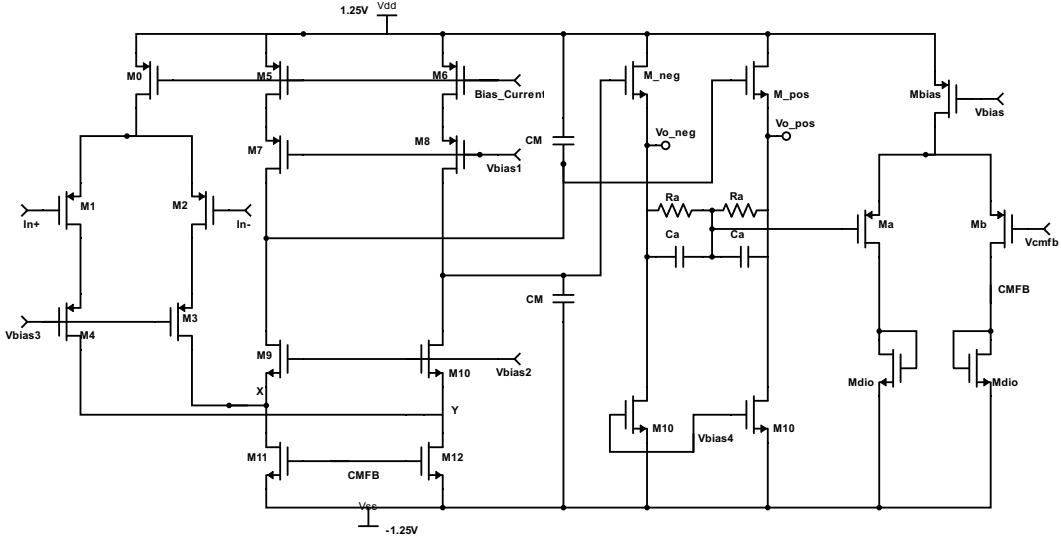

| 6.1.1    | Fully differential folded cascode amplifier . . . . .                            | 97        |

| 6.1.2    | Transistor-level design sizing . . . . .                                         | 98        |

| 6.1.3    | Transistor-level design of buffer stages . . . . .                               | 103       |

| 6.1.4    | ASIC v2 layout structure . . . . .                                               | 104       |

| 6.2      | ASIC simulation . . . . .                                                        | 105       |

| 6.2.1    | Post-layout simulation for a single PE . . . . .                                 | 106       |

| 6.2.2    | Monte Carlo simulations of ASIC v2 . . . . .                                     | 107       |

| 6.3      | Experimental results of ASIC V2 - Front-end 2 . . . . .                          | 110       |

| 6.3.1    | Key parameters of the front-end electronics . . . . .                            | 112       |

| 6.3.2    | RMS noise . . . . .                                                              | 112       |

| 6.3.3    | Signal to noise ratio . . . . .                                                  | 114       |

|                                                                      |                                           |            |

|----------------------------------------------------------------------|-------------------------------------------|------------|

| 6.3.4                                                                | Rising time . . . . .                     | 115        |

| 6.3.5                                                                | Dynamic range . . . . .                   | 116        |

| 6.3.6                                                                | DC gain and output swing issues . . . . . | 119        |

| <b>Conclusion</b>                                                    |                                           | <b>123</b> |

| Aspect Ratio of the TIA amplifier - ASIC v1 . . . . .                | 125                                       |            |

| Aspect Ratio of the summing voltage amplifier . . . . .              | 126                                       |            |

| Aspect Ratio of the TIA amplifier - ASIC v2 . . . . .                | 127                                       |            |

| Aspect Ratio of the summing voltage amplifier - ASIC v2 . . . . .    | 128                                       |            |

| Aspect Ratio of the fully differential amplifier - ASIC v2 . . . . . | 129                                       |            |

| Aspect Ratio of the converter output stages - ASIC v2 . . . . .      | 130                                       |            |

| <b>Bibliography</b>                                                  |                                           | <b>132</b> |

# List of Tables

|     |                                                                                                                                                                                                                           |     |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Normalized resistance over temperatures in CMOS technology. Table is taken from [43] . . . . .                                                                                                                            | 28  |

| 4.1 | Simulation results of Front-end electronics at 300 K and 77 K. NoN means there is no any specification for this parameter . . . . .                                                                                       | 64  |

| 5.1 | Signal to noise ratio table vs overvoltages . . . . .                                                                                                                                                                     | 77  |

| 5.2 | Signal to noise ratio table vs overvoltages using a new SiPM structure . . . . .                                                                                                                                          | 77  |

| 5.3 | Experimental and simulation results of Front-end electronics at 77 K, applying an overvoltage equal to 5 V. . . . .                                                                                                       | 82  |

| 6.1 | Simulation results of ASIC v2 FE1 and FE2 at 77 K. . . . .                                                                                                                                                                | 106 |

| 6.2 | Key parameters of ASIC v1 and ASIC v2 implementing the charge injection board with the same input charge from Liquid Nitrogen tests. The single PE parameters are extrapolated from the ASIC v1 results at 5 VoV. . . . . | 118 |

| 3   | Transistor characterization of Folded Cascode for TIA . . . . .                                                                                                                                                           | 125 |

| 4   | Transistor characterization of Folded Cascode for TIA . . . . .                                                                                                                                                           | 126 |

| 5   | Transistor characterization of Folded Cascode for TIA . . . . .                                                                                                                                                           | 127 |

| 6   | Transistor characterization of Folded Cascode of summing amplifier ASIC v2 . . . . .                                                                                                                                      | 128 |

| 7   | Transistor characterization of Folded Cascode for TIA . . . . .                                                                                                                                                           | 129 |

| 8   | Transistor characterization of Folded Cascode for TIA . . . . .                                                                                                                                                           | 130 |

# List of Figures

|      |                                                                                                                                      |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Deep space antenna for the future space missions of the European Space Agency (ESA). Picture taken from ESA . . . . .                | 5  |

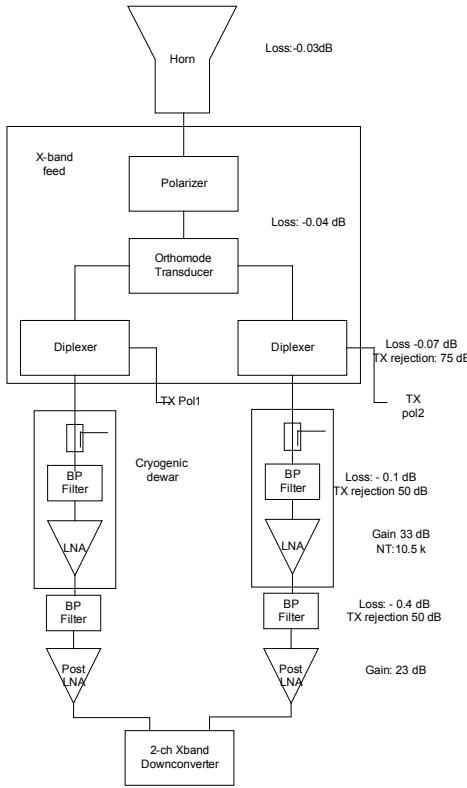

| 2.2  | Fully schematic of the front-end electronic circuits for space missions. Picture taken from [11] . . . . .                           | 6  |

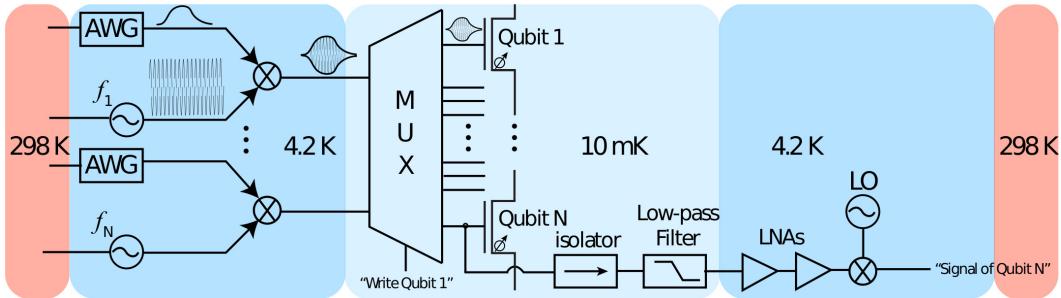

| 2.3  | Fully schematic of the front-end electronic circuits for controlling and measuring spin qubits. Picture taken from [22] . . . . .    | 7  |

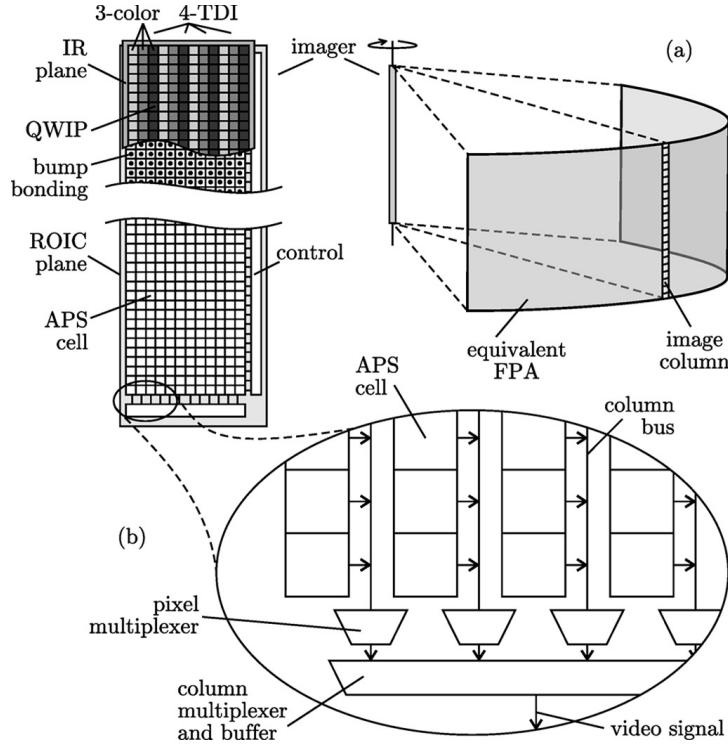

| 2.4  | CMOS APS Circuits for Hybrid Cryogenic Infrared Fast Imaging schematic. Picture taken from [23] . . . . .                            | 8  |

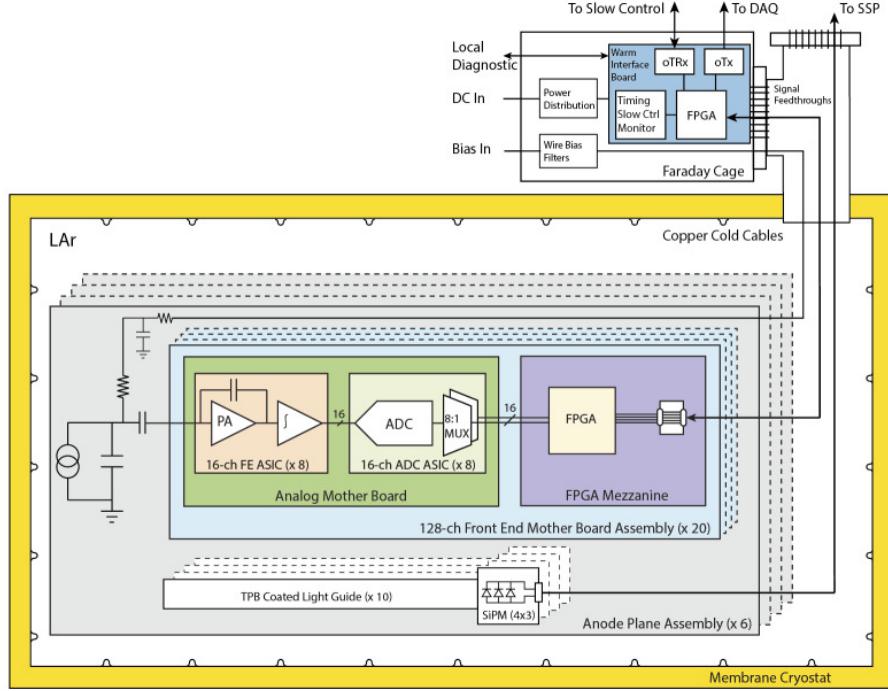

| 2.5  | ProtoDUNE cryogenic electronics architecture. Picture taken from [27]                                                                | 10 |

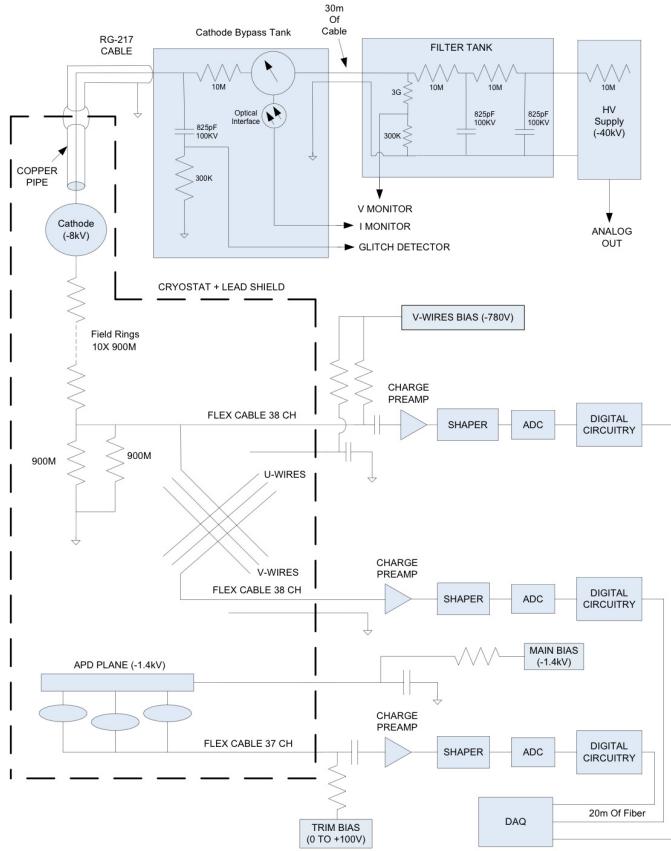

| 2.6  | TPC biasing and readout electronics systems of EXO-200. Picture taken from [30] . . . . .                                            | 11 |

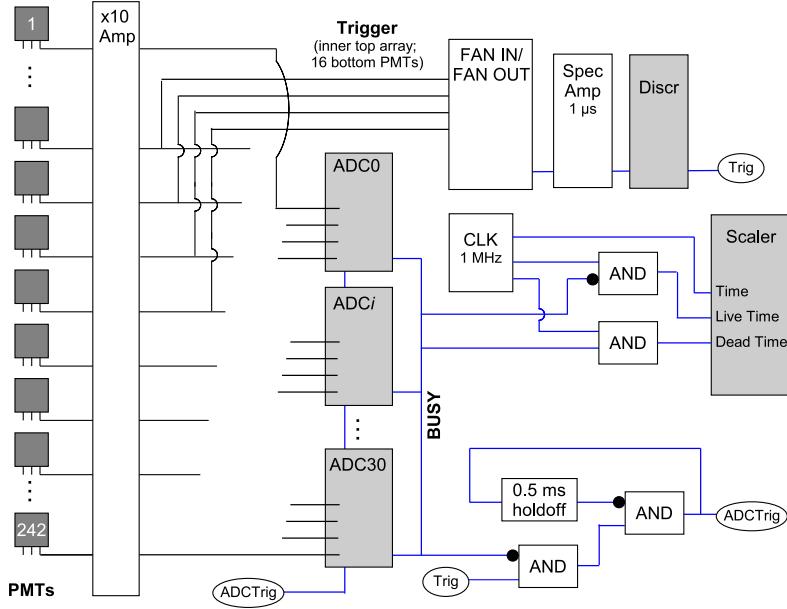

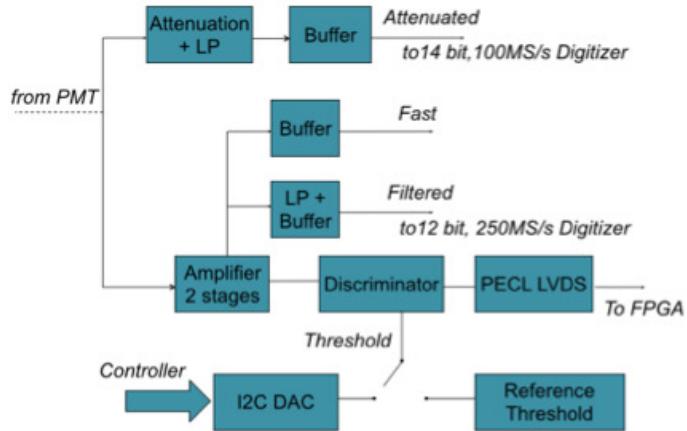

| 2.7  | Data acquisition schematic for all 242 PMT realized in XENON100 experiment. Picture taken from [31] . . . . .                        | 13 |

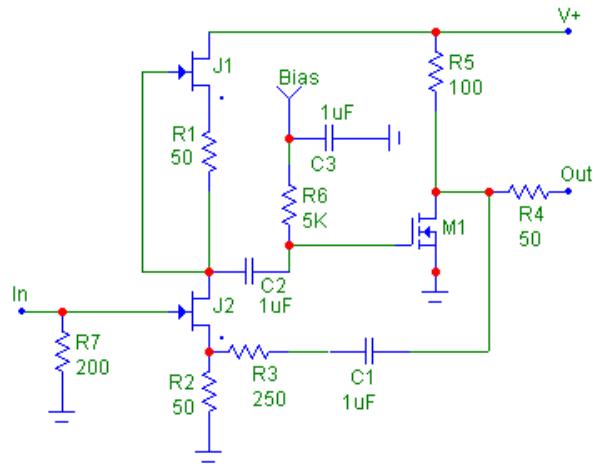

| 2.8  | Block diagram of the DarkSide 50 Front-End-Module. Picture taken from [36] . . . . .                                                 | 14 |

| 2.9  | Block diagram of the DarkSide 50 Front-End-Module. Picture was taken from [36] . . . . .                                             | 14 |

| 2.10 | Preliminary prototype of DarkSide 20K. The picture was taken from [39]                                                               | 15 |

| 2.11 | Time projection chamber system implemented within DarkSide 20k. Picture taken from [39] . . . . .                                    | 16 |

| 2.12 | VETO system implemented within DarkSide 20k. . . . .                                                                                 | 17 |

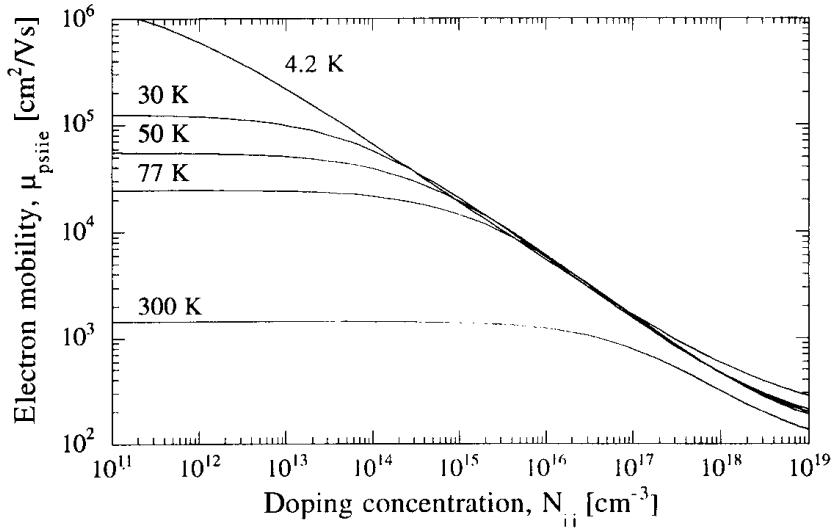

| 3.1  | Phonon and ionized impurity scattering vs doping concentration at different operation temperatures, graphic taken from [45]. . . . . | 22 |

| 3.2  | Electron mobility vs electric field at different operation temperatures, graphic taken from [45]. . . . .                            | 24 |

| 3.3  | Electron response under heating. Picture taken from [49]. . . . .                                                                    | 24 |

| 3.4  | LF noise versus temperature scan for a pMOS in a range of 6 - 295 K. Graph taken from [53]. . . . .                                  | 26 |

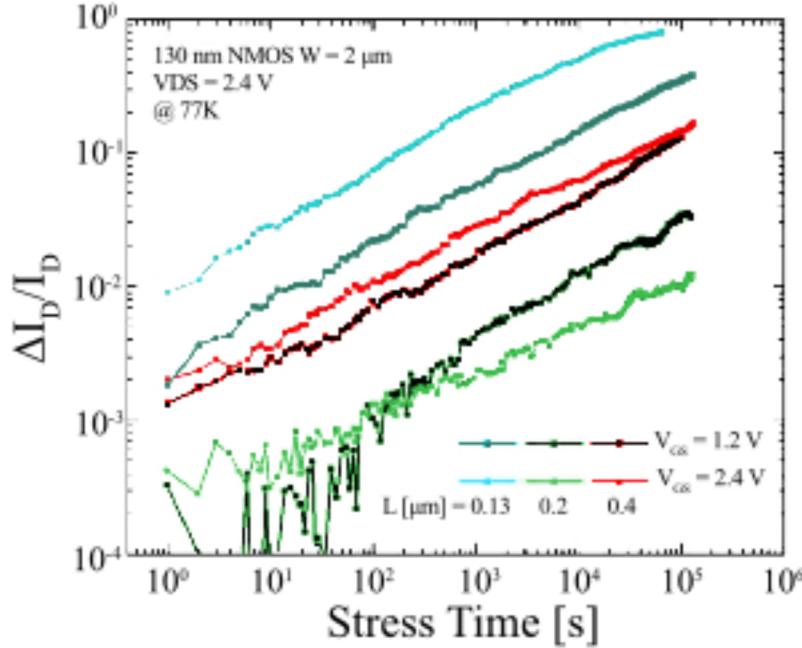

| 3.5  | Lifetime of transistor 130 nm using different channel length at 77 K. Figure taken from [9] . . . . .                                | 29 |

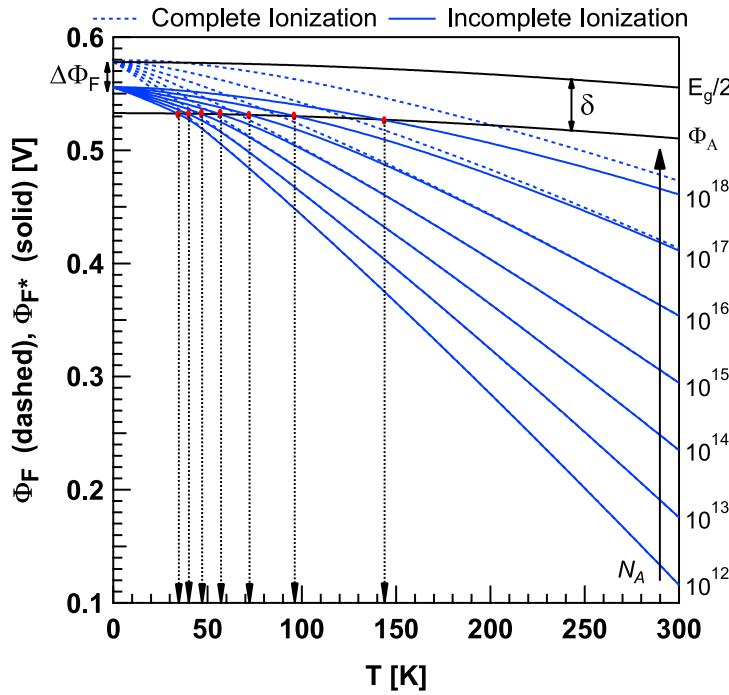

| 3.6  | Fermi potential in a NMOS transistor over temperature. Figure taken from [60] . . . . .                                              | 30 |

|      |                                                                                                                                                                                                                                                                                                                                                   |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

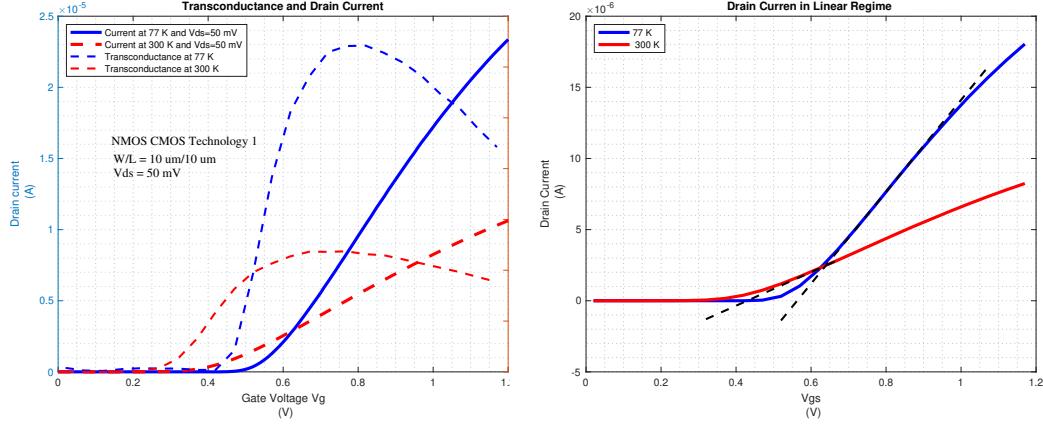

| 3.7  | Drain Current and Transconductance curve in strong inversion regime of the CMOS linear region (left) and linear extrapolation curve (right). . . . .                                                                                                                                                                                              | 32 |

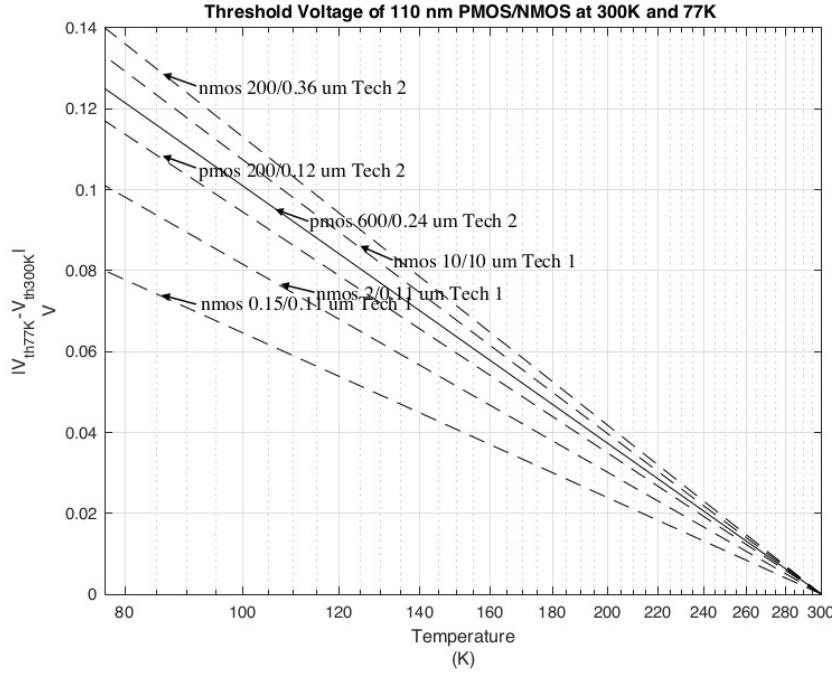

| 3.8  | Threshold voltage variation at 300 K and 77 K, considering the pMOS and nMOS structure of two 110 nm technologies (Tech1 and Tech 2). The figure only represents the points at 300 K and 77 K. This means the curve does not present a linear behavior in the intermediate temperatures, but just a unification of 2 temperature corners. . . . . | 33 |

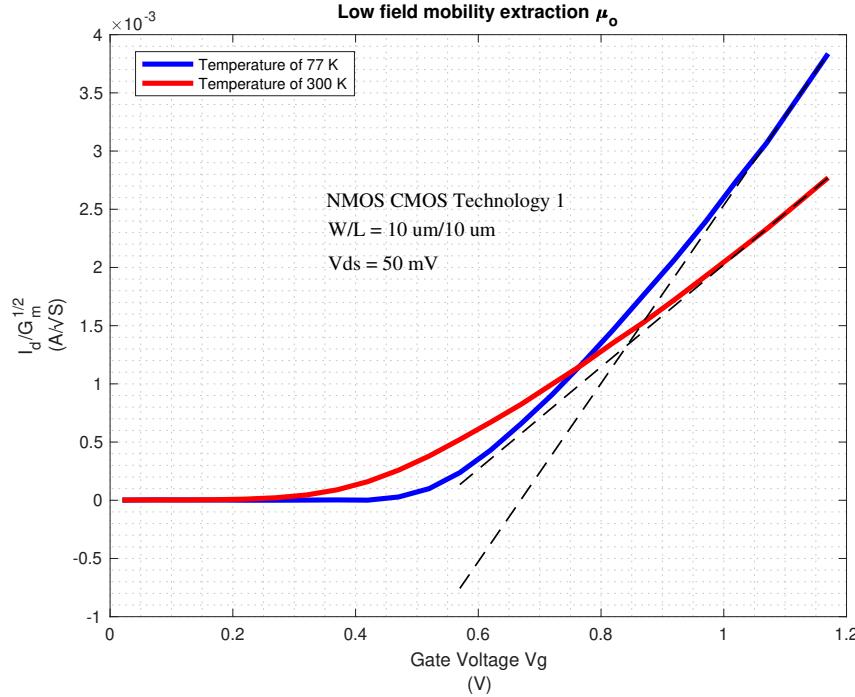

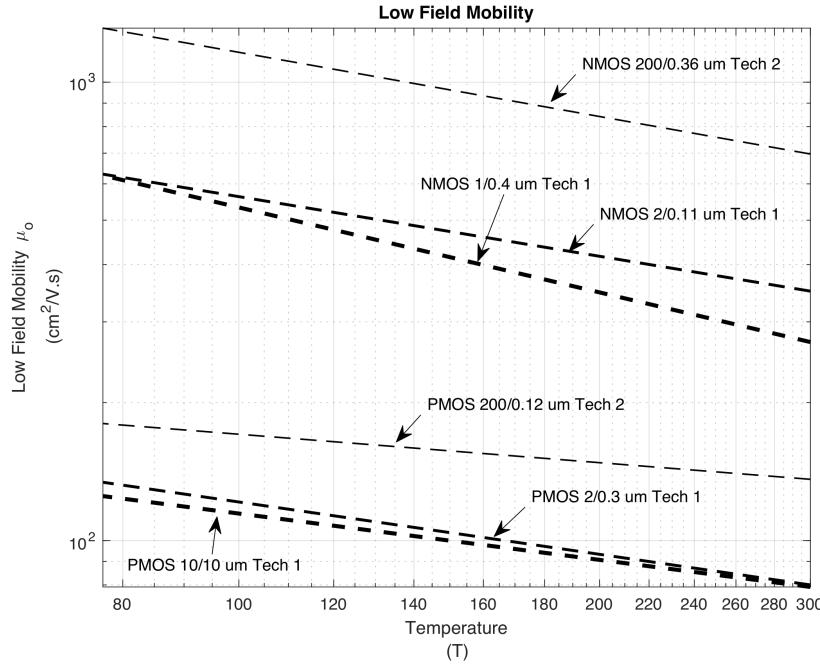

| 3.9  | CMOS low field mobility extraction at 300 K and 77 K. . . . .                                                                                                                                                                                                                                                                                     | 34 |

| 3.10 | Low field mobility extracted from different transistor aspect ratio and technology at 300 K and 77 K. The figure only represents the points at 300 K and 77 K. This means the curve does not present a linear behavior in the intermediate temperatures. . . . .                                                                                  | 35 |

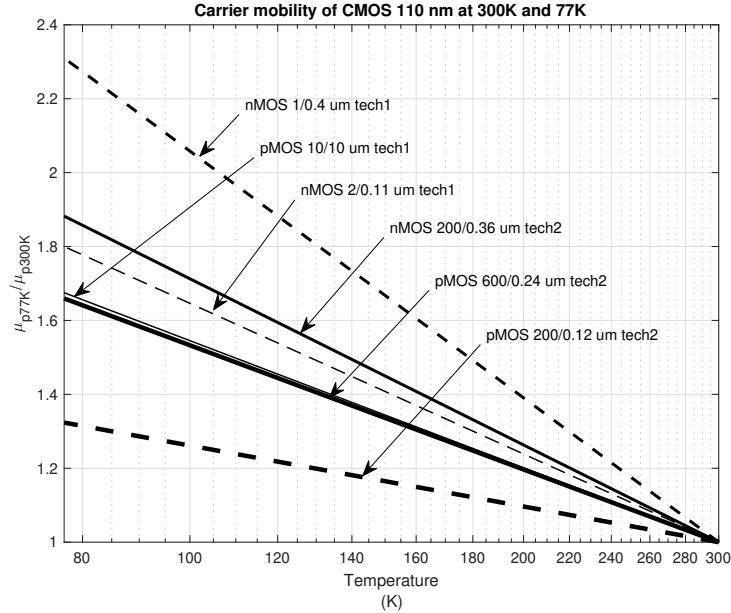

| 3.11 | Normalized low field mobility in a CMOS technology. The figure just represents two points at 300 K and 77 K. This means the curve does not present any data in the intermediate temperatures. . . . .                                                                                                                                             | 36 |

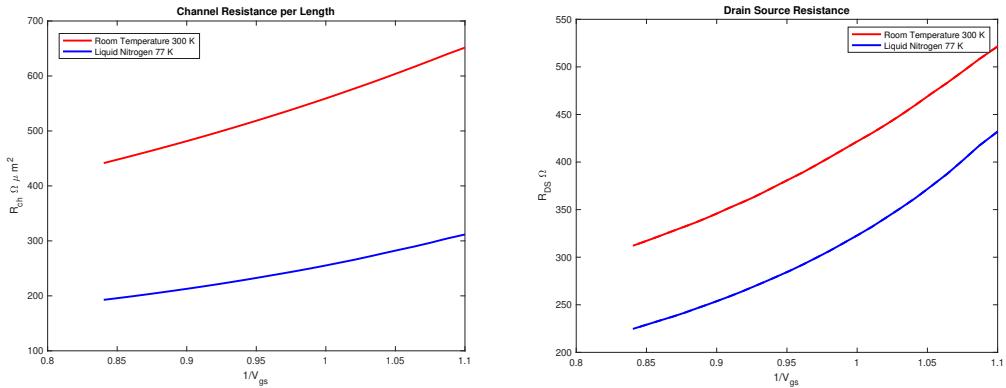

| 3.12 | Channel per unit length resistance (left) and drain-source resistance (right) at 300 K and 77 K. . . . .                                                                                                                                                                                                                                          | 36 |

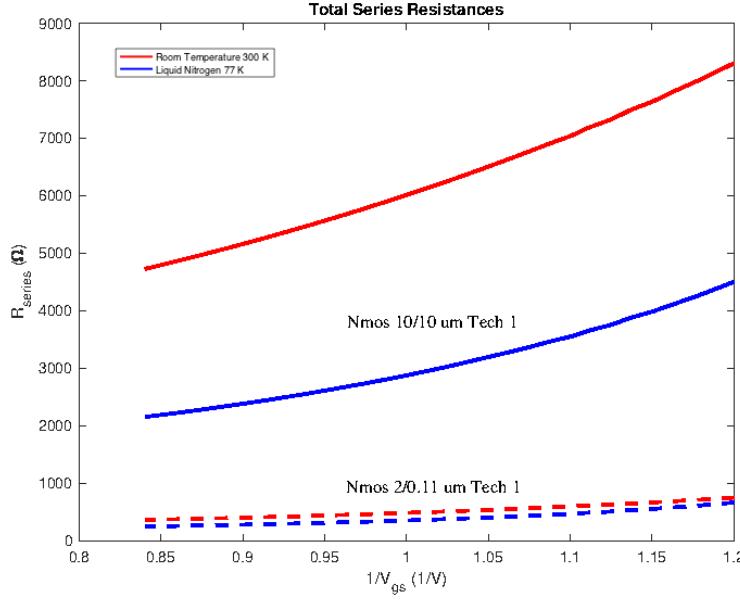

| 3.13 | Total series resistance at 300 K and 77 K of 2 nMOS transistor with different channel length. . . . .                                                                                                                                                                                                                                             | 37 |

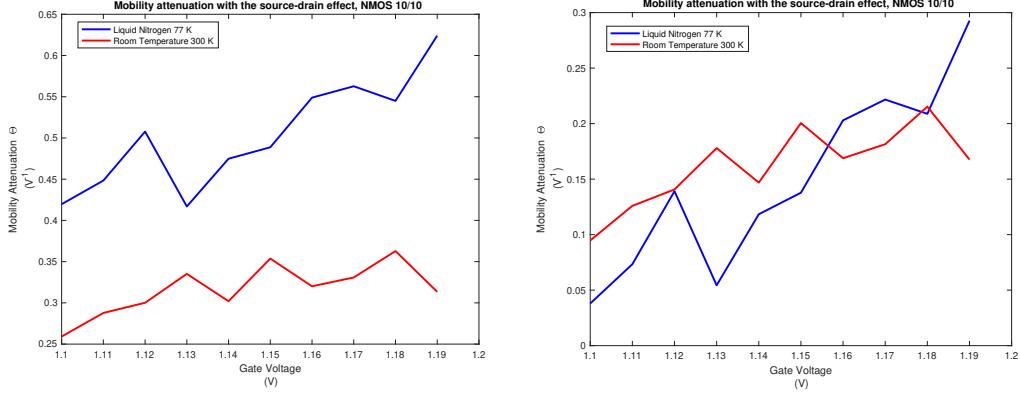

| 3.14 | Mobility attenuation at 300 K and 77 K with the drain-source resistance effect (left) and without the drain-source resistance effect (right). . . . .                                                                                                                                                                                             | 38 |

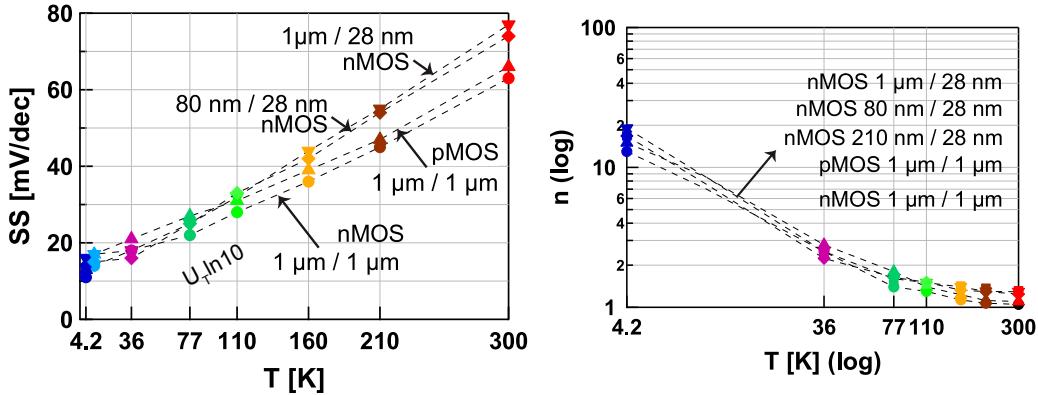

| 3.15 | Sub-threshold swing (left) and the slope factor (right) behavior on temperature. Figure taken from [63] . . . . .                                                                                                                                                                                                                                 | 39 |

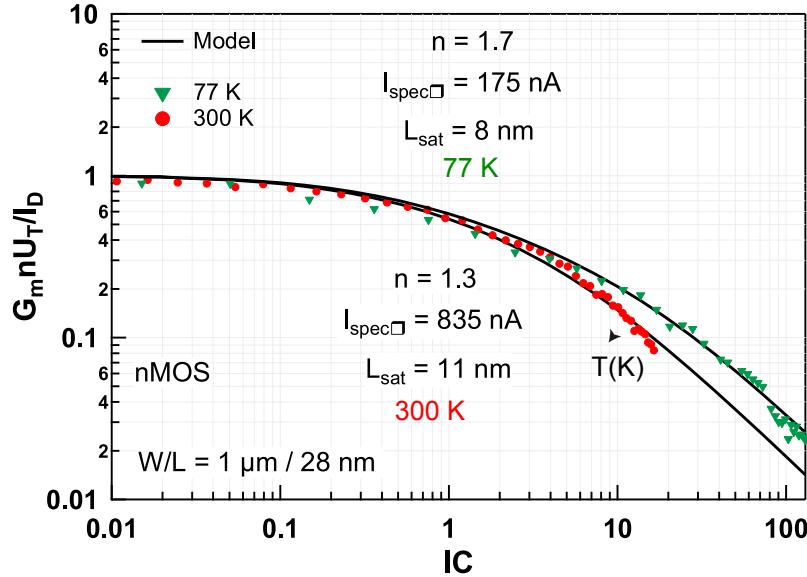

| 3.16 | Normalized transconductance efficiency of a 28 nm technology over the inversion coefficient, figure taken from [54]. . . . .                                                                                                                                                                                                                      | 40 |

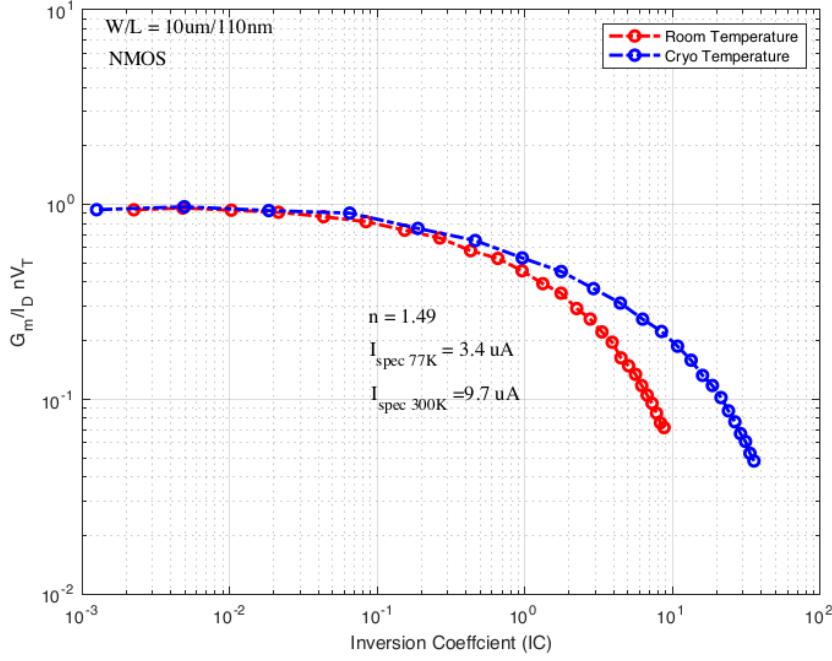

| 3.17 | Normalized transconductance efficiency over the inversion coefficient, using a 110 nm technology. . . . .                                                                                                                                                                                                                                         | 41 |

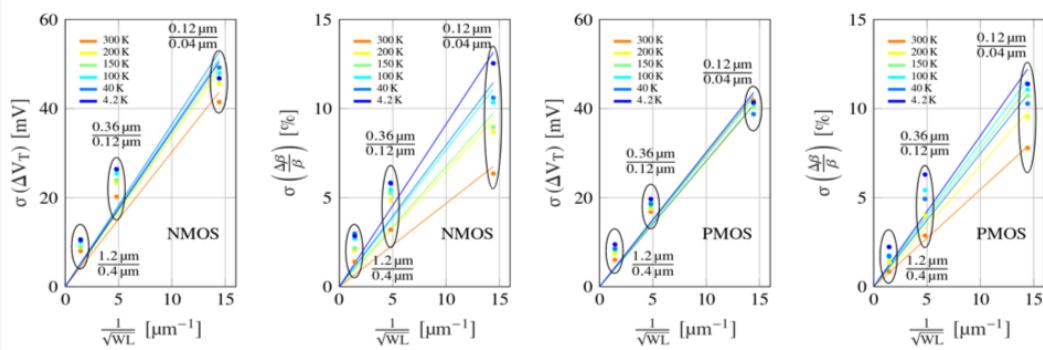

| 3.18 | Mismatch parameters variation from 300 K to 77 K. Figure taken from [64]. . . . .                                                                                                                                                                                                                                                                 | 41 |

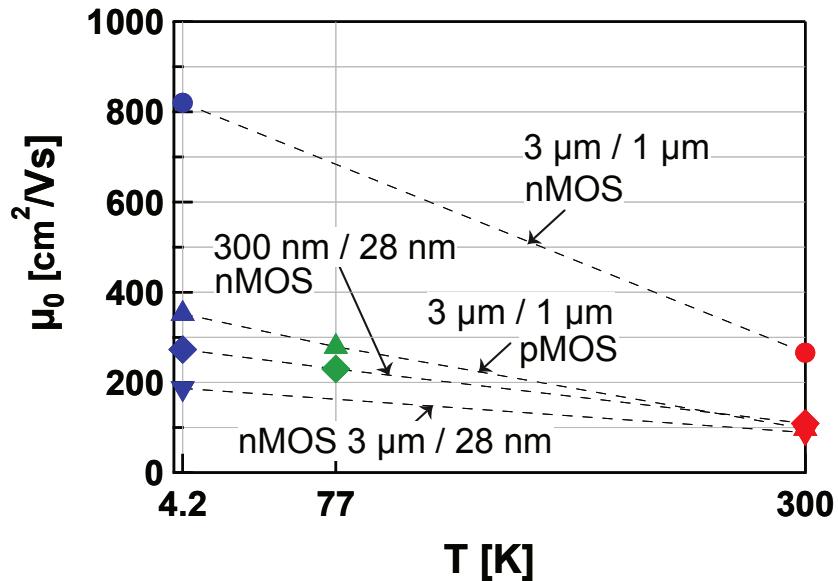

| 3.19 | Low field mobility from 300 K to 4.2 K extracted from 28 nm CMOS technology [3]. . . . .                                                                                                                                                                                                                                                          | 42 |

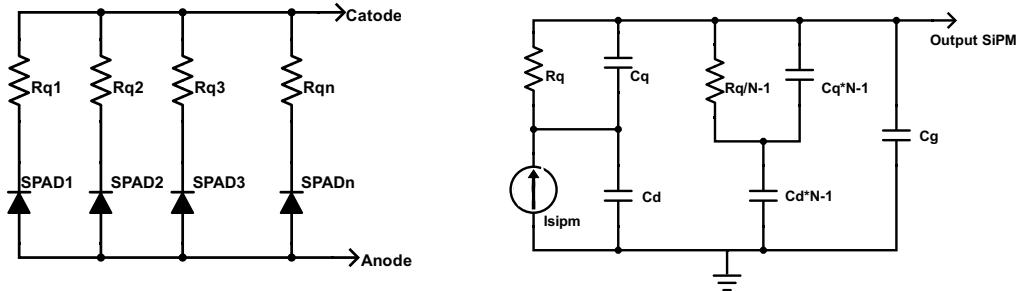

| 4.1  | Structure of SiPM microcells (left) and SiPM electrical model (right) . .                                                                                                                                                                                                                                                                         | 46 |

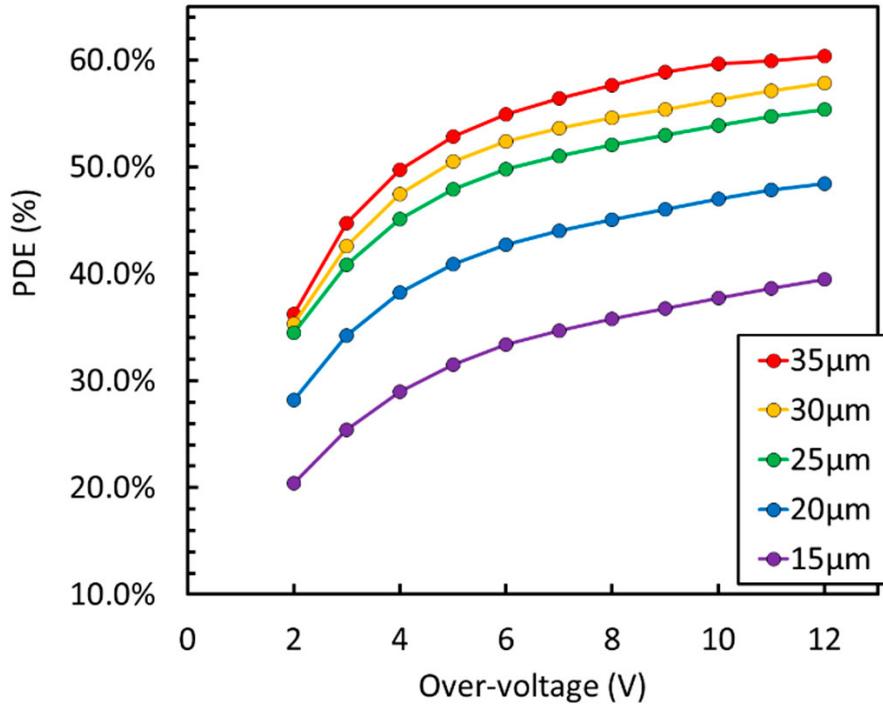

| 4.2  | Photo detection efficiency for visible light at different overvoltages. Each curve corresponds to a particular size of the SiPM micro-cell. Figure taken from [66] . . . . .                                                                                                                                                                      | 47 |

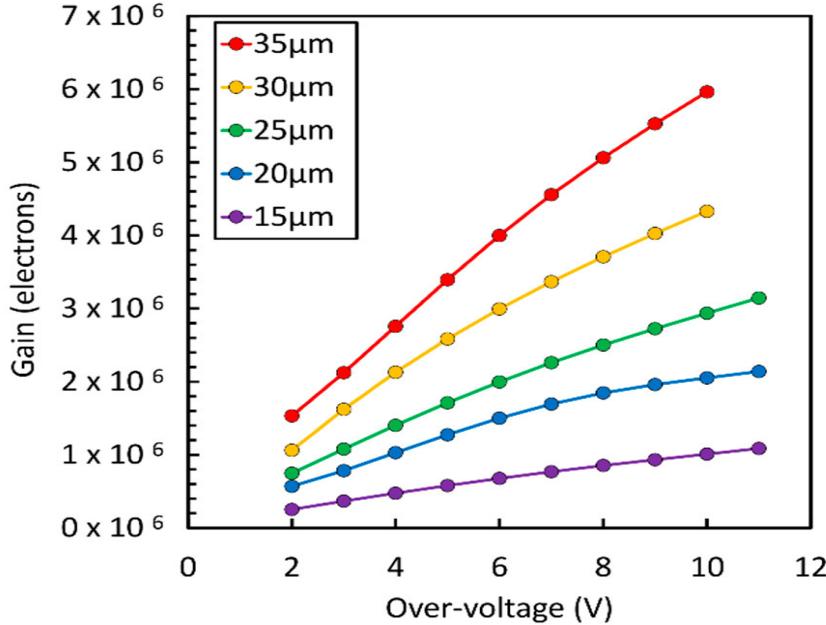

| 4.3  | SiPM gain vs overvoltage at different micro-cell sizes. Figure taken from [1]. . . . .                                                                                                                                                                                                                                                            | 48 |

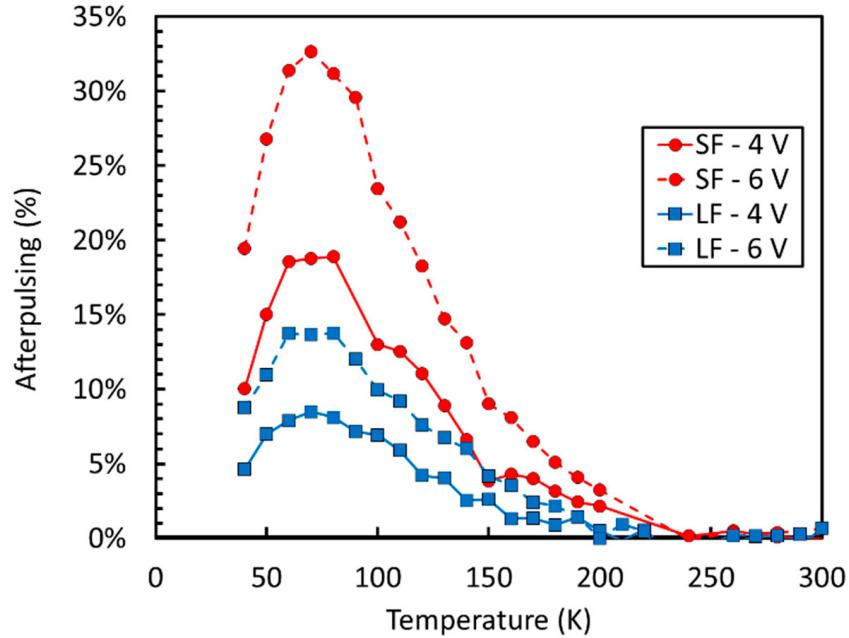

| 4.4  | Afterpulsing probability vs temperature using a 25 um micro-cell. Figure taken from [66]. . . . .                                                                                                                                                                                                                                                 | 49 |

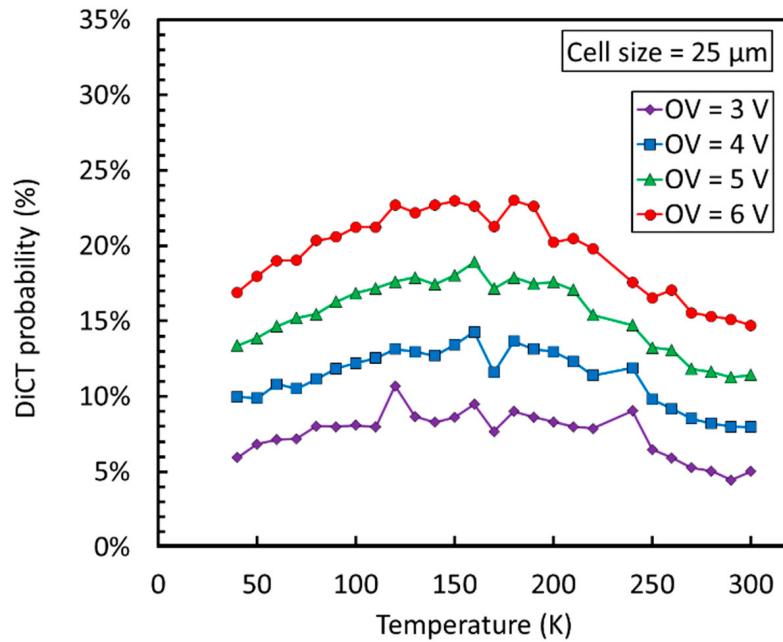

| 4.5  | Direct crosstalk probability vs temperature. Figure taken from [66]. . .                                                                                                                                                                                                                                                                          | 50 |

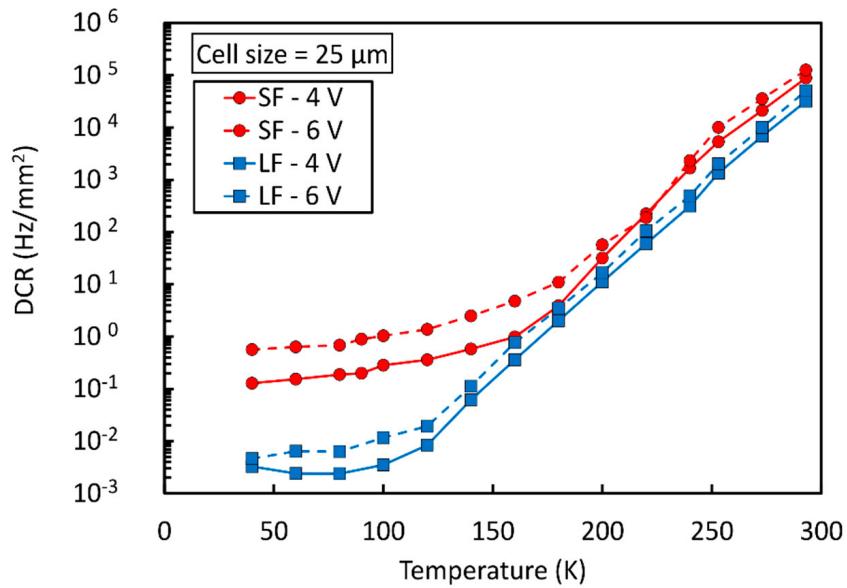

| 4.6  | Dark count rate vs temperature .Figure taken from [66]. . . . .                                                                                                                                                                                                                                                                                   | 50 |

| 4.7  | 24 cm <sup>2</sup> array of Silicon Photomultipliers. Figure taken from [67]. . . .                                                                                                                                                                                                                                                               | 51 |

|      |                                                                                                                              |    |

|------|------------------------------------------------------------------------------------------------------------------------------|----|

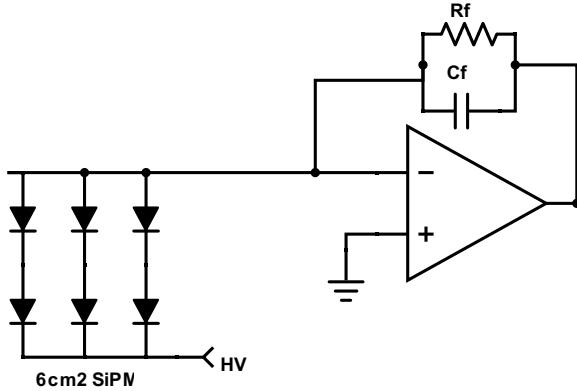

| 4.8  | 6 cm <sup>2</sup> 2-series 3-parallel configuration . . . . .                                                                | 51 |

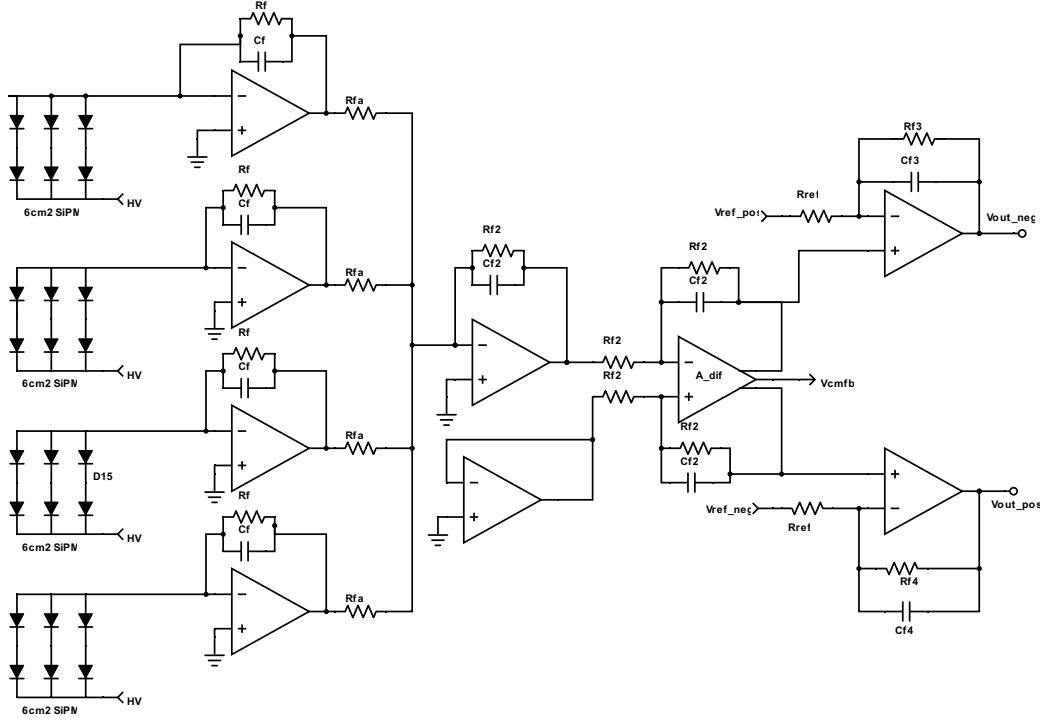

| 4.9  | Full front-end to readout the 24 cm <sup>2</sup> SiPM tile. . . . .                                                          | 53 |

| 4.10 | Transistor-level circuit of the folded cascode OTA. . . . .                                                                  | 54 |

| 4.11 | Frequency compensation schematic. . . . .                                                                                    | 60 |

| 4.12 | Trans-impedance amplifier schematic. . . . .                                                                                 | 61 |

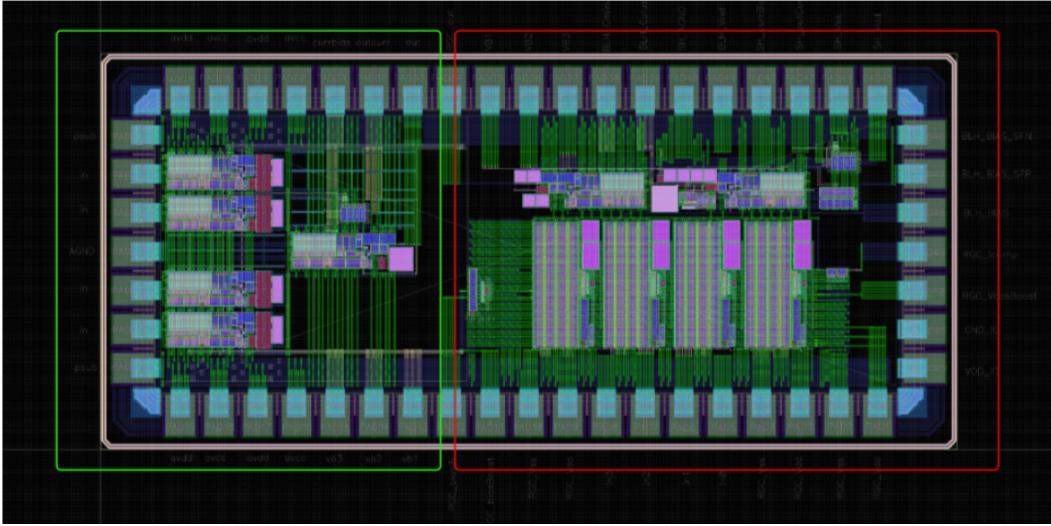

| 4.13 | Layout structure of the ASIC V1 (green) . . . . .                                                                            | 63 |

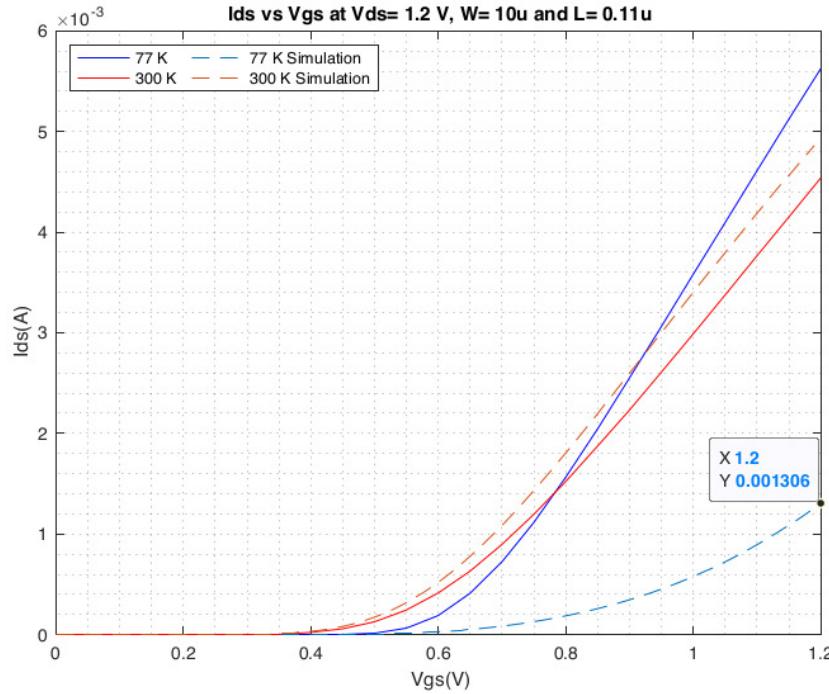

| 4.14 | Drain current vs gate voltage of nMOS transistor W/L=10/0.11, simulation and experimental results . . . . .                  | 64 |

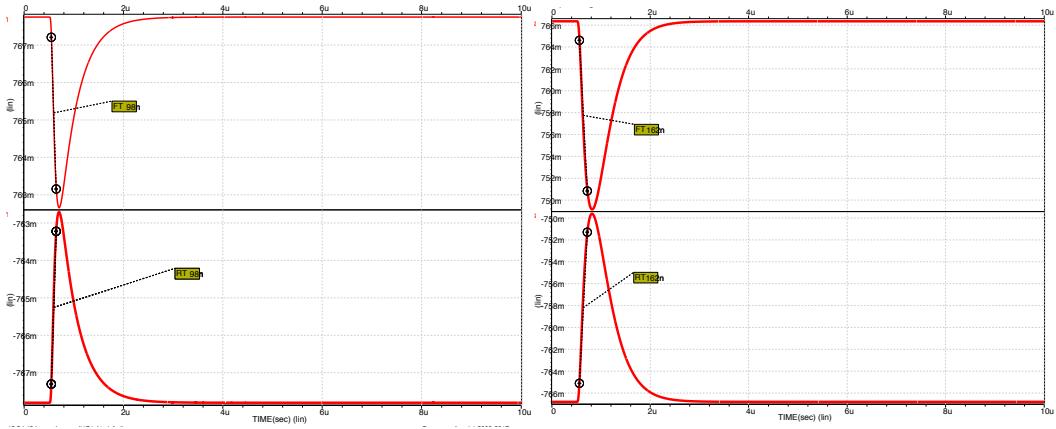

| 4.15 | Output signal waveform of front-end electronics at 300 K. . . . .                                                            | 65 |

| 4.16 | Output signal waveform of front-end electronics at 77 K. . . . .                                                             | 65 |

| 4.17 | Mismatch Montecarlo simulation of input common mode at 300 K. . . . .                                                        | 66 |

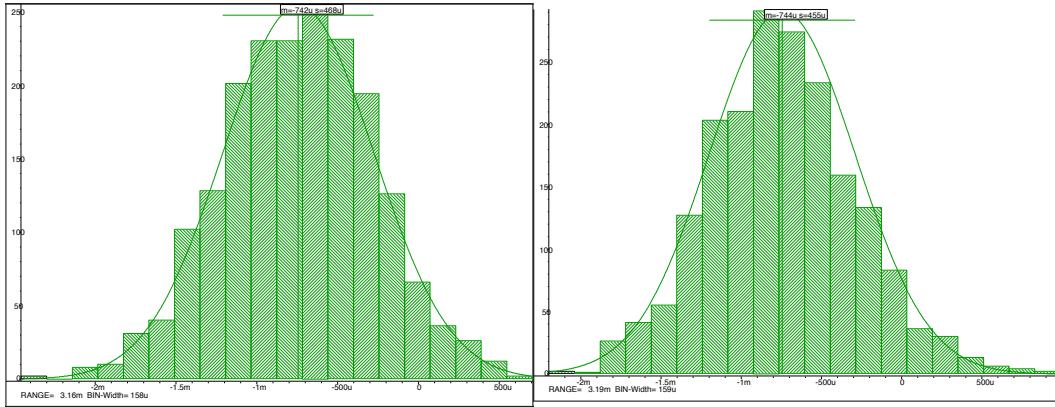

| 4.18 | Mismatch Montecarlo simulation of output baseline at 300 K. . . . .                                                          | 67 |

| 4.19 | Mismatch Montecarlo simulation of output amplitude at 300 K. . . . .                                                         | 68 |

| 4.20 | Mismatch Montecarlo simulation of signal to noise ratio. . . . .                                                             | 69 |

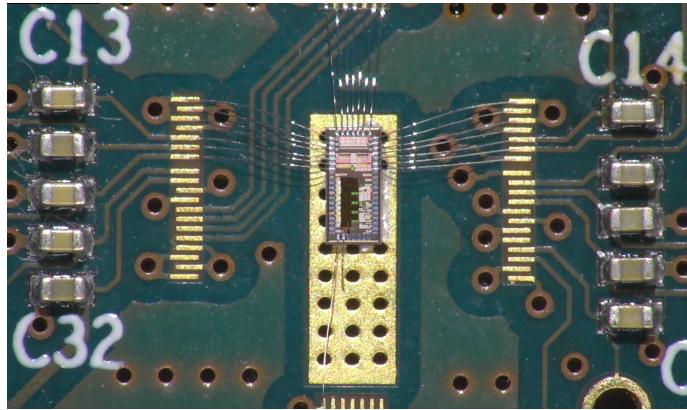

| 5.1  | Silicon ASIC v1 mounted and wire-bonded on the PCB. . . . .                                                                  | 72 |

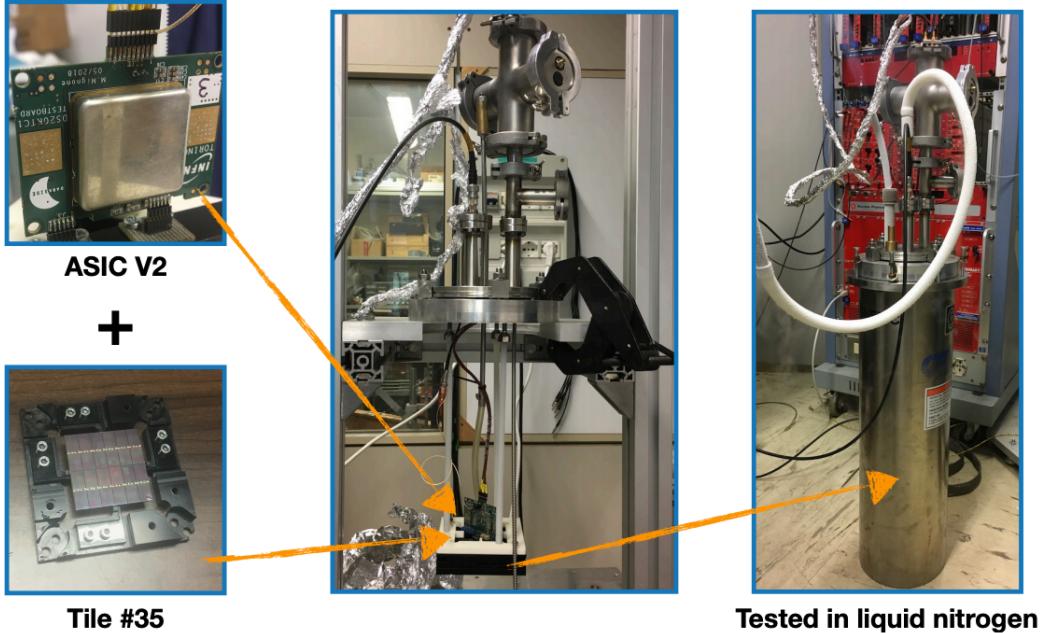

| 5.2  | Cryogenic setup implemented for the ASIC v1 test. . . . .                                                                    | 73 |

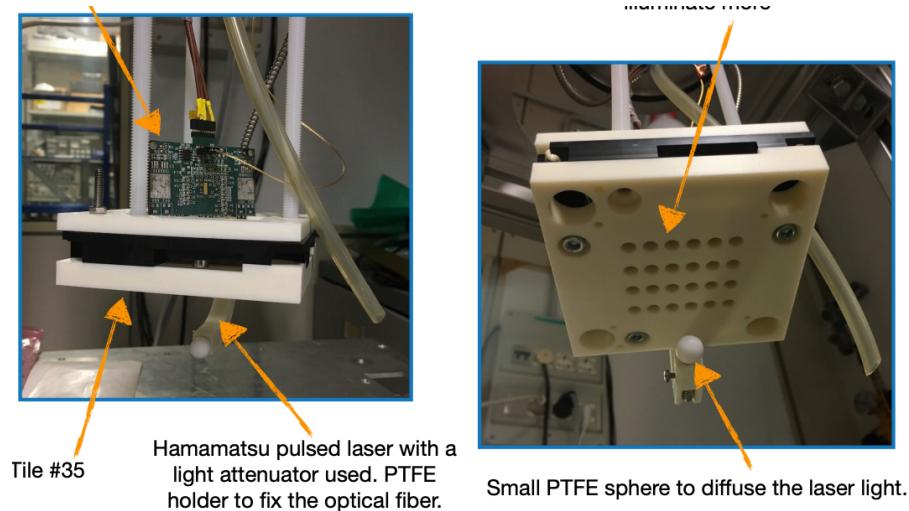

| 5.3  | Optical fiber location on the cryogenic electronics setup . . . . .                                                          | 74 |

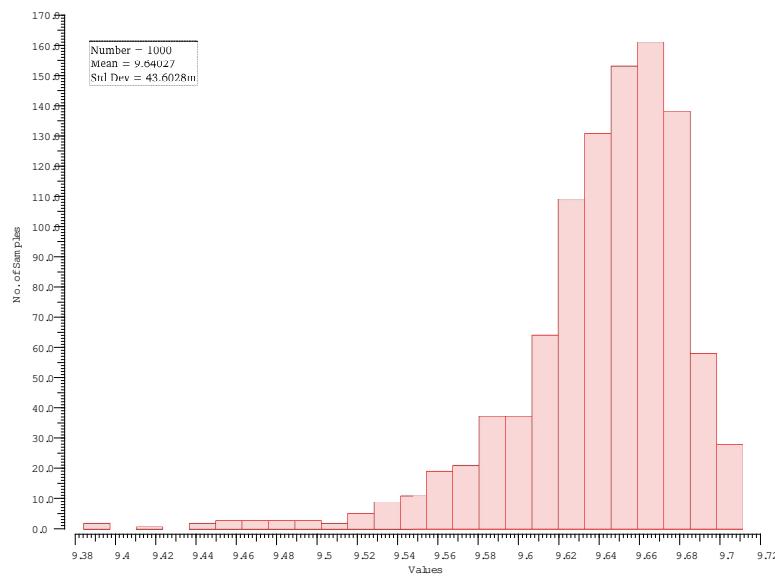

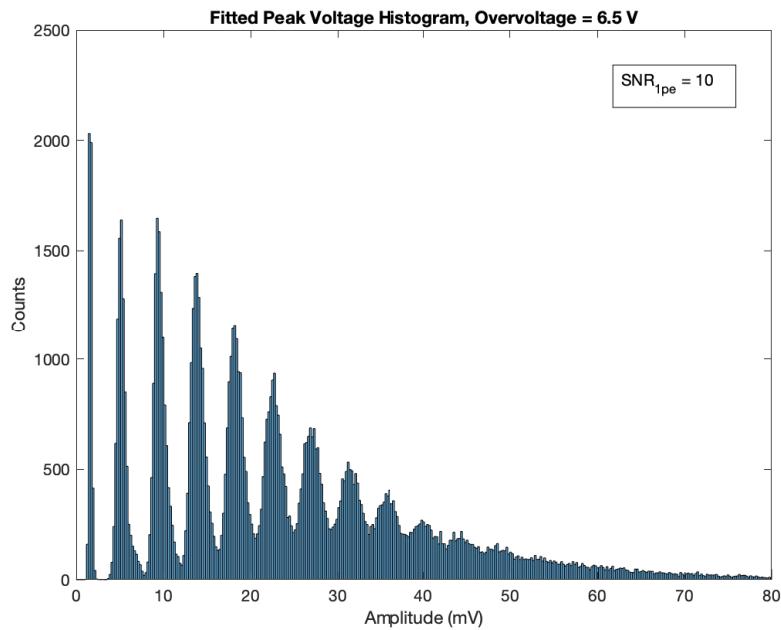

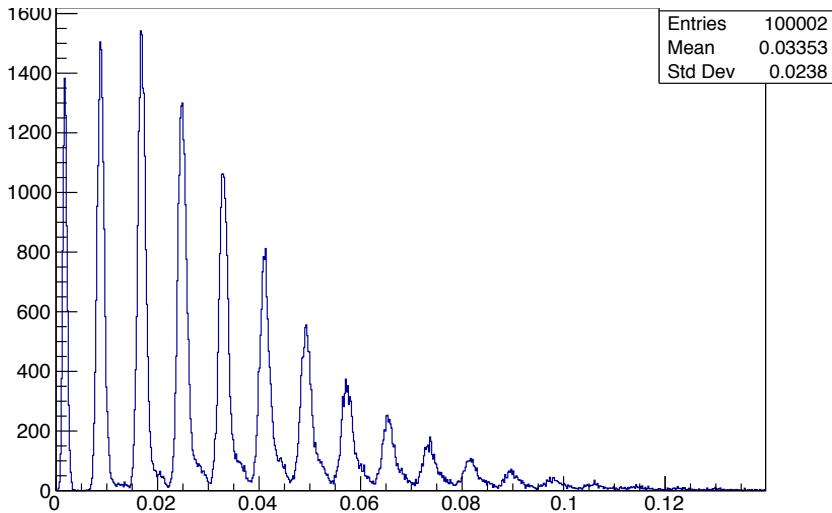

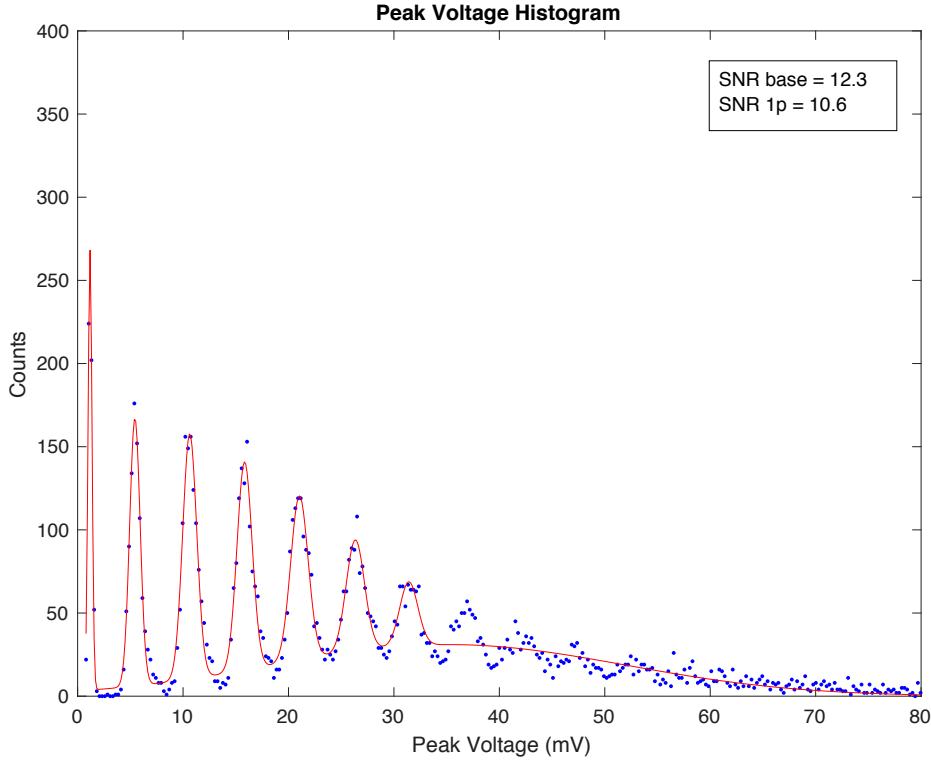

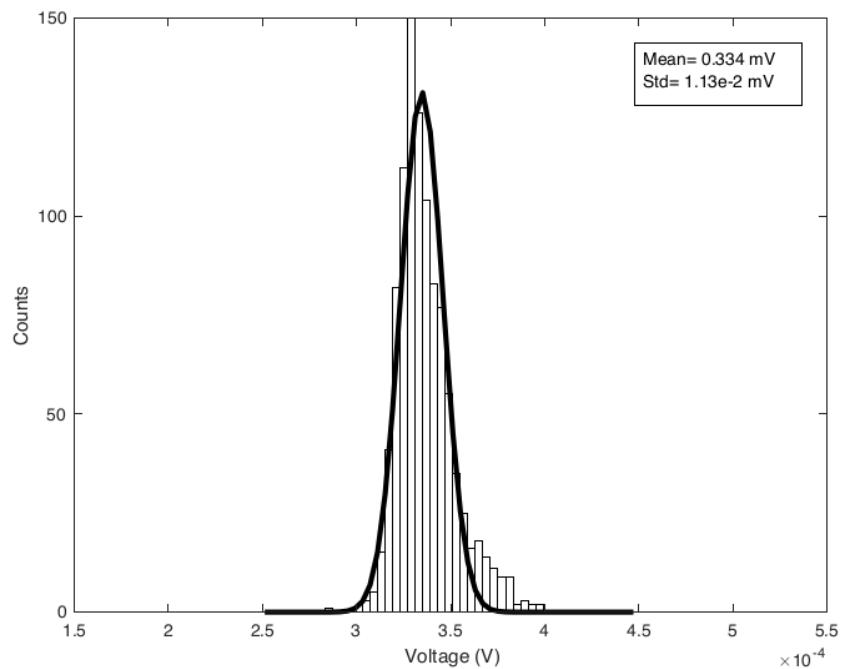

| 5.4  | Peak voltages histogram of ASIC v1 applying a 6.5 V of overvoltage to SiPM. . . . .                                          | 74 |

| 5.5  | Peak voltages histogram of ASIC v1 applying a 9 V of overvoltage to the new SiPM detector. The SNR is equal to 17.7. . . . . | 75 |

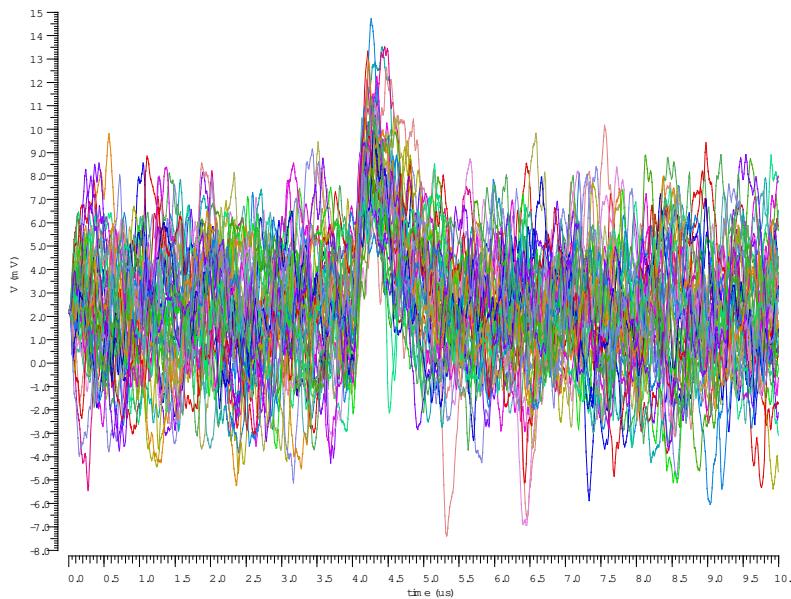

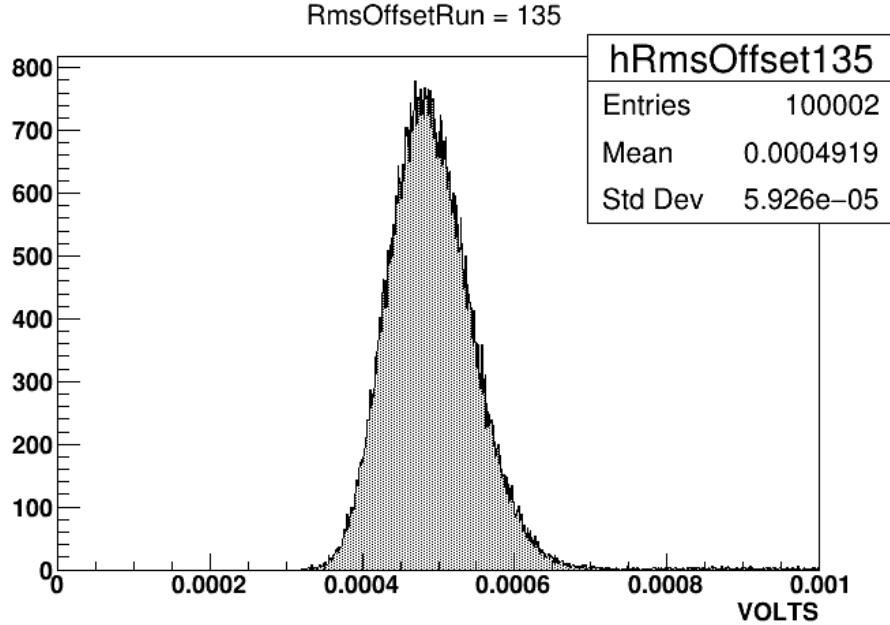

| 5.6  | RMS noise of the output baseline evaluated 6 us before the pulse. . . . .                                                    | 76 |

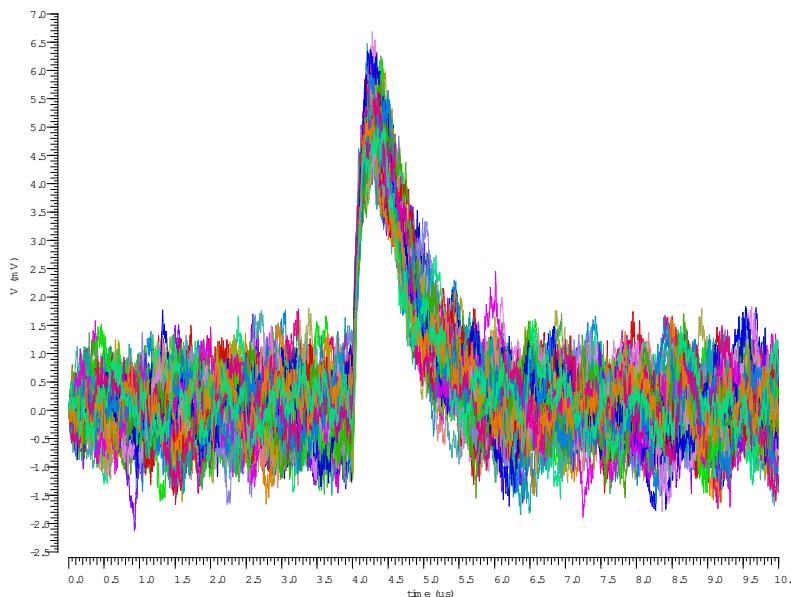

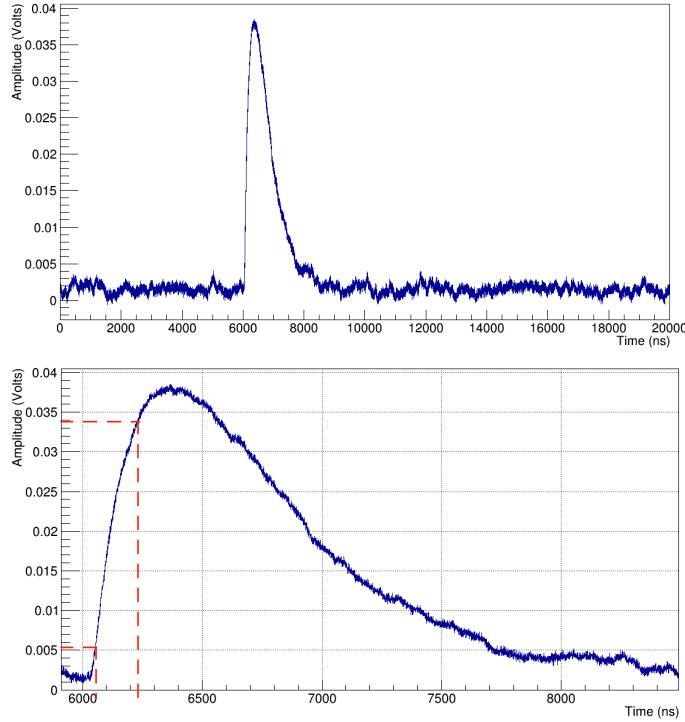

| 5.7  | Photo-electrons output signal (top), Zoomed photo-electron signal (bottom). . . . .                                          | 78 |

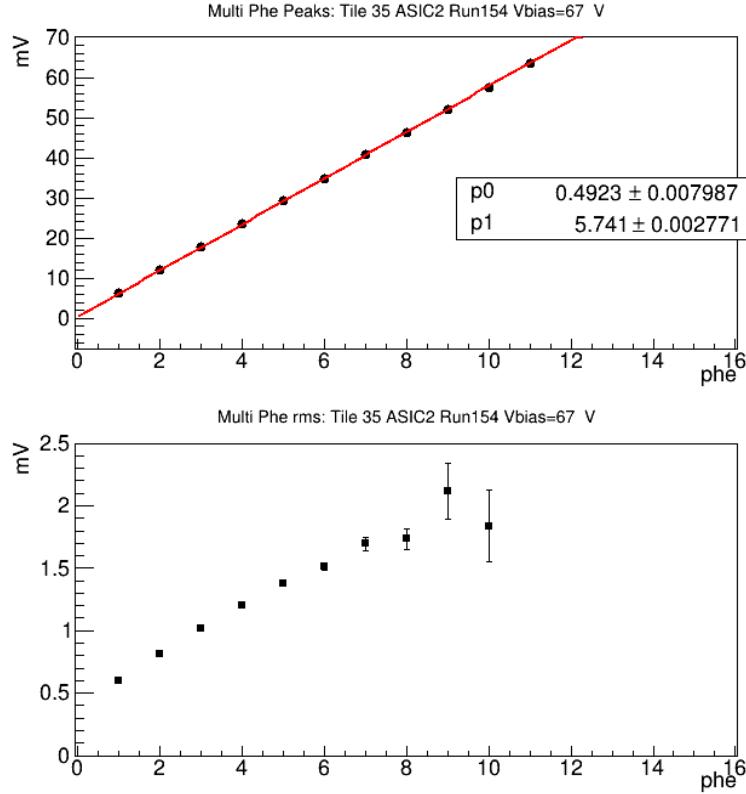

| 5.8  | Front-end electronic linearity (Top) and RMS noise variation (bottom) over number of photo-electrons. . . . .                | 79 |

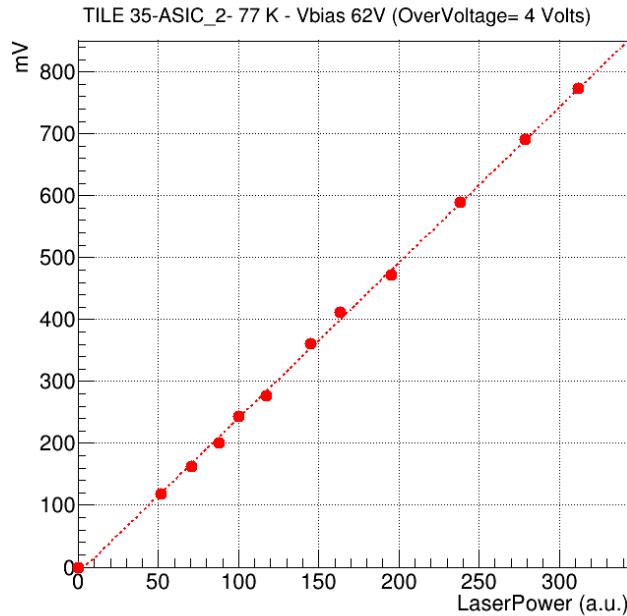

| 5.9  | Front-end electronic linearity and dynamic range over number of photo-electrons. . . . .                                     | 80 |

| 5.10 | Front-end electronic linearity (top) and RMS noise variation (bottom) over number of photo-electrons. . . . .                | 81 |

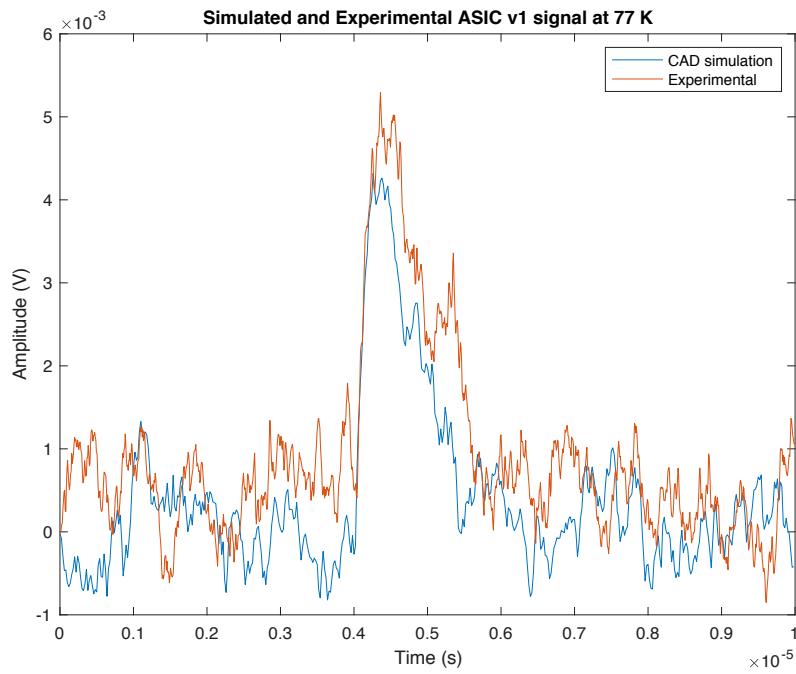

| 5.11 | Simulated and experimental output waveform at 77 K. . . . .                                                                  | 82 |

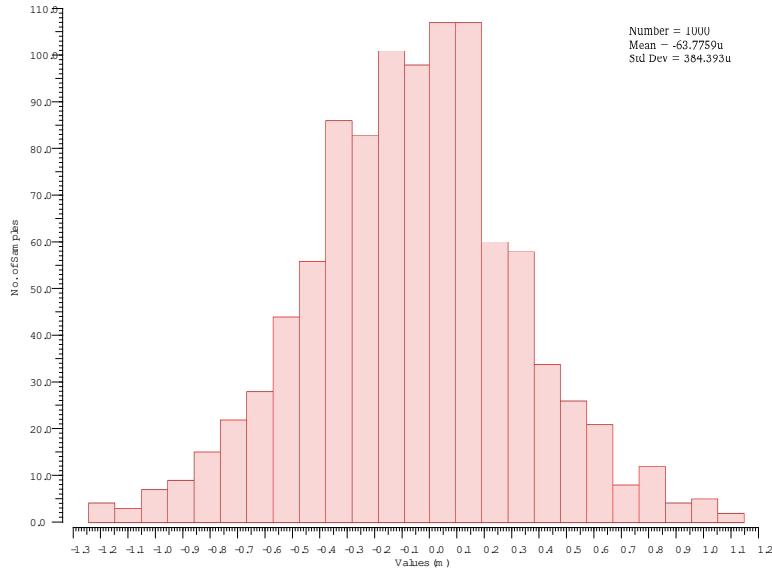

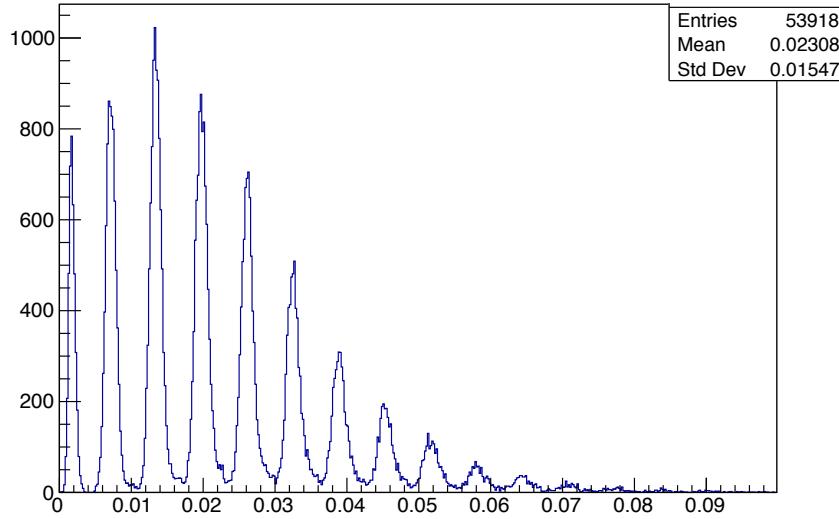

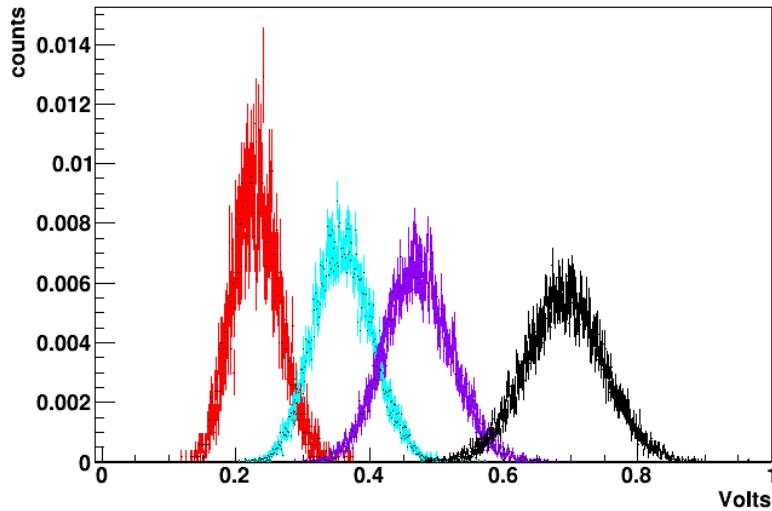

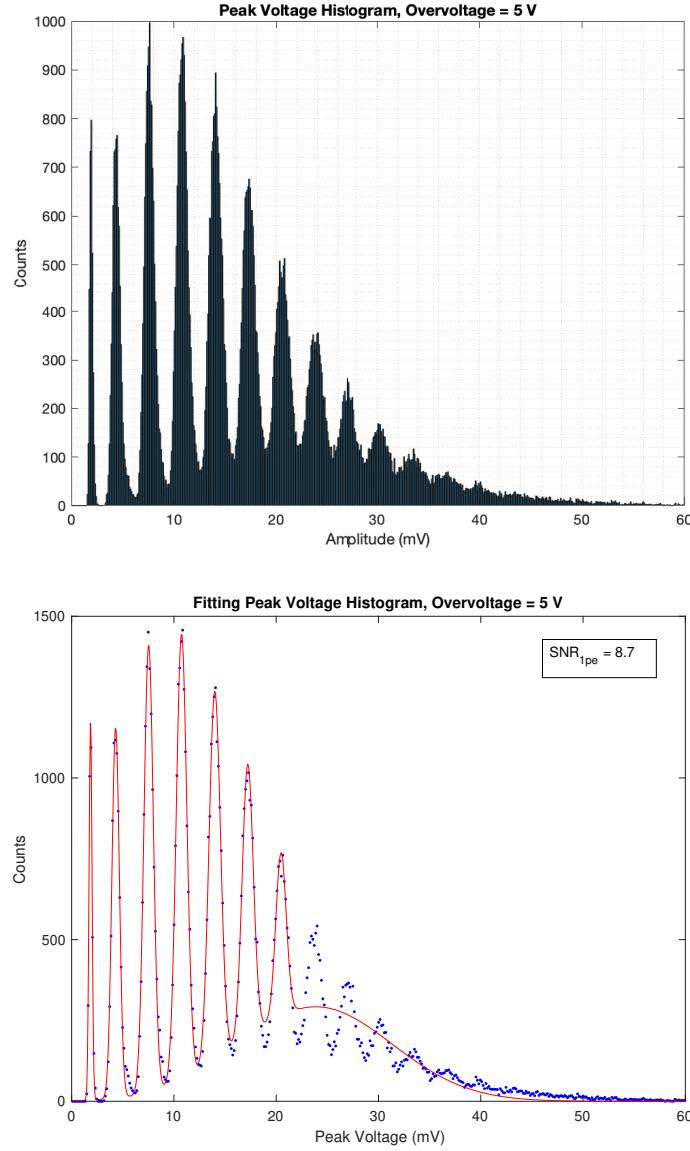

| 5.12 | Peak voltage histogram with a low laser intensity at 5 VoV (top), and fitted histogram (bottom). . . . .                     | 84 |

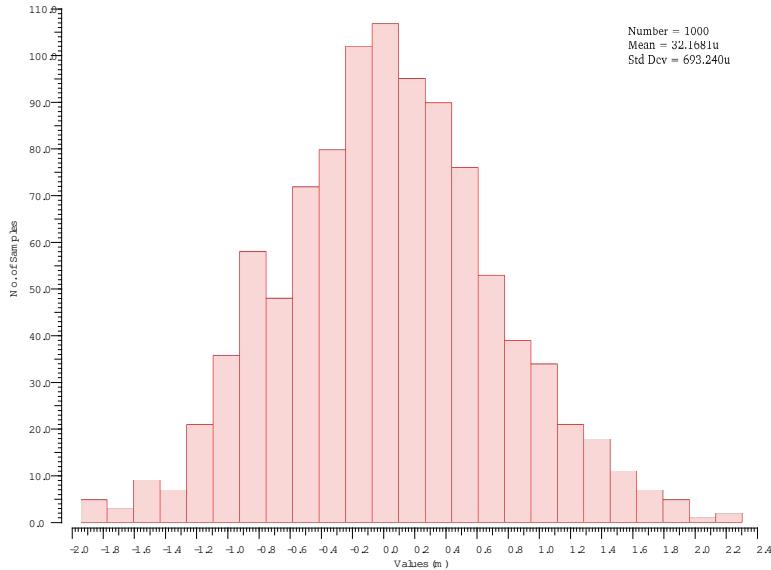

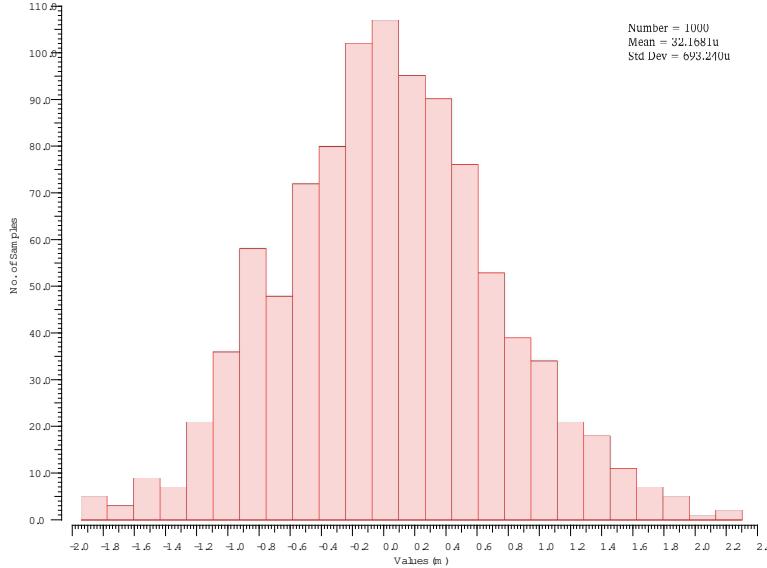

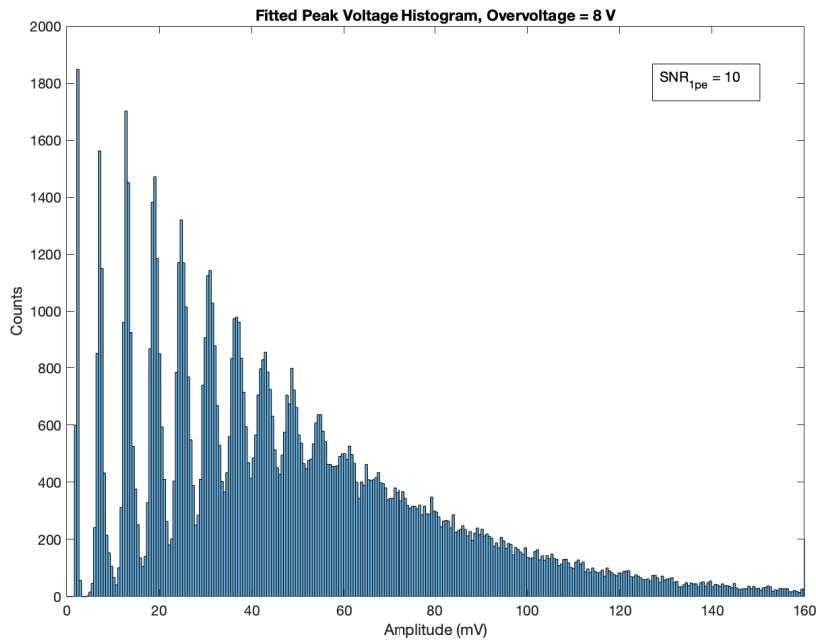

| 5.13 | Peak voltages histogram with a high laser intensity at 8 VoV. . . . .                                                        | 85 |

| 5.14 | Peak voltages histogram of ASIC v1 applying a 11 V of overvoltage to the new SiPM detector. . . . .                          | 85 |

| 5.15 | Front-end integrated electronics schematic plus an ADC and DSP block                                                         | 87 |

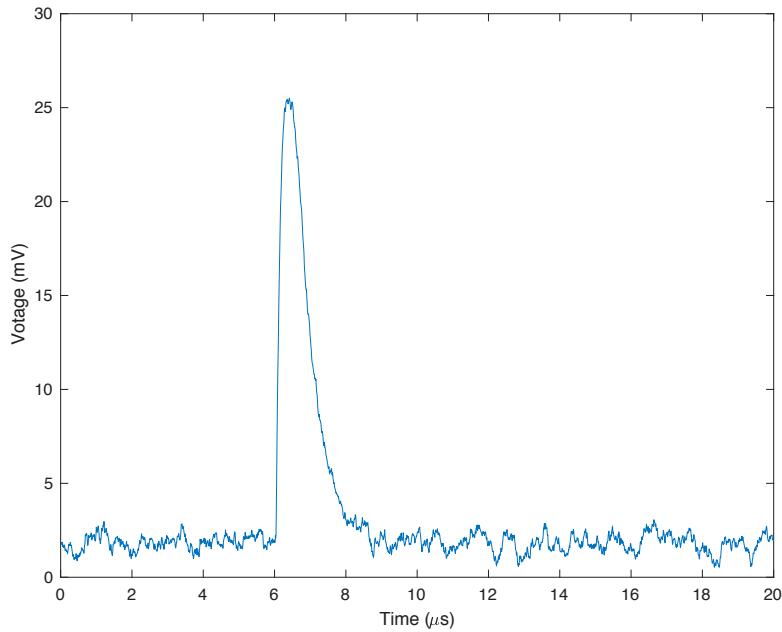

| 5.16 | Single photo-electron waveform before digitizing . . . . .                                                                   | 89 |

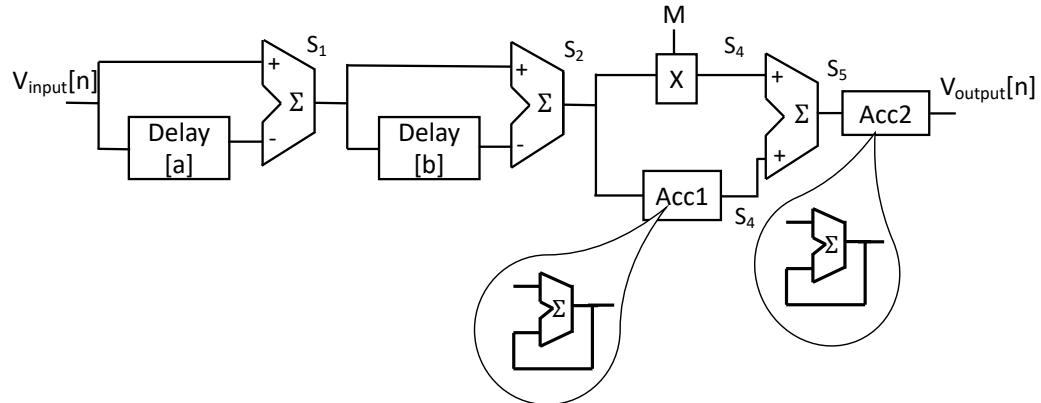

| 5.17 | Digital trapezoidal filter schematic . . . . .                                                                               | 89 |

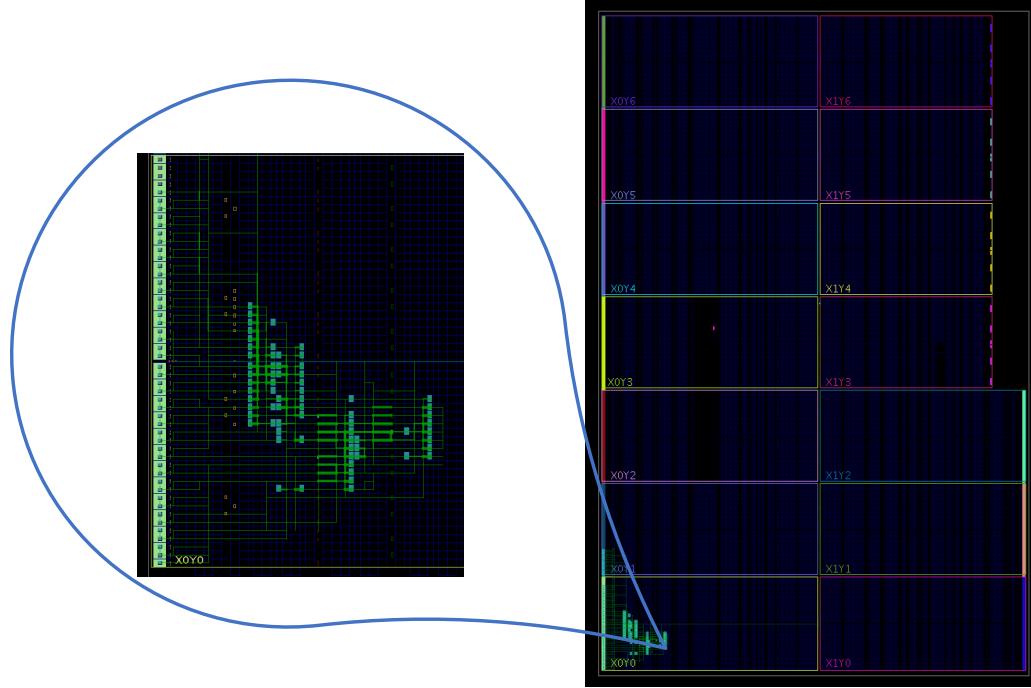

| 5.18 | Place & Route layout of the digital trapezoidal filter . . . . .                                                             | 91 |

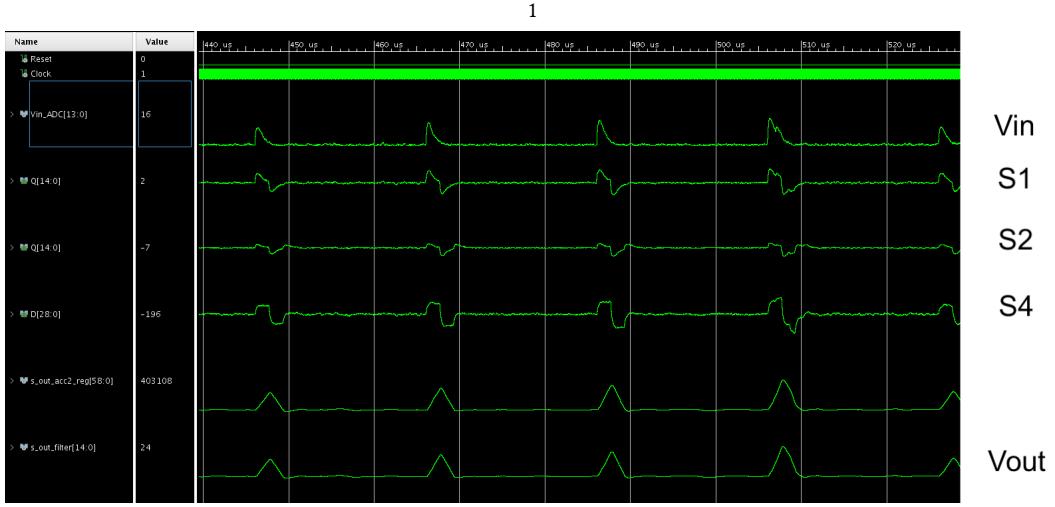

| 5.19 | Signal waveform produced on the output of each stage . . . . .                                                               | 92 |

| 5.20 | Peak voltage histogram of the front-end electronics without filtering. .                                                     | 93 |

|      |                                                                                                                                                                                        |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

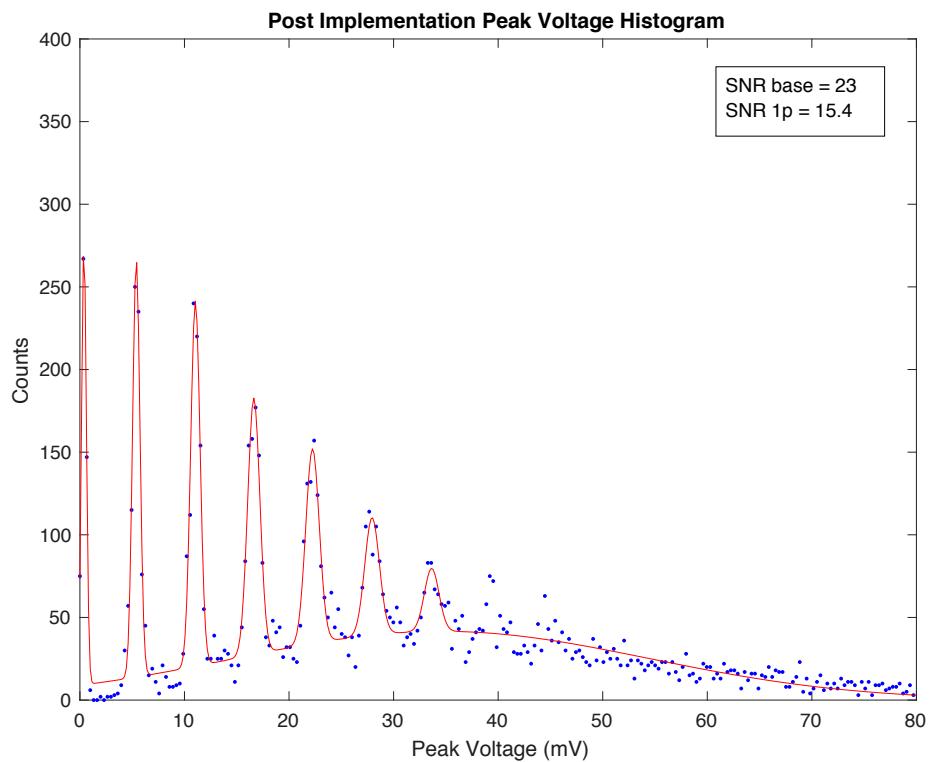

| 5.21 | Peak voltage histogram after trapezoidal digital filtering. . . . .                                                                                                                    | 94  |

| 6.1  | Full front-end for the readout of 24 cm <sup>2</sup> SiPM tile with differential outputs. . . . .                                                                                      | 97  |

| 6.2  | Transistor-level circuit of fully differential Folded Cascode with Common mode feedback. . . . .                                                                                       | 98  |

| 6.3  | Transistor-level circuit of output stage ( $V_{out_{neg}}$ and $V_{out_{pos}}$ ). . . . .                                                                                              | 103 |

| 6.4  | Layout structure of ASIC V2, including Front-End 1 and 2 . . . . .                                                                                                                     | 104 |

| 6.5  | Current mirror orientation to generate a good matching. . . . .                                                                                                                        | 105 |

| 6.6  | Single-ended output waveform of Front-End 1 (left) and Front-End 2(right) . . . . .                                                                                                    | 106 |

| 6.7  | Differential output signal of ASIC FE 1 (left) and FE 2 (right) at 77 K . . . . .                                                                                                      | 107 |

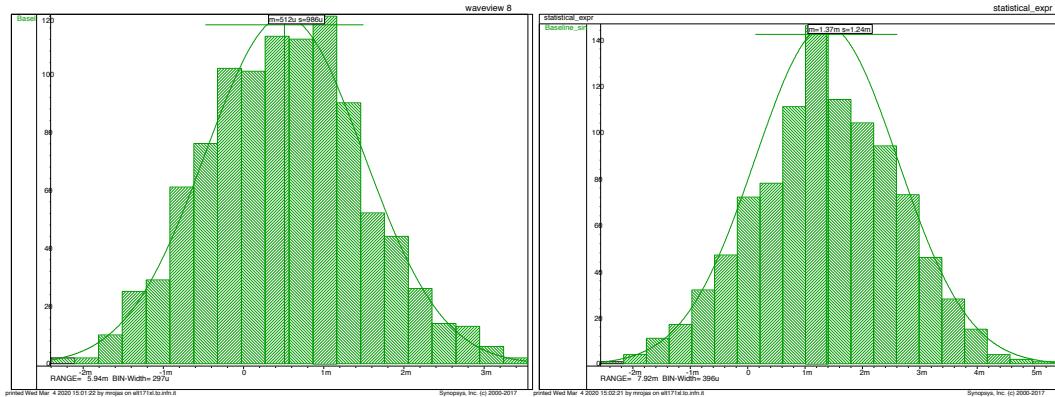

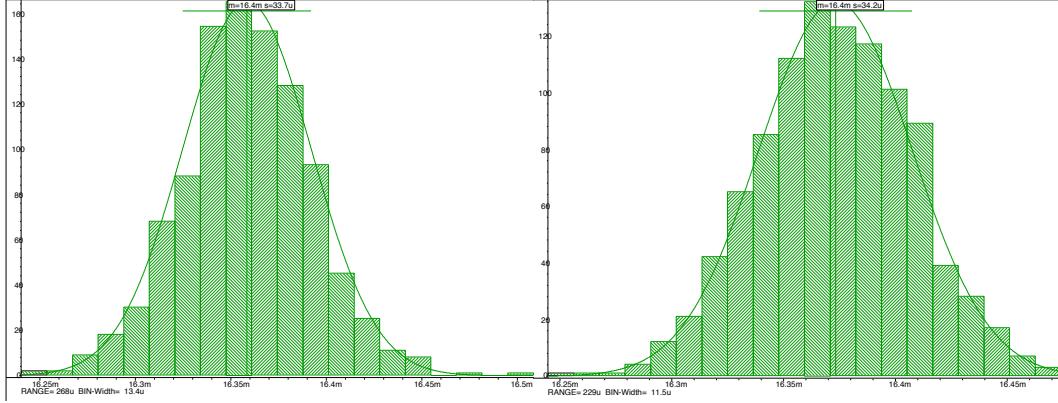

| 6.8  | Montecarlo simulation of input offset FE 1 (left) and FE 2 (right) at 300 K. . . . .                                                                                                   | 108 |

| 6.9  | MonteCarlo simulation of single-ended output baseline of ASIC FE 1 (left) and FE 2 (right) at 77 K. . . . .                                                                            | 108 |

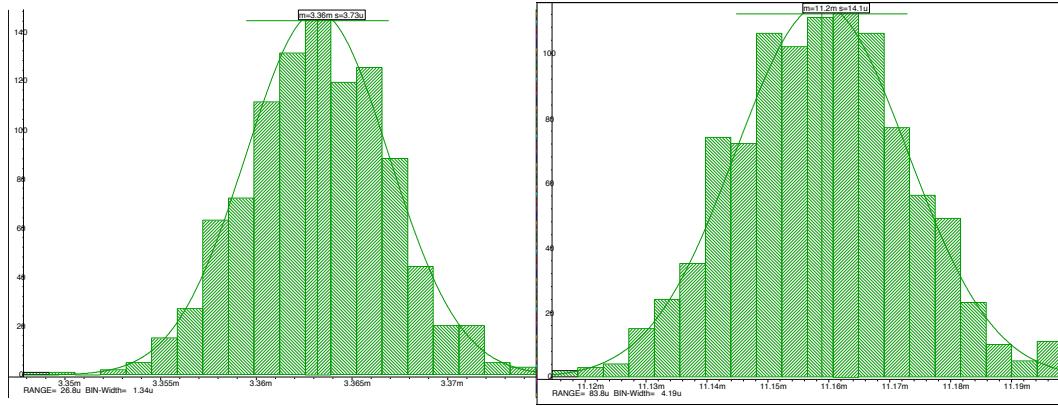

| 6.10 | MC single ended amplitude of Front-End 1 (left) and Front-End 2 (right) at 77 K. . . . .                                                                                               | 109 |

| 6.11 | Montecarlo simulation of differential output signal of Front-End 1(left) and Front-End 2 (right) at 77 K . . . . .                                                                     | 110 |

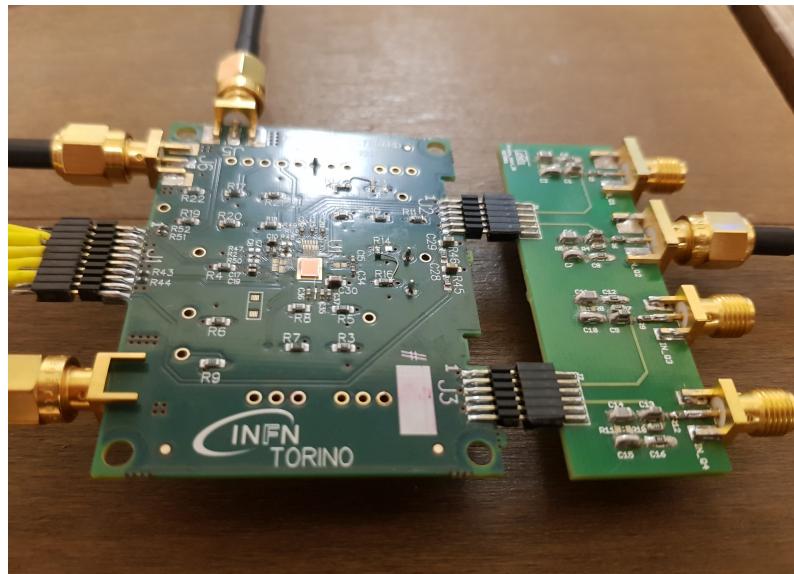

| 6.12 | Integrated circuit ASIC V2 and the charge injection board. . . . .                                                                                                                     | 111 |

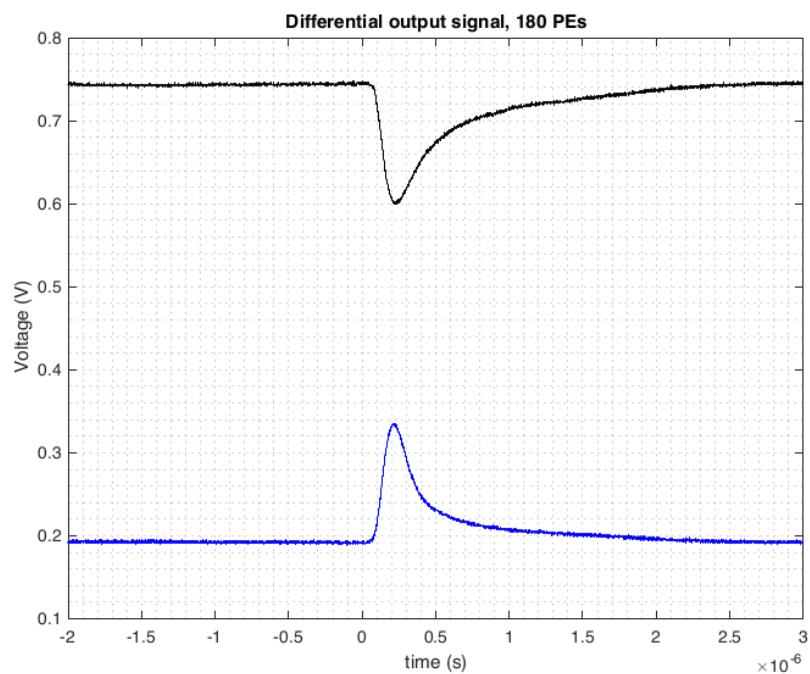

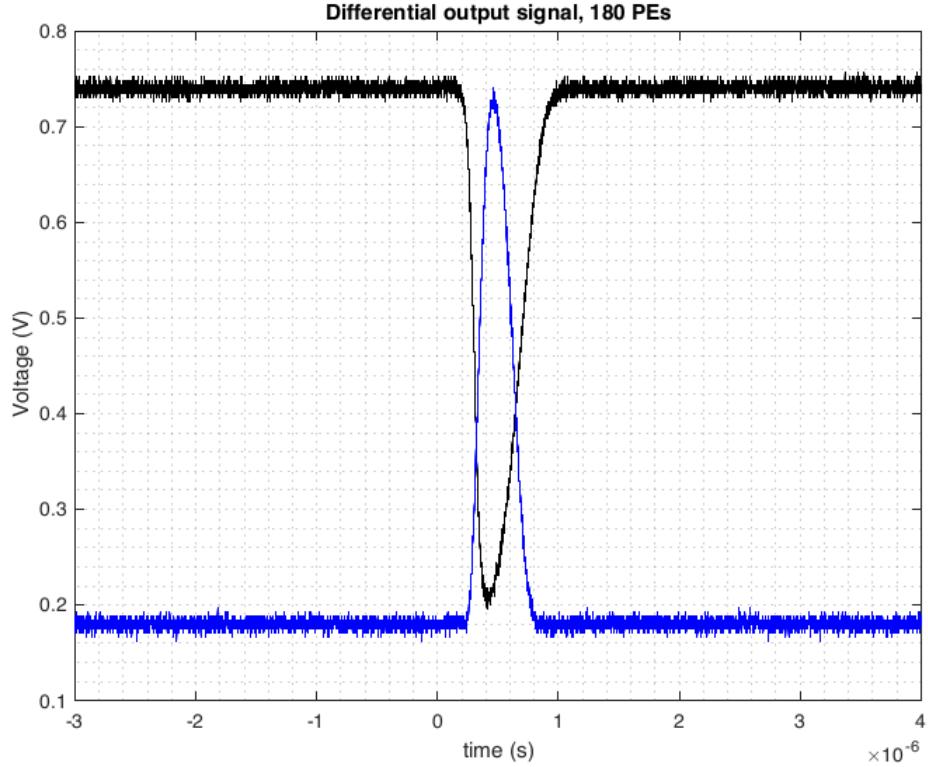

| 6.13 | Differential output signal using the charge injection board with equivalent charge of 30 PEs at 77 K. . . . .                                                                          | 111 |

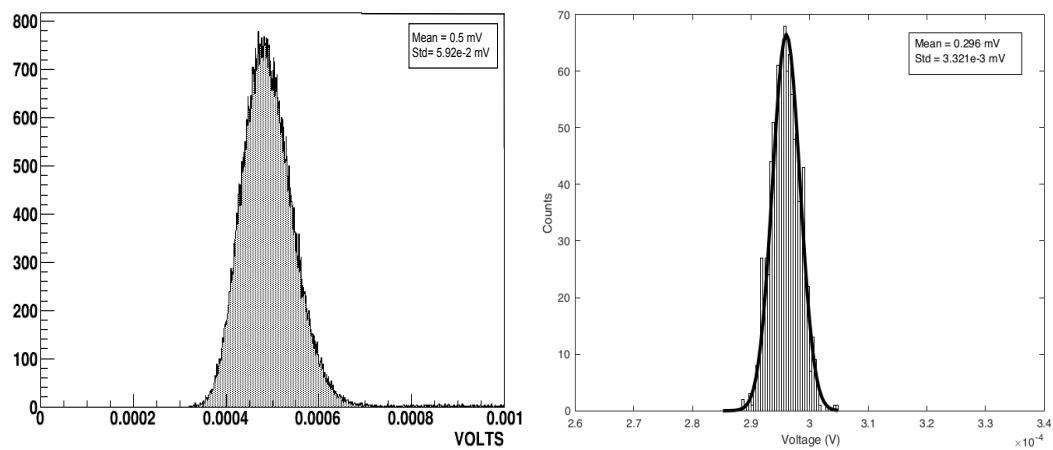

| 6.14 | Experimental RMS noise distribution of ASIC V1 structure (left) and ASIC V2 (right) at 77 K. . . . .                                                                                   | 113 |

| 6.15 | Experimental RMS noise distribution from differential output of ASIC v2 at Liquid Nitrogen temperature. . . . .                                                                        | 113 |

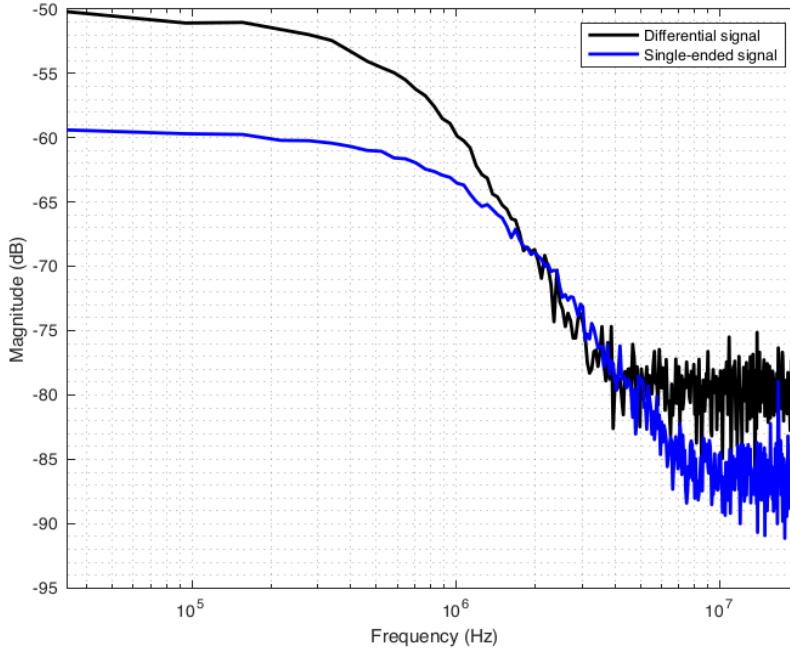

| 6.16 | Frequency spectrum of single-ended and differential output at 77 K. . . . .                                                                                                            | 114 |

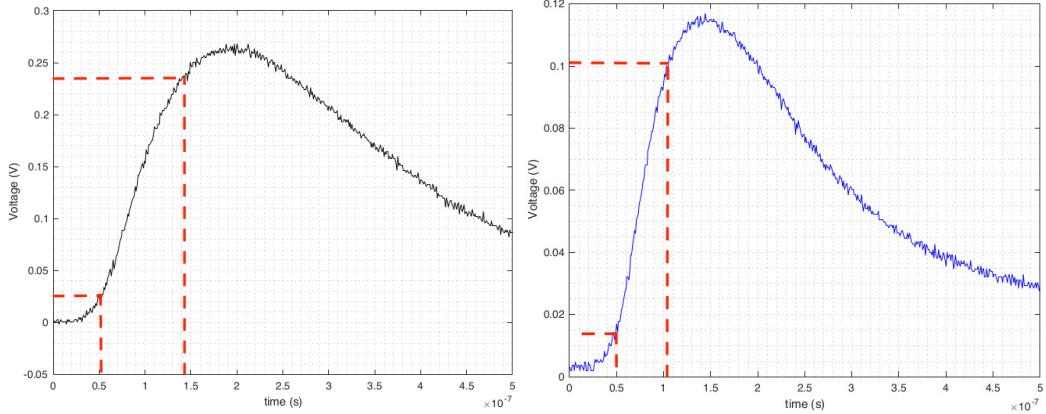

| 6.17 | Single-ended rising time of ASIC v1 (left) and ASIC v2 (right). . . . .                                                                                                                | 115 |

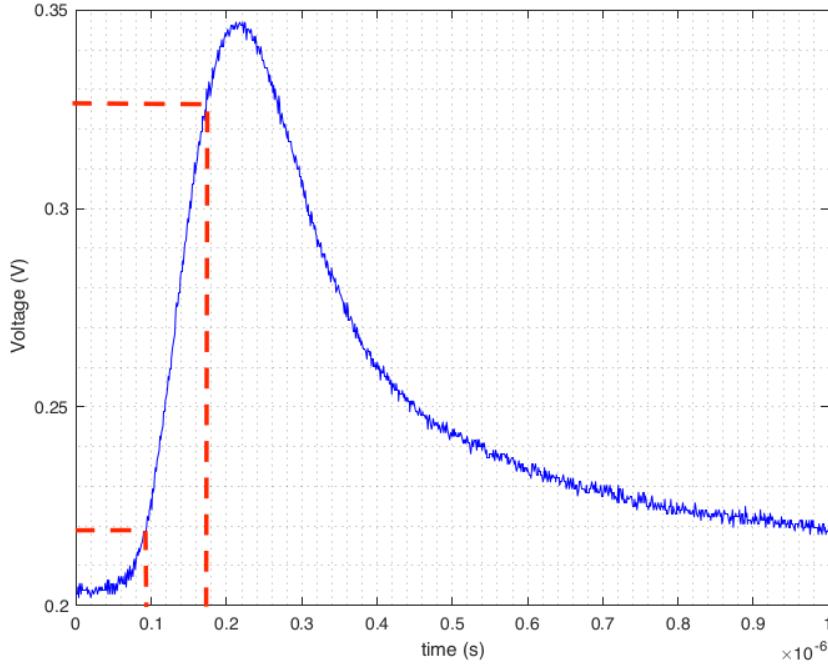

| 6.18 | Rising-edge time of ASIC v2 differential signal. . . . .                                                                                                                               | 116 |

| 6.19 | Differential output signal with the maximum number of PE on the input before saturation. This waveform provides the information about the dynamic range, in this case 184 PEs. . . . . | 117 |

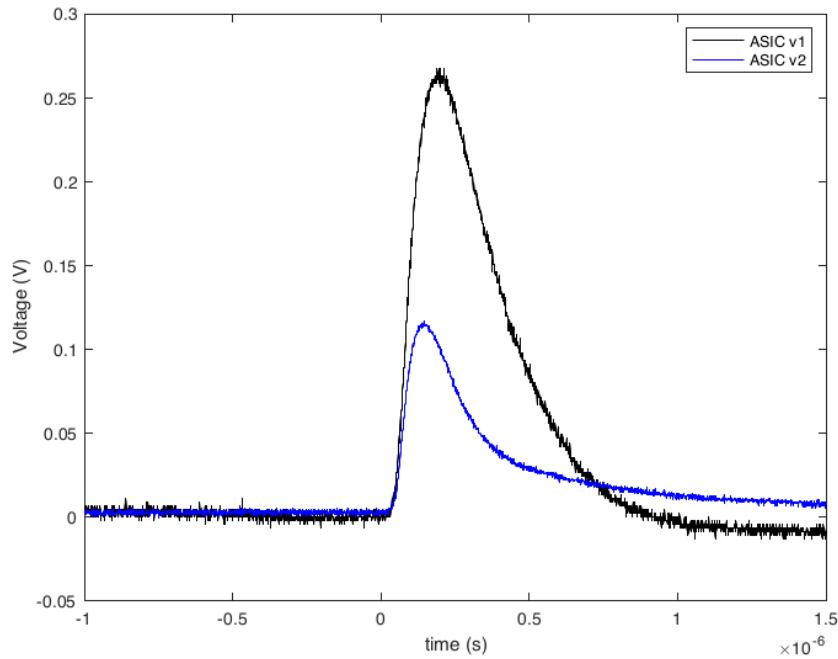

| 6.20 | Single-ended output signal of ASIC v1 and ASIC v2 at 77 K. . . . .                                                                                                                     | 118 |

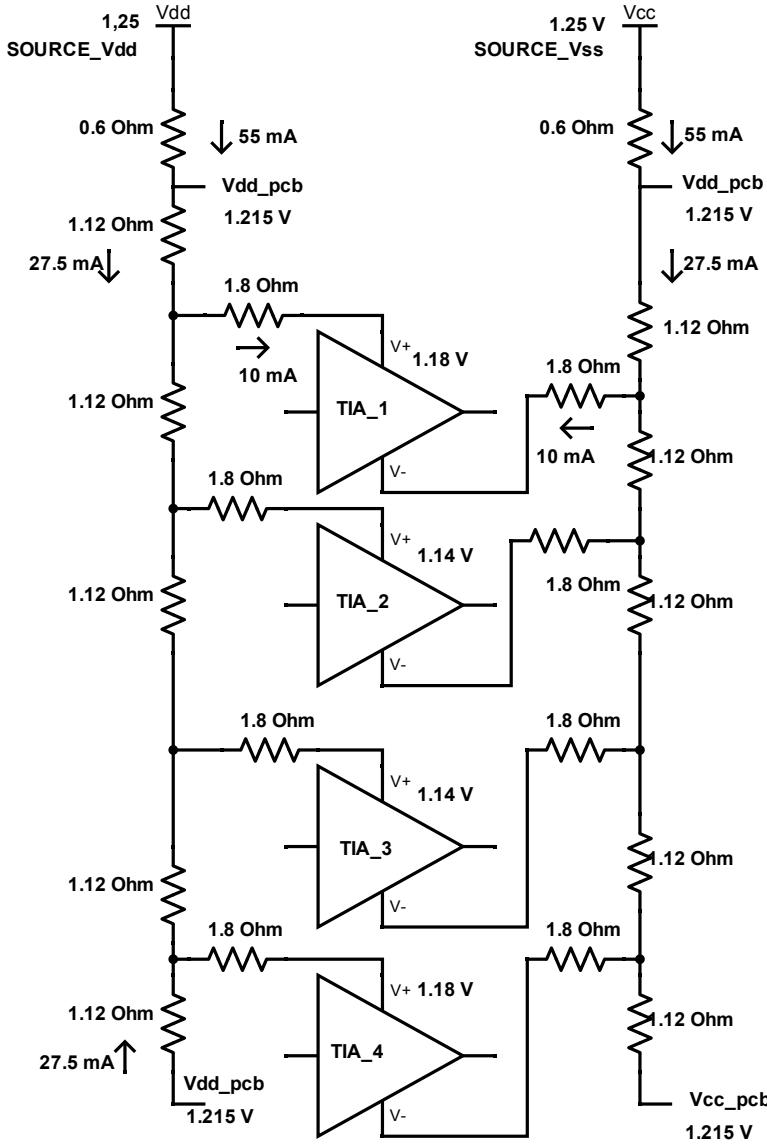

| 6.21 | Schematic of the IR drop over the power supply interconnection applying a Vdd=1.25 V. The metal resistances were computed from the layout structure. . . . .                           | 120 |

# Chapter 1

## Introduction

Historically speaking the cryogenic electronics has always provided attractive features to enhance many scientific and industrial processes. However, this has not been implemented widely in many field. In recent years cryogenic electronics have started to be considered in several research areas, such as deep space, underground astroparticle, imaging, and so on. Cold electronics allows high performances in terms of noise, current drive capability, bandwidth to be achieved due to the thermal interaction reduction at cryogenic temperatures. These advantages make cryogenic electronics a widely explored and developed area shortly.

The thesis is focused on the integrated cryogenic electronics design for the readout of large-area sensors ( $24 \text{ cm}^2$  Silicon PhotoMultiplier) with optimal performances in terms of the signal to noise ratio, dynamic range, and timing jitter. The cryogenic electronics points to improve the current photodetection system in neutrino and dark matter experiments since most of them implement the pre-amplification stage outside the cryogenic structure. Furthermore, many photodetection systems just readout a small-area sensor due to its large detector capacitance. The small-area detector requires a higher number of the readout electronic chains causing a small increment of radioactive impurity, but important for low-background experiments. The cryogenic prototype

The thesis covers the design and post-implementation simulations of a real-time digital filter. In this digital signal processing stage, the figure-of-merit is enhanced by more than 50 %. The thesis is divided into 5 sections.

Section 2 contains information about the most relevant projects where cryogenic electronics is implemented. Furthermore, describe the current photo-detection systems in underground astroparticle experiments. Section 3 presents the behavior of the CMOS technology and the Silicon PhotoMultiplier at a cryogenic temperature of 77 K.

Besides, the second section owns the experimental results of the CMOS extraction parameters. This step was crucial for the cryogenic electronics design. Section 4 described the transistor-level design and mismatch optimization of ASIC v1. The chapter also includes post-layout and Monte-Carlo simulation. The experimental result of ASIC v1, as the real-time digital filter implementation is described in Section 5. The section shows a couple of peak voltage histograms to describe the cryogenic front-end efficiency. Finally, the last chapter describes a new front-end prototype to readout large-areas sensors, including a single-end to the differential converter. Besides, the new prototype implements a different CMOS technology in comparison to ASIC v1. The section includes preliminary results obtained with a charge injection board, instead of the SiPM.

## **1.1 Need for Underground Astroparticle experiment**

The underground astroparticle physics experiments present two structures, which require cryogenic electronics, such as the Time Projection Chamber (TPC) and the VETO system. The experiment detector operates with noble gas elements, as a result, the element determines the operation temperature of the TPC and VETO. Mainly the astroparticle experiments utilize the Liquid Argon and Liquid Xenon as the scintillator. Hence, cryogenic electronics are required to work at 87 K or 175 K.

## **Chapter 2**

### **Key developments in cryogenic electronics**

Cryogenic electronics design has been implemented in many technological and scientific research in recent years. This chapter illustrates the most important experiments, which the cryogenic electronics contributions have been crucial for its development. The research areas include quantum computing, the deep space mission, fast imaging, and underground astroparticle experiments.

## 2.1 Cryogenic electronics for general purposes

In recent decades the cryogenic electronics has been applied in several research areas due to its low-temperature advantages. The most well-known research fields are the readout of the superconductive astronomical detectors [1], spacecraft project [2], the operation of qubits in the quantum computers [3] and astroparticle physics experiments [4]. In this study, just space and deep space application, quantum computing, the infrared fast imagining will be deepening in details.

### **The emerging cryogenic space and deep-space application**

Cryogenic electronics has become an attractive environment for space and deep-space projects due to its thermal noise advantages. The cold electronics has been implemented within international projects, such as Lunar and Martian robotics [5] and deep space antenna (Figure 2.1). In the Lunar robotics, the temperature conditions are established down to 43 K due to the Lunar shadowed polar craters [6]. Furthermore, the cryogenic devices must consume a restricted amount of available power due to the limitation of a power supply within the space. Initially many researches have focused on the cryogenic performance of commercial electronics to develops a cryogenic ASIC prototype [7].

As a first step, the reliability of the technologies, such as CMOS or SiGe, has been tested in order to guarantee a high functionality along the time before a full architecture implementation.

For instance, a cryogenic Lunar electronics [6] implements a commercial  $0.5 \mu\text{m}$  SiGe HBT BiCMOS technology. The technology has demonstrated adequate reliability under specific work conditions. The commercial SiGe HBT has sufficiently indicated advanced performance to be considered, as cryogenic technologies to the Lunar space missions. However, the commercial technology requires an own bias and loading changes to make them work at a required cold temperature [7].

On the other hand, CMOS technology develops an optimal carrier mobility increment, current drive capability, thermal noise reduction, and a higher transit frequency. The previous characteristics make the CMOS an attractive technology at cryogenic temperatures. Nonetheless, its flicker noise increases due to the oxide layer between the metal gate and the active conducting channel [8]. The low-frequency noise approximately presents a rise at temperatures lower than 40, affecting the experiments at Helium temperature (4.2 K). Furthermore, CMOS reliability has demonstrated to achieve a lifetime more than 20 years [9].

Figure 2.1: Deep space antenna for the future space missions of the European Space Agency (ESA). Picture taken from ESA

The previous technologies have been implemented in any type of electronic circuit. For instance, one of the required cryogenic circuits for space application includes the low noise amplifier (LNA). In the European space agency (ESA), the cryogenic LNA has been implemented for the deep space mission through the ESA technology research program [10]. In this RF project, the cryogenic conditions are necessary to improve the signal-to-noise ratio, which allows the deep space signals to be recognized. At room temperature, the high thermal noise in the receiver makes the signal recognition a complex or an almost impossible process. Thus, the deep-space antenna demands a cryogenic front-end architecture, as shown within Figure 2.2. In this circuit, the LNA was designed by a cryogenically cooled High Electron Mobility Transistor technology (HEMT).

### Quantum computing application

Quantum computing (QC) is one of the most attractive projects within these decades. The project has caused a relevant interest from the important electronics industries, such as IBM [12], Intel [13], and for technological industries, such as Google [14] and Microsoft [15]. Quantum computing owns engaging features to be applied in several areas, such as machine learning in which a computer must process the petabytes of unanalyzed data. In the biomedical simulation, QC will allow the complex molecular

Figure 2.2: Fully schematic of the front-end electronic circuits for space missions. Picture taken from [11]

structure to be created, simulated, and modeled much faster and efficiently. In financial service, the QC could develop complex financial modeling and risk management.

Currently, the computing systems are manipulated by ordinary computers, which implement bits (1s or 0s) as the data unit. The quantum computer implements a quantum mechanical process to control the information. In other words, this new computing method realizes calculations supported by the probability of an object's state before it is measured. Hence, the basic containers of information are changed by the quantum bit or qubit [16]. The quantum units require to be operated at deep cryogenic temperatures in order to remain coherent for a short time [8]. Otherwise, the thermal energy in a qubit could give a motion enough to decoherence any quantum state that has been established previously [17].

In the QC field, the cryogenic electronics may be built by the MOS technology or by the HEMT. The MOS technology is well-known to operate at 4.2 K, therefore the CMOS

could in principle be employed in a fault-tolerant loop [18], [19]. CMOS operation at 4.2 K provides optimal results in terms of transit-frequency, despite the increase of the slope factor and flicker noise at deep cryogenic temperatures [3],[8].

On the other hand, the HEMT technology can work with a low flicker noise at 4.2 K. This technology is fabricated on a heterostructure with a high purity material interface. Experimentally the equivalent input noise voltage of HEMTs at low frequency and Helium temperature is inversely proportional to the square root of their input capacitance  $C_{gs}$  [20]. Furthermore, the HEMT transistor can achieve a transit-frequency around 160 GHz [21].

A cryogenic ASIC for quantum computing additionally requires high tested reliability and functionality of each circuit implemented in a prototype. For instance, Figure 2.3 described a complex cryogenic full system prototype working on deep cryogenic temperatures.

Figure 2.3: Fully schematic of the front-end electronic circuits for controlling and measuring spin qubits. Picture taken from [22]

### Imaging application

Imaging application has been popular for the usage of cryogenic electronics. The infrared fast imaging presents a system architecture called linear imager, or in this case, an infrared cryogenic imager. This architecture is formed by a row of hundreds or thousands of IR sensors. In many fast imaging projects, the IR sensors are connected to front-end electronics, which operates at a cryogenic temperature of 77 K. In other words, the IR sensor is monolithically on top of the CMOS read-out circuit [23]. Figure 2.4 illustrates an infrared cryogenic imager including the IR sensor, Read-Out Integrated Circuit (ROIC), and a grid of the active-pixel sensors, which connect the ROIC and IR sensor.

Figure 2.4: CMOS APS Circuits for Hybrid Cryogenic Infrared Fast Imaging schematic.

Picture taken from [23]

The Active-Pixel Sensors (APS) are conformed by a silicon photodiode integrated with its readout electronics. The APS works efficiently at cryogenic temperatures of 77 K, 60 K, and 40 K. Inasmuch as cryogenic electronics implements a simple 4-transistors architecture. This topology makes the transistor parameter variation much easier to control at cryogenic temperatures. Furthermore, it provides high reliability at low temperatures due to the circuit simplicity [24].

### **Military aircraft application**

The battle shift and the aircraft in the future will likely exploit the benefit of the cryogenic technologies by implementing cryogenic power converter in generators and motors [25]. This application utilizes the performance benefits of semiconductor power devices at low temperatures. Then, one expects a significant gain in terms of energy dissipation, higher cut-off frequencies, and so on. This could reduce one of the biggest problems of the aircraft related to the electric power consumption and dissipation.

## 2.2 Cryogenic electronics for underground astroparticle experiments

One of the most important cryogenic applications has been underground astroparticle experiments. These physics projects implement structures for astroparticle detection with an operating temperature of 175 K (Liquid Xenon) and 87 K (Liquid Argon). The searched astroparticle has been the neutrinos and the weakly interactive massive particle (WIMP).

Many countries have been collaborating within international frameworks for astroparticle researches. The underground experiments have been divided into two research areas. Firstly, the neutrino searching, which is conformed by couples of experiments, such as the Deep Underground Neutrino Experiment (DUNE) and the Enriched Xenon Observatory (EXO). Both DUNE and EXO experiments operate at a temperature of 87 K. Secondly, the dark matter searching, which is integrated by several experiments, however, only two of them will be mentioned in this study. The experiments are the XENON and DarkSide project.

### 2.2.1 Deep Underground Neutrino Experiment

Neutrino is an elementary particle that may hold the key to solving the great mysteries of nature, and this leads to a great effort to understand its role in the universe. The Deep Underground Neutrino Experiment (DUNE) realizes observations through a nucleon decay detector.

A single-phase detector prototype has been designed and implemented in the DUNE framework [26]. This has been the first DUNE 10-kt fiducial mass far detector module with total liquid argon (LAr) mass of 0.77 kt. The ProtoDUNE detector was built at CERN and has become the largest detector for the DUNE experiment so far. ProtoDUNE-SP Far Detector prototype consists of a TPC, a cryogenic electronics (CE), and a Photon Detection System (PDS), implemented all inside a cryostat full of Liquid Argon (LAr).

The cryogenic electronics of the DUNE single-phase TPC is mounted directly to the sensor, therefore the parasitic elements and noise due to the long interconnections are minimized considerably, in comparison to the coaxial connection between the sensor and its corresponding readout electronics outside the cryostat. The cold electronics of ProtoDUNE presents several channels readout with an amplifier, a shaper, a digitizer, a buffer, and a multiplexer circuit [27].

The protoDUNE owns an Anode Plane Assemblies with 2,560 channels readout by 20 Front-End Motherboards. The motherboard architecture, illustrated in Figure 2.5, presents the cryogenic front-end circuit readout a 4-groups of 3 SiPM of  $6 \text{ mm}^2$  with a detection efficiency of 41 %. The total sensor readout takes an area of  $72 \text{ mm}^2$  [27].

Figure 2.5: ProtoDUNE cryogenic electronics architecture. Picture taken from [27]

## 2.2.2 Enriched Xenon Observatory

The Enriched Xenon Observatory (EXO) is an experiment in particle physics aiming to detect a neutrino-less double beta decay. The double-beta decay is a second-order weak transition in which two neutrons simultaneously decay into two protons. The EXO experiment tries to observe the hypothetical neutrinoless mode ( $0\nu\beta\beta$ ). The search for  $0\nu\beta\beta$  is recognized as the most sensitive probe for the Majorana nature of neutrinos [28], [29].

EXO-200 is a 200-kg detector using Liquid Xenon (LXe). It was designed as a baseline for the future and a larger double beta decay detector. EXO 200 implements an LXe TPC at an operating temperature of 167 K. In this detector, the front-end electronics are

located outside the cryogenic environment and connect to the sensor by cabling. Each channel circuit (a total of 300 channels) is conformed by a low noise charge amplifier, two shapers (integrator and differentiator) stages. Next, the front-end feedthrough a sample-and-hold circuit and a 12 bit, 1 MS/s Analog to Digital Converter [30]. The Front-end architecture, shown in Figure 2.6, readout the photomultiplier tube (PMT).

Figure 2.6: TPC biasing and readout electronics systems of EXO-200. Picture taken from [30]

### 2.2.3 XENON

XENON is a dark matter experiment to detect the nuclear recoils ensuing from the dispersion of the Weakly Interacting Massive Particles (WIMPs) within Liquid Xenon (LXe) [31]. The Xenon experiment has evolved over the years to increase the detection resolution (sensibility). The target of the resolution improvement is to detect the ever-elusive dark matter. The experiment starts with Xenon100, which contains 62 kg of LXe in a time projection chamber (TPC) [31]. Next, the project expected to Xenon1t with a TPC filled with 1 ton of LXe [32]. The last proposal is the construction of the XENONnt to operate a total of 8.3 tonnes of liquid xenon to search for the dark matter particles.

Experiments, such as Xenon100 and Xenon1t, has implemented the photomultiplier tube (PMT) with enhanced response in the vacuum ultraviolet (VUV) regime. Besides, the PMT presents a high photoelectron collection efficiency and high performance at cryogenic temperatures.

Xenon100 presents a data acquisition system that amplifies the 242 PMT signals by a factor of 10 using commercial Phillips 776 NIM amplifiers and then digitized by CAEN VME V1724 Flash ADCs with 10 ns sampling period, 14-bit resolution, 2.25 V full scale, and 40 MHz bandwidth. The front-end electronics (Figure 2.7) implements commercial components, which require additional filters to reduce the typical wide bandwidth of the commercial amplifier. This prototype locates the amplifiers and ADCs in a room temperature environment through 12 m PTFE-coated RG-196 coaxial cables.

On the other hand, the Xenon1t presents an identical front-end structure of Xenon100. The front-end electronics connected to the PMT through a coaxial cable perform a total gain equal to 10 within a warm data acquisition [33]. Finally, the XENONnt project is currently in construction with 496 PMTs for signal read-out.

Xenon dark matter experiment does not include the read-out electronics within the cryogenic environment close to the detector. Hence, the detection efficiency may be reduced due to the physical distance between the sensor and the reading electronics.

Figure 2.7: Data acquisition schematic for all 242 PMT realized in XENON100 experiment. Picture taken from [31]

## 2.2.4 DarkSide 50

DarkSide-50 (DS50) is classified as a dark matter experiment for searching the weak interactive massive particles (WIMPs). DS50 was the first physics detector of the Dark-Side program. The experiment implements a TPC of 46 kg active volume of Liquid Argon, which has produced the first WIMP search results using a low-radioactivity underground argon [34].

DS-50 contains 38 3" PMTs distributed on the top (19 PMTs) and on the bottom (19 PMTs) of the TPC [35]. The low-gain front-end electronics were mounted directly on the PMT sensor inside the cryogenic environment [36], to reduce the parasitic connections and losses generated by cabling connected to a warm amplification. The cold electronics (Figure 2.8) was designed using a commercial JFET, and a figure of merit to generate a low-noise in the input JFETs and output drive transistor.

The output signal from the cryogenic front-end is guided to the warm data processing area. In this structure, the output analog signal is buffered and digitized, as shown the Figure 2.9. The DS-50 has been used as a baseline for DarkSide20K. The last and bigger prototype of the Darkside collaboration.

Figure 2.8: Block diagram of the DarkSide 50 Front-End-Module. Picture taken from [36]

Figure 2.9: Block diagram of the DarkSide 50 Front-End-Module. Picture was taken from [36]

## 2.3 Cryogenic electronics for DarkSide-20K experiment

Dark matter particles may conform to a large percentage of the matter in the universe with dark energy. Theoretically, the dark matter may be composed of weakly interacting massive particles (WIMPs) [37]. However, the particle does not exist in the Standard Model [38] and has not been directly observed yet at any experiment. The observation of the WIMPs could demonstrate the existence of dark matter and would be a great advance in the mission to know the universe and its origin.

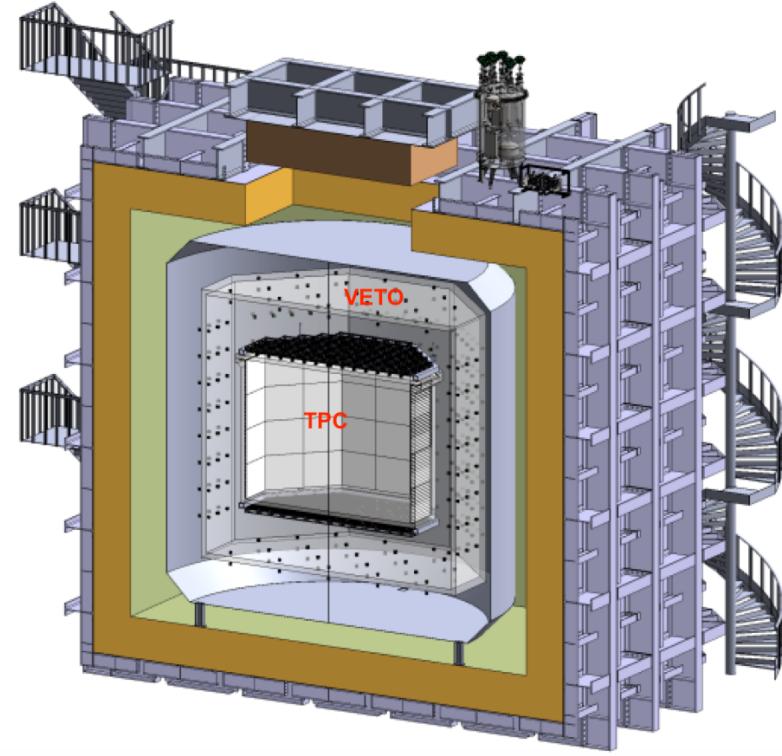

DarkSide 20K is a direct WIMP search using a Time Projection Chamber (TPC) of 20 tonnes of Liquid Argon fiducial mass, shown in Figure 2.10. The LAr TPC is deployed within a Veto system with an octagon Liquid Scintillator Veto (LSV), as shown in the Figure 2.10. VETO aims to reject or follow-up closely the non-WIMP events.

Figure 2.10: Preliminary prototype of DarkSide 20K. The picture was taken from [39]

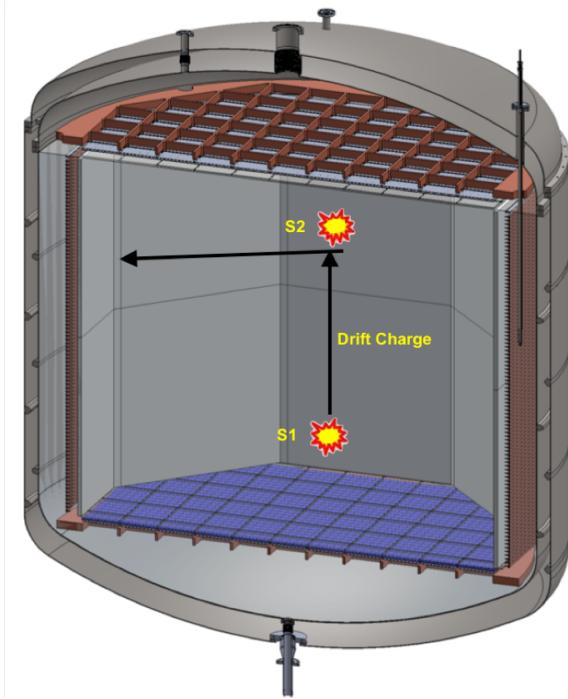

An event inside the TPC can be produced by electron and nuclei recoil, which release energy within Liquid Argon, then it produces a direct excitation, generating a fast

scintillation signal (S1). The remaining free electrons of recombination are accelerated by an electric field up to be extracted from Liquid Argon. The accelerated electrons excite the Argon gas on the top of the TPC. Then, this generates a secondary scintillation signal, called S2. The S2 acquisition provides the 3D position of particles as shown in the Figure 2.11. The 3D position is crucial to figure out how much energy the particles release in the Liquid Argon.

Figure 2.11: Time projection chamber system implemented within DarkSide 20k. Picture taken from [39]

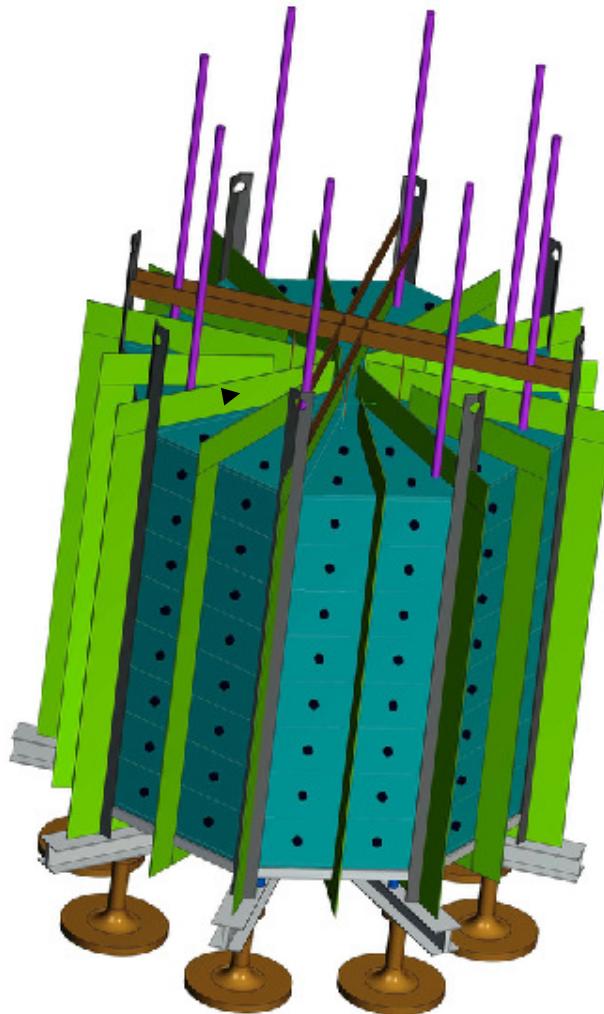

Several photodetection modules (PDMs) are integrated within the walls of the VETO system (shown Figure 2.10) and in the TPC. PDM structures are integrated by a cryogenic front-end electronics mounted on an array of  $24 \text{ cm}^2$  SiPM. The analog output signal is transported to the warm data acquisition through the optical fiber. Thus, an optical transceiver is connected to the PDM's signal.

This study is focused on the development of the integrated cryogenic electronics design for the VETO system of the Darkside 20k experiment. VETO structure requires around 3000 PDMs distributed along with the whole structure, as shown in the Figure

2.12. The PDM structure is placed on the black point located on the wall of the VETO structure.

Figure 2.12: VETO system implemented within DarkSide 20k.

Integrated cryogenic electronics for VETO systems implements in a 110 nm CMOS technology. Before the electronic design, careful and deep studies of the single transistor were performed to analyze and comprehend the behavior of technology at 77 K. The temperature of 77 K results from the usage of Liquid Nitrogen (LN) to test the electronics, because LN is much easier and cheaper to implement in the laboratory than Liquid

Argon.

Afterward, the successful results obtained from the first cryogenic electronics prototype have pushed us to realize a second tape-out. The new prototype optimizes the previous results and includes an single-ended to differential converter. Furthermore, the new front-end implements in a new 110 nm CMOS technology. The new CMOS technology implements a 4-metal interconnection, which may cause problems, for instance, a considerable IR drop due to the large interconnection resistivity. It makes the IC layout structure be changed to avoid large IR drops. The idea of the second tape-out is to test a new 110 nm technology at cryogenic temperatures. The new electronics version presents improvements in terms of the dynamic range and SNR in comparison to ASIC v1. In the ASIC v2, a differential signaling allows the VETO system signal to be led to warm data acquisition by cabling instead of the optical fiber. However, ASIC v2 implements a power domain for the amplification and signal conversion stage. Then, the converter circuit can turn off in the case that only a single-ended output is required.

### 2.3.1 Conclusion

A couple of underground astroparticle experiments have developed the detector using warm front-end electronics, inducing many parasitic components and losses. Other detector prototypes, such as ProtoDUNE and DarkSide 50, have decided to include the first amplification step inside the cryostat to improve signal efficiency. The previous detectors have designed cryogenic electronics using discrete or commercial components. In the case of DarkSide 20k, the discrete electronics may be big trouble due to the large sensor capacitance ( $> 10 \text{ nF}$ ). This new condition demands the inclusion of additional filtering stages and offline signal processing. Otherwise, it becomes complex to achieve an acceptable signal to noise ratio.

Implementing an integrated electronics, the internal parameters of the circuit could be tuned by external bias currents and voltages. The tuning especially allows the input transistors trans-conductance to be modified when the integrated circuit passes from 300 K to 77 K. The biases tuning provides flexibility hard to find in discrete electronics.

# Chapter 3

## Cryogenic CMOS electronics

The use of CMOS electronics at cryogenic temperatures offers relevant device enhancements in terms of RMS noise, power dissipation, electromigration, and overheating. The reduction of power consumption with respect to 300 K operation for the same or improved performance is particularly significant for digital circuits. [40]. Furthermore, cryogenic operation is mandatory in many fields, ranging from quantum computing [41] to new generation underground detectors for dark matter and neutrino experiments [41].

Unfortunately, cryogenic operation has also several drawbacks. For instance, CMOS technology exhibits a sensitive degradation due to the hot carrier effect. This degradation could be reduced considerably by an optimal transistor design. In this way, the lifetime of transistors is extended more than 20 years. In this chapter the advantages of using a CMOS tecnologies at cryogenic temepratures are discussed, along with the drawbacks and main solutions to circumvent them.

[42].

### 3.1 Advantages of CMOS electronic at 77 K

CMOS technology performs improvements concerning the carrier mobility, power consumption, thermal noise, transit frequency of a single transistor at a cryogenic temperature of 77 K [43]. Besides, the transistors and metalization do not suffer the effect of electromigration and heating. The behavior of carrier mobility, threshold voltage, slope factor is considered and analyzed in this study.

#### 3.1.1 Carrier mobility

Carrier mobility establishes the effective velocity of electrons or holes under an electric field effect. In this way, scattering mechanisms determine the magnitude of the transistor parameters. The mechanisms allow the momentum and kinetic energy of electrons/holes to be exchanged with the environment [44]. The scattering includes mechanisms as a result of the lattice vibration and charges ionized impurity atoms. All these are represented by the Equation 3.1.

$$\frac{1}{\mu_{eff}} \propto \frac{1}{\mu_{pii}} + \frac{1}{\mu_{vs}} + \frac{1}{\mu_{cc}} + \frac{1}{\mu_{ni}} \quad (3.1)$$

where:

- $\mu_{eff}$ , total effective carrier mobility;

- $\mu_{pii}$ , phonon and ionized impurity scattering;

- $\mu_{vs}$ , velocity saturation scattering;

- $\mu_{cc}$ , carrier to carrier collisions scattering;

- $\mu_{ni}$ , neutral impurity scattering.

Each scattering mechanism depends on the temperature in different ways, therefore the effective carrier mobility is modified following the strongest mechanism variation and magnitude. Firstly, the phonon scattering contribution is considered:

### Phonon scattering

Phonon scattering occurs due to electron-phonon interactions. For instance, the hole scatters because of interacting with crystal vibration. The energy bandgap depends on the lattice constant, which changes with the lattice vibration [45]. The crystal vibration alters the periodic crystal structure by producing a scattering of hole wave. As a result, the carrier mobility of phonon is represented by the equation 3.2 [46].

$$\mu_{ph} = \frac{q\tau_{ph}}{m} \quad (3.2)$$

Where  $\tau_{ph}$  is the mean free time of phonon scattering. The mean free time highly depends on the inverse of phonon density and the thermal velocity, which converts  $\mu_{ph}$  into a temperature-dependent variable. Thus, the carrier mobility of phonon due to the temperature is represented by equation 3.3. This parameter considerably increases as the temperature decreases.

$$\mu_{ph} \propto \tau_{ph} \propto \frac{1}{ph_{density} \cdot thermal \cdot velocity} \propto \frac{1}{T\sqrt{T}} \quad (3.3)$$

### Ionized impurity scattering

Ionized impurity is a scattering mechanism produced by the high doping concentration. The high concentration level is typical of scaling down technology to improve its electrical performance [45]. Thus, a consequence of this high doping is a carrier mobility reduction as a result of an increase of scattering center, which interferes with the carrier motion. The electrons or holes can be scattered by either a donor or an acceptor ion [46].

Carrier mobility due to ionized impurity scattering is inversely proportional to the donor or acceptor ion concentrations. However, it is proportional to T, as illustrate the Equation 3.4.

$$\mu_{iie} = \sqrt{\frac{\pi}{m_e}} \frac{64\epsilon_s^2(2kT)}{q^3 N_{ii}} \left[ \frac{1}{\ln(1+x) - \frac{x}{1+x}} \right] \quad (3.4)$$

Ionized impurity and phonon scattering behavior over temperatures and doping concentration are illustrated in Figure 3.1.

Figure 3.1: Phonon and ionized impurity scattering vs doping concentration at different operation temperatures, graphic taken from [45].

### Velocity saturation scattering

CMOS devices under a large applied electric field always present a drift velocity with a saturation around  $10^7 \frac{cm}{s}$ . Because once the carrier kinetic energy overcomes the optical phonon energy. The devices generate an optical phonon, and consequently losses the kinetic energy [46].

The electron and hole mobility of the velocity saturation perform different temperature variation, as described the Equation 3.5 and 3.6.

$$\mu_{vse} = 10^7 \frac{T}{300}^{-0.87} \quad [\text{cm/s}] \quad (3.5)$$

$$\mu_{vsh} = 8.37^6 \frac{T}{300}^{-0.52} \quad [\text{cm/s}] \quad (3.6)$$

### Carrier to carrier collisions scattering

Carrier to carrier scattering is a mechanism generated in submicron devices because of high current densities. In other words, the high carrier concentration modifies the formed mobility by the inter-carrier scattering. The optimal model, studied for this process, is described by the Equation 3.7 [47].

$$\mu_{cc} = \frac{2 * 10^{17} / \sqrt{np}}{\ln(1 + 8.28 * 10^8 T^2 (np)^{-1/3})} \quad (3.7)$$

Where n and p represent the level of electrons and holes. The scattering is inversely proportional to the temperature.

### Neutral impurity scattering

Neutral impurity mechanism affects semiconductor with doping levels below the degeneration level ( $10^{18} cm^3$ ). It becomes a significant factor at temperatures below 125 K. The Equation 3.8 represents the neutral scattering mechanism with its temperature dependence. This model was developed by Erginsoy [48].

$$\mu_{ni} = C_o \left[ \frac{2}{3} \sqrt{\frac{KT}{E_{ni}}} + \frac{1}{3} \sqrt{\frac{E_{ni}}{KT}} \right] \quad (3.8)$$

Assuming that a large portion of the impurities is ionized, and the operating currents are well below the high-injection. In this condition, the most significant contributors to the effective carrier mobility are the phonon, ionized impurity, and velocity saturation scattering. Then, the effective carrier mobility increases around twice between 300 K and 4.2 K. It is considering an electric field below  $10^4$ , as shown the Figure 3.4.

As a result, the carrier mobility owns a temperature dependence involving all the scattering mechanisms. Hence, the rough carrier mobility equation because of the temperature variation is described by Equation 3.9 [44].

$$\mu_{eff}(T) \propto \mu_{eff}(T_{room}) \left( \frac{T}{300} \right)^{-k_3} \quad (3.9)$$

Where  $k_3$  is a constant, which presents values from 1.2 to 2.

Figure 3.2: Electron mobility vs electric field at different operation temperatures, graphic taken from [45].

### 3.1.2 Thermal and low frequency noise

Thermal noise is a disturbance caused by thermal agitation of electrons in a conductor [49]. Besides, the thermal noise acquires a random component in their motion, as shown the Figure 3.3. The noise component disappears at absolute zero.

Figure 3.3: Electron response under heating. Picture taken from [49].

The thermal noise spectrum is modeled by Equation 3.10. Where  $\beta$  constant is a bias-dependent parameter, which presents a value of 1/2 in weak inversion and 2/3 in strong inversion [50]. It is possible to infer from the Equation 3.10 that thermal noise is reduced at cryogenic temperatures due to the  $kT$  term.

$$S_{Vg} = e_n^2 = \beta \frac{4kT}{g_m} \quad (3.10)$$

On the other hand, low frequency or flicker noise caused by the imperfections in crystalline structure [49]. Flicker noise shows a clear dependence on the overdrive voltage, as shown in its representative Equation 3.11. Considering that there is no a consolidated noise representation, the low-frequency noise has been modeled by two theories. One is the mobility fluctuation ( $\Delta\mu$ ), and secondly, the carrier density fluctuation ( $\Delta N$ ). The carrier density fluctuation theory is validated by using the drain current noise modeled by the Reimbold approximation described by the Equation 3.12 [51].

$$S_{Vg}(f) = \frac{q}{C_{ox}WLf} \frac{\alpha_H}{(V_{gs} - V_{th})} \quad (3.11)$$

$$\frac{S_I}{I_D^2} = \frac{q^2}{a^2 WLk f T \alpha_{tunn}} \frac{N_T(E_g)}{C_{ox} + C_D + C_{it} + C_i} \quad (3.12)$$

Where  $C_i$  is the inversion layer capacitance per unit area,  $C_D$  is the corresponding depletion layer capacitance, and  $C_{it} = \frac{gN_{it}}{kT}$  represents the interface trap capacitance.

Assuming the two flicker noise theories, a unified flicker noise theory has been developed considering both the density and the correlated mobility fluctuations through the carrier scattering. These aspects provides a normalized drain current noise spectral density represented by the Equation 3.13 [52].

$$\frac{S_I}{I_D^2} = \frac{kT}{WL f T \alpha_{tunn}} \left( \frac{1}{N} + \alpha_{scatt} \mu \right)^2 N_T(E_F) \quad (3.13)$$

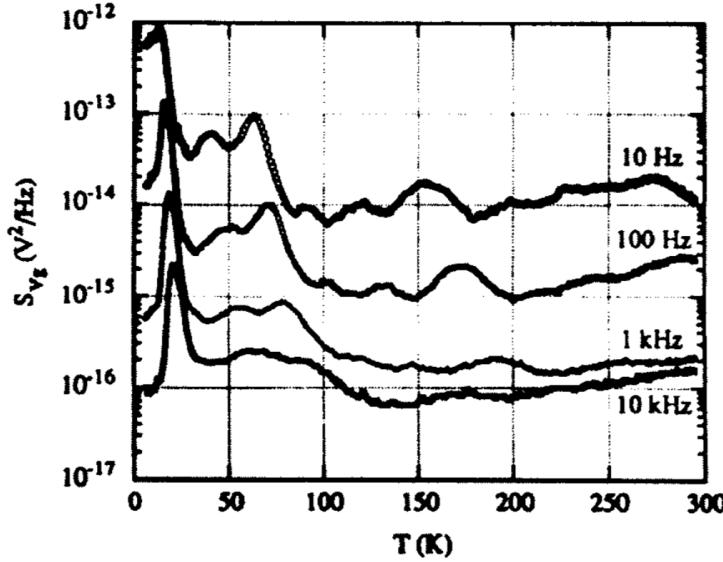

Afterward, the flicker noise behavior of pMOS structure at different frequencies is illustrated by Figure 3.4. This graph shows the increasing trend of low-frequency noise at temperatures below 80 K and becomes a critical factor below 25 K.

### 3.1.3 Transit Frequency and Power consumption

Transit frequency or cut-off frequency is a measure of the intrinsic speed of a transistor. It is defined as the frequency where the current gain falls to 1. The transit frequency of a single transistor is computed by the Equation 3.14.

$$f_T = \frac{g_m}{2\pi C_{GS}} \quad (3.14)$$

Figure 3.4: LF noise versus temperature scan for a pMOS in a range of 6 - 295 K. Graph taken from [53].

Transit frequency proportionally depends on the transconductance as shown the Equation 3.14. Then, assuming a weak inversion operation the  $f_T$  increases at low temperatures by the thermal term  $kT$  ( $G_m = \frac{I_d}{nV_T}$ ). The  $f_T$  growth follows the factor expressed by the Equation 3.15 considering identical bias current conditions. On the other side, a strong inversion condition modifies the increment ratio of transit frequency, since the cut-off frequency ( $f_T$ ) will depends on a new factor expressed by the Equation 3.16, which is not linear as in weak inversion condition.

$$f_{T77K} = \frac{T_{300K}}{T_{77K}} \frac{n_{77K}}{n_{300K}} f_{T300K} \quad (3.15)$$

$$f_{T77K} = \sqrt{\frac{\mu_{n_{77K}}}{\mu_{n_{300K}}}} f_{T300K} \quad (3.16)$$

Where the  $n_{77K}$  and  $n_{300K}$  represent the slope factors at that temperature. T represents the operation temperature in Kelvins. The  $f_T$  increment must be analyzed carefully in a full transistor-level design of an operational amplifier, because it could modify the poles and zeros of the circuit, causing an uncontrollable or unknown gain bandwidth and phase margin. As a result, the circuit could be led to an unstable region.

Moreover, the power consumption of a transistor could be reduced by the same factor of the transit frequency (Equation 3.15, 3.16). But in this case, the power reduction is generated by reducing the bias current up to obtain the room temperature transconductance [54]. As a result, the  $f_T$  is reduced up to its room temperature value.

### 3.1.4 Electromigration and series resistance

Electromigration is considered as a flux of atoms in the electrons' flow direction. The atom flux produces structure damage, resistance increases, and electrical failures in the interconnection [55]. Then, the electromigration becomes a crucial factor of circuit reliability, since if a single interconnection fails, the entire device no longer works as required. The phenomenon is rather general and happens in solids, liquids, and gases.

Every metal interconnection presents a maximum current density to avoid electromigration. The maximum current density is reduced substantially by the temperature increases [56]. As a result, the failure probability increases under high-temperature conditions. For this reason, the cryogenic operation condition allows the metal to be handled with a much higher current density. Hence, a much lower probability of the electromigration effect.

On the other hand, the series resistance is composed of the drain, source, and channel resistance of the transistor. Series resistance produces a voltage drop on the transistor, generating power consumption. In other words, drain-source resistances are considered as parasitic components, which increases the power dissipation of the transistor. In cryogenic temperatures, the total series resistance is reduced, and thus, the power consumption for a single transistor either. [57].

### 3.1.5 Interconnect resistance

Interconnection between the transistors becomes a meaningful factor in integrated circuit design, because their parasitic resistance and capacitance contribute to increase the propagation delay. Cryogenic temperature offers ICs important advantages in terms of interconnecting resistivity. Here, resistivity is significantly reduced in each MOSFET components, as shown in Table 3.1.

| Resistance   | 300 K | 77 K | 4.2 K     |

|--------------|-------|------|-----------|

| N+ Diffusion | 1     | 0.76 | 0.72      |

| Polysilicon  | 1     | 0.89 | 0.88      |

| Alluminium   | 1     | 0.14 | 0.05      |

| P-well       | 1     | 0.3  | $10^{-5}$ |

Table 3.1: Normalized resistance over temperatures in CMOS technology. Table is taken from [43]

## 3.2 Drawbacks of CMOS electronic at 77 K

### 3.2.1 Hot carrier degradation