### POLITECNICO DI TORINO Repository ISTITUZIONALE

### Reliability in Power Electronics and Power Systems

| Original Reliability in Power Electronics and Power Systems / Piumatti, Davide (2021 Jul 08), pp. 1-165.                                |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| Availability: This version is available at: 11583/2918006 since: 2021-08-17T15:32:31Z                                                   |

| Publisher: Politecnico di Torino                                                                                                        |

| Published<br>DOI:                                                                                                                       |

| Terms of use: Altro tipo di accesso                                                                                                     |

| This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository |

|                                                                                                                                         |

| Publisher copyright                                                                                                                     |

|                                                                                                                                         |

|                                                                                                                                         |

(Article begins on next page)

# Doctoral Dissertation Doctoral Program in Computer and Control Engineering (33<sup>th</sup> Cycle)

# Reliability in Power Electronics and Power Systems

By

## **Davide Piumatti**

### **Supervisor**

Prof. Matteo Sonza Reorda

#### **Doctoral Examination Committee:**

Prof. Tiago Balen, Referee, Universidade Federal do Rio Grande do Sul

Prof. Michele Portolan, Referee, Université Grenoble Alpes

Prof. Stefano Di Carlo, Politecnico di Torino

Prof. Franco Fiori, Politecnico di Torino

Dr. Michelangelo Grosso, STMicroelectronics

Politecnico di Torino July 8, 2021

## **Declaration**

Davide Piumatti July 8, 2021

<sup>\*</sup> This dissertation is presented in partial fulfillment of the requirements for **Ph.D. degree** in the Graduate School of Politecnico di Torino (ScuDo).

## Academic Acknowledgement

Before proceeding with the discussion, I would like to dedicate a few lines to all those who have been near to me in this path of personal and professional growth.

I would like to thank all the people who allowed me to achieve this goal and to perform the different activities performed during the Ph.D. My thanks go especially to Prof. Matteo Sonza Reorda, Prof. Ernesto Sanchez, Prof. Paolo Bernardi and Prof. Giovanni Squillero for guiding me along this path and for giving me numerous opportunities.

I wanted to thank all the people involved in the Power Electronics Innovation Center (PEIC) of the Politecnico di Torino.

Special thanks go to Prof. Radu Bojoi, Prof. Eric Giacomo Armando, Dr. Stefano Borlo and Dr. Fabio Mandrile, involved in the PEIC for the technical support.

Further thanks go to Prof. Franco Fiori, Dr. Matteo Vincenzo Quitadamo, involved in the PEIC, and Dr. Erica Raviola for the collaborations about the thermal research activities.

I thank all the LAB3 researchers of the Control and Computer Engineering Department (DAUIN) for these years of collaboration; in particular, I thank Dr. Annachiara Ruospo, Dr. Andrea Floridia, Dr. Alessandro Ianne, Dr. Marco Restifo, Dr. Jacopo Sini, Dr. Ludovica Bozzoli and Dr. Riccardo Cantoro for the splendid research activities carried out over the years, for time spent together outside the academic activities, for having been by my side in this intense period and for enjoying the achievements.

I want to thank Dr. Sergio De Luca, Dr. Alessandro Sansonetti, Dr. Rosario Martorana and Dr. Mosè Alessandro Pernice for the technical support concerning the digital systems research activities.

Moreover, I want to thank Prof. Jaan Raik, Prof. Raimund Ubar, Prof. Maksim Jenihhin, Dr. Cemil Cem Gursoy and Dr. Oyeniran Stephen Oyeniran for the wonderful time granted to me at the Tallinn University of Technology (TTU) in Estonia.

Finally, I acknowledge all the researchers I have been in contact with over these years. Thanks to the fruitful collaboration and the time spent together in conferences and meetings.

# **Personal Acknowledgment**

I am very grateful to my parents **Matteo** and **Grazia** who have always supported me, supporting my every decision, right from the choice of my course of study.

I thank my brother **Andrea** for supporting me in all these demanding years.

Special thanks go to all my friends who have always helped me morally in difficult moments; in particular, Stefano Restagno, Gianni Cassotta, Alessandro Nuovo, Fabio Cergnar, Marco D'elia, Andrea Giordano, Moreno Monteverde, Federico Pistone, Sandra Rombolà, Andrea Emonti, Cristina Battisti, Erica Montesano, Simone Lobozzo.

To conclude, I would like to thank an important person, **Marta Lovino**, who in these years of Ph.D. has always been ready and willing to listen to me and advise me.

## **Abstract**

The electronic devices used in modern analog and digital systems can be affected by faults. For example, physical manufactury defects or device ageing are common causes of faults. Typically, the defects of an electronic device can arise during its production, or during the assembly phase of the device in the final system, for example on the Printed Circuit Board (PCB). In other cases, unexpected external events, such as physical shocks, or exposure to unwanted operating conditions such as overheating, can damage the device. In some situations, the device fails over time due to its intrinsic ageing. It is particularly important to detect the faulty electrical devices and to put the faulty systems in a safe state, i.e., in a state where they cannot cause harm to people or to other systems. Detecting faulty devices is not a trivial task, especially in complex systems consisting of many devices. Typically, electronic devices are tested at the end of manufacturing using different techniques. Furthermore, testing is a key parameter for increasing the quality of a system. Currently, the effectiveness of test methodologies for analog devices is in most cases qualitatively assessed considering the experience of engineers and the number of defective products returned from the field. In general, the effectiveness of the test procedures is performed without resorting to a precise device fault model. The absence of a fault model for analog devices does not allow a systematic and exhaustive generation of a list of all the possible faults to be considered. Therefore, it is not possible to assess the real effectiveness of a test method for analog devices. However, in recent years, numerous efforts have been performed to identify a fault model applicable to analog and power circuits. For example, the emerging IEEE P2427 standard proposes some solutions to the above issue, e.g., based on the adoption of a catastrophic fault model. In this thesis, this recently fault model is used with different aims. Initially, the catastrophic fault model is used to assess the effectiveness of the power devices test procedures; afterwards, the considered fault model is used to assess the effectiveness of thermal test procedures for power devices. Finally, the catastrophic fault model is used to study the impact of the device faults on cyber-physical systems and for performing the Failure Mode, Effects, and Criticality Analysis (FMECA) for the power devices.

My research activities have been focused on assessing the effectiveness of devices test methodologies using the new device fault models recently proposed by the scientific and industrial community. The aim of my research is to allow a quantitative evaluation of the effectiveness of a test strategy for power devices and systems; in other words, my work aims at making possible to calculate a Fault Coverage (FC) figure for a test solution targeting a power device or system. In particular, I devised an approach targeting different power devices, such as Insulated Gate Bipolar Transistors (IGBTs) and Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs). A key point in the proposed method is the ability to generate in an automatic and systematic way the list of possible faults, thus paving the way to perform fault simulation experiments and compute the Fault Coverage figure.

The obtained results show which faults are detected by different test methods, allowing to also highlight the faults that are never detected. These results indicate which efforts are needed to improve the available test methods with the aim of detecting faults that are not yet detected. Moreover, the experimental results have shown that with an adequate combination of different test methods it is possible to reach a high FC (at least 90%) of the possible faults. Furthermore, some power devices are used in such a way to implement redundant solutions in the target system. The aim of these redundancies is to distribute the management of high currents and high voltages across multiple power devices. Furthermore, these redundancies create systems tolerant to the faults. However, experimental results obtained on a real target system have shown that some end of manufacturing tests significantly lose their effectiveness in the presence of redundant configurations. The redundant configurations can be useful to improve device output capacitance and for creating a system tolerant to the faults. Clearly, these configurations can introduce untestable faults, the presence of which can affect the long-term device reliability.

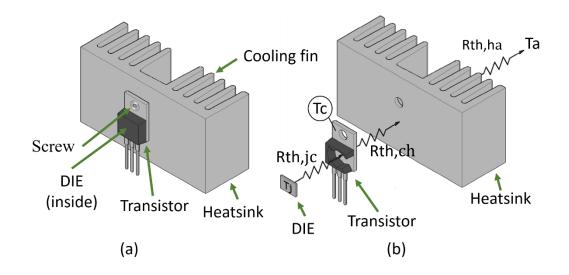

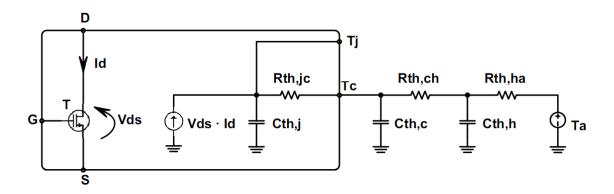

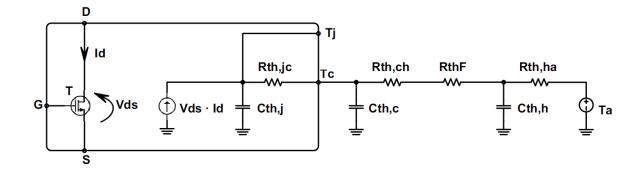

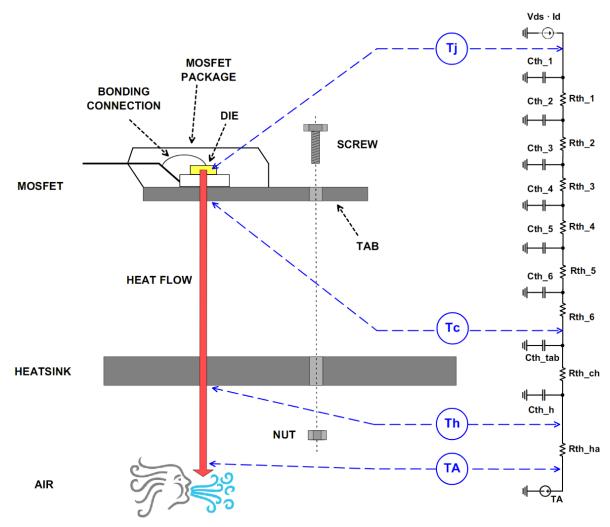

Power devices require an adequate system to dissipate the heat produced during their operation. In fact, an excessive junction temperature in the power device may cause different breakdown phenomena. Usually, an efficient heat dissipation system is present on the power devices; typically, a heatsink is assembled on the power device. Heatsink incorrect operation may cause a significant increase in the power device junction temperature. Therefore, it is necessary to check the correct assembly and operation of the heatsinks used on the power devices. Currently, heatsinks are often tested using automatic optical inspection or by an x-ray inspection. However, this approach gives only a qualitative idea of the heatsink assembling, requires complex equipment and does not guarantee the systematic detection of possible defects affecting the heatsink system. In this thesis, a test method based only on electrical measurements is proposed; the test method allows to estimate the thermal resistance present between the device junction and the environment. This measure allows performing a quantitative test on the heatsink assembly. The effectiveness of the proposed methodology is assessed experimentally and by means of a thermal model of the adopted dissipation system.

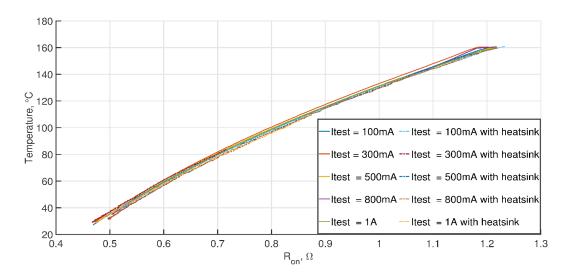

The results obtained show that the effectiveness of the thermal test methodologies strongly depends on the specific target system; in some circuits, electrical components present around the power device under test can reduce the effectiveness of the test methods by masking the fault effects. This highlights the importance of quantitatively assessing the test methodology adopted, which, for some real target systems, may require new engineering in order to maintain its high effectiveness. Furthermore, the experimental results highlighted the effectiveness of the proposed test method. The proposed solution (assessed on a real target system) has identified the heatsink incorrect assembly in 100% of the cases considered.

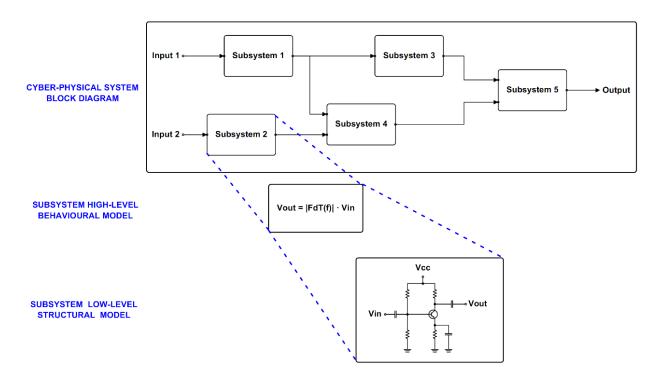

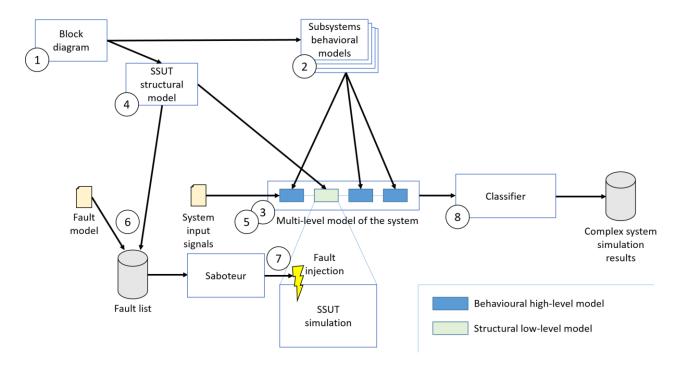

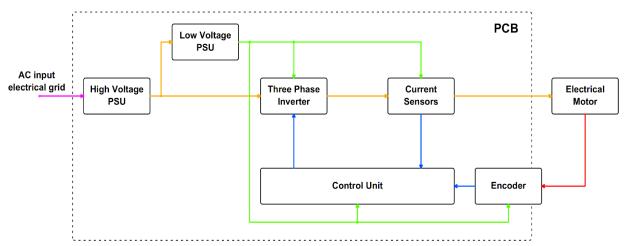

Finally, a methodology for performing the FMECA analysis on power systems considering the newly introduced catastrophic fault model is proposed. FMECA is a widely used methodology to identify the critical faults. This analysis is required by numerous international standards for safety-critical applications. It requires studying the impact of each fault on the whole system. In this thesis, a methodology to perform the FMECA analysis for faults present inside a power device is proposed. The novelty introduced in this thesis concerns in particular the underlying simulation methodology, targeting the whole complex cyber-physical system and considering the possible catastrophic faults present in the power devices. Furthermore, the proposed methodology allows assessing the effectiveness of the adopted fault mitigation strategies. The proposed approach allows the systematic and automatic identification of critical faults in a cyber-physical system. These analyses are particularly useful to the designers of the cyber-physical systems used in safety-critical applications.

The results obtained show the versatility of the multilevel simulators used in FMECA analyzes. Moreover, the multilevel simulators allow to reduce the simulation times, compared to traditional circuit simulations, by about 70% without affecting the quality and accuracy of the simulations performed.

# **Contents**

| Chapter 1 Introduction                                     | 1  |

|------------------------------------------------------------|----|

| 1.1 Motivations                                            | 1  |

| 1.2 Thesis contributions                                   | 3  |

| 1.3 Thesis structure                                       | 5  |

| Background                                                 | 7  |

| 2.1 Power Electronics Applications                         | 8  |

| 2.2 Power Electronics Test Approaches and Metrics          | 9  |

| 2.2.1 Analog Testing Difficulties                          | 12 |

| 2.2.2 PCOLA                                                |    |

| 2.2.3 Fault Models for Analog Electronics                  | 16 |

| 2.2.4 Effectiveness of a Test Procedure - State of the Art | 18 |

| 2.3 Power electronics test methods                         | 20 |

| 2.3.1 Incoming Inspection test                             | 20 |

| 2.3.2 In-circuit test                                      | 20 |

| 2.3.3 Functional test                                      | 22 |

| 2.4 Power devices and models                               | 22 |

| 2.4.1 Diode                                                | 23 |

| 2.4.2 MOSFET                                               | 23 |

| 2.4.3 IGBT                                                 | 24 |

| 2.5 Thermal basic concepts on Power Devices                | 26 |

| 2.5.1 Thermal Effects on Power Devices                     | 26 |

| 2.5.2 Heat Dissipation Strategies                          | 27 |

| 2.5.3 Temperature-Sensitive Electrical Parameters (TSEPs)  | 29 |

| 2.5.3.2 MOSFET  2.5.3.3 IGBT  2.5.4 Thermal Model  2.5.5 Thermal Fault Model  2.6 Power Devices Used in Cyber-Physical System | 30<br>33<br>34<br>35<br>36 |

|-------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2.5.4 Thermal Model                                                                                                           | 30<br>33<br>34<br>35<br>36 |

| 2.5.5 Thermal Fault Model                                                                                                     | 33<br>34<br>35<br>36       |

|                                                                                                                               | 34<br>35<br>36             |

| 2.6 Power Devices Used in Cyber-Physical System                                                                               | 35<br>36<br>38             |

|                                                                                                                               | 36<br>38                   |

| 2.6.1 Safety International Standards                                                                                          | 38                         |

| 2.6.2 Failure Mode, Effects, and Criticality Analysis (FMECA)                                                                 |                            |

| 2.6.3 Complex Cyber-Physical System Models                                                                                    |                            |

| 2.6.4 Multilevel Simulation Strategy                                                                                          | 39                         |

| Assessing the Effectiveness of Test Methods for Power Devices                                                                 | 41                         |

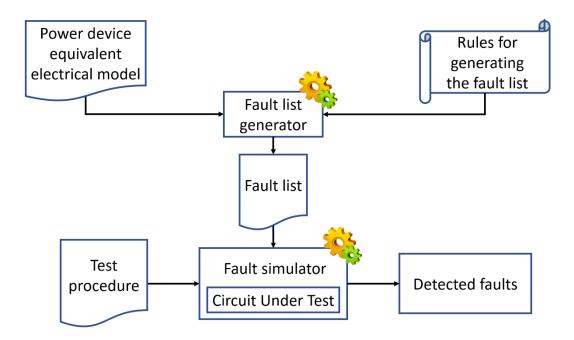

| 3.1 Fault List Generation Flow                                                                                                | 42                         |

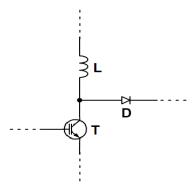

| 3.1.1 Diode                                                                                                                   | 46                         |

| 3.1.2 MOSFET                                                                                                                  | 47                         |

| 3.1.3 IGBT                                                                                                                    | 47                         |

| 3.2 Analog Fault Simulation Flow                                                                                              | 48                         |

| 3.3 Proposed Approach Evaluation                                                                                              |                            |

| 3.3.1 Case Study                                                                                                              | 50                         |

| 3.3.1.1 High-Voltage PSU subsystem                                                                                            | 53                         |

| 3.3.1.2 Communication subsystems                                                                                              |                            |

| 3.3.2 Incoming Inspection Test Method                                                                                         | 56                         |

| 3.3.2.1 Diode                                                                                                                 | 56                         |

| 2.3.2.2 IGBT                                                                                                                  | 57                         |

| 3.3.2.3 MOSFET                                                                                                                | 61                         |

| 3.3.2.4 Experimental results                                                                                                  | 63                         |

| 3.3.3 In-Circuit Test Method                                                                                                  | 64                         |

| 3.3.3.1 Diode                                                                                                                 | 64                         |

| 3.3.3.2 IGBT                                                                                                                  | 65                         |

| 3.3.3.3 Experimental results                                                                                                  | 68                         |

| 3.3.4 Functional Test Method                                                                                                  | 68                         |

| 3.3.4.1 Experimental results                                                                                                  | 69                         |

| 3.3.5 Results analysis                                                                                                        | 70                         |

| 3.4 Chapter Summary                                                                                                                 | 71  |

|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| Assessing the Effectiveness of the Test for Heatsink Assembling                                                                     | 73  |

| 4.1 Heatsink Assembling Test Approach                                                                                               | 74  |

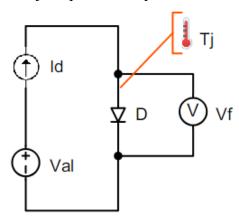

| 4.1.1 Thermal Diode Test Procedure                                                                                                  | 74  |

| 4.1.1.1 Diode TSEP Temperature Characterization                                                                                     |     |

| 4.1.2 Thermal MOSFET Test Procedure                                                                                                 | 76  |

| 4.1.2.1 MOSFET TSEP Temperature Characterization 4.1.2.2 MOSFET In-Circuit Test Procedure                                           |     |

| 4.1.3 Thermal IGBT Test Procedure                                                                                                   | 78  |

| 4.1.3.1 IGBT TSEP Temperature Characterization                                                                                      |     |

| <ul><li>4.2 Fault List Generation Flow</li><li>4.3 Thermal Fault Simulation Flow</li><li>4.4 Proposed Approach Evaluation</li></ul> | 83  |

| 4.4.1 Case Study                                                                                                                    | 87  |

| 4.4.4.1 In-Circuit Thermal Test                                                                                                     | 92  |

| 4.4.5 Thermal Fault Effects Experimental Evaluation                                                                                 | 93  |

| 4.4.5.1 Case Study                                                                                                                  | 96  |

| 4.5 Chapter Summary                                                                                                                 | 99  |

| Fault effects study on a cyber-physical system                                                                                      | 101 |

| 5.1 Proposed multilevel simulator                                                                                                   |     |

| 5.2.1 Case Study                                                                                                                    |     |

| 5.2.3 Experimental Results                         | 109 |

|----------------------------------------------------|-----|

| 5.2.4 Critical Faults Effect                       | 111 |

| 5.2.5 Environment Setup                            | 113 |

| 5.3 Chapter Summary                                | 114 |

| Conclusions                                        | 117 |

| 6.1 Research achievements                          | 119 |

| 6.3 Other research activities performed            |     |

| Software Test Library enhancements                 | 121 |

| A.1 Motivations.                                   | 121 |

| A.2 Contributions                                  | 122 |

| Publication list                                   | 125 |

| B.1 Analog Test, Thermal Test and FMECA Papers     | 125 |

| B.1.1 Journals                                     | 125 |

| B.1.2 Conferences                                  | 126 |

| B.2 Digital Test Papers                            | 126 |

| B.2.1 Journals  B.2.2 Conferences  B.2.2 Workshops | 126 |

| References                                         | 129 |

# **List of Tables**

| Table 1 Physical quantities meaning                            | 31 |

|----------------------------------------------------------------|----|

| Table 2 STTH12S06 diode equivalent electrical model parameters | 54 |

| Table 3 STGF19NC60 IGBT equivalent electrical model parameters | 55 |

| Table 4 BSS138 MOSFET equivalent electrical model parameters   | 56 |

| Table 5 Diode test procedure                                   | 56 |

| Table 6 IGBT test procedure                                    | 57 |

| Table 7 MOSFET test procedure                                  | 61 |

| Table 8 Diode incoming inspection test results                 | 64 |

| Table 9 IGBT incoming inspection test results                  | 64 |

| Table 10 MOSFET incoming inspection test results               | 64 |

| Table 11 Diode in-circuit test results                         | 68 |

| Table 12 IGBT in-circuit test results                          | 68 |

| Table 13 Functional stimuli                                    | 69 |

| Table 14 Diode functional test results                         | 69 |

| Table 15 IGBT functional test results                          | 69 |

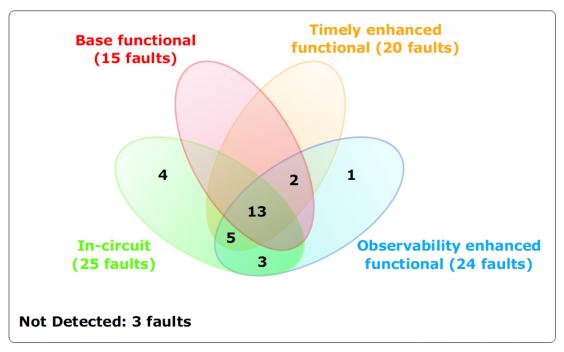

| Table 16 Numbers of faults detected                            | 70 |

| Table 17 Thermal model parameters                              | 86 |

| Table 18 Thermal faults                                        | 87 |

| Table 19 In-Circuit Thermal Test IGBT results                  | 90 |

| Table 20 In-Circuit Thermal Test diode results                 | 91 |

| Table 21 Functional thermal test IGBT results                  | 92 |

| Table 22 Functional thermal test diode results                 | 92 |

| Table 23 Results analysis                                      | 93 |

| Table 24 SPP07N60C3 thermal paramiters                         | 94 |

| Table 25 Thermal model paramiters                              | 95 |

| Table 26 Heatsink physic parameters                            | 96 |

| Table 27 Heatsink thermal parameters                           | 96 |

| Table 28 Thermal test experimental results | 97  |

|--------------------------------------------|-----|

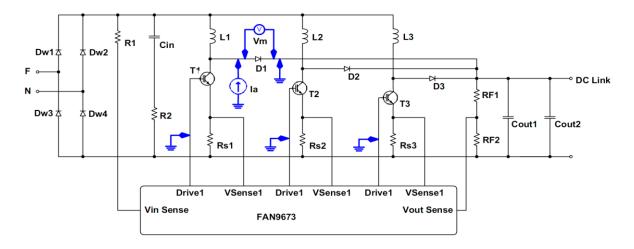

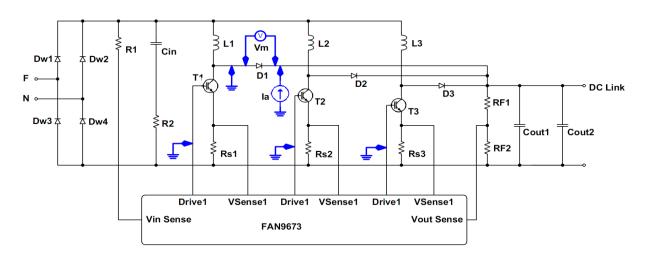

| Table 29 Project specifications features   | 107 |

| Table 30 Faults considered                 | 109 |

| Table 31 Fault simulation results          | 111 |

| Table 32 Critical faults identified        | 111 |

|                                            |     |

# **List of Figures**

| Figure 1 Typical power electronics applications                                |

|--------------------------------------------------------------------------------|

| Figure 2 Test procedure for a resistor                                         |

| Figure 3 Test Points                                                           |

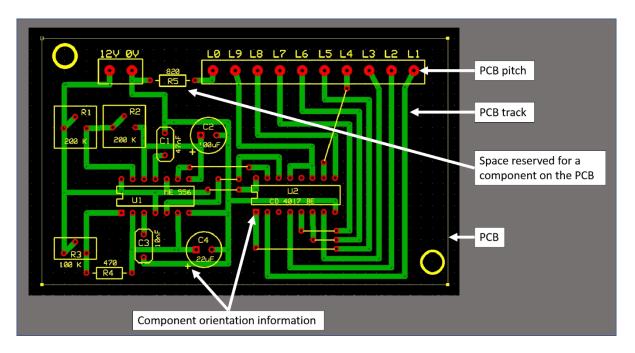

| Figure 4 Typical elements of a PCB16                                           |

| Figure 5 (a) MARS model; (b) MARS model with faults20                          |

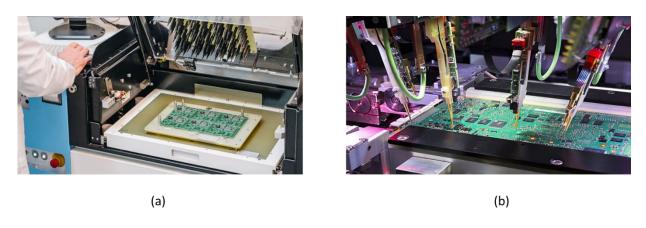

| Figure 6 (a) ATE with bed of nails approach; (b) ATE with flaying probes       |

| approach21                                                                     |

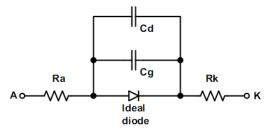

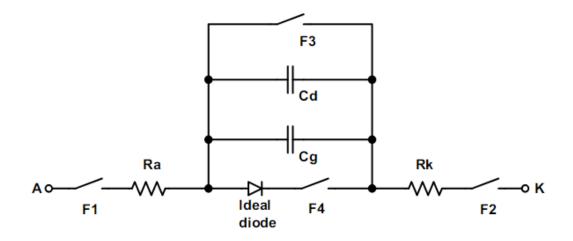

| Figure 7 Diode equivalent electrical model23                                   |

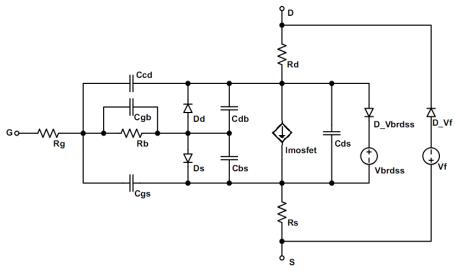

| Figure 8 MOSFET equivalent electrical model23                                  |

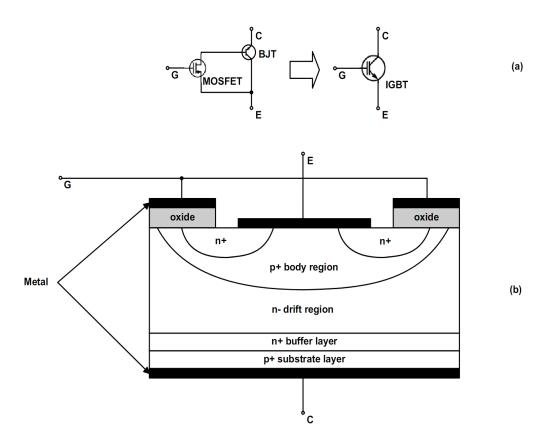

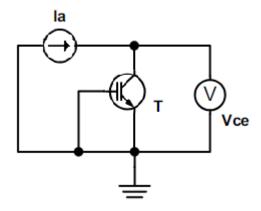

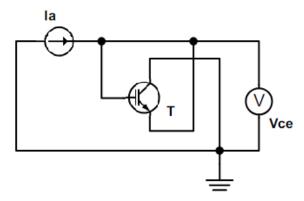

| Figure 9 (a) IGBT conceptual model; (b) IGBT structure25                       |

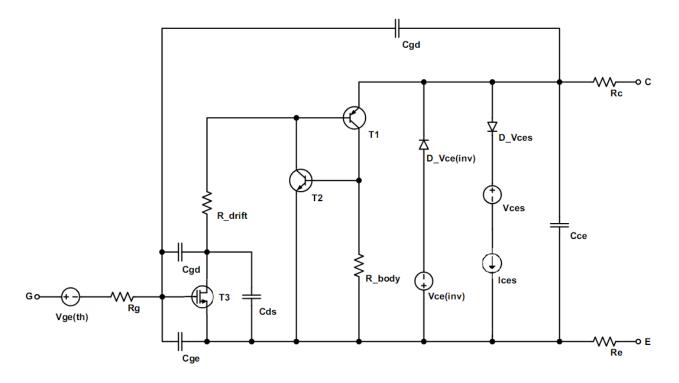

| Figure 10 IGBT equivalent electrical model26                                   |

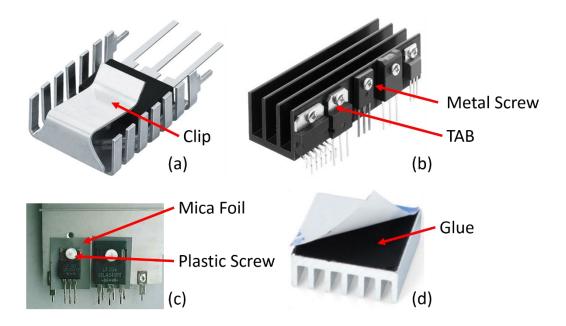

| Figure 11 Typical heatsink assembly strategies (a) Clip; (b) Metal screw; (c   |

| Plastic screw; (d) Glue28                                                      |

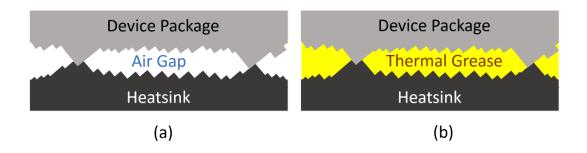

| Figure 12 Heatsink-device mechanical coupling29                                |

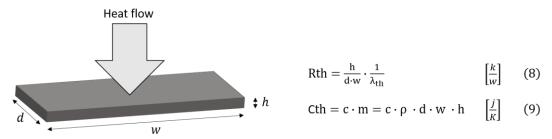

| Figure 13 Thermal resistance and thermal capacitance of a parallelepiped o     |

| homogeneous material31                                                         |

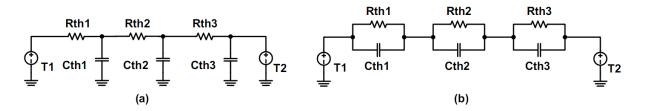

| Figure 14 (a) Cauer thermal network; (b) Foster thermal network32              |

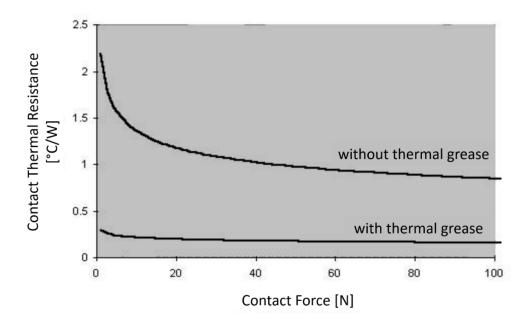

| Figure 15 Thermal contact resistance                                           |

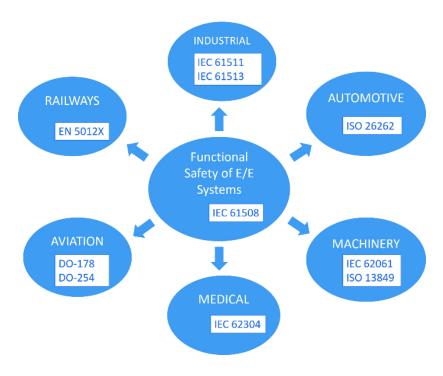

| Figure 16 Different international standards for safety-critical applications36 |

| Figure 17 Cyber-Physical System models                                         |

| Figure 18 Overall proposed flow                                                |

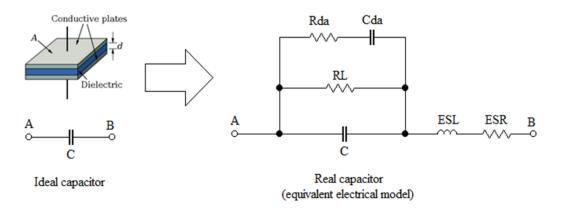

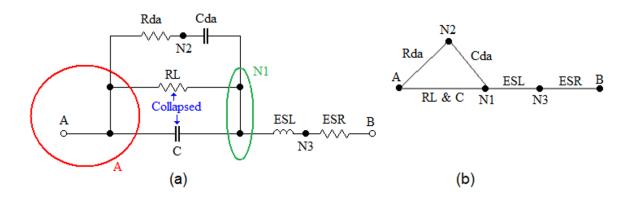

| Figure 19 Equivalent electrical model of the capacitance44                     |

| Figure 20 The serial switches (a) and the parallel switches (b) in the         |

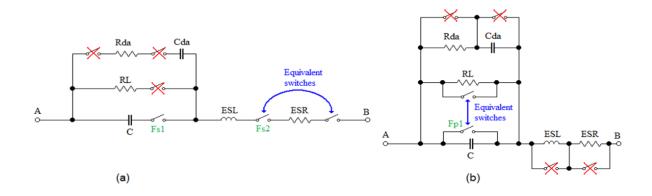

| equivalent electrical model of the capacitance45                               |

| Figure 21 (a) The nodes and the components collapsed in the capacitance's      |

| equivalent electrical model. (b) The incidence graph of the capacitance's      |

| equivalent electrical model4                                                   |

| Figure 22        | The     | equivalent    | electrical    | model      | of the    | capacitance    | with | the |

|------------------|---------|---------------|---------------|------------|-----------|----------------|------|-----|

| catastrophic fau | lts     |               |               |            |           |                |      | 46  |

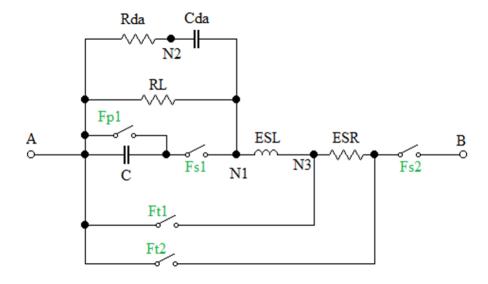

| Figure 23 D      | oiode e | equivalent o  | electrical m  | odel wi    | th faults |                |      | 47  |

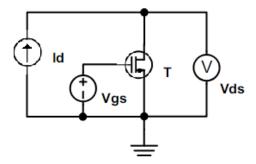

| Figure 24 M      | (IOSF)  | ET equivale   | ent electrica | al model   | with fa   | ults           |      | 47  |

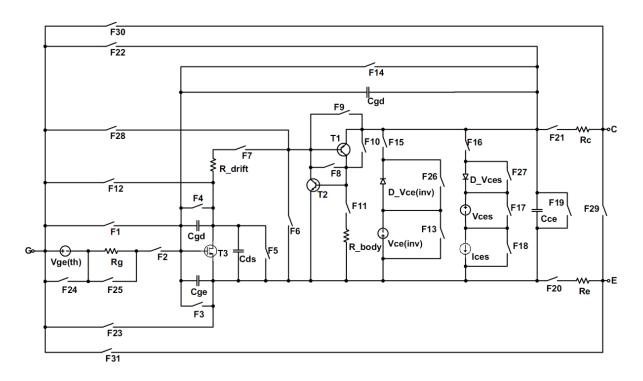

| Figure 25 IO     | GBT e   | equivalent e  | electrical m  | odel wit   | th faults |                |      | 48  |

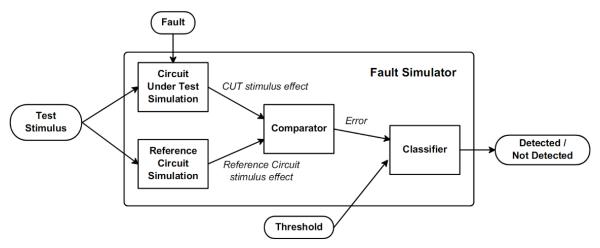

| Figure 26 A      | nalog   | fault simu    | lation flow   |            |           |                |      | 49  |

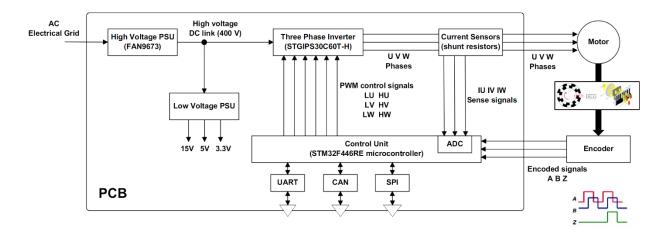

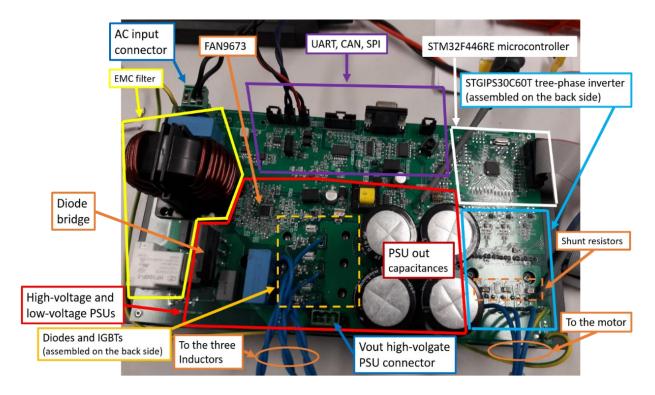

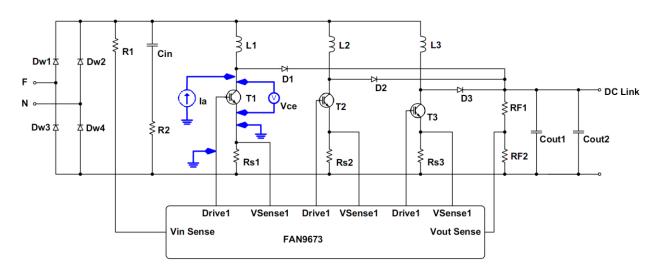

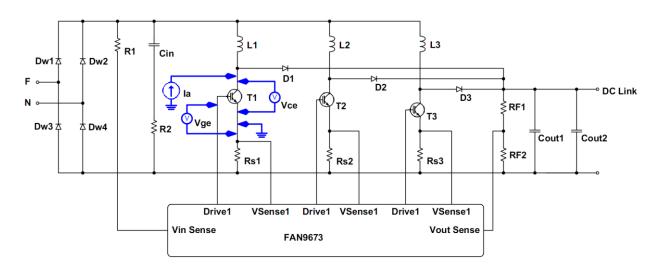

| Figure 27 T      | hree-p  | phase moto    | r control sy  | stem       |           |                |      | 51  |

| Figure 28 T      | hree-p  | phase moto    | r control sy  | stem PC    | В         |                |      | 51  |

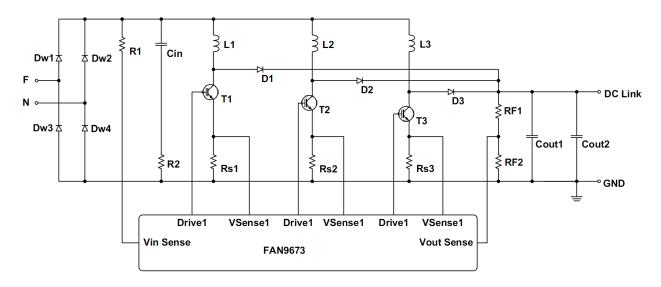

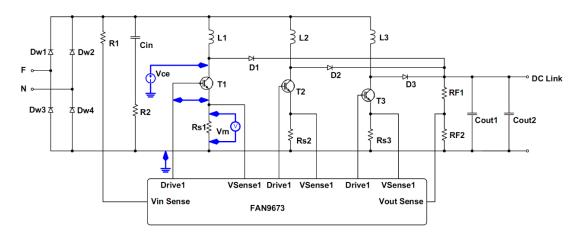

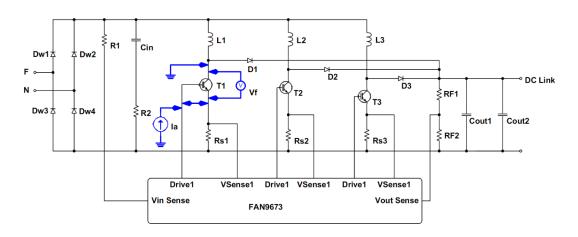

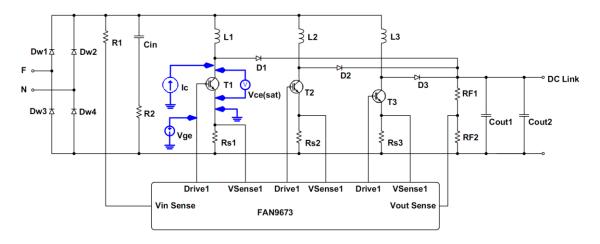

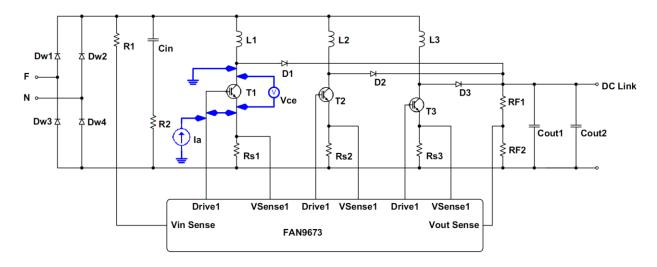

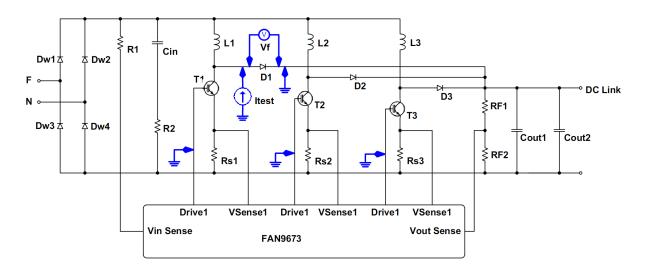

| Figure 29 H      | Iigh-v  | oltage PSU    | circuit dia   | gram       |           |                |      | 54  |

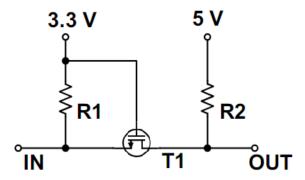

| Figure 30 C      | CMOS    | -TTL logic    | adapter       |            |           |                |      | 55  |

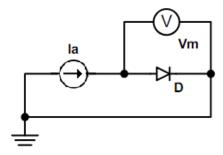

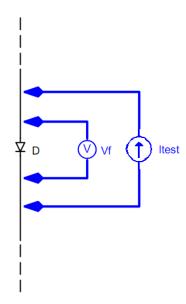

| Figure 31 D      | oiode l | PN junction   | test direct   | ly biased  | 1         |                |      | 56  |

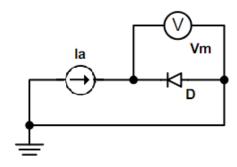

| Figure 32 D      | oiode l | PN junction   | test polari   | zed inve   | rsely     |                |      | 57  |

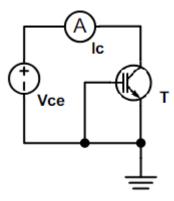

| Figure 33 IO     | GBT I   | PN junction   | test polari   | zed inve   | rsely     |                |      | 58  |

| Figure 34 IO     | GBT I   | PN junction   | test direct   | ly biased  | l         |                |      | 58  |

| Figure 35 IO     | GBT g   | gate-emitter  | impedance     | e test     |           |                |      | 59  |

| Figure 36 IO     | GBT g   | gate-collect  | or impedan    | ce test    |           |                |      | 59  |

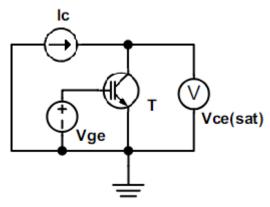

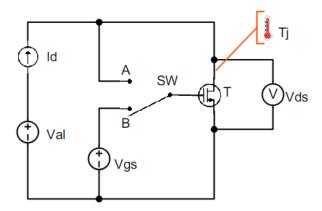

| Figure 37 I      | GBT V   | Vce(sat) tes  | t             |            |           |                |      | 59  |

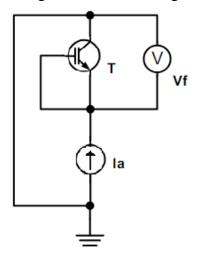

| Figure 38 IO     | GBT a   | intiparallel  | diode Vf te   | est        |           |                |      | 60  |

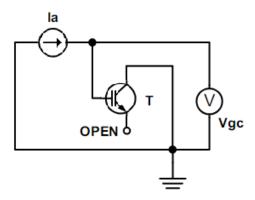

| Figure 39 I      | GBT I   | ces test (ble | ocking dev    | ice)       |           |                |      | 60  |

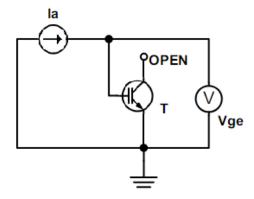

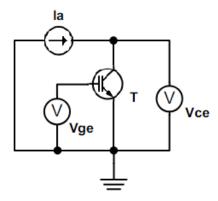

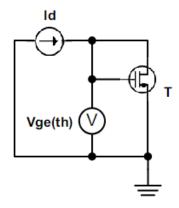

| Figure 40 I      | GBT V   | Vge(th) test  |               |            |           |                |      | 61  |

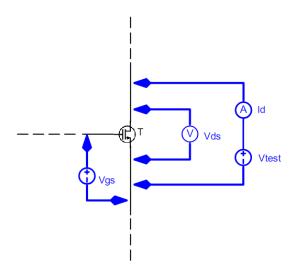

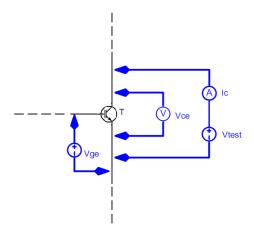

| Figure 41 M      | (IOSF   | ET Vge(th)    | test          |            |           |                |      | 61  |

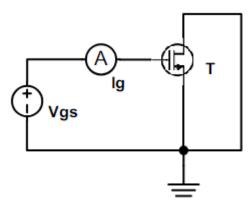

| Figure 42 M      | (IOSF)  | ET impedaı    | nce test      |            |           |                |      | 62  |

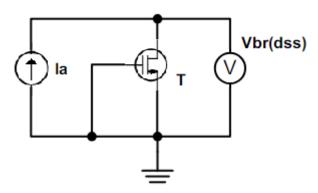

| Figure 43 N      | (IOSF   | ET Vds Bre    | akdown te     | st         |           |                |      | 62  |

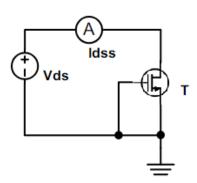

| Figure 44 M      | (IOSF   | ET Ices dev   | ice off test  |            |           |                |      | 62  |

| Figure 45 M      | (IOSF)  | ET Rds(on)    | test          |            |           |                |      | 63  |

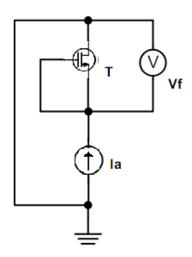

| Figure 46 M      | (IOSF)  | ET antipara   | llel diode \  | Vf test    |           |                |      | 63  |

| Figure 47 D      | oiode l | In-Circuit to | est of PN ju  | anction t  | est direc | tly biased     |      | 65  |

| Figure 48 D      | oiode l | In-Circuit to | est of PN ju  | anction t  | est pola  | rized inversel | y    | 65  |

| Figure 49 I      | GBT I   | n-Circuit te  | est of PN ju  | inction to | est polar | ized inversel  | y    | 66  |

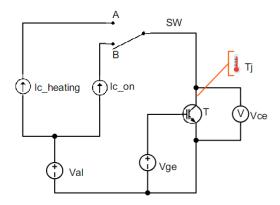

| Figure 50 IO     | GBT I   | n-Circuit te  | est of PN ju  | inction to | est direc | tly biased     |      | 66  |

| Figure 51 IO     | GBT I   | n-Circuit te  | est of Vce(s  | sat) test  |           |                |      | 66  |

| Figure 52 IO     | GBT I   | n-Circuit te  | est of Antip  | arallel d  | iode Vf   | test           |      | 67  |

| Figure 53 IO     | GBT I   | n-Circuit te  | est of Ices t | est (bloc  | king de   | vice)          |      | 67  |

| Figure 54 IO     | GBT I   | n-Circuit te  | est of Vge(1  | th) test   |           |                |      | 67  |

| Figure 55 IO     | GBT f   | ault covera   | ge results    |            |           |                |      | 71  |

|                  |         |               |               |            |           |                |      |     |

|                  |         |               |               |            |           |                |      |     |

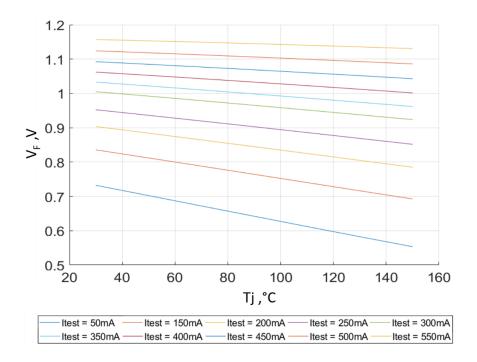

| Figure 58 M      | (IOSF   | ET TSEP T     | emperature    | e Charac   | terizatio | n              |      | 76  |

|                  |         |               |               |            |           |                |      |     |

| Figure 59 MOSFET In-Circuit Test Procedure                               | 78  |

|--------------------------------------------------------------------------|-----|

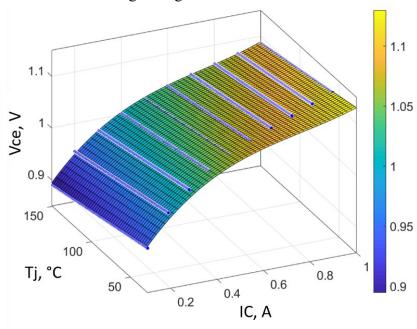

| Figure 60 IGBT TSEP Temperature Characterization                         | 79  |

| Figure 61 IGBT In-Circuit Test Procedure                                 | 80  |

| Figure 62 (a) A typical heatsink physical system; (b) Steady-state model | 81  |

| Figure 63 Thermal model of the system                                    | 81  |

| Figure 64 Thermal model of the system with thermal fault                 | 82  |

| Figure 65 Thermal model of the system with thermal fault in steady-state | 82  |

| Figure 66 Thermal Fault Simulation Flow                                  | 83  |

| Figure 67 Case study heatsink configuration                              | 84  |

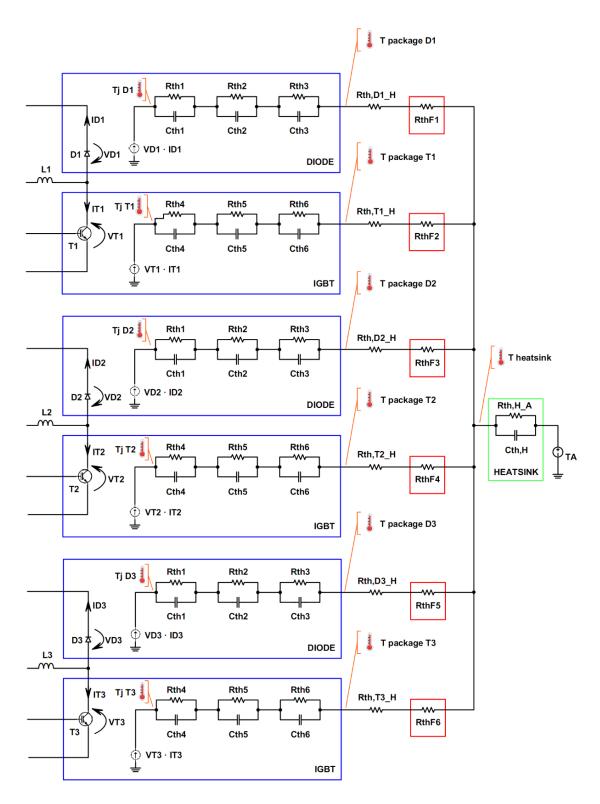

| Figure 68 Case study thermal model                                       | 85  |

| Figure 69 Case study thermal model with faults                           | 88  |

| Figure 70 Diode TSEP catacterization                                     | 89  |

| Figure 71 IGBT TSEP catacterization                                      |     |

| Figure 72 In-circuit thermal test for IGBT device                        | 90  |

| Figure 73 In-circuit thermal test for diode device                       | 91  |

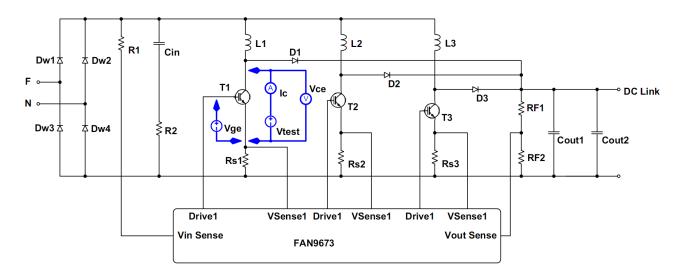

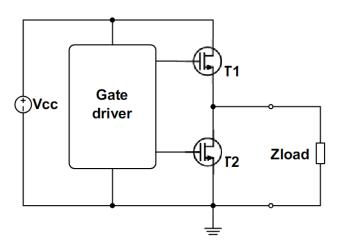

| Figure 74 Half-bridge converter                                          | 94  |

| Figure 75 Thermal model of the cooling system                            | 95  |

| Figure 76 MOSFET TSEP catacterization                                    | 96  |

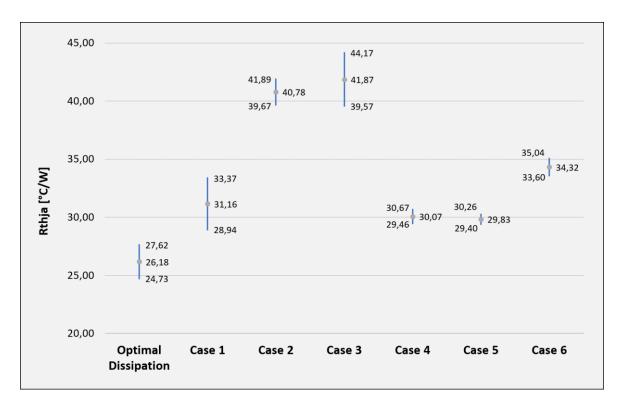

| Figure 77 MOSFET Rthja results                                           |     |

| Figure 78 Multi-level simulation proposed                                | 105 |

| Figure 79 Three-phase motor control system block diagram                 | 106 |

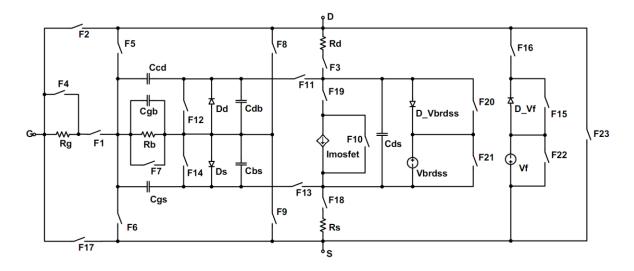

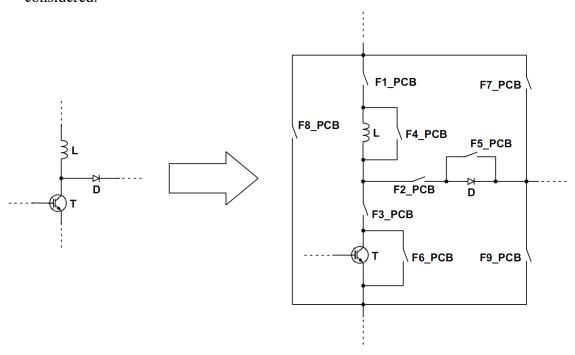

| Figure 80 High-voltage PSU boost cell                                    | 107 |

| Figure 81 High-voltage PSU boost cell with faults                        | 108 |

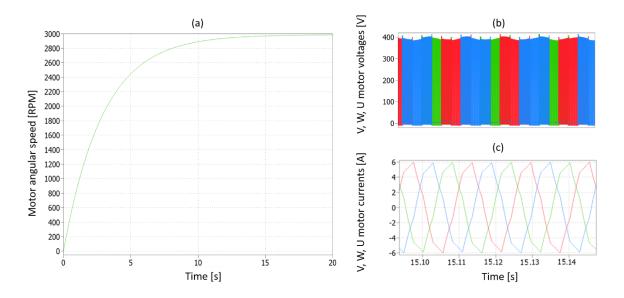

| Figure 82 Cyber-physical system behavior in fault free                   | 112 |

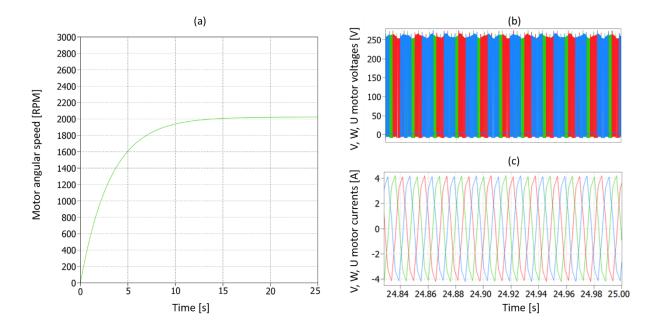

| Figure 83 Cyber-physical system behavior affected by F1_DIODE            | 112 |

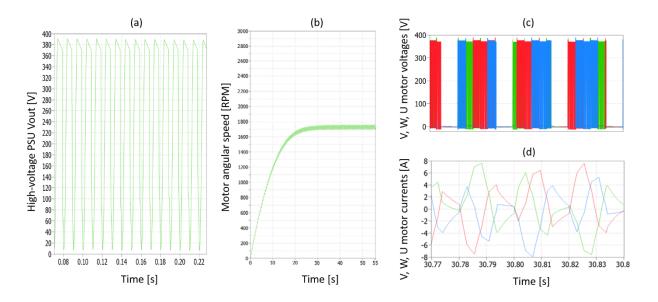

| Figure 84 Cyber-physical system behavior affected by F5_PCB              | 113 |

|                                                                          |     |

## **List of Acronyms**

AMSIM Multilevel SIMulation ART Adaptive Real-Time

ATE Automatic Test Equipment

BIST Built-In Self-Test

BJT Bipolar Junction Transistor

CAD Computer Aided Design

CAN-bus Controller Area Network-bus

CCM Continuous Conduction Mode

CMOS Complementary Metal-Oxide Semiconductor

COTS Commercial Off The Shelf

CPS Cyber-Physical System

Cth Thermal capacitance

CUT Circuit Under Test

DAC Digital-Analog Converter

DCB Direct Copper Bonded

DMM Digital Multi-Meter

DT faults detected

DUT Device Under Test

E/E Electrical and Electronic ECU Electronic Control Unit

EDA Electronic Design Automation EMC Electro Magnetic Compatibility

FC Fault Coverage

FDT Fault Detection Time

FMECA Failure Mode, Effects, and Criticality Analysis

FPU Floating Point Unit GTO Gate Turn Off IC Integrated Circuits

IGBT Insulated Gate Bipolar Transistor

L-BIST Logic-BIST

MARS Multivariate Additive Regression Splines

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

NDT faults not detected PCB Printed Circuit Board PCOLA Presence Correctness Orientation Live Alignment

PCOLA/SOQ Presence Correctness Orientation Live Alignment / Shorts Opens Quality

POST Power On Self Test

PSU Power Supply Unit

PWM Pulse-Width Modulation

RPN Risk Priority Number

Rth Thermal resistance

SBST Software-Based Self-Test SMD Surface Mounting Device SPI Serial peripheral interface

SPICE Simulation Program with Integrated Circuit Emphasis

SSUT SubSystem Under Test

STL Software Test Library

TF Transfer Function

Tj junction temperature

TSEP Temperature-Sensitive Electrical Parameters

UART Universal Asynchronous Receiver-Transmitter

# Chapter 1

### Introduction

This first chapter provides general motivations for the research work reported in the thesis. Moreover, it provides a brief and concise overview of the current state of the art in the area and it reports the main scientific contributions introduced by this thesis. Finally, this chapter describes the overall structure of this document.

### 1.1 Motivations

Many different electronic components may appear in electronic systems. Typically, there may be some power devices able to handle the high voltages and currents present in some systems. Some trends, like the increasing electrification of vehicles, tend to widen their usage and importance. Insulated Gate Bipolar Transistors (IGBTs), Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs), Bipolar Junction Transistors (BJTs) and power diodes are power devices often present in such systems. The power devices are used in different applications, such as for driving electrical motors, managing and recharging batteries, for electric power supplies, for the production and distribution of electricity, and for many other applications. Many of these applications are safety critical, i.e., applications whose malfunction can cause significant economic damage or physical harm to people.

Electrical systems require adequate tests before being used, especially for those used in safety-critical applications. All devices used in an electrical system, in

general assembled on Printed Circuit Boards (PCBs), require to be properly tested. The aim of the test is to identify the components affected by a fault. Due to a faulty device, the system may not work properly; in general, a faulty electrical system can produce potentially dangerous and undesirable behaviours. Of course, detecting faulty devices in a system is not a trivial task. The design of a test requires considerable knowledge and skills. Assessing the effectiveness of a test is also a complex operation. Initially, it is necessary to identify quantitative metrics for assessing the reliability of the power devices used in safety-critical applications, as required by different standards [1]. In particular, it is necessary to identify a metric to assess the effectiveness of the test procedures used to verify the correct behavior of the power devices once assembled on the PCBs often composing the system. In other words, a methodology for computing a Fault Coverage (FC) figure for the different test methods used in the industrial field for power devices is needed. Currently, the effectiveness of the power device test methods is often performed qualitatively, based on the experience of test engineers and without using a well-defined fault model.

For computing a FC figure it is first necessary to define a fault model; for example, for the digital circuits, the stuck-at [2] fault model is often adopted. The stuck-at fault model is based on the binary behaviour of digital circuits founded on only two possible logic values. This digital circuits behaviour has allowed the definition of a practical fault model for digital circuits. Based on the stuck-at fault model, a list of possible faults present in the digital circuit is produced; this list is called fault list. Afterwards, a fault simulation campaign is performed with the aim of verifying the ability of the test to detect the considered faults. The FC is defined as the number of faults detected by the test method divided by the total number of faults present in the circuit. The FC figure provides a quantitative measure of the test effectiveness. In order to apply this approach to the power devices, it is first of all necessary to define an analog fault model suitable for them, i.e., a fault model for power devices, or more generally for analog devices. The fault model must represent the possible physical defects that can affect a device; moreover, it must be easy to handle, for example during fault simulation campaigns.

In contrast to the binary behavior of digital circuits based on only two possible logic values, for the analog and power circuits it is not possible to define a practical fault model since an analog signal can assume infinite values, as discussed in [2][3]. Furthermore, the intrinsic tolerances of the components, the electrical noise and the thermal effects can greatly influence the voltages and currents present in the circuits. All these facts did not allow until now the wide adoption of a fault model for the analog circuits. In turn, the absence of a universally adopted fault model for analog devices/modules did not allow a quantitative assessment of the effectiveness of a test targeting them. Currently, the effectiveness of an analog test is often qualitatively assessed considering the experience of engineers and the number of defective products returned from the field, as discussed in [4][5][6][7][8]. A product returned from the field is studied to identify the causes of the malfunction; afterwards, the tests are improved or

new specific tests are implemented. However, the emerging IEEE P2427 [3][9][10] standard introduces a first practical fault model for analog and power circuits and devices.

Moreover, power devices suffer of non-negligible thermal problems, which require special attention in safety-critical applications. In particular, the high voltages (in the order of KVs) and the high currents (about few tens of As) produce a considerable amount of heat in the power device. Therefore, numerous thermal problems due to the dissipation of the heat present inside the devices are present. It is necessary to introduce a suitable heatsink systems able to dissipate the heat produced in the power device and to keep the junction temperature within the allowed thresholds. The correct assembly and behavior of the heatsink system also requires to be tested. Currently, the heatsink test is in most cases performed using manual or automatic optical inspections [2][11][12] or resorting to the x-ray [2][11][12] technology; the x-ray inspection allows to observe the physical coupling between the heatsink and the power device in a more effective way than the simple optical inspection. Furthermore, the effectiveness of these thermal test methods is assessed qualitatively without considering any fault model.

As for the test of the power devices, also for the test of the heatsinks it is necessary to identify a methodology to quantitatively assess the effectiveness of thermal test methods. In addition, a thermal model must be identified to compute a quantitative FC for thermal test methods. To summarize, an efficient fault model for heat dissipation systems that can be used to assess the effectiveness of thermal test methods has not been proposed until now in the literature.

A further important aspect, required by different industrial standards for the safety-critical applications [13][14][15], concerns the analysis of the effect on the overall system behaviour of a fault present in a power device. The Failure Mode and Effect Analysis (FMEA) approach is typically used to analyze the failure modes of a product, identify the causes, and assess the effects on the whole system, as required by the IEC 61508 [1] standard. In other words, a methodology is necessary for studying and analyzing the effect of faults present in power devices on the overall system.

Currently, this analysis is performed based on theoretical considerations and by simulating the system. Furthermore, the FMECA approach allows identifying the critical faults present in a system, i.e., the faults that bring the system in a potentially harmful unsafe state. Finally, the FMECA analysis is useful for assessing the effectiveness of the fault mitigation strategies adopted and implemented in safety-critical systems.

#### 1.2 Thesis contributions

In this thesis, the problem of assessing the effectiveness of a test method for the power devices in an electronic system is faced. This analysis requires first the identification of a suitable fault model and the generation of the fault list for each power device. In this thesis, a methodology for generating automatically and systematically the fault list for power devices is proposed. Obviously, the fault list generated is composed of a finite and countable number of possible faults. The fault list is used in the fault simulation phase to compute a figure of FC for each test method.

The results obtained show the validity of the analog fault model proposed in the IEEE P2427 standard. Moreover, the proposed approach allows identifying failures never detected by any test method. Furthermore, the results highlight the dependence between the faults not detected and the phenomena that can inhibit the effectiveness of the test methods. For example, some electrical components placed in parallel to the power device under test can reduce the effectiveness of the tests by masking the effect of the faults. Moreover, with the results obtained with the proposed approach, it is possible to identify the best set of tests, considering the cost of each test methodology, the time required to perform each test, the effectiveness of each test and the test equipment necessary to run each test.

Furthermore, the problem of the junction temperature increase in the power devices associated with an incorrect assembling of the heatsinks on the devices is faced in this thesis. The effects of temperature on the power devices features are analyzed. These effects are exploited to perform an end of production test of the heatsink assembly. Again, different test methods were considered and assessed. I proposed a methodology to model thermal failures in a circuit simulator such as SPICE. The results obtained show how the effects of some faults are masked by the circuit; therefore, some faults are not detected by a test. Moreover, I proposed a methodology for testing the heatsinks assembled on power devices recurring only to electric measurements. The effectiveness of this methodology was evaluated experimentally and with a thermal model of the dissipation system.

Similar to the results obtained for the power devices test methods, also for the thermal test methods the results obtained show which faults are detected by a test method and which faults are never detected. This analysis allows to identify the causes that reduce the effectiveness of a test method, such as other devices that mask the effect of thermal faults, and to improve the thermal test method in order to increase its effectiveness.

Finally, a strategy for performing the FMECA analysis on a complex cyber-physical system is proposed. A cyber-physical system is an electro-mechanical system automatically and continuously controlled by a control software executed by a microcontroller. The approach proposed differs from other approaches in literature [14][16][17] for the cyber-physical system simulation modality and for the faults considered. Our approach, compared with others present in the literature, allows performing a more accurate simulation and in shorter times by simulating the whole electro-mechanical system, including the control software. Moreover, the proposed approach allows performing the FMECA analysis on a whole cyber-physical system, taking into account faults in power devices.

The results obtained show how the design tool, typically used during the cyber-physical system design phase, can be also used for studying the effects of faults and therefore for performing the FMECA analyzes required by numerous international standards. These design tools are equipped with efficient multilevel simulator that allows the developer to describe the systems at different levels (specific, behavioral, implementation) and in many cases to automatically generate the description of the implementation levels; for example, with the model-based approach, it is possible to automatically obtain the implementation of part of the code starting from a behavioral description of the software desired [18]. The model-based approach is also applicable to hardware, obtaining an implementation of a circuit starting from its behavioral description, as discussed in [19]. The multilevel simulation method allows to simulate the hardware and software elements present in a cyber-physical system at the same time, allowing to study the behavior of the faults mitigation mechanisms introduced by the engineers. Moreover, compared to traditional SPICE simulations, multilevel simulation introduces a considerable simulation times reduction, without significantly impacting the accuracy and the quality of the results, as evidenced by the experimental results obtained.

### 1.3 Thesis structure

In addition to Chapter 1, this thesis is composed of other 5 chapters.

Chapter 2 overviews the state of the art about the different test methodologies and about the analog fault models currently being defined and in use. Moreover, Chapter 2 describes the main power electronic devices typically used in electronic systems and describes their equivalent electrical models. Furthermore, the thermal aspects of the power devices are considered; in particular, the thermal model of the devices and the heat dissipation systems used for the power devices are considered. Finally, Chapter 2 provides an overview of the Failure Mode, Effects, and Criticality Analysis and about complex Cyber-Physical Systems.

Chapter 3 describes a possible methodology for generating a fault list for different power devices. Furthermore, in Chapter 3 the methodology used for performing an fault simulation of these devices is discussed. The effectiveness of different test methodologies for power devices is also evaluated in Chapter 3 on some real cases of study.

Chapter 4 proposes a methodology for testing the heatsinks assembled on the power devices; in addition, the effectiveness of the proposed methodology is assessed. A thermal fault model is also identified and a method to generate the fault list of the possible thermal faults is introduced.

Chapter 5 proposes a methodology for performing the FMECA on a cyberphysical system; in other words, a methodology for building a simulator useful for analyzing the impact of a fault affecting a power device on the whole system behavior is proposed.

Finally, Chapter 6 closes this thesis by summarizing the main results obtained and providing some considerations about some further possible works.

In addition to the 6 chapters, the thesis include 2 appendices. Appendix A offers an overview of the research activities performed on the test of microcontrollers used in safety-critical applications. Appendix B reports the list of publications produced classified by topic and type.

# Chapter 2

# **Background**

This section provides to the reader the main knowledge about power electronics, the semiconductor devices used in power circuits and the problems encountered in the power circuits test, with particular emphasis on the test of the power devices typically used in different analog and power applications. This chapter summarizes the state of the art relating to the test of power devices and to the fault models applied to the analog and power electronics. In addition, a wide background about the power devices electrical and thermal models and about the possible models to deal with cyber-physical systems is provided. Moreover, the role of the international standards that govern the development and the testing of the applications that use the power devices is also discussed in this chapter. In particular, subsection 2.1 provides an overview of the typical power devices used; subsection 2.2 discusses the new fault models recently introduced and formalized by the scientific and industrial community. Subsection 2.3 shows the typical test methods currently used to test the PCB in the factories, while subsection 2.4 discusses the models of some of the power devices typically used in the power applications. Subsection 2.5 focuses on the thermal aspects of power electronics; in particular, the strategies used for dissipating the heat produced by the power devices and the thermal models of the cooling systems typically used are discussed. Finally, subsection 2.6 discusses the problems associated with the impact of faults present in power devices on the whole cyber-physical system they are part of, as required by different international standards relating to the engineering and testing of safety-critical applications.

### 2.1 Power Electronics Applications

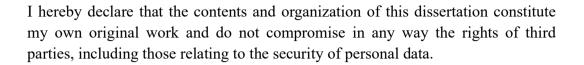

Power electronics is a multidisciplinary field that involves several aspects connected to electronics circuit design, control theory, signal processing, power semiconductor devices, magnetic phenomena, power network analysis and renewable energy [20][21]. Power devices are specifically developed with the purpose of handling high voltages and high currents. Power electronics can be defined as the application of solid-state electronics (i.e., of semiconductor devices) to the control and conversion of electrical power [21]. Typically, as discussed in [21], power systems are controlled by a microcontroller that manages and drives the power devices. Power electronics plays a fundamental role in modern technology and it is used in a wide variety of products and applications. Figure 1, extracted from "Power Electronics Handbook" [21], provides an overview about some of the main possible power electronics applications. Furthermore, Figure 1 shows the typical frequencies and powers involved in each application.

Figure 1 Typical power electronics applications

As shown in Figure 1, the applications that use power devices can work in a very wide range of powers; for example, the systems devoted of the production and distribution of electricity manage powers of a few megawatts (MW), while the electrical appliances normally found in homes manage typically few hundred watts or less. Between these extremes, there are numerous industrial and sanitary applications that operate at different powers and frequencies.

Among the different applications of power electronics, it is possible to identify many safety-critical applications, i.e., applications whose malfunction can cause serious consequences. For example, automotive applications, or more generally those applications associated with the people or goods movement, are classified as safety-critical. Moreover, the applications associated with the management, production, distribution of energy or the applications used for the management of strategic infrastructures, such as the internet, are also classified as safety-critical. In all these applications the power devices are considerably used. Figure 1 shows some of the different possible power devices used in different power applications. Among the devices typically used in power systems, it is possible to find the MOSFET transistors, typically used in medium-low power applications that require high switching speeds. Instead, BJT and IGBT transistors are used in applications that handle higher electrical powers; however, these devices have higher switching times and operate at lower frequencies. Instead, the Gate Turn Offs (GTOs) devices and the Thyristors devices are solid-state components conceptually similar to power diodes able of handling very high voltages and currents. Furthermore, all the power devices suffer of different thermal problems due to the management of the heat intrinsically produced by the power devices. Thermal aspects must also be considered during the engineering, production and testing of power systems.

### 2.2 Power Electronics Test Approaches and Metrics

Testing plays a fundamental role in product engineering, especially for safety-critical applications. The role of the test is to detect if something in the product went wrong [2], i.e., to verify that the system is able to function correctly without introducing any dangerous behavior. In practice, the purpose of the test is to check the whole system, the different subsystems present in the product and the components that compose each subsystem. The test does not identify the cause of the malfunction but indicates the presence of a malfunction in the system [2]. Following a failed test, some precautions are taken; for example, the system is placed in a safe state, i.e., in a state in which it is inactive or it cannot introduce dangerous behavior. Moreover, following a failed test, a diagnosis process can be initiated to determine exactly what went wrong [2]. The test can be performed at different moments in the product production and/or in the product operating phase or maintenance cycle.

Different tests are performed at the end of production, i.e., at the end-of-manufacturing of the product. The purpose of these tests is to verify that the manufactured product correctly works; for example, for detecting accidental defects that arise during the production of the product, such as a component not soldered on a PCB or a component badly soldered. Sometimes, the product does not pass the end-of- manufacturing test phase because the components/devices used were already affected by malfunction before their assembly in the final product. For this reason, an incoming test phase is typically introduced in order to verify the correct functioning of the components before their assembly.

In-field test is typically introduced in the safety-critical applications. The purpose of the in-field test is to periodically check the correct working of the product. Some in-field tests require that the test be performed with the product in a particular test configuration; in general, the in-filed tests are performed mainly at the system startup; for example, in the automotive area, the Electronic Control Units (ECUs) tests are performed during the ignition key phase [22].

Moreover, the test is fundamental in the production cycle of a product with the aim of creating safe and quality products [2]. For the end of production, a good testing process can eliminate all bad products before they reach the final user; instead, the in-field test can prevent than an over time failed product causing damage. Regardless of the test strategy adopted, it is necessary to assess the correctness and the effectiveness of the test strategies adopted [2].

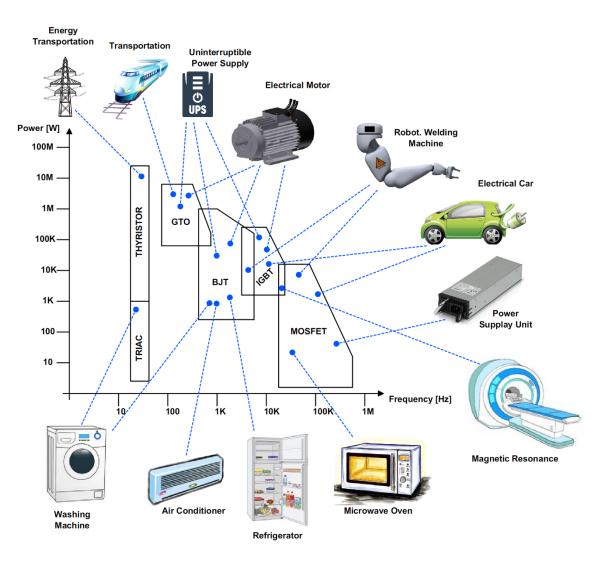

A test procedure is a sequence of steps that must be performed to execute a test; for example, the diagram of Figure 2 describes the steps necessary to verify the correct work of a resistor before it is assembled on the PCB of the final product. The first step consists of implementing the circuit shown in Figure 2 and applying a test stimulus to the component under test. A test stimulus is an electrical signal (typically a voltage or current test signal) applied to the component under test for performing the test. In the proposed example, the test stimulus consists of a continuous direct voltage (Vtest) applied to the resistor. Furthermore, in the first step, the response to the test stimulus provided by the component under test is measured. In this specific case, the current (Im) that flows in the resistor is measured.

Figure 2 Test procedure for a resistor

In the second step, the resistance (Rm) of the resistor under test is calculated using the Ohm's law. Finally, in the last step, the resistance value obtained during the test is compared with the nominal one value (Rn) defined by the manufacturer. The test passes if the Rm resistance value is similar to the Rn value defined by the resistor manufacturer, considering also the tolerance, or rather a valid range around the nominal value defined by the manufacturer. The test fails if the resistance value is outside of the validity range, as shown in the step 3 of Figure 2.

The test of a resistor is extremely simple; in literature, there are numerous test procedures for other components and devices. For example, in [23] the test procedure for a capacitor is discussed, while in [24][25][26] the test procedures for a diode, a MOSFET and an IGBT devices are discussed, respectively.

The real problem is how to assess the effectiveness of an analog test procedure. In literature, different methods have been proposed to perform the fault simulation of digital circuits [27][28] and recently to perform the fault simulation of analog circuits [29][30]; these approaches required a fault model identification. A fault model is an abstraction of the error caused by one or more particular physical defects; the fault model does not need to accurately model the physical failure but to describe the presence of the failure [2]. Afterwards, the fault model is applied to the product under test, generating the list of the possible faults. Finally, with a fault simulator, the ability of the test procedure to detect the injected faults is verified. As defined in [2], the Fault Coverage (FC) is defined as the ratio between the number of faults detected (DT) by the test procedure and the total number of the potential faults, as described by the equation (1). In the equation (1), the faults not detected by the test procedure are indicated with NDT. In general, at the end of the fault simulation procedure, each fault can be classified as DT or NDT.

$$FC = \frac{\#DT}{\#tot. faults} = \frac{\#DT}{\#DT + \#NDT}$$

(1)

Therefore, the FC represents an index of the effectiveness of a test procedure, i.e., it is the percent number of faults that the test procedure is able to detect. In general, the FC allows comparing the effectiveness of the different test strategies.

The binary behavior of digital systems has allowed the identification of a practical fault model called stuck-at [2]. This fault model allows generating a list of the possible faults present in a digital circuit. In the presence of a well-defined fault list, it is possible to assess the effectiveness of a test procedure, i.e., computing a fault coverage figure for a given test procedure [27][28].

In contrast to the test of digital systems, for the test of analog systems (including power ones), there are different additional difficulties that prevent the definition of a fault model. Consequently, the effectiveness of the test procedures

is currently assessed in an approximate and qualitative manner without resorting to a precise fault model, as discussed in section 1.1.

In subsection 2.2.1, the main difficulties present in the test of analog devices and systems are described, while subsection 2.2.2 describes a state of the art metric widely used for generating the fault list. Subsection 2.2.3 discusses the recent fault models introduced with the new emerging standard IEEE P2427 currently under definition. Finally, subsection 2.2.4 describes the most significant strategies currently used for assessing the effectiveness of a test method.

#### 2.2.1 Analog Testing Difficulties

Developing and assessing the effectiveness of an analog test procedure for the power device assembled on a PCB is currently an open problem. As discussed in [2], the test of the power device, or more generally the test of an analog circuit, is manually performed designing specific test solutions for each different case study. Currently, there are few Computer Aided Design (CAD) tools able of assisting the analog test design; in general, the test effectiveness is carried out without a precise fault model. As introduced in [2], the first tests developed for analog systems and for analog devices began in the 1960s. Usually, the first tests were developed in a functional way, considering the operating specifications and the features of the analog system under test. The aim of the functional test is to verify the correctness of the system behaviours to the test stimulus, i.e., that the response of the system to the test stimulus is that expected. This approach, currently still used and integrated with other test methods, is widely used for systems with few input ports and few output ports. Test stimuli applied to the system's input ports are generated by the system's technical specifications. However, this testing method is expensive in terms of time in case of the number of specifications is very wide; in particular, if the test is performed in a systematic way by testing all the possible specifications or combination of specifications. Furthermore, this approach requires a long time to perform all the possible functional tests. Nowadays, with the large scale automatic production manufacturing, it is not possible to think of performing all possible functional tests for each product. Therefore, it is advisable to identify a minimal but efficient set of tests, i.e., to combine different test strategies in order to maximize the overall effectiveness of the test also considering the execution costs of the different tests. In other words, considering different test aspects as the costs in terms of test execution time, the test equipment required and the time required to develop each test. However, for identifying the best set of tests, it is necessary to identify a methodology to assess the effectiveness of each test. A fundamental step of this workflow is to establish a list of possible faults that can afflict the analog system, and then verify which tests are able to detect each fault. Nowadays, the list of possible faults is manually generated considering the experience of the test engineers [6].

In contrast to the test of digital systems [2][31][32], the test of analog systems presents numerous additional difficulties. The first of these difficulties lies in the fault model to be adopted. Analog systems are composed of numerous devices and components whose characteristic parameters can widely vary [2]. Therefore, a nominal value and a range of acceptable values, defined around the nominal value, are typically indicated for each parameter of each device. The acceptable variations of these parameters are defined in the system engineering phase by means of simulations and circuit analysis [33]. Moreover, in addition to the intrinsic device parameters variations, there are many random variations due to the parasitic components present in the analog systems. Estimating the value of these parasitic components a prior is very difficult [11][12][34]; furthermore, the value of these parasitic components can significantly greatly among the different production batches. In addition, the components nominal parameters variation and the variation of the parasitic components depend on many external factors, including the manufacturing process variations, the thermal drift and the device ageing. Often, the list of possible faults is generated considering an excessive deviation of the component parameters [2]. This approach requires a complex circuit analysis for identifying the maximum deviation tolerated by the system. In [35] an exhaustive analysis of the variation of a single circuit parameter is proposed. The analysis is performed analytically by studying the mathematical relationships present between the different components of the circuit. The analytical study is validated through experimental laboratory tests performed on a grid converter influenced by a severe three-phase symmetrical fault. Moreover, the effect of the fault on the system stability is also considered. The approach proposed in [35] is inapplicable on a large scale or on complex analog systems composed of many devices. In general, analog circuits have complex relationships between input and output signals. Many analog circuits introduce non-linear relationships that greatly complicate the analysis of circuits [2] (for example, the characteristic equations of MOSFET transistors introduce a quadratic relationship). Moreover, the statistical distributions of analog faults may not be known with such precision of allowing an adequate faults statistical study [2]. For example, in [36], a faulty circuit passes all the conventional tests performed at the end-of-manufacturing. In particular, the fault hypothesized in [36] is masked during the test by other components present in the circuit.

Currently, the scientific and industrial community is looking for an efficient fault model to apply on the analog circuits. Recently, different efforts have been done for defining a fault model; the efforts performed converging on the emerging IEEE P2427 standard [3][37][38].

The next step consists in identifying a practical methodology for applying the proposed fault model to an electrical circuit or to a device; in other words, for generating automatically and systematically the list of possible faults present in a power device. In general, the effectiveness of an analog test is now often qualitatively assessed without using a fault model, by only considering the experience of engineers and the number of defective PCBs returned from the field [4][5][6][7][8].

A further difficulty present in the design and assessment of analog tests is associated with circuit simulation problems. In particular, from the numerical accuracy of the simulation algorithm used and from the precision and completeness of the devices electrical models used [2].

The measurement instruments used to perform the analog test also introduce additional difficulties that must be considered in the design of the test. In particular, the measurement errors introduced by the instruments can influence the effectiveness of the test. An electrical quantity, such as a voltage or a current, may not be easily measurable, or observable, due to uncertainties of the measurements. For example, the impedance of the electrical probes or the loading effect of the instruments can influence the electrical measurements during the test [2]. Furthermore, electrical noise, the bandwidth of the instrument and its accuracy can influence the effectiveness of the test by masking the effect of the fault [2][33][39], which it is therefore undetectable by the test.

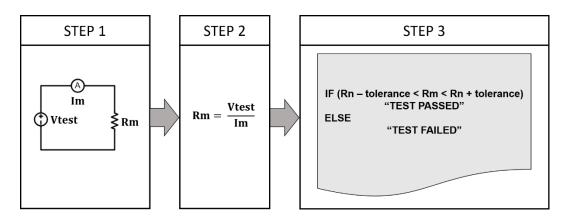

Furthermore, the electrical measurement must be physically possible; in other words, the measuring instrument must have easy access to the components and the power device under test present on the PCB; or more generally, to the test points present on the PCB. The test points are special locations on the PCB used to measure an electrical value or to apply a test stimulus [12], as shown in Figure 3. Typically, test points simplify the test but occupy space on the PCB and require numerous new PCB traces. Figure 3 shows two different ways of using the test points; in Figure 3.a the electrical contact is manually executed by hooking the test point with an electric probe. Typically this procedure is done by a technician. Instead, Figure 3.b shows a different test point strategy typically automatically contacted by test equipment.

**Figure 3 Test Points**

The next subsection shows the Presence Correctness Orientation Live Alignment (PCOLA) metric used to generate the list of possible faults present in a PCB. The PCOLA metric is specific for PCBs and not for devices assembled on them. However, one of the points of the PCOLA metric is related to the component test, even if the test proposed is not exhaustive.

#### **2.2.2 PCOLA**

As discussed in [40], the PCOLA metric allows generating the list of possible faults present on a PCB. In particular, the faults associated with the single devices and the single components assembled on the PCB are generated. Figure 4 shows a PCB in which the main elements that characterize it are defined, such as the electrical tracks used for connecting the different components, the pitches used for soldering the components and information about the orientation of the components. In addition, the extended version of this metric, called Presence Correctness Orientation Live Alignment / Shorts Opens Quality (PCOLA/SOQ), also considers the possible faults present between the tracks of the PCB. In particular, the SOQ extension deals with the connections between components. A connection is a place where a component is electrically attached to the PCB, typically a solder or press-fit joint. The following list discusses the 5 points of the PCOLA metric and the 3 points added with the SOQ extension.

- o **Presence**, this point required to verify that the component has been assembled on the PCB.

- o **Correctness**, this point requires of verifying that the right component has been assembled on the PCB.

- Orientation, this point requires of verifying that the component has been assembled on the PCB in the correct direction. In other words, that it has not been assembled with an orientation different than the exact one. This point is fundamental for all components that have polarity, such as diodes, transistors, integrated circuits (IC) or electrolytic capacitors. However, this point can be ignored for those components that do not have polarity, such as resistors, fuses or non-polarized capacitors.

- Live, this point requires of verifying that the component qualitatively to an electrical stimulus, i.e., that the component is "live" from an electrical point of view. In general, this point does no required a full functional qualification, but it verifies that the component is basically alive.

- Alignment, this point verifies that the device is correctly aligned in the PCB. In other words, that the component has not been assembled with small rotations or small inclinations, and that the component is centrally in the space reserved for it on the PCB.

- Shorts, this point verifies that there are no short circuits between the PCB tracks.

- Opens, this point verifies that there is the electrical continuity in each track present on the PCB; in particular, between the different pitches of each track.

- O Quality, this point checks the quality of the welds, i.e., that the weld is free of malformations, that too little or too much tin has been deposited, that there are no cold weld gaps.

Figure 4 Typical elements of a PCB

As discussed in [40], the points Presence, Correctness, Orientation, Live, Shorts and Opens are called fundamental, while the points Alignment and Quality are qualitative. The fundamental points are typically detected with in-circuit tests on each component, while the qualitative points can be detected with automatic optical inspection or with x-ray technology. However, for the purposes of this thesis, we consider only the faults potentially detectable with electrical tests, i.e., Presence, Correctness, Live, Shorts, Opens. Moreover, the Live point identifies a very generic and qualitative condition of a component or device. This condition may not be sufficient. Verifying the functioning of an electronic device may require an exhaustive test of all its features and functionality. For example, the test of a transistor may require to polarize the device in different configurations and verify that in each of them it assumes the desired behavior.

For the purposes of this thesis, the Live point requires to perform a generic device test to verify that it responds correctly to a test stimulus. This qualitative test does not constitute an exhaustive test of the analog or power device. Furthermore, the PCOLA metric does not require to assess the effectiveness of the test stimulus used.

#### 2.2.3 Fault Models for Analog Electronics

Currently, the effectiveness of a test procedure for analog systems is empirically assessed considering the experience of the engineers that developing the test, as discussed in [4][5][6][7][8] and in chapter 1. In the academic world, different researchers have been involved in the identification of a fault model applicable to analog systems, such as the stuck-at or the transient fault models used for the digital systems [2]. As reported in [38], a working group, that now includes over 40 members, was born in 2018 with the aim of developing a

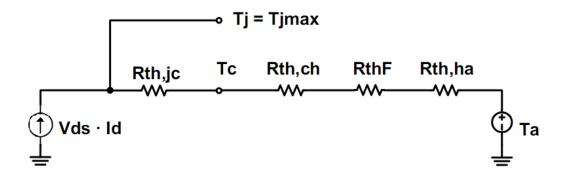

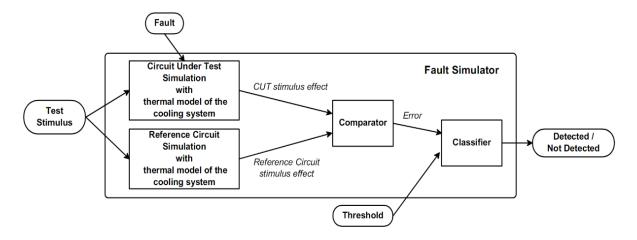

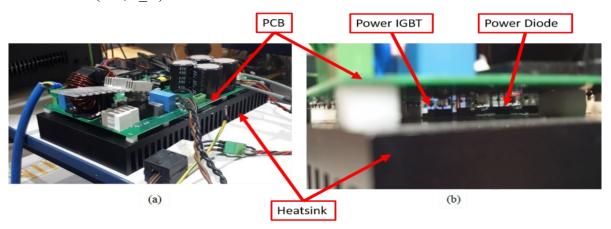

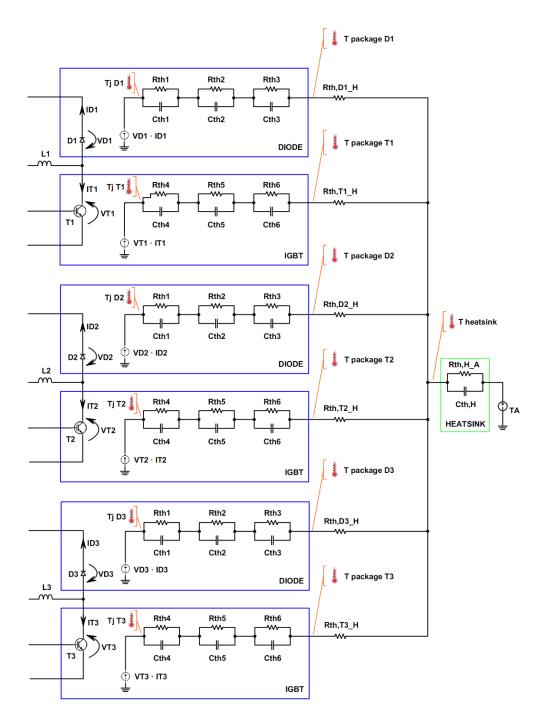

standard for analog defect modelling and coverage [37][41]. The recent IEEE P2427 standard emerged from the periodic meetings and research performed by this working group. The final publication of the P2427 is expected at the end of 2022, as discussed in [38]. The first contribution provided by the P2427 standard is a set of definitions aimed at clearly and concisely indicating the quantitative information about the fault coverage of a test procedure.