# POLITECNICO DI TORINO Repository ISTITUZIONALE

Design Space Optimization of a Three-Phase LCL Filter for Electric Vehicle Ultra-Fast Battery Charging

| Original Design Space Optimization of a Three-Phase LCL Filter for Electric Vehicle Ultra-Fast Battery Charging / Cittanti, Davide; Mandrile, Fabio; Gregorio, Matteo; Bojoi, Radu In: ENERGIES ISSN 1996-1073 ELETTRONICO 14:5(2021), p. 1303. [10.3390/en14051303] |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Availability: This version is available at: 11583/2872973 since: 2021-03-03T09:20:54Z                                                                                                                                                                                |

| Publisher: MDPI                                                                                                                                                                                                                                                      |

| Published<br>DOI:10.3390/en14051303                                                                                                                                                                                                                                  |

| Terms of use: openAccess                                                                                                                                                                                                                                             |

| This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository                                                                                                                              |

|                                                                                                                                                                                                                                                                      |

| Publisher copyright                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                      |

| (Article begins on next page)                                                                                                                                                                                                                                        |

Energies **2021**, 14, 1303 15 of 26

### 4. Simulation and Experimental Results

In this section, the harmonic attenuation achieved by the designed *LCL* filter and the current control performance of the AFE converter are verified by means of simulation and experimental testing.

The converter-side and grid-side inductors share the same design (i.e.,  $L = L_{\rm f}$ ), which is obtained from an internally developed optimization procedure taking into account a wide database of core geometries, core materials and wire formats/sizes [57]. The adopted loss and thermal models are described in [58].

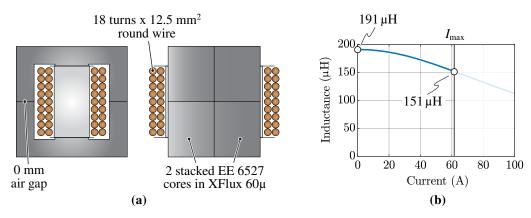

The resulting inductor design features two stacked EE 6527 cores in XFlux 60µ powder material from Magnetics [59], with an 18-turn winding of enameled round wire, as illustrated in Figure 12a. The powder material simultaneously provides high saturation flux density and low relative permeability (i.e.,  $\mu_r = 60$  in the present case), enabling an extremely compact inductor realization. In particular, the low permeability property allows to drastically reduce or even eliminate the air gap between the two core halves. In this way, the inductance value is no longer affected by the gap mechanical tolerance and the unwanted high-frequency winding losses caused by the air gap fringing field (e.g., present in ferrite core implementations) are avoided. However, the complete flux density range of the material (i.e., 0-1.6 T) is not exploited, due to the intrinsic soft saturation characteristics of powder materials [59]. In the present case the inductor is designed to operate between 191  $\mu$ H in no-load conditions and 151  $\mu$ H at  $I_{max}=61.5$  A, as illustrated in Figure 12b, utilizing only a 0–0.6 T interval to avoid excessive inductance variation during the fundamental line cycle. As a further note, a round wire with large cross-section is used since winding losses are completely dominated by the low-frequency (i.e., 50 Hz) current component. Therefore, the inductor optimization procedure aims to minimize the overall wire DC resistance, clearly avoiding winding arrangements with low window utilization such as litz wire implementations.

**Figure 12.** Schematic representation of the designed inductor ( $L = L_f$ ) (**a**) and differential inductance value dependence on the DC-bias current (**b**), which highlights the soft saturation characteristic of the selected powder core material.

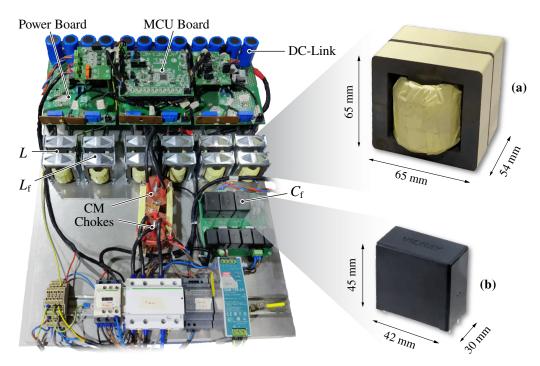

The AFE converter prototype, including the 3-level unidirectional T-type rectifier and the LCL filter, is shown in Figure 13. The rectifier (see Figure 7) employs 650 V Si MOSFETs switching at 20 kHz and 1200 V Si fast-recovery diodes. The AFE also includes an EMI filter consisting of a three-stage differential-mode filter (including the LCL stage) and a two-stage common-mode filter. Figures 13a,b provide a closer view of the realized filter inductors ( $L = L_{\rm f}$ ) and the selected filter capacitors ( $C_{\rm f}$ ), highlighting the size difference between them.

It is worth noting that the converter prototype is a  $60 \,\mathrm{kW}$  unit consisting of two three-phase sub-units in parallel. In the present case, only one  $30 \,\mathrm{kW}$  three-phase unit is operated and the boost inductors of the other unit are exploited as grid-side filter inductors ( $L_{\mathrm{f}}$ ).

Energies **2021**, 14, 1303 16 of 26

**Figure 13.** Overview of the active front-end (AFE) prototype utilized for the experimental tests, with highlight of (**a**) the realized inductor ( $L = L_f$ ) and (**b**) the selected capacitor ( $C_f$ ).

## 4.1. Filter Transfer Functions

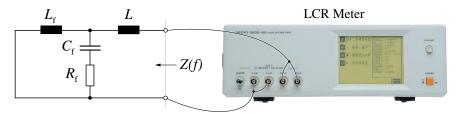

The only LCL filter transfer function that can be directly measured is Y(s), which represents the inverse of the filter impedance seen from the converter side. This impedance is measured with the setup illustrated in Figure 14, where a Hioki 5352-50 LCR meter is adopted for the task.

**Figure 14.** Experimental setup utilized to measure the value of Y = 1/Z (see Figure 15a).

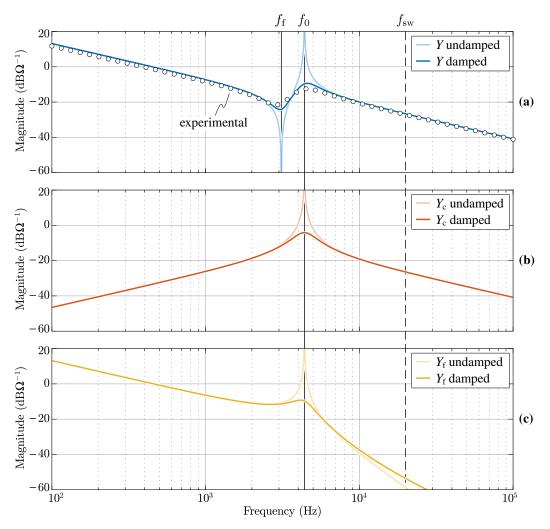

The transfer functions Y,  $Y_c$  and  $Y_f$  of the designed LCL filter are analytically calculated with the parameters reported in Figure 10 according to (1), (2) and (3), respectively. These transfer functions are illustrated in Figure 15 for both the undamped ( $R_f = 0$ ) and the damped ( $R_f = 0.8 \,\Omega$ ) cases. The measurement results of Y are reported in Figure 15a for comparison purposes, where a close match with the analytical model is observed. A slight asymptotic deviation between the two transfer functions is mainly attributable to the inductance value of 191  $\mu$ H at zero DC-bias current (i.e., the measurement condition), which differs from the design value of 175  $\mu$ H. Another discrepancy is observed around the two resonance frequencies  $f_f$  and  $f_0$ , where the experimental results show a stronger damping of the resonance peaks. This is caused by the unmodeled parasitic AC resistance of the filtering elements, mostly given by the inductors (i.e., winding and core losses). In particular, this high-frequency resistance contribution helps to damp the filter resonance, thus improving the converter closed-loop current control stability without generating additional losses at the grid frequency, as opposed to  $R_f$ .

Energies **2021**, 14, 1303 17 of 26

**Figure 15.** Analytical *LCL* filter transfer functions (**a**) Y, (**b**)  $Y_c$  and (**c**)  $Y_f$ , with and without passive damping (i.e.,  $R_f = 0.8 \Omega$  in the damped case). The value of Y measured experimentally is reported for comparison purposes in (**a**).

### 4.2. Filter Attenuation

The filter attenuation performance is verified experimentally by measuring the current injected into the grid and assessing its harmonic distortion.

The experimental setup consists of a grid emulator connected at the input of the *LCL* filter, emulating the European low-voltage grid (i.e.,  $U=230\,\mathrm{V_{RMS}}$ ,  $f=50\,\mathrm{Hz}$ ), and an electronic load connected at the output of the DC-link, emulating the DC/DC stage of the battery charger (i.e., the load). Since the AFE is directly connected to the grid emulator, this setup emulates a stiff grid with negligible inner impedance (i.e., SCR  $\approx \infty$ ), representing a worst case scenario from the filtering perspective.

The measurements are performed with a Teledyne LeCroy 500 MHz, 12-bit, 10 GS/s, 8-channel oscilloscope, employing isolated high-voltage differential probes for voltage measurements and standard current probes for current measurements.

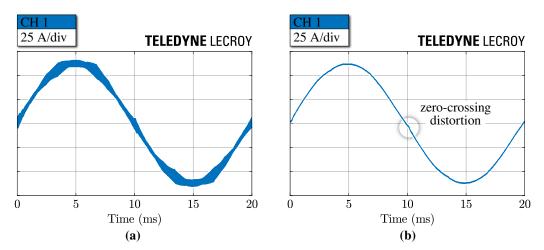

The experimental grid-side and converter-side current waveforms in nominal stationary conditions (i.e.,  $I=61.5\,\mathrm{A}$  and  $V_{\mathrm{dc}}=800\,\mathrm{V}$ ) are illustrated in Figure 16. The ripple attenuation provided by the LCL filter is evident, achieving a current THD of 1.2%. A slight distortion of the grid-side current is observed in proximity of the current zero crossings, as the T-type rectifier briefly enters the discontinuous conduction mode. This distortion is limited by the converter closed-loop control, which must be tuned to achieve high disturbance rejection performance [10].

Energies **2021**, 14, 1303 18 of 26

**Figure 16.** Experimental converter-side current i (a) and filtered grid-side current  $i_f$  (b) at I = 61.5 A and  $V_{dc} = 800$  V. Zero mid-point current modulation (ZMPCPWM) is adopted [20].

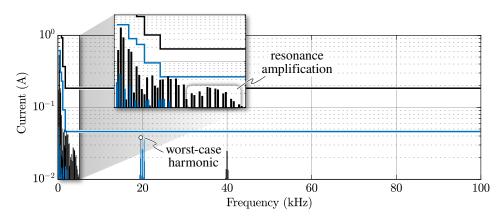

The filtered grid current spectrum is calculated by means of a DFT and the results are reported in Figure 17. It is observed that all harmonics comply with the IEEE 519 limits. In particular, the worst-case current harmonic at the design frequency  $f_{\rm d}=19.6\,{\rm kHz}$  is attenuated with a 20% margin.

The slight current distortion related to the converter unidirectional operation generates several low-frequency harmonics, nevertheless they are limited by the closed-loop current control. Moreover, a group of harmonics is visible around the resonance frequency  $f_0 = 4.39 \, \mathrm{kHz}$ , as the filter transfer function  $Y_\mathrm{f}$  tends to amplify the local harmonics (see Figure 15c). These harmonics are effectively limited by the filter passive damping.

**Figure 17.** Experimental filtered grid-side current  $i_f$  spectrum compared with IEEE 519 odd-order (black) and even-order (blue) harmonic limits. The worst-case harmonic at the design frequency is indicated and the amplification effect around the filter resonance frequency  $f_0$  is highlighted.

It is worth noting that with increasing grid impedance (i.e.,  $L_{\rm g} > 0$ ), the high-frequency filtering results can only improve, as the filter corner frequency  $f_0$  reduces and the asymptotic attenuation increases. Moreover, the high-frequency current harmonics are independent on the load, as they only depend on the PWM voltage harmonics. Therefore, the high-frequency (i.e., asymptotic) attenuation performance of the designed LCL filter can be considered successfully verified in all operating conditions.

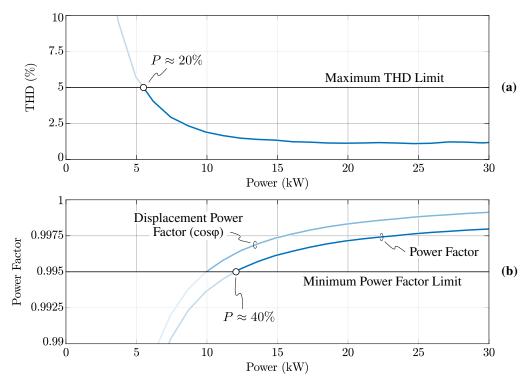

The low-frequency harmonic distortion, highlighted in Figure 17, depends on the converter load and is thus analyzed further. In particular, when operating at light load, the closed-loop current control is not able to perfectly compensate the large zero-crossing distortion related to DCM operation. This phenomenon leads to higher current THD at lighter loads, as illustrated in Figure 18a. It is important to keep in mind that the *LCL* filter is designed to comply with the operational constraints reported in Section 3, taking advan-

Energies **2021**, 14, 1303 19 of 26

tage of the AFE modular structure shown in Figure 7. Specifically, the converter modularity allows to turn-off selected modules at light load (i.e.,  $P_{\min} = 0.5 P$ ), thus ensuring the high-power operation of the remaining modules. Figure 18b shows that the current THD is limited below 5% between 20% and 100% of the nominal power (i.e., 6–30 kW), achieving acceptable distortion over the complete design operating range of the converter module.

Another quantity affected by the converter load is the power factor, as illustrated in Figure 18b, where both the displacement power factor ( $\cos \varphi$ ) and the total power factor (PF) are shown. The relation between the two is straightforward:

$$PF = \frac{\cos \varphi}{\sqrt{1 + THD^2}} \tag{16}$$

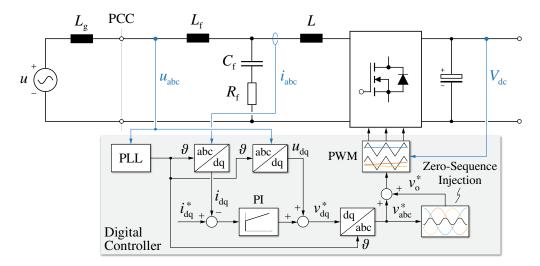

The adopted control strategy, schematically represented in Figure 19, does not compensate for the reactive current generated by the filter capacitors, thus leading to non-unity  $\cos\varphi$  operation. This feature, already taken into account during the design phase (i.e., see constraint ⑥), is directly related to the unidirectional operation of the active rectifier, which is not able to produce/absorb any significant amount of reactive power without affecting the input current distortion. Additionally, in this case, the adopted modular structure allows to maintain high power factor values at light load by turning off selected modules and ensuring the high-power operation of the remaining modules. Overall, Figure 18b shows that the total power factor stays above 0.995 between 40% and 100% of the nominal power (i.e., 12–30 kW), thus complying with the design restriction ⑥.

**Figure 18.** Experimentally measured grid-side current total harmonic distortion (THD) (a) and power factor (b) as functions of the transferred power. The maximum THD limit and the minimum power factor requirement are indicated.

#### 4.3. Converter Control Stability and Dynamic Response

The performance of the converter closed loop control is assessed experimentally with the hardware setup previously described. A conventional voltage-oriented control scheme is adopted [10,22,23,30] and is schematically illustrated in Figure 19.

Energies 2021, 14, 1303 20 of 26

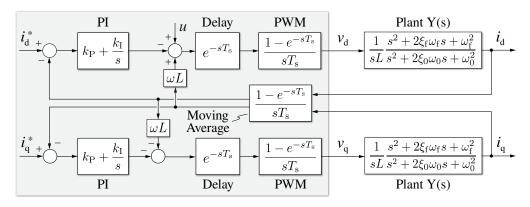

**Figure 19.** Simplified overview of the converter closed-loop current control: the digital controller schematic is highlighted in grey.

The rotating dq frame is exploited to obtain zero stationary error with a simple PI controller. The PCC voltages are measured to achieve the reference frame synchronization with the grid, which is performed by a phase locked loop (PLL). These voltages are passed through a resonant filter (i.e., the PLL itself) and are then fed forward in the current control loop, to unburden the integral part of the PI regulator. The digital sampling and update process is performed once per switching period ( $f_s = f_{sw} = 20\,\mathrm{kHz}$ ), however the current feedback values are obtained by means of oversampling (32 samples per switching period) and averaging, in order to improve the measurement reliability and thus the control performance around the current zero-crossings. In fact, conventional sampling does not yield the correct average current value when discontinuous conduction mode is encountered [60], thus inhibiting the accuracy of the current control and leading to increased low-frequency distortion.

The digital implementation of the control introduces three main delay components, which reduce the achievable control bandwidth and/or decrease the closed-loop stability margin [23]. The first delay contribution is directly related to the digital processing, which generates one sampling period delay ( $T_{\rm s}=1/f_{\rm s}$ ) between the measured quantities and the control signal output. The second component is linked to the PWM modulator, which introduces a zero-order hold (ZOH) effect with a  $T_{\rm s}$  duration . Finally, the last contribution derives from the current oversampling and averaging process, which results in a moving-average delay of  $T_{\rm s}/2$ . The complete dq current control block diagram is illustrated in Figure 20.

**Figure 20.** Complete block diagram of the  $i_d$  and  $i_q$  current control loops [10], including the plant transfer function Y(s).

Energies **2021**, 14, 1303 21 of 26

Since the LCL filter transfer function Y behaves as a pure inductance (i.e.,  $L_{\rm tot} = L + L_{\rm f} + L_{\rm g}$ ) up until the first resonance frequency  $f_{\rm f}$  (see Figure 4a), the current control tuning can be performed in a conventional way. The PI regulator is tuned to achieve a 60° phase margin [10], setting the open-loop cross-over frequency  $f_{\rm c}$  to 850 Hz and positioning the PI zero five times lower ( $f_{\rm z} = f_{\rm c}/5$ ) to achieve good disturbance rejection capabilities. Since the grid inductance  $L_{\rm g}$  is not known in general, the tuning is performed as

$$\begin{cases} k_{\rm P} = 2 \,\pi \, f_{\rm c} \, (L + L_{\rm f}) \\ k_{\rm I} = 2 \,\pi \, f_{\rm z} \, k_{\rm P} \end{cases}$$

(17)

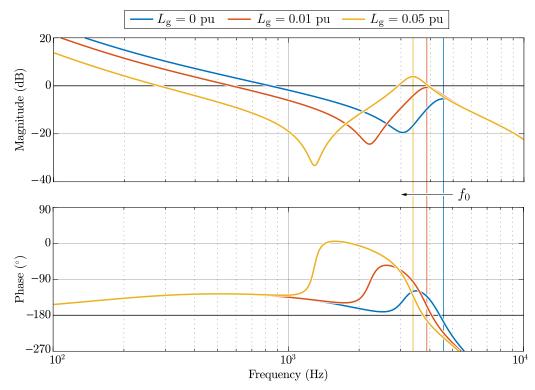

The current control open-loop transfer function is derived analytically and its magnitude and phase Bode plots are illustrated in Figure 21, for different values of grid inductance  $L_{\rm g}$ . Three situations are considered, namely an infinitely stiff grid ( $L_{\rm g}=0$  pu, SCR =  $\infty$ ), a typical grid for an EV fast charging connection ( $L_{\rm g}=0.01$  pu, SCR = 100) and a reasonably weak grid ( $L_{\rm g}=0.05$  pu, SCR = 20).

**Figure 21.** Bode plots of the analytical  $i_d$  and  $i_q$  compensated loop gains for different values of grid inductance  $L_g$ . The PI controllers are tuned according to (17).

In general, to achieve the closed-loop current control stability, the magnitude of the open-loop system transfer function has to be lower than 0 dB when its phase crosses  $-180^{\circ}$  (Nyquist criterion) [25]. From Figure 21 it is observed that the system gain margin decreases for higher values of  $L_{\rm g}$  (i.e., lower SCR), as the system resonance frequency  $f_0$  reduces and the peak magnitude increases. Theoretically, the stability limit is reached around  $L_{\rm g}\approx 0.05$  pu (SCR  $\approx 20$ ). Figure 21 also shows that a larger  $L_{\rm g}$  simultaneously reduces the converter bandwidth and the distance between  $f_{\rm c}$  and  $f_{\rm z}$ , thus decreasing the low-frequency phase margin and leading to a more nervous control response.

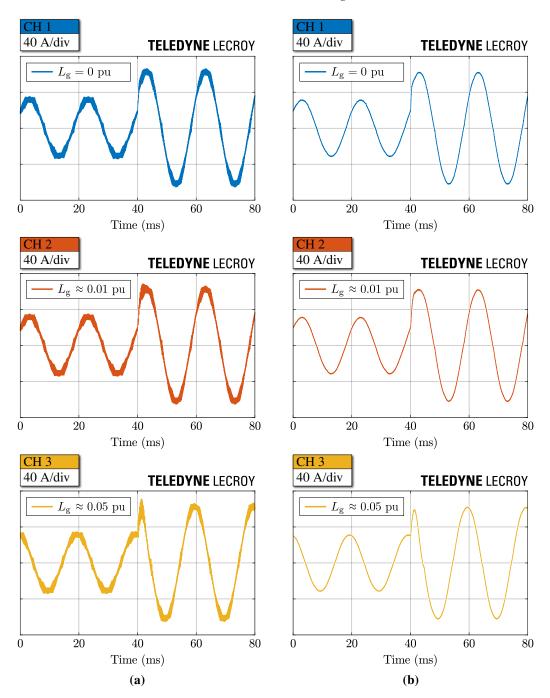

To experimentally verify the closed-loop control stability, the converter response to a reference current step is tested. Different values of grid inductance are emulated by inserting three-phase power inductors between the converter and the grid emulator, approximately achieving  $L_{\rm g}=0$  pu (i.e., no inductor),  $L_{\rm g}\approx 0.01$  pu and  $L_{\rm g}\approx 0.05$  pu.

Energies **2021**, 14, 1303 22 of 26

The results of the tests are illustrated in Figure 22, where the reference step response of both the converter-side current i and the grid-side current  $i_f$  are reported. It is observed that the control loop is stable in all conditions, however the converter-side current shows a damped high-frequency oscillation for large values of  $L_g$ .

**Figure 22.** Experimental current control loop step response between 50% and 100% load for different values of grid inductance  $L_g$ : (a) converter-side current i and (b) grid-side current  $i_f$ .

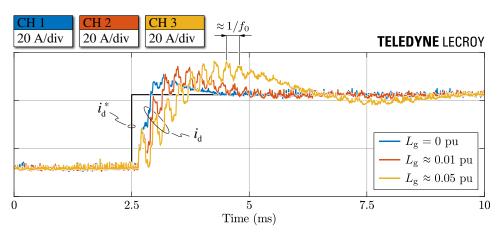

This is better highlighted in Figure 23, where the step response of the converter-side currents is reported on the d-axis of the rotating dq frame. The value of  $i_d$  is obtained from the digital-to-analog converter (DAC) of the microcontroller unit (MCU), therefore it is discretized in time (i.e., with a  $T_s$  periodicity) and is characterized by a large noise content. Figure 23 shows that higher grid inductance values cause at the same time a slower response (i.e., lower bandwidth), a higher overshoot (i.e., lower phase margin) and

Energies **2021**, 14, 1303 23 of 26

an increased high-frequency oscillation (i.e., lower gain margin at the phase cross-over frequency). All of these aspects could already be observed from the open-loop control transfer functions analysis previously reported (see Figure 21), nevertheless they have been verified experimentally.

The current reference step responses reported in Figure 23 show that the stability margin is still not reached for  $L_{\rm g}=0.05$  pu, as expected instead from the small-signal transfer function analysis. This is mainly due to the unmodeled AC resistance components of the system, which increase the damping of the resonance peaks (see Figure 15a) and thus lead to a wider control stability range.

In conclusion, the closed-loop current control stability is achieved for all grid SCR values up to 20 (i.e., weak grid connection). Therefore, the proposed *LCL* filter design and optimization procedure can be considered successfully validated.

**Figure 23.** Experimental d-axis current control loop step response between 50% and 100% load for different values of grid inductance. The value of  $i_d$  is obtained from the DAC of the MCU (i.e., as a voltage value between 0 and 3.3 V) and then rescaled, thus showing a high amount of noise.

#### 5. Conclusions

This work has presented a complete analysis, design and optimization procedure of a three-phase LCL filter for the active front-end unit of a modular EV ultra-fast battery charger. The proposed novel design methodology is based on the graphical representation of the filter design space in the  $(C_f, L_{tot})$  plane. By translating the constraints on the filter parameters into analytical equations, the design space boundaries are identified and the LCL filter design minimizing the total required inductance (i.e., optimizing the filter size/loss trade off) can be selected.

This design procedure has been applied to the AC-side filter of a  $30\,\mathrm{kW}$ ,  $20\,\mathrm{kHz}$  T-type unidirectional rectifier for ultra-fast charging applications. The functionality of the selected optimal LCL filter has been first verified in simulation, by checking the filter transfer functions and their effect on the current harmonic attenuation and the system stability. In particular, the LCL filter impedance (seen from the converter side) has been experimentally measured, showing an accurate matching with the analytical expectations and thus providing a preliminary validation of the attenuation capabilities of the filter. Then, the LCL filter has been tested together with an active rectifier prototype, to verify both the filter attenuation performance and the converter closed-loop current control stability. The current spectrum at full load has been shown to comply with the international technical standards, achieving results well within the prescribed limits, both for even and odd harmonics. The system stability has been finally verified with different values of grid impedance, emulating various grid point connections. Therefore, the proposed novel design methodology has been successfully validated.

Energies **2021**, 14, 1303 24 of 26

**Author Contributions:** Conceptualization, D.C. and F.M.; methodology, D.C. and F.M.; software, M.G.; validation, D.C., F.M. and M.G.; formal analysis, D.C.; investigation, D.C. and F.M.; resources, F.M. and R.B.; data curation, D.C., F.M. and M.G.; writing—original draft preparation, D.C.; writing—review and editing, D.C., F.M., M.G. and R.B.; visualization, D.C.; supervision, F.M. and R.B.; project administration, F.M. and R.B.; funding acquisition, R.B. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research was funded by the Power Electronics Innovation Center (PEIC), Politecnico di Torino.

**Conflicts of Interest:** The authors declare no conflict of interest.

#### References

- 1. Manzetti, S.; Mariasiu, F. Electric Vehicle Battery Technologies: From Present State to Future Systems. *Renew. Sustain. Energy Rev.* **2015**, *51*, 1004–1012, doi:10.1016/J.RSER.2015.07.010.

- 2. Clement-Nyns, K.; Haesen, E.; Driesen, J. The Impact of Charging Plug-In Hybrid Electric Vehicles on a Residential Distribution Grid. *IEEE Trans. Power Syst.* **2010**, 25, 371–380, doi:10.1109/TPWRS.2009.2036481.

- 3. Tu, H.; Feng, H.; Srdic, S.; Lukic, S. Extreme Fast Charging of Electric Vehicles: A Technology Overview. *IEEE Trans. Transp. Electrif.* **2019**, *5*, 861–878, doi:10.1109/TTE.2019.2958709.

- 4. Mandrile, F.; Cittanti, D.; Mallemaci, V.; Bojoi, R. Electric Vehicle Ultra-Fast Battery Chargers: A Boost for Power System Stability? *World Electr. Veh. J.* **2021**, 12, 16, doi:10.3390/wevj12010016.

- 5. Nicholas, M.; Hall, D. Lessons Learned on Early Electric Vehicle Fast-Charging Deployments. *Int. Counc. Clean Transp.* **2018**, 7–26. Available online: https://www.theicct.org/sites/default/files/publications/ZEV\_fast\_charging\_white\_paper\_final.pdf (accessed on 21 February 2020).

- 6. IEA. Global EV Outlook 2020–Analysis, 2020. Available online: https://www.iea.org/reports/global-ev-outlook-2020 (accessed on 21 February 2020).

- 7. Aggeler, D.; Canales, F.; Zelaya-De La Parra, H.; Coccia, A.; Butcher, N.; Apeldoorn, O. Ultra-Fast DC-Charge Infrastructures for EV-Mobility and Future Smart Grids. In Proceedings of the IEEE Innovative Smart Grid Technologies Conference Europe (ISGT Europe), Gothenburg, Sweden, 11–13 October 2010, doi:10.1109/ISGTEUROPE.2010.5638899.

- 8. Yilmaz, M.; Krein, P.T. Review of Battery Charger Topologies, Charging Power Levels, and Infrastructure for Plug-In Electric and Hybrid Vehicles. *IEEE Trans. Power Electron.* **2013**, *28*, 2151–2169, doi:10.1109/TPEL.2012.2212917.

- Channegowda, J.; Pathipati, V.K.; Williamson, S.S. Comprehensive Review and Comparison of DC Fast Charging Converter Topologies: Improving Electric Vehicle Plug-to-Wheels Efficiency. In Proceedings of the IEEE International Symposium on Industrial Electronics (ISIE), Buzios, Brazil, 3–5 June 2015; pp. 263–268. doi:10.1109/ISIE.2015.7281479.

- Cittanti, D.; Gregorio, M.; Bojoi, R. Digital Multi-Loop Control of a 3-Level Rectifier for Electric Vehicle Ultra-Fast Battery Chargers. In Proceedings of the AEIT International Annual Conference (AEIT), Catania, Italy, 23–25 September 2020, doi:10.23919/AEIT50178.2020.9241196.

- 11. Cittanti, D.; Gregorio, M.; Armando, E.; Bojoi, R. Digital Multi-Loop Control of an LLC Resonant Converter for Electric Vehicle DC Fast Charging. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 11–15 October 2020; pp. 4423–4430, doi:10.1109/ECCE44975.2020.9236177.

- 12. De Breucker, S.; Engelen, K.; D'hulst, R.; Driesen, J. Impact of Current Ripple on Li-ion Battery Ageing. *World Electr. Veh. J.* **2013**, *6*, 532–540, doi:10.3390/wevj6030532.

- 13. Teichmann, R.; Bernet, S. A Comparison of Three-Level Converters versus Two-Level Converters for Low-Voltage Drives, Traction, and Utility Applications. *IEEE Trans. Ind. Appl.* **2005**, *41*, 855–865, doi:10.1109/TIA.2005.847285.

- 14. Schweizer, M.; Friedli, T.; Kolar, J.W. Comparative Evaluation of Advanced Three-Phase Three-Level Inverter/Converter Topologies Against Two-Level Systems. *IEEE Trans. Ind. Electron.* **2013**, *60*, 5515–5527, doi:10.1109/TIE.2012.2233698.

- 15. Kolar, J.W.; Friedli, T. The Essence of Three-Phase PFC Rectifier Systems—Part I. *IEEE Trans. Power Electron.* **2013**, 28, 176–198, doi:10.1109/TPEL.2012.2197867.

- Cittanti, D.; Guacci, M.; Mirić, S.; Bojoi, R.; Kolar, J.W. Comparative Evaluation of 800V DC-Link Three-Phase Two/Three-Level SiC Inverter Concepts for Next-Generation Variable Speed Drives. In Proceedings of the International Conference on Electrical Machines and Systems (ICEMS), Hamamatsu, Japan, 24–27 November 2020; pp. 1699–1704, doi:10.23919/ICEMS50442.2020.9291123.

- 17. Ogasawara, S.; Akagi, H. Analysis of Variation of Neutral Point Potential in Neutral-Point-Clamped Voltage Source PWM Inverters. In Proceedings of the IEEE Industry Applications Conference, Toronto, ON, Canada, 2–8 October 1993; pp. 965–970, doi:10.1109/IAS.1993.299015.

- 18. Kolar, J.W.; Drofenik, U.; Zach, F.C. On the Interdependence of AC-Side and DC-Side Optimum Control of Three-Phase Neutral-Point-Clamped (Three-Level) PWM Rectifier Systems. In Proceedings of the International Power Electronics and Motion Control Conference (PEMC), Budapest, Hungary, 2–4 September 1996.

- Kolar, J.; Drofenik, U.; Zach, F. Current Handling Capability of the Neutral Point of a Three-Phase/Switch/Level Boost-Type PWM (VIENNA) Rectifier. In Proceedings of the IEEE Power Electronics Specialists Conference (PESC), Baveno, Italy, 23–27 June 1996; Volume 2, pp. 1329–1336, doi:10.1109/PESC.1996.548754.

Energies **2021**, 14, 1303 25 of 26

20. Cittanti, D.; Bojoi, R. Modulation Strategy Assessment for 3-Level Unidirectional Rectifiers in Electric Vehicle Ultra-Fast Charging Applications. In Proceedings of the AEIT International Conference of Electrical and Electronic Technologies for Automotive (AEIT AUTOMOTIVE), Turin, Italy, 18–20 November 2020, doi:10.23919/AEITAUTOMOTIVE50086.2020.9307416.

- 21. IEEE Recommended Practice and Requirements for Harmonic Control in Electric Power Systems. In *IEEE Std 519-2014*; IEEE: New York, NY, USA, 2014; pp. 1–29, doi:10.1109/IEEESTD.2014.6826459.

- Jalili, K.; Bernet, S. Design of LCL Filters of Active-Front-End Two-Level Voltage-Source Converters. IEEE Trans. Ind. Electron. 2009, 56, 1674–1689, doi:10.1109/TIE.2008.2011251.

- 23. Blasko, V.; Kaura, V. A Novel Control to Actively Damp Resonance in Input LC Filter of a Three-Phase Voltage Source Converter. *IEEE Trans. Ind. Appl.* **1997**, *33*, 542–550, doi:10.1109/28.568021.

- 24. Liserre, M.; Dell'Aquila, A.; Blaabjerg, F. Stability Improvements of an LCL-Filter Based Three-Phase Active Rectifier. In Proceedings of the IEEE Power Electronics Specialists Conference (PESC), Cairns, QLD, Australia, 23–27 June 2002; Volume 3, pp. 1195–1201, doi:10.1109/PSEC.2002.1022338.

- 25. Dannehl, J.; Liserre, M.; Fuchs, F.W. Filter-Based Active Damping of Voltage Source Converters With LCL Filter. *IEEE Trans. Ind. Electron.* **2011**, *58*, 3623–3633, doi:10.1109/TIE.2010.2081952.

- 26. Peña-Alzola, R.; Liserre, M.; Blaabjerg, F.; Sebastián, R.; Dannehl, J.; Fuchs, F.W. Analysis of the Passive Damping Losses in LCL-Filter-Based Grid Converters. *IEEE Trans. Power Electron.* **2013**, 28, 2642–2646, doi:10.1109/TPEL.2012.2222931.

- 27. Han, Y.; Yang, M.; Li, H.; Yang, P.; Xu, L.; Coelho, E.A.A.; Guerrero, J.M. Modeling and Stability Analysis of LCL -Type Grid-Connected Inverters: A Comprehensive Overview. *IEEE Access* 2019, 7, 114975–115001, doi:10.1109/ACCESS.2019.2935806.

- 28. Raggl, K.; Nussbaumer, T.; Kolar, J.W. Guideline for a Simplified Differential-Mode EMI Filter Design. *IEEE Trans. Ind. Electron.* **2010**, *57*, 1031–1040, doi:10.1109/TIE.2009.2028293.

- 29. Burkart, R.M.; Kolar, J.W. Overview and Comparison of Grid Harmonics and Conducted EMI Standards for LV Converters Connected to the MV Distribution System. In Proceedings of the Power Electronics South America Conference and Exhibition (PCIM South America), SaõPaulo, Brazil, 11–13 September 2012.

- 30. Liserre, M.; Blaabjerg, F.; Hansen, S. Design and Control of an LCL-Filter-Based Three-Phase Active Rectifier. *IEEE Trans. Ind. Appl.* **2005**, *41*, 1281–1291, doi:10.1109/TIA.2005.853373.

- 31. Channegowda, P.; John, V. Filter Optimization for Grid Interactive Voltage Source Inverters. *IEEE Trans. Ind. Electron.* **2010**, 57, 4106–4114, doi:10.1109/TIE.2010.2042421.

- 32. Reznik, A.; Simões, M.G.; Al-Durra, A.; Muyeen, S.M. LCL Filter Design and Performance Analysis for Grid-Interconnected Systems. *IEEE Trans. Ind. Appl.* **2014**, *50*, 1225–1232, doi:10.1109/TIA.2013.2274612.

- 33. Peña-Alzola, R.; Liserre, M.; Blaabjerg, F.; Ordonez, M.; Yang, Y. LCL-Filter Design for Robust Active Damping in Grid-Connected Converters. *IEEE Trans. Ind. Inform.* **2014**, *10*, 2192–2203, doi:10.1109/TII.2014.2361604.

- 34. Jayalath, S.; Hanif, M. Generalized LCL-Filter Design Algorithm for Grid-Connected Voltage-Source Inverter. *IEEE Trans. Ind. Electron.* **2017**, *64*, 1905–1915, doi:10.1109/TIE.2016.2619660.

- 35. Jayalath, S.; Hanif, M. An LCL-Filter Design With Optimum Total Inductance and Capacitance. *IEEE Trans. Power Electron.* **2018**, 33, 6687–6698, doi:10.1109/TPEL.2017.2754100.

- 36. Muhlethaler, J.; Schweizer, M.; Blattmann, R.; Kolar, J.W.; Ecklebe, A. Optimal Design of LCL Harmonic Filters for Three-Phase PFC Rectifiers. *IEEE Trans. Power Electron.* **2013**, *28*, 3114–3125, doi:10.1109/TPEL.2012.2225641.

- 37. Park, K.B.; Kieferndorf, F.D.; Drofenik, U.; Pettersson, S.; Canales, F. Weight Minimization of LCL Filters for High-Power Converters: Impact of PWM Method on Power Loss and Power Density. *IEEE Trans. Ind. Appl.* **2017**, 53, 2282–2296, doi:10.1109/TIA.2017.2657479.

- 38. Kolar, J.W.; Drofenik, U.; Biela, J.; Heldwein, M.L.; Ertl, H.; Friedli, T.; Round, S.D. PWM Converter Power Density Barriers. In Proceedings of the Power Conversion Conference (PCC), Nagoya, Japan, 2–5 April 2007, doi:10.1109/PCCON.2007.372914.

- 39. Boillat, D.O.; Friedli, T.; Mühlethaler, J.; Kolar, J.W.; Hribernik, W. Analysis of the Design Space of Single-Stage and Two-Stage LC Output Filters of Switched-Mode AC Power Sources. In Proceedings of the IEEE Power and Energy Conference (PEC), Champaign, IL, USA, 24–25 February 2012, doi:10.1109/PECI.2012.6184594.

- Cittanti, D.; Mandrile, F.; Bojoi, R. Optimal Design of Grid-Side LCL Filters for Electric Vehicle Ultra-Fast Battery Chargers. In Proceedings of the International Universities Power Engineering Conference (UPEC), Turin, Italy, 1–4 September 2020, doi:10.1109/UPEC49904.2020.9209771.

- 41. Burkart, R.; Kolar, J.W. Component Cost Models for Multi-Objective Optimizations of Switched-Mode Power Converters. In Proceedings of the IEEE Energy Conversion Congress (ECCE), Denver, CO, USA, 15–19 September 2013; pp. 2139–2146, doi:10.1109/ECCE.2013.6646971.

- 42. Park, K.; Burkart, R.M. Filter Hardware Optimization of Grid-Tied Converters: LCL vs. LLCL Filter. In Proceedings of the International Conference on Renewable Energy Research and Applications (ICRERA), Paris, France, 14–17 October 2018; pp. 209–214, doi:10.1109/ICRERA.2018.8566781.

- 43. Dannehl, J.; Fuchs, F.W.; Hansen, S.; Thøgersen, P.B. Investigation of Active Damping Approaches for PI-Based Current Control of Grid-Connected Pulse Width Modulation Converters With LCL Filters. *IEEE Trans. Ind. Appl.* **2010**, *46*, 1509–1517, doi:10.1109/TIA.2010.2049974.

- 44. Parker, S.G.; McGrath, B.P.; Holmes, D.G. Regions of Active Damping Control for LCL Filters. *IEEE Trans. Ind. Appl.* **2014**, 50, 424–432, doi:10.1109/TIA.2013.2266892.

Energies **2021**, 14, 1303 26 of 26

45. Peña-Alzola, R.; Liserre, M.; Blaabjerg, F.; Sebastián, R.; Dannehl, J.; Fuchs, F.W. Systematic Design of the Lead-Lag Network Method for Active Damping in LCL-Filter Based Three Phase Converters. *IEEE Trans. Ind. Inform.* **2014**, *10*, 43–52, doi:10.1109/TII.2013.2263506.

- Pan, D.; Ruan, X.; Bao, C.; Li, W.; Wang, X. Capacitor-Current-Feedback Active Damping With Reduced Computation Delay for Improving Robustness of LCL-Type Grid-Connected Inverter. IEEE Trans. Power Electron. 2014, 29, 3414–3427, doi:10.1109/TPEL.2013.2279206.

- 47. Erickson, R. Optimal Single Resistors Damping of Input Filters. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Dallas, TX, USA, 14–18 March 1999; Volume 2, pp. 1073–1079, doi:10.1109/APEC.1999.750502.

- 48. Wang, T.C.Y.; Ye, Z.; Sinha, G.; Yuan, X. Output filter design for a grid-interconnected three-phase inverter. In Proceedings of the IEEE Annual Conference on Power Electronics Specialist (PESC), Acapulco, Mexico, 15–19 June 2003; Volume 2, pp. 779–784, doi:10.1109/PESC.2003.1218154.

- 49. Xing, L.; Sun, J. Optimal Damping of Multistage EMI Filters. *IEEE Trans. Power Electron.* **2012**, 27, 1220–1227, doi:10.1109/TPEL.2011.2161617.

- 50. Wu, W.; He, Y.; Tang, T.; Blaabjerg, F. A New Design Method for the Passive Damped LCL and LLCL Filter-Based Single-Phase Grid-Tied Inverter. *IEEE Trans. Ind. Electron.* **2013**, *60*, 4339–4350, doi:10.1109/TIE.2012.2217725.

- 51. Beres, R.N.; Wang, X.; Liserre, M.; Blaabjerg, F.; Bak, C.L. A Review of Passive Power Filters for Three-Phase Grid-Connected Voltage-Source Converters. *IEEE J. Emerg. Sel. Top. Power Electron.* **2016**, *4*, 54–69, doi:10.1109/JESTPE.2015.2507203.

- 52. Liserre, M.; Teodorescu, R.; Blaabjerg, F. Stability of Photovoltaic and Wind Turbine Grid-Connected Inverters for a Large Set of Grid Impedance Values. *IEEE Trans. Power Electron.* **2006**, *21*, 263–272, doi:10.1109/TPEL.2005.861185.

- 53. Hoevenaars, T.; LeDoux, K.; Colosino, M. Interpreting IEEE STD 519 and Meeting its Harmonic Limits in VFD Applications. In Proceedings of the IEEE Petroleum and Chemical Industry Conference (PCIC), Houston, TX, USA, 15–17 September 2003; pp. 145–150, doi:10.1109/PCICON.2003.1242609.

- 54. Leibl, M.; Kolar, J.W.; Deuringer, J. Sinusoidal Input Current Discontinuous Conduction Mode Control of the VIENNA Rectifier. *IEEE Trans. Power Electron.* **2017**, *32*, 8800–8812, doi:10.1109/TPEL.2016.2641502.

- Cittanti, D.; Vico, E.; Gregorio, M.; Mandrile, F.; Bojoi, R. Iterative Design of a 60 kW All-Si Modular LLC Converter for Electric Vehicle Ultra-Fast Charging. In Proceedings of the AEIT International Conference of Electrical and Electronic Technologies for Automotive (AEIT AUTOMOTIVE), Turin, Italy, 18–20 November 2020, doi:10.23919/AEITAUTOMOTIVE50086.2020.9307381.

- 56. Holmes, D.G.; Lipo, T.A. Pulse Width Modulation for Power Converters: Principles and Practice; John Wiley: Hoboken, NJ, USA, 2003.

- 57. Borlo, S.; Cittanti, D.; Gregorio, M.; Mandrile, F.; Musumeci, S. Comparative CCM-DCM Design Evaluation of Power Inductors in Interleaved PFC Stage for Electric Vehicle Battery Chargers. In Proceedings of the International Conference on Clean Electrical Power (ICCEP), Otranto, Italy, 2–4 July 2019; pp. 180–186. doi:10.1109/ICCEP.2019.8890112.

- 58. Leibl, M.; Kolar, J.W. Comparative Analysis of Inductor Concepts for High Peak Load Low Duty Cycle Operation. In Proceedings of the International Power Electronics Conference (IPEC), Hiroshima, Japan, 18–21 May 2014; pp. 899–906, doi:10.1109/IPEC.2014.6869694.

- 59. Magnetics. Available online: https://www.mag-inc.com/Home (accessed on 27 January 2021).

- 60. Cittanti, D.; Gregorio, M.; Mandrile, F.; Bojoi, R. Full Digital Control of an All-Si On-Board Charger Operating in Discontinuous Conduction Mode. *Electronics* **2021**, *10*, 203, doi:10.3390/electronics10020203.