# POLITECNICO DI TORINO Repository ISTITUZIONALE

#### A 3-3.8 GHz Class-J GaN HEMT Power Amplifier

#### Original

A 3-3.8 GHz Class-J GaN HEMT Power Amplifier / Nasri, Abbas; Estebsari, Motahhareh; Toofan, Siroos; Piacibello, Anna; Ramella, Chiara; Camarchia, Vittorio; Pirola, Marco. - STAMPA. - (2020), pp. 416-419. ((Intervento presentato al convegno 2020 23rd International Microwave and Radar Conference (MIKON) tenutosi a Warsaw, Poland, Poland nel 5-8 Oct. 2020 [10.23919/MIKON48703.2020.9253829].

Availability:

This version is available at: 11583/2854540 since: 2020-12-12T15:28:58Z

Publisher:

Institute of electrical and electronics engineering

Published

DOI:10.23919/MIKON48703.2020.9253829

Terms of use: openAccess

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright

IEEE postprint/Author's Accepted Manuscript

©2020 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collecting works, for resale or lists, or reuse of any copyrighted component of this work in other works.

(Article begins on next page)

## A 3-3.8 GHz Class-J GaN HEMT Power Amplifier

Abbas Nasri<sup>1</sup>, Motahhareh Estebsari<sup>1</sup>, Siroos Toofan<sup>3</sup>, Anna Piacibello<sup>2</sup>, Chiara Ramella<sup>1</sup>, Vittorio Camarchia<sup>1</sup>, Marco Pirola<sup>1</sup>

<sup>1</sup> Department of Electronics and Telecommunications, Politecnico di Torino, Turin, Italy

<sup>2</sup> Department of Electronic Engineering, University of Rome Tor Vergata, Rome, Italy

<sup>3</sup> Department of Electronic Engineering, University of Zanjan, Zanjan, Iran

abbas.nasri@polito.it, marco.pirola@polito.it, s.toofan@znu.ac.ir

Abstract— This paper presents a wideband class J power amplifier (PA) based on a packaged 10 W GaN HEMT device covering the 3 GHz to 3.8 GHz frequency range. A good trade-off between efficiency and gain has been pursued in synthesizing the second harmonic output termination. The achieved output power is in excess of 41 dBm with drain efficiency ranging from 59% to 65.5% and a small signal gain above 14 dB. Preliminary large signal measurements at 3.3 GHz confirm the proper behavior of the PA.

Keywords— Class J PA, Wideband PA, GaN HEMT, Harmonic control.

#### I. INTRODUCTION

With the continuous evolution of wireless systems towards higher data rates, the need for high-performance transceivers is increasing day-by-day [1, 2]. From the system efficiency standpoint, the most important block in the wireless transceivers is the power amplifier (PA). PAs are required to provide increasingly higher efficiencies together with high gain in increasingly wider bandwidths to allow for complex modulation schemes to be adopted. At the same time, linearity of the PA should be ensured to limit spectral regrowth and other non-linear effects [3]. Common PA operating classes cannot achieve all the target specifications, in terms of gain, linearity efficiency and bandwidth at the same time. Class A power amplifiers have very good linearity but relatively low drain efficiency. On the contrary, class B and class AB PAs, thanks to a lower conduction angle, are able to enhance the achievable efficiency both at saturation and in power back-off and, thus, are usually preferred in presence of amplitude modulated signals, even if they show poorer linearity and may require the adoption of linearization techniques [4]. However, a main limitation of the class AB/B PA concerns the achievable bandwidth. The class J overcome this limitation achieving same performance of class AB/B PAs in a wider bandwidth. In a class J power amplifier the output matching network should present a purely reactive impedance at the second harmonic and a reactive-resistive impedance at the fundamental harmonic [5, 6]. Hence, the advantage of the class J PA with respect to tuned-load classes, which require instead harmonic short or open circuits, is that the output matching network is less resonant, thus less sensitive to frequency and wider bandwidth [7].

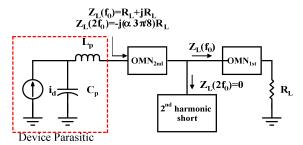

Fig. 1. Output section of a class J power amplifier.

In this paper, a wideband and high efficiency class J power amplifier is designed with the CGH40010F GaN HEMT from Cree/Wolfspeed. Drain and gate voltage of this circuit are 28 V and -2.8 V, respectively, corresponding to a quiescent bias current around 160 mA (8% class-AB). The proposed output matching network (OMN) structure, based on a relatively simple but effective topology, provides the possibility to trade-off between maximum efficiency and bandwidth. Simulation results show that a drain efficiency above 61.5% can be achieved at an output power higher than 10 W and with an associated gain in excess of 10.3dB in the frequency range from 3 GHz to 3.8 GHz. The implemented PA has been fabricated and a large-signal characterization at 3.3 GHz has been carried out showing 40 dBm output power with associated gain and efficiency of 10 dB and 54 %, respectively.

This paper is organized as follows. In Section II, the theory of the class J PA is briefly reviewed and the design of the proposed power amplifier is detailed. Section III presents the results obtained both in simulations and in measurements. Finally, in Section IV some conclusions are drawn.

#### II. CLASS J PA DESIGN

The class J power amplifier is based on harmonic control at the device output. The output section of a class J PA is shown in Fig. 1, where the active device is represented by an ideal current generator with output parasitic elements. In this work, the 10 W CGH40010F GAN HEMT device from Cree/Wolfspeed is adopted. Among the possible models of the output section of the device available in literatures [8, 9], we selected a simple model with a parallel capacitance  $C_P = 1.27\,\mathrm{pF}$  and a series inductance  $L_P = 0.73\,\mathrm{nH}$ .

The output matching network consists of three parts: the second harmonic output matching network, terminated by a harmonic short, and the matching network at the fundamental frequency. The former is needed to synthesize the proper purely imaginary load at second harmonic, while the latter sets the proper real and imaginary part of the load at the fundamental frequency.

The intrinsic drain current of a class J PA is defined as [6]:

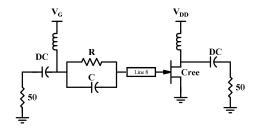

Fig. 2. Stabilization network of the transistor.

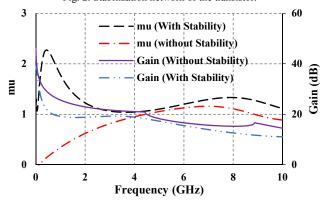

Fig. 3. Mu stability factor and maximum available gain of the device with respect to frequency with and without the stabilization network.

$$i_D(\varphi) = \frac{I_{\text{max}}}{\pi} + \frac{I_{\text{max}}}{2}\cos(\varphi) + \frac{2I_{\text{max}}}{3\pi}\cos(2\varphi) + \dots$$

(1)

where  $\varphi$  is angular phase and  $I_{max}$  is the maximum current of the transistor. The drain-source voltage is defined as [6]:

$$V_{DS}(\varphi) = V_{K} + (V_{DD} - V_{K})\cos(\varphi) - \alpha(V_{DD} - V_{K})\sin(\varphi) + 0.5\alpha\sin(2\varphi) + \dots$$

(2)

where  $V_K$ ,  $V_{DD}$  and  $\alpha$  are the knee voltage of transistor, the supply voltage and the reactive component coefficient of the class J PA, respectively. From equations (1) and (2), the required output impedance at the fundamental and second harmonic can be found to be:

$$Z_L(f_0) = (1+j\alpha)R_{opt}$$

(3)

$$Z_{L}(2f_{0}) = -j\frac{3\pi}{8}\alpha R_{opt}$$

(4)

where  $R_{opt} = 2(V_{DD}-V_K)/I_{max}$  is the optimum load for power of the device. According to equations (3) and (4), a resistive-reactive impedance at fundamental harmonic and a purely reactive impedance at second harmonic are needed, together with a short circuit at all other harmonics, which is however quite easy to be achieved, thanks to the output parasitic capacitance.

The selected device is not unconditionally stable in the target operating frequency range, as shown in Fig. 3, thus the very first step to design the PA is selecting a suitable stabilization network to ensure unconditional stability at all frequencies without compromising gain and efficiency. As shown in Fig. 2, a high-pass parallel RC circuit ( $R = 62\Omega$  and  $C = 4.7 \, pF$ ) in series with the gate has been used to stabilize the transistor. Fig. 3 compares the Mu stability factor and the maximum available gain with and without the stability network. As shown, unconditional stability is achieved maintaining a good trade-off with gain.

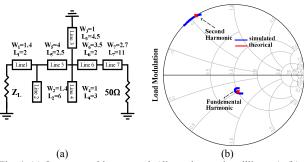

Fig. 4. (a) Output matching network (dimension are in millimetre). (b) Variation of the load impedance of OMN with respect to frequency.

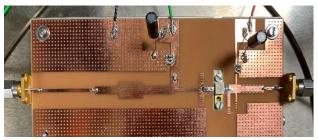

Fig. 5. Photograph of the fabricated class-J power amplifier.

The designed output matching network (OMN) is shown in Fig. 4 (a). The output parasitic capacitance of the transistor has not been resonated out in the OMN, but, instead it has been effectively exploited for achieving wideband matching [9]. As anticipated in Fig. 1, the matching network consists of three parts: Line 2 and Line 1 provide the desired reactance at second harmonic. Line 3 only provides the drain bias supply and does not affect match. All other elements provide the proper impedance at fundamental frequency. Fig. 4 (b) shows the synthesized output intrinsic impedances at fundamental and second harmonic.

#### III. PA PERFORMANCE

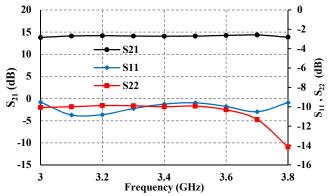

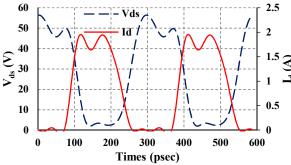

The photograph of the fabricated class J PA is shown in Fig. 5. The microstrip circuit is designed on FR4 substrate ( $\varepsilon_r=4.6$ , substrate height of 0.8 mm and metal thickness of 35 µm). All passive structures have been EM simulated to provide a highly accurate model. Small-signal simulation results (S-parameters) of the PA are presented in Fig. 6: the small-signal gain is between 14dB and 15dB in the 3GHz to 3.8GHz range while input/output return losses are better than -10 dB. Time domain simulation results at 3.3 GHz are demonstrated in Fig. 7 reporting the intrinsic drain current and the drain-source voltage waveforms: as expected for a class J PA, voltage is half-sinusoidal, thanks to the shaping effect of the second harmonic load, while the current-to-voltage phase shift is different from 180° due to reactive component of the fundamental load.

Fig. 6. Simulated S-parameters of the proposed class J power amplifier.

Fig. 7. Simulated time-domain drain-source voltage (dashed line) and drain current (solid line) waveforms at 3.3 GHz.

Fig. 8. Simulated performance at 3.3 GHz.

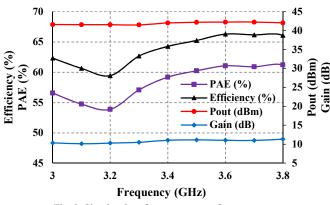

Fig. 9. Simulated performance versus frequency.

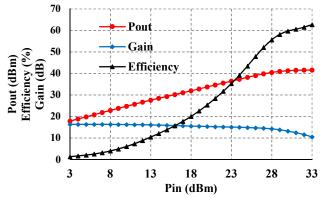

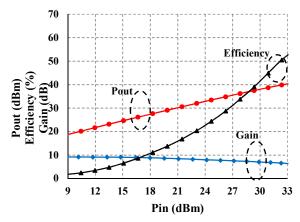

Fig. 10. Measured performance at 3.3 GHz.

Large-signal simulation result in continuous wave (CW) at 3.3 GHz are shown in Fig. 8, reporting output power, gain, and drain efficiency versus input power. Fig. 9 shows instead the saturated performance of the PA in the entire bandwidth. As can be seen from these figures, the performance is very good in the entire design frequency range: output power is above 41 dBm with an associated gain higher than 10 dB, and both show very good flatness (1dB). Drain efficiency is larger than 59.5% at all frequencies with peak value of 66.5%.

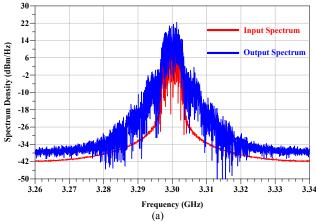

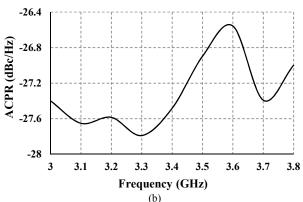

The fabricated PA has been characterized under CW large-signal. The measurement results at 3.3 GHz obtained are shown in Fig. 10: the saturated output power is 40dBm with 54% drain efficiency. Small-signal gain is almost 10dB, while gain compression at saturation is slightly below 4dB. These results can be considered satisfying, taking into account also that the selected bandwidth close to the maximum limit of both the active device and the substrate. Interestingly, the PA proved to be able to maintain very good large-signal performance in a wide measurement bandwidth. Finally, a system-level simulation at 3.3 GHz has also been performed, adopting a 16QAM input modulated signal with 5MHz bandwidth and with 4dB peak to average power ratio (PAPR). The input and output power spectrum at 41 dBm output power are shown in Fig. 11 (a). The ACPR versus frequency is less than -26.5 dBc/Hz as illustrated in Fig. 11 (b), proving that the proposed PA linearity is fairly good, and comparable to that of a class AB amplifier. This relaxes the requirements on the linearization circuit, which is crucial from the system efficiency standpoint. Table I demonstrates that the proposed power amplifier well compares to other class J modules adopting same device.

Fig. 12. (a) Input and output power spectrum at 3.3 GHz, (b) ACPR versus frequency.

### TABLE I. PERFORMANCE OF THE PROPOSED PA AND COMPARISON WITH PREVIOUS WORKS.

| Ref            | [1]     | [2]     | [4]     | This work (sim/meas) |     |

|----------------|---------|---------|---------|----------------------|-----|

| Freq.<br>(GHz) | 2.5-3.5 | 1.6-2.2 | 2.3-2.7 | 3-3.8                | 3.3 |

| Gain<br>(dB)   | 10      | 9-12    | 12-15   | 14-15                | 10  |

| Pout<br>(dBm)  | 39.9    | 49-40   | 40-40.8 | 41.5-42.5            | 40  |

| DE<br>(%)      | 66-68   | 55-68   | 60-70   | 55-68                | 54  |

#### IV. CONCLUSION

A class J power amplifier working in the 3 GHz to 3.8 GHz bandwidth is presented in this paper. This circuit is designed with the CGH40010F GaN HEMT transistor. A simple but effective output matching network, embedding the drain-source parasitic capacitance of the device, has been adopted, allowing for wideband operation. An optimum trade-off between bandwidth and efficiency has been pursued, achieving, in simulation, more than 60% drain efficiency in the whole frequency range at an output power in excess of 41 dBm and with more than 10 dB gain. Preliminary measurement result at 3.3 GHz achieved 40 dBm output power with 54% efficiency, showing the proper behaviour of the proposed PA.

#### REFERENCES

- E. C. Tubitak, O. Palamutcuogullan, O. K. Tubitak, B. S. Yarman and M. Yazgi, "High Efficiency Wideband Power Amplifier with Class-J Configuration," 2018 18th Mediterranean Microwave Symposium (MMS), Istanbul, pp. 394-397, 2018.

- [2] K. Mimis, K. A. Morris, S. Bensmida, and J. P. McGeehan, "Multichannel and Wideband Power Amplifier Design Methodology for 4G Communication Systems Based on Hybrid Class-J Operation," *IEEE Trans. Microw. Theory Techn*, vol. 60, no. 8, pp. 2562-2570, 2012.

- [3] A. Piacibello, R. Quaglia, V. Camarchia, C. Ramella and M. Pirola, "Dual-input driving strategies for performance enhancement of a doherty power amplifier," 2018 IEEE MTT-S International Wireless Symposium (IWS), Chengdu, 2018, pp. 1-4.

- [4] N. Tuffy, A. Zhu, and T. J. Brazil, "Class-J RF power amplifier with wideband harmonic suppression" in IEEE MTT-S Int. Microw. Symp. Dig., Baltimore, MD, USA, pp. 1-4, 2011.

- [5] A. R. Dehqan, S. Toofan, and A. Medi, "A Highly efficient class-EF<sub>2</sub> power amplifier in GaAs pHEMT technology," vol. 93, no. 2, pp. 197-203, Sep. 2017.

- [6] P. Wright, J. Lees, J. Benedikt, P. J. Tasker, and S. C. Cripps, "A Methodology for Realizing High Efficiency Class-J in a Linear and Broadband PA," *IEEE Trans. Microw. Theory Techn.*, vol. 57, pp. 3196–3204, Nov. 2009.

- [7] A. Alizadeh, M. Frounchi, and A. Medi, "Dual-band design of integrated class-J power amplifiers in GaAs pHEMT technology," *IEEE Trans. Microw. Theory Techn.* vol. 65, pp. 3034-3045, Mar. 2017.

- [8] A. Piacibello, R. Quaglia, M. Pirola and S. Cripps, "Design of an S-Band Chireix Outphasing Power Amplifier Based on a Systematic Bandwidth Limitation Analysis," 2018 13th European Microwave Integrated Circuits Conference (EuMIC), Madrid, 2018, pp. 186-189.

- [9] V. Camarchia, A. Piacibello and R. Quaglia, "Integrated Doherty power amplifiers for satellite systems: challenges and solutions," 2019 IEEE Topical Workshop on Internet of Space (TWIOS), Orlando, FL, USA, 2019, pp. 1-4.