### POLITECNICO DI TORINO Repository ISTITUZIONALE

### Optimization Tools for ConvNets on the Edge

Original

| Optimization Tools for Convincts on the Edge / Peluso, Valentino (2020 Sep 03), pp. 1-158.                               |

|--------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                          |

|                                                                                                                          |

| Availability:                                                                                                            |

| This version is available at: 11583/2845792 since: 2020-09-16T09:29:19Z                                                  |

| Publisher:                                                                                                               |

| Politecnico di Torino                                                                                                    |

| Published                                                                                                                |

| DOI:                                                                                                                     |

|                                                                                                                          |

| Terms of use: Altro tipo di accesso                                                                                      |

| This article is made available under terms and conditions as specified in the corresponding bibliographic description in |

| the repository                                                                                                           |

|                                                                                                                          |

|                                                                                                                          |

| Publisher copyright                                                                                                      |

|                                                                                                                          |

|                                                                                                                          |

|                                                                                                                          |

|                                                                                                                          |

(Article begins on next page)

# Doctoral Dissertation Doctoral Program in Computer and Control Engineering (32.nd cycle)

# Optimization Tools for ConvNets on the Edge

### Valentino Peluso

\* \* \* \* \* \*

### **Supervisors**

Prof. Enrico Macii, Supervisor Prof. Andrea Calimera, Co-supervisor

#### **Doctoral Examination Committee:**

Prof. Rene van Leuken, Referee, Delft University of Technology

Prof. Francesco Regazzoni, Referee, Università della Svizzera italiana

Prof. Nicola Bombieri, Università degli Studi di Verona

Prof. Maurizio Martina, Politecnico di Torino

Prof. Fabrizio Lamberti, Politecnico di Torino

Politecnico di Torino September 3, 2020

| This thesis is licensed under a Creative Commons License, Attribution - Noncommercial-                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NoDerivative Works 4.0 International: see www.creativecommons.org. The text may be reproduced for non-commercial purposes, provided that credit is given to the original author.                                                     |

| I hereby declare that, the contents and organisation of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data. |

| Valentino Peluso Turin, September 3, 2020                                                                                                                                                                                            |

|                                                                                                                                                                                                                                      |

### Summary

The advancement of low power technologies and design strategies for integrated circuits, together with the improvement of wireless communication systems and infrastructures, enabled a massive deployment of smart IoT sensors able to sense the physical world. Meanwhile, thanks to the recent breakthroughs in Artificial Intelligence (AI), Convolutional Neural Networks (ConvNets) in particular, computers took a further step towards the human intelligence, acquiring skills like autonomous learning and decision making. The integration of such AI technologies into the end-nodes of the IoT is the premise for a new paradigm——Artificial Intelligence of Things (AIoT)—where sensors will evolve from passive data collectors to active intelligent devices able to infer the meaning of data locally. This shift will thus enable the design of more efficient, scalable, and secure digital ecosystems.

The migration from the cloud to the edge devices poses several issues due to the complexity of modern ConvNet models. The quest for high accuracy has brought the design of ConvNets with billions of hidden parameters and millions of arithmetic operations, thus preventing their deployment on resource-constrained, low-power devices. To tackle this problem, there is a wide consensus that the design of portable ConvNets needs a proper understating of the hardware resources available from the early stage of the training process. Specifically, the optimization of ConvNets should encompass a multi-objective problem formulation, involving extra-functional metrics like memory, energy, and power, besides accuracy. Rather than improving accuracy, the goal is to identify the trade-off frontiers in the design space to pick the best solution meeting the resource constraints. In practice, this can be achieved with algorithmic transformation built upon compression methods that exploit the intrinsic resiliency of neural networks to identify and remove those parts of the model with less contribution to accuracy.

The search for optimality, however, gets challenging due to several reasons. Just like for training, the lack of a closed-form solution to describe the dynamics of the learning flow makes the optimization loop slow and uncertain. Moreover, the high number of dimensions to explore introduced an additional level of complexity overlooked by most of the existing works. A problem formulation neglecting these aspects might result too weak, or unsuited, for real-life applications. This

optimization problem recalls the design of digital integrated circuits (ICs), where multiple conflicting constraints should be addressed, like area, power, and performance. Which of these dimensions gets the highest priority depends on the use-cases, the cost requirements, and in general on the design specifications. For instance, some use-cases require fast processing, whereas those applications with relaxed timing constraints are often limited in area and power consumption. To serve this purpose, the EDA tools for the IC segment have been engineered in a modular way, providing a collection of computer-aided methods with specific goals and formulations. Designers are free to build their own pipeline, integrating the most suited tools depending on their needs.

Applying the same approach to the optimization of ConvNets seems a natural choice and it is exactly the main topic of this dissertation. Indeed, a one-size-fits-all solution does not exist due to the diversity of applications and the hardware back-end. Rather, dedicated solutions are needed for the analysis and optimization of memory, energy, and power, and their integration undergoes a vertical implementation, from software to hardware.

Moreover, compression methods originally applied at design-time can be operated at run-time, leading ConvNets to become dynamic algorithms that modulate the resource usage depending on external triggers raised at the application level (e.g. the battery level or the severity of the task). Once again, whereas the adaptive/dynamic control of resources is a well-known standard in hardware design (e.g. dynamic power management), it is a less explored field in the optimization of ConvNets. For this reason, special attention is devoted to this topic, demonstrating that algorithmic knobs for run-time reconfiguration introduce additional degrees of freedom in the optimization space.

This dissertation is organized into three main parts, each of them focusing on a specific design goal. In the first part, it focuses on aggressive memory optimization which is particularly suited for devices with extreme memory constraints ( $<1\,\mathrm{MB}$ ). It first presents Prune and Quantize, a smart heuristic to explore the memory-accuracy space when neural network compression is pushed towards the deep memory region. Then, it introduces Encoding-Aware Sparse Training, a novel training technique for sparse ConvNets designed to maximize the compression rate of standard encoding algorithms. In the second part, the energy optimization problem is addressed elaborating the idea of Adaptive ConvNets, a solution that allows ConvNets to trade accuracy for energy at run-time. Two different implementations conceived for software-programmable neural accelerators with mixed-precision arithmetic are discussed and validated. In the third part, the focus shifts on power optimization, with emphasis on dynamic power and thermal management. A novel power distribution scheme named FINE-VH is presented, together with an automatic design methodology and the integration in a standard EDA

flow, which enables a more efficient Dynamic-Voltage-Frequency Scaling (DVFS) policy. At last, the efficacy of ConvNets under thermal and accuracy constraints is assessed using DVFS as the main control knob.

Overall, the technical contributions described in this dissertation offer a collection of design&optimization tools for ConvNets to (i) assess at the design-time both functional and extra-functional metrics, (ii) explore different dimensions of the design-space (iii) identify the optimal solution that can meet the hardware requirements.

## Acknowledgements

I would like to thank Prof. Enrico Macii, for giving me the opportunity to join the EDA research group.

I am extremely grateful to prof. Andrea Calimera, for its valuable advice and the countless hours devoted to discuss my ideas and support my research.

I also acknowledge the project "SENSEI - Sensemaking for Scalable IoT Platforms with In-Situ Data-Analytics: A Software-to-Silicon Solution for Energy-Efficient Machine-Learning on Chip," funded by Compagnia di San Paolo, with Università di Bologna as academic partner and ST Microelectronics as non-academic partner.

It is not his possession of knowledge, of irrefutable truth, that makes the man of science, but his persistent and recklessly critical quest for truth.

Karl Raimund Popper The Logic of Scientific Discovery

# Contents

| Li | st of | Table  | $\mathbf{s}$                                              | X    |

|----|-------|--------|-----------------------------------------------------------|------|

| Li | st of | Figur  | es                                                        | XII  |

| 1  | Intr  | oduct  | ion                                                       | 1    |

|    | 1.1   | Conte  | xt & Motivation                                           | . 1  |

|    | 1.2   | Towar  | rds Edge Inference                                        | . 3  |

|    |       | 1.2.1  | Software Optimization: the Evolution of ConvNet Architec- |      |

|    |       |        | tures                                                     | . 3  |

|    |       | 1.2.2  | Hardware Optimization: Platforms for Edge Inference       | . 5  |

|    | 1.3   | Objec  | tives & Contribution                                      | . 8  |

| 2  | Mei   | mory-l | Driven Optimization                                       | 11   |

|    | 2.1   | Backg  | round on Neural Network Compression                       | . 12 |

|    |       | 2.1.1  | Pruning                                                   | . 12 |

|    |       | 2.1.2  | Quantization                                              | . 14 |

|    |       | 2.1.3  | Pruning and Quantization                                  | . 15 |

|    | 2.2   | PaQ:   | Prune and Quantize                                        | . 16 |

|    |       | 2.2.1  | Framework Overview                                        | . 17 |

|    |       | 2.2.2  | Evaluation of PAQ                                         | . 22 |

|    |       | 2.2.3  | Discussion                                                |      |

|    | 2.3   | EAST   | Encoding-Aware Sparse Training for Deep Memory Com-       |      |

|    |       | pressi | on of ConvNets                                            | . 32 |

|    |       | 2.3.1  | Motivation                                                | . 34 |

|    |       | 2.3.2  | Flow overview                                             | . 35 |

|    |       | 2.3.3  | Experimental Results                                      | . 37 |

| 3  | Ene   | rgy-D  | riven Optimization                                        | 41   |

|    | 3.1   | Taxon  | nomy of Adaptive ConvNets                                 | . 45 |

|    |       | 3.1.1  | Control Knob                                              | . 45 |

|    |       | 3.1.2  | External Trigger                                          | . 46 |

|    |       | 3.1.3   | Optimization and search engine                           | . 47  |

|----|-------|---------|----------------------------------------------------------|-------|

|    |       | 3.1.4   | Training                                                 | . 48  |

|    | 3.2   | Mixed-  | -precision ConvNets                                      | . 48  |

|    |       | 3.2.1   | Fixed-Point Quantization                                 | . 48  |

|    |       | 3.2.2   | Training Mixed-Precision ConvNets                        | . 49  |

|    | 3.3   | Energy  | y-Driven Adaptive ConvNets via On-line Precision Scaling | . 50  |

|    |       | 3.3.1   | Design and Optimization                                  | . 51  |

|    |       | 3.3.2   | Runtime implementation                                   | . 57  |

|    |       | 3.3.3   | Experimental Results                                     | . 59  |

|    |       | 3.3.4   | Discussion                                               | . 66  |

|    | 3.4   | Scalab  | le-Effort ConvNets for Multilevel Classification         | . 68  |

|    |       | 3.4.1   | Motivation                                               | . 68  |

|    |       | 3.4.2   | Multilevel Classification                                | . 69  |

|    |       | 3.4.3   | Precision Scalable Arithmetic                            | . 72  |

|    |       | 3.4.4   | Fixed-point Quantization & Fine-Tuning                   | . 76  |

|    |       | 3.4.5   | Precision Assignment Heuristic                           | . 77  |

|    |       | 3.4.6   | Experimental Results                                     | . 79  |

|    |       | 3.4.7   | Discussion                                               | . 84  |

| 4  | Pow   | er-Dri  | ven Optimization                                         | 87    |

|    | 4.1   |         | optimization on ASICs: FINE-VH                           |       |

|    |       | 4.1.1   | Background                                               |       |

|    |       | 4.1.2   | Implementing FINE-VH                                     |       |

|    |       | 4.1.3   | Simulation and Emulation                                 |       |

|    |       | 4.1.4   | Evaluating FINE-VH                                       |       |

|    |       | 4.1.5   | Discussion                                               |       |

|    | 4.2   | Power   | optimization on CPUs: Voltage-Scaled ConvNets            |       |

|    |       | 4.2.1   | Thermal-Aware Power Management in embedded               |       |

|    |       |         | CPUs: Reactive vs. Proactive DVFS                        | . 111 |

|    |       | 4.2.2   | Thermal-Aware Performance Optimization and Characteri-   |       |

|    |       |         | zation Framework                                         | . 115 |

|    |       | 4.2.3   | Experimental Setup and Results                           | . 116 |

|    |       | 4.2.4   | Discussion                                               |       |

| 5  | Con   | clusior | ns                                                       | 124   |

| т: | at ar | nubli-  | ations                                                   | 196   |

| Li | st of | public  | ations                                                   | 126   |

| Bi | bliog | raphy   |                                                          | 129   |

# List of Tables

| 2.1        | Hardware figures of the Cortex-M IoT MCUs by ARM                                                                                                   | 12 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2        | List of abbreviations                                                                                                                              | 23 |

| 2.3        | Benchmark overview. Convolutional layer with shape $(c_{out}, k_h, k_w)$ , fully-connected layer with shape $(c_{out})$ and max-pooling layer with |    |

|            | shape $(k_h, k_w)$ ; $k_h$ and $k_w$ are the height and width of input planes                                                                      |    |

|            | in pixels, while $c_{out}$ refers the number of output channels                                                                                    | 24 |

| 2.4        | Hardware specification of the boards adopted as test-bench                                                                                         | 25 |

| 2.5        | Optimal vs. hardware-compliant solutions under different memory                                                                                    |    |

|            | constraints $M_t$ : column Pareto lists the Pareto points P as for the                                                                             |    |

|            | plots of Fig. 2.2; columns PaQ-8 and PaQ-16 refer to solutions                                                                                     |    |

|            | generated by the <b>PaQ</b> flow using 8- and 16-bit respectively(red lines                                                                        |    |

|            | in Fig. 2.2); column $\Delta$ reports the distance (the lower is better)                                                                           |    |

|            | between optimal and hardware-compliant solutions for both PaQ-                                                                                     |    |

|            | 8 and PaQ-16 in terms of accuracy. Cells corresponding to those                                                                                    |    |

|            | solutions with a top-1 accuracy $\ll 50\%$ have not been filled                                                                                    | 28 |

| 2.6        | Average number of fine-tuning epochs to achieve the maximum top-                                                                                   |    |

|            | 1 accuracy on the test set.                                                                                                                        | 32 |

| 2.7        | Top-1 classification accuracy on CIFAR-10 and weight memory of                                                                                     |    |

|            | the dense ResNet-9 after 32-bit floating-point training (FP32), after                                                                              | 20 |

| <b>0</b> 0 | quantization (Q8), and after LZ4 compression (Q8+LZ4)                                                                                              | 38 |

| 2.8        | Sparsity (S) and Top-1 Accuracy (A) of weight pruning (WP) and                                                                                     |    |

|            | EAST on ResNet-9 at different memory constraint $M_{\rm t}$ (KB). CR is                                                                            | 20 |

| 3.1        | the compression ratio w.r.t. the floating-point ConvNet                                                                                            | 39 |

| 0.1        | Schematic classification of different implementations of Adaptive ConvNets                                                                         | 44 |

| 3.2        | Top-1 classification accuracy of five state-of-the-art ConvNets on the                                                                             | 44 |

| 0.4        | ImageNet validation-set at different precision: 32-bit floating-point                                                                              |    |

|            | (FP32), 16-bit fixed point (FX16), 8-bit fixed-point with truncation                                                                               |    |

|            | (FX8-T), 8-bit fixed-point with rounding (FX-R)                                                                                                    | 52 |

| 3.3        | Benchmark ConvNets overview. Top-1 accuracy refers to the 32-bit                                                                                   | 92 |

| J.0        | floating-point model                                                                                                                               | 60 |

|            | O F 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                            |    |

| 3.4  | Hardware configuration of the adopted ConvNet accelerator                          | 61  |

|------|------------------------------------------------------------------------------------|-----|

| 3.5  | Optimization parameters NSGA-II*                                                   | 62  |

| 3.6  | Figure of merits of the Pareto fronts for the selected benchmarks                  | 63  |

| 3.7  | Upper bound of the energy cost for weight re-configuration. Values                 |     |

|      | are normalized to the energy of a full-precision inference                         | 65  |

| 3.8  | Figure of merits of the Pareto fronts for the selected benchmarks                  |     |

|      | using weight re-configuration with truncation                                      | 65  |

| 3.9  | Normalized computational effort (#Operations) at different preci-                  |     |

|      | sion settings (1 Operation = 1 MAC $4x4$ )                                         | 75  |

| 3.10 | List of benchmarks                                                                 | 79  |

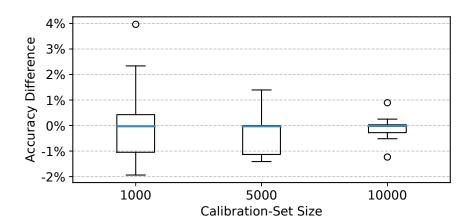

| 3.11 | Top-1 accuracy difference ( $\Delta$ Accuracy) with respect to fp-32 after         |     |

|      | quantization (Q-fx) and after fine-tuning at full precision (Fine-                 |     |

|      | fx:full)                                                                           | 80  |

| 3.12 | Top-1 Accuracy in multilevel classification at different levels (L) of             |     |

|      | abstraction. The test set is composed by 40k images                                | 82  |

| 3.13 | AlexNet results                                                                    | 85  |

| 3.14 | SqueezeNet results                                                                 | 85  |

| 3.15 | MobileNet results                                                                  | 86  |

| 4.1  | Figures of merit of the RI5CY after FINE-VH                                        | 102 |

| 4.2  | Memory, accuracy, and nominal latency of the selected benchmarks.                  | 117 |

| 4.3  | Thermal headroom of different ConvNets in continuous inference.                    |     |

|      | $N_{\rm safe}$ and $t_{\rm safe}$ are the maximum number of consecutive inferences |     |

|      | and the execution time at safe temperature values (i.e., $T < T_{\text{max}}$ ).   | 118 |

| 4.4  | Nominal inference latency at 3 thread execution vs. worst case la-                 |     |

|      | tency under DVFS based proactive management at 4 thread execution.                 | 120 |

# List of Figures

| 1.1 | Schematic view of a ConvNet Architecture for Image Classification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Top-1 Accuracy vs. Number of Parameters of open-source ConvNets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|     | on the Imagenet dataset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4  |

| 1.3 | Schematic view of the dissertation outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9  |

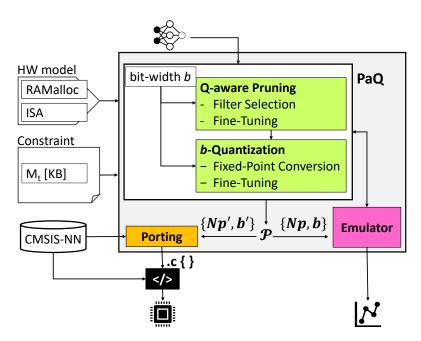

| 2.1 | Framework overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 18 |

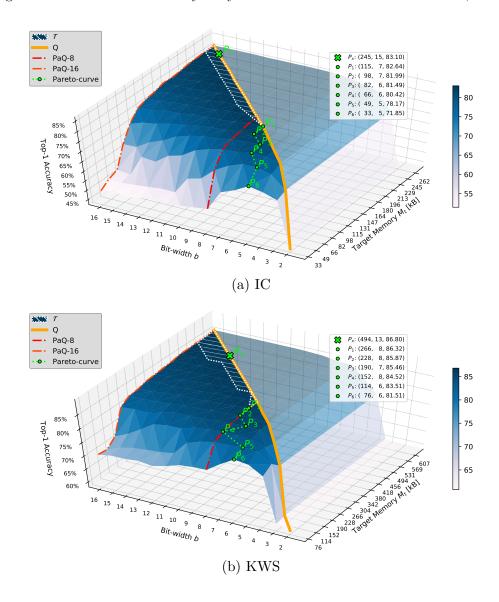

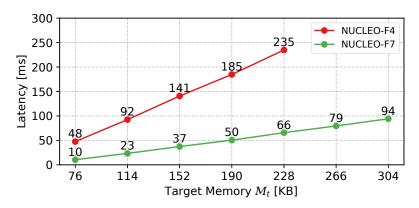

| 2.2 | Solutions of $\mathbf{PaQ}$ in the memory-accuracy space for the three tasks under analysis (a) IC, (b) KWS, (c) FER. The solution with the best accuracy $(P_x)$ is marked with the green cross. The hatched area (enclosed by the white dotted curve) covers the plateau $(\mathcal{T})$ collecting all solutions s.t. the accuracy loss $\mathcal{L} \leq 0.5$ w.r.t $P_x$ . The yellow line $(\mathbf{Q})$ highlights the solutions where only $b$ -quantization applies. The red dash-dotted lines $(\mathbf{PaQ-8} \text{ and } \mathbf{PaQ-16})$ highlights the solutions generated by $\mathbf{PaQ}$ using 8- and 16-bit respectively, i.e. the solutions compliant with the target hardware. The green dotted line indicates the Pareto points $(P)$ in the memory-accuracy space, i.e. all the solutions more accurate than all the other points with the same target memory $M_t$ . The right box reports the absolute coordinates of $P_x$ and each Pareto point in the format (target memory, |    |

|     | bit-width, top-1 accuracy)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27 |

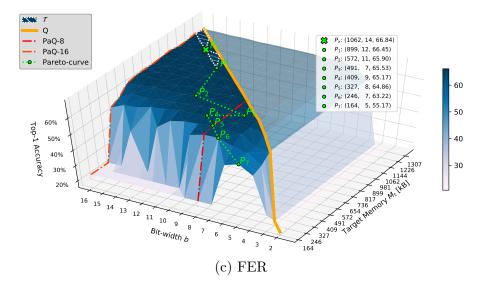

| 2.3 | Top-1 accuracy vs. memory footprint for KWS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 30 |

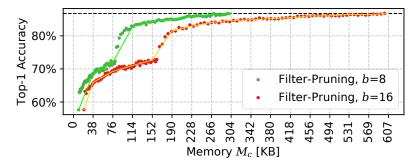

| 2.4 | Average inference time per sample of PaQ-8 solutions on KWS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31 |

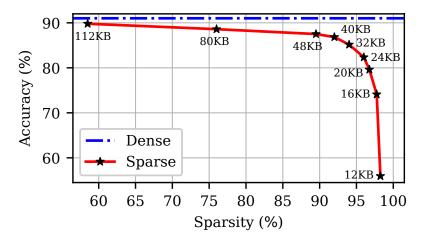

| 2.5 | Sparsity vs. Accuracy trade-offs of a compressed 9-layer ResNet under different memory constraints (the labeled numbers). The net is trained on CIFAR-10, then compressed via weight pruning and encoding. The blue dash-dotted line marks the accuracy of the original dense version (140 KB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 33 |

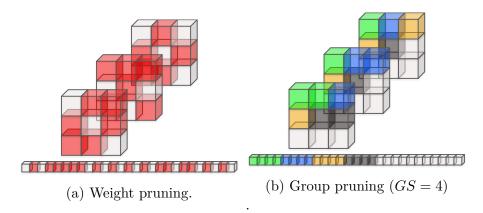

| 2.6 | Weight Pruning (a) vs Group Pruning (b). Colored weights denotes zero-values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 36 |

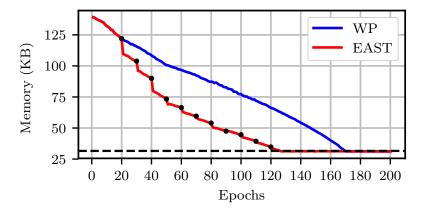

| 2.7 | Epochs vs. Memory in weight pruning (blue line) and EAST (red line) for $M_{\rm t}=32{\rm KB}$ (dashed line). The dots indicates when the group size increases.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40 |

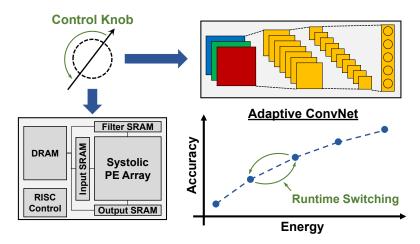

| 3.1  | Abstract template for Adaptive ConvNets. At run-time, a control-                                           |          |

|------|------------------------------------------------------------------------------------------------------------|----------|

|      | knob changes the configuration of the processing elements (PEs)                                            |          |

|      | and of the ConvNet to switch among different operating point in the                                        |          |

|      | energy-accuracy space. In this work, the control-knob is precision                                         |          |

|      | scaling                                                                                                    | 42       |

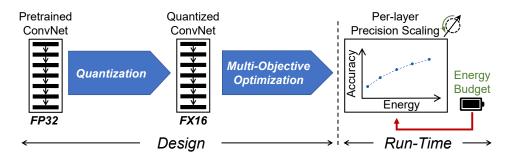

| 3.2  | Design-Flow Overview                                                                                       | 53       |

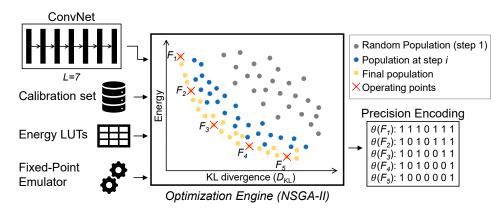

| 3.3  | Schematic view of design-time optimization flow                                                            | 54       |

| 3.4  | Abstract execution flow and PE configuration at 16-bit (3.4a) and                                          |          |

|      | 8-bit (3.4b)                                                                                               | 58       |

| 3.5  | Weight $(W_i)$ re-configuration with truncation (3.5a) and rounding                                        |          |

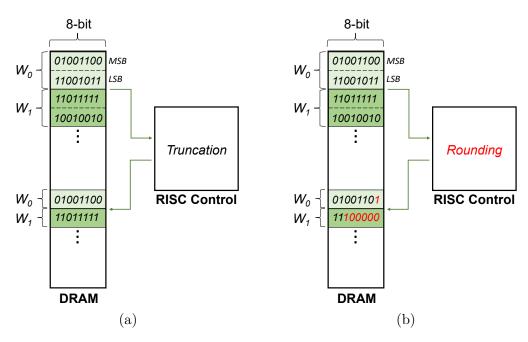

|      | (3.5b)                                                                                                     | 59       |

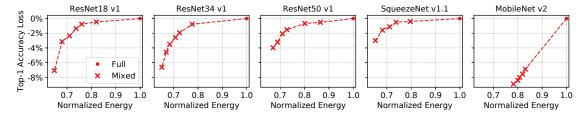

| 3.6  | Pareto fronts of the selected benchmark. The x-axis is the normal-                                         |          |

|      | ized energy with respect to the full-precision ConvNet (all layers                                         |          |

|      | at FX16). The y-axis is the Top-1 Accuracy loss with respect to                                            |          |

|      | the full-precision ConvNet. The crosses $(\times)$ indicate the operat-                                    |          |

|      | ing points returned by Algorithm 2. The dot (•) denotes the full-                                          |          |

|      | precision ConvNet.                                                                                         | 63       |

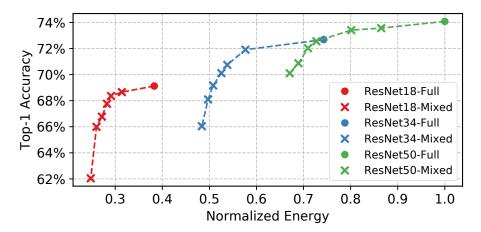

| 3.7  | Energy vs Accuracy of topology and precision scaling. Energy is                                            | 6.4      |

|      | normalized with respect to ResNet50 at full-precision (green dot).                                         | 64       |

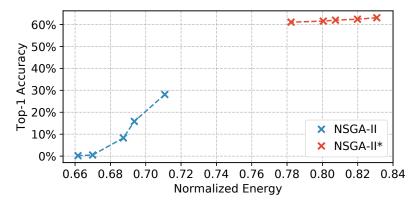

| 3.8  | Pareto curve of MobileNet v2 with standard NSGA-II and our                                                 | 0.0      |

| 0.0  | NSGA-II* implementation with penalty score.                                                                | 66       |

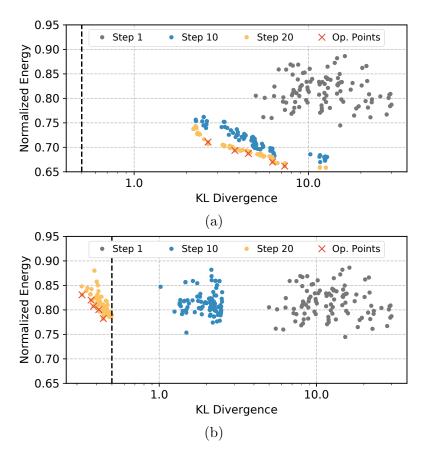

| 3.9  | Population evolution across different iterations for MobileNet v2                                          | C.T.     |

| 2 10 | with NSGA-II (a) and NSGA-II* (b)                                                                          | 67       |

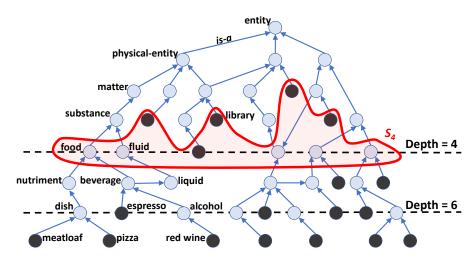

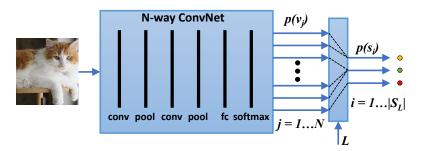

| 3.10 | 0 1                                                                                                        | 69<br>71 |

|      | Multilevel classification with ConvNets                                                                    | 71       |

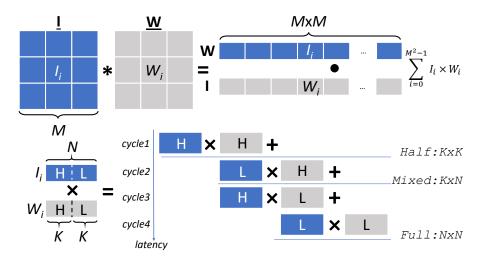

| 3.12 | Iterative product procedure to compute the dot-product between two vectors                                 | 73       |

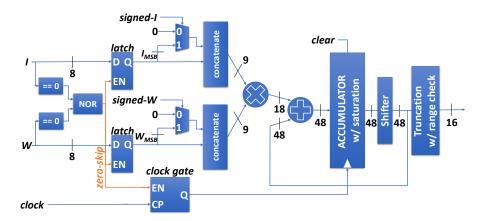

| 2 12 | Structural view of the scalable-precision processing element                                               | 75       |

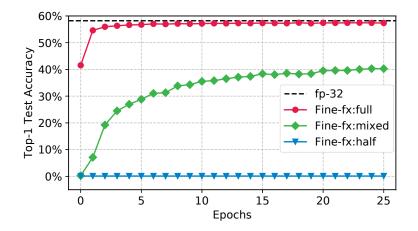

|      | SqueezeNet Top-1 Accuracy during fine-tuning. Black line (dashed):                                         | 13       |

| 5.14 | fp-32.; Red line (o) Fine-fx: full (8x8); Green line (o): Fine-                                            |          |

|      | $\mathbf{fx}$ : mixed (8x4); Blue line ( $\bigtriangledown$ ): $\mathbf{Fine}$ - $\mathbf{fx}$ :half (4x4) | 81       |

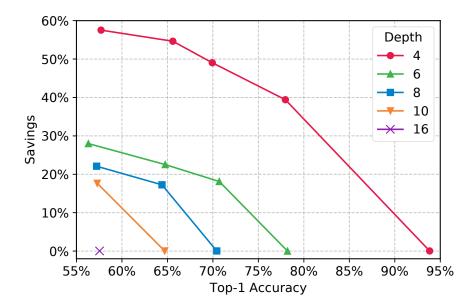

| 3 15 | Operation Savings vs. Top-1 Accuracy trade-off for SqueezeNet                                              | O1       |

| 0.10 | with calibration set size equal to 10000                                                                   | 83       |

| 3.16 |                                                                                                            |          |

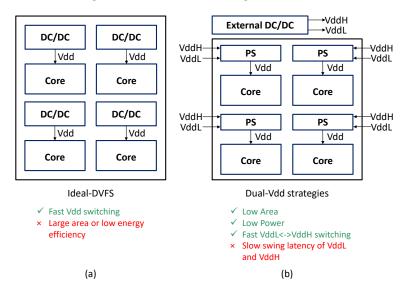

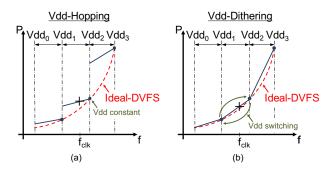

| 4.1  | Schematic view ideal-DVFS and dual-Vdd power management                                                    | 89       |

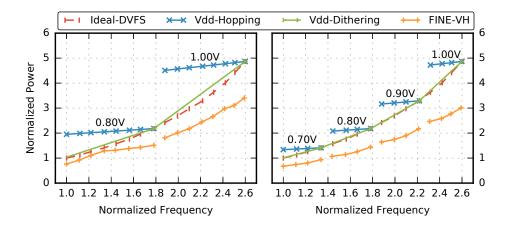

| 4.2  | Performance-Power trade-off curves of existing DVFS schemes                                                | 91       |

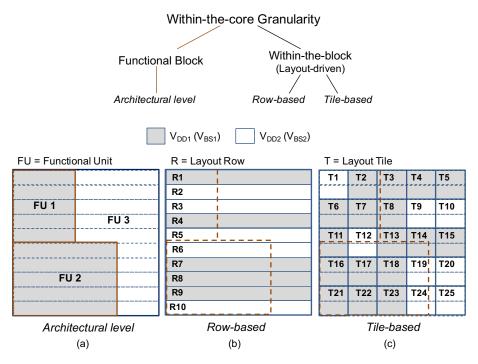

| 4.3  | Classification of low-power knobs granularity. From coarse-grained                                         | - •      |

|      | architectural level (a), up to fine grained solutions like row-based                                       |          |

|      | (b) and tile-based (c) partitioning                                                                        | 93       |

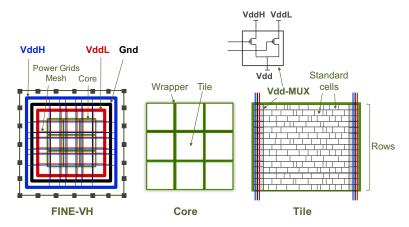

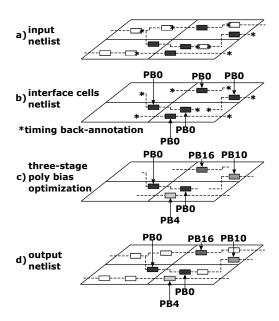

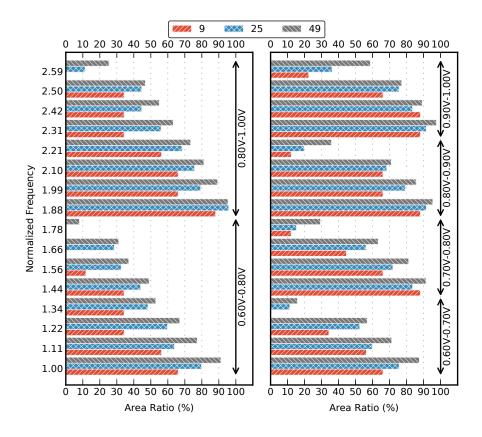

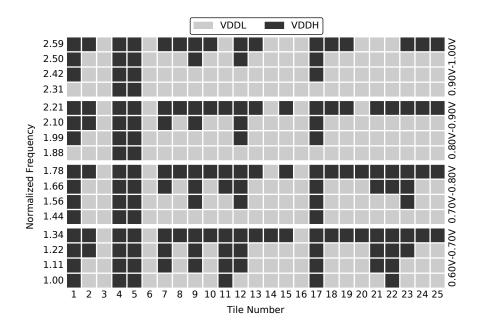

| 4.4  | Tile-based partitioning and tile organization                                                              | 95       |

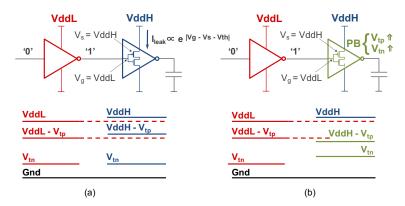

| 4.5  | Intra-tile leakage current (a) and its mitigation via poly-biasing (b) 97                 |

|------|-------------------------------------------------------------------------------------------|

| 4.6  | Optimal poly-bias assignment through local re-synthesis 98                                |

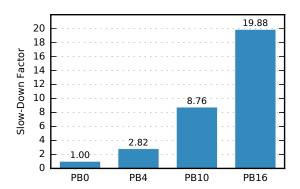

| 4.7  | Average slow-down factors for the different poly-bias options 98                          |

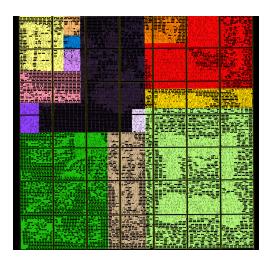

| 4.8  | Layout partitioning of A RI5CY core after standard-cell placement                         |

|      | (49 tiles)                                                                                |

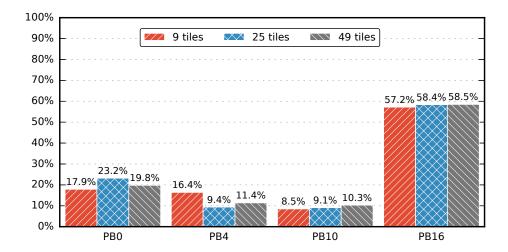

| 4.9  | Poly-bias distribution across the interface-cells                                         |

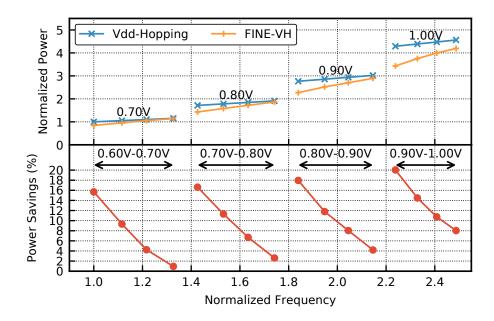

| 4.10 | Comparative analysis among four DVFS schemes: i) ideal-DVFS, ii)                          |

|      | Vdd-Hopping, iii) Vdd-Dithering, iv) FINE-VH (49 tiles); $\Delta$ Vdd=200 mV              |

|      | (left), $\Delta Vdd=100 \mathrm{mV}$ (right)                                              |

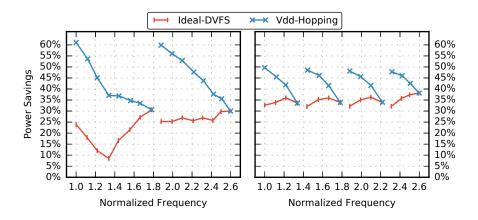

| 4.11 | Power savings of the proposed FINE-VH (49 tiles) with respect to                          |

|      | ideal-DVFS and Vdd-Hopping; $\Delta$ Vdd=200 mV (left), $\Delta$ Vdd=100 mV               |

|      | (right)                                                                                   |

| 4.12 | Percentage of standard cell area @VddL for different number of tiles. $105$               |

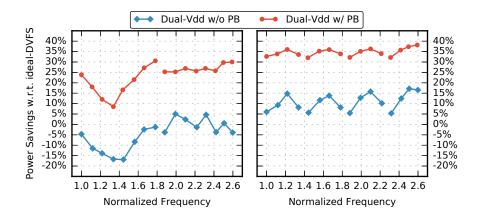

| 4.13 | Power savings with respect to ideal-DVFS before and after PB op-                          |

|      | timization for $\Delta Vdd=100\mathrm{mV}$ and $\Delta Vdd=200\mathrm{mV}$ (49 tiles) 106 |

| 4.14 | Voltage Assignment (25 tiles)                                                             |

| 4.15 | Power comparison between Vdd-Hopping and FINE-VH for a PE                                 |

|      | partitioned into 400 tiles (after place&route)                                            |

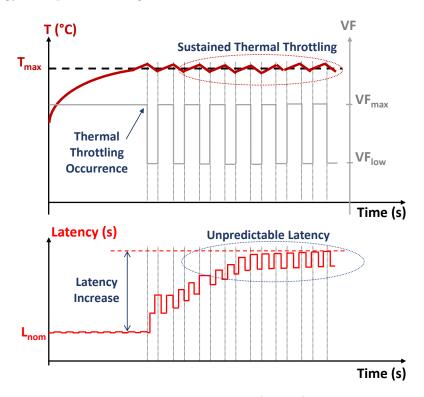

| 4.16 | Qualitative trends of temperature (above) and inference latency (be-                      |

|      | low) over time under reactive thermal management                                          |

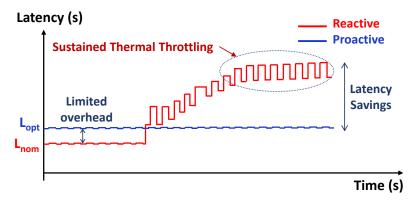

| 4.17 | Inference latency in reactive (red) and proactive (blue) thermal                          |

|      | management                                                                                |

| 4.18 | Average latency $(L_{\text{avg}})$ under reactive and proactive thermal man-              |

|      | agement strategies                                                                        |

|      | Schematic view of the proposed characterization flow                                      |

| 4.20 | Percentage of execution time at $VF_{low} = 900 \mathrm{MHz}$ over a runtime              |

|      | of 100 s                                                                                  |

|      | Results of the characterization flow                                                      |

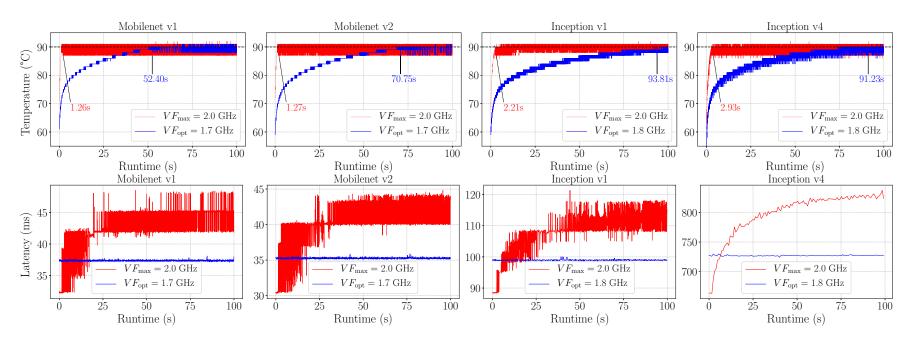

| 4.22 | Temperature gradient (top) and inference latency (down) of contin-                        |

|      | uous inference for 100 s. The annotations reports the occurrence of                       |

|      | the first thermal throttling event                                                        |

### Chapter 1

### Introduction

### 1.1 Context & Motivation

Deep Convolutional Neural Networks (ConvNets hereafter) are brain-inspired computational models that have brought breakthroughs in many fields, such as computer vision [1], speech recognition [2] and natural language processing [3]. In its more general embodiment, a ConvNet consists of a sequence of processing stages commonly called layers. At each layer, transformations learned during the training phase project raw data over a multi-dimensional space where standard classifiers can outperform the accuracy of humans [4]. From a computational viewpoint, ConvNets are nothing more than matrix multiplications between pretrained parameters (the synaptic weights of the hidden neurons) and the input data.

The most common use-case for ConvNets is image classification where a multichannel image (e.g. RGB) is processed producing as output the probability that the subject depicted in the picture belongs to a specific class of objects or concepts (e.g. car, dog, airplane, etc.). One can see this end-to-end inference process as a kind of data compression: high-volume raw-data (the pixels of the image) are compressed into a highly informative tag (the resulting class). In this regard, the adoption on the Internet-of-Things (IoT) is disruptive: distributed smart-objects with embedded ConvNets may implement data-analytics at the edge, near the source of data [5], with advantages in terms of predictability of the service response time, energy efficiency, privacy and, in general, scalability of the IoT infrastructure.

Starting from the astounding results obtained by Krizhevsky et al. [1] in 2012, ConvNets evolved quickly achieving impressive results. However, it is possible to recognize some basic characteristics common to many models. The organization of a ConvNet reflects the hierarchical structure of the primary sensory areas of

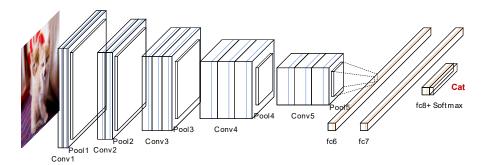

the visual cortex [6]. The rationale is the same implemented by the human brain, indeed: extract, evaluate, and combine features that have been learned to be common among the majority of samples belonging to the same class. The feature extraction is hierarchical, namely, low-level features are extracted first and then used to extract features at a higher level. Intuitively, edges may form shapes, which in turn may form objects. Features at the higher levels are then used to classify the content of the picture. This sequential procedure is built through a chain of computational layers that implement algebraic operations on matrices. Fig. 1.1 shows the topology of a generic ConvNet. Convolutional layers run matrix-matrix convolution between their local filters and the multi-dimensional map generated by previous layers; filters correspond to different features to extract. Activation layers (blue blocks) introduce non-linearity in the feature space applying specific functions, e.g. Rectified Linear Unit (ReLU), on the output map produced by the convolutional layers; non-linearity helps to amplify semantic differences. Finally, reduction layers apply a sub-sampling of the activation maps using functions like max-pooling or average pooling; sub-sampling helps in reducing the cardinality of the features, increase the level of abstraction and make classification less sensible to geometrical distortions. Once all the features have been extracted, the last stages of a ConvNets implement the actual classification. Fully connected layers serve this purpose using multi-layer perceptrons that apply geometric separation. At the very last stage, a softmax function is used to score the available labels; the one with the highest probability identifies the class.

Figure 1.1: Schematic view of a ConvNet Architecture for Image Classification.

The design of ConvNets encompasses a training stage during which the synaptic weights of the hidden neurons are learned using a back-propagation algorithm (e.g. the Stochastic Gradient Descent [7]). The learning is supervised and accuracy-driven, namely, it adjusts the weights such that an accuracy loss function evaluated over a set of labeled samples is minimized. Although the basic theory is known since long time, only the advent of GPUs made ConvNets evolving from pure mathematical models to practical solutions. Indeed, the learning stage involves a

brute-force search that can be afforded only by massively parallel processing, just what GPUs offer.

Since a proper design and optimization methodology does not exist yet, today's ConvNets are typically oversized in terms of both computational and memory resources. Even small networks require billions of multiplications and millions of weights to be stored. This prevents their use on low-power embedded platforms which offer low storage capacity, low computational power, and limited energy budget. How to design ConvNets that fit the stringent resource constraints while preserving classification accuracy is an open issue.

Specifically, the processing of ConvNets under resource constraints is a technological challenge at the intersection between the theories of machine learning and those of computer engineering, where vertical strategies spanning from the design of highly efficient circuits and systems to algorithmic optimization and model training must be brought together.

The research community is attacking the problem from two opposite directions. At the software level, with the design of more compact network architectures and optimization techniques reducing the cardinality of ConvNets, yet preserving competitive prediction accuracy. At the hardware level, with the design of custom accelerators [8], or reconfigurable spatial architectures [9]. The achieved results are impressive: performance close to the TOPS with power consumption of few hundreds of  $\mu$ W [10].

In this chapter, we first review the relevant trends in this context (Section 1.2): Section 1.2.1 focuses on the software level, summarizing the main advancements in neural network design; Section 1.2.2 focuses on the hardware level, presenting a brief overview of the available hardware platforms for edge inference. Then, we introduce the goals and the main contributions of our research, together with the overall organization of the dissertation (Section 1.3).

### 1.2 Towards Edge Inference

# 1.2.1 Software Optimization: the Evolution of ConvNet Architectures

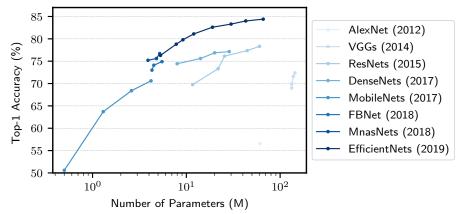

In the early years of life, ConvNets were mainly optimized to improve accuracy, without any concern on their computational complexity. Since higher accuracy can be afforded increasing the number of parameters and the operations, the evolution of ConvNets experienced an exponential increase in the resources needed for inference. This trend is clearly depicted in Fig. 1.2, which shows the accuracy-complexity trade-off achieved by the most common open-source ConvNets trained on the Imagenet dataset. The rise of accuracy from 50.6% (bottom-left MobileNet)

to 84.4% (top-right EfficientNet) comes at the cost of  $132\times$  more parameters.

Figure 1.2: Top-1 Accuracy vs. Number of Parameters of open-source ConvNets on the Imagenet dataset.

The growing need of portability pushed designers to consider hardware related metrics besides accuracy. Rather than searching for the most accurate solution, designers soon focused on a wider exploration of the design space, aiming to offer a set of solutions in the accuracy-complexity space from which the user can pick the best configuration meeting the hardware constraints. To this purpose, modern ConvNets follow a common characteristic: they are built upon an architectural template that can be resized depending on memory and performance requirements. This can be observed in Fig. 1.2, which reports the different existing versions of each network. The different versions are generated through the implementation of different scaling knobs: depth, width, and resolution. Their joint application enables to span the design space. The depth indicates the number of processing layers; its adoption as scaling knob was introduced by VGG [11]. The width refers to the number of filters of each convolutional layer; one standard practice is to define a multiplicative factor—the width multiplier—that indicates the ratio of filters related to the baseline implementation. The resolution represents the spatial dimension of the input data, which also affects the cardinality of the inner tensors. Width and resolution scaling were pioneered by MobileNet [12] and are still adopted by more recent networks like EfficientNet [13]. The latter introduced the concept of compound scaling, which seeks the optimal balance between the three knobs. Regardless of the knob adopted, lower resources imply lower accuracy. The challenge is to identify Pareto fronts in the design space.

In this context, Neural Architecture Search (NAS) [14] has emerged as the most promising technology to discover novel topology configurations. The basic principle of NAS is to integrate the network hyper-parameters, like the number of layers, the filter shapes, and the kind of operations, in the training loop besides the

network weights. This enables to fully automate the search for new architectures, but at the cost of much longer training time, from few hours up to several days of GPU processing. FBnet, MnasNet, and EfficientNet (see Fig. 1.2) are some representative networks generated by NAS, achieving better trade-offs than previous hand-crafted designs.

Although the impressive advancements, there is still room for further optimization. In this regard, this dissertation investigates orthogonal strategies to lower the complexity of ConvNets, generated either by manual or automatic design. Our contribution is threefold. First, with compression methods that remove redundant information (i.e. pruning) and/or exploit the resiliency of ConvNets through low-precision arithmetic (i.e. quantization). Second, with the design of dynamic models that can modulate their resource requirements at run-time. Third, with a joint co-operation between software and hardware optimizations, especially when dealing with power minimization. A thorough overview of existing compression strategies related to our works is presented throughout the dissertation.

# 1.2.2 Hardware Optimization: Platforms for Edge Inference

Despite the research efforts towards the development of optimized and compressed models, the deployment of ConvNets remains an open problem. Besides complexity, one of the major obstacles is the diversity of the existing hardware architectures for edge inference. The main candidate solutions include (but are not limited to) (i) custom accelerators based on application-specific designs (ASICs) (ii) general-purpose embedded CPUs, and (iii) ultra low-power microcontroller units (MCUs). These options are not in competition, rather the optimal choice depends on the application, as each use case has different compute, area, and cost requirements. This heterogeneity prevents the development of a one-size-fitsall optimization pipeline. Moreover, the hardware can offer additional degrees of freedom in the optimization, providing specific features and/or knobs that enable to achieve a better quality of results with smaller and faster models. A comprehensive optimization of edge ConvNets should therefore include a set of different algorithmic solutions, each of them tailored to the underlying hardware. Whereas this aspect is often overlooked by current research, it receives particular attention in this dissertation. In this section, we summarize the pros and cons of the alternative hardware architectures, highlighting the opportunities and challenges of each case.

### Application Specific Integrated Circuits

Custom ASICs for neural network inference are today integrated into many system-on-chips for the mobile segment. Their success lies in their performance stability and power efficiency, thanks to the availability of memory logic and functional cores dedicated to host only deep learning workloads. They consist of a processing unit, usually built as an array of processing elements (PEs), assisted by a distributed memory hierarchy that helps to improve the bandwidth and to avoid frequent accesses to large and energy-hungry off-chip memories (DRAM). The processing unit is an array of tightly coupled processing elements (PEs) that receive the incoming operands from the main inputs or the upstream nodes and produce partial results that are locally stored and/or passed downstream following a pre-defined data-flow. Thanks to the distributed communication among PEs, an array of  $N \times N$  elements consumes N+N inputs and produces  $N \times N$  outputs at each cycle, thereby enabling massive parallel computation. Systolic units are a particular class of such processing arrays that leverage the intrinsic locality of the convolution operation and enable efficient data reuse. Architectural templates of this kind can be re-scaled to fit the requirements of both cloud [15] and edge [16] systems.

Due to the success of low-precision ConvNets, custom ASICs often integrate multi-precision arithmetic units, which enable to exploit the resilience of neural networks to arithmetic errors in favor of higher compression ratio. Since the degree of resilience, hence the precision, depends on the network and the application, the trend is to develop flexible arithmetic units that support a fine-grain control on the bit-width [17].

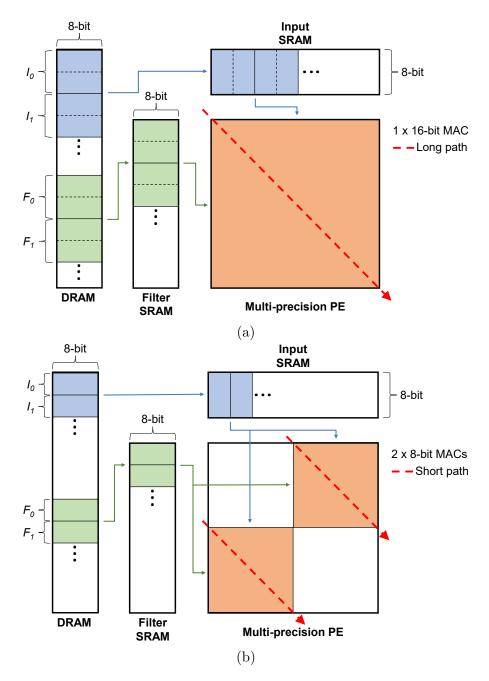

The architecture presented in [18] is one of the most representative examples with hardware support for mixed-precision computing. The core is built using an array of multi-precision PEs that can deliver 1 × 16-bit MAC or 2 × 8-bit MAC per cycle. Running to low-precision, the PEs can operate at a lower voltage-frequency level, which means lower power consumption, keeping the same throughput of the full-precision. Hence, the joint application of voltage and precision scaling improves the overall energy efficiency. More recent architectures offer additional degrees of freedom with a finer selection of the bit-width: BitFusion [19] is an ASIC accelerator with support of 2-, 4-, 8-, and 16-bit operations; BISMO [20] is a time-scheduled design for FPGAs that implements a bit-serial matrix multiplication algorithm; UNPU [21] is an ASIC accelerator that provides an arithmetic instruction set with arbitrary bit-widths from 1- to 16-bit. Different solutions for variable precision are available also in commercial products, like the NVIDIA Turing GPU [22] (4- and 8-bit) and the PowerVR Series 2NX by Imagination [23] (arbitrary bit-width from 4 to 16-bit).

However, standard ConvNets do not exploit efficiently the reconfigurability of

the hardware. The bit-width is a fixed parameter, selected at design-time such that the prediction quality keeps the same level of the full-precision model. ConvNets are therefore designed and implemented as static models. Instead, the design of Adaptive ConvNets that can self-tune their arithmetic precision at run-time could enable dynamic trade-offs between accuracy and complexity. To this purpose, there is a strong need to develop novel algorithmic optimizations. In Chapter 3, we address this need, presenting two different strategies for the design and implementation of Adaptive ConvNets.

#### Embedded CPUs

Embedded CPUs represent the most attractive solutions to deploy ConvNets on mobile platforms like smartphones. Indeed, today most mobile devices integrate high-performance multi-core system-on-chips, which can become intelligent systems through a software update. Moreover, CPUs offer higher flexibility than custom hardware, as they can run also other tasks than inference, such as driving peripherals and sensors, and therefore host comprehensive sensing environments.

An example is the Cortex-A family by ARM. It comes with the NEON unit, an advanced single-instruction multiple-data (SIMD) architecture that supports float and integer vector operations. Proper use of such a module allows to maximize the parallelism, reduce the memory accesses, and hence achieve substantial performance boost [24].

The success of CPUs in the field of embedded ConvNets is demonstrated by the growing number of inference engines [25]. These tools provide an abstract user interface coupled with specialized deep learning libraries that collect handwritten kernels built with NEON intrinsics and/or assembly code. The most advanced and stable solutions include Arm NN by Arm, ncnn by Tencent, and TensorFlow Lite by Google.

Due to the integration of high-performance components in small form-factor, the primary bottleneck of CPU-based platforms is their limited thermal design power. Indeed, the execution of intensive workloads like ConvNets raises several concerns related to power dissipation. This problem is often neglected by standard optimization pipelines, which evaluate the inference performance in nominal operating conditions, a too optimistic choice not reflecting actual use-cases. To provide a more realistic analysis, Section 4.2 presents a thorough characterization of the achievable power-performance trade-offs in embedded CPUs.

### Microcontreller Units

To sustain the scalability of the IoT, there is an increasing demand to deploy ConvNets on ultra low-power sensing systems powered by tiny MCUs. Coupled with low-power sensors (e.g. MEMS), MCUs are extremely popular in several fields, spanning from battery-powered applications (e.g. wearable technologies) to high-end devices for navigation and positioning, predictive maintenance in industry, and augmented virtual reality components.

However, the migration towards such tiny devices introduces several challenges. ConvNets previously processed in the cloud with plenty of resources shall be processed in a mW power envelope using processor cores with tight resource budgets and low storage capacity. As an example, the RISC-based MCUs designed by ARM for the IoT segment (i.e. the Cortex-M family) integrate limited integer arithmetic options (16- and 8-bit) and very small on-chip memories (few hundreds of KB). Clearly, this limits the complexity of ConvNets that can be hosted.

As will be discussed in Chapter 2, MCUs poses additional constraints besides low performance and memory, originating from the limited instruction set. Due to the lack of proper hardware components, most of the existing compression strategies turn out to be inefficient when implemented on MCUs. Considering the actual constraints is therefore paramount when devising algorithmic optimizations. To answer this need, we present two novel compression strategies tailored to port ConvNets in memory-bounded MCUs.

### 1.3 Objectives & Contribution

Due to the growing diversity of applications and devices, a *one-size-fits-all* approach to optimize and deploy ConvNets might generate sub-optimal solutions. Instead, there is an urgent need for a comprehensive collection of dedicated tools, responding to different design goals and tailored to different use-cases. In this context, the objective of this dissertation is threefold:

- Develop cross-layer optimizations for software-to-silicon mapping of ConvNets, with vertical strategies aware of the opportunities and the limitations of the hosting systems in order to maximize the portability and the efficiency.

- Offer a collection of methods for the analysis and the compression of ConvNets, addressing different design goals: memory, energy, and power. Designers can adopt the most suited solutions depending on their needs.

- Devise dynamic knobs to extend the achievable accuracy-complexity tradeoffs. Whereas ConvNets are built as static computational graphs, they can leverage software-based (e.g. arithmetic precision) and/or hardware-based (e.g. power management) knobs to adapt at run-time their computational effort depending on context variables, e.g. the available resource budget.

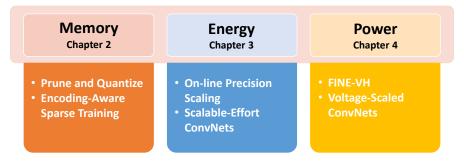

Figure 1.3 summarizes the organization of the thesis, which is split in three main chapters, one for each of the optimization metrics/objectives.

Figure 1.3: Schematic view of the dissertation outline.

Chapter 2 focuses on memory-driven optimizations. We first review existing algorithmic compression techniques, with emphasis on their applicability on real use-cases. The conducted analysis reveals the limits of state-of-the-art techniques, which either cannot be ported on tiny IoT devices like micro-controllers or yield poor performance due to the lack of proper hardware support. We therefore present Prune and Quantize, an efficient heuristic to explore the memory-accuracy design space, assessing the figure of merits of theoretic vs. practical implementations. Second, we introduce a novel training procedure, referred to as Encoding-Aware Sparse Training, aiming at reducing the memory footprint of network weights. As demonstrated by the collected results, our proposal outperforms the accuracy-compression trade-offs of existing reduction strategies based on a sparse representation of data.

Chapter 3 deals with energy-driven optimizations, with emphasis on run-time scaling strategies for dynamic energy-accuracy trade-offs. The chapter first presents a taxonomy of Adaptive ConvNets, with a review and classification of related techniques. As key contributions, the chapter introduces two novel implementations of Adaptive ConvNets: On-line Precision Scaling and Scalable-ConvNets. The former is a design&optimization flow that makes use of per-layer precision scaling strategy to modulate energy and accuracy at run-time. The latter brings the dynamic nature of the human reasoning to static ConvNets, leveraging the concept of multilevel classification. Just like as humans, we show that ConvNets intrinsically learns to classify at different abstraction layers, spanning from coarse categories to fine details. Clearly, high-level classification is easier than low-level classification, creating the opportunity to either reduce the effort or improve the accuracy.

Chapter 4 addresses power-driven optimizations. The most common strategy to reduce power consumption is to design custom hardware components dedicated to run a specific task, inference in our case. Intuitively, architectures tailored to a single task can reach higher performance at lower power consumption than general-purpose cores. Rather than focusing on architectural design, our contribution investigates an orthogonal direction, i.e. power management. First, we propose a novel power distribution scheme called FINE-VH, aiming to bring power management at an ultra-fine granularity, i.e. within the functional units. Through an optimization&emulation framework fully integrated in a standard EDA flow, we demonstrate that FINE-VH pushes power savings beyond the theoretical limits of standard DVFS strategies. Second, we explore the power-performance trade-offs of voltage-scaled ConvNets running on general-purpose systems, e.g. embedded CPUs, where limited cost budgets prevent the adoption of dedicated architectures or custom power distribution schemes. Our study reveals interesting trends, suggesting (i) new directions for thermal-aware training procedures and (ii) useful guidelines for a better co-operation between hardware and software knobs.

Finally, Chapter 5 concludes the dissertation, summarizing the main findings of our research.

### Chapter 2

### Memory-Driven Optimization

An efficient deployment of ConvNets on the network edge requires smart optimizations to fit large models into memory-limited cores. In this chapter, we focus on low-cost IoT applications [26, 27], where small form-factor and limited energy budget are the major bottlenecks. In these cases, the software stack runs on tiny RISC cores mounted on-board of off-the-shelf embedded platforms. Without loss of generality, we consider as a case study the microcontroller units (MCUs) of the Cortex-M family by ARM<sup>1</sup>, reported in Table 2.1. Low-power MCUs integrate small on-chip RAM memories (from 4 to 32 KB for the M0, from 256 to 512 KB for the M7—depending on the chip-set). Off-chip memories are often not integrated as they degrade several metrics, like performance, energy, integration cost, endurance, and reliability. The instruction set architecture (ISA) supports only few 16- and 8-bit integers operations (16- and 8-bit) and often no floating-point. Furthermore, they lack parallel units to accelerate vector operations. A tiny 2lane Single Instruction Multiple Data (SIMD) unit is available in the M4 and M7 cores only. These hardware figures prevent the deployment of ConvNets of some practical use. Even the most compact topology involves the processing of multidimensional tensors of a size that impedes full on-chip storage and real-time processing. A pragmatic solution is to play with algorithmic optimizations, e.g. through compression techniques that shrink the size of the inner tensors. Among the available options [28], pruning and quantization have emerged as the most adopted techniques. Both applied during or after training, they aimed to remove redundant information, namely, those components of the ConvNet with low impact on the prediction quality. Pruning removes less important parameters. Quantization reduces the bit-width of the arithmetic representation of the parameters. As demonstrated by the latest advancements, a joint combination of the two achieves

<sup>&</sup>lt;sup>1</sup>https://os.mbed.com/platforms/

state-of-the-art [29]. Compressed ConvNets show fewer parameters to store, hence fewer operations to run.

| Cortex-M | $\begin{array}{c} \textbf{Power} \\ (\mu \text{W/MHz}) \end{array}$ | RAM<br>(KB) | Floating (32b) | <b>Integer</b> (16b,8b) | SIMD Unit<br>(#lane) |

|----------|---------------------------------------------------------------------|-------------|----------------|-------------------------|----------------------|

| M0       | 5.3                                                                 | 4-32        | No             | Yes                     | No                   |

| M3       | 11.0                                                                | 32 - 128    | No             | Yes                     | No                   |

| M4       | 12.3                                                                | 128 - 256   | No/Optional    | Yes                     | 2                    |

| M7       | 33.0                                                                | 256-512     | No/Optional    | Yes                     | 2                    |

Table 2.1: Hardware figures of the Cortex-M IoT MCUs by ARM.

In the first part of this chapter (Section 2.1), we summarize the existing strategies to alleviate the memory requirements of ConvNets. As will be discussed later, they are based on theoretic studies overlooking the constraints of real hardware. For this reason, they might returns solutions centered on specific configurations that result difficult to be ported on tiny general-purpose cores.

To address this limitation, we present two novel strategies to deploy ConvNets on memory-bounded cores, namely *Prune and Quantize* (Section 2.2) and *Encoding-Aware Sparse Training* (Section 2.3). The former is a two-stage framework that efficiently explores the memory-accuracy space using a lightweight, hardware-aware heuristic optimization. The latter is a novel memory-constrained training procedure that brings quantized ConvNets towards deep compression.

The content of this chapter is a revised version of our previous works found in [30, 31, 32].

# 2.1 Background on Neural Network Compression

With the advent of edge computing, memory and storage capacity have become the main design constraints to consider in order to guarantee the portability of ConvNets. For this reason, many compression methods have been conceived and validated on different platforms [28]. However, only a few of them can be implemented on tiny MCUs. This section reviews prior works in this topic, motivating the choices implemented in our proposals.

### 2.1.1 Pruning

Based on the assumption that ConvNets are over-parameterized, pruning techniques aim to identify and remove those parameters that less contribute to the

expressive power of the model. The pruning can operate at different degrees of spatial granularity. Weight-pruning is the finest level, filter-pruning the coarsest. As a general rule of thumb, a finer grain enables better trade-offs between accuracy and compression. Regarding the implementation on-board of general-purpose cores, a coarse grain achieves better performance, as it keeps regular memory and resource allocation.

Weight-pruning [33] follows an unstructured pattern, i.e. every single weight can be removed, both from fully-connected layers and convolutional layers. To preserve the regular structure of the multi-dimensional tensors, weights are simply zeroed. Unstructured sparsity does not reduce the memory footprint directly but generate long sequences of zero values that can be encoded with standard compression schemes [33]. As the regular structure may get lost, many techniques to accelerate the processing of dense matrices can no longer be applied, e.g. matrix tiling [34]. The efficient processing of sparse data requires dedicated hardware components supporting advanced indexing mechanisms. Examples of this kind can be found in the Texas Instruments TDAx processor [35] family or the custom ASIC described in [36]. Unfortunately, low power budgets impede the integration of such components on MCUs. Even though an equivalent software implementation based on compressed sparse row storage formats could be adopted, the latency overhead due to extra operations is mitigated only when sparsity overcomes a certain threshold [34].

Group-pruning removes bunches of adjacent weights. The group-size is a parameter tuned to maximize the utilization of parallel processing units [34]. Clearly, cores without a parallel unit do not benefit from this approach incurring the same limitations of weight-pruning. As will be discussed in Section 2.2, we present a novel training procedure based on group pruning. However, in our procedure, the group size is tailored to minimize memory rather than improve performance.

Filter-pruning [37] follows structured patterns: neurons (in the fully-connected layers) or entire convolutional filters (in the convolutional layers) are removed reducing both memory footprint and number of operations. Thanks to its regularity, its implementation is straightforward in RISC cores integrating an SRAM memory controlled with a standard indexing mechanism. One potential downside is the risk of a higher accuracy loss, because the information is drained out at a much faster pace (than weight-pruning). However, short few incremental training iterations help to recover the information lost.

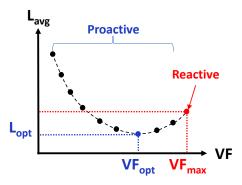

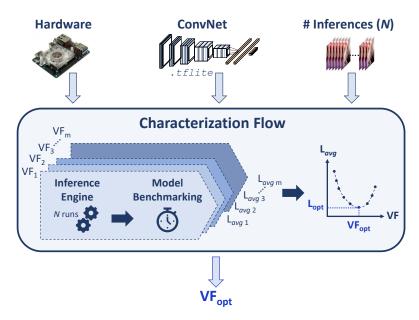

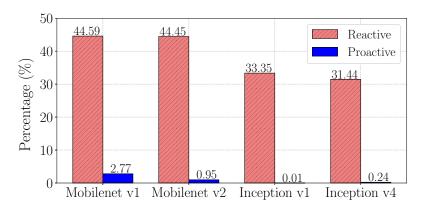

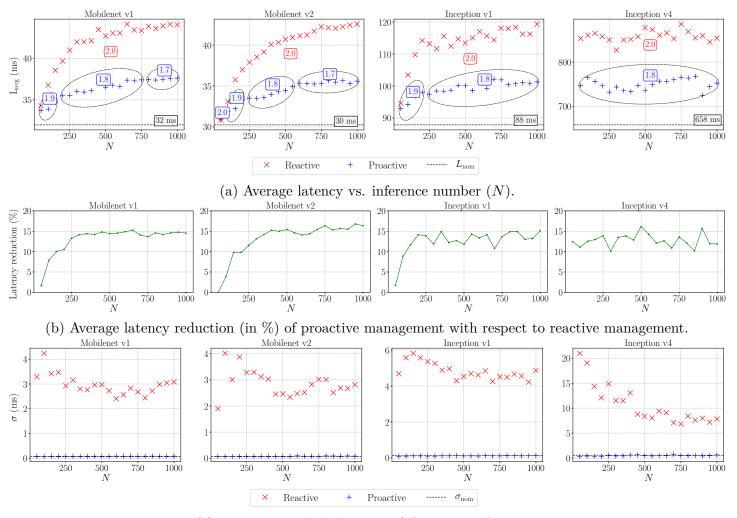

Due to the lack of formal methods to identify the weakest filters, different proxies have been studied to determine the filter priority during the pruning process: (i) the  $\ell_n$ -norm of the kernel weights, (ii) some statistics on the layers output, like mean or standard deviation, (iii) the mutual information between intermediate