FACTA UNIVERSITATIS Series: Electronics and Energetics Vol. 35, N° 2, June 2022, pp. 187-198 https://doi.org/10.2298/FUEE2202187R

**Original scientific paper**

# DESIGN AND PERFORMANCE ANALYSIS OF FULL ADDER USING 6-T XOR-XNOR CELL

# K Srinivasa Rao, Marupaka Aditya, B.S.D. Karthik Raja, CH. Manisai, M. Tharun Sai Reddy, K. Girija Sravani

## Department of ECE, Koneru Lakshmaiah Education Foundation, Vaddeswaram, India

**Abstract**. In this paper, the design and simulation of a high-speed, low power 6-T XOR-XNOR circuit is carried out. Also, the design and simulation of 1-bit hybrid full adder (consisting of 16 transistors) using XOR-XNOR circuit, sum, and carry, is performed to improve the area and speed performance. Its performance is being compared with full adder designs with 20 and 18 transistors, respectively. The performance of the proposed circuits is measured by simulating them in Microwind tool using 180 and 90nm CMOS technology. The performance of the proposed circuit is measured in terms of power, delay, and PDP (Power Delay Product).

Key words: XOR-XNOR circuit, Hybrid full adder

## 1. INTRODUCTION

Logic gates are the basic building blocks of any digital system design. It is an electronic circuit having at least one input and only one output. Logic gates are primarily executed utilizing diodes or transistors acting as electronic switches. Logic circuits include devices such as multiplexers, registers, arithmetic logic units (ALUs), and computer memory, all the way up through complete microprocessors, which may contain in excess of 100 million gates. At present, most gates are made from MOSFETs. The basic circuits we are more familiar at are adders.

There are two types of adders namely half adder and full adder. Half adder which is having two inputs and two outputs are not used in practical applications. Full adders, which are having three inputs and two outputs are being mostly used in applications, like, generating memory addresses inside a computer and to make the Program Counter point to next instruction, the ALU makes use of this adder, FFT algorithms, FIR and IIR filters etc. [1] The conventional full adders used in ALU contains around 28 transistors, which results

Received March 8, 2021; accepted March 27, 2022

Corresponding author: K Srinivasa Rao

Department of ECE, Koneru Lakshmaih Education Foundation (Deemed to be University), Vaddeswaram, India E-mail: srinivasakarumuri@gmail.com

<sup>© 2022</sup> by University of Niš, Serbia | Creative Commons License: CC BY-NC-ND

in more power consumption, delay in output and area. But people today are keener on using technology, which is simple, small, easily carriable, and more reliable for longer time and can be used in more applications. All the above aspects have led to the development of hybrid technology. The building of low power hybrid VLSI systems has emerged as a significant performance goal because of the fast growing technology in mobile communications and computation. [2] Hybrid technology is the combination of two or more different logic styles. Mainly the hybrid 1-bit full adder is a combination of CMOS logic design style, transmission gate logic and pass transistor logic. [3] Most of the hybrid adders are lacking with poor driving capability and power delay product (PDP) when operated at lower voltages.

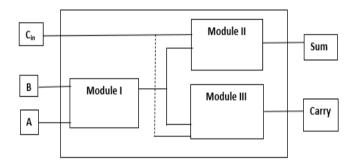

In [3], hybrid logic full adder using 10 transistors XOR-XNOR circuit is proposed and performance parameters like power consumption, delay, PDP and driving capabilities are simulated in Cadence virtuoso tool using 90-nm CMOS technology. The proposed XOR–XNOR circuit is based on CPL and cross-coupled structure. A full adder was also proposed using the same XOR-XNOR circuit, sum and carry as shown in Fig.1.

Fig. 1 Block diagram of hybrid logic FA circuit [3]

In [4], circuits of XOR/XNOR and simultaneous XOR-XNOR circuits are proposed. The proposed XOR-XNOR circuit has 12 transistors and not having a NOT gate on its critical path shows good performance on terms of power consumption, delay, low output capacitance, driving capability and robustness. The proposed XOR–XNOR circuit is saving almost 16.2%–85.8% in PDP, and it is 9%–83.2% faster than the other circuits. In [5], a technique is proposed to access the timing behavior of hybrid full adder, made of both CMOS and FinFET technologies of size 32-nm, and compare their performance in multistage circuits in HSPICE tool. The circuits include transistor function full adder (TFA), transmission gate full adder (TGA), New-HPSC (Hybrid Pass Static CMOS), New-14T full adder and a CCMOS full adder (Conventional CMOS).

In this proposed method, three parameters have been considered for timing behavior namely speed, driving capability and input capacitance. In [6], a design of hybrid full adder using Pass transistors, transmission gates and CMOS logic is proposed. The full adder is implemented in 45-nm technology in Cadence simulation tool. Performance parameters of the proposed full adder is compared with performance of twenty existing full adders with supply voltage ranging from 0.4V to 1.2V. In [7], a 1-bit hybrid full adder using modified XNOR gates is proposed to improve the area & speed and compare its performance with conventional full adder. Performance analysis of the proposed design is simulated in 90-

nm technology with 1.2 V supply voltage. The research is still going on to get a full adder which is applicable for practical applications and at the same time providing good performance in all aspects.

In this paper, our focus is to reduce transistor count and delay of a full adder and then to compare it with the 20 and 18 transistor full adder. First, we tried to present the proposed logic in Xilinx software, which is taking a long time. Then we had the option to do in Tanner software, but the software was not licensed and was not compatible to make circuit with 90-nm and lower nm technologies. Finally, we have constructed the circuit in DSCH tool, converted this into a Verilog file and simulated in Microwind tool.

The rest of the paper is organized as follows: In Section II, the two input 6-T XOR-XNOR Cell is proposed and the full adder (FA) using the proposed XOR–XNOR circuit is also proposed in the same section. In Section III, the performance of the proposed XOR– XNOR cell and full adder in terms of power, speed, and PDP is compared with those of available XOR–XNOR circuits and FAs. Section IV concludes the paper.

#### 2. PROPOSED DESIGN

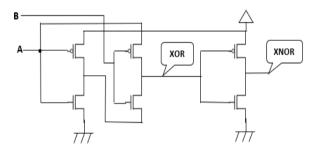

#### 2.1. XOR-XNOR Circuit

XOR-XNOR circuits are the basic building block of many arithmetic and encryption circuits. The proposed XOR-XNOR circuit consists of six transistors as shown in Fig.2. It consists of three PMOS and three NMOS transistors. Here we are using two inverter circuits, one for getting the inverted input of A and other to get inverted output of XOR operation, that is XNOR output. This circuit provides full swing outputs simultaneously.

Fig. 2 Proposed XOR–XNOR circuit

## 2.2. Full Adder Circuit

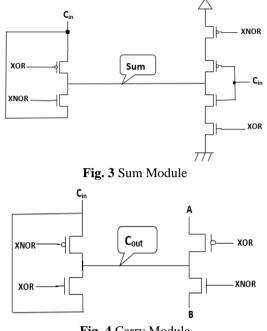

For hybrid logic design, full adder is designed using XOR-XNOR, sum and carry circuits. Here we shall be considering the sum (Fig.3) and carry ( $C_{out}$ ) (Fig.4) circuits with the following expressions (1) & (2):

$$Sum = (A \oplus B)C' + (A \oplus B)'C = (A \oplus B \oplus C)$$

(1)

$$C_{out} = (A \oplus B)C + AB \tag{2}$$

Fig. 4 Carry Module

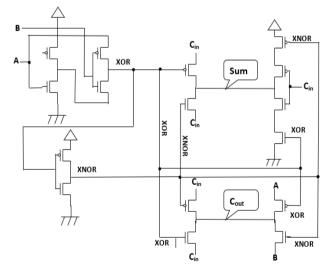

Both sum and carry circuits are constructed using CMOS logic wherein, sum circuit uses six transistors and provides good driving capability and high robustness and carry circuit uses four transistors and consumes lesser power while providing better delay. The proposed XOR-XNOR circuit in Section 2.1, sum (Fig.3) and carry (Fig.4) circuits discussed above are combined to form a full adder of 16 transistors as shown in Fig. 5.

Fig. 5 Proposed Full Adder circuit

Using the logical expressions (1) and (2), truth table for this full adder can be derived as follows:

| Inputs |   |     | Out | puts  |

|--------|---|-----|-----|-------|

| А      | В | Cin | Sum | Carry |

| 0      | 0 | 0   | 0   | 0     |

| 0      | 0 | 1   | 1   | 0     |

| 0      | 1 | 0   | 1   | 0     |

| 0      | 1 | 1   | 0   | 1     |

| 1      | 0 | 0   | 1   | 0     |

| 1      | 0 | 1   | 0   | 1     |

| 1      | 1 | 0   | 0   | 1     |

| 1      | 1 | 1   | 1   | 1     |

Table 1 Truth Table of Full-adder

### 3. RESULTS AND DISCUSSION

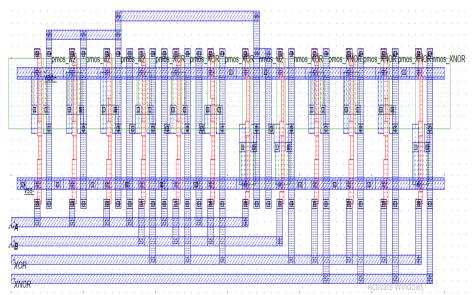

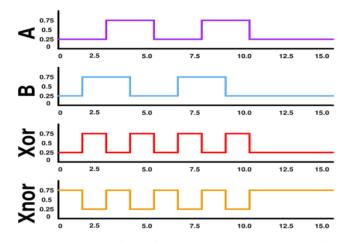

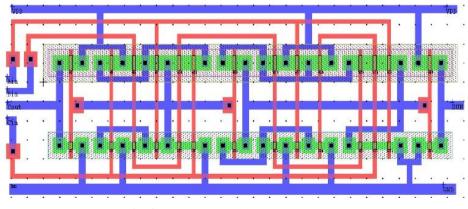

All the circuits which were discussed in previous section are built in DSCH tool and converted into a Verilog file and then compile this file in Microwind tool to get the required circuits as shown in Fig.6 and Fig.8 and verified the performance parameters such as delay, power, and PDP at various supply voltages ranging from 0.5 V to 1.2 V at random frequencies.

## 3.1. XOR-XNOR Circuit

In the XOR-XNOR circuit only two inputs A and B are required which are taken as piecewise linear (pwl) input signal. Fig. 6 shows the circuit design in Microwind tool and Fig.7 shows the applied input pattern to the corresponding XOR–XNOR circuit. In output graph, there are small glitches, but they do not have more affect and we get full swing at the output. Hence, we get the XOR-XNOR outputs simultaneously, which is required for full adder design.

Fig. 6 Proposed XOR-XNOR circuit in Microwind

Fig. 7 Input-output waveforms for the proposed XOR-XNOR circuit

Performance of the same XOR-XNOR circuit is compared at in two different CMOS technologies, i.e., 180 and 90 nm, respectively. For calculation of PDP the worst-case delay of XOR and XNOR outputs is taken. In Table I, XOR circuit delay, in Table II, XNOR circuit delay, in Table III power consumption and in Table IV PDP values are compared.

| _             | Techno | ologies |

|---------------|--------|---------|

| nput Voltages | 180 nm | 90 nm   |

| 0.5 V         | 31     | 11      |

| 0.6 V         | 35     | 13      |

| 0.7 V         | 40     | 16      |

| 0.8 V         | 52     | 19      |

| 0.9 V         | 86     | 23      |

| 1.0 V         | 86     | 30      |

| 1.1 V         | 105    | 36      |

| 1.2 V         | 120    | 49      |

Table 2 XOR Circuit Delay (ps)

|          | Techno | ologies |

|----------|--------|---------|

| Voltages | 180 nm | 90 nm   |

| 0.5 V    | 0      | 0       |

| 0.6 V    | 15     | 15      |

| 0.7 V    | 42     | 24      |

| 0.8 V    | 65     | 25      |

| 0.9 V    | 83     | 37      |

| 1.0 V    | 98     | 43      |

| 1.1 V    | 115    | 55      |

| 1.2 V    | 126    | 62      |

Table 3 XNOR Circuit Delay (ps)

|          | Technologies |       |  |

|----------|--------------|-------|--|

| Voltages | 180 nm       | 90 nm |  |

| 0.5 V    | 6            | 2     |  |

| 0.6 V    | 10           | 4     |  |

| 0.7 V    | 11           | 5     |  |

| 0.8 V    | 12           | 6     |  |

| 0.9 V    | 13           | 7     |  |

| 1.0 V    | 15           | 7     |  |

| 1.1 V    | 15           | 8     |  |

| 1.2 V    | 16           | 9     |  |

Table 4 XOR Power Consumption of XOR-XNOR Circuit (uW)

|          | Technologies |       |  |

|----------|--------------|-------|--|

| Voltages | 180 nm       | 90 nm |  |

| 0.5 V    | 186          | 22    |  |

| 0.6 V    | 350          | 26    |  |

| 0.7 V    | 440          | 72    |  |

| 0.8 V    | 624          | 75    |  |

| 0.9 V    | 1118         | 100   |  |

| 1.0 V    | 1204         | 150   |  |

| 1.1 V    | 1725         | 325   |  |

| 1.2 V    | 1712         | 650   |  |

Table 5 PDP of XOR-XNOR Circuit

As the technology is scaled down, the power as well the PDP values, have a good improvement, when operated in between 0.7 V-1 V. From the above values it can be concluded that whether the delays may have been very high, still the power and PDP values will be suitable for practical use at lower supply voltages.

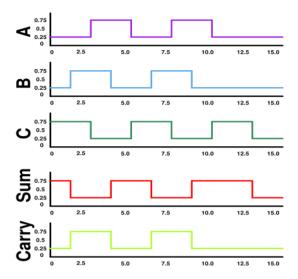

## 3.2. Full Adder Circuit

Fig. 8 shows the full adder circuit design in Microwind tool and Fig.9 shows the applied input pattern and the corresponding full adder circuit. The circuit provides full swing outputs with small glitches.

Fig. 8 Proposed FA circuit in Microwind

Fig. 9 Input-output waveforms for the proposed FA circuit

Performance of the same full adder circuit is compared with two different CMOS technologies, i.e., 180 and 90 nm, respectively. For delay calculation,  $C_{in}$  to  $C_{out}$  delay is considered as this delay is crucial for most of the high-level designs. In Table 6, delay, in Table 7 power consumption and in Table 8 PDP values are compared.

|          | Techno | ologies |

|----------|--------|---------|

| Voltages | 180 nm | 90 nm   |

| 0.5 V    | 1120   | 1021    |

| 0.6 V    | 1062   | 1023    |

| 0.7 V    | 1074   | 1026    |

| 0.8 V    | 1081   | 1029    |

| 0.9 V    | 1088   | 1030    |

| 1.0 V    | 1094   | 1029    |

| 1.1 V    | 1098   | 1030    |

| 1.2 V    | 1120   | 1031    |

| Table 6 Full | Adder | Circuit | Delav | (ns) |

|--------------|-------|---------|-------|------|

|              |       |         |       |      |

|          | Techno | ologies |

|----------|--------|---------|

| Voltages | 180 nm | 90 nm   |

| 0.5 V    | 6      | 6       |

| 0.6 V    | 21     | 7       |

| 0.7 V    | 32     | 9       |

| 0.8 V    | 38     | 10      |

| 0.9 V    | 43     | 12      |

| 1.0 V    | 48     | 16      |

| 1.1 V    | 53     | 35      |

| 1.2 V    | 58     | 75      |

|          | Techno | ologies |

|----------|--------|---------|

| Voltages | 180 nm | 90 nm   |

| 0.5 V    | 6720   | 6126    |

| 0.6 V    | 22302  | 7161    |

| 0.7 V    | 34368  | 9234    |

| 0.8 V    | 41078  | 10290   |

| 0.9 V    | 46784  | 10360   |

| 1.0 V    | 52512  | 16464   |

| 1.1 V    | 58194  | 36050   |

| 1.2 V    | 68032  | 77325   |

Table 8 PDP of Full Adder Circuit

Design and Performance Analysis of High-Performance Full Adder Using 6-T XOR–XNOR Cell 195

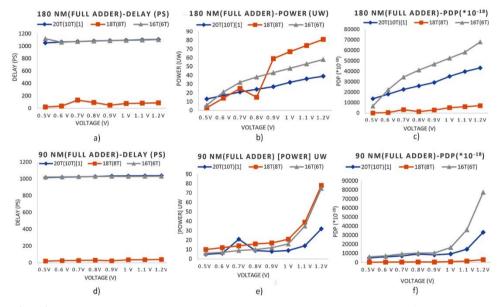

A comparison of the full adder designs with 20T [3] and 18T full adder is done in the form of graphs considering each parameter both in 180 and 90nm technologies, for supply voltages from 0.5 V to 1.2V as shown in Fig. 10.

**Fig. 10** (a) Delay, (b) Power, (c) PDP [180nm] and (d) Delay, (e) Power, (f) PDP [90nm] comparison utilizing different supply voltages 0.5V-1.2V

The delay of the proposed circuit is compared in Fig. 10(a) and Fig. 10(d), power is compared in Fig. 10(b) and Fig. 10(e), PDP is compared in Fig.10(c) and Fig. 10(f). The proposed circuit shows good performance in terms of power and PDP. Although, the delay values are high, but can be applicable for practical uses because the circuit uses least number of transistors.

The approach presented here, faces the challenge in reducing power consumption and delay. This can be controlled by replacing the MOSFETs with the FinFETs.

| Parameters | 180nm Full Adders |       |      |       |

|------------|-------------------|-------|------|-------|

|            | Voltage (V)       | 20T   | 18T  | 16T   |

|            | 0.7V              | 1075  | 131  | 1074  |

| Delay      | 0.8V              | 1082  | 93   | 1081  |

|            | 0.9V              | 1089  | 49   | 1088  |

|            | 1V                | 1095  | 77   | 1094  |

|            | 0.7V              | 21    | 25   | 32    |

| P          | 0.8V              | 24    | 15   | 38    |

| Power      | 0.9V              | 27    | 59   | 43    |

|            | 1V                | 32    | 67   | 48    |

|            | 0.7V              | 22575 | 3275 | 34368 |

| PDP        | 0.8V              | 25968 | 1395 | 41078 |

|            | 0.9V              | 29241 | 2891 | 46784 |

|            | 1V                | 35040 | 5159 | 52512 |

Table 9 Overall Comparison of 180-nm technology

Table 10 Overall Comparison of 90-nm technology

| Parameters | 90nm Full Adders |      |     |       |

|------------|------------------|------|-----|-------|

|            | Voltage (V)      | 20T  | 18T | 16T   |

|            | 0.7V             | 1024 | 28  | 1026  |

| Delay      | 0.8V             | 1029 | 31  | 1029  |

|            | 0.9V             | 1034 | 23  | 1030  |

|            | 1V               | 1035 | 35  | 1029  |

| Power      | 0.7V             | 21   | 14  | 9     |

|            | 0.8V             | 9    | 16  | 10    |

|            | 0.9V             | 8    | 17  | 12    |

|            | 1V               | 9    | 21  | 16    |

| PDP        | 0.7V             | 7168 | 392 | 9234  |

|            | 0.8V             | 9261 | 496 | 10290 |

|            | 0.9V             | 8272 | 391 | 10360 |

|            | 1V               | 9315 | 735 | 16464 |

Table 9 and Table 10 represent the overall comparison of the performance parameters using 180 nm and 90 nm technology, respectively.

Here both the 20T and 18T full adder designs used for comparison of parameters were again designed in Microwind software and obtained different values and compared with our 16T full adder. The previous work was done on cadence tool [4], since we were unable to get same software hence, we performed again using Microwind software.

Table 11 Comparison of Performance parameters of proposed architecture and existing architectures

| Architecture | Power (mW) |

|--------------|------------|

| Proposed     | 21         |

| [27]         | 53         |

| [28]         | 25         |

| [29]         | 40         |

| [30]         | 71         |

Table 11 gives the performance comparison of different architectures in terms of Power. As can be seen that the power consumed of the proposed adder is lower in comparison to that of existing architectures.

#### 4. CONCLUSION

In this paper, a new XOR-XNOR circuit consisting of six transistors is proposed which reduces complexity of the circuit and provides full swing outputs simultaneously. This circuit is combined with sum and carry circuits to form a 16-T full adder circuit. The performance of the proposed XOR-XNOR circuit and the full adder are tested by simulating them using Microwind tool using 180 and 90 nm CMOS technology. The proposed circuits show good performance in terms of power and PDP at lower supply voltages between 0.7 V-1 V. The proposed full adder circuit at 90 nm technology is applicable for higher order cascaded full adder circuits and practical applications at lower supply voltages. It he same circuit is tested in another software, then result could have been much better, and this circuit can be used in applications like digital signal processing, microprocessors etc.

#### REFERENCES

- [1] R. Rajaei, and A. Amirany, "Nonvolatile Low-Cost Approximate Spintronic Full-Adders for Computing in Memory Architectures", *IEEE Trans. Magn.*, vol. 56, no. 4, pp. 1-8. April 2020.

- [2] E. Pakniyat, S. R. Talebiyan and M. J. A. Morad, "Design of high performance and low power 16T full adder cell for sub-threshold technology", In Proceedings of the IEEE International Congress on Technology, Communication and Knowledge (ICTCK), Mashhad, Iran, 2015, pp. 79–85.

- [3] D. Radhakrishnan, "Low voltage CMOS full adder cells", *Electron. Lett.*, vol. 35, no. 21, pp. 1792–1794, Oct. 1999.

- [4] J. Kandpal, A. Tomar, M. Agarwal and K. K. Sharma, "High-Speed Hybrid-Logic Full Adder Using High-Performance 10-T XOR-XNOR Cell", *IEEE Trans. Very Large Scale Integr. VLSI Syst.*, vol. 28, no. 6, pp. 1413–1422, June 2020.

- [5] H. Naseri and S. Timarchi, "Low-power and fast full adder by exploring new XOR and XNOR gates", IEEE Trans. Very Large Scale Integr. VLSI Syst., vol. 26, no. 8, pp. 1481–1493, Aug. 2018.

- [6] H.-R. Basireddy, K. Challa, and T. Nikoubin, (2019) "Hybrid Logical Effort for Hybrid Logic Style Full Adders in Multistage Structures", *IEEE Trans. Very Large Scale Integr. VLSI Syst.*, vol. 27, no. 5, pp. 1138–1147, May 2019.

- [7] M. Hasan, M. J. Hossein, M. Hossain, H. U. Zaman and S. Islam, (2019) "Design of a Scalable Low-Power 1-bit Hybrid Full Adder for Fast Computation", *IEEE Trans. Circuits Syst. II: Express Briefs*, vol. 67, no. 8, pp. 1464–1468, Aug. 2020.

- [8] C. P. Kadu and M. Sharma, "Area-Improved High-Speed Hybrid 1-bit Full Adder Circuit Using 3T-XNOR Gate", In Proceedings of the International Conference on Computing, Communication, Control and Automation (ICCUBEA), 2017, pp. 1–5.

- [9] K. Sanapala and R. Sakthivel, "Ultra-low-voltage GDI-based hybrid full adder design for area and energyefficient computing systems", *IET Circuits, Devices Syst.*, vol. 13, no. 4, pp. 465–470, May 2019.

- [10] D. Abedi and G. Jaberipur, "Decimal Full Adders Specially Designed for Quantum-Dot Cellular Automata", *IEEE Trans. Circuits Syst. II: Express Briefs*, vol. 65, no. 1, pp. 106–110, Jan. 2018

- [11] V. Kolla, T. Nagateja and R. Vaddi, "Robust and energy efficient non-volatile reconfigurable logic circuits with hybrid CMOS-MTJs", In Proceedings of the 3rd International Conference on Emerging Electronics (ICEE), 2016, pp. 1–5.

- [12] R. Rajaei and S. Bakhtavari Mamaghani, "Ultra-Low Power, Highly Reliable, and Non-volatile Hybrid MTJ/CMOS Based Full-Adder for Future VLSI Design", *IEEE Trans. Device Mater. Reliab.*, vol. 17, no. 1, pp. 213–220, March 2017.

- [13] M. Keerthana and T. Ravichandran, "Implementation of Low Power 1-bit Hybrid Full Adder using 22 nm CMOS Technology", In Proceedings of the IEEE 6th International Conference on Advanced Computing and Communication Systems (ICACCS) - Coimbatore, India, 2020, pp. 1215–1217.

- [14] P. Bhattacharyya, B. Kundu, S. Ghosh, V. Kumar and A. Dandapat, "Performance analysis of a low-power high-speed hybrid 1-bit full adder circuit", *IEEE Trans. Very Large Scale Integr. VLSI Syst.*, vol. 23, no. 10, pp. 2001–2008, Oct. 2015.

- [15] H. Thapliyal, F. Sharifi and S. D. Kumar, "Energy-Efficient Design of Hybrid MTJ/CMOS and MTJ/Nanoelectronics Circuits", *IEEE Trans. Magn.*, vol. 54, no. 7, pp. 1–8, July 2018.

#### 198 K. S. RAO, M. ADITYA, B.S.D. K. RAJA, CH. MANISAI, M. THARUN SAI REDDY, K. GIRIJA SRAVANI

- [16] T. Nikoubin, M. Grailoo and S. H. Mozafari, "Cell design methodology based on transmission gate for low-power high-speed balanced XOR-XNOR circuits in hybrid-CMOS logic style", J. Low Power Electron., vol. 6, no. 4, pp. 503–512, Dec. 2010.

- [17] T. Nikoubin, M. Grailoo, C. Li, "Energy and Area Efficient Three-Input XOR/XNORs With Systematic Cell Design Methodology", *IEEE Trans. Very Large Scale Integr. VLSI Syst.*, vol. 24, no. 1, pp. 398–402, Jan. 2016.

- [18] A. M. Shams, T. K. Darwish, and M. A. Bayoumi, "Performance analysis of low-power 1-bit CMOS full adder cells", *IEEE Trans. Very Large Scale Integr. VLSI Syst.*, vol. 10, no. 1, pp. 20–29, Feb. 2002.

- [19] S. Janwadkar and S. Das, "Design and Performance Evaluation of Hybrid Full Adder for Extensive PDP Reduction at 180 nm technology", In Proceedings of the 3rd International Conference for Convergence in Technology (I2CT), Apr. 06-08, 2018, pp. 1–6.

- [20] M. Agarwal, N. Agrawal and M. A. Alam, "A new design of low power high speed hybrid CMOS full adder", In Proceedings of the International Conference on Integrated Networks, 2014, pp. 448–452.

- [21] S. Goel, A. Kumar and M. Bayoumi, "Design of robust, energy efficient full adders for deep-submicrometer design using hybrid-CMOS logic style", *IEEE Trans. Very Large Scale Integr. VLSI Syst.*, vol. 14, no. 12, pp. 1309-1321, Dec. 2006.

- [22] R. Zimmermann and W. Fichtner, "Low-power logic styles: CMOS versus pass-transistor logic", *IEEE J. Solid-State Circuits*, vol. 32, no. 7, pp. 1079-1090, July 1997.

- [23] K. Navi, M. Maeen, V. Foroutan, S. Timarchi and O. Kavehei, "A low-power full-adder cell for low voltage", VLSI J. Integr., vol. 42, no. 4, pp. 457–467, Sept. 2009.

- [24] A. M. Shams, T. K. Darwish and M. A. Bayoumi, "Performance analysis of low-power 1-bit CMOS full adder cells", *IEEE Trans. Very Large Scale Integer. VLSI Syst.*, vol. 10, no. 1, pp. 20–29, Feb. 2002.

- [25] J.-F. Lin, Y.-T. Hwang, M.-H. Sheu and C.-C. Ho, "A hybrid high-speed and energy efficient 10-transistor full adder design", *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 54, no. 5, pp. 1050–1059, May 2007.

- [26] S. Kumar, A. Kumar and P. Bansal, "High speed area efficient 1-bit hybrid full adder" In Proceedings of the IEEE International Conference on Electrical, Electronics, and Optimization Techniques (ICEEOT)-Chennai, India, 2016, pp. 682–686.

- [27] N. Temenos and P. P. Sotiriadis, "Nonscaling Adders and Subtracters for Stochastic Computing Using Markov Chains", *IEEE Trans. Very Large Scale Integer. VLSI Syst.*, vol. 29, no. 9, pp. 1612–1623, Sept. 2021.

- [28] V. T. Lee, A. Alaghi, J. P. Hayes, V. Sathe and L. Ceze, "Energy-efficient hybrid stochastic-binary neural networks for near-sensor computing", In Proceedings of the Design, Automation & Test in Europe Conference & Exhibition, Lausanne, Switzerland, Mar. 2017, pp. 13–18.

- [29] P. Ting and J. P. Hayes, "Eliminating a hidden error source in stochastic circuits", In Proceedings of the IEEE International Symposium Defect Fault Tolerance VLSI Nanotechnology Syst. (DFT), Oct. 2017, pp. 1–6.

- [30] A. Ren et al., "SC-DCNN: Highly-scalable deep convolutional neural network using stochastic computing", In Proceedings of the 22nd ACM International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), Xi'an, China, Apr. 2017, pp. 405–418.