FACTA UNIVERSITATIS Series: Electronics and Energetics Vol. 35, N° 1, March 2022, pp. 29-41 https://doi.org/10.2298/FUEE2201029B

**Original scientific paper**

# ALL-OPTICAL FREQUENCY ENCODED DIBIT-BASED PARITY GENERATOR USING REFLECTIVE SEMICONDUCTOR OPTICAL AMPLIFIER WITH SIMULATIVE VERIFICATION\*

## Surajit Bosu<sup>1</sup>, Baibaswata Bhattacharjee<sup>2</sup>

<sup>1</sup>Department of Physics, Bankura Sammilani College, Bankura, India (W.B) <sup>2</sup>Department of Physics, Ramananda College, Bishnupur, Bankura, India (W.B)

Abstract. High-speed signal computation and communication are an essential part of modern communication that increases optical necessity. Therefore, researchers developed different types of digital devices in the all-optical domain. Due to the versatile gain medium of reflective semiconductor optical amplifiers (RSOAs), it has various important applications in passive optical networks. In comparison with semiconductor optical amplifier (SOA), RSOAs exhibit better gain performance because of their double pass property. Therefore, RSOA shows better switching properties. In this communication, co-propagation scheme of RSOA is used to design and analyze a frequency encoded dibit-based parity generator. Taking the advantages of RSOA like high switching speed, low noise, high gain, and low power consumption, the proposed design achieves these qualities. This design simulated in MATLAB and simulated outputs accurately verify the truth table.

Key words: Optical communication, Reflective semiconductor optical amplifier, Frequency encoding, Dibit-based logic system, Parity generator.

## 1. INTRODUCTION

The photon becomes more popular for information transmission [2, 3]. Photons can carry information at a superfast speed. Therefore, the researchers are very interested to design photon-based devices [4, 5] instead of electron-based devices. The data signal can be transmitted in long-range using different types of encoding techniques [6-8]. The frequency encoding [9-13] technique is more reliable in long-range signal propagation. In optical communication, the adder [1, 14-16], subtractor [17], comparator [9, 18], parity generator are basic components for arithmetic, decision-making circuits, logic units [19-25], and memory units [11].

Received August 9, 2021; accepted September 29, 2021

Corresponding author: Surajit Bosu

Bankura Sammilani College, Faculty of Physics, Bankura, West Bengal, India

- E-mail: surajitbosu7@gmail.com

- <sup>\*</sup> An earlier version of this paper was presented at the 4th International conference on 2021 Devices for Integrated Circuit (DevIC 2021), May 19-20, 2021, in Kalyani, West Bengal, India [1].

S. BOSU, B. BHATTACHARJEE

These are the basic building blocks of optical data processors. In the frequency encoding concept [1], the digital logic states '0' and '1' are indicated by frequencies  $v_1$  and  $v_2$  respectively. In communication and data storage systems, the parity generator is a very essential device. In the last decade, researchers are working for parity generators.

From the literature survey, it is found that the even/odd parity generator units are not designed in a single device and also dibit-based logic and frequency encoding scheme is also first time implementation. In this communication, a frequency encoded dibit-based even/odd parity generator in the all-optical domain, using add/drop multiplexer (ADM) and reflective semiconductor optical amplifier (RSOA) is devised. From the previous version [1], we adopted the logic of SUM from the design of a half adder using RSOA and ADM. In half-adder design [1], two input dibit-based logic is used but in this proposed design, we have implemented three inputs dibit-based logic. So the operation of the three inputs dibit-based logic is much more complicated than the previous version [1]. This proposed design is a single device for the even/odd parity generator units and it has no extra control terminal. As a result, the devised design reduces the space of the device as well as simultaneously generates even and odd parity. Introducing the dibit-based logic in this design, one can be expected a high degree of parallelism. The frequency encoding and dibit-based systems reduce also the bit error problems and enhance the speed of operation in long-range transmission. Since RSOA has ultrafast switching property with low noise, so the proposed design operates at ultrafast speed. In the results and discussion section, the proposed design is compared with the other designs [26, 28, 33, 36] which are given in Table 3.

The remaining part is structured as follows: Related works are described in Section 2. The working principle of RSOA and ADM are described in Section 3. Section 4 describes the operation scheme of the proposed parity generator. The simulation experiment of the proposed model is described in Section 5. The results and discussion of the proposed system are presented in Section 6. Finally, the conclusions with potential future works are given in Section 7.

## 2. RELATED WORKS

The researchers are working for parity generators during the past several years. Some of these legendary works are discussed here. Chowdhury et al. [26] have introduced a design of 4-bit parity generator and checker using non-linear material-based switches. Using spatial light modulator and Savart plate a parity generator and parity checker has been reported by Ghosh [27]. Dimitriadou et al. [28] have introduced a 4-bit parity generator and checker. They used a high-speed switch to design the parity generator. This high-speed switch is based on Quantum-Dot-SOA-based MZI and their design is verified through numerical simulation. This design is based on the modified trinary number system. A micro-ring-resonator (MRR)-based parity generator and checker have been reported by Rakshit et al. [29] and it also verified using numerical simulation. Mehra et al. [30] have introduced an SOA-MZI-based 7-bit parity generator and checker circuit. This design is simulated at high-speed 120 GHz. Bhattacharyya et al. [31] have reported a 4-bit parity generator using an SOA-assisted Sagnac switch and the design is verified through numerical simulation. Kumar et al. [32] have reported a parity checker using the electro-optic effect in MZI. Using the MATLAB software, results are obtained and

optiBPM software is used for verification of the implementation of this design. Wang et al. [33] have reported parity checker in the all-optical domain and the works implemented in the nanoscale-integrated chip. Plasmonic Metal-Insulator-Metal (MIM)-based parity generator has been reported by Singh et al. [34]. This design is simulated in MATLAB. Kaur et al. [35] have proposed an SOA-MZI-based 3-bit parity generator and checker and also transfer matrix method (TMM) based time-domain simulation is done for this design. Nair et al [36] have introduced an SOA-MZI-based 3-bit parity generator and checker in the all-optical domain. They used the tree architecture concept to design their work. Maji et al. [37] have proposed a design of a 4-bit parity generator and checker using a reflective semiconductor optical amplifier. They have introduced a single device in which even/odd parity generator units are designed but they have used an extra control terminal to switch between the even-odd parity units.

#### 3. WORKING PRINCIPLE OF RSOA AND ADM

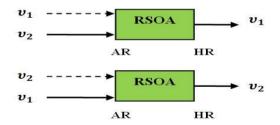

As mentioned in the introduction, the basic key components of the proposed design are RSOA and ADM. Now, the working principle of these two is logically explained in this section. So, one pump signal (strong) and a probe signal (weak) are injected into the input signals of SOA but a high power probe beam is obtained at the output. This design is based on cross gain modulation (XGM) [1, 38]. Therefore, it is called RSOA. A high reflective (HR) and an anti-reflective (AR) coating are placed in the two facets of RSOA [1, 22, 25, 38-41]. It has a very versatile high gain medium so it has various important applications in passive optical networks (PON). Here, the frequency corresponding to the wavelengths of the probe signals is in the C-band (1535-1570 nm). The saturation power of RSOA may be used within 5-20 dBm [1, 9, 43].

Fig. 1 Block diagram of RSOA

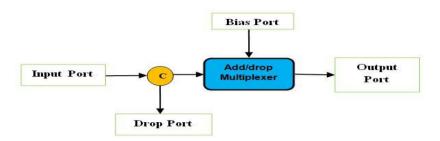

An add/drop multiplexer (ADM) [41-43] is very popular as a frequency selector. If we consider, the frequencies,  $v_2$  and  $v_1$  are injected into the bias and input port of ADM respectively, then at the output frequency,  $v_1$  is obtained whereas nothing at the drop port. If we consider the same frequency,  $v_1$  (or  $v_2$ ) into the input and bias port then ADM reflects the input signal,  $v_1$  (or  $v_2$ ) at the drop port by the circulator whereas nothing is obtained at the output. The schematic diagram of ADM is given in Fig. 2. RSOA and ADM are used to develop different devices such as multiplexer, adder, comparator, etc. [1, 9-10, 41].

Fig. 2 Block diagram of ADM

4. PROPOSED SCHEME OF OPERATION OF THE THREE-BIT PARITY GENERATOR

In this section, the 3-bit parity generator and its operational scheme is proposed. Here, A, B, and C are the frequency encoded dibit-based inputs whose parity will be generated. The Boolean expression of even and odd parity generators are

$$Y_{even} = A \oplus B \oplus C \tag{1}$$

$$Y_{odd} = A \oplus B \oplus C \tag{2}$$

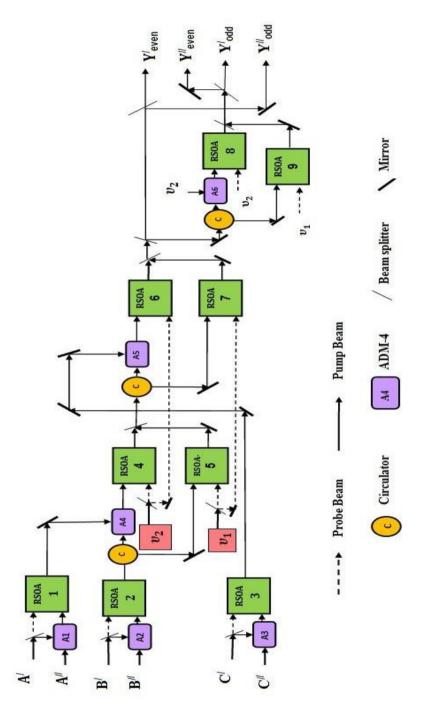

The schematic diagram of this design is given in Fig. 3. In this proposed design, frequency encoding technique and dibit-based logic are opted. Mukhopadhyay [44] first reported the dibit-based representation technique. According to this representation technique [1, 9-10, 42-44], two consecutive bit positions are chosen to represent a digit. Here, digital logic states '0' and '1' are represented by the dibits '01' and '10' respectively. Since the proposed design is frequency encoding, so two different frequencies  $v_1$ , and  $v_2$  when placed side by side as ' $v_2 v_1$ '' indicates the logic state '1' and ' $v_1 v_2$ '' indicates the digital logic state '0'. Here, we adopted the logic of SUM from the design of half adder [1] using RSOA and ADM. In half-adder design, two inputs dibit-based logic. So the operation of the three inputs dibit-based logic is much more complicated than the previous version [1]. The operation of the proposed designs is based on the Eqs. 1-2. Now, the operation scheme of the proposed frequency encoded dibit-based parity generator describe in the following cases.

#### 4.1. Case-I (When all the inputs are the same)

In this case,  $A'=v_1$ ,  $A''=v_2$ ,  $B'=v_1$ ,  $B''=v_2$ ,  $C'=v_1$ ,  $C''=v_2$  frequencies are injected into the input terminals. Therefore,  $v_1$  frequencies are obtained from the RSOA-3, RSOA-2, and RSOA-1. The outputs of RSOA-2 and RSOA-1 are injected into A4 (ADM-4) as input and bias signals. Since both the frequency, of A4 is the same then frequency,  $v_1$  is obtained at the drop port through the circular. This frequency,  $v_1$  acts as a pump signal of RSOA-5 and probe signal frequency,  $v_1$  so the output of RSOA-5 is frequency,  $v_1$ . This frequency,  $v_1$  acts as an input signal of A5 (ADM-5) and its biasing signal is  $v_1$  which is the output frequency of RSOA-3. Since both the frequencies of A5 (ADM-5) are the

same then A5 reflects the input signal,  $v_1$  at the drop port. This frequency,  $v_1$  works as a pump signal of RSOA-7. Therefore, the output of RSOA-7 is frequency,  $v_1$ . One part of this frequency directly shows the dibit output  $Y'_{even}$  and another part acts as an input of A6 (ADM-6) which is biased by the signal of frequency,  $v_2$ . Therefore, A6 selects the input signal of frequency,  $v_1$  to the output and this output frequency,  $v_1$  works as the pump signal of RSOA-8. This yields  $v_2$  at the dibit output terminal,  $Y'_{even}$ . Finally, the dibit outputs  $v_1$  and  $v_2$  are obtained at the output terminals,  $Y'_{even}$  and  $Y''_{even}$  respectively, which indicates the digital logic state '0' and the dibit outputs  $v_2$ ,  $v_1$  are obtained at the dibit output terminals,  $Y'_{otd}$  and  $Y''_{otd}$  which altogether indicates the digital logic state '1'. Therefore, when inputs, A=0, B=0, and C=0 then the outputs show even parity,  $Y_{even}=0$  and odd parity,  $Y_{otd} = 1$ .

Similarly, when  $A'=v_2$ ,  $A''=v_1$ ,  $B'=v_2$ ,  $B''=v_1$ ,  $C'=v_2$ , and  $C''=v_1$  are taken as input signals to the device then the dibit outputs  $v_1$ ,  $v_2$  are obtained at the dibit output terminals,  $Y'_{even}$  and  $Y''_{even}$  respectively which altogether indicates the digital logic state '0' and the dibit outputs  $v_2$ ,  $v_1$  are obtained at the dibit output terminals,  $Y'_{odd}$  and  $Y''_{odd}$  which altogether indicates the digital logic state '1'. Therefore, when inputs, A=1, B=1, and C=1 then the outputs show even parity,  $Y_{even}=0$  and odd parity,  $Y_{odd}=1$ .

## 4.2. Case-I I (When one input is different)

Here,  $A'=v_2$ ,  $A''=v_1$ ,  $B'=v_1$ ,  $B''=v_2$ ,  $C'=v_2$ , and  $C''=v_1$  are applied as the input signals of the device. Therefore, frequencies,  $v_2$ ,  $v_1$ , and  $v_2$  are obtained at the outputs of RSOA-3, RSOA-2, and RSOA-1 respectively. The outputs from RSOA-2 and RSOA-1 are injected into the A4 (ADM-4) as input and biasing signals respectively. Since both the frequencies of A4 are not the same then the input signal is selected by the A4 at the output. This frequency,  $v_1$  acts as a pump signal of RSOA-4 and its probe signal is  $v_2$  so the output of RSOA-5 is  $v_2$ . This frequency,  $v_2$  acts as an input frequency of A5 (ADM-5), and the output frequency,  $v_2$  of RSOA-3 works as biasing frequency. Since both the frequency of A5 (ADM-5) are the same then A5 reflects the input signal of frequency,  $v_2$  at the drop port. This frequency,  $v_2$  works as a pump signal of RSOA-7. Therefore, the output of RSOA-7 is frequency,  $v_1$ , one part of this frequency directly shows the dibit output  $Y'_{even}$ and another part acts as an input of A6 (ADM-6) which is biased with the frequency, v2. Therefore, A6 selects the frequency,  $v_1$  at the output, and this output frequency,  $v_1$  acts as pump signal of RSOA-8 which gives  $v_2$  at the dibit output terminal,  $Y''_{even}$ . Finally, the dibit output  $v_1$  and  $v_2$  are obtained at the output terminals,  $Y'_{even}$  and  $Y''_{even}$  respectively, which indicates the digital logic state '0' and the dibit outputs  $v_2$  and  $v_1$  are obtained at the dibit output terminals,  $Y'_{odd}$  and  $Y''_{odd}$  which altogether indicates the digital logic state '1'. Therefore, when inputs, A=1, B=0, and C=1 then the outputs show even parity,  $Y_{even}=0$  and odd parity,  $Y_{odd}=1$ .

Fig. 3 Schematic diagram of proposed parity generator

Similarly, when  $A'=v_1$ ,  $A''=v_2$ ,  $B'=v_2$ ,  $B''=v_1$ ,  $C'=v_2$ , and  $C''=v_1$  are taken as input signals to the device then the dibit outputs  $v_1$ ,  $v_2$  are obtained at the dibit output terminals,  $Y'_{even}$  and  $Y''_{even}$  respectively which altogether indicates the digital logic state '0' and the dibit outputs  $v_2$ ,  $v_1$  are obtained at the dibit output terminals,  $Y'_{odd}$  and  $Y''_{odd}$  which altogether indicates the digital logic state '1'. Therefore, when inputs, A=0, B=1, and C=1 then the outputs show even parity,  $Y_{even}=0$  and odd parity,  $Y_{odd}=1$ . In this way, other outputs can be obtained and these are given in Table 1.

|              |              | Di           | bit Input    | Dibit Output |              |              |                      |                    |                          |  |

|--------------|--------------|--------------|--------------|--------------|--------------|--------------|----------------------|--------------------|--------------------------|--|

|              | Input Input  |              |              |              | Input        |              | Even parity          |                    | Odd parity               |  |

|              | (Â)          |              | ( <b>B</b> ) |              | (Ĉ)          |              | (Yeven)              |                    | (Y <sub>odd</sub> )      |  |

| A'           | A″           | Β′           | B″           | C′           | C//          | Y'even       | Y <sup>//</sup> even | $Y^{\prime}_{odd}$ | $Y^{\prime\prime}_{odd}$ |  |

| $\upsilon_1$ | $\upsilon_2$ | $\upsilon_1$ | $\upsilon_2$ | $\upsilon_1$ | $\upsilon_2$ | $\upsilon_1$ | $\upsilon_2$         | $\upsilon_2$       | $\upsilon_1$             |  |

| $\upsilon_1$ | $\upsilon_2$ | $\upsilon_1$ | $\upsilon_2$ | $\upsilon_2$ | $\upsilon_1$ | $\upsilon_2$ | $\upsilon_1$         | $\upsilon_1$       | $\upsilon_2$             |  |

| $\upsilon_1$ | $\upsilon_2$ | $\upsilon_2$ | $\upsilon_1$ | $\upsilon_1$ | $\upsilon_2$ | $\upsilon_2$ | $\upsilon_1$         | $\upsilon_1$       | $\upsilon_2$             |  |

| $\upsilon_1$ | $\upsilon_2$ | $\upsilon_2$ | $\upsilon_1$ | $\upsilon_2$ | $\upsilon_1$ | $\upsilon_1$ | $\upsilon_2$         | $\upsilon_2$       | $\upsilon_1$             |  |

| $\upsilon_2$ | $\upsilon_1$ | $\upsilon_1$ | $\upsilon_2$ | $\upsilon_1$ | $\upsilon_2$ | $\upsilon_2$ | $\upsilon_1$         | $\upsilon_1$       | $\upsilon_2$             |  |

| $\upsilon_2$ | $\upsilon_1$ | $\upsilon_1$ | $\upsilon_2$ | $\upsilon_2$ | $\upsilon_1$ | $\upsilon_1$ | $\upsilon_2$         | $\upsilon_2$       | $\upsilon_1$             |  |

| $\upsilon_2$ | $\upsilon_1$ | $\upsilon_2$ | $\upsilon_1$ | $\upsilon_1$ | $\upsilon_2$ | $\upsilon_1$ | $\upsilon_2$         | $\upsilon_2$       | $\upsilon_1$             |  |

| $\upsilon_2$ | $\upsilon_1$ | $\upsilon_2$ | $\upsilon_1$ | $\upsilon_2$ | $\upsilon_1$ | $\upsilon_2$ | $\upsilon_1$         | $\upsilon_1$       | $\upsilon_2$             |  |

Table 1

Frequency encoded truth table of proposed design

#### 5. SIMULATION OF THE PROPOSED PARITY GENERATOR

In the previous section, the operational scheme of the proposed design is explained theoretically. Now, we discuss the simulation model of the proposed design. Using MATLAB (R2018a) software, the proposed design of the parity generator is verified. RSOAs and ADMs are programming on the basis of their characteristics using MATLAB language. If frequencies,  $v_1=193.5$  THz (wavelength=1550 nm) and  $v_2=194.1$  THz (wavelength=1545 nm) are considered as the probe signal and pump signal then, 193.5 THz is obtained at the output port whereas 194.1 THz is obtained at the output port when  $v_1=193.5$  THz (wavelength=1550 nm) and  $v_2=194.1$  THz are considered as the pump and probe signals. If frequencies,  $v_1=193.5$  THz and  $v_2=194.1$  THz are considered as the input and biasing signals then, ADM selects the input signal (193.5 THz) at the output whereas nothing is obtained at the drop port. If the same frequencies are injected at the biasing and input port then, ADM reflects the input signal at the drop port whereas output gives nothing. By the use of these considerations, this design is simulated.

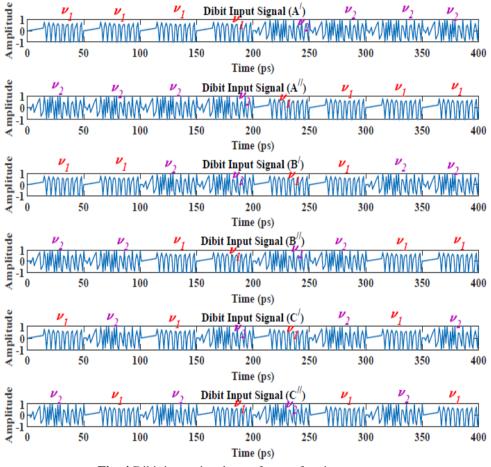

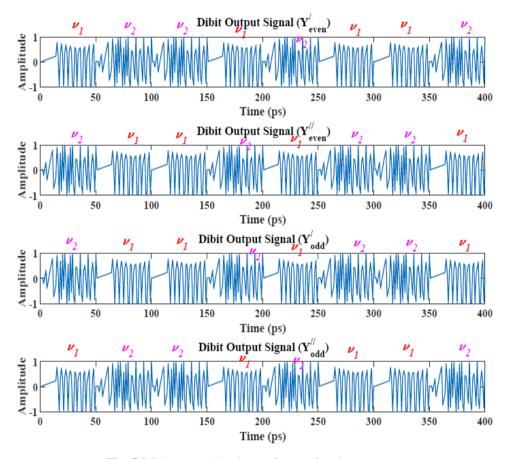

In Figs. 4, and 5, dibits <193.5><194.1> and <194.1><193.5> indicate the digital logic states '0', and '1' respectively. From Fig. 4, the dibits <193.5><194.1>, <194.1><193.5> and <193.5><194.1>, <194.1><193.5> and <193.5><194.1>, are injected into the dibit inputs 'A', 'B' and 'C' terminals of the device respectively. As a result, <194.1><193.5> and <193.5><194.1> are obtained as dibit even parity, Y<sub>even</sub> and dibit odd parity, Y<sub>odd</sub> at the output terminals respectively. Dibits <194.1><193.5>, and <193.5><194.1> are injected into the dibit inputs 'A', 'B' and 'C' terminals respectively. Dibits <194.1><193.5>, and <193.5>, <194.1><193.5>, and <193.5><194.1> are injected into the dibit inputs 'A', 'B', and 'C' terminals respectively. As a result, <193.5><194.1> are injected into the dibit inputs 'A', 'B', and 'C' terminals respectively. As a result, <193.5><194.1> and <194.1><193.5> are obtained as dibit even parity, Y<sub>even</sub> and dibit odd parity, Y<sub>odd</sub> at the output terminals

respectively. <194.1><193.5>, <194.1><193.5>, and <194.1><193.5> are injected into the dibit inputs 'A', 'B' and 'C' terminals respectively. Therefore, <194.1><193.5>, and <193.5><194.1> are yielded as dibit even parity, Y<sub>even</sub> and dibit odd parity, Y<sub>odd</sub> at the output terminals respectively. Similar way, other outputs are obtained corresponding to the applied inputs. All the dibit output waveforms corresponding to the dibit input waveforms are given in Fig. 5. The results of the simulation are discussed in the next section.

Fig. 4 Dibit input signal waveforms of parity generator

## 6. RESULTS AND DISCUSSION

In this section, the theoretical interpretation and the simulation results are discussed. In this design, two signals with different frequencies,  $v_1$ =193.5 THz and  $v_2$ =194.1 THz are injected into the 50 ps time intervals to the input. The input and output signal waveforms are given in Figs. 4 and 5. The simulation (given in Table 2) verifies the parity generator results.

Fig. 5 Dibit output signal waveforms of parity generator

S. BOSU, B. BHATTACHARJEE

In the first 50 ps, we applied " $v_1 v_2$ " in A, " $v_1 v_2$ " in B, and " $v_1 v_2$ " in C that indicates A=0, B=0, and C=0. After simulation with these data, we obtained  $Y'_{even}=v_1$ ,  $Y''_{even}=v_2$ , and  $Y'_{odd}=v_2$ ,  $Y''_{odd}=v_1$  that indicates  $Y_{even}=0$ , and  $Y_{odd}=1$ . In 50-100 ps, we applied " $v_1$  $v_2$ " in A, " $v_1$   $v_2$ " in B, and " $v_2$   $v_1$ " in C that indicates A=0, B=0, and C=1. After simulation with these data, we obtained  $Y'_{even} = v_2$ ,  $Y''_{even} = v_1$ , and  $Y'_{odd} = v_1$ ,  $Y''_{odd} = v_2$  that indicates Yeven=1, and Yodd=0. In 100-150 ps, we applied "v1 v2" in A, "v2 v1" in B, and " $v_1$   $v_2$ " in C that indicates A=0, B=1, and C=0. After simulation with these data, we obtained  $Y'_{even} = v_2$ ,  $Y''_{even} = v_1$ , and  $Y'_{odd} = v_1$ ,  $Y''_{odd} = v_2$  that indicate  $Y_{even} = 1$ , and  $Y_{odd} = 0$ . In 150-200 ps, we applied " $v_1 v_2$ " in A, " $v_2 v_1$ " in B, and " $v_2 v_1$ " in C that indicates A=0, B=1, and C=1. After simulation with these data, we obtained  $Y'_{even}=\upsilon_1$ ,  $Y''_{even}=\upsilon_2$ , and  $Y'_{odd}=v_2$ ,  $Y''_{odd}=v_1$  that indicate  $Y_{even}=0$ , and  $Y_{odd}=1$ . In 200-250 ps, we applied " $v_2 v_1$ " in A, "v<sub>1</sub> v<sub>2</sub>" in B, and "v<sub>1</sub> v<sub>2</sub>" in C that indicates A=1, B=0, and C=0. After simulation with these data, we obtained  $Y'_{even} = v_2$ ,  $Y''_{even} = v_1$ , and  $Y'_{odd} = v_1$ ,  $Y''_{odd} = v_2$  that indicate  $Y_{even} = 1$ , and Y<sub>odd</sub>=0. In 250-300 ps, we applied " $\upsilon_2 \upsilon_1$ " in A, " $\upsilon_1 \upsilon_2$ " in B, and " $\upsilon_2 \upsilon_1$ " in C that indicates A=1, B=0, and C=1. After simulation with these data, we obtained  $Y'_{even}=v_1$ ,  $Y''_{even} = v_2$ , and  $Y'_{odd} = v_2$ ,  $Y''_{odd} = v_1$  that indicates  $Y_{even} = 0$ , and  $Y_{odd} = 1$ . In 300-350 ps, we applied " $v_2 v_1$ " in A, " $v_2 v_1$ " in B, and " $v_1 v_2$ " in C that indicates A=1, B=1, and C=0. After simulation with these data, we obtained  $Y'_{even} = v_1$ ,  $Y''_{even} = v_2$ , and  $Y'_{odd} = v_2$ ,  $Y''_{odd} = v_1$ that indicates Y<sub>even</sub>=0, and Y<sub>odd</sub>=1. In 350-400 ps, we applied "v<sub>2</sub> v<sub>1</sub>" in A, "v<sub>2</sub> v<sub>1</sub>" in B, and "v<sub>2</sub> v<sub>1</sub>" in C that indicates A=1, B=1, and C=1. After simulation with these data, we obtained  $Y'_{even} = v_2$ ,  $Y''_{even} = v_1$ , and  $Y'_{odd} = v_1$ ,  $Y''_{odd} = v_2$  that indicate  $Y_{even} = 1$ , and  $Y_{odd} = 0$ . After the verification of the simulation results (given in Table 2), and the truth table (Table1), it is interpreted that the proposed design works accurately. A comparative study with previous work is given in Table 3.

Table 2 Simulation results of proposed parity generator (all the frequencies are in THz range)

|         |       | Ι     | Dibit Inp     | ut    | Dibit Output |       |                     |                      |                    |                          |

|---------|-------|-------|---------------|-------|--------------|-------|---------------------|----------------------|--------------------|--------------------------|

|         | Input |       | Input         |       | Input        |       | Even parity         |                      | Odd parity         |                          |

| Time    | (Å)   |       | (B)           |       | (C)          |       | (Yeven)             |                      | $(Y_{odd})$        |                          |

| (ps)    | Α′    | A″    | $\mathbf{B}'$ | B″    | C′           | C″    | Y <sup>/</sup> even | Y <sup>//</sup> even | $Y^{\prime}_{odd}$ | $Y^{\prime\prime}_{odd}$ |

| 0-50    | 193.5 | 194.1 | 193.5         | 194.1 | 193.5        | 194.1 | 193.5               | 194.1                | 194.1              | 193.5                    |

| 51-100  | 193.5 | 194.1 | 193.5         | 194.1 | 194.1        | 193.5 | 194.1               | 193.5                | 193.5              | 194.1                    |

| 101-150 | 193.5 | 194.1 | 194.1         | 193.5 | 193.5        | 194.1 | 194.1               | 193.5                | 193.5              | 194.1                    |

| 151-200 | 193.5 | 194.1 | 194.1         | 193.5 | 194.1        | 193.5 | 193.5               | 194.1                | 194.1              | 193.5                    |

| 201-250 | 194.1 | 193.5 | 193.5         | 194.1 | 193.5        | 194.1 | 194.1               | 193.5                | 193.5              | 194.1                    |

| 251-300 | 194.1 | 193.5 | 193.5         | 194.1 | 193.5        | 194.1 | 193.5               | 194.1                | 194.1              | 193.5                    |

| 301-350 | 194.1 | 193.5 | 194.1         | 193.5 | 193.5        | 194.1 | 193.5               | 194.1                | 194.1              | 193.5                    |

| 351-400 | 194.1 | 193.5 | 194.1         | 193.5 | 194.1        | 193.5 | 194.1               | 193.5                | 193.5              | 194.1                    |

| Work          | Simulation of bit pattern | RSOA<br>used or not | Even and Odd parity generator |     |     |

|---------------|---------------------------|---------------------|-------------------------------|-----|-----|

|               | given                     |                     | in one device                 |     |     |

| Ref. [26]     | No                        | No                  | No                            | No  | No  |

| Ref. [28]     | Yes                       | No                  | No                            | No  | No  |

| Ref. [33]     | Yes                       | No                  | No                            | No  | No  |

| Ref. [37]     | Yes                       | Yes                 | Yes                           | No  | No  |

| Proposed Work | Yes                       | Yes                 | Yes                           | Yes | Yes |

Table 3 Comparative Study with previous work

#### 7. CONCLUSIONS

In this communication, RSOA and ADM are utilized to design a frequency encoded dibit-based 3-bit parity generator. In this devised design, input dibit control units pass the error-free dibit logic that decreases the bit-error problems and enhances the operational speed. So, it promotes reliable and faithful operation. MATLAB software is used to simulate and verify the devised design. Furthermore, a comparative study with parity generators designed using different nonlinear materials has been conducted. This design is a single device for the even/odd parity generator units and it has no extra control terminal. As a result, the devised design reduces the space of the device as well as simultaneously generates even and odd parity. By introducing the dibit-based logic in this design, a high degree of parallelism can be expected. The frequency encoding and dibit-based systems also reduce the bit error problems and enhance the speed of operation in long-range transmission. In the future, we intend to develop a higher bit parity generator and checker. We also intend to use the proposed design in the full adder, cryptographic systems, and in the development of binary to gray code converter devices in the future.

## REFERENCES

- S. Bosu and B. Bhattacharjee, "A design of frequency encoded dibit-based half adder using reflective semiconductor optical amplifier with simulative verification", In Proceedings of the 4th International Conference on Devices for Integrated Circuit (DevIC 2021), IEEE, Kalyani, India, 19-20 May, 2021, pp. 175–179.

- [2] S. Kumar, K. Boone, J. Tuszyński, P. Barclay and C. Simon, "Possible existence of optical communication channels in the brain", *Sci. Rep.*, vol. 6, no. 1, pp. 1–13, Nov. 2016.

- [3] S. Mukhopadhyay, S. Dey and S. Saha. "Photonics: A Dream of Modern Technology" in *Photonics and Fiber Optics: Foundations and Applications*, p. 39, 2019.

- [4] S. Ma, A. Kotb, Z. Chen, and N. K. Dutta, "All optical logic gates based on two-photon absorption", in *Photonics North, International Society for Optics and Photonics*, vol. 7750, p. 77501L, 2010.

- [5] A. Kotb, "AND gate based on two-photon absorption in semiconductor optical amplifier", *Optoelectron.* Lett., vol. 9, no. 3, pp. 181–184, May 2013.

- [6] A. Chatterjee and S. Mukhopadhyay, "Use of optical Kerr medium for parametric generation of very low frequency electrical signal", J. Opt., vol. 48, no. 4, pp. 582–585, Nov. 2019.

- [7] K. Mukherjee and A. Raja, "Three Input NAND Gate Using Semiconductor Optical Amplifier", In Proceedings of the IEEE VLSI Device Circuit and System (VLSI DCS), 2020, pp. 142–145.

- [8] N. K. Dutta and Z. Xiang, *Optoelectronic devices*. World Scientific, 2018.

- [9] S. Bosu and B. Bhattacharjee, "All-optical frequency encoded dibit-based comparator using reflective semiconductor optical amplifier with simulative verification", In Proceedings of the 4th International IEEE Conference on Devices for Integrated Circuit (DevIC 2021), Kalyani, India, 2021, pp. 388–392.

#### S. BOSU, B. BHATTACHARJEE

- [10] S. Bosu and B. Bhattacharjee, "A novel design of frequency encoded multiplexer and demultiplexer systems using reflected semiconductor optical amplifier with simulative verification", J. Opt., vol. 50, no. 3, pp. 361–370, June 2021.

- [11] S. Saha and S Mukhopadhyay, "All optical frequency encoded quaternary memory unit using symmetric configuration of MZI-SOA", Opt. Laser Technol., vol. 131, p. 106386, Nov. 2020.

- [12] B. Ghosh, S. Hazra, N. Haldar, D. Roy, S. N. Patra, J. Swarnakar and S. Mukhopadhyay, "A novel approach to realize of all optical frequency encoded dibit based XOR and XNOR logic gates using optical switches with simulated verification", *Opt. Spectrosc.*, vol. 124, no. 3, pp. 337–342, March 2018.

- [13] K. Maji, K. Mukherjee and A. Raja, "An alternative method for implementation of frequency-encoded logic gates using a terahertz optical asymmetric demultiplexer (TOAD)", J. Comput. Electron. vol. 18, no. 4, pp. 1423–1434, Dec. 2019.

- [14] P. K. Nahata, A. Ahmed, S. Yadav, N. Nair and S. Kaur, "All optical Full-Adder and Full-Subtractor using Semiconductor Optical Amplifiers and All-Optical Logic Gates", In Proceedings of the 7th International Conference on Signal Processing and Integrated Networks (SPIN), 2020, pp. 1044–1049.

- [15] N. Nair, S. Kaur and H. Singh, "All-optical ripple carry adder based on SOA-MZI configuration at 100 Gb/s", Optik, vol. 231, p. 166325, Apr. 2021.

- [16] K. Mukherjee, K. Maji and M. K. Mandal, "Design and analysis of all-optical dual control dual SOA Tera Hertz asymmetric demultiplexer based half adder", *Opt. Quantum Electron.*, vol. 52, no. 9, pp. 1–15, Sept. 2020.

- [17] P. Shanmugapriya, M. Margarat and A. Jayaraj, "Design of All-Optical Half Adder and Half Subtractor based on SOA-MI", In *Journal of Physics: Conference Series*, 2021, vol. 1717, no. 1, p. 012005, IOP Publishing.

- [18] K. Komatsu, G. Hosoya and H. Yashima, "Ultrafast all-optical digital comparator using quantum-dot semiconductor optical amplifiers", *Opt. Quantum Electron.*, vol. 51, no. 2, p. 39, Jan. 2019.

- [19] A. Kotb, K. E. Zoiros and W. Li, "Execution of all-optical Boolean OR logic using carrier reservoir semiconductor optical amplifier-assisted delayed interferometer", *Opt. Laser Technol.*, vol. 142, p. 107230, Oct. 2021.

- [20] A. Kotb, K. E. Zoiros and W. Li, "Numerical study of carrier reservoir semiconductor optical amplifierbased all-optical XOR logic gate", J. Mod. Opt., vol. 68, no. 3, pp. 161–168, Feb. 2021.

- [21] A. Kotb, K. E. Zoiros and C. Guo, "2 Tb/s all-optical gates based on two-photon absorption in quantum dot semiconductor optical amplifiers", *Opt. Laser Technol.*, vol. 112, pp. 442–451, Apr. 2019.

[22] A. Kotb, K. E. Zoiros and C. Guo, "Performance investigation of 120 Gb/s all-optical logic XOR gate

- [22] A. Kotb, K. E. Zoiros and C. Guo, "Performance investigation of 120 Gb/s all-optical logic XOR gate using dual-reflective semiconductor optical amplifier-based scheme", J. Comput. Electron., vol. 17, no. 4, pp. 1640–1649, Sept. 2018.

- [23] A. Alquliah, A. Kotb, S. C. Singh and C. Guo, "All-optical AND, NOR, and XNOR logic gates using semiconductor optical amplifiers-based Mach-Zehnder interferometer followed by a delayed interferometer", *Optik*, vol. 225, p. 165901, Jan. 2021.

- [24] K. Mukherjee, "Design and analysis of all optical frequency encoded X-OR and X-NOR gate using quantum dot semiconductor optical amplifier-Mach Zehnder Interferometer", *Opt. Laser Technol.*, vol. 140, p. 107043, Aug. 2021.

- [25] A. Kotb, K. E. Zoiros, W. Li and C. Guo, "Theoretical investigation of 120 Gb/s all-optical AND, and OR logic gates using reflective semiconductor optical amplifiers", *Opt. Eng.*, vol. 60, no. 6, p. 066107, June 2021.

- [26] K. R. Chowdhury, D. De and S. Mukhopadhyay, "Parity checking and generating circuit with nonlinear material in all-optical domain", *Chin. Phy. Lett.*, vol. 22, no. 6, p. 1433, June 2005.

- [27] A. K. Ghosh, "Parity generator and parity checker in the modified trinary number system using savart plate and spatial light modulator", *Opt. Lett.*, vol. 6, no. 5, pp. 325–327, Sept. 2010.

- [28] E. Dimitriadou, K. E. Zoiros, T. Chattopadhyay and J. N. Roy, "Design of ultrafast all-optical 4-bit parity generator and checker using quantum-dot semiconductor optical amplifier-based Mach-Zehnder interferometer", J. Comput. Electron., vol. 12, no. 3, pp. 481–489, May 2013.

- [29] J. K. Rakshit, J. N. Roy and T. Chattopadhyay, "Design of micro-ring resonator based all-optical parity generator and checker circuit", Opt. Commun., vol. 303, pp. 30–37, Aug. 2013.

- [30] R. Mehra, S. Jaiswal and H. K. Dixit, "Parity checking and generating circuit with semiconductor optical amplifier in all-optical domain", *Optik*, vol. 124, no. 21, pp. 4744–4745, Nov. 2013.

- [31] A. Bhattacharyya, D. K. Gayen and T. Chattopadhyay, "All-optical parallel parity generator circuit with the help of semiconductor optical amplifier (SOA)-assisted Sagnac switches", *Opt. Commun.*, vol. 313, pp. 99–105, Feb. 2014.

- [32] A. Kumar and S. K. Raghuwanshi, "Implementation of optical gray code converter and even parity checker using the electro-optic effect in the Mach–Zehnder interferometer", *Opt. Quantum Electron.*, vol. 47, no. 7, pp. 2117–2140, July 2015.

- [33] F. Wang, Z. Gong, X. Hu, X. Yang, H. Yang and Q. Gong, "Nanoscale on-chip all-optical logic parity checker in integrated plasmonic circuits in optical communication range", *Sci. Rep.*, vol. 6, no. 1, pp. 1–8, Apr. 2016.

- [34] L. Singh, A. Bedi and S. Kumar, "Modeling of all-optical even and odd parity generator circuits using metal-insulator-metal plasmonic waveguides", *Photonic Sens.*, vol. 7, no. 2, pp. 182–192, June 2017.

- [35] S. Kaur and M. K. Shukla, "All-optical parity generator and checker circuit employing semiconductor optical amplifier-based Mach–Zehnder interferometers", *Optica Applicata*, vol. 47, no. 2, pp. 263–271, 2017.

- [36] N. Nair, S. Kaur and R. Goyal, "All optical integrated parity generator and checker using an SOA-based optical tree architecture", *Curr. Opt. Photonics*, vol. 2, no. 5, pp. 400–406, Oct. 2018.

- [37] K. Maji, K. Mukherjee, A. Raja and J. N. Roy, "Numerical simulations of an all-optical parity generator and checker utilizing a reflective semiconductor optical amplifier at 200 Gbps", J. Comput. Electron, vol. 19, no. 4, pp. 800–814, June 2020.

- [38] W. B. Kwon, C. G. Lee, D. Seo and C. S. Park, "Tunable Photonic Microwave Band-pass Filter with High-resolution Using XGM Effect of an RSOA", *Curr. Opt. Photon*, vol. 2, pp. 563-567, Dec. 2018.

- [39] A. Kotb and C. Guo, "Reflective semiconductor optical amplifiers-based all-optical NOR and XNOR logic gates at 120 Gb/s", J. Mod. Opt., vol. 67, no. 18, pp. 1424–1435, Dec. 2020.

- [40] A. Kotb and C. Guo, "120 Gb/s all-optical NAND logic gate using reflective semiconductor optical amplifiers", J. Mod. Opt., vol. 67, no. 12, pp. 1138–1144, Aug. 2020.

- [41] P. P. Sarkar, B. Satpati and S. Mukhopadhyay, "New simulative studies on performance of semiconductor optical amplifier based optical switches like frequency converter and add-drop multiplexer for optical data processors", J. Opt., vol. 42, no. 4, pp. 360–366, Dec. 2013.

- [42] B. Ghosh, S. Hazra and P. P. Sarkar, "Simulative study of all-optical frequency encoded dibit-based controlled multiplexer and de-multiplexer using optical switches", J. Opt., vol. 48, no. 3, pp. 365–374, Sept. 2019.

- [43] P. P. Sarkar, B. Ghosh and S. N. Patra, "Simulative study of all optical frequency encoded dibit based universal NAND and NOR logic gates using a reflective semiconductor optical amplifier and an add/drop multiplexer", J. Opt. Technol., vol. 83, no. 4, pp. 257–262, Apr. 2016.

- [44] S. Mukhopadhyay, "Binary optical data subtraction by using a ternary dibit representation technique in optical arithmetic problems", *Appl. Opt.*, vol. 31, no. 23, pp. 4622–4623, Aug. 1992.