# **Extended-Range Second-Order Incremental Sigma-Delta ADC**

Department of Electrical, Computer and Biomedical Engineering University of Pavia

UNIVERSITA' DI PAVIA

## **Extended-Range Second-Order Incremental Sigma-Delta ADC**

Dissertation submitted in partial fulfillment

of the requirements for the degree of

### **Doctor of Philosophy**

in

**Microelectronics**

by Abhijeet Taralkar

based on research carried out

under the supervision of

Prof. Piero Malcovati

and

Prof. Andrea Baschirotto

UNIVERSITA' DI PAVIA

April, 2021

Department of Electrical, Computer and Biomedical Engineering University of Pavia

То

My Beloved Family...

## Acknowledgment

First and foremost, I express my deep appreciation and gratitude to my advisor *Prof. Piero Malcovati* for his active support and crucial guidance throughout the duration of three years of the PhD. It's his guidance that provided me the perspective, intuitive skills along with analytical capabilities that helped me to improve my technical understanding. His constructive approach and passion towards his job are very inspirational to us. His positive words and encouragement always cheered me up, to gain the productivity and proactiveness.

I also like to extend my gratitude to acknowledge my co-advisor *Prof. Andrea Baschirotto* for his association and active collaboration. The challenging tasks assigned by him benefited me to enhance and outreach my potential. His supervision and suggestions always helped me to set and organise the agenda, follow it systematically and accomplish the tasks within specified time.

Further, I would like to thank Infinoen Technologies Austria, AG. for providing me the resources and the opportunity to tape-out my designs. During the PhD while I spent 14 months in the Infineon, *Francesco Conzatti* was always there to help me out, be it with tools or the technical challenges, so I also thank him for his great contribution.

A significant contribution from the colleagues in our IMS lab must be acknowledged as well. It is them who made the lab environment so friendly and pleasant that the tasks felt more like fun activity. In the beginning of the project, I got help from *Marco Grassi* with his expert suggestions. My stay in Pavia happened to be comfortable because of *Arun* who was all the time ready for help in any emergency. Productive discussions and review from *Arun* helped to maintain the quality of work. *Karan, Satya, Roberto di Lorenzo, Thomas, Alper* were there to have conversations with full of amusement.

Finally, I would like to thank my beloved parents, who fostered me teaching the value of education, for their unconditional love and support towards me, for encouraging me on every crucial step of my life and believing in me. Thanks to my gorgeous sister *Tejaswini* who gives me a feeling of myself being her pride, for her immense support.

Abhijeet Taralkar University of Pavia April 2021

## Abstract

A single-stage two-steps Extended-Range Second-Order Incremental ADC in  $0.13\mu m$  CMOS technology is presented here which achieves a Signal-to-Noise and Distortion Ratio (SNDR) as large as 73 dB. The proposed architecture of Extended-Range ADC based on Second-order multi-bit CIFF Incremental ADC reuses the IADC structure for coarse (input signal) as well as fine (residue) quantization without need of employment of explicit second ADC thereby minimizing power consumption and area occupancy. With a clock frequency of 80 MHz, the complete ERADC achieves in extracted simulation a peak SNDR of 73 dB at a data rate of 3.2 MS/s (25 clock cycles per conversion).

*Keywords: Oversampling; Sigma-Delta ADC; Incremental ADC; Extended-Range ADC; Noise Shaping; Decimation Filter.*

## Contents

|    |          |               |                                               | iii |

|----|----------|---------------|-----------------------------------------------|-----|

| A  | cknov    | vledgmo       | ent                                           | v   |

| A  | bstrac   | et            |                                               | vii |

| Li | ist of ] | Figures       |                                               | xi  |

| Li | ist of [ | <b>Fables</b> |                                               | XV  |

| 1  | Intr     | oductio       | n                                             | 1   |

| 2  | Pro      | posed A       | rchitectures                                  | 3   |

|    | 2.1      | Introd        | uction                                        | 3   |

|    | 2.2      | Incren        | nental A/D Converter:                         | 4   |

|    |          | 2.2.1         | Second-Order CIFB IADC Architecture:          | 4   |

|    |          | 2.2.2         | Second-Order CIFF IADC Architecture:          | 5   |

|    |          | 2.2.3         | Modified Second-Order CIFF IADC Architecture: | 5   |

|    | 2.3      | Extend        | ded-Range Incremental ADC                     | 8   |

|    |          | 2.3.1         | Proposed Architecture - I                     | 8   |

|    |          | 2.3.2         | Proposed Architecture - II                    | 16  |

| 3  | Sim      | ulink N       | Iodeling & System Verification                | 25  |

|    | 3.1      | Introd        | uction                                        | 25  |

|    | 3.2      | Block         | Description:                                  | 26  |

|    |          | 3.2.1         | Integrator Block:                             | 26  |

|    |          | 3.2.2         | Quantizer:                                    | 27  |

|    |          | 3.2.3         | Decimation Filter:                            | 27  |

|    | 3.3      | Analy         | sis of Op-Amp Requirements                    | 28  |

|    |          | 3.3.1         | Effect of Low-Frequency Gain                  | 28  |

|    |          | 3.3.2         | Effect of Finite GBW of the Op-Amps           | 37  |

|    |          | 3.3.3         | Performance Comparison                        | 41  |

| 4 | Circuit Design |                        |                                   | 43 |

|---|----------------|------------------------|-----------------------------------|----|

|   | 4.1            | Introd                 | uction                            | 43 |

|   | 4.2            | Integra                | ators                             | 44 |

|   |                | 4.2.1                  | Op-Amp for the First Integrator:  | 44 |

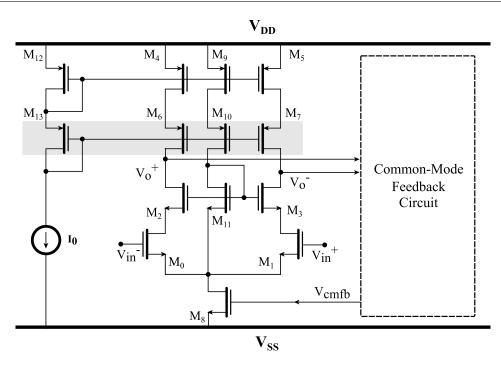

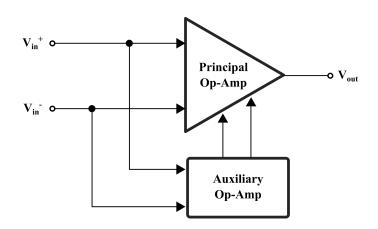

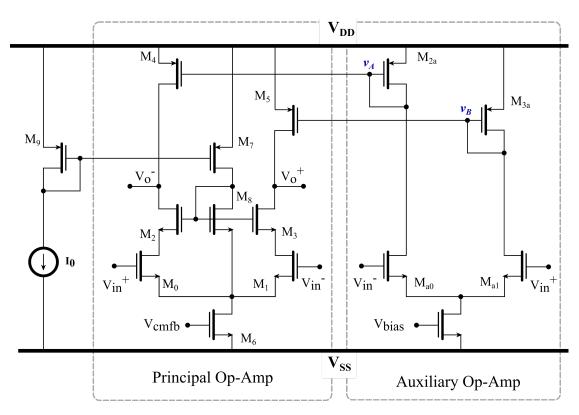

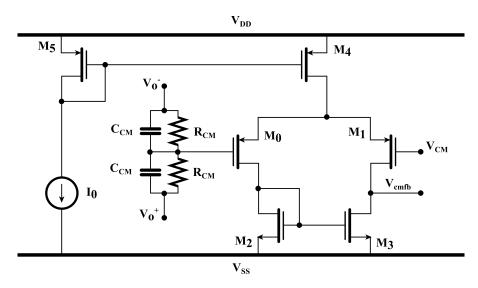

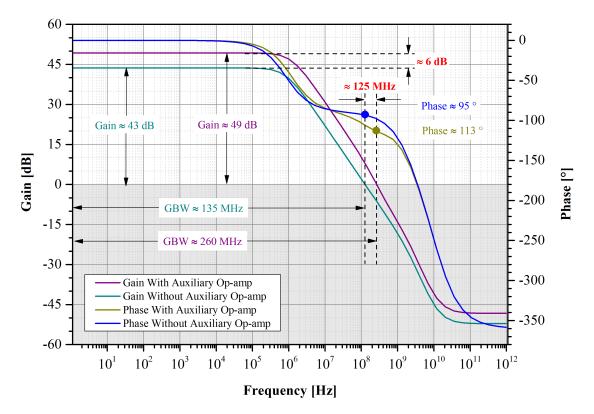

|   |                | 4.2.2                  | Gain and GBW Enhancement:         | 46 |

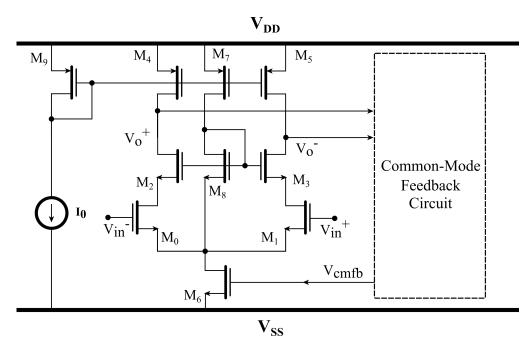

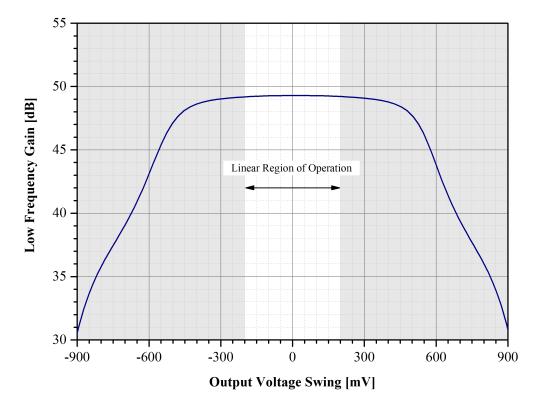

|   |                | 4.2.3                  | Op-Amp for the Second Integrator: | 50 |

|   | 4.3            | Quant                  | izer                              | 52 |

|   |                | 4.3.1                  | Threshold Generator               | 53 |

|   |                | 4.3.2                  | Comparator                        | 56 |

|   | 4.4            | DAC                    | Architecture                      | 59 |

|   | 4.5            | Inter-S                | Stage Gain Block                  | 59 |

|   | 4.6            | 4.6 Supporting Blocks  |                                   | 62 |

|   |                | 4.6.1                  | Biasing                           | 62 |

|   |                | 4.6.2                  | Dynamic Element Matching (DEM)    | 64 |

|   |                | 4.6.3                  | Timing Block                      | 65 |

|   |                | 4.6.4                  | Thermometer to Binary Conversion  | 66 |

| 5 | Sim            | ulation                | and Measurement Results           | 69 |

|   | 5.1            | Introd                 | uction                            | 69 |

|   | 5.2            | 2 Simulation Results   |                                   | 70 |

|   | 5.3            | 3 Measurements Results |                                   |    |

|   |                | 5.3.1                  | Sigma-Delta Mode:                 | 72 |

|   |                | 5.3.2                  | Incremental Mode:                 | 75 |

| 6 | Con            | clusion                |                                   | 79 |

# **List of Figures**

| 2.1  | ADC modeled as an additive noise source                                | 4  |

|------|------------------------------------------------------------------------|----|

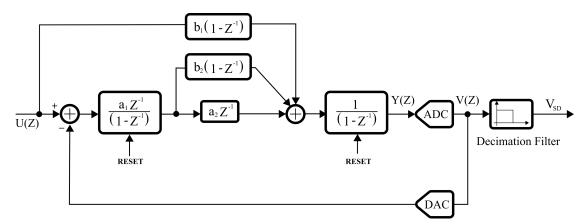

| 2.2  | Second Order Incremental Feedback Sigma-Delta Modulator Architecture   | 4  |

| 2.3  | Second Order Incremental Feed-forward Architecture of Sigma-Delta      |    |

|      | Modulator                                                              | 5  |

| 2.4  | Second Order Incremental Modified Feed-forward Architecture of         |    |

|      | Sigma-Delta Modulator                                                  | 6  |

| 2.5  | Circuit Diagram of Second Order Incremental Modified Feed-forward      |    |

|      | Architecture of Sigma-Delta Modulator                                  | 7  |

| 2.6  | Block diagram of an ERADC based on a conventional second-order         |    |

|      | CIFF IADC topology                                                     | 8  |

| 2.7  | Block diagram of an ERADC based on a modified second-order CIFF        |    |

|      | IADC topology                                                          | 9  |

| 2.8  | Block diagram of the proposed ERADC based on a modified                |    |

|      | second-order CIFF IADC topology                                        | 10 |

| 2.9  | Operation of the proposed ERADC during the coarse conversion phase .   | 11 |

| 2.10 | Operation of the proposed ERADC during the fine conversion phase       | 12 |

| 2.11 | Operation of the proposed ERADC during the recombination phase         | 13 |

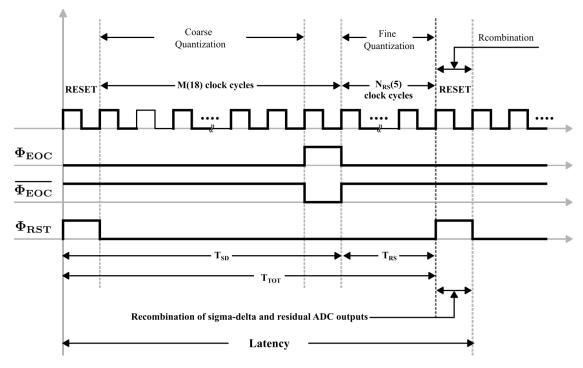

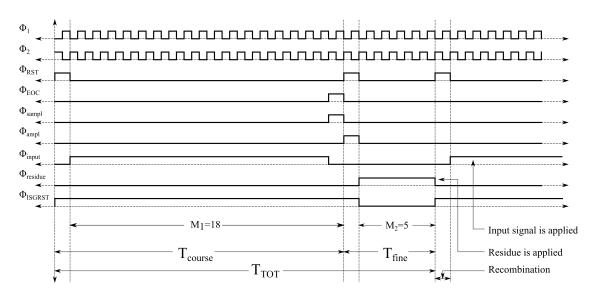

| 2.12 | Conversion timing in an extended-range IADC                            | 13 |

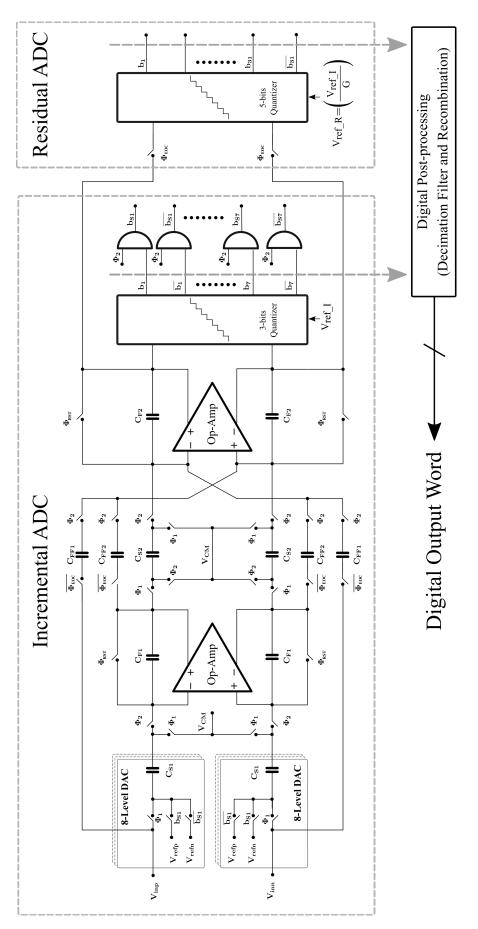

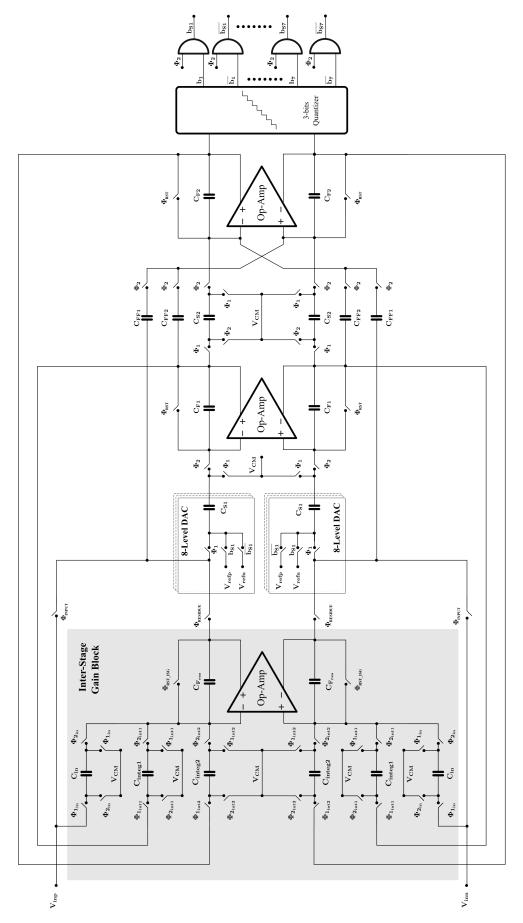

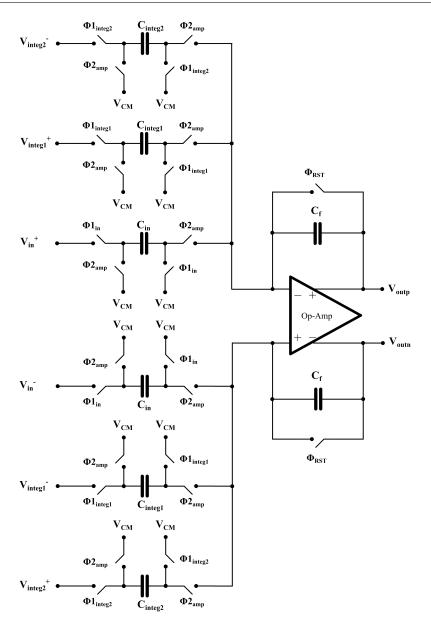

| 2.13 | Circuit diagram of a proposed Extended-Range second-order CIFF IADC    | 15 |

| 2.14 | Block diagram of the proposed architecture of an extended-range IADC   | 16 |

| 2.15 | Proposed architecture of an extended-range IADC configuration in       |    |

|      | Coarse quantization phase                                              | 17 |

| 2.16 | Proposed architecture of an extended-range IADC configuration in Fine  |    |

|      | quantization phase                                                     | 19 |

| 2.17 | Proposed architecture of an extended-range IADC configuration in       |    |

|      | Recombination phase                                                    | 20 |

| 2.18 | SQNR Vs $M_2$                                                          | 21 |

| 2.19 | Timing Diagram with all the Phases                                     | 22 |

| 2.20 | Circuit diagram of the proposed architecture of an extended-range IADC | 24 |

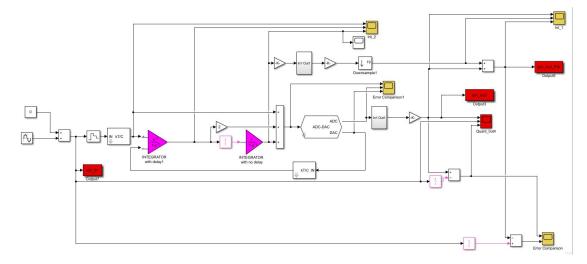

| 3.1 Simulink Model of Second Order Incremental Feed-forward                             |       |

|-----------------------------------------------------------------------------------------|-------|

| Architecture of Sigma-Delta Modulator                                                   | 26    |

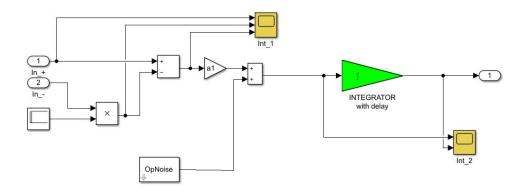

| 3.2 Simulink Model of the Integrators employed in the I $\Sigma\Delta M$ architecture . | 27    |

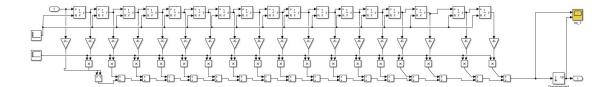

| 3.3 Simulink Model of the Decimation Filter                                             | 27    |

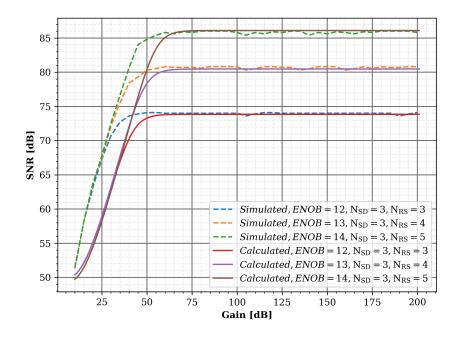

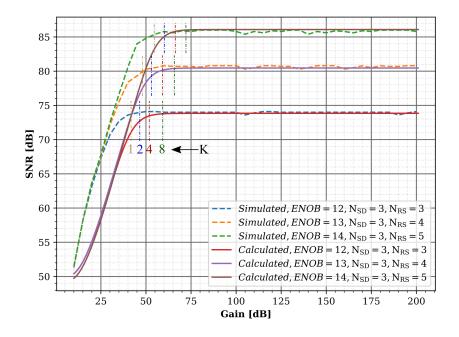

| 3.4 Simulated and Calculated SNR as a function of Low-frequency gain                    | 33    |

| 3.5 Simulated and Calculated SNR as a function of Low-frequency gain                    | 35    |

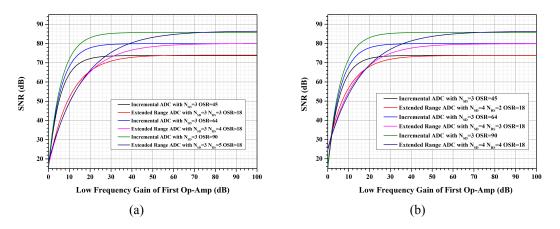

| 3.6 Comparison of the IADC and extended-range IADC with different                       |       |

| values of the first-integrator op-amp gain                                              | 36    |

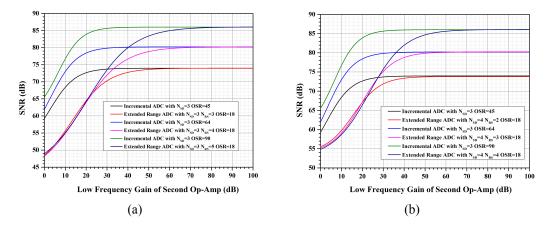

| 3.7 Comparison of the IADC and extended-range IADC with different                       |       |

| values of the second-integrator op-amp gain                                             | 36    |

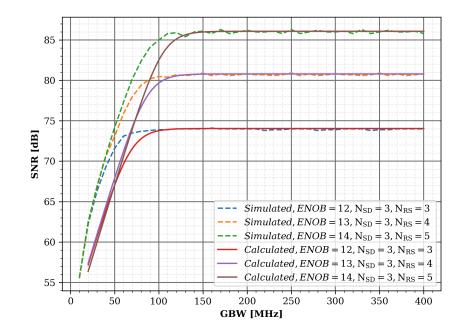

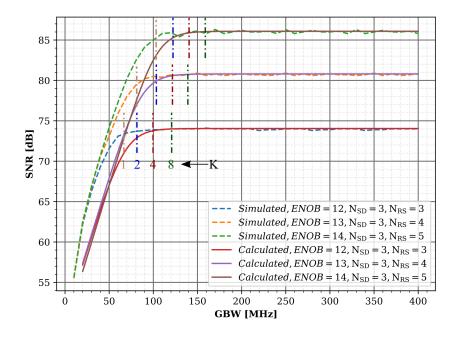

| 3.8 Comparison between the simulated and modeled SNR equation w.r.t. GBV                | W 38  |

| 3.9 Comparison between the simulated and modeled SNR equation w.r.t. GBV                | W 39  |

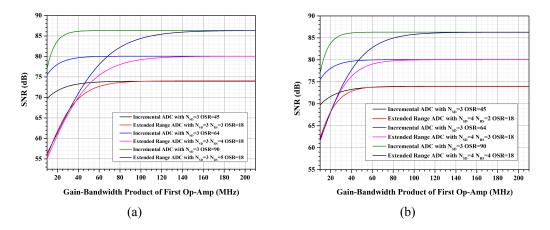

| 3.10 Comparison of the IADC and extended-range IADC with different                      |       |

| values of the first-integrator op-amp GBW                                               | 40    |

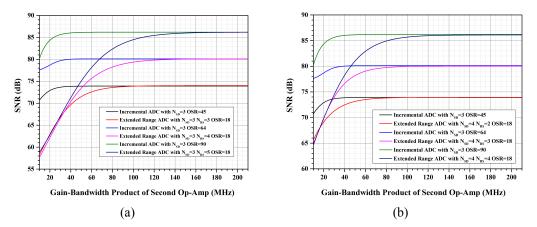

| 3.11 Comparison of the IADC and extended-range IADC with different                      |       |

| values of the second-integrator op-amp GBW                                              | 41    |

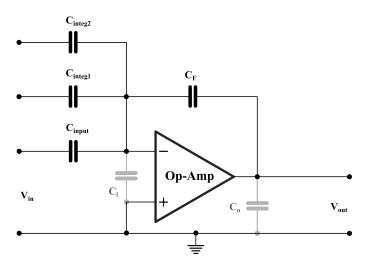

| 4.1 Single Ended representation of the First Integrator in the integrating phase        | se 44 |

| 4.2 Conventional Telescopic Amplifier Circuit Diagram                                   | 45    |

| 4.3 Modified Telescopic Amplifier for improved output swing                             | 46    |

| 4.4 Block Diagram of Gain and GBW Enhancement                                           | 47    |

| 4.5 Gain enhanced Telescopic Amplifier for improved output swing with                   |       |

| GBW boost(Common-Mode Feedback circuit not shown)                                       | 47    |

| 4.6 Conventional continuous time Common-Mode Feedback Circuit                           | 49    |

| 4.7 Frequency Response comparison between the modified Telescopic                       |       |

| amplifier architectures with and without the Auxiliary op-amp for the                   |       |

| first integrator                                                                        | 50    |

| 4.8 Output swing of the Op-amp Vs low frequency gain                                    | 51    |

| 4.9 Single Ended representation of the second Integrator in the integrating             |       |

| phase                                                                                   |       |

| 4.10 Resistive Ladder generating differential threshold voltages for comparator         | rs 53 |

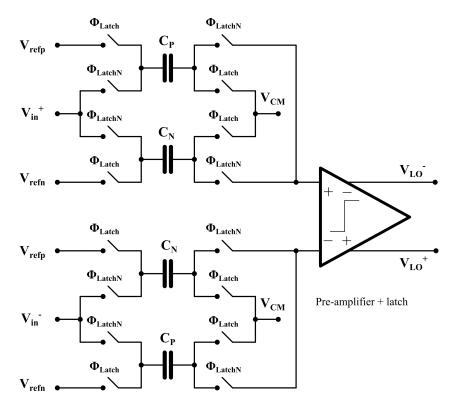

| 4.11 (a)Switched capacitor arrangement to generate threshold and taking                 |       |

| difference with input sample (b)Threshold generator in a phase sampling                 |       |

| reference voltage (c)Threshold generator in a phase sampling signal voltage             |       |

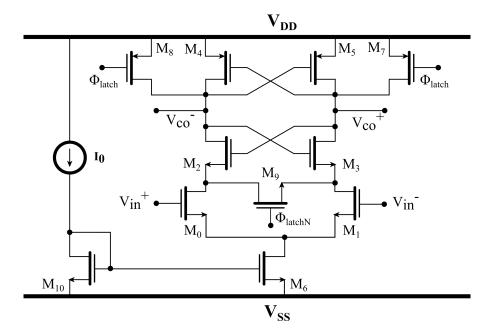

| 4.12 Schematic of the Comparator employed in the Quantizer                              |       |

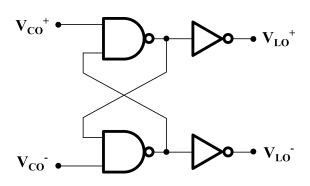

| 4.13 Latch Comprised of NAND gates and digital buffers                                  |       |

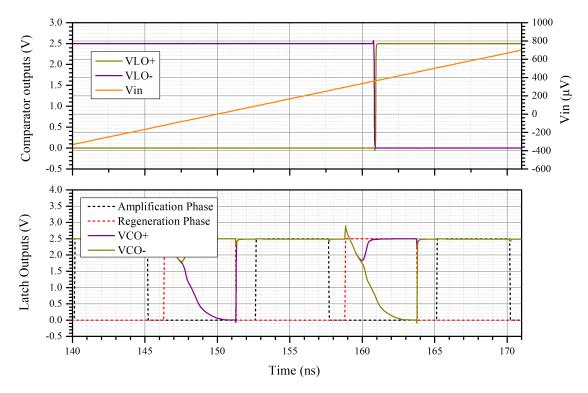

| 4.14 Signals at the different nodes of the Comparator                                   |       |

| 4.15 A complete structure of Comparator                                                 |       |

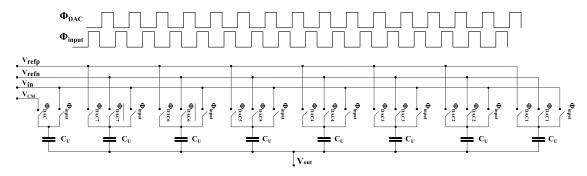

| 4.16 A 3-bit Thermometric Capacitive DAC at the input of First integrator .             | 59    |

| 4.17                                                                                                                             | Inter-Stage Gain Block Diagram                                                                                                                                                                                                                                                                                                                                                         | 60                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 4.18                                                                                                                             | Single ended representation of the Inter-stage Gain Block in the                                                                                                                                                                                                                                                                                                                       |                                                                                                            |

|                                                                                                                                  | amplification phase                                                                                                                                                                                                                                                                                                                                                                    | 61                                                                                                         |

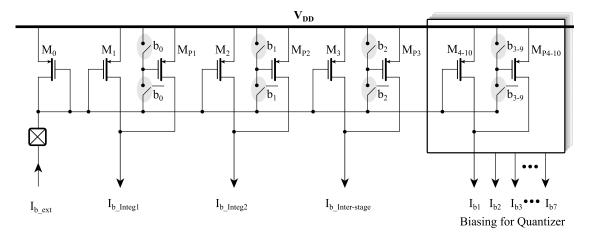

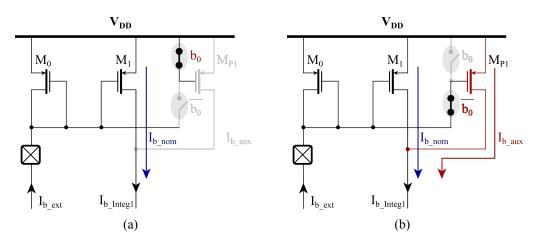

| 4.19                                                                                                                             | Programmable Biasing Block Diagram                                                                                                                                                                                                                                                                                                                                                     | 62                                                                                                         |

| 4.20                                                                                                                             | (a) Typical bias current: programming bit disables additional current (b)                                                                                                                                                                                                                                                                                                              |                                                                                                            |

|                                                                                                                                  | Higher bias Current: programming bit enables additional current                                                                                                                                                                                                                                                                                                                        | 63                                                                                                         |

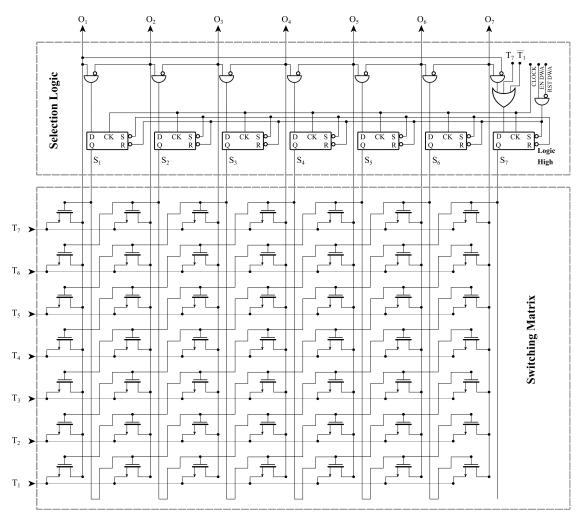

| 4.21                                                                                                                             | Data Weighted Averaging (DWA) implementation approach                                                                                                                                                                                                                                                                                                                                  | 63                                                                                                         |

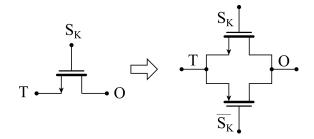

| 4.22                                                                                                                             | Transmission Gate                                                                                                                                                                                                                                                                                                                                                                      | 64                                                                                                         |

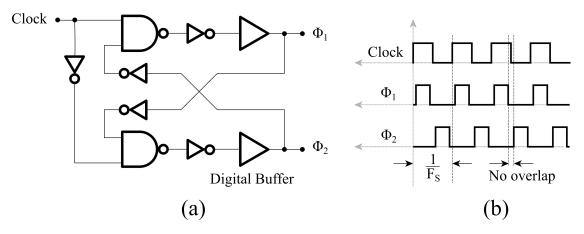

| 4.23                                                                                                                             | Schematic for generation of non-overlapping clock phases                                                                                                                                                                                                                                                                                                                               | 65                                                                                                         |

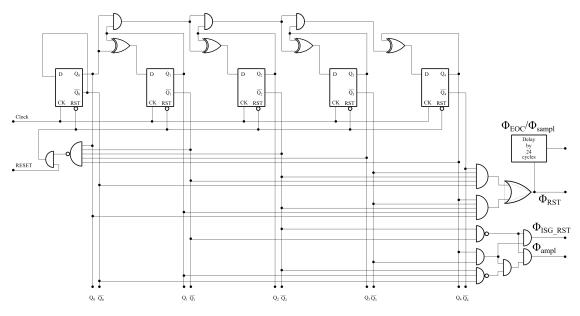

| 4.24                                                                                                                             | Schematic for generation of the different control signals for IADC and                                                                                                                                                                                                                                                                                                                 |                                                                                                            |

|                                                                                                                                  | ISG                                                                                                                                                                                                                                                                                                                                                                                    | 65                                                                                                         |

| 4.25                                                                                                                             | Timing diagram of the different control signals for IADC and ISG                                                                                                                                                                                                                                                                                                                       | 66                                                                                                         |

| 4.26                                                                                                                             | Thermometer to Binary Encoder                                                                                                                                                                                                                                                                                                                                                          | 66                                                                                                         |

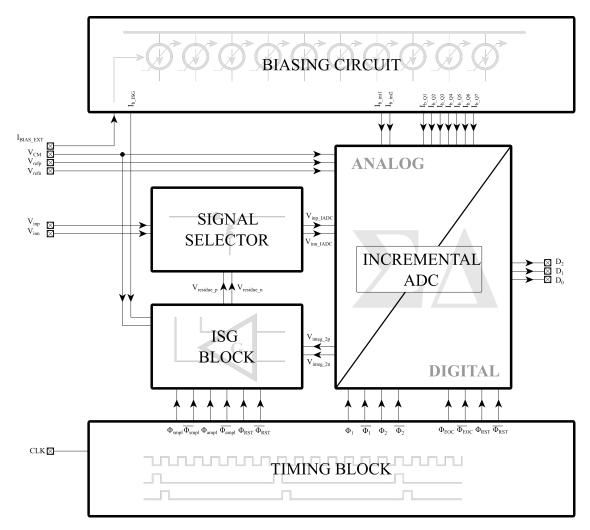

| 4.27                                                                                                                             | Block Diagram of full architecture of ERADC with core and the                                                                                                                                                                                                                                                                                                                          |                                                                                                            |

|                                                                                                                                  | supporting blocks                                                                                                                                                                                                                                                                                                                                                                      | 67                                                                                                         |

|                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                            |

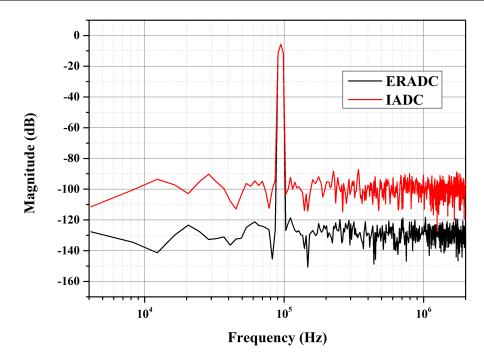

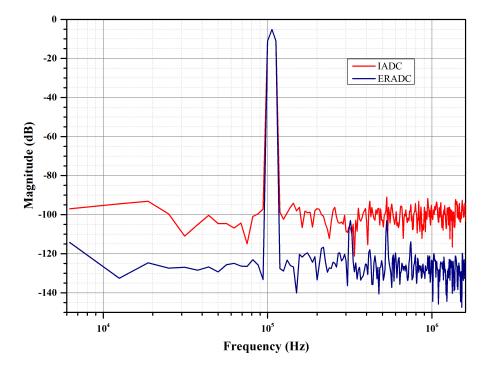

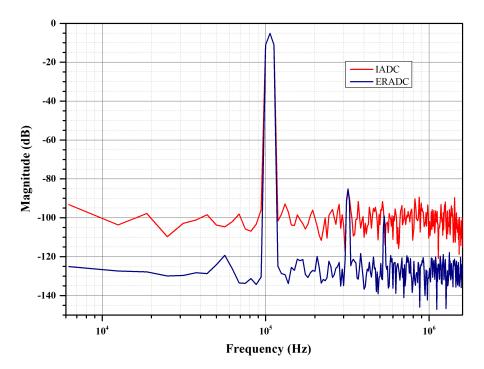

| 5.1                                                                                                                              | Power Spectral Density of the output of Incremental ADC and Extended                                                                                                                                                                                                                                                                                                                   |                                                                                                            |

| 5.1                                                                                                                              | Power Spectral Density of the output of Incremental ADC and Extended<br>Range ADC with all the blocks ideal                                                                                                                                                                                                                                                                            | 70                                                                                                         |

| 5.1<br>5.2                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                        | 70                                                                                                         |

|                                                                                                                                  | Range ADC with all the blocks ideal                                                                                                                                                                                                                                                                                                                                                    | 70<br>71                                                                                                   |

|                                                                                                                                  | Range ADC with all the blocks ideal          Power Spectral Density of the output of Incremental SDM and Extended                                                                                                                                                                                                                                                                      |                                                                                                            |

| 5.2                                                                                                                              | Range ADC with all the blocks idealPower Spectral Density of the output of Incremental SDM and ExtendedRange ISDM at Transistor Level                                                                                                                                                                                                                                                  | 71                                                                                                         |

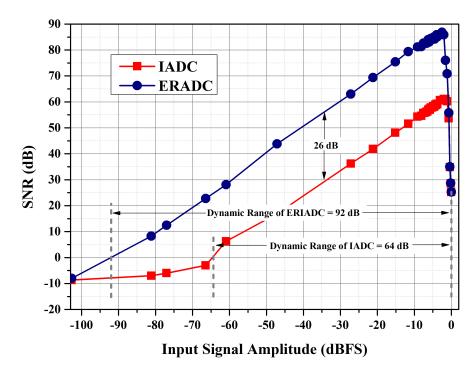

| 5.2<br>5.3                                                                                                                       | Range ADC with all the blocks idealPower Spectral Density of the output of Incremental SDM and ExtendedRange ISDM at Transistor LevelPost-Layout simulation Power Spectral Density of the Incremental SDM                                                                                                                                                                              | 71                                                                                                         |

| 5.2<br>5.3                                                                                                                       | Range ADC with all the blocks idealPower Spectral Density of the output of Incremental SDM and ExtendedRange ISDM at Transistor LevelPost-Layout simulation Power Spectral Density of the Incremental SDMSignal-to-Noise Ratio Vs input signal amplitude of ERADC with all the                                                                                                         | 71<br>71                                                                                                   |

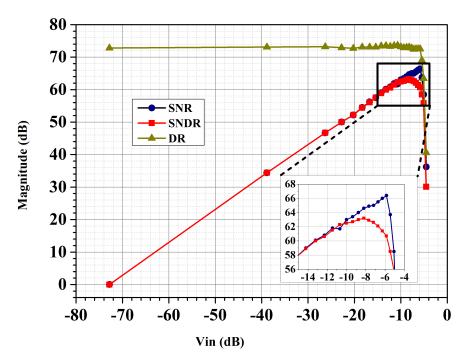

| 5.2<br>5.3<br>5.4                                                                                                                | Range ADC with all the blocks idealPower Spectral Density of the output of Incremental SDM and ExtendedRange ISDM at Transistor LevelPost-Layout simulation Power Spectral Density of the Incremental SDMSignal-to-Noise Ratio Vs input signal amplitude of ERADC with all theblocks at transistor level design                                                                        | 71<br>71<br>72                                                                                             |

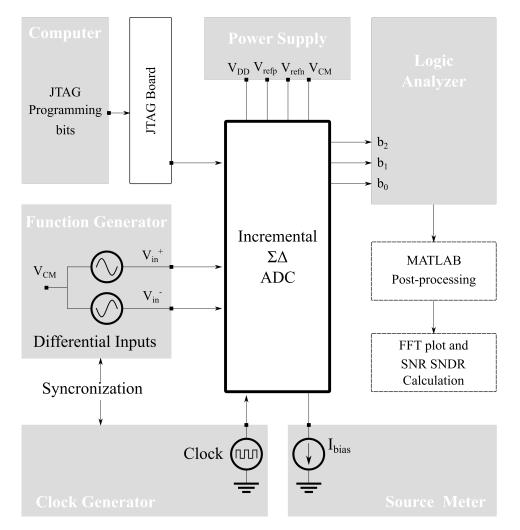

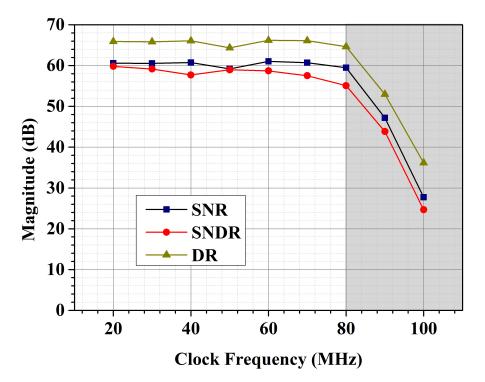

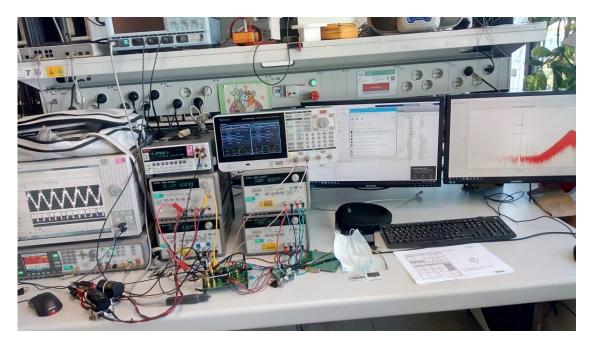

| <ul><li>5.2</li><li>5.3</li><li>5.4</li><li>5.5</li></ul>                                                                        | Range ADC with all the blocks idealPower Spectral Density of the output of Incremental SDM and ExtendedRange ISDM at Transistor LevelPost-Layout simulation Power Spectral Density of the Incremental SDMSignal-to-Noise Ratio Vs input signal amplitude of ERADC with all theblocks at transistor level designMeasurement Set-up for the characterization of the Incremental (ΣΔ) ADC | 71<br>71<br>72<br>73                                                                                       |

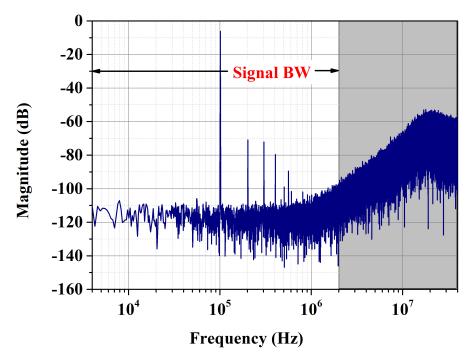

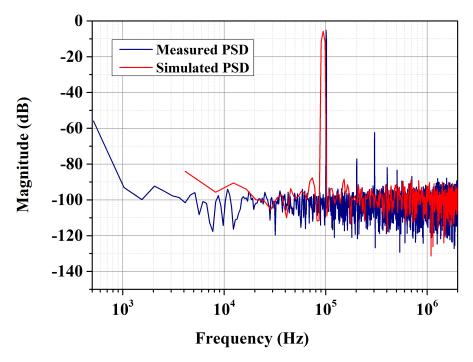

| <ul> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> </ul>                                                      | Range ADC with all the blocks ideal Power Spectral Density of the output of Incremental SDM and Extended<br>Range ISDM at Transistor Level Post-Layout simulation Power Spectral Density of the Incremental SDM<br>Signal-to-Noise Ratio Vs input signal amplitude of ERADC with all the<br>blocks at transistor level design                                                          | 71<br>71<br>72<br>73<br>74                                                                                 |

| <ul> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>5.7</li> </ul>                                         | Range ADC with all the blocks ideal                                                                                                                                                                                                                                                                                                                                                    | 71<br>71<br>72<br>73<br>74<br>74                                                                           |

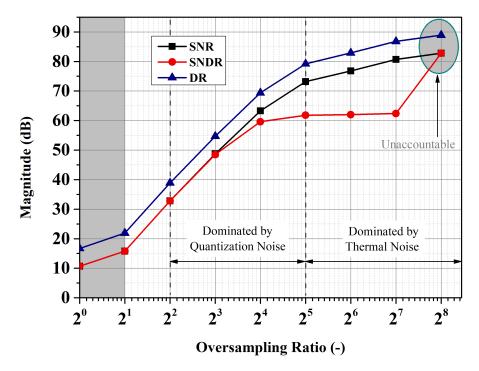

| <ul> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>5.7</li> <li>5.8</li> </ul>                            | Range ADC with all the blocks ideal Power Spectral Density of the output of Incremental SDM and Extended<br>Range ISDM at Transistor Level                                                                                                                                                                                                                                             | <ul> <li>71</li> <li>71</li> <li>72</li> <li>73</li> <li>74</li> <li>74</li> <li>75</li> </ul>             |

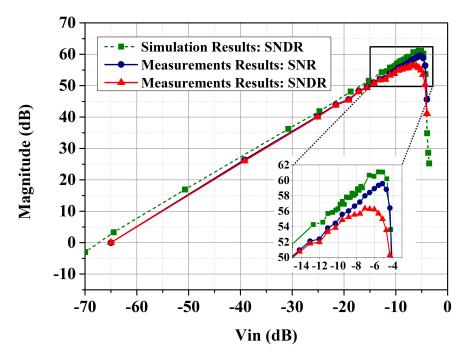

| <ul> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>5.7</li> <li>5.8</li> <li>5.9</li> <li>5.10</li> </ul> | Range ADC with all the blocks ideal Power Spectral Density of the output of Incremental SDM and Extended Range ISDM at Transistor Level Post-Layout simulation Power Spectral Density of the Incremental SDM Signal-to-Noise Ratio Vs input signal amplitude of ERADC with all the blocks at transistor level design                                                                   | <ul> <li>71</li> <li>71</li> <li>72</li> <li>73</li> <li>74</li> <li>74</li> <li>75</li> <li>76</li> </ul> |

# **List of Tables**

| 3.1 | Parameters of the considered extended-range IADC                               | 28 |

|-----|--------------------------------------------------------------------------------|----|

| 3.2 | Comparison between the Simulated and Calculated SNR (in dB) for                |    |

|     | different values of $K$ as a function of Low-frequency gain in (dB)            | 35 |

| 3.3 | Comparison between the Simulated SNR and the SNR on the modeled                |    |

|     | characteristic (in dB) for different values of $K$ as a function of calculated |    |

|     | Finite GBW (in MHz)                                                            | 40 |

| 3.4 | Comparison of the op-amp requirements for standalone IADC and                  |    |

|     | extended-range IADC                                                            | 41 |

| 4.1 | Op-Amp specification requirements                                              | 43 |

| 4.2 | Transistor sizes in the Op-amps in the first and second integrator             | 51 |

| 4.3 | The threshold voltages generated for 3-bit quantizer                           | 55 |

| 4.4 | Modified threshold voltages, generated for 3-bit quantizer                     |    |

|     | accommodating the signal to full scale.                                        | 56 |

| 4.5 | The Output codes of the DEM based on the selection logic                       | 64 |

| 5.1 | Performance summary of the proposed ADC and comparison with the                |    |

|     | state-of-the-art                                                               | 77 |

### **Chapter 1**

## Introduction

As the technology is advancing in the automotive field, the traditionally used mechanical motors are being replaced by the electrical motors to enable the automotive architectures that supports energy efficiency. To meet these requirements, the robust, flexible and intelligent motor driver ICs are needed, so that the size and performance of the product can be optimized. In order to serve such an application, a low power, low area, general purpose 12-bit ADC is necessary.

The obligatory requirements for such an automotive applications for the ADC encompasses a high absolute accuracy, superior linearity, very low offset and noise with low power consumption. These requisites of the automotive are well-suited to the properties of the Sigma-Delta ( $\Sigma\Delta$ ) Modulator [1–11]. The Sigma-Delta Modulators find many applications in various fields from consumer electronics to military applications. However, exercise of the  $\Sigma \Delta M$  becomes impractical when multiple input sources has to be evaluated, since they retain the quantization noise memory from the previous conversions. This way, this class of ADC actually act upon the complete input signal waveform and not the individual samples. In other words, there is no one-to-one correspondence between present input sample and the digital output equivalent sample but the complete input signal and the complete digital output signal. With standard IC technologies, the performance in terms of SNDR that can be attained by employing these architectures is around 120 dB or ENOB of around 20. The implementation of  $\Sigma\Delta Ms$  can be done with either continuous-time technique or discrete-time technique.

The Incremental (IADC) ADCs [12–18] overcomes the limitations of the  $\Sigma\Delta Ms$ . With multi-sensor platform, where the analog to digital conversion of more than one signal is desired, the exercise of the Incremental ADC is practical. In this class of ADC, all the analog and digital memory blocks are reset at the beginning of the conversion cycle thereby erasing the quantization noise memory from the previous samples' conversions. Then the next input sample is applied to IADC and the structure is iterated for Mnumber of clock cycle. During this period, the memory blocks in the architecture do retain the noise memory, however, which is from the same sample. At the end of the conversion cycle, it delivers the digital equivalent of the input sample and next cycle starts again resetting the memory blocks. This way, IADCs have advantage of noise shaping property of  $\Sigma \Delta Ms$  within the conversion cycle as well as advantage of one-to-one correspondence of the input sample and output digital equivalent property of the Nyquist ADCs. Therefore, employment of IADC for multi-sensor platform ensures the respective conversion of the input samples without contamination from each other. Nevertheless, in order to achieve high performance in terms of Signal-to-Noise Ratio (SNR) or Dynamic Range (DR), this category of the converts requires high OSR or long conversion time. In other words, the employment of the IADC for the applications with short conversion time or for the signals with large bandwidth is not suitable.

The shortcomings of IADCs can be overcome by exploiting the extended-range techniques which allows the resolution to be increased still maintaining the conversion time relatively short. The Extended Range ADCs (ERADCs) [19–29] are basically two stage ADCs where IADC conventionally serves as a first stage also known as principal ADC. The basic idea behind the extended range technique is to further digitize the residue generated from the first stage, i.e. IADC, through the second stage or supplemental ADC. Since the supplemental ADC is used to process and convert the residue, it is usually referred as Residual ADC (RADC) as well. Based on the different parameters such as power consumption, resolution in IADC, resolution required in RADC, the architecture of the residual ADC is chosen, which can be flash, SAR, pipelined, sigma-delta or even another IADC. Ultimately the two outputs from first stage and the second stage are recombined with proper coefficients which brings the digital output closer to the input signal than output of standalone IADC, thereby improving the performance.

### **Chapter 2**

### **Proposed Architectures**

### 2.1 Introduction

Sigma-delta modulators ( $\Sigma\Delta M$ ) are the data converters used in most low-signal-bandwidth applications, in many different fields, from consumer electronics to military applications. This kind of A/D converters (ADCs) inherently retains a memory of the quantization noise from previous samples and uses it to push it outside the signal bandwidth, implementing noise shaping, thereby improving the resolution. Along with noise shaping, oversampling is another parameter that plays important role in improving the dynamic range of  $\Sigma\Delta M$  ADCs. However, because of the inherent memory effect, these converters are only suitable for applications with single input source. Therefore, in applications in which the same ADC has to be used for multiple different input sources, this class of converters becomes impractical.

Incremental ADCs (IADCs) are the appropriate solution to overcome this drawback of  $\Sigma\Delta Ms$ . Since they are reset at the beginning of each conversion cycle, all the memory effects from previous conversions are cleared. Therefore, an IADC operates sporadically, unlike a  $\Sigma\Delta M$ , delivering the digital output with one-to-one correspondence with the input samples, thereby implying the suitability of IADCs for applications with multiple input sources. Further improvement of dynamic range in IADCs is possible at the expense of higher number of clock cycles per conversion limiting their use in applications with small signal bandwidth.

Extended-Range Incremental ADCs (ERADCs) are a promising alternative to

address high-dynamic range applications while maintaining the conversion time short. An ERADC is basically a two-stage ADC, with an IADC as first stage, a Residue ADC (RADC) as second stage and the required recombination logic [19].

### 2.2 Incremental A/D Converter:

Some of the crucial key features of the IADC are precise high-resolution even with the poor accuracy in the unit elements, relatively short conversion time, small bandwidth requirement and most importantly, no memory effect, since the architecture is reset after conversion of the every individual sample. This leads to the one-to-one correspondence between the input sample and the output code of the modulator.

Diverse requirements, demanded to develop the different architectures of the IADC and a particular structure need to be chosen to fulfill the given requirements. Therefore, there exists several structures of IADC, out of which some are; feedback architecture, feedforward architecture, modified feedforward architecture of IADC etc.

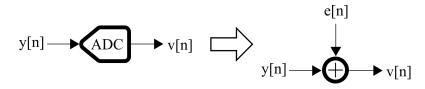

Figure 2.1: ADC modeled as an additive noise source

### 2.2.1 Second-Order CIFB IADC Architecture:

1

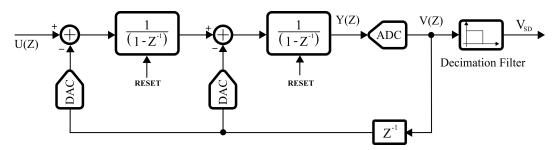

Feedback structure of the second-order Incremental ADC is shown in Fig.2.2. This structure is comprised of two integrators, followed by quantizer, feedback DACs and Decimation filter as shown. In order to realize the structure, the two DACs need to be implemented. That cause the circuit complexity to increase. Furthermore, the swing requirements of the op-amps are also quite high. The output of the quantizer V(Z) is given by,

Figure 2.2: Second Order Incremental Feedback Sigma-Delta Modulator Architecture

$$V(Z) = U(Z) + (1 - Z^{-1})^2 E(Z)$$

(2.1)

where E(Z) is the additive quantization error added by the quantizer. The input to the quantizer is Y(Z) which is the output of the second integrator which can, then from eq(2.1) and fig. (2.1), be expressed as,

$$Y(Z) = U(Z) + (1 - Z^{-1})^2 E(Z) - E(Z)$$

= U(Z) + (Z^{-2} - 2Z^{-1})E(Z) (2.2)

From eq(2.2), it clear that, the output of the second integrator is comprised of input signal component as well as the quantization noise with some transfer function which shows the necessity of high output swing of the op-amp.

#### 2.2.2 Second-Order CIFF IADC Architecture:

In order to reduce the swing requirement of the op-amp, feedforward architecture is developed as shown in Fig. 2.3. The input to the loop filter is only the second order high pass filtered noise i.e.  $(1 - Z^{-1})^2 E(Z)$ , which is passed through a series of two low pass filters, gives exclusive quantization error E(Z) at the output of the second integrator. Since the variance of the noise E(Z) is exceptionally small compared to the signal swing, the swing demand of the op-amp goes down significantly.

Figure 2.3: Second Order Incremental Feed-forward Architecture of Sigma-Delta Modulator

However, the input signal to the quantizer Y(Z) is still the same as expressed by eq (2.2)

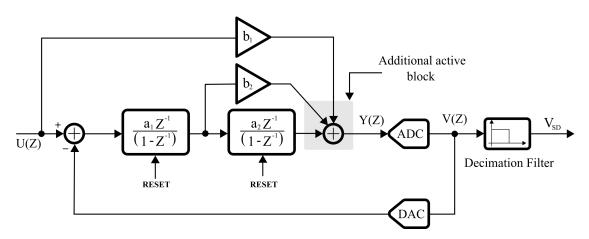

### 2.2.3 Modified Second-Order CIFF IADC Architecture:

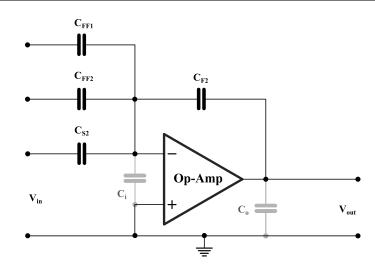

It is explicit from the Fig. 2.3 that, the active adder is mandatory for the addition of the input signal, a signal from first integrator and a signal from second integrator and the resulting signal is provided to the quantizer. To avoid the use of this active adder

and thus to save the remarkable amount of power, the structure is modified as shown in Fig. 2.4. The summing point is moved from output to the input of the second integrator. Thus the integrator can be collaboratively used as an adder as well as an integrator. But since in this scenario, the feedforward signals has to pass through the integrator, they are differentiated prior to the addition so that the resulting input signal to the quantizer remains same.

Figure 2.4: Second Order Incremental Modified Feed-forward Architecture of Sigma-Delta Modulator

The block diagram of the second order IADC is shown in Fig. 2.4. This structure is consists of two integrators followed by a multi-bit quantizer, a feedback DAC, delay block, differentiators and the decimation filter. In order to reuse the same hardware to digitize more than one analog input signals, reset feature is incorporated in  $\Sigma\Delta$ modulator, hence the name Incremental Sigma-Delta Modulator. The structure is reset at the beginning of the new conversion cycle including analog and digital memory elements. Then next sample is acquired using sample and hold circuit and is applied to the input of the first integrator. If the input signal amplitude is less than or equal to the Maximum Stable Amplitude (MSA), and if the poles of the NTF are well within the unit circle i.e. the system is stable then second integrator output y[n] remains bounded. Then at a given instant, the signals at the output of integrators and summing point can be expressed as,

$$w[j] = w[j-1] + a_1 u - a_1 V_{ref} v[j-1]$$

(2.3)

$$sum[j] = b_1 u[j-1] + a_2 w[j-1] + b_2 (w[j] - w[j-1])$$

(2.4)

$$y[j] = y[j-1] + sum[j]$$

(2.5)

Where the  $a_1$  and  $a_2$  are the modulation coefficients of the integrators,  $b_1$  and  $b_2$  are the coefficients of the feedforward input signal and the first integrator output signal paths respectively,  $V_{ref}$  is the reference voltage of the DAC and j is the index of the sampling instant. If the system run for the i number of clock cycles, then the non-iterative expressions of the signals at the output of first integrator, second integrator and the

Figure 2.5: Circuit Diagram of Second Order Incremental Modified Feed-forward Architecture of Sigma-Delta Modulator

summing point are,

$$w[i] = a_1 i u - a_1 V_{ref} \sum_{j=1}^{i} v[j-1]$$

(2.6)

$$y[i] = b_1 u + b_2 w[i] + a_1 a_2 u \sum_{j=1}^{i} (j-1) - a_1 a_2 V_{ref} \sum_{j=1}^{i} \sum_{k=1}^{j-1} v[k-1]$$

(2.7)

The equation for the residue after running the structure for OSR (M) number of clock cycles yields,

$$y[M] = b_1 u + b_2 w[M] + a_1 a_2 \frac{M(M-1)}{2} u - a_1 a_2 V_{ref} \left( v[M-2] + \dots + (M-1)v[0] \right)$$

(2.8)

Since the terms y[M] and w[M] are negligible, it can be pronounced that the reconstruction of the input signal sample 'u' is attainable from the (M - 2) number of output codes of the modulator.

Provided that the oversampling ratio M is high enough, the terms y[M] and w[M] becomes insignificant with respect to the term  $a_1a_2V_{ref}(v[M-2] + ... + (M-1)v[0])$ , and reconstruction can be achieved by passing this signal through a decimation filter with down sampling by a factor of M i.e. OSR. Thus can be represented as in Eq(2.9).

$$V_{SD} = \frac{2a_1a_2}{2b_1 + a_1a_2M(M-1)} V_{ref} \left( v[M-2] + \dots + (M-1)v[0] \right)$$

$$\approx \frac{2}{M(M-1)} V_{ref} \left( v[M-2] + \dots + (M-1)v[0] \right)$$

(2.9)

since  $2b_1 \ll a_1 a_2 M(M-1)$ , Where  $V_{SD}$  represents the close digital equivalent of the input sample.

When the conversion of one sample accomplished, the next cycle starts by resetting the analog integrators and digital memory blocks in the system, next sample is acquired by sample and hold block and cycle repeats for the conversion of the acquired sample.

For multi-bit quantizer, considering second order loop filter with oversampling ratio of M, the obtainable effective number of bit (ENOB) can be expressed approximately as,

$$ENOB = N_{SD} + 2\log_2(M) - 2 \tag{2.10}$$

where,  $N_{SD}$  is the resolution of the quantizer used in  $\Sigma\Delta$  loop and M is the over sampling ratio.

### 2.3 Extended-Range Incremental ADC

#### 2.3.1 Proposed Architecture - I

For moderate resolutions, the IADC used as a first stage of an ERADC can be based on a first-order architecture, but, when high-dynamic range is required, a second- or higher-order IADC is mandatory. Second-order IADCs can be based either on Cascade of Integrators with Feedback (CIFB) or Cascade of Integrators with Feed-forward (CIFF) architectures. The CIFF topology is typically preferable, since it relaxes the output swing and linearity requirements of the operational amplifier used in the first integrator. In any case the residue of the IADC conversion is available at the output of the second integrator at the end of each conversion cycle [19].

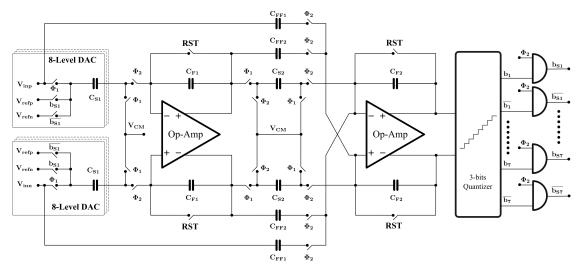

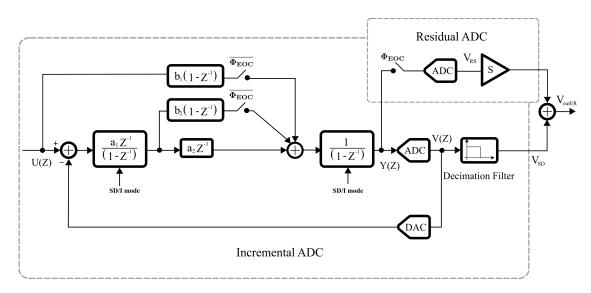

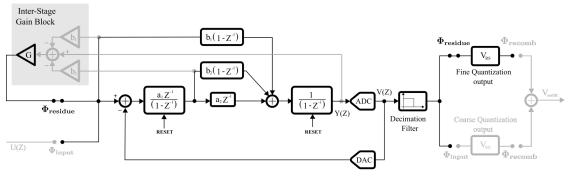

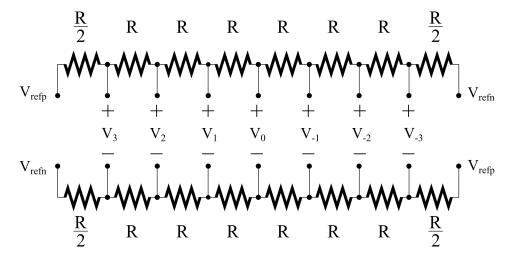

The block diagram of an ERADC based on a second-order CIFF IADC is shown in Fig. 2.6. The IADC, consisting of two integrators followed by an adder, a single-

Figure 2.6: Block diagram of an ERADC based on a conventional second-order CIFF IADC topology

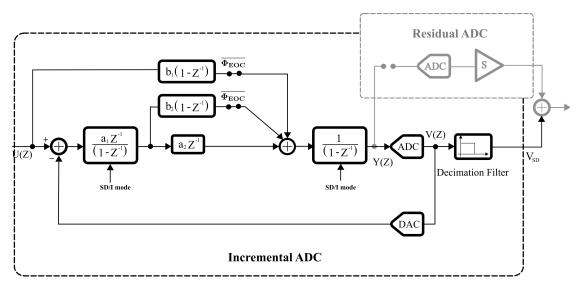

Figure 2.7: Block diagram of an ERADC based on a modified second-order CIFF IADC topology

or multi-bit quantizer, a feedback DAC and a decimation filter, performs the coarse quantization of the input sample. The residue of the coarse conversion is available at the output of second integrator at the end of each conversion cycle. In order to adapt the voltage swing of the residue to the input range of the RADC (typically the same as in the IADC), the residue has to be amplified by a factor *G*, through an inter-stage gain block (ISG). The amplified residue is then converted into the digital domain by the RADC, providing the fine quantization bit. The coarse and fine bit are finally combined to produce the complete ERADC output word.

It turns out that the use of an active adder in a CIFF IADC can be eliminated if the architecture is modified as shown in Fig. 2.7 [20]. The summing node is moved from the output to the input of second integrator and all the signals are differentiated. In this scheme, the second integrator collaboratively acts as an adder as well as an integrator, thus eliminating the need of an active adder. However, its output does not represents any longer the residue, but it includes also components proportional to the input signal and the first integrator output. Therefore, in order to calculate the residue to be provided to the RADC, these components have to be subtracted from second integrator output at the input of the ISG block. The ISG block, therefore, in this case collectively serves as an adder and an amplifier, avoiding the need of any additional active element for the residue calculation.

The inter-stage gain factor G can be implemented either with an actual amplifier with gain G or by scaling the RADC full-scale voltage by a factor G with respect to the IADC full-scale voltage. In the second case, the residue can be applied directly to the RADC, without the need of any active ISG block. However, in the ERADC architecture shown in Fig. 2.7, the input signal and first integrator output components present in the

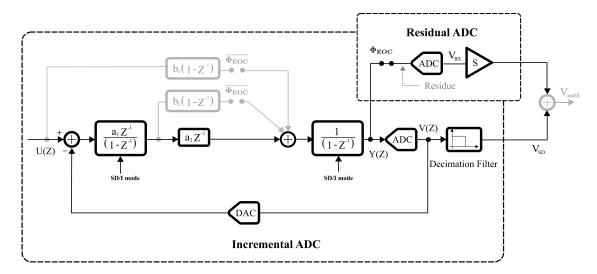

Figure 2.8: Block diagram of the proposed ERADC based on a modified second-order CIFF IADC topology

second integrator output make the use of an ISG block unavoidable, whereas the ERADC architecture shown in Fig. 2.6, does not need an ISG block, but it does need an active adder before the quantizer, leading in both case to extra power consumption.

The proposed ERADC architecture, shown in Fig. 2.8, does not require an ISG block nor an active adder in front of the quantizer of the IADC, since it performs the subtraction of the input signal and first integrator output components also at the input of the second integrator during the last clock cycle of the conversion, thus producing at the output of the second integrator directly the residue. The RADC is simply a SAR ADC, which samples the output of second integrator of the IADC during the last clock cycle of each conversion.

The implementation of the proposed architecture has been shown in more details in Fig.2.13, where RADC consists of just a quantizer, the reference voltage of which is G times smaller than that of IADC, and two switches. The decimation filtering of the output samples from IADC and the scaling the output of RADC is done in the digital domain and off-chip.

The IADC is reset before the beginning of each conversion cycle in order to clear any memory from previous samples. During the coarse conversion phase, the switches driven by  $\overline{\Phi_{EOC}}$  are closed, while those driven control signal  $\Phi_{EOC}$  are open, as shown in Fig. 2.9. If the IADC conversion lasts for *i* clock cycles, then the signal y[i] at the output of second integrator can be expressed as

$$y[i] = b_1 u + b_2 w[i] + a_1 a_2 u \sum_{j=1}^{i} (j-1) - a_1 a_2 V_{ref} \sum_{j=1}^{i} \sum_{k=1}^{j-1} v[k-1]$$

(2.11)

where u is the input signal (assumed constant), w[i] is the output signal of the first

Figure 2.9: Operation of the proposed ERADC during the coarse conversion phase

integrator,  $a_1$  and  $a_2$  are the integrator coefficients ( $a_1 = 1, a_2 = 1$ ) and  $b_1$  and  $b_2$  are the coefficients of the feedforward paths ( $b_1 = 1$  and  $b_2 = 2$ ). Parameter M represents the oversampling ratio (i. e. the number of clock cycles of each conversion). The coarse conversion is iterated for M - 1 clock cycles with the switches driven by control signal  $\overline{\Phi_{EOC}}$  closed, while in the last ( $M^{th}$ ) clock cycle they are opened preventing the feedforward paths to reach the input of the second integrator. The values of y[M - 1] and y[M] are then given by given by

$$y[M-1] = u + w[M-1] + \frac{(M-1)(M-1)}{2}u$$

-  $V_{ref} (v[M-3] + \dots + (M-2)v[0])$  (2.12)

and

$$y[M] = \frac{M(M-1)}{2}u - V_{ref}\left(v[M-2] + \dots + (M-1)v[0]\right)$$

(2.13)

respectively.

The filtered and decimated digital output of the IADC can be expressed as

$$V_{SD} \approx \frac{2}{M(M-1)} V_{ref} \left( v[M-2] + \dots + (M-1)v[0] \right)$$

(2.14)

For a second-order IADC with multi-bit quantizer, the obtainable effective number of bit (ENOB) is approximately given by

$$ENOB_{IADC} \approx N_{SD} + 2\log_2(M) - 2 \tag{2.15}$$

where,  $N_{SD}$  is the resolution of the IADC quantizer and M is the oversampling ratio.

Since, for (M-1) clock cycles, the feedforward signals (i. e. u[i] and w[i]) are

Figure 2.10: Operation of the proposed ERADC during the fine conversion phase

applied to the second integrator input, (2.11) holds. However, in the last clock cycle, these signals are blocked (i. e. u[M] = w[M] = 0). Therefore, the expression of the signal at the output of second integrator is given by (2.13). From (2.13), it is clear that in the last clock cycle of the conversion, the output of the second integrator represents the difference between the accumulated input signal and the digital output signal, which is indeed the residue of the IADC conversion, which can be directly applied to the RADC, as shown in Fig. 2.10.

In particular, the output voltage of the second integrator is sampled by the Sample-and-Hold (S/H) block of the SAR RADC. The reference voltages of the SAR RADC are scaled down by a factor of  $G = 2^{(N_{SD}-1)}$  with respect to the IADC reference voltages, so that the residue actually covers the whole SAR RADC input range. The SAR RADC runs for  $N_{RS}$ ,  $N_{RS}$  being the resolution of the SAR RADC, as illustrated in Fig. 2.11. The output of the SAR RADC  $V_{RS}$  is the digital representation of the residue. In order to recombine the RADC output with the IADC output,  $V_{RS}$  is passed through a scaling block with scaling coefficient S, given by

$$S = \frac{2}{M(M-1)}$$

(2.16)

The recombination of the outputs of the IADC ( $V_{SD}$ ) and the RADC ( $V_{RS}$ ) with proper coefficients results in the digital output  $V_{outER}$ , given by

$$V_{outER} = \frac{2}{M(M-1)} \left( V_{RS} + V_{ref} \left( v[M-2] + \dots + (M-1)v[0] \right) \right)$$

(2.17)

Therefore, the overall achievable ENOB can be expressed as

$$ENOB_{TOT} \approx N_{RS} + N_{SD} + 2\log_2(M) - 2 \tag{2.18}$$

Figure 2.11: Operation of the proposed ERADC during the recombination phase

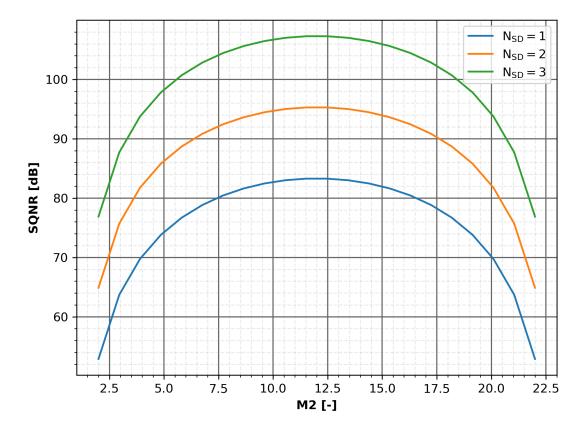

The timing diagram of the proposed ERADC is shown in Fig. 2.12. The total number of clock cycles available for the conversion is 24. Choosing M = 18 as oversampling ratio in the IADC, we use 19 clock cycles, since one clock cycle is needed for the reset at the beginning of each conversion cycle. Therefore, the IADC runs for 18 clock cycles, out of which, only for 17 clock cycles the feedforward paths are connected to the second integrator input, while in the 18<sup>th</sup> clock cycle they are not. Therefore, the control signal  $\overline{\Phi_{EOC}}$  is high for first 17 (M - 1) clock cycles and goes low in the last 18<sup>th</sup> ( $M^{th}$ ) clock cycle. Accordingly, the control signal  $\Phi_{EOC}$  is high only in the 18<sup>th</sup> ( $M^{th}$ ) clock cycle,

Figure 2.12: Conversion timing in an extended-range IADC

where residue is generated and applied to the RADC. Then, the SAR RADC runs next for

5 ( $N_{RS}$ ) clock cycles, converting the residue. In the next clock cycle, which is in fact the reset cycle of the IADC, the available digital outputs from both stages are recombined, delivering the extended-range output (recombination phase). The total conversion time  $T_{TOT}$  is then given by

$$T_{TOT} = T_{SD} + T_{RS}$$

=  $\left(\frac{M+1}{F_{ck}}\right) + \left(\frac{N_{RS}}{F_{ck}}\right)$  (2.19)

whereas the latency time  $T_{LATENCY}$  can be expressed as

$$T_{LATENCY} = \left(\frac{M+1}{F_{ck}}\right) + \left(\frac{N_{RS}}{F_{ck}}\right) + \left(\frac{1}{F_{ck}}\right)$$

(2.20)

where,  $T_{SD}$  denotes the conversion time of the IADC,  $T_{RS}$  the conversion time of the RADC and  $F_{ck}$  is the clock frequency.

Figure 2.13: Circuit diagram of a proposed Extended-Range second-order CIFF IADC

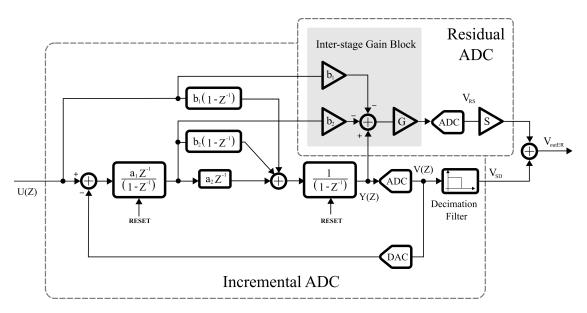

#### 2.3.2 Proposed Architecture - II

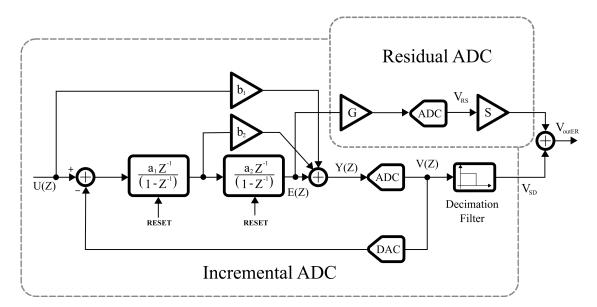

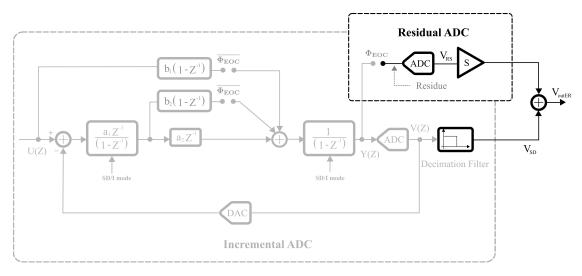

In a conventional Extended-Range ADCs, the implementation of the architecture is usually done with two different ADCs, i.e. first stage (or Principal ADC) and second stage ADC (or Residual ADC) where first stage is usually an Incremental ADC and the second stage could be flash ADC, SAR ADC, pipeline ADC or even incremental ADC etc. based on the quantizer resolution in IADC, quantizer resolution required in RADC, power consumption and the total available conversion time, as shown in Fig. 2.6 and Fig. 2.7.

Extended-Range ADC

Figure 2.14: Block diagram of the proposed architecture of an extended-range IADC

The second order IADC (first stage) consists of two integrators followed by single-bit or multi-bit quantizer, a feedback DAC and digital decimation filter, while second stage is comprised of an Inter-stage Gain block, a quantizer and digital scaling block. The implementation needs the employment of two separate ADCs which involves the designing and the layout for both the stages which in turn becomes a time consuming process. Moreover, along with necessity of more time, the architecture also occupies larger area as well as requires more power (since involves two ADCs). These shortcomings associated with Two-stage ERADCs necessitates to anticipate a solution with lesser hardware so that area, power consumption and the time for the development of the architecture is comparatively reduced.

The block diagram of the proposed architecture of the Extended-Range ADC is shown in Fig. 2.14. Unlike conventional extended range techniques, it comprised of just single-stage A/D converter and the inter-stage gain block where the ADC structure is an Incremental ADC. The IADC exercised is a second-order CIFF modified structure. It consists of two integrators, multi-bit quantizer, feedback DAC, switched-capacitive structure to realise differentiator and delay, decimation filter, memory blocks and recombination logic while ISG consists of active adder to extract the residue dealing the three signals (input sample, first integrator output and second integrator output) as shown in Fig. 2.14 and Fig. 2.20.

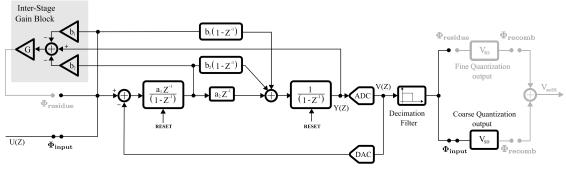

The operation of the proposed ERADC architecture can be divided into three sections: coarse quantization, fine quantization and recombination.

#### **Coarse Quantization**

The operation of the ADC begins with resetting the analog and digital memory blocks. The switch  $\Phi_{residue}$  is opened and the switch with control signal  $\Phi_{input}$  is closed connecting the input signal to the IADC structure as shown in Fig. 2.15. As long as the amplitude of the input signal u[n] is less than or equal to the Maximum Stable Amplitude (MSA) and the poles of the loop filter lies within the unit circle, the input to the quantizer y[n] remains bounded validating the stability of the IADC.

Extended-Range ADC

Figure 2.15: Proposed architecture of an extended-range IADC configuration in Coarse quantization phase

Then if the IADC structure is iterated for i number of clock cycles, the input to the quantizer at  $i^{th}$  clock cycles, i.e. y[i] can be given as,

$$y[i] = b_1 u + b_2 w[i] + a_1 a_2 u \sum_{j=1}^{i} (j-1) - a_1 a_2 V_{ref} \sum_{j=1}^{i} \sum_{k=1}^{j-1} v[k-1]$$

(2.21)

where,  $a_1 = 1$ ,  $a_2 = 1$  are the integrator's coefficients while  $b_1 = 1$  and  $b_2 = 2$  are the coefficients of the feed-forward paths. Considering the oversampling ratio for the coarse quantization to be  $M_1$ , the non-iterative expression of input to the quantizer at the end of conversion cycle of coarse quantization can then be expressed as,

$$y[M_1] = u[M_1] + w[M_1] + \frac{M_1(M_1 - 1)}{2}u - V_{ref}\left(v[M_1 - 2] + \dots + (M_1 - 1)v[0]\right)$$

(2.22)

When the OSR  $M_1$  is very high the term  $w[M_1]$  becomes insignificant with respect to the other terms. Then the filtered and decimated output from first conversion  $V_{SD}$  is

the coarse digital equivalent of the input sample, can be extracted from Eq.(2.22) and is approximately expressed as,

$$V_{SD} \approx \frac{2}{M_1(M_1 - 1)} V_{ref} \left( v[M_1 - 2] + \dots + (M_1 - 1)v[0] \right)$$

(2.23)

The quantization error can be given as,

$$\Delta_{SD} = \frac{2}{M_1(M_1 - 1)} \frac{V_{ref}}{(2^{N_{SD}} - 1)}$$

(2.24)

Then, the ENOB that can be achieved from the coarse quantization can be expressed as,

$$ENOB_{SD} = \log_2 \left(\frac{V_{ref}}{\Delta_{SD}}\right)$$

$$\approx N_{SD} + 2\log_2(M_1) - 1$$

(2.25)

The Signal-to-Quantization Noise (SQNR) can be given as,

$$SQNR_{SD} = 10 \log_{10} \left( \frac{\frac{V_{ref}^2}{8}}{\frac{\Delta_{SD}^2}{12}} \right)$$

$$\approx 20 \log_{10} \left( \frac{V_{ref}}{\Delta_{SD}} \right)$$

$$\approx 6N_{SD} + 40 \log_{10}(M_1) - 6$$

(2.26)

Once the coarse conversion cycle is completed, the output is stored in the digital memory block for the post-processing as shown in Fig. 2.15. It is explicit from Eq.(2.22) that the output of the second integrator in the last clock cycle does not have only the residue but also have the input signal component ( $u[M_1]$ ) and the component of the first integrator's output( $w[M_1]$ ). Therefore, in order to extract the residue, the input signal with coefficient  $b_1$  and the output of the first integrator with coefficient  $b_2$  is subtracted from the output of second integrator only in the last clock cycle.

$$e = y[M] - b_1 u - b_2 w[M]$$

=  $\frac{M_1(M_1 - 1)}{2} u - V_{ref} (v[M_1 - 2] + \dots + (M_1 - 1)v[0])$  (2.27)

Furthermore, the extracted residue need to be amplified by a factor G which makes the swing of the residue equal to the  $V_{ref}$  of the IADC to bring it to full-scale signal amplitude. However, the required amplitude for the IADC is not really the  $V_{ref}$  but the MSA of the IADC which is slightly lesser than the  $V_{ref}$ . The inter-stage gain block collectively serves as a subtractor as well as an amplifier, thus calculating the residue prepared for the further processing.

#### **Fine Quantization**

Similar to the operation of coarse quantization phase, that of fine quantization also start with resetting the analog blocks and digital decimation filter in the structure, thereby erasing the memory from the coarse quantization. The control signal  $\Phi_{input}$  is pulled to zero opening the switch and disconnecting the input while the switch controlled by control signal  $\Phi_{residue}$  is closed thereby connecting the residue from ISG to the IADC structure as shown in Fig. 2.16.

Extended-Range ADC

Figure 2.16: Proposed architecture of an extended-range IADC configuration in Fine quantization phase

Then, if the IADC is further iterated for  $M_2$  (i.e. oversampling ratio considered for the conversion of residue), then the input to the quantizer at the last i.e.  $M_2^{th}$  clock cycle is given by,

$$y[M_2] = e[M_2] + w[M_2] + \frac{M_2(M_2 - 1)}{2}e - V_{ref} \left(v[M_2 - 2] + \dots + (M_2 - 1)v[0]\right)$$

(2.28)

Since the OSR corresponding to the fine conversion  $M_2$  is high enough, the term  $w[M_2]$  becomes small enough compared to the other terms so that the digital equivalent of the residue filtered and decimated, can be derived as,

$$V_{RS} \approx \frac{2}{M_2(M_2 - 1)} V_{ref} \left( v[M_2 - 2] + \dots + (M_2 - 1)v[0] \right)$$

(2.29)

At the end of fine quantization conversion cycle, the converted residue into digital, is stored in the memory block as shown in Fig. 2.16.

Similarly, the LSB of the IADC, ENOB, and the SQNR in fine conversion configuration can be expressed as follows,

$$\Delta_{RS} = \frac{2}{M_2(M_2 - 1)} \frac{V_{ref}}{(2^{N_{SD}} - 1)}$$

(2.30)

$$ENOB_{RS} \approx N_{SD} + 2\log_2(M_2) - 1$$

(2.31)

$$SQNR_{RS} \approx 6N_{SD} + 40\log_{10}(M_2) - 6$$

(2.32)

#### Recombination

At the end of the fine quantization cycle, both the outputs, i.e. digital equivalent of input sample as well as the digital equivalent of the residue are available. Then, in the recombination phase these digitized signals are recombined with proper coefficients in order to get the final output i.e.  $V_{outER}$  as shown in Fig. 2.17. Then the expression for  $V_{outER}$  can be given as,

$$V_{outER} = V_{SD} + \frac{2}{M_1(M_1 - 1)} V_{RS}$$

=  $\frac{2}{M_1(M_1 - 1)} [V_{RS} + V_{ref} (v[M_1 - 2] + \dots + (M_1 - 1)v[0])]$

=  $\frac{2}{M_1(M_1 - 1)} \left[ \frac{2}{M_2(M_2 - 1)} V_{ref} (v[M_2 - 2] + \dots + (M_2 - 1)v[0]) \right]$

$V_{ref} (v[M_1 - 2] + \dots + (M_1 - 1)v[0])]$  (2.33)

Extended-Range ADC

Figure 2.17: Proposed architecture of an extended-range IADC configuration in Recombination phase

The LSB of the overall architecture is,

$$\Delta_{ER} = \frac{2}{M_1(M_1 - 1)} \frac{2}{M_2(M_2 - 1)} \frac{V_{ref}}{(2^{N_{SD}} - 1)^2}$$

(2.34)

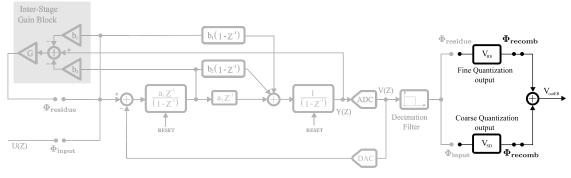

Figure 2.18: SQNR Vs  $M_2$

From the equation above, the total ENOB that can be achieved with this architecture is,

$$ENOB_{TOT} = \log_2 \left(\frac{V_{ref}}{\Delta_{ER}}\right)$$

$$\approx 2N_{SD} + 2\log_2(M_1) + 2\log_2(M_2) - 2$$

$$\approx 2(N_{SD} - 1) + 2\log_2(M_1M_2)$$

(2.35)

And the overall Signal-to-Quantization Noise achievable can be derived as,

$$SQNR_{TOT} \approx 20 \log_{10} \left( \frac{V_{ref}}{\Delta_{ER}} \right)$$

$$\approx 12N_{SD} + 40 \log_{10}(M_1) + 40 \log_{10}(M_2) - 12$$

$$\approx 12(N_{SD} - 1) + 40 \log_{10}(M_1 M_2)$$

(2.36)

The total number of clock cycles required for the complete conversion are, therefore  $M = M_1 + M_2$ . Then for given quantizer resolution  $(N_{SD})$  and given number of total clock cycles available for conversion (M), what would be the number of clock cycles that can be allocated for the coarse  $(M_1)$  and fine conversion  $(M_2)$  so that the maximum SQNR can be obtained. This can be found by converting the Eq.2.36 from two variables  $(M_1 and M_2)$  to single variable either by putting  $M_1 = M - M_2$   $(M_2 = M - M_1)$ ,

Figure 2.19: Timing Diagram with all the Phases

differentiating it w.r.t. to  $M_2(M_1)$  and equating it to zero.

$$\frac{d}{dM_2}SQNR_{TOT} = 0 \tag{2.37}$$

$$\frac{d}{dM_2} SQNR_{TOT} = \frac{d}{dM_2} \left\{ 12(N_{SD} - 1) + 40 \log_{10} \left[ (M - M_2)M_2 \right] \right\}$$

= 0 + 40  $\frac{1}{\ln 10} \frac{M - 2M_2}{(M - M_2)M_2}$  (2.38)

Equation above Eq.(2.38) represents the derivative or the slope of the  $SQNR_{TOT}$  characteristic for given  $N_{SD}$  and M and considering  $M_2$  as a variable. Putting the value of Eq.(2.38) in Eq.(2.37) yields,

$$M_2 = \frac{M}{2} \tag{2.39}$$

$$M_1 = M - M_2 = \frac{M}{2} \tag{2.40}$$

This process yields that, in order to achieve maximum SNR possible  $M_1 = M_2 = \frac{M}{2}$ . This can also be verified from Fig. 2.18. For  $M_2 = 12$  (where M is 24, i.e.  $M_2 = \frac{M}{2}$ ), the peak SNR is obtained considering various cases with different values of  $N_{SD}$ . The total conversion time  $T_{TOT}$  and Latency time  $T_{LATENCY}$  can be given as,

$$T_{TOT} = T_{CQ} + T_{FQ}$$

=  $\left(\frac{M_1 + 1}{F_{ck}}\right) + \left(\frac{M_2 + 1}{F_{ck}}\right)$  (2.41)

$$T_{LATENCY} = \left(\frac{M_1 + 1}{F_{ck}}\right) + \left(\frac{M_2 + 1}{F_{ck}}\right) + \left(\frac{1}{F_{ck}}\right)$$

(2.42)

where  $T_{SD}$  denotes the time required for the coarse conversion,  $T_{RS}$  is the time required for the fine conversion,  $M_1$  is the OSR for the coarse conversion,  $M_2$  is OSR for fine conversion and  $F_{ck}$  is the clock frequency.

Figure 2.20: Circuit diagram of the proposed architecture of an extended-range IADC

# **Chapter 3**

# Simulink Modeling & System Verification

# 3.1 Introduction

Conventional sigma-delta modulators are commonly used for performing A/D conversion in several sensor read-out applications, such as automotive, consumer electronics, medical instrumentation, environmental measurements, or even live audio recording from a microphone [1]. However, these ADCs, which exhibit very high Dynamic Range (DR) thanks to oversampling and noise shaping techniques, typically feature a narrower bandwidth with respect to Nyquist rate ADCs.

Moreover, because of the memory effect inherent in sigma-delta modulation (each digital output sample somehow depends on the value of previous samples), they are not suitable for applications where single-shot events or multiple input sources with multiplexing must be evaluated. Incremental ADCs (IADCs) overcome this limitation, since they are reset at the beginning of each conversion cycle [12]. However, in IADCs high-resolution is obtained at the expense of a large number of clock cycles per conversion, preventing their use when relatively large bandwidth or short conversion time (latency) is required.

This shortcoming of IADCs can be overcome by exploiting the extended-range technique [22][23][20][19][30], which allows the resolution to be increased while maintaining the conversion time relatively short. Extended-range architectures,

however, are more susceptible than conventional IADCs to building-block non-idealities, which have then to be considered carefully. This chapter provides some insight on the effect of operational amplifier (op-amp) specifications on extended-range IADC performance, in order to allow proper choice of the design parameters.

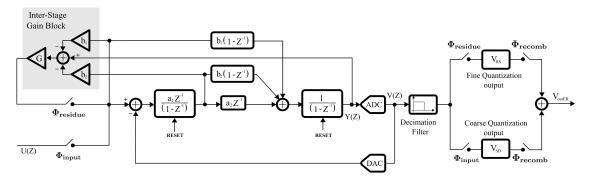

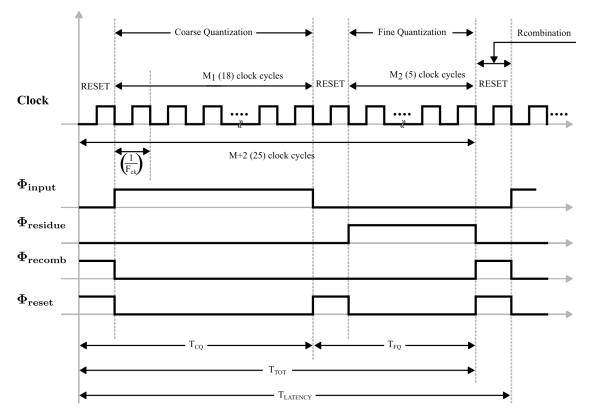

Simulink modeling and verification of the preferred architectures is considered as crucial step in the process of the design, which enables to authenticate the feasibility of the architecture for given specifications. Therefore, a simulink model is developed for I $\Sigma\Delta M$  and residual ADC as shown in the Fig. 3.1. Developed simulink model

Figure 3.1: Simulink Model of Second Order Incremental Feed-forward Architecture of Sigma-Delta Modulator

architecture incorporates sample-and-hold, two delayed integrators, quantizer followed by decimation filter in the I $\Sigma\Delta M$  path, while residue signal digitization path comprised of gain block, residual quantizer and decimator as shown in the Fig. 3.1.

# **3.2 Block Description:**

### **3.2.1 Integrator Block:**

Integrator block has been built in order to incorporate the RESET feature to ensure the incremental function of the structure. Then a coefficient can be set with the solution of gain block. Along with this, different non-idealities of the Op-Amp needed to be consolidated, e.g. op-amp noise is included by using a block 'OpNoise' while the MATLAB functions are written to encompass other non-idealities like slew rate, loop gain and Gain-Bandwidth Product inside the 'INTEGRATOR with delay' block. The simulink model of the integrator is shown in the Fig. 3.2 For the ideal simulation, these parameters are set to,  $Gain = 100 \ dB$ ,  $Slew Rate = 1 \ V/ns$  and  $GBW = 1 \ GHz$  so

Figure 3.2: Simulink Model of the Integrators employed in the I $\Sigma\Delta M$  architecture

the integrator reflects all the ideal characteristics.

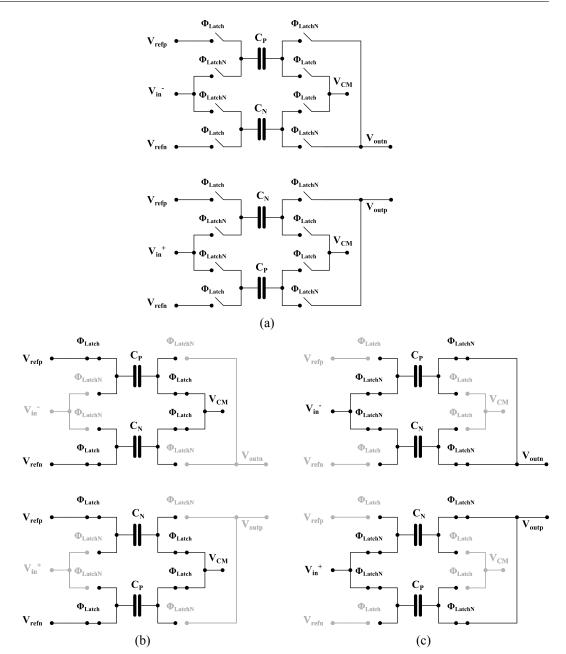

### 3.2.2 Quantizer:

'ADC-DAC' block from the SDtoolbox library allows to specify the number of comparators, mismatch parameter along with total capacitance to be used in the quantizer e.g. for 2 bit quantizer i.e. 4 level quantizer, the required comparators are 3, while that for 3 level quantizer are 2 and so on.

#### 3.2.3 Decimation Filter:

Figure 3.3: Simulink Model of the Decimation Filter

Decimation filter block is the combination of the Finite Impulse Response (FIR) filter with decimator block. The FIR filter transfer function can be expressed as,

$$H(Z) = a_0 + a_1 Z^{-1} + a_2 Z^{-2} + \dots + a_{M-1} Z^{(M-1)}$$

(3.1)

which is implemented with M number of gain blocks, (M - 1) number of delay elements and (M - 1) number of adders as shown in Fig.3.3, where M is the over sampling ratio. The decimator block followed by FIR filter, samples the output of the filter after every M number of clock cycles.

| <b>ENOB</b> <sub>TOT</sub> | 12 |    |    | 13 |    |    | 14 |    |    |

|----------------------------|----|----|----|----|----|----|----|----|----|

| N <sub>SD</sub>            | 3  | 3  | 4  | 3  | 3  | 4  | 3  | 3  | 4  |

| <b>ENOB</b> <sub>INC</sub> | 12 | 9  | 10 | 13 | 9  | 10 | 14 | 9  | 10 |

| N <sub>RS</sub>            | 0  | 3  | 2  | 0  | 4  | 3  | 0  | 5  | 4  |

| Μ                          | 45 | 18 | 18 | 64 | 18 | 18 | 90 | 18 | 18 |

Table 3.1: Parameters of the considered extended-range IADC

# **3.3** Analysis of Op-Amp Requirements

Different combinations of resolution in IADC with a given value of M and ERADC can fulfill a specific ENOB requirement. However, the sensitivity of each combination to the op-amp non-idealities varies, while selection of the optimum solution is necessary for robust performance. Therefore, the analysis of the op-amp specifications plays a very important role in selecting the best combination. The effects of op-amp non-idealities, such as gain and gain-bandwidth product (GBW), are, therefore, determined for an extended-range IADC with the combinations of resolution in IADC and ERADC summarized in Tab. 3.1, using a Simulink model.

A complete model of the Incremental  $\Sigma\Delta$  Modulator with extended counting (Extended Range Incremental  $\Sigma\Delta$  Modulator) is developed in the simulink as shown in Fig. 3.1. All the parameters of the Op-Amps are set with intention to reflect the ideal characteristics of Op-Amp and simulations are carried out. Various permutations and combinations of the resolutions of the I $\Sigma\Delta$ M and Residual ADC can be verified for given clock frequency of 80 MHz, total conversion time of 25 clock cycles to attain the ideal overall performance in terms of ENOB of 12, 13 and 14 and the other parameters considered are given in the Tab. 3.1 However the additional 12 dB margin of SNR or 2-bit of ENOB must be considered over the exact requirement of SNR or ENOB to accommodate parasitic effects and process corners degradation as a usual practice.

#### 3.3.1 Effect of Low-Frequency Gain

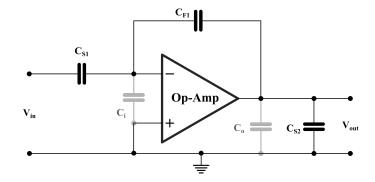

The first parameter to be considered is the low-frequency gain of the op-amps used in the first and second integrator of the second-order IADC. The variation of the gain affects the integrator coefficient, as well as the location of the integrator pole. In a stand-alone IADC, the shift in the location of the pole has more significant effect than the modification of the integrator coefficient, since the integrator pole sets the zero of the IADC NTF. However, in an extended-range IADC also the variation of the integrator coefficient becomes important, since it affects the value of the residue and can cause a degradation of the overall performance after recombination. The integrator transfer function considering finite op-amp low-frequency gain is given by [31]

$$H(Z) = \frac{C_s}{C_f} \frac{Z^{-1}}{1 - \alpha Z^{-1}}$$

(3.2)

Parameter  $\alpha$  is given by

$$\alpha \approx \frac{A_0 C_f}{A_0 C_f + C_s} \tag{3.3}$$