# Embedded Systems Energy Characterization using non-Intrusive Instrumentation

Nicolas Fournel, Antoine Fraboulet, Paul Feautrier

#### ▶ To cite this version:

Nicolas Fournel, Antoine Fraboulet, Paul Feautrier. Embedded Systems Energy Characterization using non-Intrusive Instrumentation. Research Report RR2006-37, LIP - ENS Lyon. 2006. <a href="https://doi.org/10.2006/journal.com/">https://doi.org/10.2006/journal.com/</a>

HAL Id: hal-00399644

https://hal.archives-ouvertes.fr/hal-00399644

Submitted on 27 Jun 2009

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### Laboratoire de l'Informatique du Parallélisme

École Normale Supérieure de Lyon Unité Mixte de Recherche CNRS-INRIA-ENS LYON-UCBL  $\rm n^o\,5668$

## Embedded systems energy characterization methodology using non-intrusive instrumentation

Nicolas Fournel Antoine Fraboulet Paul Feautrier

November 2006

Research Report No RR2006-37

### École Normale Supérieure de Lyon

46 Allée d'Italie, 69364 Lyon Cedex 07, France Téléphone : +33(0)4.72.72.80.37 Télécopieur : +33(0)4.72.72.80.80 Adresse électronique : lip@ens-lyon.fr

# Embedded systems energy characterization methodology using non-intrusive instrumentation

Nicolas Fournel Antoine Fraboulet Paul Feautrier

November 2006

#### **Abstract**

This research report presents a non intrusive methodology for building embedded systems energy consumption models. The method is based on measurement on real hardware in order to get a quantitative approach that takes into account the full architecture. Based on these measurements, data are grouped into class of instructions and events. These classes can then be reused in software simulators and in high-level source code transformation cost functions for optimizing compilers. The computed power model is much more simpler than previous power models while being accurate at the platform level.

The methodology is illustrated using experimental results made on an ARM Integrator platform for which an accurate and full system energy model is build.

**Keywords:** Embedded Systems, Energy Consumption Model, Simulation Instrumentation, Optimizing Compilers Cost Functions.

#### Résumé

Ce rapport de recherche présente une méthodologie non intrusive de construction de modèles de consommation pour des architectures embarquées. La méthode utilise des mesures effectuées sur des plateformes réelles afin d'avoir une approche quantitative prenant en compte la plateforme complète. Les mesures sont ensuite groupées en classes d'instructions et d'événements pour simplifier le modèle. Ces données peuvent ensuite être facilement réutilisées dans des simulateurs instrumentés ou comme indiquation dans des modèles de coût utilisés dans les transformations de haut niveaux des compilateurs optimiseurs.

Une application de la méthode est présentée en utilisant une plateforme ARM Integrator pour laquelle un modèle de consommation est construit au nivveau système.

**Mots-clés:** Systèmes embarqués, Modèle de consommation énergétique, Instrumentation pour la simulation, Fonctions de coût pour compilateurs optimiseurs.

## **Contents**

| 1 | Introduction  State of the Art and Related Work  2.1 Energy consumption models  2.2 Model classification and related work  2.2.1 Level of granularity  2.2.2 Data gathering method  2.2.3 Related work |    |  |  |  |  |  |  |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|--|--|

| 2 |                                                                                                                                                                                                        |    |  |  |  |  |  |  |

| 3 | A methodology for energy consumption model construction                                                                                                                                                | 10 |  |  |  |  |  |  |

|   | 3.1 Measurement setup                                                                                                                                                                                  | 11 |  |  |  |  |  |  |

|   | 3.1.1 Protocol                                                                                                                                                                                         | 12 |  |  |  |  |  |  |

|   | 3.2 Measurement error verification                                                                                                                                                                     | 15 |  |  |  |  |  |  |

|   |                                                                                                                                                                                                        |    |  |  |  |  |  |  |

|   | 3.3 Model structure and parameters                                                                                                                                                                     | 16 |  |  |  |  |  |  |

| 4 | Measurement results: experimentations on the ARM Integrator/CM 922T-XA10                                                                                                                               |    |  |  |  |  |  |  |

|   | 4.1 Architecture exploration                                                                                                                                                                           | 18 |  |  |  |  |  |  |

|   | 4.2 Benchmarks construction                                                                                                                                                                            | 20 |  |  |  |  |  |  |

|   | 4.3 Measures and model adaptation                                                                                                                                                                      | 21 |  |  |  |  |  |  |

|   | 4.4 Resulting model                                                                                                                                                                                    | 23 |  |  |  |  |  |  |

|   | 4.4.1 Basic model                                                                                                                                                                                      | 23 |  |  |  |  |  |  |

|   | 4.5 Advanced information extraction                                                                                                                                                                    | 23 |  |  |  |  |  |  |

|   | 4.5.1 Frequency scaling                                                                                                                                                                                | 24 |  |  |  |  |  |  |

|   | 4.5.2 DVS extension                                                                                                                                                                                    | 26 |  |  |  |  |  |  |

|   | 4.5.2 DVS extension                                                                                                                                                                                    | 20 |  |  |  |  |  |  |

| 5 | Model validation                                                                                                                                                                                       | 27 |  |  |  |  |  |  |

|   | 5.1 Model validation                                                                                                                                                                                   | 27 |  |  |  |  |  |  |

| 6 | Conclusion and Future Works                                                                                                                                                                            | 28 |  |  |  |  |  |  |

| A | Complete results list                                                                                                                                                                                  | 31 |  |  |  |  |  |  |

## **List of Figures**

| 1         | Architectural hierarchy from transistor to embedded system | 4                          |

|-----------|------------------------------------------------------------|----------------------------|

| 2         | Energy consumption model usage.                            | 4                          |

| 3         | Simulation based energy consumption modelling              | 6                          |

| 4         | Measurement based energy consumption modelling             | 6                          |

| 5         | Sampled signals at 2.5G samples/s                          | 2                          |

| 6         | Acquisition results                                        | 5                          |

| 7         | model block examples                                       | 7                          |

| 8         | Basic image architecture                                   | 9                          |

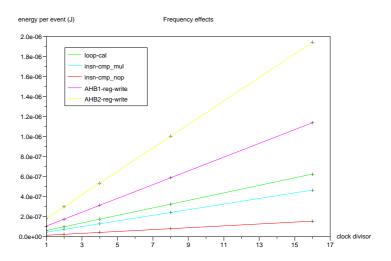

| 9         | Multiple frequencies experiments                           | 24                         |

|           | energy consumption                                         | 25                         |

| 10        |                                                            |                            |

|           | of Tables                                                  |                            |

|           | of Tables  Results of benchmarks                           | :1                         |

| List (    | Results of benchmarks                                      |                            |

| List (    |                                                            | 21                         |

| List (    | Results of benchmarks                                      | 21<br>22                   |

| 1 2 3     | Results of benchmarks                                      | 21<br>22<br>26             |

| 1 2 3 4   | Results of benchmarks                                      | 21<br>22<br>26<br>26       |

| 1 2 3 4 5 | Results of benchmarks                                      | 21<br>22<br>26<br>26<br>28 |

#### 1 Introduction

Embedded computing systems go through a dramatic increase of computational power. While this computational power is growing, electrical consumption follows the same kind of trend. Unfortunately battery capacity used to power these systems does not keep the same pace. The consequences of these differences in evolution drive designers to take the electrical consumption as a major constraint. We reached a point where hardware solutions are not sufficient anymore. One of the multiple solutions to reduce significantly energy consumption is to organize software and drive the hardware in a power efficient way.

One can use software optimization techniques during software design or source code optimization at compile time. To know where the software is the more power-hungry and what are the best optimization choices, quantitative consumption data are of great value. Manufacturers reference manuals usually provide some consumption figures for different system parts. Unfortunately, these figures are generally not precise enough to build a complete system power consumption model. The usability of these figures (CPU instructions, caches, bus access, scratch-pad and external memories, peripherals, ...) is made difficult for software developers and tools by their varying levels of description that are most of the time different from each other among components of the same embedded system. The result is that it is very difficult to aggregate the figures of different components for a full system electrical consumption. In the same manner it is often difficult to handle them during hardware simulation or within optimizing compilers.

In this report, we propose a methodology which aims at building electrical consumption models that overcome these problems. As it is targeting embedded software development for fixed architectures, the power consumption model is based on measurement on real hardware. The measurement procedure should not be intrusive because these setups are generally difficult to implement and represent a lot of work that might not be feasible for software developers. The proposition of this report use a model building methodology based on external system measurements only. The model generated by this methodology must be simple enough to be used in fast simulation for software organization choices or automated optimizations at compile time. Experimentations have been made on an ARM Integrator platform and an accurate full system energy consumption model is built from a series of measurements using micro benchmark codes.

The report is organized as follows. In Section 2 we review the different existing techniques used for building hardware power consumption model and their use. Section 3 presents our methodology used to build full platform energy consumption models. Section 4 presents our experimental results on an ARM target platform that highlights the points mentioned above and shows that an accurate energy consumption model can be build and used in software platform simulators using only simple and non intrusive measurements. Finally, the model will be validated in section 5.1.

#### 2 State of the Art and Related Work

Before giving some examples of existing models, we explain in this section how an energy consumption model is used and why it is interesting.

#### 2.1 Energy consumption models

We give here an overview of the end user model usage. This overview will be preceded by an architecture presentation, which will help to understand this usage.

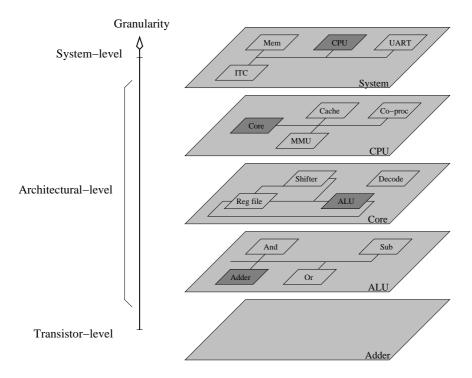

The aim of using a model in energy consumption estimation is to reduce the design complexity and to test some solutions before production. We will give more details about these specific aims after model building description. The architecture of targeted systems can be seen as a hierarchical stack. At the lowest level, we find the transistors, elementary components of VLSI (Very Large Scale Integration) circuits, and at the upper level, there is the overall system. This hierarchy is depicted on Figure 1.

Every model is built at a specific level of granularity. The major influence of this level of granularity is on the model parameters. The parameters of a system-level model are not as fine grained as the one taken for a gate-level model. For example in the first case we will have microprocessor instructions whereas in the second we will use binary test vectors.

Figure 1: Architectural hierarchy from transistor to embedded system

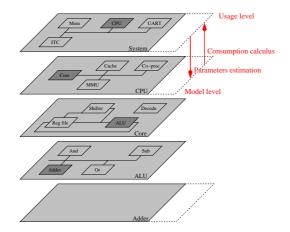

When using the model, we must use the correct parameters values to get the most precise energy consumption estimation. If the model has architectural level parameters and if our goal is to know how many Joules were spent by a given software application, we should proceed as follows. We should simulate the behavior of the platform between system level (usage level) and architectural level (model level), to estimate the model parameters values. At system level, activity informations are given by the application itself. Once the parameters values are fed in the model, a computation phase is needed to aggregate the data. This example is illustrated by figure 2.

Figure 2: Energy consumption model usage.

#### 2.2 Model classification and related work

We will now see that many work has been already done on the task of energy characterization or power estimation. Before giving examples of these works, we will expose here how we decided to classify them. These models can be characterized by two main orthogonal criteria. The first is the level of granularity of the resulting model, and the second is the data acquisition method at model building time.

#### 2.2.1 Level of granularity

The first criterion is level of granularity of the model. Up to now there exists several power consumption models for processing systems (general purpose and specialized processing unit). These models can be ordered by level of abstraction, from circuit-level (the lowest) to system-level (the highest). Figure 1 depicts the increasing level of granularity of the model as far as we consider a higher level in the architectural hierarchy. We can classify them into three main groups: circuit/gate-level models, architectural models and finally system/instruction-level models.

Thus, in the highest class of abstraction level, which is instruction/system level, efforts are made to characterize the energy consumption of instructions. Some only builds an instruction cost table, where others also take into account the inter-instruction cost (control logic switching cost) or the data values (data logic switching cost).

At the architecture level, the system is first divided into functional blocks. Each of these blocks has its own energy consumption model. An important advantage of this kind of model is the possibility to choose completely different types of model for each functional block, and thus completely different parameters for them. Most of the time, models used for functional unit are analytical models, but statistical or empirical models built thanks to simulated or measured data can be used too.

Finally, as far as circuit/gate level model are concerned, the work is to describe very fine grained behavior of the target system or processor.

#### 2.2.2 Data gathering method

In the model building process, quantitative value of energy consumption are needed to calibrate the final model to suit more closely the underlying architecture energy consumption. Two of the methods can be distinguished by their data acquisition method and the third does not even need data. For this criterion, we can find the three following classes: analytical models, simulation based models and physical measurement based models.

The first method of model building is analytical construction. In fact, in this method no energy consumption data are needed. This method use physical laws and architecture description to predict accurately the electrical consumption of the targeted element. This method is often used on low-level and regularly structured units such as caches memories. It appears to be really difficult on irregular structures or not really accurate due to extreme simplifications.

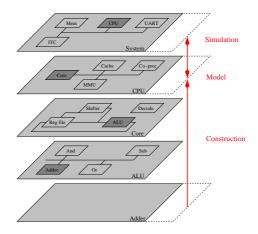

The second method gathers quantitative data from simulation. In this method, we build the model by a bottom-up process, which consists in using models of lower level of granularity, as described in section 2.1. This process can be repeated level by level. At each step, parameters of the lower level must be calculated by simulation and quantitave data gathered. All informations are then deduced from the hardware architecture. Figure 3 depicts this method. Since this method only requires the detailed architecture of the system, no hardware platform is needed. It can be used during design of VLSI circuits to estimate the resulting consumption or to test the viability of new solutions before production.

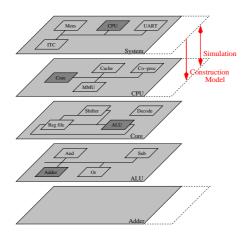

An alternate solution to simulation and lower level model based methodology is to use measurements. Indeed, by measuring the energy consumption on real hardware, it is possible to build an energy consumption model. In fact, the production process of this kind of models is the exact opposite of the one described before for simulation based ones. The process is a top-down construction, since the data gathered by measurement concern the overall system, and detailed informations must be extracted from these global ones, and not aggregated. Figure 4 gives an overview of this method. The models built by this kind of method are generally less complex since quantitative data are coarse-grained.

Figure 3: Simulation based energy consumption modelling.

Figure 4: Measurement based energy consumption modelling.

We will give examples of each methods at different level of granularity in the following section. As our interest is in a measurement based method, we give here a few examples of measurement setups proposed in the literature. The solutions proposed for measurement have a wide range of complexity.

- The simplest solution is proposed in [20], by Tiwari et al. It consists in using a ammeter connected to the power supply pins of the processor. This method has for advantage to be very simple to implement, but it has also a huge disadvantage, which is the loss of information. Due to the poor time resolution of the ammeter, we only get mean values.

- A way to overcome this problem is proposed by Russell and Jacome in [18]. Their data acquisition solution use a digitalizing oscilloscope coupled with a resistor placed in series with the power supply connection. For this kind of measurement, they use a high performance oscilloscope (LeCroy LC534) which has a high sample rate. The setup even allows the authors to have a trigger signal, which gives the beginning and the end of the measurement period. The sample rate of the data is limited by the performance of the oscilloscope.

- Another solution for instantaneous current measures is proposed by Nikolaidis and Laopoulos in [16]. The setup is based on an oscilloscope and a current mirror unit. The reason of a current mirror usage is the reduction of the influence of the measurement setup on measured hardware. The authors can measure power consumption of the system at high sampling speed without interfering with the supply voltage.

- Finally, Chang et al., in [3], propose a setup that gives the consumption cycle by cycle. This setup is based on the charge and discharge of capacitors. Indeed, the setup is placed in series with the power supply. The principle is that at each cycle one capacitance charges and the other discharges. Thus by sampling only twice a clock cycle they can deduce the power consumed by the target system during this cycle. The setup is completed by an AD converter (Analog-Digital Converter) which is in charge of sampling, and a Fast SRAM that is fed by the ADC with the voltage values. The data are then computed from the SRAM.

#### 2.2.3 Related work

The two criteria of classification are not fully orthogonal, since all combination are not possible or pertinent. Indeed, analytically built models targets low level units due to the complexity of the building process. This building method will not be detailed any further in the remaining of this report, because our interest is in a higher level model. As far as simulation based model are concerned, they are rarely used in the highest level of granularity since they are highly time consuming at building time. Finally we do not find lower level model based on measurements since it is complicated to extract low level informations from measures which are representing the whole system consumption.

In the following paragraphs, we will give an overview of the basic models of electrical consumption of circuits, and then some examples of abstraction level/building method combinations investigated in related works. The presentation of these works will be organized by level of abstraction.

**The basic model** Before giving examples of models by architectural layer class, we present here the basic power model of VLSI (Very Large Scale Integration) circuits. This model is one of the lowest level power model, since it models the power consumption of the most elementary gate, the inverter (2 transistors).

The consumption of a gate can by divided into two main parts: static and dynamic power. The first part, static power, does not depend on the gate input changes and hence gate activity. However, the second part, dynamic power, is correlated to these input signal changes.

The static power is composed of the current leakage of a closed transistor. It is usually modeled by equation (1).  $V_{dd}$  is the power supply voltage and  $I_{leak}$  is the leakage current.

$$P_{static} = V_{dd} \times I_{leak} \tag{1}$$

The dynamic power can be subdivided into two parts : short-cut power and output capacitance load power.

The short-cut power is due to the fact that the transistors are all (N-MOS group and P-MOS group) opened at the same time in the transition period. Some are switching from 1 to 0 and the others from 0 to 1. When the input signal is around the threshold voltage  $V_{th}$ , the two group of transistors are open and a current can pass between ground  $V_{cc}$  and  $V_{dd}$ . This power can be modeled by equation (2). Once again  $V_{th}$  is the threshold voltage and  $V_{dd}$  is the power supply voltage. Finally,  $\tau$  is the signal raise time.

$$P_{short\ cut} = K.(V_{dd} - 2V_{th})^3.\tau\tag{2}$$

The second part of the dynamic power is the output capacitance load power. This formula express the fact that the energy stored in the output capacitance is shorted to ground when the input switches from 1 to 0.

$$P = \frac{1}{2}CV_{dd}^2 \tag{3}$$

where C is the output capacitance of the gate.

In present day technologies, the first two sources of power dissipation are negligible against the amount of power that the third represents. The power consumption of the inverter is then simplified to the output capacitance load described by equation (3).

This model is generalized to all gates by the approximation that all other consumption can be neglected against the output capacitance charge.

A second generalization is used in architectural and system level models. A naive extension of the model described before (equation (3)) to a full block or chip gives formula (4):

$$P = \frac{1}{2} C_m V_{dd}^2 f \alpha \tag{4}$$

where  $C_m$  is the total output capacitance of the system, f is the operating clock frequency and  $\alpha$  is the proportion of gates switching from 0 to 1 in a clock cycle. The parameters  $\alpha$  and  $C_m$  are difficult to estimate but can be obtained by detailed simulation.

This latter model is widely used, even in other models, where it gives approximation of the power consumption of a system or block, but it is not adapted to the specificity of the logic contained in the block.

**Transistor/Gate-level Models** One of the most accurate methods to estimate power consumption before a circuit is realized is doubtlessly transistor/gate level simulation. In fact most of synthesis tools provide power consumption prediction. For example PowerMill [8] from Synopsys and QuickPower [7] from Mentor. These tools are low level (circuit or HDL) simulators. Other simulators operate at circuit level, such as Spice-based simulators (Star-Sim [11] for example). This kind of simulation gives accurate finegrained results, but are very time-expensive. In fact the time of simulation limits the number of events simulated.

A first improvement for this drawback is the gate level simulation. The elementary unit is not the transistor anymore but the gate (an assembly of transistor). Mynoch [17] for example, runs 450 times faster than Spice based simulation.

The models (and simulators based on these models) presented here requires detailed information on the hardware modeled, HDL source or equivalent informations. At software development phase, it is almost impossible to get these information from the manufacturers. Then this kind of models do not meet our needs of simplicity. Moreover measurement based model does not exist and are probably impossible to build at such a low level of granularity.

**Architectural-level models** As we saw before, the peculiarity of architectural models is that they are centered on the functional units. Energy consumption is estimated by estimating the consumption of all the blocks.

The first architectural-level model we will talk about is proposed by Chen et al. in [6, 5, 4]. The system modeled in this work is a full system comprising a CPU and a DSP, plus a bus and memories. This system is divided into functional blocks, such as registers, ALU, MAC, ... On top of that, the decomposition proposed by the authors is hierarchical, and apply to all features of the target. As far as efficiency is concerned, the authors want their model to be accurate, hence they decided to take into account logic

switching generated by instructions and data values. The blocks are grouped into two families: *bit-dependent* and *bit-independent* blocks, regarding if their consumption varies while input vector changes. The models used in the functional blocks are based on tabular form called Look-Up Tables (LUT) filled thanks to the model presented in equation (4). The final results gives an accuracy at about 9% of the real values.

Li and Henkel [14] build a model at a higher architectural level. Indeed, the system class targeted by their model is also a full system integrating a CPU, memories and even custom ASICs (representing peripherals), but in their model the CPU is a unique functional block. Other blocks are then main memory, caches and specific hardware. The models used for each of the units are purely analytical ones, based on architectural data found in the literature (number of row and columns for memory, ...), or behavioral data of the application (number of miss, ...).

Kim et al. [10] augment a cycle accurate simulator with an architectural power consumption model. The targeted system of their model is a CPU. The model proposed has the peculiarity to be a "recursive" architectural level model. The system is divided into functional units called micro-architectural blocks. What is interesting in their model is that the micro-architectural models can be subdivided in turn. The micro-architectural block consumption is defined by three components: load of the input capacitance, switching of the logic due to the switching of inputs and finally the leakage power. These data are stored in LUTs calculated off-line (the LUTs can be replaced by analytical models for example).

Wattch [1] is a power model integrated in SimpleScalar [2], a cycle accurate instruction set simulator. The modified SimpleScalar tracks the access to functional units to predict energy consumption of a CPU. The authors regroup the functional unit power model into four classes: array structures, CAM (Content Addressable Memory) structures, complex logic blocks and clocking. Array structures represents caches for example. CAM structures are part of TLBs (Translation Look-aside Buffer) or write queues. Complex logic blocks are ALU, FPU. Clocking represents the clock distribution tree. In each class, the consumption is estimated by a parameterized analytical model based on architectural parameters. As far as Wattch performances are concerned, it performs power estimation 1000 times faster than circuit level simulator with an error of only 10%.

SimplePower [22] works in the same way as SimpleScalar, by simulating the execution of each instruction in each pipeline stage of the CPU. From these information only activated functional blocks of the architectural model of SimplePower are called to estimate power. The simulator use a cache simulator, analytical models and LUT (Look-Up Tables) models to predict power consumption. These models are fed with input values and behavioral informations (ex: cache misses, ...). The resulting accuracy of this model is about 15% against transistor level simulation.

To conclude, architectural level power models are build to be flexible. In fact, the main aim of most of them is the reuse of part of the model between different target system. Indeed, there is no need to recreate an entirely new model for a new architecture, but to add, remove or modify existing functional blocks. Their goal is to be less complex than circuit-level models, and more accurate than instruction-level models. In this kind of model, every gate or transistor are not simulated, hence the model is less time-consuming, but the model take into account the specificity of certain part of the architecture by using different model for each functional unit of the system. Some of the models presented in this family are easily adaptable to our objectives of modelling the full platform, since they can be augmented to take into account the full system (CPU plus peripherals, memories, ...). This is the case of the first two examples of architectural model. In the examples cited here no measurement based models are present.

**Instruction-level models** Tiwari et al. [20, 21] model of power consumption estimation for a CPU (x86) is based on measurement. The power measurements are obtained by measuring the current drawn by the CPU with a digital ammeter. As this tool averages the values, simple measurement would have meant nothing. The method proposed by the authors gives a mean consumption value for each instruction by executing each one in a well sized loop and measuring the consumption of the overall application. The consumption is then divided by the number of instruction executed. The sum of instructions mean consumption does not reflect the effect of control logic switching between instructions. In order to take this into account, the authors proposed to characterize what they call inter-instruction consumption. To measure this, they proposed to renew the same experience with each combination of two instructions in the loops.

Once the consumption obtained, they subtract the amount of energy due to the instructions themselves, and then divide the rest by the number of instruction switch. In their approach, inter-instructions are symmetric. The main difficulty of this method is that the table of inter-instruction has a size of  $N^2$  (if N is the size of instruction set). The accuracy of their model is within 3% of the measured values.

Lee et al. [12] enhance the model described before on a DSP, by regrouping instructions into classes. Thus the complexity of the inter-instruction table falls under  $O(N^2)$ . The accuracy still stays under 10% of error.

Another work, from Steinke et al. [19], uses an ammeter to get the desired consumption on an ARM7TDMI. Their model is build thanks to linear regression with detailed instruction informations like the instruction, and its parameters (register number, register value, immediate value, ...). The error falls here under 2%.

The previous measurement procedure has an important drawback, which is its narrow frequency spectrum. The setup only allows them to get mean power consumption values. In this condition they loose peak power consumption. Russell and Jacome in [18] propose a solution that has a better temporal resolution. They use a digital oscilloscope (Lecroy LC534). Thanks to the temporal resolution enhancement, instruction power consumption are more precise. Indeed, Tiwari et al. are forced to measure consumption of the instruction repeated in a loop. But their measures include the consumption of the branch instruction too, neglected because it is executed only once in a huge loop. Russell and Jacome [18] use a trigger signal to only measure the consumption of the body of the loop (without the branch instruction). The resulting model proposed by the authors is based on a statistical method, a constant parameter model. The parameters of this model are the types of instructions. Experiments were made on an Intel i960 and the estimated values give about 8% of error.

Lee et al. [13] propose another solution to get rid of the inaccuracy of the measures based on statistics. Their technique is also based on a simple setup for measuring real power consumption on an existing target (CPU), and aimed at building an instruction-level model. What is different in their approach is the use of regression analysis. If applied correctly, their model allows to know even less architectural informations on the target system/processing unit and reach a good accuracy of 2.5%. In fact by applying the regression successively with each selected parameter, one does not have to know the underlying architecture because the parameter are not estimated from the hardware. The parameters are finer-grained than the previous proposition, since in this model takes into account the per pipeline stage cost of instructions.

All models here are centered on estimating CPU power consumption. Our interest is to estimate this consumption plus the consumption generated by the rest of the embedded system. System/Instruction level models would not allow this, our proposition will not be based at system level of granularity. But measurement are widely used at this level of abstraction, some of the building methods proposed here have the characteristics we are wanting of our methodology, simplicity, minimum architectural information.

To conclude, simulation and analytical model building methods are generally oriented for early stage VLSI design, before material production. Conversely measurement based method needs less information on the underlying material architecture. These last points drive us to propose a measurement based methodology, since at software development phase, all informations needed for simulation based method will not necessarily be available.

The second point is that the setup used for data acquisition in our methodology must not require electronic skills. Compared to all setup proposed in the literature we should use one of the simplest.

Finally, all system/instruction level models proposed before are centered on a CPU, and do not take into account peripherals. The whole system is then not modelled with these models. Some exceptions are present in the architecture level models. For example, Li et al. [14] propose a model in which CPU, memory and busses are different units. This model is closer to system-level modeling than the instruction-level ones.

### 3 A methodology for energy consumption model construction

As presented before, until now overall embedded system energy consumption model were proposed, but they are not based on simple data acquisition methods. Conversely simple acquisition method based models were proposed, but they are usually taking into account only a subset of the system, the CPU. We will propose in this report a methodology which is both using simple non-intrusive measurements and a model that is representing the whole embedded system. The aim of this methodology is to be simple and generic enough to be reproducible by software developpers on their hardware platform.

In this section, we will give details about this proposition of methodology for building an energy consumption model based on simple non-intrusive measurement. We will describe the measurement setup, we will give an overview of the measurement protocol and the data extraction. Finally we will say a few words about the setup validation.

#### 3.1 Measurement setup

First of all, it is necessary to remember what we have to measure exactly to know what our system is consuming. Basically, every electrical appliance power is given by the following formula:

$$P = IV (5)$$

Where I is the current drawn at input and V is the power supply voltage.

In fact we will be more interested by energy, since it represents the real cost in terms of electrical consumption. The definition of the energy is the following:

$$E = Pt (6)$$

where P is defined by formula (5) and t is the time.

These two definitions are correct if the current and the voltage are constants. This is exactly what Tiwari et al. [20] considered by using using human reading on an off-the shelf ammeter. It should not be the case on our target system, so current and voltage become functions of time i and v. On top of that, the process of data acquisition, that is to say physical measures induce that i and v will not be continuous, but in discrete time. We then have the new definitions:

$$p_j = i_j v_j \tag{7}$$

$$E = \int_{-\infty}^{t} p dt \approx \sum_{j=1}^{n_{samp}} p_j \Delta t_{samp}$$

(8)

Where  $\Delta t_{samp} = \frac{1}{f_{samp}}$  and  $f_{samp}$  is the sampling frequency.

In that condition, measurement will consists in sampling current and voltage. From these informations we can deduce the power and energy consumption of the system during the time of the experiment.

Now that we know what we have to measure, we must define where to take these measures.

The choice of measurement point is very important. In fact, this choice will have an influence on many other choices in the following steps. The most important thing is that it is tightly coupled with the informations we can/want to extract from the measures.

What we mean here is that if we want to measure the electrical consumption of the CPU, we would have better sampling the current and voltage at the power supply input of the CPU. This is a huge prerequisite, which is that it must be accessible and that you can instrument it for current sampling (voltage sampling is easier).

As we said before, we are not necessarily interested in very fine grained measures. On top of that we base this approach on non intrusive measures, because software developers often do not have time and skills to make this kind of measures. The better way to be non intrusive is to place our measurement point at the power supply input of the system.

More precisely, our approach is based on the whole system electrical consumption in order to closely fit to the real consumption of the studied system. This means that we should place at the point where the battery is fitted, since it is the only energy supplier in embedded systems.

This approach has an interesting advantage, since it allows the model generated to take into account the integration costs (in term of electrical consumption). We not only measure the consumption of the main chip containing the desired device, but of the components.

Finally, once we have chosen such a measurement point, we must select the measurement material, which will be used in the model building. There is only one contraint in this selection, which is that probes bandwidth and sampling frequencies must meet Shannon's law on target signal. If we still would like to have CPU electrical consumption and if our measurement point is placed at the power supply input of this CPU, we might probably have signals whose frequency is the CPU frequency. We would have then to select an acquisition material of which bandwidth is sufficient to acquire this signal.

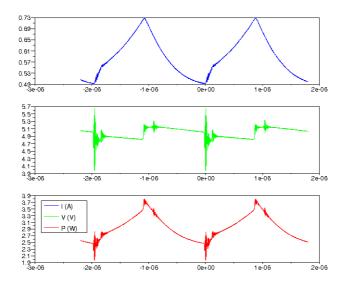

In the experiments depicted in section 4 we decided to sample current and voltage at the power supply input of the development board ARM Integrator CM922T-XA10. At this boards power supply input, we have the signal depicted by figure 5.

Figure 5: Sampled signals at 2.5G samples/s: We can observe that the sampled current and voltage present a frequency of 500kHz which is far away from the CPU frequency (198MHz)

The sampling rate for this figure is 2.5G samples per second. The frequency of the signal depicted is about 500kHz. The explanation for this is that the board current switching stabilizer has an operating frequencies of around 500kHz (as stated on the manufacturer's specifications). As a consequence, it is evident that we will not have cycle accurate energy consumption. In fact, the voltage stabilizer does not do a perfect job. Power variation are due both to events in the evaluation board and to the supply voltage variations. The latter effect must be averaged out of the measurements.

The second important fact is the duration of the measurement. In fact it can be limited by the hardware used for the acquisition. If it is the case, it will give an upper bound to the sampling rate. In our case there are two stabilizers. Their frequencies are slightly different *i.e.* about 2 or 3 kHz. The time of experience must then be sufficient to take this variation into account. We had to adjust the time window by modifying the sampling rate.

The resulting setup is the following. For current sampling, we selected an ampermetric clamp Tektronix P6021. As far as voltage sampling is concerned, we used a voltage probe Tektronix P6139A. Finally, the acquisition was made by a DPO (Digital Phosphor Oscilloscope) TDS 7054A series. This oscilloscope was only used as an acquisition device.

In terms of sampling frequencies, we finally used a 2.5M sample per second rate, which gives us a  $10^{-2}$  s time window thanks to its 250 000 sample memory.

#### 3.1.1 Protocol

Once the measurement setup is chosen, which means we have decided where and what will be measured and with what material, we have to organize our experiments in order to extract the information we are

interested in. Indeed, placing the measurement point at the power supply input, will certainly not allow us to get CPU cycle accurate measures.

As our main aim is to build a software electrical energy model, the events which will be the subjects of our measures will range from CPU instructions to operating system services. More details about those events will be given in section 3.3. What is important to underline here is that the duration of most of the target events will fall below the time accuracy of the setup.

To solve this problem, there are two solutions. The first will be to change the setup to collect measures closer to the CPU, for example. This solution is not acceptable, since this measurement point was chosen for reasons expressed above. The second solution is then to repeat each event a certain number of times, and average the energy consumption.

In this second solution, measurement experiments must meet a several requirements. We must know how many times the target event occurs during the measurement interval, we also need to know the exact duration of the experiment, and finally it is important that nothing else than the target event happens during the time window. All these requirements induce that we base the measurements on benchmarks raising each a different target event.

First of all, we have to know exactly how many times the event occurs during our measure in order to make a correct average. Indeed, supposing that we can calculate exactly the energy spent in the benchmark, we will have to divide this amount of energy by the number of occurrence to have the per event energy cost. The only way to get this information is to build the benchmark to execute the event a known-in-advance time. This number of repetition should be adapted to the acquisition window imposed by the measurement material. Two alternatives are available for implementation of the benchmark, the first would be a fully linear program containing the required number of events, or the implementation of a loop containing a submultiple of the number of event.

In our case, we select the second solution, since many embedded systems integrates caches, and then the loop implementation can take advantage of it, if the size of the loop is adapted to the cache geometry. In that situation, instruction cache misses will not pollute benchmarks results. The cost of the loop in time and power must be estimated and can be taken into account in the results extraction.

As we said above, the loop must be of the right size in order to eventualy take advantage of the instruction cache.

In fact, the loop body must be large enough to minimize the influence of the loop skeleton on the final results. It must also be smaller than the size of the instruction cache to avoid cache misses during the loop execution.

Other factors are important and must not be forgotten, which are cache loading of the loop. Indeed, this loading phase generates compulsory cache misses. The best way to get rid of these misses is to preload the loop body in the cache before starting the measurements. This is possible on some processors. The second solution is to minimize the influence of these misses on the measurement.

The influence of this second class of factors is opposed to the first class ones. The smaller the loop is, the less misses we have. The loop size choice is then a trade off problem.

To formalize this problem, we have to identify the two major components. Equations (9) and (10) give the number of occurences of each of these components  $n_{loop}$  and  $n_{misses}$ , against the total number of events in term of instruction  $n_{insn\_evt}$ , the loop size  $l_{loop}$ , and the cache line width in words  $w_{cache\_line}$ .

$$n_{loop} = \frac{n_{insn\_evt}}{l_{loop}} \tag{9}$$

$$n_{misses} = \frac{l_{loop}}{w_{cache\_line}} \tag{10}$$

Once these two amount are weighted by their cost we obtain the problem expressed by equation (11).

$$E = \frac{n_{insn\_evt}}{l_{loop}} \times c_{loop} + \frac{l_{loop}}{w_{cache\ line}} \times c_{miss}$$

(11)

where  $c_{loop}$  and  $c_{miss}$  are the costs of loop skeleton and cache misses. These two costs can be either time costs or energy costs. The most relevent one would be energy cost, but a first approximation can be

estimated thanks to time (cycles) informations, since time and energy consumption are correlated in this kind of problem.

The optimal value is hence obtained thanks to the solution given by (12):

$$l = \sqrt{\frac{n_{insn\_evt} \times c_{loop} \times w_{cache\_line}}{c_{miss}}}$$

$$l < \frac{s_{cache}}{w_{insn}}$$

(12)

$$l < \frac{s_{cache}}{w_{insn}} \tag{13}$$

(14)

where  $s_{cache}$  is the cache size in bytes and  $w_{insn}$  is the instruction width in bytes. For example, if we have a 8 word wide line cache of 8kB, with a  $c_{loop}$  of 4 cycles and a  $c_{miss}$  of 40 cycles, the optimal loop size is 2048, for 15000000 events.

To conclude on loop size choice, we must underline the fact that the estimation of number of misses is based on the fact that the number of misses is predictable. In fact it is a little simplistic in the previous problem, since in some associative caches the replacement policy is random. If we put two lines in the same set, the probability of the replacement of the previously loaded line is not zero, as it is for a round-robin replacement rule. The estimation of the number of misses should be adjusted to the level of associativity. The solution to get predictability in the benchmark with random replacement rule is to only use one line of each associative set. Such a restriction avoid a line to be replaced by a second load in this same set.

The final solution is then to use prefetching solution if they are available, or to minimize the misses influence by resolving the trade-off exposed before, with the predictability constraint.

As we mentioned above it is important to be able to calculate the energy consumption of the benchmark, and only it. We should thus know when the core of the benchmark starts and when it ends. These informations can be collected thanks to a trigger signal controlled by the benchmark itself. This trigger signal must change state just before the first iteration of the loop and after the last one. The interesting data can then be selected thanks to this third sampled signal.

The last benchmark requirement for accurate event cost measure is the control of what is running on the platform. Indeed, during the benchmark core loop, only the target event should happen. This means that the platform must be initialized in a way that deactivate all useless peripherals, and only the benchmark should run on the platform.

To conclude the measurement experiments are organized as follows: each event energy cost measure is the subject of a particular benchmark, whose task is to trigger this event a predefined number of time, using a loop.

For example, in our experiments on the Integrator CM922T-XA10, each cycle of the measured signal represents approximately the electrical consumption of 400 CPU cycles. CPU runs at a frequency of 198 MHz and the voltage stabilizers frequency is about 500 kHz.

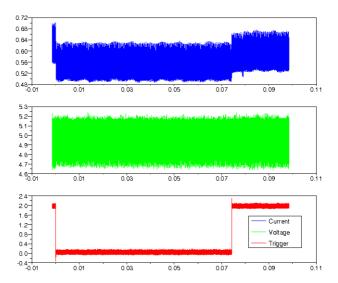

In the experiments on the CM922T-XA10 we opt for a LED as triggering signal. The benchmark turns it off just before the beginning of the loop, and on just after the last loop, the data acquired between these two fronts are relative to the energy spend in the benchmark. The interesting data can then be selected thanks to a third sampled signal. Figure 6 gives an overview of the acquired data (two upper graphs) and the trigger signal (lower graph). The payload data are present between the two state change of the trigger.

In order to have a full control of the platform, we use a lightweight operating system called Mutek [15]. At present, we only use hardware initialization of Mutek. OS initialization is replaced by the benchmark

As we explained in section 3.1, at the end of a data collection phase we have two series of measures, on current and on voltage. We also presented how we can extract power information from the data (7).

From this sampled power we can extract two different informations. The first is a mean power over the benchmark.

$$P = \frac{\sum_{i=1}^{n_{samp}} p_i}{n_{samp}} \tag{15}$$

where  $n_{samp}$  is the number of samples. Mean power gives us information about gate activity. This is an interesting information, but it does not allow us to have the real cost of an addition or a memory access.

Figure 6: Acquisition results: the two upper graphs are interesting data i and v, and the lower one is the trigger signal LED

The main reason is the heterogeneity in event lengths. In our case we want to know the cost in term of battery consumption.

We will work in energy rather. As we mentioned before it is given by equation (8). This equation gives the total energy consumed during the benchmark, this information is important, but should be normalized to give the event consumption. To do so, all we have to do is to normalize the energy by the number of event executed during the benchmark:

$$E_{evt} = \frac{E_{bench}}{n_{evt}} \tag{16}$$

where  $E_{evt}$  is our event energy cost,  $E_{bench}$  is the benchmark total energy and  $n_{evt}$  is the number of times our event happened during the benchmark.

If the loop skeleton cost is negligible, the previous result can be considered as the final result, but if it is not the case, we should subtract the cost of loops to the total energy of the benchmark.

The loop skeleton may be evaluated by an empty benchmark, and its cost  $E_{loop}$  may be calculated by the previous equation. Once this cost estimated, we can use the following equation for the other benchmarks:

$$E_{evt} = \frac{E_{bench} - E_{loopcost}}{n_{evt}} \tag{17}$$

where  $E_{loopcost} = E_{loop} \times n_{loop}$ , and  $E_{loop}$  is the cost of one loop cycle and  $n_{loop}$  is the number of loop executed in the benchmark.

This gives more accuracy to the value obtained.

#### 3.2 Measurement error verification

In order to validate the measurement setup, we have to estimate the error made on measures. The error will allow us to know the reachable precision in measures.

We make a measurement on both sampled signals, i and v. This error is modelled as follows:

$$i = i^{meas} + i^{err} \tag{18}$$

$$v = v^{meas} + v^{err} (19)$$

where i and v are real values,  $i^{meas}$  and  $v^{meas}$  are measured values and  $i^{err}$  and  $v^{err}$  are errors due to measurement setup.

If we put these new definitions of i and v in equation (7), we get the following result:

$$p_j = (i_j^{meas} + i_j^{err})(v_j^{meas} + v_j^{err})$$

$$(20)$$

By deduction, we can state that  $p_j^{meas}=i_j^{meas}v_j^{meas}$ . In that case we obtain the following error  $p_j^{err}$ :

$$p_i^{err} = i_i^{err} v_i^{meas} + i_i^{meas} v_i^{err} + i_i^{err} v_i^{err}$$

$$\tag{21}$$

The error made on power measures (equation (21)) can be then reported in the energy calculus defined by equation (8).

$$E_{bench} = \sum_{i=1}^{n_{samp}} \left( p_j^{meas} + p_j^{err} \right) * \Delta t_{samp}$$

(22)

As we did previously for power, we can state that  $E^{meas} = \sum_{j=1}^{n_{samp}} p_j^{meas} * \Delta t_{samp}$ . The error on total benchmark energy is then given by equation (23).

$$E^{err} = \sum_{j=1}^{n_{samp}} p_j^{err} * \Delta t_{samp}$$

(23)

The final step in information extraction is the normalization of the results at the event. This is made thanks to equation (16). In the same way, the error can be normalized. Then we obtain:

$$E_{evt}^{err} = \frac{E_{bench}^{err}}{n_{evt}} \tag{24}$$

In our particular case, the measurement error is bounded by the error made at quantization by the oscilloscope. Error of the ampermetric clamp and the voltage probe are negligible in respect to the error made by the oscilloscope Analog-to-Digital Converter (ADC). According to the adjustments of the oscilloscope, we obtain the following errors on each channel:

As far as current is concerned, we convert every measure of 2A into a range of 16bits. The quantization error is then:

$$i^{err} = \pm \frac{2}{216} = \pm 3.052 \, 10^{-5} A$$

Voltage error calculus is very close, since we have 10V converted on binary values on 16bits. He have then:

$$v^{err} = \pm \frac{10}{216} = \pm 1.526 \, 10^{-4} V$$

To validate the measures taken during our benchmarks, we computed their error. The resulting conclusion is that we have a good accuracy. For example, on a benchmark which aim is to give us the consumption of a load instruction, the energy cost found is  $1.242761\ 10^{-08}\ J$  and the measurement error is equal to  $1.154064\ 10^{-12}\ J$ .

#### 3.3 Model structure and parameters

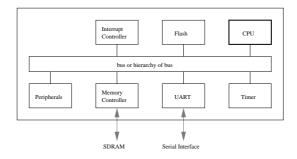

Our choice among all the modeling method which have been presented in Sect. 2.2.3 is to build an architecture level model, in which the platform is divided in functional blocks, as in figure 7.

The energy consumption of an application  $E_{\rm app}$  is obtained be adding the all blocks consumptions  $E_{\rm bl}$ :

$$E_{\rm app} = \sum_{blacks} E_{\rm bl} \tag{25}$$

Figure 7: model block examples

Each block can have its own energy consumption model. To have a platform model better suited for software development, we apply the instruction level model solution for CPU modeling. The CPU energy consumption  $E_{\mathrm{CPU}}$  is thus model as described in the next equation.

$$E_{\rm CPU} = E_{\rm insn} + E_{\rm cache} + E_{\rm MMU} \tag{26}$$

The energy consumption is the sum of the energy consumed by instruction execution, plus cache and MMU overheads consumptions, and consumption of the other blocks of the platform.

$$E_{\rm app} = E_{\rm CPU} + \sum_{blocks} E_{\rm bl} \tag{27}$$

This model aims at being integrated in a cycle accurate simulation tool of the complete platform. The most interesting way of writing the model for this kind of purpose is to define a per time slot energy consumption. The chosen time slot is the CPU instruction execution. There are two reason for choosing this time reference. The first is that it is the finest time reference since CPU have generally the highest clock frequency in embedded systems. Secondly, interrupt requests, the only mean for the hardware peripherals to interact with the software, are managed at the end (or beginning) of the instruction execution. From a software point of view, there is no need to use a finer time reference to report hardware events more precisely.

The model can be rewritten in a form where the consumption of CPU and other blocks are reported for the currently executed instruction. All  $E_*$  will be kept for overall application consumptions, for the sake of notation simplicity instruction reported consumptions will be noted as  $\mathcal{E}_*$ . This new model formula is expressed in the following equation:

$$\mathcal{E}_{\text{slot}} = \mathcal{E}_{\text{CPU}} + \sum_{blocks} \mathcal{E}_{\text{bl}}$$

(28)

$$E_{\rm app} = \sum_{insn} \mathcal{E}_{slot} \tag{29}$$

(30)

The last peculiarity in this model is the measurement based data collection. As we only get global measures for the platform consumption, we can foresee that the base consumptions of every blocks will not be easily distinguishable. We mean here that once the embedded system is put in its laziest state, idle state for example with all possible units powered off, the resulting consumption is considered as a base consumption regrouping the base consumption of every powered peripherals. Obviously, a part of this consumption is static power dissipation. We will call this term  $\mathcal{E}_{\mathrm{base}}$ , it is important to note that this consumption is reported to the current executed instrustion on the CPU. It can be expressed as in equation (32), as it is dependent on the instruction length  $l_{insn}$ . Equation (28) becomes equation (31).

$$\mathcal{E}_{slot} = \mathcal{E}_{base} + \mathcal{E}_{CPU} + \sum \mathcal{E}_{bl}$$

(31)

$\mathcal{E}_{base} = l_{insn} \times \mathcal{E}_{c\_base}$  (32)

$$\mathcal{E}_{\text{base}} = l_{insn} \times \mathcal{E}_{\text{c base}}$$

(32)

The CPU and other blocks consumption are then expressed as overhead against the idle state.

As described in equation (26), CPU energy consumption is given by the executed instruction energy cost. This model can be simplified by regrouping instructions in classes as proposed in [12].

As far as other blocks are concerned, we can expand them as bus, memories and other peripherals. This is interesting since bus and memories will be subject to events generated by the processor, such as memory writes. The peripherals will be then modeled by state machines giving the energy consumption of the peripheral during the time slot.

The last step in model construction consists in defining all possible parameters for these components. Due to the limited information available, the developers would not necessarily know the behavior of intrablocks logic. The parameters for the CPU are already selected, since it is modeled thanks to instructions consumptions. The same can be done for cache, MMU and even co-processors consumptions. The parameters for other blocks are limited to behavioral parameters (UART sending a byte) and their states such as operating mode (running, stopped).

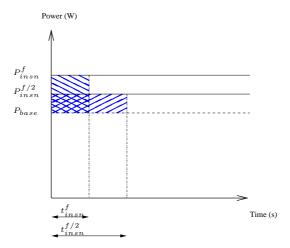

Each energy cost in this model is function of the running frequency and power supply voltage to allow dynamic and frequency scaling capabilities of the platform to be modeled. An example of this is presented in the next section.

## 4 Measurement results: experimentations on the ARM Integrator/CM 922T-XA10

In this section we will give more details about this methodology, by giving an example of application. As we said before, we applied this methodology on an ARM based platform, ARM Integrator CM922T-XA10. We will explain the architecture exploration procedure, give a few details about the benchmarks implementation and finally give the results of these measures.

#### 4.1 Architecture exploration

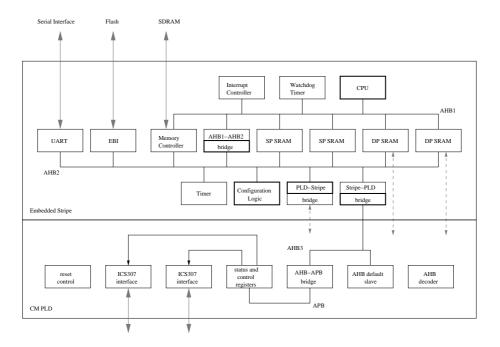

As the first step of the model construction consists in defining the model parameters, we have to explore the architecture of our platform to find clues about which events could be the most representatives of the energy consumption. We will give here a rapid overview of the hardware architecture, the interested reader could find for more details about it in [9]

As all Core Module (CM) sold by ARM, this CM is based on an ARM CPU, but this one is a little special since the ARM processor is in fact integrated in a FPGA (Field Programmable Gate Array), an Altera Excalibur EPXA10. With the CPU, few peripherals were integrated in the stripe, which means that they are placed in the chip along the FPGA. On top of that, some peripherals can be implemented in the FPGA, since there are bridges that allow communications between the stripe and the PLD (Programmable Logic Device), *i.e.* the peripherals placed in the FPGA.

The global architecture is depicted on figure 8. As we can see from this figure, the stripe has a two level bus architecture, where the second level could be connected to the PLD. As far as memory is concerned, there are different level of memories, with different access time. The first level is SP (single port) and DP (dual port) SRAM, which are static RAMs connected to the AHB (Advanced High-speed Bus). These RAMs are accessed with only one bus access cycle. Further, we have first level of SDRAM, accessible through the memory controller. This memory is accessed in a longer time since we access to the memory controller through the first level of bus, and then we access to the RAM chips by going out of the EPXA10 chip. A second level of SDRAM or SSRAM could be used by implementing a second memory controller in the FPGA, since SDRAM can be connected thanks to a DIMM connector or a SSRAM chip is integrated on the CM board. This second level will not be mentioned any further.

As we said before, our model is placed at the architectural level. At this level, we found the following blocks:

- CPU

- SP/DP SRAM

Figure 8: Basic image architecture. Bold blocks are bus masters

- busses (AHB1 and AHB2)

- ITC (Interrupt Controller)

- Timer

- Memory controller and SDRAM

This blocks enumeration gives us clues on the potential parameters of our model. In fact from the software point of view, some of the parameters becomes evidents. In fact, since ARM CPU's have a RISC architecture, all operations are from registers to registers except the load and store operations. In this situation, we can define two classes of instructions: load and store, and the second group all other instructions. To complete the coverage, we should add a third group, the co-processors operations.

Once we have made this first classification, we can easily imagine that the address of the load and stores will define the memory level of the access, and then define if we access to memories or memory mapped registers, through bus level 1 and level 2, and so on.

These different remarks are focused on the CPU and memories. On top of these two classes, we find peripherals. This class of blocks can have an autonomous operating mode. In that case their energy consumption should be modeled by finite state machines, since only access to their control registers can change their state.

The parameters selected after this architecture exploration are the following:

- CPU instructions of class 2.

- load/stores in cache

- · bus accesses

- main memory accesses

- Scratch Pad memory access

- peripherals states consumptions

On top of these informations, the architecture exploration reveals that this platform possesses an interesting feature. The PLL (Phase-locked loop) of the clock signal generation is programmable by the mean of a control register. Unfortunately, there is no possibility of adjusting the supply voltage.

#### 4.2 Benchmarks construction

Once every possible parameters are listed, we have to measure their cost. As described before, we build benchmarks for each of the parameters.

The procedure is the same as the one depicted in section 3.1.1, which means that we generate the targeted events a predefined number of occurrence thanks to a loop.

ARM922T, the CPU embedded in the EPXA10, has caches. Theses caches are separated 8kB data and instruction caches. They are 4 way set associative with 8-words wide lines, which means that they have 64 sets of 4 lines. The instruction cache of the ARM 922T allows prefetching. We used this feature in the benchmark implementation. The second point concerns the replacement rule in the associative sets. Two rules are available, random and round robin. As we mentioned in section 3.1.1, the most predictable rule is round-robin, but we kept the possibility of testing the random one by using only one line per set. Then as far as the loop sizing is concerned, we selected a 512 instructions loop body, since it is the size of the direct mapped cache (we are using one line of each set).

Most of the events could not be measured directly, which means that we cannot build a benchmark that makes this event and only this one to occur. By measuring two series of benchmark's consumption, one causing the event and the other not, we can determine the consumption increase due to the event. For example, to estimate the memory access overhead, we should run benchmarks that load or store in memory cached and not cached. Then the CPU executes the same instruction in the two tests, but one generates a memory access and not the other. The difference in energy consumption represents the overhead of a memory access.

Here is a short list of benchmarks that were built, and their target event:

- insn-XXX: This benchmark allows us to compare different instructions executed in the CPU. (add, mul, mov, ...). It is only executing the instruction in the loop.

- Dcache-access: With this benchmark we can get the ldr/str instruction cost. It is accessing a cached memory address. Then all the access read or writes in a memory cell in the D-cache.

- AHB1-reg-write: This one gives the bus access (level 1) overhead. We write in a peripheral register a value that has no effect on the preipheral. The register must be accessible through the first level of bus. For example, we use ITC register (see figure 8).

- AHB2-access: Like the previous, this one is giving a bus access (level 2) overhead. In that case, the benchmark is working like the previous one, but with a register accessible through the second level of bus. For example, we use timer register (see figure 8).

- mem-access: To get data memory access overhead with this benchmark, we desactivate D-cache. Indeed, all load or store instructions access the main memory.

- spm-access: The aim of this benchmake is to get data scratch pad memory overhead. To have this result, we access scratch pad addresses instead of main memory addresses. The D-cache is desactivated. Every memory access is then made on the SP-SRAM (see figure 8).

- timer-test: As an example of peripherals energy characterization, this benchmark allows us to get running/stopped timer consumption. It is subdivided into two benchmarks, one in which the timer is stopped and the second in which the timer is running. The structure of the loop is the same as the insn-cmp benchmark with a nop instruction, since it is the instruction generating the less activity.

- loop-calibration: Finally, this benchmark is the one which gives loop skeleton overhead. By running an empty loop benchmark, we can estimate the loop overhead.

On top of these various benchmarks, which correspond to most of the parameters events, they all have parameters that allow us to estimate the remaining parameters of the model. Then all benchmarks can be run at different frequencies. As we mentioned before, frequency and voltage scaling are potential parameters of the model, and our tested platform only allows us to modify frequency. However, we can extrapolate our results to a platform with Dynamic Voltage Scaling (DVS) by assuming that the supply voltage can be scaled down in proportion to the clock frequency, which is a reasonable approximation if far away from the threshold voltage.

#### 4.3 Measures and model adaptation

| bench name          | length | energy (nJ) | error_meas (pJ) | error_stdev (pJ) | p_mean (W) |

|---------------------|--------|-------------|-----------------|------------------|------------|

| loop-calibration    | 4      | 69.084      | 5.1777          | 20.338           | 3.421      |

| insn-nop            | 1      | 16.747      | 1.2884          | 6.1914           | 3.317      |

| insn-add            | 1      | 16.762      | 1.2889          | 3.0943           | 3.319      |

| insn-and            | 1      | 16.769      | 1.2892          | 6.2788           | 3.32       |

| insn-mov            | 1      | 16.76       | 1.2889          | 5.1092           | 3.319      |

| insn-lsr            | 1      | 16.764      | 1.289           | 6.4375           | 3.32       |

| insn-mul            | 3      | 50.378      | 3.8494          | 20.599           | 3.327      |

| AHB1-access         | 6      | 101.33      | 7.7132          | 154              | 3.347      |

| AHB2-access         | 18     | 300         | 22.998          | 542.9            | 3.304      |

| timer-test_on(nop)  | 1      | 16.754      | 1.285           | 27.298           | 3.298      |

| timer-test_off(nop) | 1      | 16.732      | 1.2857          | 6.0922           | 3.3        |

| Dcache-access_ldr   | 1      | 17.146      | 1.3007          | 5.942            | 3.397      |

| Dcache-access_str   | 2      | 34.341      | 2.603           | 13.381           | 3.4        |

| mem-access_ldr      | 40     | 775.44      | 54.551          | 171.04           | 3.818      |

| mem-access_str      | 28     | 543         | 38.296          | 231.29           | 3.801      |

| spm-access_ldr      | 8      | 131.72      | 10.168          | 38.48            | 3.259      |

| spm-access_str      | 7      | 115.37      | 8.9021          | 21.916           | 3.263      |

Table 1: Results of benchmarks

| bench name        | energy w/ prefetch (nJ) | energy wo/ prefetch (nJ) |

|-------------------|-------------------------|--------------------------|

| loop-calibration  | 69.084                  | 67.925                   |

| insn-nop          | 16.747                  | 17.309                   |

| insn-add          | 16.762                  | 17.307                   |

| insn-and          | 16.769                  | 17.315                   |

| insn-mov          | 16.76                   | 17.307                   |

| insn-lsr          | 16.764                  | 17.314                   |

| insn-mul          | 50.378                  | 51.967                   |

| AHB1-access       | 101.33                  | 101.49                   |

| AHB2-access       | 300                     | 300.45                   |

| Dcache-access_ldr | 17.146                  | 17.66                    |

| Dcache-access_str | 34.341                  | 35.364                   |

| mem-access_ldr    | 775.44                  | 775.29                   |

| mem-access_str    | 543                     | 543.08                   |

| spm-access_ldr    | 131.72                  | 135.82                   |

| spm-access_str    | 115.37                  | 118.79                   |

Table 2: Results of benchmarks: influence of prefetch

The results summarized in table 1 allows us to draw the following conclusions. First of all, we can conclude that the type of instruction does not matter as far as it is not a data access or it does not misses in instruction cache. This conclusion is underlined by the results of insn-XXX benchmark. We should note

| bench name         | length | energy (nJ) | error_meas (pJ) | error_stdev (pJ) | p_mean (W) |

|--------------------|--------|-------------|-----------------|------------------|------------|

| loop-calibration   | 4      | 69.084      | 5.1777          | 20.338           | 3.421      |

| loop-calibration-H | 4      | 114.08      | 9.6173          | 162.21           | 2.822      |

| loop-calibration-Q | 4      | 201.4       | 18.418          | 211.53           | 2.49       |

| loop-calibration-E | 4      | 376.22      | 36.029          | 930.49           | 2.329      |

| loop-calibration-S | 4      | 724.58      | 71.213          | 450.41           | 2.244      |

| insn-nop           | 1      | 16.747      | 1.2884          | 6.1914           | 3.317      |

| insn-nop-H         | 1      | 27.422      | 2.3924          | 24.747           | 2.717      |

| insn-nop-Q         | 1      | 48.638      | 4.5942          | 44.488           | 2.407      |

| insn-nop-E         | 1      | 90.792      | 8.9897          | 87.111           | 2.247      |

| insn-nop-S         | 1      | 174.93      | 17.776          | 115.9            | 2.164      |

| insn-mul           | 3      | 50.378      | 3.8494          | 20.599           | 3.327      |

| insn-mul-H         | 3      | 82.482      | 7.1462          | 97.676           | 2.723      |

| insn-mul-Q         | 3      | 145.81      | 13.707          | 145.18           | 2.405      |

| insn-mul-E         | 3      | 272.07      | 26.818          | 245.46           | 2.245      |

| insn-mul-S         | 3      | 524.32      | 53.034          | 120.3            | 2.162      |

| AHB1-access        | 6      | 101.33      | 7.7132          | 154              | 3.347      |

| AHB1-access-H      | 6      | 169.97      | 14.426          | 161.89           | 2.803      |

| AHB1-access-Q      | 6      | 303.26      | 27.733          | 389.56           | 2.5        |

| AHB1-access-E      | 6      | 568.79      | 54.319          | 390.06           | 2.347      |

| AHB1-access-S      | 6      | 1098.2      | 107.44          | 774.36           | 2.263      |

| AHB2-access        | 18     | 300         | 22.998          | 542.9            | 3.304      |

| AHB2-access-H      | 18     | 505.74      | 43.068          | 522.74           | 2.781      |

| AHB2-access-Q      | 18     | 905.39      | 82.903          | 823.1            | 2.489      |

| AHB2-access-E      | 18     | 1702.8      | 162.52          | 3224.9           | 2.337      |

| AHB2-access-S      | 18     | 3289.2      | 321.5           | 1203.4           | 2.26       |

Table 3: Results of benchmarks at different frequencies: H means half speed, Q quarter, E eighth and S sixteenth. These ratio are given according to reference clock speed of 198MHz