#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

#### 공학박사 학위논문

## DRAM-based Processing-in-Memory Microarchitectures for Memory-intensive Machine Learning Applications

메모리 집약적 기계학습 응용프로그램을 위한 디램 기반 프로세싱 인 메모리 마이크로아키텍처

2022년 2월

서울대학교 융합과학기술대학원 융합과학부 지능형융합시스템전공 김 병 호

## DRAM-based Processing-in-Memory Microarchitectures for Memory-intensive Machine Learning Applications

#### 지도교수 안정호

이 논문을 공학박사 학위논문으로 제출함 2022년 1월

서울대학교 융합과학기술대학원 융합과학부 지능형융합시스템전공

#### 김 병호

김병호의 공학박사 학위논문을 인준함 2021년 12월

| 위 뒤 | 원 장: | 이 원 종 | (인) |

|-----|------|-------|-----|

| 부위  | 원장:  | 안 정 호 | (인) |

| 위   | 원:   | 김 동 준 | (인) |

| 위   | 원:   | 유 민 수 | (인) |

| 위   | 원:   | 이 석 한 | (인) |

#### **Abstract**

# DRAM-based Processing-in-Memory Microarchitectures for Memory-intensive Machine Learning Applications

Byeongho Kim

Intelligence Systems

Department of Transdisciplinary Studies

The Graduate School

Seoul National University

Recently, as research on neural networks has gained significant traction, a number of memory-intensive neural network models such as recurrent neural network (RNN) models and recommendation models are introduced to process various tasks. RNN models and recommendation models spend most of their execution time processing matrix-vector multiplication (MV-mul) and processing embedding layers, respectively. A fundamental primitive of embedding layers, tensor gather-and-reduction (GnR), gathers embedding vectors and then reduces them to a new embedding vector. Because the matrices in RNNs and the embedding tables in recommendation models have poor

reusability and the ever–increasing sizes of the matrices and the embedding tables become too large to fit in the on–chip storage of devices, the performance and energy efficiency of MV–mul and GnR are determined by those of main–memory DRAM. Therefore, computing these operations within DRAM draws significant attention.

In this dissertation, we first propose a main-memory architecture called MViD, which performs MV-mul by placing MAC units inside DRAM banks. For higher computational efficiency, we use a sparse matrix format and exploit quantization. Because of the limited power budget for DRAM devices, we implement the MAC units only on a portion of the DRAM banks. We architect MViD to slow down or pause MV-mul for concurrently processing memory requests from processors while satisfying the limited power budget. Our results show that MViD provides 7.2× higher throughput compared to the baseline system with four DRAM ranks (performing MV-mul in a chip-multiprocessor) while running inference of Deep Speech 2 with a memory-intensive workload.

Then we propose TRiM, an NDP architecture for accelerating recommendation systems. Based on the observation that the DRAM datapath has a hierarchical tree structure, TRiM augments the DRAM datapath with "in-DRAM" reduction units at the DDR4/5 rank/bank-group/bank level. We modify the interface of DRAM to provide commands effectively to multiple reduction units running in parallel. We also propose a host-side architecture with hot embedding-vector replication to alleviate the load imbalance that arises across the reduction units. An optimal TRiM design based on DDR5 achieves up to a 7.7× and 3.9× speedup and reduces by 55% and 50% the energy con-

sumption of the embedding vector gather and reduction over the baseline and

the state-of-the-art NDP architecture with minimal area overhead equivalent

to 2.66% of DRAM chips.

keywords: Processing-in-Memory architecture, Near-data processing, In-

DRAM processing, Memory microarchitecture, Memory-intensive

student number: 2017-22676

iii

### Contents

| Αŀ | ostrac  | et                                                             | i    |

|----|---------|----------------------------------------------------------------|------|

| Co | onten   | ts                                                             | iv   |

| Li | st of   | Tables                                                         | vii  |

| Li | st of I | Figures                                                        | viii |

| 1  | Intro   | oduction                                                       | 1    |

|    | 1.1     | Accelerating RNNs on Edge                                      | 3    |

|    | 1.2     | Accelerating Recommendation Model                              | 5    |

|    | 1.3     | Research Contributions                                         | 8    |

|    | 1.4     | Outline                                                        | 9    |

| 2  | Bacl    | kground                                                        | 11   |

|    | 2.1     | Memory-intensive Machine Learning Applications                 | 11   |

|    | 2.2     | DRAM Organization and Operations                               | 13   |

| 3  | MV      | iD: Sparse Matrix-Vector Multiplication in Mobile DRAM for Ac- | -    |

|    | cele    | rating Recurrent Neural Networks                               | 18   |

|    | 3.1     | Background and Motivation                                      | 18   |

|   |     | 3.1.1    | Energy-efficient RNN Mobile Inference                    | 18       |

|---|-----|----------|----------------------------------------------------------|----------|

|   |     | 3.1.2    | How to Improve the Energy Efficiency and Bandwidth of    |          |

|   |     |          | DRAM Accesses in MV-mul                                  | 21       |

|   | 3.2 | MV-r     | mul in DRAM                                              | 23       |

|   |     | 3.2.1    | Exploiting Quantization and Sparsity in RNN's Matrix     |          |

|   |     |          | Elements                                                 | 23       |

|   |     | 3.2.2    | The Operation Sequence of MV-mul in DRAM                 | 27       |

|   |     | 3.2.3    | Concurrently Serving Requests from Processors and Per-   |          |

|   |     |          | forming MV-mul in DRAM                                   | 32       |

|   |     | 3.2.4    | Put It All Together: MViD Architecture                   | 37       |

|   |     | 3.2.5    | Additional Optimization Schemes                          | 38       |

|   | 3.3 | Evalua   | ation                                                    | 39       |

|   |     | 3.3.1    | Power/Area/Timing Analysis                               | 39       |

|   |     | 3.3.2    | Performance/Energy Evaluation                            | 42       |

|   | 3.4 | Discus   | ssion                                                    | 48       |

| 4 | TRi | M: Enl   | hancing Processor-Memory Interfaces with Scalable Tensor | <u>.</u> |

|   | Red | uction i | n Memory                                                 | 51       |

|   | 4.1 | Prior    | NDP architectures for accelerating Tensor Gather-and-    |          |

|   |     | Reduc    | etion                                                    | 51       |

|   |     | 4.1.1    | Tensor Gather-and-Reduction in RecSys                    | 51       |

|   |     | 4.1.2    | Prior NDP accelerators for GnR                           | 52       |

|   |     | 4.1.3    | Quantitative Analysis                                    | 56       |

|   |     | 4.1.4    | Additional Schemes for Accelerating GnR                  | 58       |

|   | 4.2 | Tenso    | r Reduction in Memory                                    | 58       |

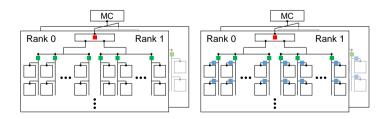

|    |               | 4.2.1  | Basic Concept for TRiM                     | 59 |

|----|---------------|--------|--------------------------------------------|----|

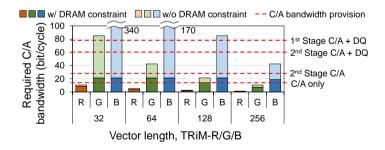

|    |               | 4.2.2  | How to Provision C/A Bandwidth             | 62 |

|    |               | 4.2.3  | Exploring NDP Unit Placement               | 65 |

|    |               | 4.2.4  | TRiM-G Organization and Operations         | 68 |

|    |               | 4.2.5  | Host-side Architecture for TRiM            | 70 |

|    |               | 4.2.6  | Schemes for Improving Reliability          | 75 |

|    | 4.3           | Exper  | imental Setup                              | 76 |

|    | 4.4           | Evalua | ation                                      | 77 |

|    |               | 4.4.1  | Performance and Energy Efficiency          | 79 |

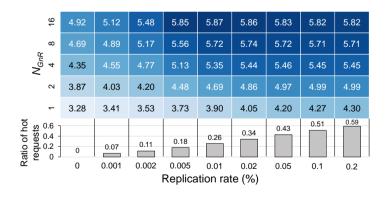

|    |               | 4.4.2  | Sensitivity Study of Hot-entry Replication | 82 |

|    |               | 4.4.3  | Design Overhead                            | 82 |

|    | 4.5           | Discus | ssion                                      | 83 |

| 5  | Disc          | ussion |                                            | 86 |

| 6  | Rela          | ted wo | rk                                         | 89 |

| 7  | Conclusion 9  |        |                                            | 92 |

| RE | REFERENCES 94 |        |                                            |    |

| 국  | 국문초록 117      |        |                                            |    |

## List of Tables

| 3.1 | Energy/area/timing of MViD components                    | 39 |

|-----|----------------------------------------------------------|----|

| 3.2 | Default simulation parameters                            | 42 |

| 4.1 | Timing/energy parameters of 16Gb DDR5-4800 ×8 DRAM chips |    |

|     | and NDP units.                                           | 76 |

## List of Figures

| 1.1 | Simplified architecture of a RecSys model                            | 6  |

|-----|----------------------------------------------------------------------|----|

| 2.1 | Roofline model for four arithmetic operations                        | 12 |

| 2.2 | Simplified DRAM datapath and module organization of DDR5             |    |

|     | DRAM                                                                 | 14 |

| 3.1 | The FLOP and execution time breakdown of Deep Speech 2               | 19 |

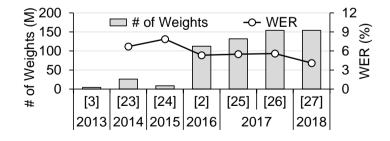

| 3.2 | The aggregate size of weight matrices and word error rate (WER)      |    |

|     | of representative ASR models over time                               | 19 |

| 3.3 | Distribution of the distance between two adjacent non-zero val-      |    |

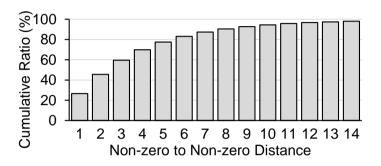

|     | ues (NZs) in the matrices of GRU layers (75% sparsity) in Deep       |    |

|     | Speech 2                                                             | 24 |

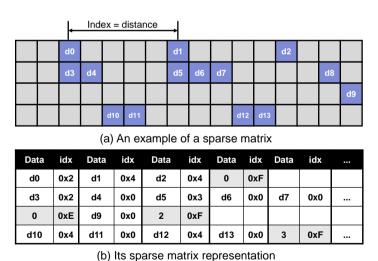

| 3.4 | An exemplary sparse matrix and its representation using the delta    |    |

|     | encoding format.                                                     | 24 |

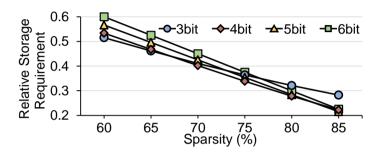

| 3.5 | The storage requirement for a matrix with different index bits       |    |

|     | when using delta encoding format                                     | 26 |

| 3.6 | The relative size of the tested matrices encoded with various sparse |    |

|     | matrix formats normalized to the size of the dense format            | 26 |

| 3.7  | Mapping of the weight matrix to DRAM reads and pipeline stages |    |

|------|----------------------------------------------------------------|----|

|      | for Single-Row per Read.                                       | 30 |

| 3.8  | The MViD architecture                                          | 37 |

| 3.9  | The breakdown of LPDDR4 peak power and MViD power con-         |    |

|      | sumption                                                       | 40 |

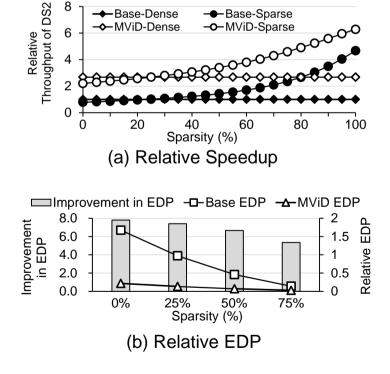

| 3.10 | The impacts of MViD on DS2 in performance and energy-delay     |    |

|      | product (EDP).                                                 | 44 |

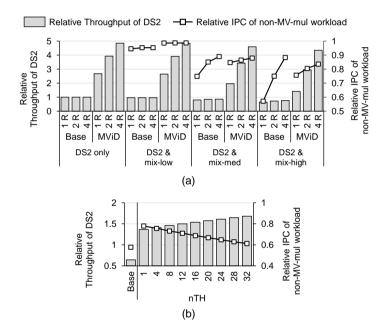

| 3.11 | The impacts of MViD when DS2 is running solely or with non-    |    |

|      | MV-mul workloads                                               | 45 |

| 3.12 | The impacts of bank partitioning when DS2 is running with non- |    |

|      | MV-mul workloads (mix-high)                                    | 48 |

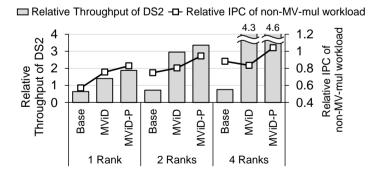

| 3.13 | The impacts of one-rank MViD on MV-mul by changing the         |    |

|      | size of the weight matrix                                      | 49 |

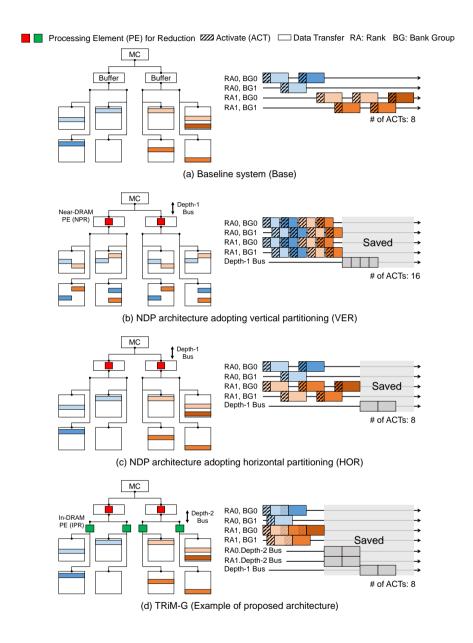

| 4.1  | Exemplar GnR in the baseline and the evaluated NDP architec-   |    |

|      | tures                                                          | 53 |

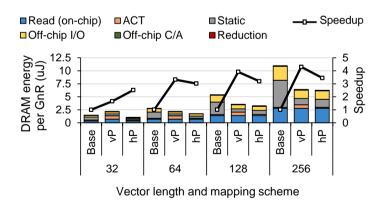

| 4.2  | Speedup and DRAM energy breakdown of baseline system and       |    |

|      | the state-of-the-art NDP accelerators when performing GnR      | 54 |

| 4.3  | High-level overview of TRiM-G/B                                | 59 |

| 4.4  | Various methods for transferring C-instr to the memory node in |    |

|      | the TRiM architecture                                          | 62 |

| 4.5  | C/A bandwidth requirement to utilize all memory nodes for each |    |

|      | TRiM architecture and bandwidth provision for each method of   |    |

|      | transferring C-instr                                           | 64 |

| 4.6  | Heatmaps showing the speedup of TRiM-R/G/B over baseline          |    |

|------|-------------------------------------------------------------------|----|

|      | system                                                            | 66 |

| 4.7  | Overall architecture of TRiM-G                                    | 69 |

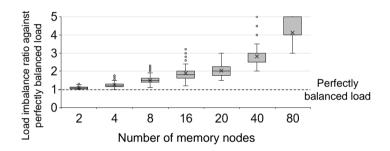

| 4.8  | Distribution of the load imbalance ratio                          | 71 |

| 4.9  | Execution flow of lookup request distribution through hot-entry   |    |

|      | replication                                                       | 71 |

| 4.10 | An overall execution flow of the lookup requests on the host-     |    |

|      | side                                                              | 73 |

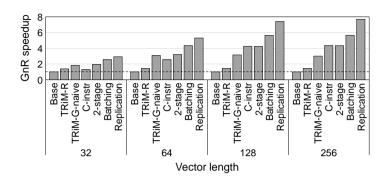

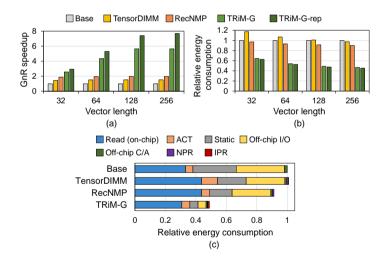

| 4.11 | The GnR speedup of the TRiM architectures                         | 78 |

| 4.12 | GnR speedup and relative DRAM energy consumption of the           |    |

|      | baseline system and the TRiM architectures, and energy con-       |    |

|      | sumption breakdown of TRiM-G                                      | 78 |

| 4.13 | Speedup of TRiM-G over the baseline system with various $p_{hot}$ |    |

|      | and $N_{GnR}$ values                                              | 81 |

#### Chapter 1

#### Introduction

Deep neural networks (DNNs) are widely used due to their significant impact [36]. A wide range of tasks can be handled by DNNs, from image classification [47] and speech recognition [8] to personalized recommendations [123] and graph processing [70]. To handle these tasks, various DNN models are used, such as convolutional neural network (CNN) [71], recurrent neural network (RNN) [19], transformer—based models [114], and recommendation models (RMs) [90].

The computational characteristic of a neural network model is determined by that of the layers composing the model. Convolutional (CONV) layer and attention layer from transformer have high reuse of data which is stored in onchip storage of a system [15,53]. These layers show compute–intensive property with high operational intensity, which represents a large amount of computation compared to the number of off–chip accesses. By contrast, the activa–

This chapter is based on [65, 66, 99].

<sup>©2020</sup> IEEE. Reprinted, with permission, from Byeongho Kim, Jongwook Chung, Eojin Lee, Wonkyung Jung, Sunjung Lee, Jaewan Choi, Jaehyun Park, Minbok Wi, Sukhan Lee, and Jung Ho Ahn, "MViD: Sparse Matrix-Vector Multiplication in Mobile DRAM for Accelerating Recurrent Neural Networks," IEEE Transactions on Computers, April 2020.

<sup>&</sup>quot;TRiM: Enhancing Processor-Memory Interfaces with Scalable Tensor Reduction in Memory" © 2021 by Byeongho Kim, Jaehyun Park, Eojin Lee, Minsoo Rhu, and Jung Ho Ahn is licensed under CC BY 4.0. https://doi.org/10.1145/3466752.3480080.

<sup>&</sup>quot;TRiM: Tensor Reduction in Memory" ©2020 by Jaehyun Park, Byeongho Kim, Sungmin Yun, Eojin Lee, Minsoo Rhu, and Jung Ho Ahn is licensed under CC BY 4.0. https://doi.org/10.1109/LCA.2020.3042805.

tion layer (e.g., ReLU), batch normalization layer, and embedding layer show memory–intensive property with low data locality, exhibiting low operational intensity [61,63].

The computational characteristic of a layer may vary depending on the use case of the network model. For example, when models composed of RNN layers or FC layers are running with a small batch size for real-time inference, the layers show memory-intensive behavior as weight matrices are hardly reused. However, when a large batch is used for training, the layers exhibit compute-intensive characteristics as input data and weight matrices are highly reused [33].

Due to the memory wall problem [119], the increase in main-memory bandwidth is relatively low compared to that in the computational power of the microprocessor within the same period [85]. Therefore, the performance improvement of the memory-intensive layers is lower than that of the compute-intensive layers, which necessitates the solution for accelerating the memory-intensive layers.

In this dissertation, we propose two processing—in—memory architectures to accelerate memory—intensive layers and models. By locating the process—ing elements near the DRAM datapath, processing elements can operate inde—pendently. Thus the PIM architectures can utilize expanded internal memory bandwidth the same as the channel bandwidth multiplied by the number of processing elements. With the ample internal bandwidth provided by the PIM architectures, memory—intensive layers can be accelerated. To further accelerate the PIM architectures, we apply optimizations that exploit the characteristics of models' use cases and their workloads.

#### 1.1 Accelerating RNNs on Edge

On edge devices such as mobile or IoT devices, Neural Networks (NNs) are frequently used for applications interacting with users. For example, Natural Language Processing (NLP) is widely used for devices such as Siri, Google Assistant, and Amazon Echo, and expected to become a key application in mobile in the near future. RNN [107] is crucial for NLP [8, 38]. Currently, edge devices typically rely on datacenters in performing a majority of RNN inference [33, 60, 124]. However, due to latency and energy burdens in transferring raw data for RNN inference over the networks, there is significant merit to perform RNN inference within the edge devices.

RNNs have many variants (e.g., LSTM [48] and GRU [20]), all of which spend most of the execution time for matrix-vector multiplication (MV-mul). A characteristic of MV-mul is that matrix elements, which correspond to weights in RNN, are used only once per vector, resulting in a limited degree of data reuse. The on-chip storage of edge devices, sized up to several megabytes (MB) [43], is typically too small to store all the weights whose sizes are reaching tens to hundreds of MB. Therefore, for each MV-mul, the matrix elements of RNN must be read from the main-memory DRAM. This is in sharp contrast to the characteristics of CNN, which has a high degree of data reuse for an input feature map while processing numerous weight channels [16].

When a matrix does not fit in on-chip memory, its MV-mul performance depends on DRAM bandwidth [33, 45, 60], which is much lower than the on-chip storage bandwidth of a processor. Also, in energy efficiency, the data transfer energy between a DRAM device and a processor dominates that of other

operation types (e.g., multiply–accumulate (MAC) operations) [49]. Thus, the performance and energy efficiency of RNN inference is determined by the band—width and energy efficiency (J/b) of main–memory DRAM.

To solve the memory bottleneck and reduce J/b of DRAM accesses, there have been many near-data processing studies [11, 30, 34, 50, 63, 68, 78, 110]. They reduced off-chip memory traffic by adding operation units or accelerators near main memory, either within a DRAM die or a logic layer of a 3D-stacked memory. However, they do not fully utilize the internal DRAM bandwidth or do not consider the power constraint of DRAM. Also, they cannot perform acceleration operations and other memory requests from processors simultaneously, so they hardly function as the main memory.

In this paper, we propose the MViD (MV-mul in DRAM) architecture, which can handle both MV-mul operations and memory requests from processors (processor requests) under the maximum power budget of DRAM devices which is determined by normal DRAM operations. MViD places MAC units near the datapath I/O within DRAM banks to improve the performance of MV-mul by utilizing abundant DRAM internal bandwidth. In particular, we analyze the operational limit due to the DRAM power constraint and confirm that MAC units can be added only to half of the banks for the current mobile DRAM standard, LPDDR4 [76].

To further reduce the total amount of computation, MViD performs a sparse MV-mul operation exploiting sparsity and quantization. Processing sparse MV-mul is actively studied in various ways depending on the characteristics of the matrix [45, 46, 104, 122], and its effectiveness depends on finding an appropriate sparse data format by understanding the characteristics of the matrix.

To find the optimum data format for MViD, we explore its design space by adjusting sparsity and quantization bits [45] of RNN weight matrices with—out accuracy loss. Also, we explore possible mappings of a weight matrix to a DRAM page.

MViD can act as the main memory by allowing other memory requests from a processor to be processed during MV-mul. MViD resolves the power and row-buffer conflicts that occur when MV-mul and processor-side requests are processed simultaneously by controlling the pace of MV-mul operation. For this, we implement MV-bank (bank performing MV-mul) control logic, which can slow down or pause the MV-mul operation. Also, MViD minimizes command/address path utilization overhead by leveraging the existing DRAM interface. MViD further improves the performance of MV-mul by placing the non-MV-mul workload data of the processor to the DRAM banks that do not perform MV-mul.

#### 1.2 Accelerating Recommendation Model

Personalized recommendation systems aim to provide the content preferred by users based on their experience. Companies such as Facebook [42], YouTube [21], and Alibaba [115] are applying deep learning to their recommendation systems to maximize the accuracy of selecting user–preferred content. Recommendation systems based on deep learning (RecSys) have recently gained significant attention within the research community due to their industrial importance. For instance, Facebook states that recommendation systems (e.g., the Deep Learning Recommendation Model (DLRM) [42]) account for 80% of the AI inference

cycles in their datacenters.

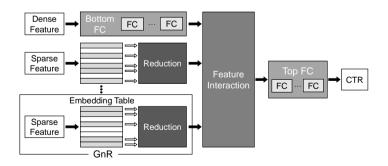

A RecSys model utilizes the features of the target user and item to predict the click—through—rate (CTR), which indicates the probability of the user click—ing the item (Figure 1.1). The input features consist of both sparse, categorical features and dense, continuous features. A dense feature is a vector whose elements are floating—point numbers. The vector is passed through bottom fully—connected (FC) layers and is collectively translated to one intermediate vector. A sparse feature is represented as a sequence of indices. A number of vectors are fetched from an embedding table using the indices of a sparse feature, which are subsequently reduced to one intermediate vector using element—wise oper—ations (henceforth referred to as tensor gather—and—reduction (GnR)). These intermediate vectors produced by GnR operations are combined through feature interaction, which is conducted by a batched matrix multiplication, and passed through top FC layers to produce a CTR.

Prior work [42] has shown that both FC layers and GnR take up a significant fraction of the end-to-end inference time of RecSys. While there have been

Figure 1.1: Simplified architecture of a RecSys model. We mainly target accelerating GnR (gather-and-reduction), which gathers embedding vectors from embedding tables and reduces them to produce one vector per table. FC and CTR stand for fully connected layer and click-through-rate.

numerous studies focusing on accelerating FC layers, only a handful of prior works have explored the acceleration of GnR, whose characteristics significantly differ from those of FC layers.

Because the embedding table used in RecSys requires a large memory capacity, the embedding table must be stored in main memory. The performance of the GnR operation is constrained by the main—memory bandwidth as the vectors for the GnR operation are fetched from main memory. Increasing the memory bandwidth in a memory channel accompanies an increase in the number of pins or the frequency of the pins, both of which are highly costly. Consequently, TensorDIMM [73] and RecNMP [63] are two recent studies that explored the efficacy of near—data processing (NDP) for accelerating GnR. These architectures accelerate the GnR operation by placing processing elements (PEs) dedicated to each rank (adopting rank—level parallelism) in the buffer chip of DRAM, thereby utilizing the internal bandwidth which is equal to the channel bandwidth multiplied by the number of ranks in the channel. However, we observe that rank—level parallelism does not fully reap the maximum potential of NDP acceleration, leaving significant performance left on the table.

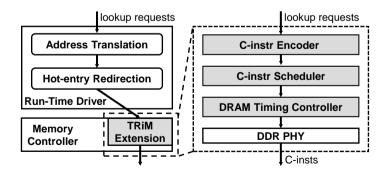

We propose an NDP-based GnR accelerator called the TRiM (Tensor Reduction in Memory) architecture, which is based on DDR4/5 DRAM. Our key approach is to utilize the hierarchical, tree topology of the DRAM datapath structure [23] to seamlessly extract additional internal bandwidth compared to rank-level-parallelism-based NDPs, improving the GnR performance. Compared to prior approaches, a key contribution of our study is the identification of effective embedding table mapping schemes when using multiple ranks/bank-groups/banks. In our work, we compare the internal bandwidth utilization

and energy efficiency in various mapping schemes. As with the existing DRAM interface, if command/address (C/A) signals are transferred only through the C/A path, we cannot fully utilize all PEs placed in/near the main-memory architecture. Therefore, we propose and analyze multiple C/A transfer schemes that can amplify the C/A signal bandwidth without significantly modifying the conventional DRAM interface. Among the embodiments of TRiM architectures, we find the optimal design that can effectively process GnR according to the workload characteristics.

Another important contribution is a detailed analysis of the load-imbalance issue that occurs when multiple ranks/bank-groups/banks process different numbers of lookups per GnR operation, a key limitation of NDP architectures including our design and RecNMP. To address this problem, we propose hotentry replication by utilizing the workload characteristic according to which the number of accesses is skewed to a small fraction of entries in the embedding table in RecSys. This scheme improves load balancing without any additional modifications to the DRAM interface. We also develop a novel data reliability solution for TRiM architectures that cannot exploit the conventional rank-level error correction code (ECC). Because GnR accesses the embedding tables in a read-only manner, we repurpose the existing on-die ECC [57] to only detect but not correct errors during GnR.

#### 1.3 Research Contributions

In this dissertation, we make the following contributions:

• We propose MViD, which adds MAC units inside DRAM to solve the memory

bottleneck of RNN inference in edge devices and to improve energy efficiency.

- MViD deploys MAC units by carefully considering various constraints (internal bandwidth, power limit, and off-chip bandwidth) that could occur when adding MAC units in the current mobile DRAM standard. For the first time to the best of our knowledge, MViD can perform processor requests simultaneously with MV-mul; therefore, MViD functions as the main memory.

- Through sparse matrix formatting, quantization, and bank partitioning, MViD improves the throughput of inference in Deep Speech 2, up to 7.2× compared to the baseline system without MViD. MViD also guarantees that MV-mul operations do not hoist processor requests.

- We conduct a quantitative analysis of existing NDP solutions aimed at accelerating the GnR operation.

- We propose TRiM, an NDP architecture that accelerates the GnR operation by utilizing the features of the DRAM data/control path structure without causing significant changes in the conventional DRAM interface.

- We propose hot-entry replication utilizing the characteristics of the RecSys workload to alleviate the load imbalance problem that occurs in TRiM.

- The optimized TRiM architecture based on DDR4/5 DRAM improved the performance of GnR by up to 7.7× and 3.9×, respectively, compared to the baseline and state-of-the-art architectures.

#### 1.4 Outline

The organization of this disseration is as follows. Chapter 2 describes the characteristics of memory–intensive machine learning operations and the organization and operation of our target memory device for PIM architecture, DRAM. In Chapter 3 and 4, we propose processing–in–memory architectures, MViD and TRiM, that accelerates mobile inference of RNNs and recommendation models. Chapter 5 describes a discussion about applying PIM microarchitectures to accelerate various memory–intensive applications. Related works are presented in Chapter 6. Conclusions and future works are presented in Chapter 7.

#### Chapter 2

#### Background

#### 2.1 Memory-intensive Machine Learning Applications

Machine learning applications are used to handle various tasks such as computer vision, natural language processing, and personalized recommendation. Because these applications require a large amount of computation to process large datasets, they require a lot of computational and memory resources.

Machine learning applications consist of various arithmetic operations such as convolutional (CONV) layers, fully-connected (FC) layers, activation functions (e.g., ReLU), and embedding layers. The computational characteristics of these applications are determined by those of the operations constituting the applications.

The roofline performance model [117] shows the computational characteristics of the operation in computer systems. The X-axis of a roofline graph rep-

This chapter is based on [65, 66, 99].

<sup>©2020</sup> IEEE. Reprinted, with permission, from Byeongho Kim, Jongwook Chung, Eojin Lee, Wonkyung Jung, Sunjung Lee, Jaewan Choi, Jaehyun Park, Minbok Wi, Sukhan Lee, and Jung Ho Ahn, "MViD: Sparse Matrix-Vector Multiplication in Mobile DRAM for Accelerating Recurrent Neural Networks," IEEE Transactions on Computers, April 2020.

<sup>&</sup>quot;TRiM: Enhancing Processor-Memory Interfaces with Scalable Tensor Reduction in Memory" © 2021 by Byeongho Kim, Jaehyun Park, Eojin Lee, Minsoo Rhu, and Jung Ho Ahn is licensed under CC BY 4.0. https://doi.org/10.1145/3466752.3480080.

<sup>&</sup>quot;TRiM: Tensor Reduction in Memory" ©2020 by Jaehyun Park, Byeongho Kim, Sungmin Yun, Eojin Lee, Minsoo Rhu, and Jung Ho Ahn is licensed under CC BY 4.0. https://doi.org/10.1109/LCA.2020.3042805.

resents the arithmetic intensity, the number of arithmetic operations per memory access. The Y-axis represents the number of arithmetic operations per second. The performance of the operation on the region under a diagonal line is limited by memory bandwidth, where the slope of the diagonal line means the memory bandwidth. The performance of the operation on the region under a horizontal line is limited by the peak arithmetic performance of the processor.

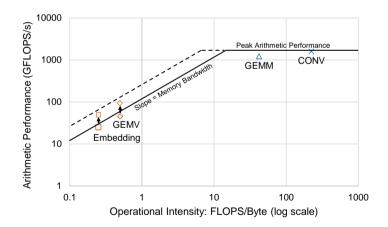

Through the roofline analysis as shown in Figure 2.1, it is possible to identify the performance bottleneck of the operation for machine learning. Operations such as a CONV operation and its base operation, MatMul (GEMM), have high arithmetic intensity, and execution time is affected by the computing power of the underlying system. These operations are called compute—intensive operations. Conversely, matrix—vector multiplication (GEMV) and embedding operation (Embedding) have low arithmetic intensity, and the execution time of

Figure 2.1: Roofline model for four arithmetic operations, where the performance ceiling is based on Intel Xeon Gold 6138 [27] with six memory channels, each with DDR4–2400 modules achieving up to 115.2GB/s. The performance of the memory–intensive operation improves if the memory bandwidth of the system increases.

those operations is affected by memory bandwidth. These operations are called memory–intensive operations.

Various companies emphasized that there is a high demand for accelerating memory–intensive operations when running machine learning applications on edge devices [13] and datacenters [33,60]. Facebook [9,24] reported that the server usage for the recommendation model, which is mainly composed of the embedding operations, accounts for more than 70% of the total machine learning inference server usage and has increased about four times in two years. Also, Facebook emphasized the acceleration of the recommendation model through many studies [24, 29, 63, 64, 100, 109, 116]. Google [13] highlights the need for accelerating matrix–vector multiplication on edge devices running RNN models and Transducer models.

As shown in Figure 2.1, increasing the memory bandwidth of the system improves the performance of memory–intensive operations. However, due to the memory wall problem [119], where the memory bandwidth improvement is much lower than the computing power improvement, a solution that simply increases memory bandwidth of the system is costly, and the computer system is bottlenecked by the memory subsystem. To overcome the memory wall problem, we introduce Processing–in–Memory (PIM) microarchitectures that can additionally utilize memory bandwidth.

#### 2.2 DRAM Organization and Operations

It is necessary to understand how a DRAM device is organized and operates to analyze its power constraint and further improve the performance by leveraging the internal data transfer bandwidth.

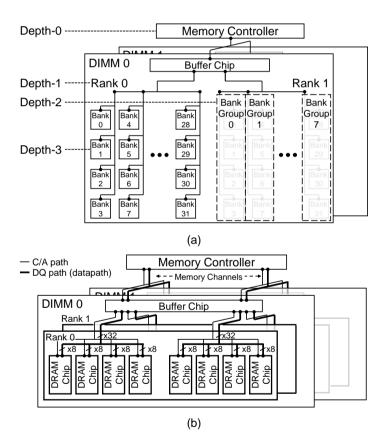

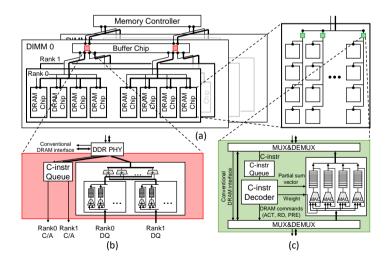

The datapath of popular main-memory systems such as DDR4/5 DRAM [54, 57] takes a hierarchical tree structure (see Figure 2.2(a)), i.e., a memory channel as a root node (depth-0) consisting of a primary host memory controller (MC) and multiple, secondary DRAM ranks (depth-1) connected through a depth-1 data bus. Each rank consists of several DRAM chips, all receiving the same command/address information by broadcasting and transferring the corresponding data accordingly. The datapath entering the rank is physically

Figure 2.2: (a) Simplified DRAM datapath assuming a single memory channel and (b) module organization of DDR5 DRAM with 2 DIMMs  $\times$  2 ranks connecting two memory channels.

divided and connected to each DRAM chip (see Figure 2.2(b)). To maximize memory—level parallelism, several ranks can physically be housed within a DIMM module.

In DDR5 DRAM, a rank consists of eight bank-groups (depth-2), each packed with four banks (depth-3). Similar to the depth-1 data bus, the depth-2 data bus and the depth-3 data bus are shared between one rank and eight bank-groups, and between one bank-group and four banks, respectively. Each bank consists of a 2D array of DRAM cells; each DRAM page (often called row) is controlled by a wordline (WL), and each column is connected to local bitlines (BLs). The sequence of a DRAM read is as follows. 1) Activation (ACT): the cells of a selected DRAM page in a bank driven through a WL share charges with the corresponding BLs, and bitline sense amplifiers (BLSAs) detect the small voltage difference of BLs due to charge sharing and amplify it. 2) Read (RD): a portion of column bits of data latched in the BLSA are transferred to GIO SAs through the global I/O. The data is amplified again in the GIO SA and transferred to the I/O multiplexer (mux) through inter-bank datalines and leaves the DRAM die. Reading the data in another column of an activated page needs only RD. To access data at a page other than the currently activated page in a bank, we should precharge BLs and BLSAs (PRE) prior to ACT and RD. The minimum time interval from ACT to PRE is tRAS, the time to restore data to the cells.

All of the banks in a DRAM chip operate independently, albeit only one bank can occupy depth-1/2/3 data buses at any given time. Therefore, RD can be issued at a minimum tCCD (column to column delay) interval to prevent a conflict in the data buses (often called inter-bank datalines). The time interval between two ACTs within a channel is limited to tRRD (row to row activation

delay). ACT can be performed simultaneously on multiple banks, but only four ACTs within tFAW (four activation window) can be issued due to the power limit.

The notion of a bank-group did not exist until DDR4. DDR4/5 DRAM started adopting such a concept to retain the frequency of DRAM banks at a low level while increasing the data transfer rate and hence the bandwidth. Because the frequency inside a bank-group bus is lower than that outside a bank-group, the consecutive read delay within a bank-group (tCCD\_L) is greater than that between the bank-groups (tCCD\_S). The bank-group organizes a level of the hierarchy between the ranks and banks, connecting hierarchical multi-drop buses among them.

DDR5 DRAM allows one DIMM to be connected to two channels, giving it a physically different configuration from previous DDR generations where one DIMM is connected to one channel. However, as the two channels operate independently, it can be seen that they have separate data/control paths.

The control path of the main-memory systems is structured similarly. An MC sends command and address (C/A) signals to all connected DRAM ranks through a C/A bus in a broadcast manner. Each rank drops the signals if it is not the right destination. A buffer chip or chipset connects an MC and the ranks in a module to alleviate signal integrity issues [56].

Processing—in—Memory (PIM) architecture is an architecture that processes operations near the DRAM cell with the higher internal bandwidth by utilizing the characteristics of the DRAM datapath. Because DRAM banks can operate independently, if the processing elements (PEs) are located near the DRAM datapath and these PEs do not share the datapath, PEs can operate indepen-

dently. Thus, the operations can be processed utilizing the bandwidth the same as the channel bandwidth multiplied by the number of PEs, and we suggest PIM microarchitectures to accelerate bandwidth-hungry operations.

As the baseline memory for Section 3, we used an LPDDR4 DRAM device [55] which is composed of two memory channels. Multiple LPDDR4 dies can be connected (e.g., through die stacking) to form a multi-rank package with two channels. For the baseline memory used in Section 4, we assume a data/control path dedicated to each rank in the buffer chip as in MCN DIMM [7], which is also assumed in the previous studies [63,73] (Figure 2.2(b)).

#### Chapter 3

MViD: Sparse Matrix-Vector Multiplication in Mobile DRAM for Accelerating Recurrent Neural Networks

#### 3.1 Background and Motivation

#### 3.1.1 Energy-efficient RNN Mobile Inference

RNN inference is mostly performed in datacenters yet [33, 60]; however, to reduce the latency and improve the energy efficiency of serving RNNs, there is a strong demand for conducting RNN inference closer to service requests, such as in mobile and IoT devices. These devices typically do not have large on—chip memory due to power and cost issues.

RNNs have several variants, such as LSTM (long short-term memory) and GRU (gated recurrent unit), depending on the existence of certain gate types.

This chapter is based on [65, 66, 99].

<sup>©2020</sup> IEEE. Reprinted, with permission, from Byeongho Kim, Jongwook Chung, Eojin Lee, Wonkyung Jung, Sunjung Lee, Jaewan Choi, Jaehyun Park, Minbok Wi, Sukhan Lee, and Jung Ho Ahn, "MViD: Sparse Matrix-Vector Multiplication in Mobile DRAM for Accelerating Recurrent Neural Networks," IEEE Transactions on Computers, April 2020.

<sup>&</sup>quot;TRiM: Enhancing Processor-Memory Interfaces with Scalable Tensor Reduction in Memory" © 2021 by Byeongho Kim, Jaehyun Park, Eojin Lee, Minsoo Rhu, and Jung Ho Ahn is licensed under CC BY 4.0. https://doi.org/10.1145/3466752.3480080.

<sup>&</sup>quot;TRiM: Tensor Reduction in Memory" ©2020 by Jaehyun Park, Byeongho Kim, Sungmin Yun, Eojin Lee, Minsoo Rhu, and Jung Ho Ahn is licensed under CC BY 4.0. https://doi.org/10.1109/LCA.2020.3042805.

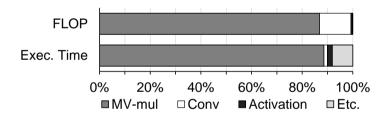

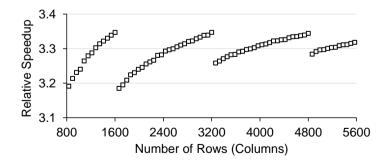

RNN operation consists mainly of matrix-vector multiplication (MV-mul), element-wise sum/multiply, and activation function such as tanh or sigmoid, but MV-mul dominates the execution time. For example, a typical configuration of Deep Speech 2 (DS2) [8], a popular RNN benchmark performing end-to-end speech recognition, is composed of two convolutional layers and five GRU layers where the size of most GRU weight matrices is  $1600 \times 1600$ . When running on an Intel Skylake-based server [27], the FLOP and execution time of MV-mul take 86.8% and 88.6% of the total (see Figure 3.1). The profiling results in the latest GPUs [32] are also similar.

Single GRU layer has six matrices (three for processing an input vector and the other three for processing the vector computed in the previous time step),

Figure 3.1: The FLOP and execution time breakdown of Deep Speech 2 [8] in an Intel Skylake-based server [27].

Figure 3.2: The aggregate size of weight matrices and word error rate (WER) of representative ASR models over time [8, 17, 37, 38, 44, 86, 106]. Not all models use the same data set.

and the size of each matrix is mostly  $1600 \times 1600$  with DS2. Assuming that the size of each element is 16 bits [45], the size of a GRU layer is 30.7 MB. When we perform whole RNN inference, it executes five GRU layers and needs 145 MB (the size of three matrices of the first GRU layer is slightly smaller than the other ones) of storage for weight matrices, which is too large to fit in the on–chip memory (mostly up to several MBs) of mobile/IoT devices. In MV–mul, each vector element is reused by the number of rows within the weight matrix, whereas each weight element is used only once. The on–chip memory size of processors grows over time, but the aggregate size of weight matrices increases as well for better recognition quality (see Figure 3.2). Therefore, the weight elements, which cannot be reused for RNN inference, must be fetched from main–memory DRAM devices.<sup>1</sup>

From an energy efficiency perspective (i.e., J/b), reading data (several to dozens of bits) from a DRAM device requires orders of magnitude more energy than performing a multiply–accumulate (MAC) operation or reading the same amount of data from an SRAM with few KBs of capacity [16, 49]. From a performance perspective, the bandwidth of off–chip DRAM devices is much lower than that of on–chip memory in a processor, making the execution time of MV–mul limited by off–chip DRAM bandwidth. Therefore, it is critical to reduce the energy consumption and increase the bandwidth of main–memory DRAM accesses in improving the energy efficiency and performance of RNN inference.

<sup>&</sup>lt;sup>1</sup>We can reuse weight elements if we perform RNN inference over a batch of input or a group of time steps. However, mobile/IoT devices typically process one or few time steps of a request at a time to reduce service latency, limiting the degree of this reuse. We interchange the terms of a DRAM device and a DRAM die.

## 3.1.2 How to Improve the Energy Efficiency and Bandwidth of DRAM Accesses in MV-mul

The best way to improve the energy efficiency of multiplying a large matrix (located at main-memory DRAM) with a vector is to perform all or most of MV-mul within DRAM dies. If a processor performs MV-mul by fetching weight elements from a separate main-memory DRAM device, inter-die communication consumes most of operating cost (data transfer energy) and capital cost (large silicon/packaging area, such as pins, pads, and TSVs) regardless of the ways interconnecting processor and DRAM dies, such as conventional package, silicon interposer (2.5D [58]), and face-to-face die stacking (3D) using TSVs [96].

If we perform MV-mul within a DRAM device but close to its inter-die I/O, we can save inter-die communication energy. However, this does not provide any performance gain unless we utilize multiple DRAM dies within a memory rank [11]. A way to achieve an additional performance benefit in MV-mul is to exploit a structural unit within a DRAM device, bank. A DRAM die has several to few dozens of banks, where each bank can operate independently and concurrently. Therefore, by conducting MV-mul in the edge of bank's datapath I/O, we can improve both performance (multiplied by the number of banks) and energy efficiency (by not dissipating energy for moving weight matrices across banks, which is a significant portion of DRAM read energy according to [95]).

Performing MV-mul on each DRAM bank saves the data transfer energy of weight elements; but, if the vector elements are from a processor, they should traverse farther through inter-die I/O and inter-bank datapath to reach the DRAM bank. Hence, one might regard that performing MV-mul on a bank

provides no energy saving. However, as described in Section 3.1.1, 1) vector elements are reused by the number of matrix rows and 2) a vector is much smaller than a weight matrix (by the number of matrix rows), so we can save most of the energy for fetching a vector by providing a small storage per bank to store the vector elements.

Still, there exists an important feasibility issue in performing MV-mul at all the banks of a DRAM device. DRAM banks can operate in parallel; however, as mentioned in Section 2.2, their operations are limited by various timing constraints. This limitation is because all banks share one or few inter-die I/O paths (called channels), which determine the maximum rate of meaningful activity (related to the data store, retrieval, and retention, which are the primary purposes of DRAM as main memory). Therefore, a DRAM die has a power limitation, which determines the design of its power delivery networks, such as the number of power and ground pins and the density of on-chip power/ground wires.

The cost of DRAM is very sensitive to this power limitation because a DRAM device uses few (typically two to three) metal layers, and hence populating more power/ground wires and pins would significantly increase fabrication cost and die size. If all the DRAM banks perform bursty data read operations for MV-mul, a DRAM device can dissipate power exceeding the aforementioned power limit. For example, on the mobile LPDDR4 DRAM device we use as a baseline, concurrently reading data from all DRAM banks to their global-I/O (GIO) sense amplifiers (SAs) would dissipate 1.7× of its power limitation. As an edge device executes applications other than RNNs as well, it is a huge waste of precious DRAM resources to design a DRAM device with a higher

power budget only for MV-mul. Therefore, it is desired to perform MV-mul under the maximum power budget determined by normal DRAM operations.

As explained in Section 2.2, DRAM reaches its peak power consumption level when each channel of DRAM performs four ACTs in tFAW and multiple RDs at tCCD interval. If we perform a DRAM read but omit inter—bank and inter—die datapath by supporting the data to the MAC units next to GIO SAs, we can save energy. According to the detailed analysis later explained in Section 3.3.1, we can conduct up to four RDs simultaneously when performing MV—mul within DRAM banks without exceeding the peak power consumption level.

#### 3.2 MV-mul in DRAM

#### 3.2.1 Exploiting Quantization and Sparsity in RNN's Matrix Elements

Under this DRAM power constraint, to further reduce the total amount of computation, we exploit a characteristic of RNN that a significant portion of its weight elements is redundant. As mentioned in [45], even if we turn a majority of the weight elements of an RNN into zeros, the impact of this pruning on the RNN inference is negligible. We verify this by conducting an experiment on DS2 [8], whose network model size is specified in Section 3.1.1 with LibriSpeech dataset [98], following the pruning strategy explained in [89]. [89] prunes down the values below certain thresholds into zeros, after every few training epochs. From the experiment, we observed no significant surge in word/character error rates with the sparsity (the portion of zero values within a matrix) of the matrices being 25%, 50%, and 75%.

When we compare a sparse matrix format (specifying non-zero elements

(NZs) with their positions) with a dense matrix format (listing all the matrix elements), if sparsity is higher than (position bits) / (data bits + position bits), the sparse matrix format represents a matrix with fewer bits. Because reading weight matrices dominates the energy and the execution time of MV-mul, it

Figure 3.3: Distribution of the distance between two adjacent non-zero values (NZs) in the matrices of GRU layers (75% sparsity) in Deep Speech 2 [8]. More than 98% of NZs have a distance of less than 15.

Figure 3.4: (a) An exemplary sparse matrix and (b) its representation using the delta encoding format. dN denotes the N-th non-zero value of a matrix in row-major order. Each row in the representation table includes up to one row of the sparse matrix.

is beneficial to exploit the sparse matrix formats for matrices whose sparsity values are above this threshold. There are several formats for representing a sparse matrix, exemplified by Compressed Sparse Row/Column (CSR/CSC), Coordinate (COO), and Diagonal (DIA) [12].

The distribution of NZs in a matrix determines the size efficiency (bytes per NZ) of a specific format. For RNN applications such as DS2, the NZs of the weight matrices are relatively uniform—randomly distributed (see Figure 3.3). In this case, there is no significant difference in the bytes per NZ between sparse formats except for the formats favoring special distributions. In this paper, we propose delta encoding, a variant of CSR.

CSR stores the absolute column indices of NZs and the number of NZs per row, together with the NZ values. By contrast, our delta encoding stores the column distance from the previous NZ as an index to represent the matrix with fewer index bits in storing (data, index) pairs (see Figure 3.4). Also, instead of storing the number of NZs per row, we reserve the maximum value which can be represented by an index to specify the end of a row. When the index indicates the end of a row, the corresponding data field stores the absolute address of the row. For example, if we dedicate four bits per index, we define 0xf (the maximum distance) as the end of a row and use the values from 0x0 to 0xe as the distance between two NZs. If the distance is greater than 0xe, we place one or more dummies (whose data value in the (data, index) pair is zero).

In addition to exploiting sparsity through pruning, we also apply quantization for a further reduction in size representing the matrix. When we applied both pruning and quantization to DS2, we observed that reducing the precision of data till 12 bits incurs no noticeable degradation in inference accuracy, which

is consistent with the results reported in [45].

In our sparse matrix format, the frequency of dummy values added depends on the size of index bits and the sparsity of a matrix. We study an optimal index bit minimizing the total size of a matrix that is formatted at each sparsity value using the GRU layers of DS2. The experiment shows that using (12 bits, 4 bits)

Figure 3.5: The storage requirement for a matrix with different index bits when using our sparse matrix encoding format (delta encoding). The storage requirement is compared to that of a dense matrix without pruning.

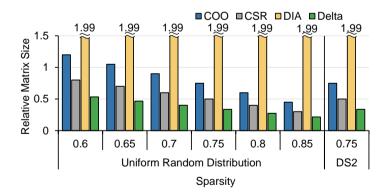

Figure 3.6: The relative size of the tested matrices encoded with various sparse matrix formats normalized to the size of the dense format [12]. We set the size of the dense format as the baseline per matrix. The matrices are categorized into two types: ones synthesized with the given sparsity values under a uniform random distribution and the other collected from the real dataset (a GRU layer of DS2), which has a sparsity of 75%. Our delta encoding format gives the smallest size per NZ among all the tested formats in our target sparsity ranges.

for (data, index) pairs is optimal for the sparsity range of 65% to 80%, where the portion of dummy pairs is less than 5% (see Figure 3.5). As a result, we assume that a (data, index) pair is (12 bits, 4 bits), and matrices are  $1600 \times 1600$  with a sparsity of 75% by default in this paper.

To verify the effectiveness of our delta encoding format on the sparse matrices, we compared the size of sparse matrices encoded with various sparse formats. From the experiment, the delta encoding format reduces the size of matrices by 32.7% compared to the CSR format for the DS2 dataset with the sparsity of 75% (see Figure 3.6).

By applying quantization and sparse formatting, the total size of weight matrices in the DS2 decreases, but it is still 36 MB, which would not fit on-chip caches of the mobile devices. Therefore, it is effective to perform MV-mul in DRAM; even if the size of matrices and the (data, index) pairs would vary as ASR applications evolve, we believe that the qualitative observation and analysis of our proposed MV-mul accelerator would stay unchanged.

# 3.2.2 The Operation Sequence of MV-mul in DRAM

To perform MV-mul within DRAM banks, we should locate a weight matrix and an input vector within banks capable of MV-mul, called MV-banks. As we can conduct four RDs simultaneously within banks due to the power constraint, each channel in a DRAM device has four MV-banks. So the weight matrix is divided into four sub-matrices and distributed to the MV-banks. As the input vector is reused and much smaller than the matrix, we duplicate the input vector to each MV-bank equipped with a dedicated SRAM (iv-SRAM). An alternative is to use another DRAM bank or another row in the same DRAM

bank for storing the input vector. However, when processing sparse matrix-vector multiplication, accesses to the input vector are not sequential (consecutive). Therefore, it is required to access a larger size of DRAM data than is needed for SRAM because the granularity of a DRAM read (256 bits) is much coarser than that of an SRAM read (12 bits); it is not efficient in terms of throughput and energy.

The power and area overheads of iv–SRAM depend on the number of entries and the size of each entry. The input vector is stored in a dense format, making iv–SRAM sized to hold 1,600 entries, each storing 12–bit value. Its area is equivalent to 2.07MB of DRAM cells (1.61% of a 128MB DRAM bank), and it dissipates just 1.9% of the total power for MV–mul. A more detailed power, area, and timing analysis is described in Section 3.3.1. Each MV–bank also has a separate SRAM to hold an output vector (ov–SRAM), where each element is 24–bit long. In our case of ov–SRAM with 400 entries, the area corresponds to 0.3 MB DRAM cells, and its power consumption is negligible because ov–SRAM has low utilization.

The main operation sequence of MV-mul is to 1) write an input vector to the iv-SRAM in MV-banks, 2) perform MV-mul in each MV-bank by sequentially performing the inner-product computation, and 3) read the generated output vector from the ov-SRAMs. We assume that the matrix elements are already stored in each MV-bank in the form of our sparse matrix format. The detailed operation sequence is as follows. First, writing the input vector is processed through broadcasting, because all iv-SRAMs in a DRAM device need the same input vector. The input vector from the processor is sent to each bank and stored in iv-SRAM simultaneously.

The core inner-product computation sequence in each MV-bank is as follows. Data reading reads data from an activated DRAM page. An LPDDR4 device stores 256 bits in GIO SAs in one read. For the size of a weight element being 16 bits, there are 16 elements per DRAM RD. Index decoding process is required as the weight element is encoded using a sparse format. The index refers to the relative column distance from the previous NZ location minus one. Therefore, we can find the absolute address needed for fetching a proper input vector element by accumulating the index values. The index of the first element represents the index of the first NZ data. Moreover, a 4-bit compare logic is required to identify the row end index (index value 0xf). Input vector fetching is performed using the absolute addresses, each pointing to one of the 16 weight elements. iv-SRAM serves 16 weight elements for decoded addresses within tCCD. MAC executing process conducts inner product through MAC units populated within an MV-bank. Because 16 weight elements and vector elements are fetched every tCCD, 16 MAC operations must be performed. We designed and compared various MAC units with different numbers of pipeline stages (more details in Section 3.3.1). We identified that populating 16 MAC units having a cycle time of tCCD is better than populating fewer MAC units with a shorter cycle time (through aggressive pipelining) in power and area perspectives. Therefore, we place 16 MAC units next to the GIO SAs of an MV-bank. Output storing process stores the result of the MAC operation in the ov-SRAM only when the row end index exists at the decoded index through the index decoder. The output store method depends on how the matrix elements are mapped to DRAM pages, as described below.

When MV-mul is finished in all the participating MV-banks, the results in

ov-SRAM are transferred to the processor. The activation function is done by the processor; because the output vector is small in size, it gives little benefit of implementing the function within a DRAM die.

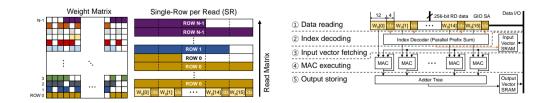

There are multiple ways to map a weight matrix represented with our delta encoding format to DRAM pages. As mapping changes, organization and operation sequence change accordingly. Considering that, we choose a mapping that we call Single-Row per Read (SR), where elements from a single DRAM read (256 bits) belong to one matrix row (see Figure 3.7).

The elements fetched on GIO SAs belong to one matrix row so that index decoding can be done sequentially using one accumulator or through parallel prefix sum. It is not possible to sequentially decode 16 indices within tCCD using one accumulator, so we use a 6-level parallel prefix sum unit. The column indices from the parallel prefix sum unit are used to fetch the input vector values from the iv-SRAM. Each MAC unit accumulates the product of an input vector element and a weight element until the DRAM read includes the end of a matrix row. If the current DRAM read includes the end of a row, the partial sums stored in all the MAC units of an MV-bank are accumulated through an adder tree, which takes 5 ns (same as tCCD).

SR is inefficient in that on average a half of weight elements in a DRAM

Figure 3.7: Mapping of the weight matrix to DRAM reads and pipeline stages for Single-Row per Read.

read (8 for LPDDR4) are padded with zero values per matrix row (performance degradation about 2% compared to an ideal configuration where MAC units are fully occupied in a 1,600×1,600 matrix). So we may consider other mapping types where the elements from a single DRAM read might belong to different matrix rows. However, from the perspective of implementation, the latter mapping types require higher hardware complexity. Hence, we choose SR as a mapping of our delta encoding format.

In utilizing this MViD architecture, we should consider how a processor controls MViD. For a DS2 matrix we use for evaluation, 1.25 MB of matrix data distributed in each bank must be read and multiplied with an input vector. If all the DRAM RD commands for operations are transferred from the memory controller (MC), it will cause a huge CA bus utilization overhead. Therefore, a single MV-mul command, including the size of the initial address and the weight matrix is passed to the MV-bank to perform all MV-mul operations.

MV-banks process MV-mul through taking commands that write/read the vector to/from the input/output SRAM (WR-iv, RD-ov). To define these two commands, we used the reserved-for-future-use (RFU) commands in the LPDDR4 specification [55]. WR-iv command broadcasts the same input vector to all MV-banks. The input vector broadcasted through inter-bank datalines is simultaneously written to the iv-SRAMs in the MV-banks. Once the broadcast is over, MV-mul can be started. Therefore, there is no separate DRAM command for starting MV-mul. RD-ov should be processed after the entire MV-mul operation is completed. Because conventional DRAM interfaces do not have a mechanism to notify the end of a specific operation to MC, the primary device in the bus interface, the MC periodically sends RD-ov to check if MV-mul is

completed (polling). This requires the MV-bank control unit (MCU) checking the status of the MV-bank; MCU is located close to the inter-die I/O within a DRAM device. If MV-mul is over, MCU returns a predefined value for RD-ov. Then, the MC issues RD-ov against to retrieve the output vector values.

# 3.2.3 Concurrently Serving Requests from Processors and Performing MV-mul in DRAM

A computer system that performs RNN inference can simultaneously run other applications. Therefore, the performance of the other applications can be drastically reduced if MV-mul operations within DRAM block the other memory requests. For example, in a system stacking four LPDDR-3200 dies each with eight MV-banks, the minimum time required to read 1.25MB of data and perform MV-mul is 6.125  $\mu$ s if all MAC units are used for one MV-mul. If DRAM devices do not accept another memory request during the MV-mul operation, the processor would wait for the main memory response at least for 6.125  $\mu$ s. Therefore, a DRAM device with MV-banks must provide a mechanism to service other memory requests while performing MV-mul.

Careful coordination is required for DRAM to serve both MV-mul and memory requests from a processor (processor requests) concurrently. Because performing MV-mul in MV-banks dissipates the maximum DRAM power, this power limit must be considered to serve processor requests. Moreover, row-buffer conflicts, which occur due to a request to DRAM row different from the active row, must be considered if a processor request heads to an MV-bank that is actively performing MV-mul.

Method for achieving concurrency: We achieve the coordination by sending a

single MV-mul command (composed of WR-iv and RD-ov explained in Section 3.2.2) to the DRAM and by controlling the progress of MV-mul inside the DRAM. This coordination requires control generator units (CGUs) to convert a single MV-mul command into a sequence of fine-grained sub-commands. A CGU is located at each MV-bank and generates DRAM ACT, PRE, and RD commands to read weight elements, compute vector indices, and perform MAC operations, obeying DRAM's timing constraints.

CGUs must slow down or pause the progress of MV-mul within MV-banks to serve processor requests. When a processor request reaches a non-MV-bank, the DRAM device should secure enough power budget. This can be achieved by slowing down the progress of MV-banks. According to our analysis (whose methodology explained in Section 3.3.1), slowing down all MV-banks into half of their original rate provides a sufficient power budget to process the processor requests with half of the rate a DRAM device can serve the requests. It can be achieved by increasing both tCCD and tRRD twice of their original values. By contrast, when a processor request reaches an MV-bank, we need to slow down all MV-banks and also pause the target MV-bank to deal with the row-buffer conflict.

Implementing commands for slow-down and pause: If a MC sends separate slow-down and pause commands prior to all memory requests, this would cause a huge CA bus utilization overhead. We alleviate this overhead by embedding the slow-down and pause information in existing DRAM commands.

First, the transmission of any normal DRAM command (i.e., RD, WR, ACT, and PRE) can be a signal to notify slow-down to MV-banks as all MV-banks must be slowed down to process normal DRAM commands to non-MV-banks.

Therefore, if MV-banks are not in a slow-down state when MCU receives any normal DRAM command, it broadcasts the slow-down command (SD) to the CGUs of all MV-banks and then sends the original DRAM command to the target bank. The timing of the original DRAM command should be increased by 3 tCK due to command decoding (1 tCK) and SD broadcast (2 tCK). This timing adjustment is only needed when none of the MV-banks are in a slow-down or pause state.

Second, PRE can be augmented to notify the target MV-bank to pause. To process a request from a processor on an MV-bank actively processing MV-mul, we must precharge the currently active DRAM row to resolve this row-buffer conflict. Therefore, we define a pause PRE command (p-PRE) by modifying PRE and use it to pause an MV-bank prior to PRE. The timing (latency) of p-PRE should be different from that of PRE (tRP) because a MC does not exactly know what operation is being performed in the MV-bank when it sends p-PRE. For example, if p-PRE is sent while the target MV-bank is activating a row for MV-mul, the precharge operation must be delayed by up to tRAS because the MV-bank must restore the row being activated. Therefore, in order not to violate the internal DRAM timing constraints, the timing of p-PRE must be at least tRAS+tRP (= tRC).

The worst case for p-PRE is when the target MV-bank just started PRE for MV-mul. There are two options for CGU in this case: one is to stop MV-mul and to directly enter the pause state when PRE is finished, and the other is to perform the planned ACT followed by RD for MV-mul and then PRE for pause. The former favors a processor request as the time of p-PRE can be tRC. The latter favors the progress of MV-mul, at the cost of a higher timing value of

p-PRE being tRC+tRP. We prefer the progress of MV-mul and set the timing of p-PRE to tRC+tRP, leaving the quantitative comparison of these two options as future work.

After all processor requests are processed, MV-banks must resume or return to the original processing throughput (speed-up). Because PRE is issued at the end of serving requests from a processor, we leverage PRE once again to notify speed-up (s-PRE) and resume (r-PRE). MC checks the state of each MV-bank and sends s-PRE or r-PRE command to MCU when speed-up or resume is needed. When MCU receives s-PRE, it sends the speed-up signal to the CGUs of all MV-banks and then sends PRE to the target bank. When MCU receives r-PRE, it is passed to the CGU of the target MV-bank, and the CGU resumes MV-mul after precharge. In LPDDR4, PRE has three unused CA bits; we use these to distinguish PRE from p-PRE, s-PRE, and r-PRE.

Policies for slow—down and pause: If we slow down or pause MV—banks every time MC receives a request, the throughput of MV—mul would be deteriorated significantly. To prevent such a throughput drop, MC checks the memory request queue at every time interval (tIV). When the aggregate number of pending requests over multiple tIVs surpasses a certain threshold (nTH), MV—mul is slowed down or paused. In determining whether to slow down or pause, MC checks the following metrics: an aggregated number of memory requests to normal banks (num\_req\_nonMV), and an aggregated number of memory requests to each MV—bank (num\_req\_MV[n]). The policy that we propose is:

- num\_req\_nonMV  $\geq$  nTH  $\rightarrow$  slow down all MV-banks.

- num\_req\_MV[n]  $\geq$  nTH  $\rightarrow$  pause the n-th MV-bank and slow down the

other MV-banks.

When a pause happens, we also slow down all MV-banks that are not paused due to the power budget (check a detailed analysis in Section 3.3.1). Also, once an MV-bank enters pause or slow-down state, MV-mul resumes or speeds up after the MV-bank processes all requests that can be processed in that state. Thus, processor requests heading to the MV-banks that are already paused have no additional delay due to the p-PRE command.

We use the same nTH for both slow-downs and pauses, making pauses less frequent than slow-downs when memory requests are evenly distributed among banks (which are common cases). This design choice is reasonable as a pause is more costly than a slow-down as a sequence of PRE and ACT should follow a pause to resolve a row-buffer conflict.

We accumulate num\_req\_nonMV and num\_req\_MV[n] over multiple tIVs, not resetting them at the end of every tIV. This accumulation prevents a MC from waiting until MV-mul is finished when few requests (less than nTH) from a processor form dependency on future requests (forming a deadlock). The frequency of slow-down and pause can be controlled by changing nTH and tIV. Large nTH and tIV help MV-mul finish earlier at the cost of a longer tail latency for requests from a processor, and vice versa for small nTH and tIV. We can adaptively control both nTH and tIV values to either favor MV-mul over processor requests or vice versa.

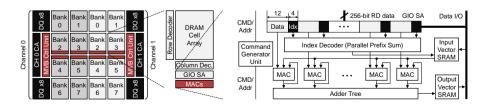

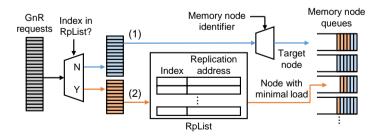

# 3.2.4 Put It All Together: MViD Architecture

Putting it all together, we propose MViD architecture, as illustrated in Figure 3.8, whose design decisions are made through a series of design space exploration

made in the previous sections. We populate an MCU close to the inter-die I/O within a DRAM device, which orchestrates the whole MV-mul process. 16 MAC units are placed near GIO SAs in four banks, as only up to four concurrent RD operations are permitted under the power constraint of the baseline LPDDR4 DRAM. Each of these MV-banks has a CGU, which takes commands and addresses that come to the MV-bank from the MCU and converts them to the fine-grained sub-commands. An iv-SRAM and an ov-SRAM are placed per MV-bank to store the input/output vectors. We used a parallel prefix sum logic for index decoding, and an adder tree to aggregate the output from the 16 MAC units.

The core inner-product computation part of MViD consists of five pipeline stages: data reading, index decoding, input data fetching, MAC executing, and output storing. First, 256-bit data are read from the DRAM bank and latched to GIO SAs, followed by the index decoding stage, which comes with parallel prefix sum and fetching stage, which loads 16 input elements from iv-SRAM. Then, MAC operations are executed, and the results are added up by an adder tree per weight matrix row, forming an output value, which is stored into an ov-SRAM. MCU and CGU deal with requests from a processor through slowing down or pausing MV-mul.

Figure 3.8: The MViD architecture.

We augment LPDDR4 DRAM commands with p-PRE, s-PRE, r-PRE, WR-iv, and RD-ov to slow down or pause MV-banks, to upload an input vector followed by starting an MV-mul operation, and to check if MV-mul is over and then retrieve the output vector from ov-SRAMs. A CGU generates a repeated sequence of ACT, multiple RDs, and PRE for the aforementioned core computation. By contrast, an MCU manages slow-down and pause of MV-banks.

Because MV-mul operates within DRAM devices, not on a processor, the data transfers of the input/output vectors are controlled in a similar way to DMA between the processor and MViD. Data can be transferred to MViD by giving start address, data length, and operation type to the register allocated for MViD. The MC uses the commands described above to transfer the vector to multiple MV-banks and gather the output vector. When MV-mul is over, the MC sends an interrupt to the processor to indicate the end of MV-mul and transfers data to the processor. Besides, there is a cache coherence issue between the processor and MViD. We can deal with this by either 1) flushing cache lines that hold weight matrices prior to every MV-mul or 2) marking that memory region as uncacheable, which was also proposed by [30].

# 3.2.5 Additional Optimization Schemes

MViD architecture can be augmented with a bank partitioning scheme to enhance performance further. The progress of MV-mul is delayed by slow-downs and pauses of the MV-banks, and pauses are caused by the necessity of serving processor requests to the specific MV-banks. By exploiting the bank partitioning method [75], it is possible to store data of the non-MV-mul workloads from a processor in non-MV-banks, thereby preventing MV-banks from serv-

Table 3.1: Energy/area/timing of MViD components.

| Component                     | Energy (pJ)A | Area ( $\mu m^2$ | )Cycle time (ns) |

|-------------------------------|--------------|------------------|------------------|

| DRAM RD (to GIO SA) 2.54 pJ/b |              |                  | 5.00             |

| MAC                           | 1.31 pJ/op   | 6,318            | 5.00             |

| Input vector SRAM             | 1.17 pJ/acc  | 30,048           | 1.25             |

| Output vector SRAM            | 0.53 pJ/acc  | 3,931            | 2.50             |

| Input decoder (SR)            | 1.23 pJ/op   | 5,067            | 5.00             |

| Adder tree (SR)               | 1.39 pJ/op   | 6,071            | 5.00             |

ing processor requests. Because no MV-bank is paused, MV-mul and processor requests can be served only experiencing slow-downs, leading to additional performance enhancement. In the perspective of memory capacity, only non-MV-banks can be used as storage by applying bank partitioning.

#### 3.3 Evaluation

# 3.3.1 Power/Area/Timing Analysis

We analyzed the power, area, and timing for each major component of MViD (LPDDR4–3200 DRAM device, MAC unit, input decoder, adder tree, and iv–/ov–SRAM). We calculated the power and energy of DRAM based on the IDD specification of LPDDR4–3200.<sup>2</sup> We designed a MAC unit, input decoder, and adder tree as Verilog, and synthesized them with 20nm DRAM process.<sup>3</sup> We added 100% area redundancy to the result considering PnR (place and route). We set the cycle time constraint of MAC unit and SR components to 5 ns (200

<sup>&</sup>lt;sup>2</sup>Because IDD values of LPDDR4 is not publicly available, we refer to [76] and use the projection values from LPDDR3 values considering voltage, transfer rate, and fabrication process scaling.

<sup>&</sup>lt;sup>3</sup>We synthesized based on FreePDK45 [91] and calculated power, area, and timing by multiplying scale factor considering transistor size and process characteristics as there is no public 20nm DRAM library.

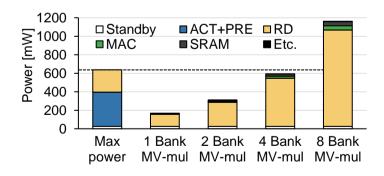

MHz) so that it can operate within tCCD. We used CACTI [113] to model iv-SRAM with 1,600 of 12-bit entries and ov-SRAM with 400 of 24-bit entries. Power and energy: We define the maximum power of one DRAM channel as the power when bursty data reads occur consecutively with the maximum number (four) of ACTs every tFAW. The calculated maximum power is higher than the power of IDD5 (all bank refresh) and IDD7 (ACT-RD burst), which are the power-hungry IDD values in the LPDDR4 specification. We calculated the power of DRAM read for MV-mul (read only up to GIO SA) by referring to FGDRAM [95], and scaled it considering DRAM page size, the number of banks, and data path length. Within the maximum power, we can perform MV-mul simultaneously up to four banks per channel (see Figure 3.9). Most of the MV-mul power of MViD is consumed for internal bank RD, and the power consumption of MAC, SRAM, and other components account for 2.7%, 1.9%, and 0.4% of the total power for MV-mul operation.

We cannot process DRAM requests from a processor with original DRAM timing values because there is a limited power budget for normal DRAM com-

Figure 3.9: The breakdown of LPDDR4 peak power and MViD power consumption; LPDDR4 consumes maximum power with consecutive RDs and concurrent ACTs obeying the tFAW constraint.

mands even if MV-banks are slowed down or partially paused. When four MV-banks are slowed down to half the frequency, four MV-banks consume 300.8 mW, so that the available power budget is 337.0 mW. By doubling tCCD and tRRD, the maximum power required for normal DRAM commands is 326.2 mW, which is operable within the given power budget. When two MV-banks are paused, and the other two MV-banks are slowed down to half the frequency, these four MV-banks consume 163.4 mW, resulting in a power budget of 474.4 mW. When tRRD is set to double, the maximum power required for normal DRAM commands is 441.7 mW, which is also operable within a given power budget.

The energy for DRAM RD is the largest among the energy required for each component to perform MV-mul in MViD, as summarized in Table 3.1. The energy required for internal bank RD is 2.54 pJ/b, so 650.24 pJ is required for 256-bit read operation. The energy per MAC operation is 1.31 pJ/op, and 20.98 pJ is required for every DRAM RD because 16 MACs operate for processing 256-bit data. Each MAC operation requires access to an iv-SRAM, 1.17 pJ/acc × 16 acc = 18.72 pJ being required for 256-bit data. The input decoder is activated once for each DRAM RD, so 1.23 pJ/read is used. Moreover, the ov-SRAM and the adder tree require 0.53 pJ/acc and 1.39 pJ/op, respectively, which occupies a small fraction of the total energy because only one write is required per matrix row.

Area and timing: The area of a MAC is 6,318  $\mu$ m<sup>2</sup>, and the area of an iv-SRAM and an ov-SRAM is 30,048 and 3,931  $\mu$ m<sup>2</sup>, respectively. The areas of the input decoder and the adder tree are 5,067 and 6,071  $\mu$ m<sup>2</sup>. In the 8Gb LPDDR4 die, the area overhead of the MViD components required for half of

Table 3.2: Default simulation parameters.