#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

#### Ph.D. Dissertation of JEONGWOO PARK

# Design of Low-Power Neural Network Training Accelerators through Highly Quantized Learning Process

양자화된 학습을 통한 저전력 딥러닝 훈련 가속기 설계

FEBRUARY 2022

Graduate School of Convergence Science and Technology Seoul National University Intelligent Systems Major

JEONGWOO PARK

# Design of Low-Power Neural Network Training Accelerators through Highly Quantized Learning Process

양자화된 학습을 통한 저전력 딥러닝 훈련 가속기 설계

### 지도교수 전동석

이 논문을 공학박사 학위논문으로 제출함 2022년 2월

서울대학교 대학원 융합과학기술대학원 지능형 융합시스템 전공 박 정 우

박정우의 공학박사 학위 논문을 인준함 2022년 2월

| 위           | 원 장: | 이 재 욱     | (인) |

|-------------|------|-----------|-----|

| 부위          | 원장:  | 전 동 석     | (인) |

| 위           | 원:   | 김 장 우     | (인) |

| 위<br>위<br>위 | 원:   | 최 우 석     | (인) |

| 위           | 원:   | <br>정 두 석 | (인) |

## **Abstract**

With the advent of the deep learning era, the computational need for processing deep neural networks (DNN) have increased dramatically, both in terms of performing training the neural networks on various tasks as well as in performing inference on the trained neural networks for specific use cases. To address those needs, many custom hardware ranging from systems based on field-programmable gate arrays (FPGA) or application-specific integrated circuits (ASIC) for deployment inside data centers to acceleration blocks in system-on-chip (SoC) for low-power processing in mobile devices were proposed. In this dissertation, custom integrated circuits hardware for energy efficient processing of training neural networks are designed, fabricated, and measured for evaluation of different methodologies that could be utilized for more energy efficient processing under same training performance constraints. In particular, these methodologies are categorized to three different categories for evaluation: (1) **Training algorithm.** While standard deep neural network training is performed with the back-propagation (BP) algorithm, we investigate various training algorithms, such as neuromorphic learning algorithms with spiking neurons or bio-plausible algorithms with asymmetric feedback for exploiting computational properties for more efficient hardware implementation. (2) Low-precision arithmetic. One of the most powerful methods for increased efficiency in DNN accelerators is through scaling numerical precision. While utilizing low precision numerics for inference phase of DNNs is well studied, training DNNs without performance degradation is relatively more challenging. A novel numerical scheme for training DNNs in various models and scenarios is proposed in this dissertation. (3) **System implementation techniques**. In actual realization of a custom training system in integrated circuits, nearly infinite design space leads to vastly different quality of results depending on dataflow inside the chip, system load balancing, acceleration and gating blocks, et cetera. Different design techniques

which leads to better performance and efficiency are introduced in this dissertation.

First, a neuromorphic learning system for classifying handwritten digits (MNIST) is introduced. This learning system aims to deliver low training overhead while maintaining the training performance of classical machine learning. In order to achieve this goal, a neuromorphic learning algorithm is modified for lower operation count and memory buffer requirement while maintaining or even obtaining higher machine learning performance. Moreover, implementation techniques such as update skipping mechanism and lock-free parameter updates allow even lower training overhead, dynamically reducing training energy overhead from 25.6% to 7.5%. With these proposed methodologies, this system greatly improves the accuracy-energy trade-off in on-chip learning system as well as showing close learning performance to classical DNN training through back propagation.

Second, a programmable DNN training processor with a custom numerical format is introduced. While prior DNN inference accelerators have utilized 8-bit integers, implementing 8-bit numerics for a training accelerator remained to be a challenge due to higher precision requirements in the backward step of DNN training. To overcome this limitation, a custom 8-bit floating point format dubbed 8-bit floating point with shared exponent bias (FP8-SEB) is introduced in this dissertation. Moreover, a processing architecture of 24-way fused-multiply-adder (FMA) tree greatly increases processing energy efficiency per MAC, while complemented with a novel 2-dimensional routing data-path for making use of spatiality to increase data reuse in both forward, backward, and weight gradient step of convolutional neural networks. This DNN training processor is implemented with a custom vector processing unit, acceleration instructions, and DMA in external DRAMs for end-to-end DNN training in various models and datasets. Compared against prior low-precision training processor in ResNet-18 training, this work achieves 2.48× higher energy efficiency, 43% less DRAM accesses, and 0.8%p higher training accuracy.

Both of the designs introduced are fabricated in real silicon and verified both in

simulations and in physical measurements. Design methodologies are carefully eval-

uated using simulations of the fabricated chip and measurements with monitored data

and power consumption under varying conditions that expose the design techniques

in effect. The efficiency of various biologically plausible algorithms, novel numeri-

cal formats, and system implementation techniques are analyzed in discussed in this

dissertations based on the obtained measurements.

keywords: Neural Network Accelerator, Digital Integrated Circuits, Very Large Scale

Integration, Computational Efficiency, Learning Systems, Neuromorphics, Machine

**Learning Accelerators**

**student number**: 2017-22051

iii

# **Contents**

| A۱ | bstrac  | et            |                                                    | i    |

|----|---------|---------------|----------------------------------------------------|------|

| C  | onten   | ts            |                                                    | iv   |

| Li | st of ' | <b>Fables</b> |                                                    | vii  |

| Li | st of l | Figures       |                                                    | viii |

| 1  | Intr    | oductio       | n                                                  | 1    |

|    | 1.1     | Study         | Background                                         | 1    |

|    | 1.2     | Purpos        | se of Research                                     | 6    |

|    | 1.3     | Conte         | nts                                                | 8    |

| 2  | Har     | dware-        | Friendly Learning Algorithms                       | 9    |

|    | 2.1     | Modif         | ied Learning Rule for Neuromorphic System          | 9    |

|    |         | 2.1.1         | The Segregated Dendrites Algorithm                 | 9    |

|    |         | 2.1.2         | Modification of the Segregated Dendrites Algorithm | 13   |

|    | 2.2     | Non-E         | BP Learning Rules on DNN Training Processor        | 18   |

|    |         | 2.2.1         | Feedback Alignment and Direct Feedback Alignment   | 18   |

|    |         | 2.2.2         | Reduced Memory Access in Non-BP Learning Rules     | 23   |

| 3  | Opt     | imal Nu       | umerical Format for DNN Training                   | 27   |

|    | 3.1     | Relate        | d Works                                            | 27   |

|   | 3.2  | Propos  | sed FP8 with Shared Exponent Bias                              | 30 |

|---|------|---------|----------------------------------------------------------------|----|

|   | 3.3  | Trainii | ng Results with FP8-SEB                                        | 33 |

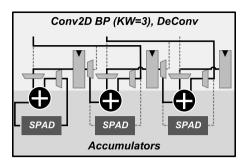

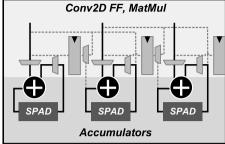

|   | 3.4  | Fused   | Multiply Adder Tree for FP8-SEB                                | 37 |

| 4 | Syst | em Imp  | olementations                                                  | 41 |

|   | 4.1  | Neuro   | morphic Learning System                                        | 41 |

|   |      | 4.1.1   | Bio-Plausibility                                               | 41 |

|   |      | 4.1.2   | Top Level Architecture                                         | 43 |

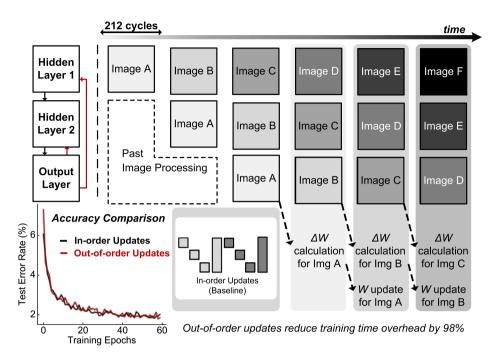

|   |      | 4.1.3   | Lock-Free Weight Updates                                       | 47 |

|   |      | 4.1.4   | Update Skipping Mechanism                                      | 48 |

|   | 4.2  | Low-P   | recision DNN Training System                                   | 51 |

|   |      | 4.2.1   | Top Level Architecture                                         | 52 |

|   |      | 4.2.2   | Optimized Auxiliary Instructions in the Vector Processing Unit | 55 |

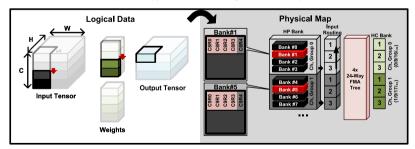

|   |      | 4.2.3   | Buffer Organization                                            | 57 |

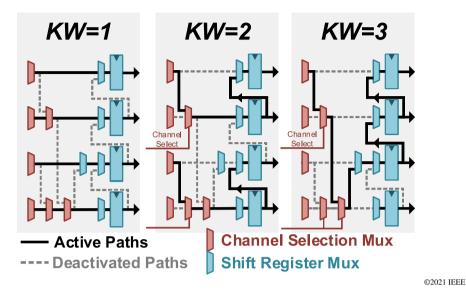

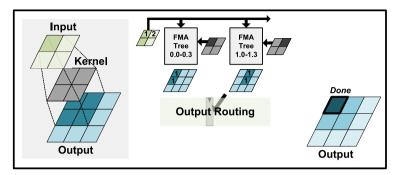

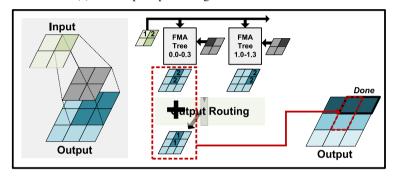

|   |      | 4.2.4   | Input-Output 2D Spatial Routing for FMA Trees                  | 60 |

| 5 | Mea  | sureme  | nt Results                                                     | 70 |

|   | 5.1  | Measu   | rement Results on the Neuromorphic Learning System             | 70 |

|   |      | 5.1.1   | Measurement Results and Test Setup                             | 70 |

|   |      | 5.1.2   | Comparison against other works                                 | 73 |

|   |      | 5.1.3   | Scalability of the Learning Algorithm                          | 77 |

|   | 5.2  | Measu   | rements Results on the Low-Precision DNN Training Processor    | 79 |

|   |      | 5.2.1   | Measurement Results in Benchmarked Tests                       | 79 |

|   |      | 5.2.2   | Comparison Against Other DNN Training Processors               | 89 |

| 6 | Con  | clusion |                                                                | 93 |

|   | 6.1  | Discus  | sion for Future Works                                          | 93 |

|   |      | 6.1.1   | Scaling to CNNs in the Neuromorphic System                     | 93 |

|   |      | 6.1.2   | Discussions for Improvements on DNN Training Processor         | 96 |

|   | 6.2  | Conclu  | ision                                                          | 99 |

Abstract (In Korean)

108

# **List of Tables**

| 2.1 | Hyperparameters used in the Segregated Dendrites Algorithm            | 13 |

|-----|-----------------------------------------------------------------------|----|

| 2.2 | Training* and Test Accuracy with Varying Time Steps                   | 17 |

| 2.3 | Hardware Cost and MNIST Accuracy in Modified SD Algorithms            | 17 |

| 2.4 | Network-in-Network CIFAR-10 Training with Various Learning Rules      | 22 |

| 2.5 | DNN Training Processor Latency and Energy Consumption                 | 25 |

| 3.1 | Energy Consumption & Area Per MAC, Synthesized Results                | 38 |

| 3.2 | PSNR in Matrix Multiplication with Varying N-Way FMAs                 | 39 |

| 4.1 | Performance of SS-MSD algorithm With Different Internal Bit Precision | 44 |

| 4.2 | Capacity and Bandwidth of Banks*                                      | 59 |

| 5.1 | Energy Consumption of Neuromorphic System with Various Configu-       |    |

|     | rations*                                                              | 76 |

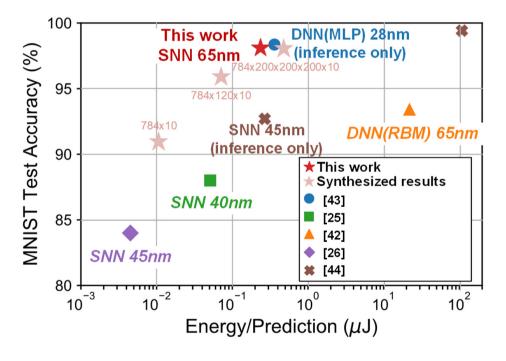

| 5.2 | Comparison of On-Chip Learning Systems                                | 77 |

| 5.3 | Performance of the Processor on Benchmark Models                      | 85 |

| 5.4 | On-Chip and Off-Chip Memory Access in AlexNet Layers                  | 88 |

| 5.5 | Comparison of Neural Network Training Processors                      | 89 |

| 5.6 | Adders, multipliers, and MAC Units with Various FP8 Configurations.*  | 91 |

| 6.1 | DNN Training Processor Power and Area with FP16/FP30 Accumula-        |    |

|     |                                                                       |    |

# **List of Figures**

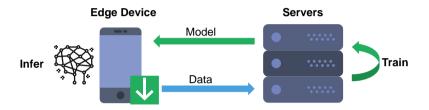

| 1.1 | Three different processing schemes for DNN models                           | 3  |

|-----|-----------------------------------------------------------------------------|----|

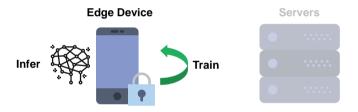

| 1.2 | Sparsity of state-of-art deep learning models have declined signifi-        |    |

|     | cantly compared to their predecessors                                       | 4  |

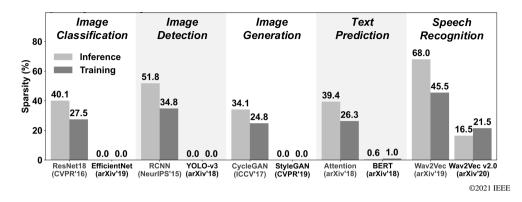

| 1.3 | More error-sensitive tasks may result in quality of results degradation     |    |

|     | in 8-bit fixed point math                                                   | 5  |

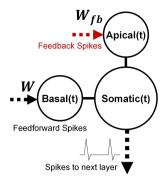

| 2.1 | Structure of the hidden neurons in the Segregated Dendrites algorithm.      | 11 |

| 2.2 | Illustration of network behavior and interconnect in forward and target     |    |

|     | phases                                                                      | 11 |

| 2.3 | Illustration of modified hidden neuron structure. Basal dendrites are       |    |

|     | omitted, and dendrite potentials are directly calculated from spikes        |    |

|     | rather than through post synaptic potentials                                | 14 |

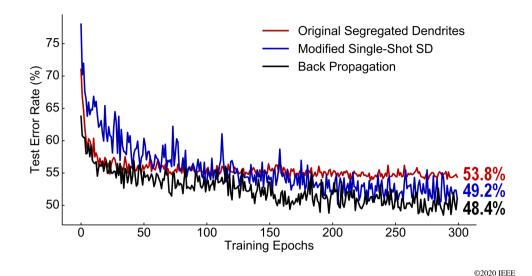

| 2.4 | Test error rate on MNIST dataset for different versions of the segre-       |    |

|     | gated dendrites algorithm.                                                  | 16 |

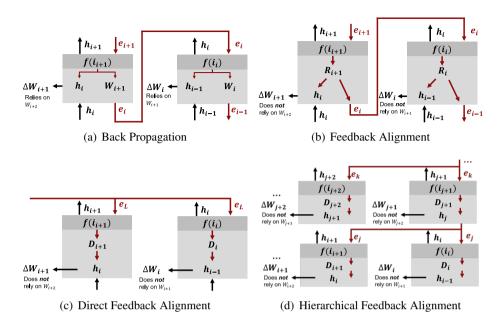

| 2.5 | Illustration of how errors are calculated in different learning algorithms. | 20 |

| 2.6 | Hardware advantages of using HFA learning rules                             | 23 |

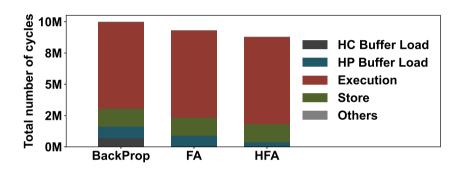

| 2.7 | Breakdown of bio-plausible learning rule execution in ResNet-18 back-       |    |

|     | ward pass                                                                   | 25 |

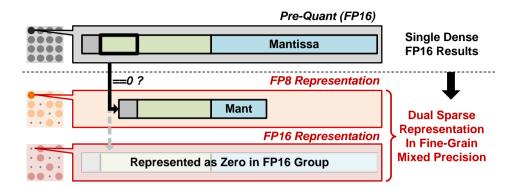

| 3.1 | An illustration of the fine-grain mixed-precision training scheme in-       |    |

|     | troduced in [1]                                                             | 28 |

| 3.2  | An illustration of the hybrid-fp8 arithmetic block introduced in [5]        | 29 |

|------|-----------------------------------------------------------------------------|----|

| 3.3  | An illustration of the dual-representation problem in block floating point. | 30 |

| 3.4  | Illustration of FP8-SEB. Biases are tracked during each computation         |    |

|      | pass with overflow/under-utilization flag to adjust to dynamic range        |    |

|      | changes                                                                     | 31 |

| 3.5  | Matrix multiplication in FP8-SEB. Convolution operations could be           |    |

|      | carried out similarly without re-quantization, as biases are shared across  |    |

|      | entirety of the tensor.                                                     | 33 |

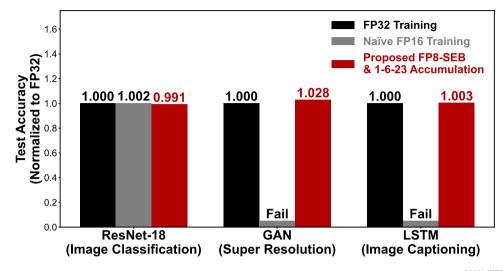

| 3.6  | Comparison of trained accuracy on selected tasks. Half-precision train-     |    |

|      | ing, shown in gray, fails for GAN and LSTM task while FP8-SEB with          |    |

|      | FP30 accumulators perform on par with models trained with full pre-         |    |

|      | cision                                                                      | 35 |

| 3.7  | Generated super-resolution images, trained in FP32 (shown on left)          |    |

|      | and FP8-SEB (shown on right).                                               | 36 |

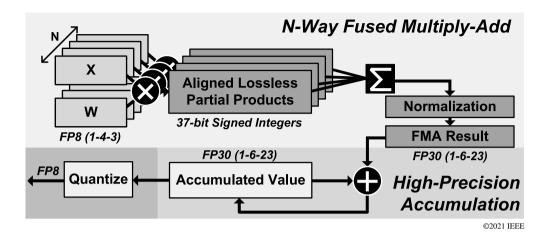

| 3.8  | FMA trees implementation. Partial products are added together in loss-      |    |

|      | less dimensions of 37-bit integers                                          | 37 |

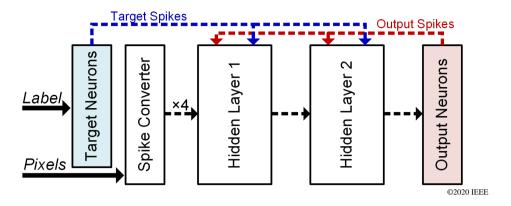

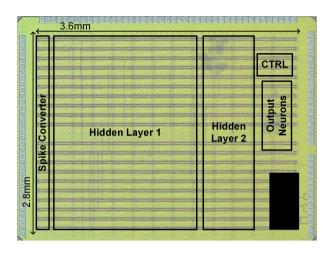

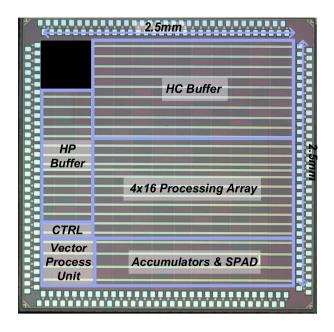

| 4.1  | A top-level view of implemented neuromorphic system                         | 44 |

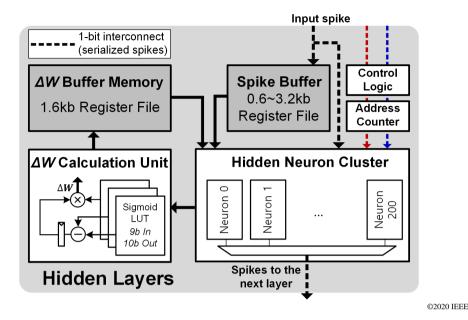

| 4.2  | Block diagram of components in a hidden layer                               | 45 |

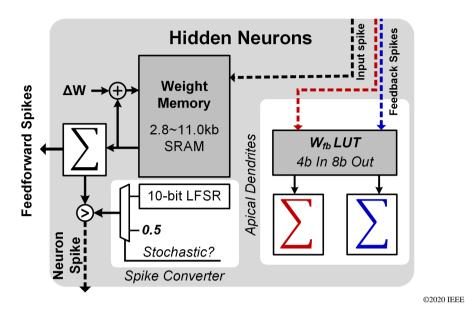

| 4.3  | Block diagram of components in a hidden neuron                              | 46 |

| 4.4  | Diagram of lock-free parallel processing.                                   | 48 |

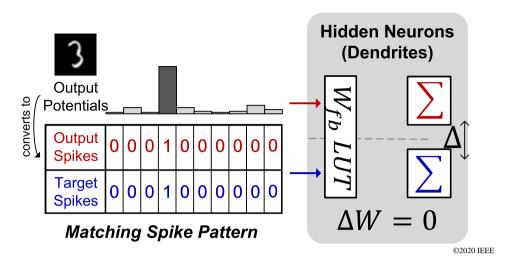

| 4.5  | Illustration of a case where output and target spikes match exactly,        |    |

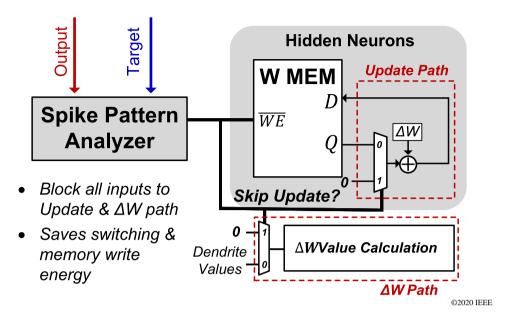

|      | where update values become zero                                             | 49 |

| 4.6  | Disabling the update path through monitoring the spike pattern              | 50 |

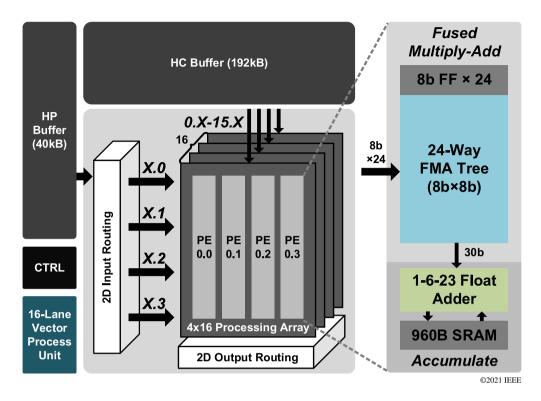

| 4.7  | Top level block diagram of the DNN training processor                       | 51 |

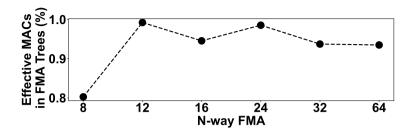

| 4.8  | Ratio of valid MACs with varying $N$ in N-way FMA trees in ResNet-          |    |

|      | 18 processing                                                               | 52 |

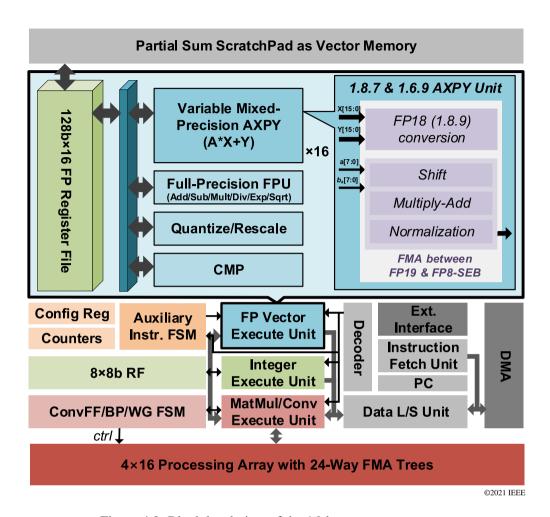

| 4.9  | Block level view of the 16-lane vector processor                            | 54 |

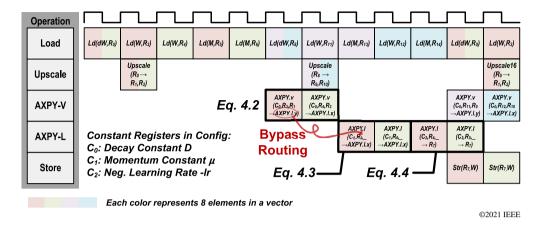

| 4.10 | Cycle-by-cycle operation of the optimized SGD instruction                   | 57 |

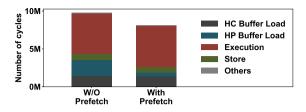

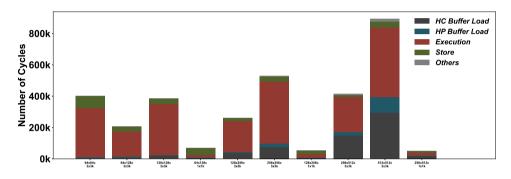

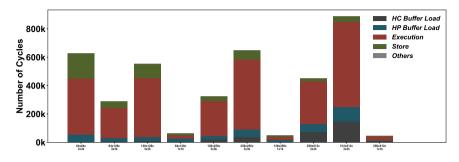

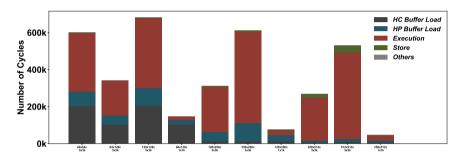

| 4.11 | Breakdown of processor states in terms of number of cycles                | 58 |

|------|---------------------------------------------------------------------------|----|

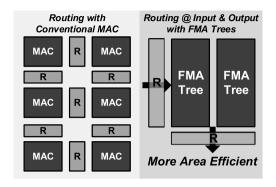

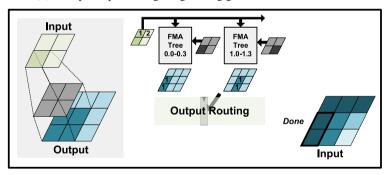

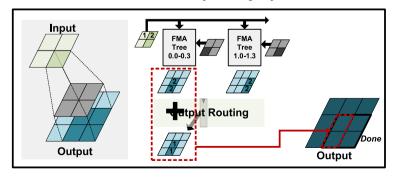

| 4.12 | The routing at inputs and outputs for tree based processing, compared     |    |

|      | against conventional routing units that is implemented between pro-       |    |

|      | cessing elements                                                          | 60 |

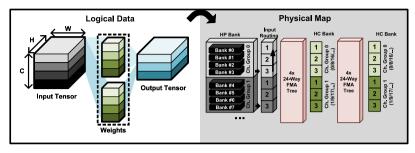

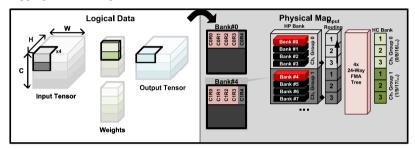

| 4.13 | Illustration of convolution feedforward processing steps in 3×3 kernel    |    |

|      | size                                                                      | 62 |

| 4.14 | Input routing unit in implementation for different cases of kernel widths |    |

|      | for illustration.                                                         | 63 |

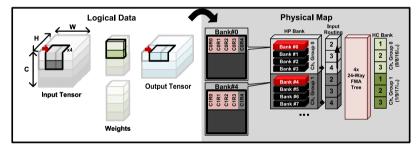

| 4.15 | Illustration of convolution backward functionality                        | 66 |

| 4.16 | Illustration of the 2D output routing unit                                | 67 |

| 5.1  | Die photo of the neuromorphic learning system                             | 71 |

| 5.2  | Diagram of the FPGA design for automated testing in the neuromor-         |    |

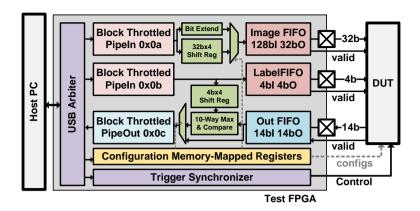

|      | phic learning system                                                      | 72 |

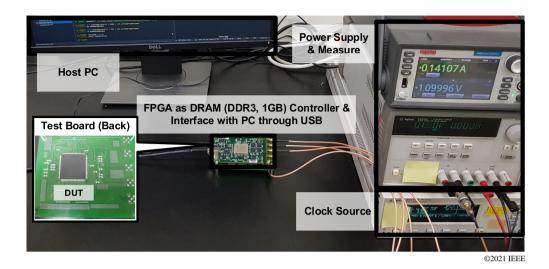

| 5.3  | Test environment setup for real time measurement and verification of      |    |

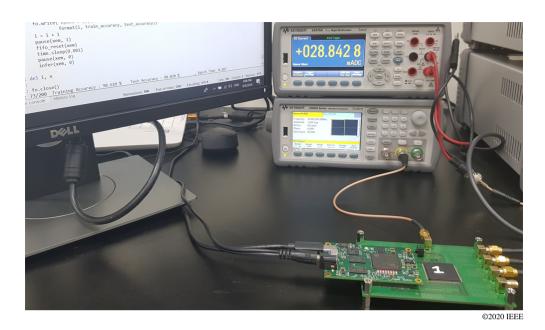

|      | the fabricated learning system.                                           | 74 |

| 5.4  | The update skipping rate and training energy normalized over infer-       |    |

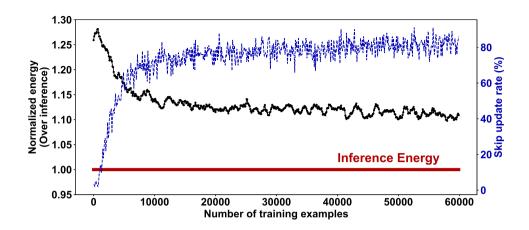

|      | ence energy is plotted.                                                   | 75 |

| 5.5  | Plot of MNIST test accuracy and energy consumption per image for          |    |

|      | various learning systems                                                  | 75 |

| 5.6  | Using fully connected network with size of 1024-512-10 for CIFAR-         |    |

|      | 10 classification, trained with original SD, modified SD, and back        |    |

|      | propagation.                                                              | 78 |

| 5.7  | Die photograph of the fabricated DNN training processor                   | 79 |

| 5.8  | Integrated test environment for automated measurement and verifica-       |    |

|      | tion of the DNN training processor                                        | 80 |

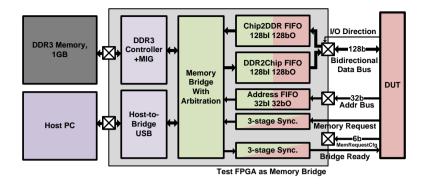

| 5.9  | Diagram of the test FPGA serving as memory bridge                         | 81 |

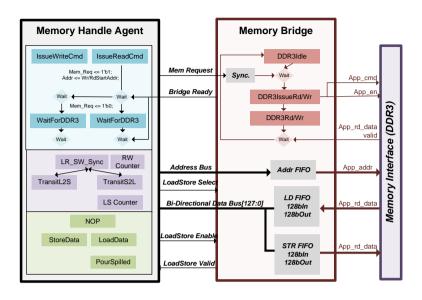

| 5.10 | Block diagram of the custom memory transfer protocol                      | 83 |

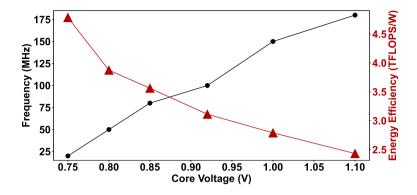

| 5.11 | Performance-Efficiency trade-off graph with core voltage                  | 85 |

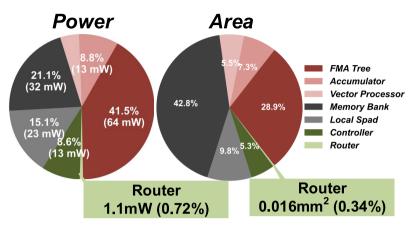

| 5.12 | Area and power breakdown of the DNN training processor. Layer con-      |    |  |

|------|-------------------------------------------------------------------------|----|--|

|      | figuration is for conv-ff with 256 input channels, 256 output channels, |    |  |

|      | 3×3 kernel size on a 14×14 image size                                   | 87 |  |

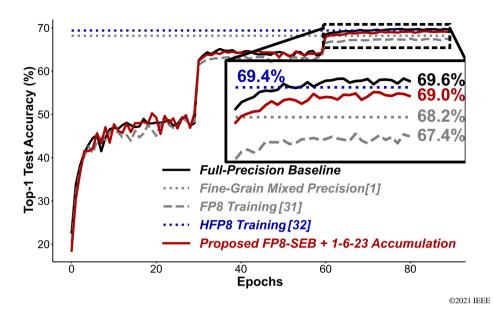

| 5.13 | Training graph for different low-precision DNN training methods on      |    |  |

|      | ResNet-18 ImageNet classification benchmark                             | 90 |  |

|      |                                                                         |    |  |

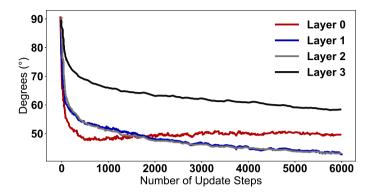

| 6.1  | Alignment of each layers in a 4-layer fully-connected network to the    |    |  |

|      | target matrix in the modified Segregated Dendrites                      | 94 |  |

| 6.2  | Processor state breakdown per layer in the backward and weight gra-     |    |  |

|      | dient phase of ResNet-18 training                                       | 98 |  |

### Chapter 1

#### Introduction

#### 1.1 Study Background

The recent advances in deep learning algorithms have driven the need for specialized hardware systems that process compute-intensive deep neural networks (DNNs) in an energy-efficient manner. Accordingly, many research and industrial application-specific integrated circuits (ASIC) and processing units designed for neural network acceleration have been proposed and deployed for efficient processing [1, 2, 3, 4, 5, 6, 7, 8, 9, 10]. Generally, processing of DNNs consist of two different types of processing phases. The first type is called inference, where a deep learning model is used on real data from end users where DNN models are used for performing practical tasks such as image detection, generating super-resolution images, translating sentences to other languages, etc. The other type of processing is called training, or learning, where DNN models' parameters are fit and adjusted according to some learning rule, based on showing filtered data, sometimes with labeled data and at other times without labels to the DNN model.

While both training and inference of DNN models were first processed inside data centers, using graphical processing units (GPUs) and sometimes with customized hardware such as tensor processing units (TPUs) [10], other processing schemes with

inference near the edge device of the end user were also being adapted. Works such as [7, 38] were part of SoC systems inside mobile devices, intended for inference of DNN models. These processing styles have the advantage that this processing style 1) shows less latency due to routing between edge device and data centers being avoided, 2) does not require network connection for performing inference, and 3) could avoid private data being sent to data centers.

While these two processing styles are categorized by the place where inference operations occur, another interesting processing scheme is performing training on edge devices, as shown in Figure 1.1. The first advantage of training on the edge devices is that neural networks customized for each end user such as customized next-word prediction could be served without violating one's privacy. Moreover, a training scheme called federated learning [12] could be deployed. Federated learning is a novel processing training scheme where the end user's devices are used to calculate the gradient values of parameters in a model based on the data on that device. Only these gradients, not the private data, are aggregated to the main server sporadically to update the DNN model for training. However, in order to realize edge-device training, an energy-efficient method for DNN training must first be satisfied.

One of the most reliable and concrete method for building more energy efficient DNN processor is through scaling numerical precision in the processing models, exploiting the numerical robustness of DNN models. For inference phase of DNN models, use of 8-bit integers with 32-bit accumulators became one of the standard practices [13] while some extreme works [14] reduced down to using only single bit representations for both weights and activations for inference, although this method suffered from some loss of machine learning task performance. However, the numerical robustness displayed during inference phase of DNN models could not be said the same for training the same models. When training DNN models with conventional back-propagation (BP) algorithm, a pioneering work [15] showed that training neural networks even for a simple machine learning task such as MNIST digit classification showed accuracy

(a) Processing in both inference and training on servers.

(b) Processing training in servers, and inference on edge devices.

(c) Processing both training and inference on the edge devices.

Figure 1.1: Three different processing schemes for DNN models.

degradation when gradients, weights and activations were quantized to 8-bit fixed point numbers, although some compensation techniques such as stochastic rounding [15] could be deployed for better training convergence. More recent works [16] demonstrated optimization methods which provide better results using fixed-point arithmetic on larger models, but still suffer from machine learning task performance degradation compared against models trained with full precision. Therefore, it could be concluded that larger arithmetic units and data transmissions are typically required for training a DNN model compared against inference for the same model.

Moreover, the changing environments in DNN models deployed for training and

Figure 1.2: Sparsity of state-of-art deep learning models have declined significantly compared to their predecessors.

inference also calls for different designs that meets the challenges that new models face. For example, many of the prior works that builds either inference or training DNN hardware were designed under the assumption that 8-bit integers provide enough precision for inference without quality degradation, and that the ReLU (Rectified Linear Unit) activation function commonly used provide ample sparsity in the activation maps. However, both of these assumptions have quickly changed in more recent stateof-art DNN models. For example, the deep learning community has come to favor other nonlinear activation functions such as Leaky Relu or Swish [35, 11]. This was due to some of the weaknesses of the traditional ReLU function such as gradient underflow for generative models or being weak against adversarial gradient attacks [11]. As such, the analysis of the change in sparsity of activation maps in many state-of-art models in different machine learning benchmarks shows a decline in average sparsity in activation maps compared to their predecessors. We analyzed state-of-art models in image classification, image generation, image recognition, language modeling, and speech recognition, shown in Figure 1.2. This figure implies that future DNN processors could not rely on sparsity for gaining more energy efficiency out of standard DNN models deployed, requiring a design that could perform efficiently not just on models with sparse activations, but also perform reliably on DNN models with dense activation maps.

(a) Low resolution image.

(b) Enhanced with full precision. (c) Enhanced with 8-bit integer.

Figure 1.3: More error-sensitive tasks may result in quality of results degradation in 8-bit fixed point math.

Moreover, the numerical precision requirements of *inference* are getting higher. DNN accelerators must account to not just image classification models, but hold robust numerical precision for more error-sensitive models such as generative models. To illustrate this point, a low-resolution image shown in Figure 1.3(a) is enhanced with two different versions (model with full-precision arithmetic and a model with 8-bit integer arithmetic) of a super-resolution generative model, ESRGAN [47] with 23-layer residual-in-residual block architecture. The full-precision model showed a PSNR of 27.79dB compared to the original image, with the generated result shown in Figure 1.3(b). The 8-bit integer model showed a PSNR of 22.43dB compared to the original image, with the generated result shown in Figure 1.3(c). In summary, our analysis on a super-resolution task showed a PSNR degradation of 5.56dB, not only with quantitative degradation but with qualitative degradation as well, displaying clear artefacts affecting the quality of generated image.

These environmental changes offer new challenges faced by mobile deep learning processors; they must process non-sparse networks efficiently, maintain higher precision for more challenging tasks, and provide features for training neural networks with minimal hardware overhead.

#### 1.2 Purpose of Research

As discussed in section 1.1, the drive for building low-power DNN training system has increased, while numerical scaling of DNN training proves to be more error-prone compared to its inference operations. In this background, this research proposes new methods for building more energy efficient DNN training systems while maintaining the same level of accuracy. Moreover, these methods are verified and evaluated in real integrated circuits systems that were taped out and verified on a silicon level in real time to show concrete evidence for the validity of the newly proposed design techniques.

In more detail, the proposed design methods could be categorized into three different areas of optimization. (1) First category is the training algorithm itself, where some learning rules such as neuromorphic algorithms that are considered to be more energy efficient compared against back-propagation based learning rules in conventional DNN training [18]. (2) The next area of optimization is in the precision scaling. This work proposes a novel floating point arithmetic that has distinct characteristics from standard IEEE floating point, designed specifically for training neural networks on various machine learning tasks. (3) Lastly, design techniques for digital circuits that could exploit properties of the learning algorithms and the numerical precision pipeline are proposed and evaluated.

The energy efficiency of the proposed design techniques in these three different areas of optimization are evaluated and analyzed through two real digital integrated circuits systems designed and taped out for this research. The first design is a neuromorphic learning processor [19], which is designed using a modified version of neuromorphic algorithm proposed in [20]. Works such as [25, 26, 46] have demonstrated the energy efficiency of neuromorphic algorithms in integrated circuits systems. However, they either lack enough training performance for machine learning performance on par with state-of-art DNN models [25, 26], or they are focused more only on the inference phase of neuromorphic networks and could not be utilized for training neu-

romorphic networks [46]. The neuromorphic processor introduced in this thesis aims to build a neuromorphic learning system that is fit for training deep learning models that are comparable to models trained with back-propagation algorithms.

The next design is a DNN training processor [21] for processing many different types of DNN models, fit for end-to-end general-purpose training. This design is built using a custom 8-bit floating point arithmetic and has been verified for real time training in selected DNN models. This DNN training processor aims to verify the efficiency of the custom 8-bit floating point, as well as proving the energy efficiency of the novel routing scheme that makes use of spatiality in all stages of DNN training for reducing data access.

Through the two designs, this thesis contributes to current research into DNN training processors in the following directions:

- Modification of existing neuromorphic algorithm for hardware implementation

- System implementation techniques such as update skipping and lock-free parameter updates

- Proposing novel 8-bit floating-point number system with shared exponent bias for DNN training

- N-way fused multiply-add trees for energy-efficient training

- Flexible routing scheme for spatial processing in tree-based processing architectures

- Extending bio-plausible learning rules to DNN training processor for hardware efficiency.

#### 1.3 Contents

The rest of the paper is organized as follows. In chapter 2, training algorithms are discussed, including modifications that were made to an existing neuromorphic algorithm and how these modifications could benefit hardware implementation. Moreover, it is shown how training algorithms that are not based on back-propagation could be beneficial in terms of hardware efficiency. Chapter 3 gives detail on the low-precision arithmetic implemented in our DNN training processor, including experiment results conducted on various DNN models. Chapter 4 introduces the two low power learning systems that implements the research discussed in chapter 2 and 3, manufactured in custom integrated circuits design. Moreover, digital circuit design techniques in those systems for low power learning is introduced. Chapter 5 discuss the analysis results of the two systems, validating the ideas discussed in the prior chapters in simulations and measurements, as well as comparing the results to similar state-of-art integrated circuits systems. Chapter 6 discusses future research directions based on the works presented in this thesis and concludes the paper.

### Chapter 2

### **Hardware-Friendly Learning Algorithms**

#### 2.1 Modified Learning Rule for Neuromorphic System

#### 2.1.1 The Segregated Dendrites Algorithm

The segregated dendrites [20] algorithm is a supervised neuromorphic algorithm, originally proposed with multi-layer perceptron (MLP) architecture and demonstrated on MNIST digits classification task. The original algorithm implements bio-plausible neurons with three capacitance-coupled compartments, training with asymmetric feedback paths that connect hidden layer neurons and output neurons together through spiking channels. This algorithm achieves 96.1% MNIST test accuracy through using fixed and random feedback paths, similar to feedback alignment [23] and direct feedback alignment [24] algorithms. The Segregated Dendrites algorithm has more similarities to the direct feedback alignment algorithm, as it only contains direct feedbacks from the output neurons from the hidden neurons. This direct feedback path is desirable for hardware implementation for two main reasons: (1) processing time overhead that is required for sequentially propagating the error gradients from the topmost layer to the bottom-most layer, realizing parallel processing for more efficient processing and (2) in cases where output neurons' numbers are significantly smaller compared against hidden neurons, the connections for the feedback paths are much simpler in

implementation.

We first inspect the computational modeling of the neuron's behavior in the Segregated Dendrites algorithm, which are derived from the observations made in biological neurons. The neurons used in the Segregated Dendrites algorithm is made up of three compartments, apical, basal, and somatic dendrites which each hold electrical potentials that are interdependent on each other. First, the apical dendrites accumulate feedback spikes from the output neurons, translating the spikes they receive to electrical potentials through a kernel function that smooths out the received spikes through a time decayed signal to a Post-Synaptic Potential (PSP). Similarly, basal dendrites accumulate feedforward spikes from previous layer neurons with the same PSP mechanism. The somatic dendrite voltage ( $V_S$ ) is determined through the capacitance coupling of apical and basal dendrite voltages ( $V_A$  and  $V_B$ , respectively), as shown in equation 2.1, with coupling constants denoted by  $g_A$ ,  $g_B$ , and  $g_L$ .

$$dV_s/d_t = g_L * V_s(t) + g_B * (V_B(t) - V_S(t)) + g_A * (V_A(t) - V_S(t))$$

(2.1)

The determined somatic voltage is stochastically translated to spikes with a sigmoid function to interpret the voltage as probability. Unlike leaky integrate and fire neuron models, the somatic potential does not drop after firing. The illustration of the hidden neurons are shown in Figure 2.1.

The apical and basal dendrites are determined through synaptic weights and post synaptic potentials (PSPs). Each of the PSPs are calculated from the kernel function in equation 2.2 and incoming spikes that correspond to that specific synaptic connection, as shown in equation 2.3. This kernel function is also known as the *dual exponential function*.

$$k(t) = (e^{-t/\tau_L} - e^{-t/\tau_S})/(\tau_L - \tau_S)$$

(2.2)

$$PSP_{j}(t) = \sum_{k \in spikes \ of \ j} k(t_{-}t_{k})$$

(2.3)

Figure 2.1: Structure of the hidden neurons in the Segregated Dendrites algorithm.

Figure 2.2: Illustration of network behavior and interconnect in forward and target phases.

Where  $t_k$  denotes the time frame of the spike k,  $\tau_L$  and  $\tau_S$  each refers to long and short time constants, and j refers to the  $j^{th}$  neuron. These PSPs are translated to apical and basal dendrite potentials through equation 2.4 and equation 2.5, where  $W_{ff}$  refers to feedforward weights and  $W_{fb}$  refers to feedbackward weights.

$$V_i^A(t) = \sum_{o=0}^{M-1} PSP_o^{fb}(t) * w_{i,o}^{fb}$$

(2.4)

$$V_i^B(t) = \sum_{j=0}^{N-1} PSP_j^{ff}(t) * w_{i,j}^{ff}$$

(2.5)

In supervised training of the segregated dendrites, two phases exist to facilitate

learning: the unsupervised forward phase and the supervised target phase. While different number of time steps could be allocated for the forward and target phases, the original paper suggests using 50 time steps for the forward phase and 20 time steps for the target phase. During the forward phase of training, all spikes are generated freely, with neurons' dendrite potentials determined by equations 2.1 2.5. Note that the while this phase is named 'forward', the feedback spikes are still transferred to the hidden neurons from the output neurons, making this phase self-supervised. The apical dendrites during the forward phase are determined through the freely generated output spikes without labels forcing output neuron behavior. In this forward phase, the average potentials are recorded to be used for weight update value calculation. However, since the nature of the algorithms are stochastic, the original paper suggests waiting some time periods to allow the network to reach a more stable plateau point. The original paper suggests waiting 20 time steps, averaging over the timesteps number 20 to 50 for generating the average potentials of apical, somatic dendrites as well as the PSPs for weight update value calculation. This forward phase behavior in the network is illustrated in Figure 2.2(a). After the forward phase, the target phase is initiated. Note that the potentials inside the neurons are not reset after a forward phase: the transition from the forward and target phase is not abrupt but a smooth process. The behavior of the neural network is the same as the forward phase everywhere except inside the output neurons, where the output neuron somatic voltage is nudged with a teaching signal to suppress all output neurons but the output neuron corresponding to the target label j. This suppression and excitation is executed through a teaching signal  $I_i(t)$  given in equation 2.6.

$$I_{i}(t) = \begin{cases} E_{E} - V_{S,i}(t) & when i = j \\ E_{I} - V_{S,i}(t) & otherwise \end{cases}$$

(2.6)

Where  $E_E$  refers to the excitatory signal constant and  $E_I$  refers to the inhibitory signal constant. The teaching signal current  $I_i$  flows to the somatic dendrite per time step, being accumulated to the right half side of the somatic dendrite differential equation

Table 2.1: Hyperparameters used in the Segregated Dendrites Algorithm.

| Notation in equations Value |      | Description                                     |  |

|-----------------------------|------|-------------------------------------------------|--|

| $g_A$                       | 0.05 | Coupling conductance between apical and somatic |  |

| $g_B$                       | 0.6  | Coupling conductance between basal and somatic  |  |

| $g_L$                       | 0.3  | Coupling conductance between somatic time steps |  |

| $	au_L$                     | 10   | Long depression constant                        |  |

| $	au_S$                     | 3    | Short potentiation constant                     |  |

| $E_E$                       | 8    | Excitatory current in target phase              |  |

| $E_I$                       | -8   | Inhibitory current in target phase              |  |

given in equation 2.1. This target phase is illustrated in Figure 2.2(b).

After the target phase, the averaged apical dendrite potential is used with the saved values from the forward phase to gain the weight update value, with the formula shown in equation 2.7. This weight update value is not added directly to the feedforward weight, but first multiplied with a learning rate hyperparameter. This learning rate differs from layer to layer in the original Segregated Dendrites algorithm. The table of hyper parameters that were described through equations that were used in this section is summarized in Table 2.1.

$$\Delta W_{ff} = \overline{PSP_{ff}} * \sigma'(\overline{V_{S,f}}) * (\sigma(\overline{V_{A,f}}) - \sigma(\overline{V_{A,t}}))$$

(2.7)

#### 2.1.2 Modification of the Segregated Dendrites Algorithm

We first re-implement the CPU-based code authors provide in [20] in a GPU-accelerated framework PyTorch [49] for faster simulations of the algorithm to evaluate the training performance of any modifications to the algorithm. This re-implementation utilizes matrix-based computation in GPUs, which results in over x20 faster simulation times. Based on this GPU-based framework, we explore the original algorithm through two

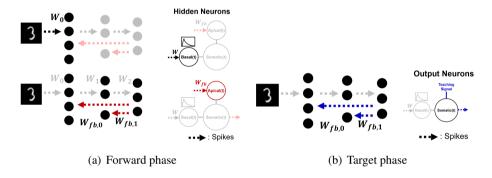

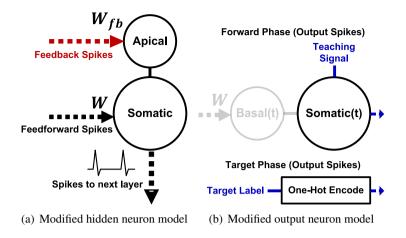

Figure 2.3: Illustration of modified hidden neuron structure. Basal dendrites are omitted, and dendrite potentials are directly calculated from spikes rather than through post synaptic potentials.

different directions: changing the neuron behavior and using different number of time steps for its impact on training performance.

For the first step in modifying the segregated dendrites algorithm for more suitable hardware implementation, we first simplify the neuron architecture to behave more similarly to point neurons in conventional deep learning. As shown in Figure 2.3, basal dendrite is omitted from determining neuron behavior and spike probability. Instead, somatic dendrite potentials are directly calculated from the input spikes and the synaptic weights. Similarly, PSPs denoted in equation 2.3 are removed from apical dendrites and apical dendrite potentials are directly calculated from feedback spikes and the feedback synaptic weights, as shown in equations 2.8 and 2.9.

$$V_S(t) = spikes_{ff}(t)W_{ff} (2.8)$$

©2020 IEEE

$$V_A(t) = spikes_{fb}(t)W_{fb} (2.9)$$

Moreover, during the target phase, we change the teaching signal behavior from soft constraining output neuron firing patterns to directly applying one-hot encoded target label as the output neuron firing pattern, which would mean that the apical dendrite potential in equation 2.9 would change to 2.10 during the target phase.

$$V_A(t) = W_{fb}[LabelIndex] (2.10)$$

Inspection of the simplified neuron behavior suggests that the neuron potentials are now temporally independent and not reliant on post-synaptic potentials and differential equations. While the original SD algorithm required a minimum waiting period for neuron potentials to reach a stable operating plateau point, this new property that is observed leads us to conclude that the new neuron behavior allows waiving the constraint on the minimum waiting period due to the neurons converging quickly compared to the original algorithm. As such, shorter time periods are allowed compared against the original algorithm, and we experiment with using shorter time step training for the modified version of the segregated dendrites algorithm, even using single-time step for forward and target phases. Moreover, as the weight update formula in equation 2.7 only demand apical dendrite potential of the target phase (which are inferred deterministically from equation 2.10), we could skip target phase altogether, requiring only single-pass computation for training in this modification in the time domain. Through using single-steps for processing weight updates, we observe that the learning rule described in equation 2.7 could be simplified to equation 2.11. Although not implemented in our hardware, further optimization that saves one sigmoid operation could be made through altering the update formula to 2.12, which is an approximation of equation 2.11.

$$\Delta W_{ff} = spikes_{ff}\sigma'(V_{S,f}) \odot (\sigma(V_{A,f}) - \sigma(V_{A,t}))$$

(2.11)

$$\Delta W_{ff} = spikes_{ff}\sigma'(V_{S,f}) \odot \sigma(V_{A,f} - V_{A,t})$$

(2.12)

The changing of the neuron model is dubbed 'modified segregated dendrites', and its

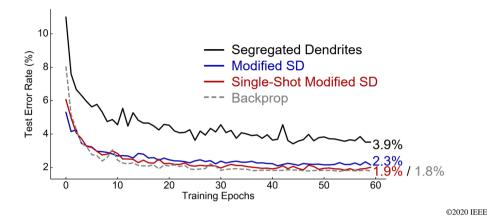

Figure 2.4: Test error rate on MNIST dataset for different versions of the segregated dendrites algorithm.

single-shot implementation is dubbed 'single-shot modified segregated dendrites'.

The test accuracy on the MNIST digit classification task is shown in Figure 2.4 for segregated dendrites, modified segregated dendrites, the single-shot modified segregated dendrites, as well as the back-propagation trained version of the same MLP architecture. While it may not be surprising that simplified neuron architectures elicit better classification accuracy, it is interesting that using single-shot results from a stochastic network reports better results compared against averaging over multiple time steps. This result is speculated to stem from the effect of increased stochasticity, which is known to yield regularization on training machine learning models [15]. Table 2.2 better supports this speculation, as it shows a trend of decreased train accuracy but increased test accuracy as time step is shortened, which is the desired effect of regularization.

Through these modifications on the original segregated dendrites algorithm, we could expect low overhead for training in terms of operations and memory required for implementing the training phase of the Segregated Dendrites algorithm. Through simplifying the neuron behavior, we no longer need to compute basal dendrites voltages to indirectly couple somatic dendrite potentials, which leads to faster convergence

Table 2.2: Training\* and Test Accuracy with Varying Time Steps

| Number of<br>Time Steps | Train Accuracy | Test Accuracy |  |

|-------------------------|----------------|---------------|--|

| 1                       | 98.54%         | 98.17%        |  |

| 2                       | 99.33%         | 98.25%        |  |

| 5                       | 99.50%         | 97.95%        |  |

| 10                      | 99.61%         | 98.12%        |  |

| 20                      | 99.56%         | 97.81%        |  |

\*Trained using batch size of 1

©2020 IEEE

Table 2.3: Hardware Cost and MNIST Accuracy in Modified SD Algorithms

|                            | Clock Cycles | MNIST<br>Accuracy | Training<br>Buffer Size | OP/Image |

|----------------------------|--------------|-------------------|-------------------------|----------|

| Original SD                | 14,000       | 96.1%             | 47.2Kb                  | 29,379K  |

| Modified SD                | 10,010       | 97.7%             | 38.4Kb                  | 20,741K  |

| Single-Shot<br>Modified SD | 212          | 98.10%            | 7.6Kb                   | 804K     |

©2020 IEEE

of somatic dendrite potentials and more even plateaus across the neurons. Moreover, the target phase could be omitted to a single time step as the output neuron behavior is deterministic. Moreover, the single-stage computations greatly reduces operation and memory requirements, reducing over ×50 as the 50 time step long forward phase is reduced to a single time step. This result is summarized in Table 2.3

In summary, the final bio-plausible algorithm that is based on modifications to the Segregated Dendrites algorithm using direct spike-only feedback requires an operational overhead of 8K accumulates and 620 sigmoid activations for computing equation 2.11, compared to its inference phase. As the inference phase of our algorithm is functionally similar to binarized DNN models, comparison against conventional BP-based learning rule gives good insight into how much overhead our training algorithm incurs. Denoting the  $i^{th}$  layer activation as  $a_i$ ,  $i^{th}$  layer hidden variable before activations.

tion as  $h_i$ , and L as the evaluated loss during training, the computations required are given as equation 2.13 and 2.14.

$$\delta L/\delta W_i = a_{i-1}\sigma'(h_i)\delta L/\delta a_{i+1} \tag{2.13}$$

$$\delta L/\delta a_i = W_i \sigma'(h_i) \delta L/\delta a_{i+1} \tag{2.14}$$

Using the same configurations of the layers in our implementation (784-200-200-10 architecture), we obtain 240.8K MAC operations and 400 sigmoid activations for obtaining the required weight update values. If binarization of the activations and gradients are applied, similar to our spike-based learning rule, the MAC operation in equation 2.13 could be removed and further reduces to 42K operations and 400 sigmoid activations, which is still over 80% reduction in terms of the number of MAC counts. Therefore, it could be concluded that this modified algorithm that only utilizes feedback spikes for training exhibit lower computational requirements over the back-propagation counterpart.

#### 2.2 Non-BP Learning Rules on DNN Training Processor

#### 2.2.1 Feedback Alignment and Direct Feedback Alignment

While neuromorphic learning rules that resemble more biological neuron behaviors suffers from performance degradation compared against deep-learning models on more difficult tasks such as ImageNet classification, recent research on bio-plausible learning rules such as feedback alignment and direct feedback alignment [27, 28] has shown that it could scale with moderate performance degradation in modern deep learning models for ImageNet classification. These bio-plausible learning rules, unlike neuromorphic algorithms with a biological neuron behavior, utilizes point neurons similar to conventional deep learning while using a different learning rule that is not based on back-propagation. As illustrated in Figure 2.5, conventional back-propagation propa-

gate errors through equation 2.15, where W refers to weights, e refers to error gradients, f' refers to derivative of activation nonlinear function f, a refers to activation, and i refers to the layer number.

$$e_i = W_{i+1,i}^T \odot e_{i+1} f'(a_{i+1}), \quad i \in \{1, 2, 3, \dots, L-1\}$$

(2.15)

This error gradient that are propagated to different layers of the neural networks are used in turn with *weight gradient* phase to generated final weight gradients. Feedback alignment (FA) algorithm and direct feedback alignment (DFA) algorithm are similar in this approach that the error gradients that are computed are used with *weight gradient* algorithms that compute final weight gradients. However, the main difference between the bio-similar algorithms (FA and DFA) and back-propagation is in the method in which the *error gradients* are computed. Feedback alignment computes the error gradients through propagate errors, similar to back-propagation, but is different in the feedback matrix that is used for next-layer error gradient computation. The feedback alignment algorithm is shown in equation 2.16. This error gradient computation path is the same except for the feedback matrix R, whereas back-propagation in equation 2.15 utilizes the weight W that was used for feedforward computation is used. Note that the R is not updated after random initialization.

$$e_i = R_{i+1,i}^T \odot e_{i+1} f'(a_{i+1})$$

(2.16)

Direct feedback alignment (DFA) is deviates more from back-propagation in comparison with FA algorithm. Instead of using propagating error gradients from the prior layer for computation, error gradients in each of the layers are directly computed from the top layer error  $e_L$  and a direct feedback matrix D as shown in equation 2.17.

$$e_i = D_i^T \odot e_L f'(a_{i+1})$$

(2.17)

Figure 2.5: Illustration of how errors are calculated in different learning algorithms.

The motivation for developing FA and DFA algorithms is to solve the *credit assignment* problem. In conventional back-propagation in equation 2.15, the feedforward weight  $W_{i+1,i}$  is used for propagating the error from layer i+1 to layer i. In a biological brain, this would mean that a feedforward synaptic connection from a neuron in layer i to layer i+1 is also used to transmit feedback signals from that same pair of neurons in layer i+1 to layer i. The problem lies in the fact that biological synaptic connections are uni-directional: in other words, back propagation could not physically be the method that our brains *learn*. However, in FA and DFA algorithms, learning is enabled without symmetric feedback and feedforward synaptic connections. Through the use of a separate feedback pathway, the learning is enabled while solving the credit assignment problem, which in turn would mean these algorithms could act as a candidate for how the real biological brain enables learning.

In terms of computational characteristics of the FA and DFA algorithms, we notice that the feedback weights R and D are generated randomly at initialization and remain constant throughout training, with no update mechanism for the feedback weights.

Moreover, DFA often suffers from scaling issues especially in CNNs both in terms of training convergence and computational complexity. The original DFA implementation require each pixels in the activation map of the CNN layers to hold feedback weights to each of the topmost layer neurons, resulting in significant increase in memory usage in deeper and larger CNN models.

In addition to FA and DFA algorithms, we propose a similar algorithm that propagates errors through hierarchical feedback paths, as shown in Figure 2.5(d). Error gradient is propagated in a hierarchical manner, where an error  $e_j$  in a local head layer is shared between the local groups with direct feedback matrix D through equation 2.18, and we hence call this error path Hierarchical Feedback Alignment algorithm (HFA).

$$e_i = D_{i,j}^T \odot e_j f'(a_{i+1}), \quad i \in \{Layers Connected to Local Head j\}$$

(2.18)

The idea behind the HFA algorithm is to bring the ideas in FA and DFA together. DFA could not scale to deeper CNNs and fails to converge as the error signals from the topmost layers are not as relevant to low-level features in the convolution neural networks. However, the hierarchical structure of DFA could provide merits to hardware implementation while providing a sort of bypass network for training deep layers, similar to Residual Networks [30]. Our HFA algorithm combines the merits of DFA with convergence stability of FA, providing a *hierarchical* feedback pathway by partially applying DFA to locally grouped layers, with the local head layer *j* serving as the topmost layer in DFA. In other words, instead of connecting to either the top layer (as in DFA) or to the very next layer (as in FA), layers are grouped hierarchically so that a layer group i j connects to a local head layer j. Using HFA, we expect to increase hardware efficiency while facilitating learning to a higher degree of convergence compared against conventional FA or DFA. Note that when using the HFA algorithm in convolutional neural networks, there exist a limitation on how layers could be grouped together. The layer groups must satisfy the condition that the tensor shape of the error

Table 2.4: Network-in-Network CIFAR-10 Training with Various Learning Rules

| Learning Rule            | CIFAR-10 Test Accuracy |

|--------------------------|------------------------|

| Back-Propagation         | 87.59%                 |

| FA                       | 82.03%                 |

| DFA                      | 10.00%                 |

| HFA                      | 85.90%                 |

| Mixture-HFA(0.8)&BP(0.2) | 87.23%                 |

gradient in each of the group layers must be the same as the error gradient shape of the local head layer. This condition should be met for proper mapping of gradients shown in equation 2.18.

In order to check the validity of the proposed algorithm, we trained a Network-In-Network [29] convolutional neural network on the CIFAR-10 dataset. We used the same training hyperparameters in back-propagation, feedback alignment, direct feedback alignment, and the proposed hierarchical feedback alignment to compare the test accuracy result. The results are shown in Table 2.4. The HFA algorithm outperforms feedback alignment algorithm by more than 3%p, and is degraded from back-propagation baseline by 1.7%p. While performance degradataion is still noticeable in HFA algorithm, this is still a major improvement over FA or DFA, which fails to converge to meaningful results.

An interesting method of training that could be implemented to provide viable learning performance while providing hardware efficiency is through alternating between back propagation and HFA algorithm in a single training session. For example, in 80% of the examples shown to a network in a single epoch, the network was trained using HFA rule while the remaining 20% was trained using back propagation. The end result show almost no degradation at 87.23%, whereas back propagation trained the network to accuracy of 87.59%. Through the use of the hybrid training method, one is able to exploit the hardware efficiency of HFA algorithm (discussed in the next sec-

Figure 2.6: Hardware advantages of using HFA learning rules.

tion 2.2.2) while maintaining training performance. In our implementation, switching between HFA and back-propagation require very little software overhead as simply branching to different code execution address provide switching.

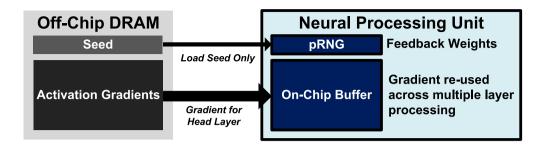

### 2.2.2 Reduced Memory Access in Non-BP Learning Rules

One of the advantages of the bio-plausible learning rules discussed in chapter 2.2.1 is that the feedback weights are generated randomly and are not updated for training. Due to this characteristic, these feedback weights could be generated on-chip with proper random seed control without accessing external memory. In the DNN training processor discussed in chapter 2.2, random number generation using LFSRs are implemented on-chip to take advantage of the bio-plausible learning rule, which allow specifying random number generation seeds with a 128-bit number initialization. Moreover, the HFA algorithm proposed in chapter 2.2.1 could be further advantageous for processing, as the gradient in the local head layer j could be reused multiple times for more efficient processing. The advantages in hardware for HFA algorithm is shown in Figure 2.6. In summary, off-chip memory access are minimized through using seed-based random weight load and head layer gradient re-use, which shows potential for minimizing memory latency and reduced power at DRAM controllers and at the DRAM itself.

Based on this observation, we create a test suite for comparing and analyzing back propagation algorithm and the two other bio-plausible learning rules (FA and HFA)

discussed in section 2.2.1. This test suite is created with minimal alterations to the DNN training processor discussed in section 4.2 to better exploit the characteristics of the bio-plausible learning rules. First, a pseudo-random number generator that creates vectors of uniform distributions are implemented with minimal logic based on XOR's and LFSRs. Moreover, existing convolution backward instruction in the DNN training processor makes use of two unused flag bit fields in the instruction to (1) indicate whether to use random feedback weight generation for processing, and (2) whether to use hierarchical feedback for parallel processing of multiple layers. The control FSM is also modified to skip weight feedback loading, and instead points to LFSRs for generating weights. Last, the memory address generator for storing result gradients from convolution backward instruction for hierarchical feedback is modified for storing different tensors in parallel. These three modifications comes at a minimal cost in hardware logic, as the main processing blocks, vector processing units, and the SRAM memory that takes up more than 95% of the total power and area budget is left untouched.

With this test suite, we compared and analyzed naïve convolution layer backward instruction execution with back propagation and convolution layer backward instruction with random number generation in place of weight loading. Results that include processor energy consumption, executed with a synthesized netlist are shown in Table 2.5. Two different configurations are used – the first configuration is part of a CIFAR-10 network-in-network training with batch size of 1, while the second configuration is a layer in ImageNet ResNet-18 training [30] with a batch size of 4. The first configuration is mainly bottlenecked with loading the weight from external memory to the processor, which results in FA saving around 63.1% in total execution time and 53.3% in total energy. However, this savings are quickly dwarfed when larger batch sizes and larger images are deployed for training, as the model parameter sizes remain constant while activations and gradients are increased by O(n) with increasing batch sizes. In order to test the bio-plausible algorithms in scaled environments, larger batch sizes and

| Table 2.5: DNN Training Processor Latency and Energy Consumption | Table 2.5: DNN | Training Processor | Latency and Ene | rgy Consumption |

|------------------------------------------------------------------|----------------|--------------------|-----------------|-----------------|

|------------------------------------------------------------------|----------------|--------------------|-----------------|-----------------|

| Configuration                     | <b>Learning Rule</b> | Latency (µs) | Energy(µJ) |

|-----------------------------------|----------------------|--------------|------------|

| 128×128 channels, 8×8 features,   | BackProp             | 292.69       | 44.20      |

| 3×3 kernel size, Batch Size=1     | FA                   | 108.00       | 20.63      |

| 128×128 channels, 28×28 features, | BackProp             | 10272.65     | 1980.24    |

| 3×3 kernel size, Batch Size=4     | FA                   | 9901.91      | 1886.86    |

|                                   | HFA*                 | 6850.29      | 1552.48    |

<sup>\*3</sup> layers are attached to a local head.

Figure 2.7: Breakdown of bio-plausible learning rule execution in ResNet-18 backward pass.

larger image feature sizes are used in the next configuration. In this configuration of using batch size of 4 on ImageNet layer configuration, memory access is more constrained by the gradient rather than the weight due to large image sizes and a larger batch size. We could observe that while FA does not scale well in this configuration (as DRAM accesses are dominated by gradients), HFA still manages to reduce total execution time by 23.3% as a result of sharing gradients and increased parallelism.

Moreover, we conducted a cycle-accurate experiment with register transfer level (RTL) code of the DNN training processor with support for optimized bio-plausible rules to evaluate system level latency and performance bottlenecks in such conditions, with the result shown in Figure 2.7. For the backward pass of ResNet-18 on the ImageNet dataset with batch size of 4, using back-propagation algorithm require 10.00M cycles in ResNet-18, with 3.06M cycles (30.6% of total execution time) spent

on memory stalls. In FA implementation on our DNN training processor, same ResNet-18 backward pass required 9.29M cycles, with 2.36M cycles (25.4% of total execution time) spent on memory stalls. In HFA implementation, through sharing gradients across layers with same conv-bp configuration, we observed total execution cycle of 8.77M cycles, with 1.84M cycles (21.0% of total execution time) on memory stalls. In conclusion, compared against conventional back-propagation algorithm on ResNet-18 ImageNet training, FA require 22.9% less memory stall time and 7.1% less execution time, while HFA require 39.9% less memory stall time and 12.3% less execution time.

# Chapter 3

# **Optimal Numerical Format for DNN Training**

### 3.1 Related Works

As discussed in section 1, scaling numerical precision for low power training proves to be more difficult compared against scaling numerical precision for inference in DNN models. Some related works [1, 31, 32, 33, 34] have addressed this problem. Work in [1] proposed using a mixed precision of 8 bits and 16 bits for representing tensors in DNN training, while maintaining the trained accuracy of full-precision based models. The method presented in [1] first represents tensors in 8-bit floating point, while leaving the elements that are out of the dynamic range of the 8-bit floating point and hence not representable with the exponents of the 8-bit floating point numbers to be zero. Instead, these out-of-range elements are represented in the complementing 16-bit floating point tensor while the elements that has been expressed as non-zero value in the 8-bit floating point tensors are zero in this complementing 16-bit floating point tensor. This method has the major drawback that it requires representing same tensors twice in terms of 8 bits and 16 bits, which they mitigate through zero-skipping features, as shown in Figure 3.1.

Work in [31] proposes using 8 bits of floating point and 16-bit accumulators for DNN training. The major contribution of the work in [31] is identifying the point

Figure 3.1: An illustration of the fine-grain mixed-precision training scheme introduced in [1].

where DNN training performance is lost when using 8-bit or similar low-precision floating point numeric system. It states that the major source of loss of precision is due to *swamping* effect, which is a known phenomena that occurs when two floating point numbers with one of the number having magnitudes of larger absolute value over the other are added together. When the exponent difference between the two addition operands are significantly large, precision loss is inevitable as the mantissa of the smaller number is lost in the addition and re-normalization process. This swamping effect is identified as the main source of precision loss, and the work in [31] suggests using a chunking accumulation, where groups of MAC operations are carried out before being added to the actual accumulator, in the hopes of relieving the absolute value difference between the accumulator and the multiply-added values in the dot product operations in DNN training. Moreover, other auxiliary training methods such as using 16-bit copies of the original weights and using stochastic rounding is proposed to aid DNN training in the bulk of computation carried out in 8-bit floating point numbers.

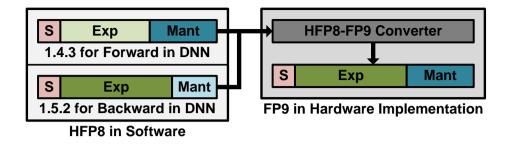

Work in [32], which succeeds the work in [31], proposed using a hybrid representation which utilizes 1.4.3 in the forward pass and 1.5.2 format during the backward and weight gradient path. (Henceforward, 1.X.Y refers to using 1 bit sign, X bit exponents, and Y bit mantissa) The purpose of this hybrid approach is to compensate the

Figure 3.2: An illustration of the hybrid-fp8 arithmetic block introduced in [5].

training performance loss that is observed in some machine learning taks and models observed following the straightforward 1.4.3 quantization format used in the work of [31]. Through using different arithmetic of 1.4.3 and 1.5.2, this work demonstrates that using two different types of 8-bit precision for DNN training shows a training performance without any accuracy loss. This hybrid method incurs some additional hardware, whereas the hardware implementation work in [5]showed that this cost could be reduced through a hybrid implementation of FP9 format (1.5.3) and an FP8-FP9 converter, as shown in Figure 3.2.

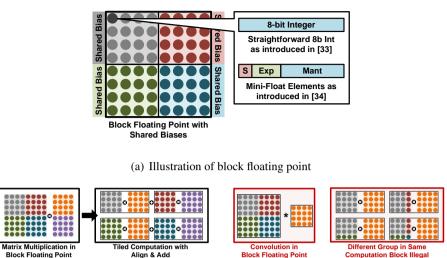

Lastly, works in [33, 34] shows utilizing block floating point for DNN training. Work in [33] proposed grouping tiles of N×N elements with 10-bit exponent value, where each of the elements are represented with 8-bit mantissa. Work in [34] generalizes the work in [33] to using a mini float representation for each of the elements instead of using only mantissa in the elements, as shown in 3.3(a). This allows exponents to differ in the elements and share biases instead of exact exponent values. This strategy works well for matrix multiplication and dot products, where the cost of accumulating the tiled results including aligning different biases could be amortized over the length of the dot product, as shown in 3.3(b). However, when applied to spatial architectures for processing convolutional layers, this strategy incurs more overhead compared to simple matrix multiplication as overlapping components inside a tensor to be convolved require special handling (such as representing same element twice or

(b) Matrix multiplication in block floating point

Align & Add

(c) Convolution in block floating point

Figure 3.3: An illustration of the dual-representation problem in block floating point.

using smaller block sizes), as shown in Figure 3.3(c). This is exemplified in an DNN accelerator [45] that adopts block floating point for training, which exhibits 78% lower TOP/s for ResNet-101 (which is consisted mostly of convolutions) compared against LSTM models (consisted mostly of matrix multiplications).

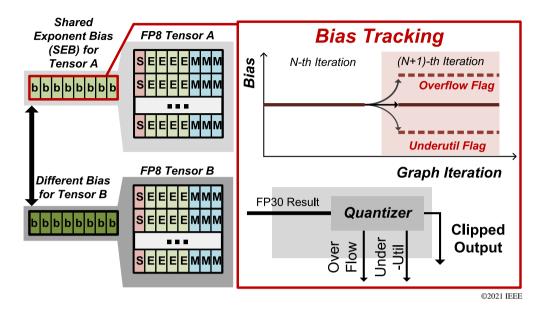

#### 3.2 **Proposed FP8 with Shared Exponent Bias**

To provide a more reliable and hardware-efficient quantization method for training DNN models with 8-bit floating point numbers, this research proposes a quantization method called FP8 with Shared Exponent Bias (FP8-SEB) that does not require realignments or hybrid computing hardware that effectively produces 9-bit floating point computation units. FP8-SEB represents elements of a tensor with 1-bit sign, 4bit exponents, and 3-bit mantissa, while sharing a common exponent bias for all the elements of the tensor. Unlike the work in [33, 34], we group all of the elements of the output activation in a layer as a tensor, weight in a layer as a single tensor, etc., instead of tiling those tensors in small groups. To compensate for the shift of dynamic range in

Figure 3.4: Illustration of FP8-SEB. Biases are tracked during each computation pass with overflow/under-utilization flag to adjust to dynamic range changes.

tensors during progression, we automatically modify the exponent bias value through tagging each tensor with flags that indicate whether it has been overflown (where the bias values are increased by 1) or underutilized (similarly, bias values are decreased by 1). The illustration of this FP8-SEB is shown in Figure 3.4.

In this numerical format, the real value for an FP8-SEB number that is represented with bias b, 1-bit sign value s, 4-bit exponent value e, and 3-bit mantissa value m could be retrieved with equation 3.1.

$$x^{Q} = (-1)^{s} 2^{e-127+b} (1+m/8)$$

(3.1)

As this representation format require using different bias values on each of the tensor elements that are grouped together, the additional cost that is associated with using different bias values for each tensor should be analyzed carefully since they are an overhead that do not exist for other quantization methods. Firstly, in terms of memory cost, the cost for storing the shared exponent bias should be considered. Our

analysis shows that this cost is negligible compared against the cost of actual elements of the tensor: for example, in ResNet-18 ImageNet training, the cost of shared biases, including the flag data for overflow and under-utilization, accounts for only 0.003% of the entire memory allocated for ResNet-18 training.

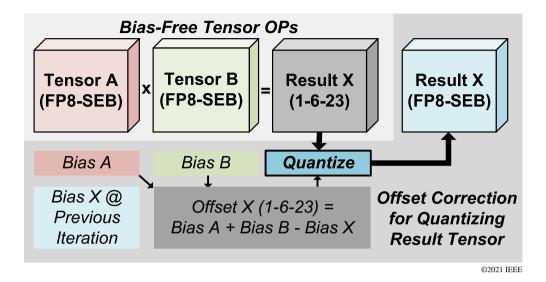

Next, it should be considered whether hardware implementation require extra logic to account for the fact that biases could take any value rather than being fixed. For some arithmetic operations such as addition between FP8-SEB tensors, this case is true as during normalization, realignment logic should be applied for arbitrary biases that are not known priori. However, for matrix multiplication and convolution operations, careful observations show that we scarcely require extra logic for using different biases that are not determined during computation. To provide insight into the implementation method that avoids extra logic, a dot product operation between two vectors  $X_1$  and  $X_2$  with length N is shown in equation 3.2. By substituting  $x_1$  and  $x_2$  with equation 3.1 and rearranging, we obtain equation 3.3.

$$y_{dot} = \sum_{i=0}^{n-1} x_{1,i}^Q x_{2,i}^Q$$

(3.2)

$$y_{dot} = 2^{b_1 + b_2 - 254} \sum_{i=0}^{n-1} (-1)^{s_{1,i} + s_{2,i}} 2^{e_{1,i} + e_{2,i}} (1 + m_{1,i}/8) (1 + m_{2,i}/8)$$

(3.3)

Observation into equation 3.3 show that computations related to the unfixed biases could be decoupled from the bulk of dot product computation inside the summation. Thus, after bias-free operations are complete, only on the accumulated value that we need to apply re-quantization accounting for the bias values. As this biases are fixed across all tensors, this could be easily scaled to matrix-matrix multiplications or convolutions. This computation process for matrix multiplication in FP8-SEB is shown in Figure 3.5. Therefore, only hardware overhead for matrix multiplication and convolution in FP8-SEB is in re-quantization step after bulk of computation is finished. As an example, suppose that FP30 (1.6.23 format) is chosen for accumulator precision, and

Figure 3.5: Matrix multiplication in FP8-SEB. Convolution operations could be carried out similarly without re-quantization, as biases are shared across entirety of the tensor.

the result target is expressed as  $Y_Q$  with a known exponent bias  $b(Y_Q)$ . Re-quantization is carried out as equation 3.4-3.6 from a final result  $Y_acc$  in FP30 format, shown in equation 3.7:

$$S_{Y_Q} = S_{Y_{acc}} (3.4)$$

$$e_{Y_Q} = clip(e_{Y_{acc}} - (b_1 + b_2 - b_{Y_Q}) + 254, 0, 15)$$

(3.5)

$$m_{Y_Q} = round(m_{Y_{acc}/2^{20}}) \tag{3.6}$$

$$Y_{acc} = (-1)^{S_{Y_{acc}}} 2^{e_{Y_{acc}}} (1 + m_{Y_{acc}}/2^{23})$$

(3.7)

# **3.3** Training Results with FP8-SEB

One of the advantages of using explicit separate biases in each of the tensors used during training is that they provide more inter-tensor dynamic range while maintaining intra-tensor dynamic range. Dynamic adjusting shown in Figure 3.4 makes sure that all of the dynamic range in the 4-bit exponents are utilized, while allowing different tensors such as weight gradients, weights, and activations, which have huge difference in terms of their dynamic ranges [17], to all be expressed accurately. Therefore, our numerical format correctly addresses the shift in dynamic range in tensors due to training progression.

However, the accumulation precision must be considered for processing matrix multiplication accurately without final neural network training degradation, as suggested in [31]. While FP8 tensors provide high intra-tensor dynamic range for representing unique data, expressing such large dynamic ranges with limited precision inevitably results in lower grain precision in between data-points, leading to devastating precision loss during accumulation. For instance, suppose an addition occurs between two positive FP8 elements (1'b0,  $E_a$ ,  $M_a$ ) and (1'b0,  $E_b$ ,  $M_b$ ), where the element with larger exponent value is assigned a such that  $E_a \geq E_b$ . The addition process including alignment is expressed as equation 3.8.

$$C_{preQ} = 2^{E_a} (1 + \frac{M_a}{2^3}) + 2^{E_b} (1 + \frac{M_b}{2^3}) = 2^{E_a} (1 + \frac{M_a + 2^{E_b - E_a} M_b + 2^{3 - E_a}}{2^3}) \quad (3.8)$$

Observing the right hand term of the equation 3.8 in combination of quantization equation 3.1, we could conclude that the resulting output FP8 value (1'b0,  $E_c$ ,  $M_C$ ) is always equal to (1'b0,  $E_a$ ,  $M_a$ ) when  $2^{E_b-E_a}M_b+2^{3-E_a}<0.5$ , resulting in quantization loss. This phenomena is exemplified in real DNN training experiments when such conditions are met. Note that this is condition is always met when  $E_a>E_b+4$ , meaning that all addition between elements with exponent difference larger than 4 are ignored entirely. When naïvely using the same FP8-SEB representation for intermediary accumulation during matrix multiplication operations, experiments showed 5%p accuracy degradation for even simple tasks such as LeNet training on CIFAR-10 and failed to converge at all on deeper networks such as ResNet-18.

Thus, it is required to choose a higher precision format for accumulation without

©2021 IEEE

Figure 3.6: Comparison of trained accuracy on selected tasks. Half-precision training, shown in gray, fails for GAN and LSTM task while FP8-SEB with FP30 accumulators perform on par with models trained with full precision.