# This electronic thesis or dissertation has been downloaded from Explore Bristol Research, http://research-information.bristol.ac.uk

Author: Yang, Feiyuan Title: Electrical optimization of AlGaN/GaN devices for power and RF applications

#### **General rights**

Access to the thesis is subject to the Creative Commons Attribution - NonCommercial-No Derivatives 4.0 International Public License. A copy of this may be found at https://creativecommons.org/licenses/by-nc-nd/4.0/legalcode This license sets out your rights and the restrictions that apply to your access to the thesis so it is important you read this before proceeding.

#### Take down policy

Some pages of this thesis may have been removed for copyright restrictions prior to having it been deposited in Explore Bristol Research. However, if you have discovered material within the thesis that you consider to be unlawful e.g. breaches of copyright (either yours or that of a third party) or any other law, including but not limited to those relating to patent, trademark, confidentiality, data protection, obscenity, defamation, libel, then please contact collections-metadata@bristol.ac.uk and include the following information in your message:

· Your contact details

Bibliographic details for the item, including a URL

• An outline nature of the complaint

Your claim will be investigated and, where appropriate, the item in question will be removed from public view as soon as possible.

# Electrical Optimization of AlGaN/GaN Devices for Power and RF Applications

Hard-Switching, Trapping Effects, Breakdown and Gate Leakage

By

FEIYUAN YANG

H. H. Wills Physics Laboratory UNIVERSITY OF BRISTOL

A dissertation submitted to the University of Bristol in accordance with the requirements for award of the degree of DOCTOR OF PHILOSOPHY in the Faculty of Science.

JANUARY 2022

Word count: ~ 26,000

ABSTRACT

he reliability issues of AlGaN/GaN HEMTs for power and RF applications have attracted much attention from the research community in order to improve their application range. In this thesis, multiple reliability issues of AlGaN/GaN HEMTs are covered with detailed characterizations, simulations and analysis, which include hard-switching, trapping effects, breakdown and gate leakages.

By comparing a set of wafers with different  $SiN_x$  passivation stoichiometries, HEMTs with Si-rich passivation layer stand out and show negligible dynamic ON-resistance after stress. In measurements of the hard- and soft-switching with tens of nano seconds switching time, it turned out that hard-switching would lead to significant self-heating and produce hot electrons. However, the temperature cools down after a few hundreds nano seconds after the switching while the surface charge trapping is the dominant reason for the dynamic ON-resistance increase.

The study of multiple types of stress including ON-state, OFF-state and substrate bias were performed on the same devices. The dynamic ON-resistance shows a 60% increase after the ONstate stress compared to OFF-state stress on the sample with a stoichiometric  $Si_3N_4$  passivation layer. The devices with additional sense node contacts enable the potential mapping between the gate and drain for ON-state and OFF-state, which helps to determine the distribution the charge trapping. By comparing the trap information extracted from the transient dynamic ON-resistance, the charge trapping appeared after the ON-state stress is proven to be associated with the deep buffer traps, likely due to the carbon acceptors in the GaN. Moreover, electroluminescence measurements show agreements with the potential mapping, and it also implies that the field plates possibly blocked the light emitted from the gate edge.

RF AlGaN/GaN-on-SiC HEMTs are used for the breakdown study. The drain injected technique is used for avoiding device degradation while measuring the breakdown voltage as a function of the gate voltage. The drain current was kept as a constant while the gate voltage was swept during the measurements. The devices show a 2-stage breakdown feature as the first breakdown plateau is associated with the punch-through within the GaN channel layer under the gate, whereas the second breakdown plateau is due to the increasing carbon doping density as the punch-through current is forced down to the doped GaN layer. The electroluminescence results suggest that additional leakage paths are triggered with a high drain bias.

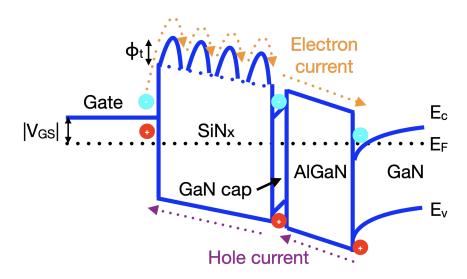

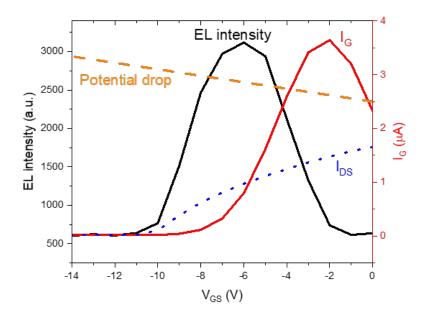

Finally, a gate leakage study is carried out on the MIS AlGaN/GaN HEMTs. The bell-shape gate leakage curves for semi-ON state suggest the gate current is contributed by the electron current and hole current independently. The electrons mainly pass through the  $SiN_x$  barrier by Poole–Frenkel emission whereas the hole current comes from the impact ionization. In addition, the peak shift of the bell shapes between the electroluminescence and the gate leakage indicates a potential competition mechanism.

#### **DEDICATION AND ACKNOWLEDGEMENTS**

would like to express my sincere gratitude to my supervisors Prof. Martin Kuball and Prof. Michael J. Uren, for both of whom have supported and guided me through my 4-year PhD by your profound knowledge without any hesitation. I would like to acknowledge EPSRC and IQE Plc for funding my PhD project, without which I can hardly move forward. Besides, I would like to thank Dr. Dong Liu for recommending me to join the CDTR from the very beginning.

CDTR is a wonderful team where I stay during my PhD and I really appreciate all the former and current members. It is my great pleasure to meet you. My special thanks go to Dr. Stefano Dalcanale and Dr. Serge Karboyan who have taught me the fundamental and advanced techniques in terms of experimental and simulation methods. I would like to thank Yuke Cao, Dr. James W. Pomeroy, Dr. Manikant, and Dr. Thomas Gerrer for our great cooperation in publications. I would like to thank Dr. William M. Waller, Dr. Filip Gucmann, Dr. Hareesh Chandrasekar, Dr. Ben Rackauskas, Taylor Moule, Filip Wach and Cainan Long for whom have ever helped me greatly in experiments or simulations. I would also like to thank Dr. Andrei Sarua and Laura Jeffries for their help regarding the University affairs.

I am grateful to the cooperated companies and labs for providing the test samples. I would like to thank Nexperia and IQE Plc for the GaN HEMT samples provided, and Dr. Mark Gajda and Dr. Trevor Martin for the feedback. I would like to thank the GaN-DaME team and Akash Systems for providing GaN-on-Si/SiC/Diamond samples, especially Dr. Abdalla Eblabla for fabricating the samples. I would like to thank Prof. Patrick Fay from the University of Notre Dame for providing the ferroelectric GaN HEMT samples.

Finally, I would like to express my gratitude to my previous roommate Dr. Chaolong Yang for his generous help. I would like to thank my mother Xiaojie Qin and my father Jianwei Yang for your selfless support throughout my life. My memory also goes to my grandfather Prof. Jun Qin who I have not been able to accompany with in the last second during the COVID pandemic.

# **AUTHOR'S DECLARATION**

declare that the work in this dissertation was carried out in accordance with the requirements of the University's Regulations and Code of Practice for Research Degree Programmes and that it has not been submitted for any other academic award. Except where indicated by specific reference in the text, the work is the candidate's own work. Work done in collaboration with, or with the assistance of, others, is indicated as such. Any views expressed in the dissertation are those of the author.

SIGNED: ...... DATE: .....

# TABLE OF CONTENTS

|    |       |         |                                           |     | Р   | age  |

|----|-------|---------|-------------------------------------------|-----|-----|------|

| Li | st of | Tables  | 5                                         |     |     | xi   |

| Li | st of | Figure  | es                                        |     |     | xiii |

| 1  | Intr  | oducti  | ion                                       |     |     | 1    |

|    | 1.1   | Devel   | opments and Challenges for AlGaN/GaN HEMT | ••• |     | 2    |

|    | 1.2   | Thesis  | s Structure                               | ••• | • • | 4    |

| 2  | The   | oretica | al Background                             |     |     | 7    |

|    | 2.1   | Galliu  | ım Nitride                                | ••• | ••• | 7    |

|    |       | 2.1.1   | GaN Properties                            | ••• | • • | 7    |

|    |       | 2.1.2   | GaN and Other Semiconductors              | ••• | ••• | 9    |

|    | 2.2   | Struct  | ture of AlGaN/GaN HEMT                    | ••• | ••• | 11   |

|    |       | 2.2.1   | Substrate                                 | ••• | ••• | 11   |

|    |       | 2.2.2   | Nucleation and Strain Relief Layer        | ••• | ••• | 12   |

|    |       | 2.2.3   | GaN Epitaxy                               | ••• | ••• | 12   |

|    |       | 2.2.4   | AlGaN/GaN Heterojunction and 2DEG         | ••• | ••• | 13   |

|    |       | 2.2.5   | GaN Cap                                   | ••• | ••• | 14   |

|    |       | 2.2.6   | Passivation                               | ••• | ••• | 14   |

|    |       | 2.2.7   | Contacts                                  | ••• |     | 15   |

|    |       | 2.2.8   | Field Plate                               | ••• |     | 15   |

|    | 2.3   | Device  | e Physics of AlGaN/GaN HEMT               | ••• |     | 16   |

|    |       | 2.3.1   | DC and Pulsed IV performance              | ••• |     | 16   |

|    |       | 2.3.2   | Drain-Induced Barrier Lowering            | ••• |     | 17   |

|    |       | 2.3.3   | Trap                                      | ••• |     | 18   |

|    |       | 2.3.4   | Gate Leakage                              | ••• |     | 18   |

|    |       | 2.3.5   | Hot Electron                              | ••• |     | 19   |

|    |       | 2.3.6   | Electroluminescence                       | ••• |     | 20   |

|    |       | 2.3.7   | Impact Ionization                         | ••• |     | 20   |

|    |       | 2.3.8   | Breakdown                                 |     |     | 21   |

|   | 2.4                                                                                                                                                       | Indust                                                                                                                                               | rial Application of AlGaN/GaN HEMT                                                                                                                     | 21                                                                                                         |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

|   |                                                                                                                                                           | 2.4.1                                                                                                                                                | Power Application                                                                                                                                      | 22                                                                                                         |

|   |                                                                                                                                                           | 2.4.2                                                                                                                                                | RF Application                                                                                                                                         | 23                                                                                                         |

| 3 | Cha                                                                                                                                                       | racteri                                                                                                                                              | zation Techniques                                                                                                                                      | 27                                                                                                         |

|   | 3.1                                                                                                                                                       | Experi                                                                                                                                               | mental Environments                                                                                                                                    | 27                                                                                                         |

|   |                                                                                                                                                           | 3.1.1                                                                                                                                                | Probe Station                                                                                                                                          | 27                                                                                                         |

|   |                                                                                                                                                           | 3.1.2                                                                                                                                                | Characterization Equipment                                                                                                                             | 28                                                                                                         |

|   |                                                                                                                                                           | 3.1.3                                                                                                                                                | Cabling                                                                                                                                                | 30                                                                                                         |

|   |                                                                                                                                                           | 3.1.4                                                                                                                                                | Test Structures                                                                                                                                        | 31                                                                                                         |

|   | 3.2                                                                                                                                                       | Electri                                                                                                                                              | cal Characterization Techniques                                                                                                                        | 32                                                                                                         |

|   |                                                                                                                                                           | 3.2.1                                                                                                                                                | DC IV Measurement                                                                                                                                      | 32                                                                                                         |

|   |                                                                                                                                                           | 3.2.2                                                                                                                                                | Transient Measurement                                                                                                                                  | 32                                                                                                         |

|   |                                                                                                                                                           | 3.2.3                                                                                                                                                | Back bias Measurement                                                                                                                                  | 32                                                                                                         |

|   |                                                                                                                                                           | 3.2.4                                                                                                                                                | Pulsed IV Measurement                                                                                                                                  | 33                                                                                                         |

|   | 3.3                                                                                                                                                       | Electro                                                                                                                                              | luminescence Measurement                                                                                                                               | 34                                                                                                         |

|   | 3.4                                                                                                                                                       | Simula                                                                                                                                               | tion                                                                                                                                                   | 36                                                                                                         |

|   |                                                                                                                                                           | 3.4.1                                                                                                                                                | Electrical Simulation - Silvaco Atlas                                                                                                                  | 36                                                                                                         |

|   |                                                                                                                                                           | 3.4.2                                                                                                                                                | Thermal Simulation - Ansys                                                                                                                             | 38                                                                                                         |

|   |                                                                                                                                                           |                                                                                                                                                      |                                                                                                                                                        |                                                                                                            |

| 4 | Har                                                                                                                                                       | d. and                                                                                                                                               | Soft-switching in Power AlGaN/GaN-on-Si HEMTs                                                                                                          | 41                                                                                                         |

| 4 |                                                                                                                                                           |                                                                                                                                                      | Soft-switching in Power AlGaN/GaN-on-Si HEMTs                                                                                                          | <b>41</b><br>42                                                                                            |

| 4 | 4.1                                                                                                                                                       | Introdu                                                                                                                                              | action                                                                                                                                                 | 42                                                                                                         |

| 4 | $\begin{array}{c} 4.1\\ 4.2\end{array}$                                                                                                                   | Introdu<br>Device                                                                                                                                    | uction                                                                                                                                                 | 42<br>43                                                                                                   |

| 4 | 4.1<br>4.2<br>4.3                                                                                                                                         | Introdu<br>Device<br>Experi                                                                                                                          | uction                                                                                                                                                 | 42<br>43<br>44                                                                                             |

| 4 | <ol> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> </ol>                                                                                            | Introdu<br>Device<br>Experi<br>Simula                                                                                                                | uction                                                                                                                                                 | 42<br>43<br>44<br>47                                                                                       |

| 4 | 4.1<br>4.2<br>4.3                                                                                                                                         | Introdu<br>Device<br>Experi<br>Simula<br>Discuss                                                                                                     | uction                                                                                                                                                 | 42<br>43<br>44                                                                                             |

| 4 | <ol> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> </ol>                                                                               | Introdu<br>Device<br>Experi<br>Simula<br>Discuss                                                                                                     | uction                                                                                                                                                 | 42<br>43<br>44<br>47<br>51                                                                                 |

| 4 | <ol> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ol>                                                                  | Introdu<br>Device<br>Experi:<br>Simula<br>Discuss<br>Conclu                                                                                          | action                                                                                                                                                 | 42<br>43<br>44<br>47<br>51<br>54<br><b>57</b>                                                              |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>Buf</li> <li>5.1</li> </ul>                                        | Introdu<br>Device<br>Experi:<br>Simula<br>Discus:<br>Conclu<br><b>fer Cha</b><br>Introdu                                                             | action                                                                                                                                                 | 42<br>43<br>44<br>47<br>51<br>54                                                                           |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>Buf</li> </ul>                                                     | Introdu<br>Device<br>Experi:<br>Simula<br>Discus:<br>Conclu<br><b>fer Cha</b><br>Introdu                                                             | action                                                                                                                                                 | 42<br>43<br>44<br>47<br>51<br>54<br><b>57</b><br>58<br>59                                                  |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>Buf</li> <li>5.1</li> </ul>                                        | Introdu<br>Device<br>Experi:<br>Simula<br>Discuss<br>Conclu<br><b>fer Cha</b><br>Introdu<br>Device                                                   | action                                                                                                                                                 | <ul> <li>42</li> <li>43</li> <li>44</li> <li>47</li> <li>51</li> <li>54</li> <li>57</li> <li>58</li> </ul> |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>Buf</li> <li>5.1</li> <li>5.2</li> </ul>                           | Introdu<br>Device<br>Experi:<br>Simula<br>Discuss<br>Conclu<br><b>fer Cha</b><br>Introdu<br>Device<br>Experi:                                        | action   under Test   mental Results   tion   sion   sion <b>rge Trapping in Power AlGaN/GaN-on-Si HEMTs</b> action under Test                         | 42<br>43<br>44<br>47<br>51<br>54<br><b>57</b><br>58<br>59                                                  |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>Buf</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> </ul>              | Introdu<br>Device<br>Experi:<br>Simula<br>Discuss<br>Conclu<br><b>fer Cha</b><br>Introdu<br>Device<br>Experi:                                        | action   under Test   mental Results   ation   sion   sion <b>rge Trapping in Power AlGaN/GaN-on-Si HEMTs</b> action   under Test   under Test   ition | 42<br>43<br>44<br>47<br>51<br>54<br><b>57</b><br>58<br>59<br>59                                            |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>Buf</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> </ul> | Introdu<br>Device<br>Experi:<br>Simula<br>Discus:<br>Conclu<br><b>fer Cha</b><br>Introdu<br>Device<br>Experi:<br>Simula                              | action   under Test   mental Results   ation   sion   sion <b>rge Trapping in Power AlGaN/GaN-on-Si HEMTs</b> action   under Test   under Test   ition | 42<br>43<br>44<br>47<br>51<br>54<br><b>57</b><br>58<br>59<br>59<br>62                                      |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>Buf</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> </ul> | Introdu<br>Device<br>Experi:<br>Simula<br>Discuss<br>Conclu<br><b>fer Cha</b><br>Introdu<br>Device<br>Experi:<br>Simula<br>Discuss                   | action                                                                                                                                                 | 42<br>43<br>44<br>47<br>51<br>54<br><b>57</b><br>58<br>59<br>59<br>62<br>63                                |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>Buf</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> </ul> | Introdu<br>Device<br>Experi:<br>Simula<br>Discuss<br>Conclu<br>fer Cha<br>Introdu<br>Device<br>Experi:<br>Simula<br>Discuss<br>5.5.1                 | nction                                                                                                                                                 | 42<br>43<br>44<br>47<br>51<br>54<br><b>57</b><br>58<br>59<br>59<br>62<br>63<br>63                          |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>Buf</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> </ul> | Introdu<br>Device<br>Experi:<br>Simula<br>Discus:<br>Conclu<br><b>fer Cha</b><br>Introdu<br>Device<br>Experi:<br>Simula<br>Discus:<br>5.5.1<br>5.5.2 | action                                                                                                                                                 | 42<br>43<br>44<br>47<br>51<br>54<br><b>57</b><br>58<br>59<br>59<br>62<br>63<br>63<br>63                    |

| 6  | Dra   | in Injected Breakdown in RF AlGaN/GaN-on-SiC HEMTs                      | 71  |

|----|-------|-------------------------------------------------------------------------|-----|

|    | 6.1   | Introduction                                                            | 71  |

|    | 6.2   | Device under Test                                                       | 73  |

|    | 6.3   | Experimental Results                                                    | 73  |

|    | 6.4   | Simulation                                                              | 77  |

|    | 6.5   | Discussion                                                              | 79  |

|    | 6.6   | Conclusion                                                              | 81  |

| 7  | Inve  | estigation of Gate Leakage and Electroluminescence in Power MIS-AlGaN/G | aN- |

|    | on-S  | Si HEMTs                                                                | 83  |

|    | 7.1   | Introduction                                                            | 83  |

|    | 7.2   | Device under Test                                                       | 84  |

|    | 7.3   | Experimental Results                                                    | 84  |

|    | 7.4   | Discussion                                                              | 86  |

|    |       | 7.4.1 Differences of Wafers                                             | 86  |

|    |       | 7.4.2 Origin of Gate Leakages and EL                                    | 87  |

|    |       | 7.4.3 Competition Mechanism                                             | 89  |

|    | 7.5   | Conclusion                                                              | 91  |

| 8  | Con   | clusions                                                                | 93  |

|    | 8.1   | Conclusions of the Work                                                 | 93  |

|    | 8.2   | Future work                                                             | 96  |

| A  | Res   | earch Output                                                            | 99  |

| B  | List  | of Abbreviations                                                        | 101 |

| С  | Silv  | aco Atlas Simulation Code                                               | 103 |

| Bi | bliog | raphy                                                                   | 113 |

# **LIST OF TABLES**

| TAB | LE                                                                                                       | Page |

|-----|----------------------------------------------------------------------------------------------------------|------|

|     | Comparison of bulk semiconductor material properties                                                     |      |

| 4.1 | LPCVD $\mathrm{SiN}_x$ properties by wafer                                                               | 43   |

| 5.1 | Thermal conductivities $\kappa$ and their temperature-dependent coefficients $\eta$ at room temperature. | 63   |

# **LIST OF FIGURES**

Page

|      |                                                                                          | _  |

|------|------------------------------------------------------------------------------------------|----|

| 2.1  | Primitive cell of the hexagonal wurtzite GaN structure.                                  | 8  |

| 2.2  | First Brillouin zone and band structure of the wurtzite GaN structure with high          |    |

|      | symmetry points                                                                          | 8  |

| 2.3  | Schematic of a AlGaN/GaN HEMT structure.                                                 | 11 |

| 2.4  | Polarization and band diagram of AlGaN/GaN heterojunction.                               | 13 |

| 2.5  | Ideal band diagrams of the Schottky contact and the Ohmic contact (n-type semicon-       |    |

|      | ductor)                                                                                  | 14 |

| 2.6  | Schematic of the source field plate.                                                     | 15 |

| 2.7  | IV characteristics on a GaN-on-diamond HEMT                                              | 16 |

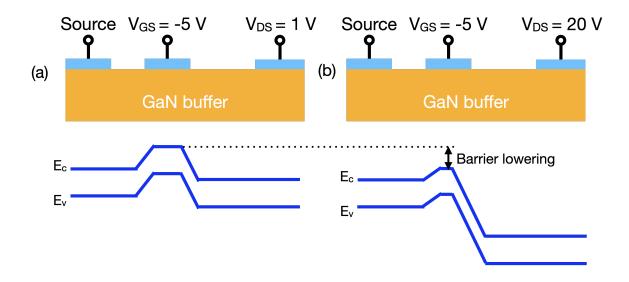

| 2.8  | Schematic of drain-induced barrier lowering mechanism in a GaN device.                   | 17 |

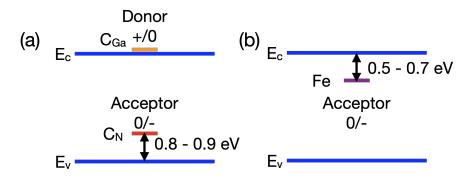

| 2.9  | Trap energy levels in GaN HEMTs with carbon and iron.                                    | 18 |

| 2.10 | Schematic of Transport mechanisms (Fowler-Nordheim tunnelling and Poole–Frenkel          |    |

|      | emission)                                                                                | 19 |

| 2.11 | Schematic of electroluminescence generation within the band structure.                   | 20 |

| 2.12 | Schematic of impact ionization process.                                                  | 21 |

| 2.13 | Schematic of punch through current during OFF-state in GaN HEMTs.                        | 22 |

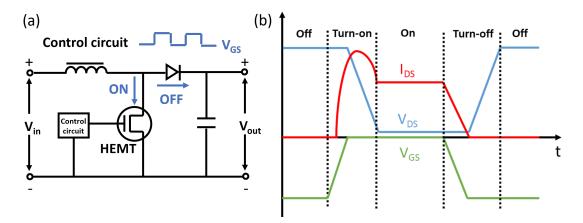

| 2.14 | Schematic of a DC-DC boost power converter circuit and the IV waveform                   | 23 |

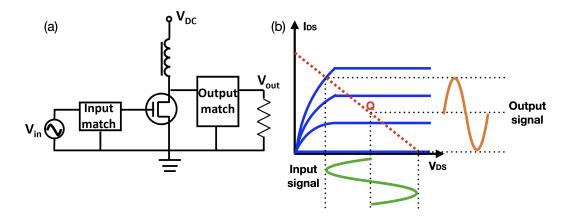

| 2.15 | Schematic of a RF power amplifier circuit with input and output signal waveforms         | 24 |

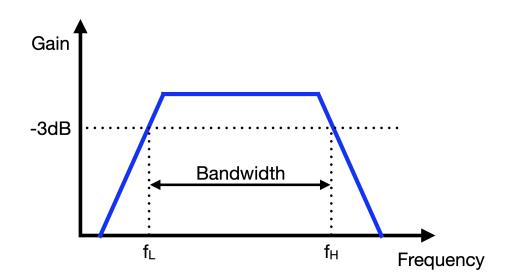

| 2.16 | Schematic of the frequency response of a filter.                                         | 24 |

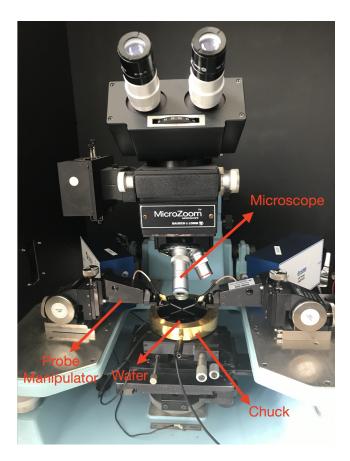

| 3.1  | Probe station with a wafer laid on the chuck and connected to the external circuit       |    |

|      | through the probe manipulators.                                                          | 28 |

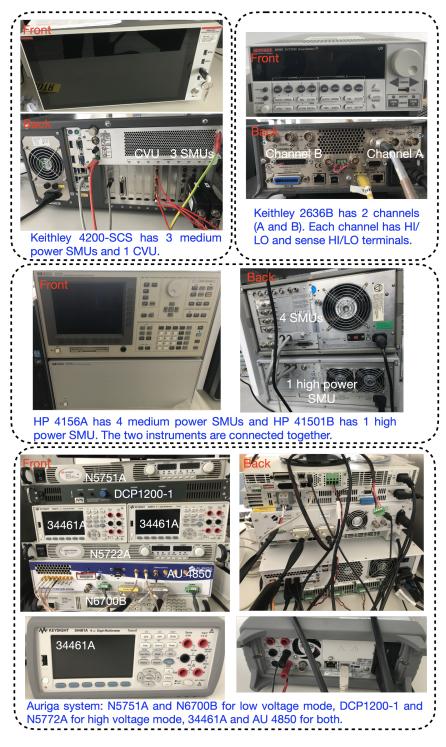

| 3.2  | Characterization instruments in the laboratory used for the measurements in this         |    |

|      | thesis.                                                                                  | 29 |

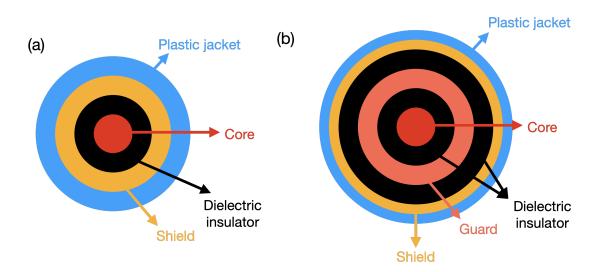

| 3.3  | Cross-section of a coaxial cable and a triaxial cable                                    | 30 |

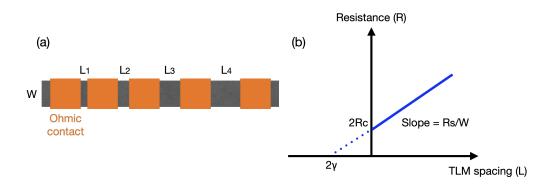

| 3.4  | Top view of the TLM structure and the fitted line for extracting resistance. $\ldots$ .  | 31 |

| 3.5  | Cross-section of the gate leakage structure and the buffer leakage structure. $\ldots$ . | 32 |

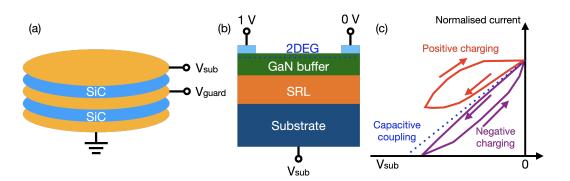

| 3.6  | Illustration of back bias measurement technique.                                         | 33 |

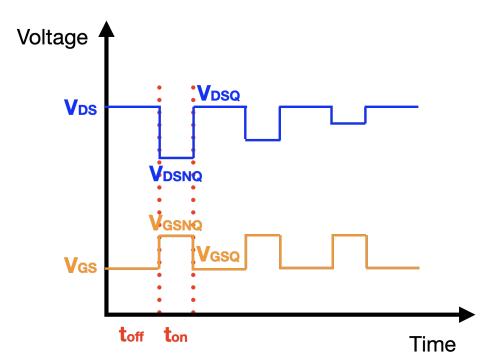

| 3.7  | Illustration of pulse IV measurement technique                                           | 34 |

FIGURE

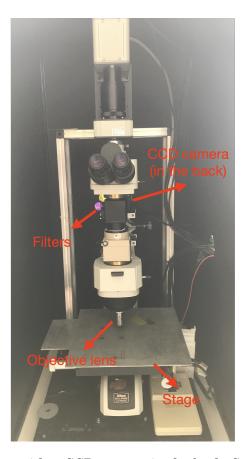

| 3.8  | Schematic of EL set up with a CCD camera in the back.                                                     | 35 |

|------|-----------------------------------------------------------------------------------------------------------|----|

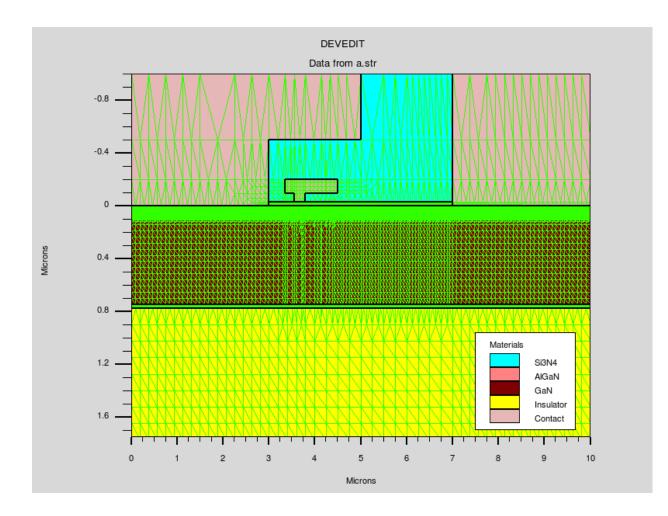

| 3.9  | A gerneral GaN HEMT cross-section built in DevEdit showing the materials of each                          |    |

|      | layers and the mesh.                                                                                      | 37 |

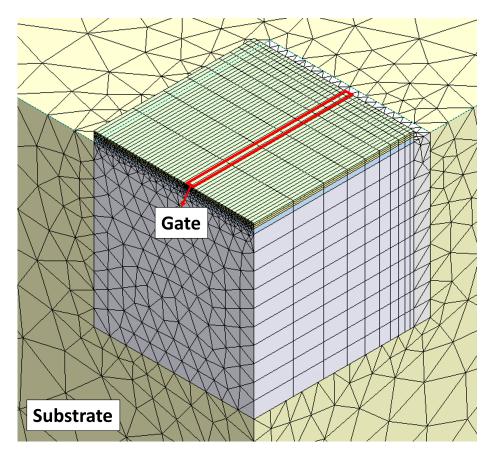

| 3.10 | A general 3D GaN HEMT structure built in DesignModeler showing the mesh in each                           |    |

|      | layer                                                                                                     | 38 |

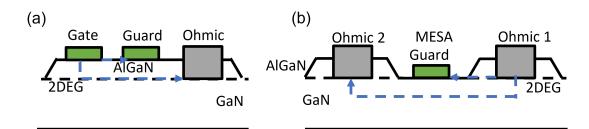

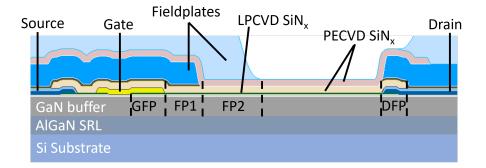

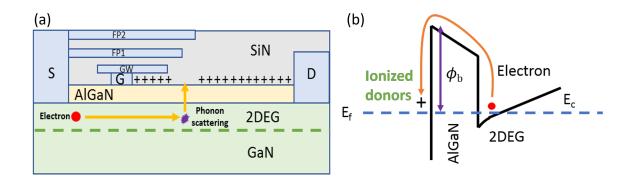

| 4.1  | Schematic of GaN HEMTs used in Chapter 4 and 5 (not to scale).                                            | 43 |

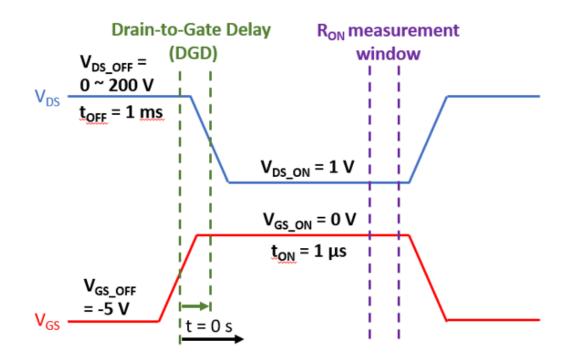

| 4.2  | Drain and Gate voltages waveforms with hard-switching.                                                    | 44 |

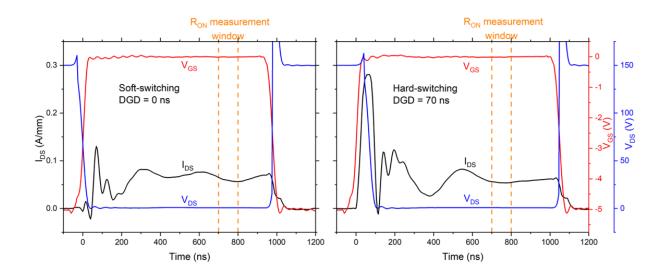

| 4.3  | Measured current and voltage waveforms with soft-switching and hard-switching                             | 45 |

| 4.4  | Static I-V curves for $V_{GS}$ ranging from -2 to 0 V in the DC measurements and the                      |    |

|      | loadlines during switchings.                                                                              | 46 |

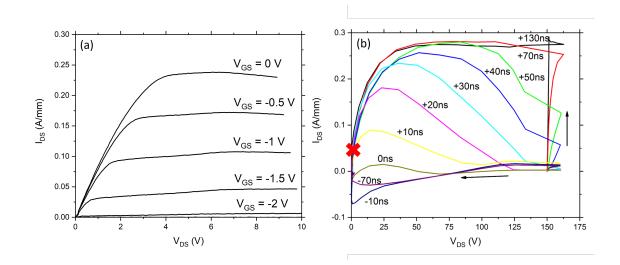

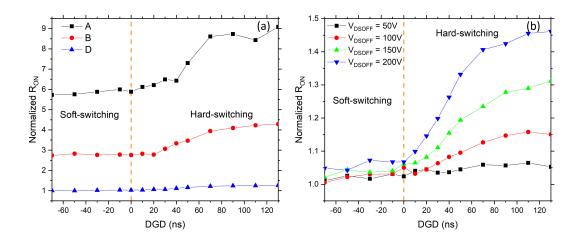

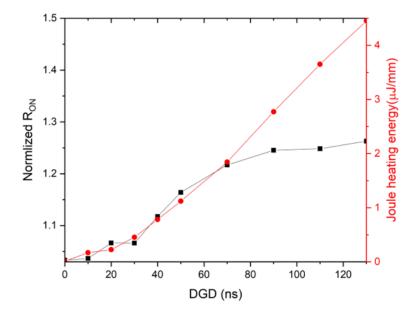

| 4.5  | Dependence of normalized $R_{ON}$ on DGD in wafer A, B and D ( $V_{DSOFF}$ = 150 V)                       | 46 |

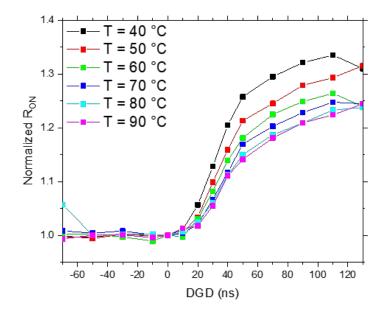

| 4.6  | Dependence of normalized $R_{ON}$ on DGD for temperature varying from 40 °C to 90 °C                      |    |

|      | $(V_{VDSOFF} = 150 \text{ V})$                                                                            | 47 |

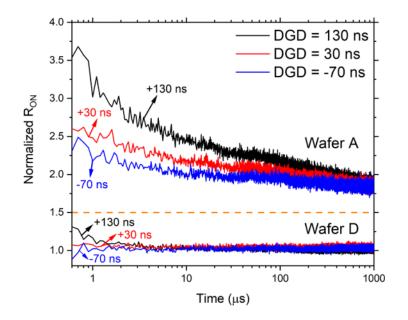

| 4.7  | The transient normalized $R_{ON}$ for different DGDs in wafer A and D ( $t_{ON}/t_{OFF} = 1$              |    |

|      |                                                                                                           | 48 |

| 4.8  |                                                                                                           | 48 |

| 4.9  |                                                                                                           | 49 |

| 4.10 |                                                                                                           | 50 |

| 4.11 | Normalized R <sub>ON</sub> and total Joule heating energy dissipated during hard-switching                |    |

|      |                                                                                                           | 51 |

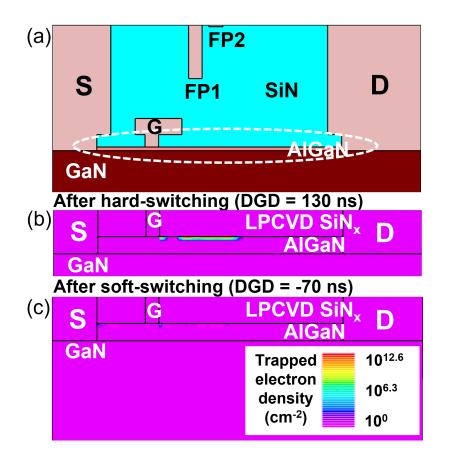

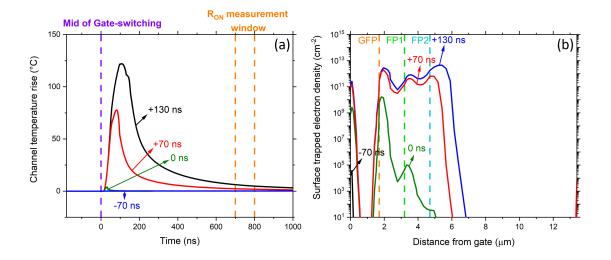

| 4.12 |                                                                                                           | 53 |

|      | Simulated lateral electric field within 2DEG and surface trapped electron density                         |    |

|      |                                                                                                           | 54 |

|      |                                                                                                           |    |

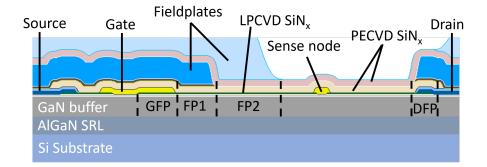

| 5.1  | Schematic of GaN HEMTs with Schottky sense node structures (not to scale) used in                         |    |

|      | Chapter 5                                                                                                 | 59 |

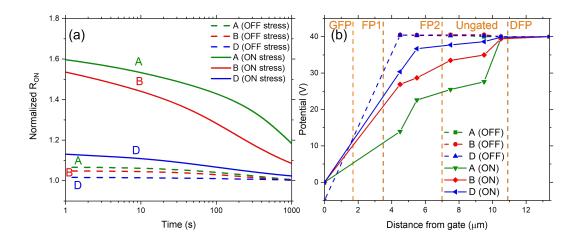

| 5.2  | Measured Dynamic $R_{\rm ON}$ and potential distribution for OFF-state and ON-state condi-                |    |

|      | tions                                                                                                     | 60 |

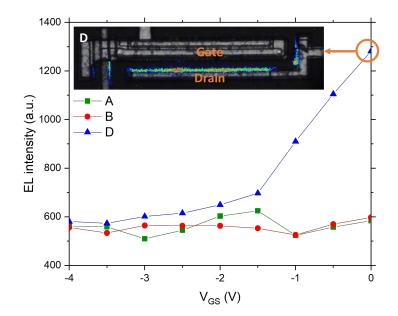

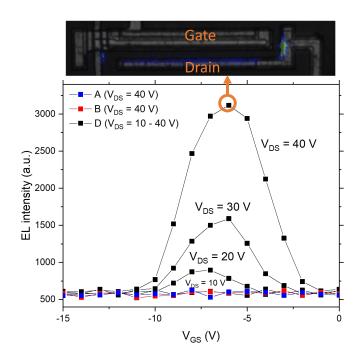

| 5.3  | Measured electroluminescence intensity against $V_{GS}$ in wafer A, B and D. $\ldots \ldots \ldots$       | 61 |

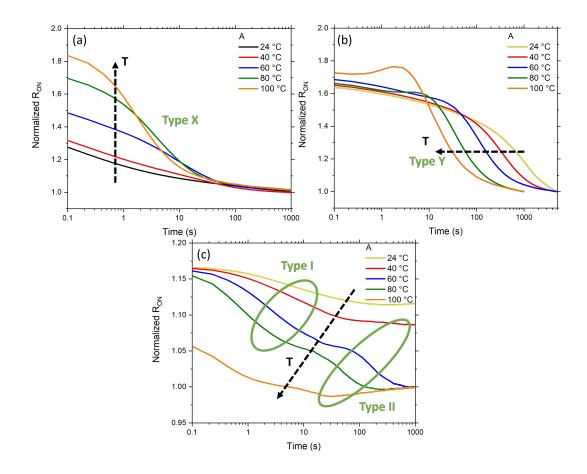

| 5.4  | $Comparison \ of \ temperature-dependent \ dynamic \ R_{ON} \ measured \ after \ different \ conditions.$ | 62 |

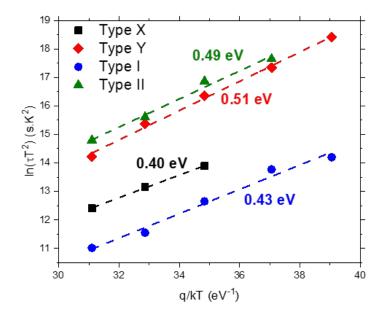

| 5.5  | Arrhenius plot of the acceptor-like trap responses (Type X, Y, I and II)                                  | 63 |

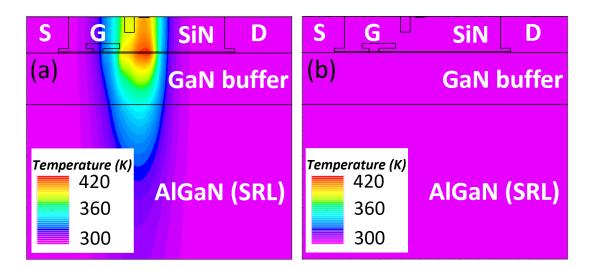

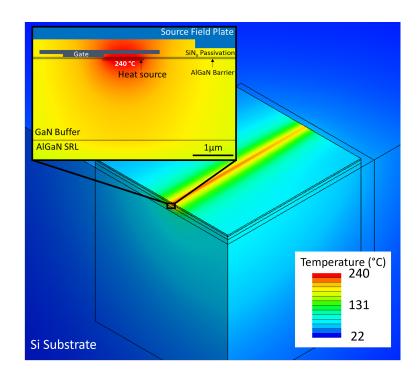

| 5.6  | The 3D finite element model shows the simulated temperature distribution during                           |    |

|      | the ON-state.                                                                                             | 64 |

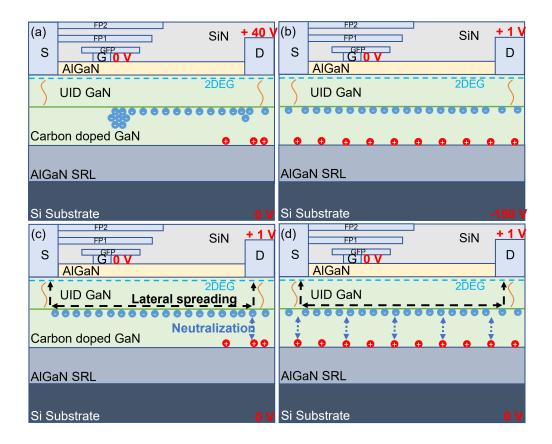

| 5.7  | Schematic of the charge distribution within the GaN buffer layer in wafer A. $\ldots$ .                   | 67 |

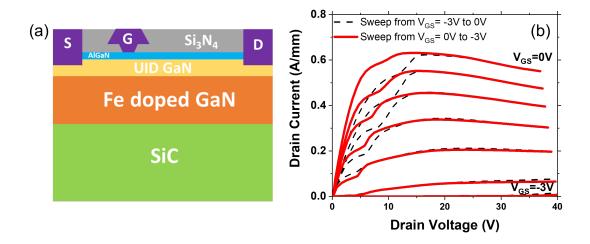

| 6.1  | Schematic of the device used in Chapter 6 and DC measurement results                                      | 73 |

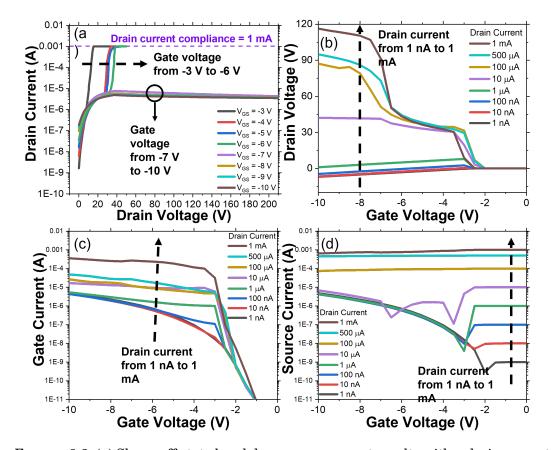

| 6.2  | Off-state breakdown measurement results with drain injected technique.                                    | 74 |

| 6.3  | Characterized EL intensity for range of $V_{\rm GS}$ bias between 0 V and -10 V (I_D = 1 mA)              |    |

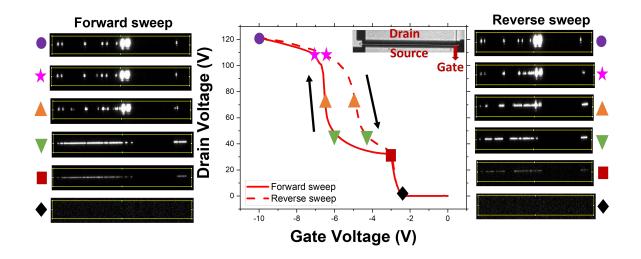

|      | with forward and reverse sweeps.                                                                          | 75 |

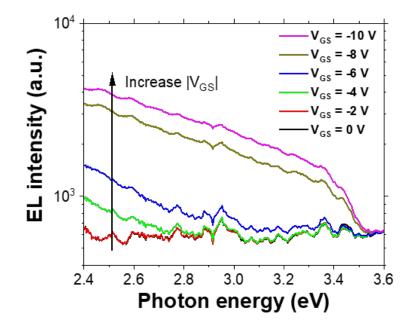

| 6.4 | EL spectra measured from the backside of the device at different gate bias (I_D = 500 $\mu A$ ).       | 76 |

|-----|--------------------------------------------------------------------------------------------------------|----|

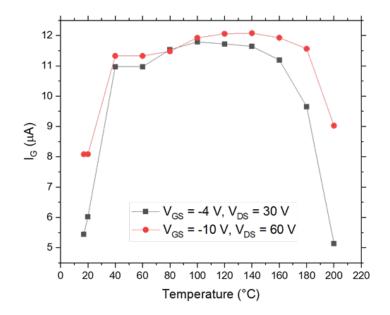

| 6.5 | Temperature-dependent gate leakage current (17 – 200 °C) under Stage 1 and Stage 2.                    | 77 |

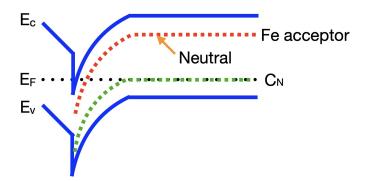

| 6.6 | Band diagram of the simulated GaN epi-layers showing the location of Fe acceptors                      |    |

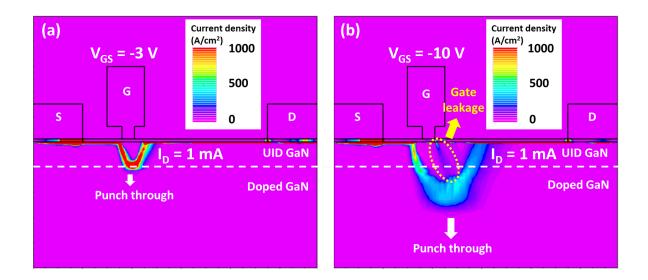

|     | and C deep acceptors (C_N)                                                                             | 77 |

| 6.7 | Simulated current density distribution during breakdown.                                               | 78 |

| 6.8 | Equivalent circuit under the gate.                                                                     | 79 |

| 7.1 | Schematic of MIS-GaN HEMTs used in Chapter 7.                                                          | 84 |

| 7.2 | Measured drain current (I_DS) against gate voltage (V_GS) in MIS-HEMTs. $\ \ldots \ \ldots$ .          | 85 |

| 7.3 | Measured gate leakage current (I_G) against gate voltage (V_GS) in MIS-HEMTs                           | 86 |

| 7.4 | Measured EL intensity against the $V_{\rm GS}$ in MIS-HEMTs of wafer A, B and D for drain              |    |

|     | voltage up to 40 V                                                                                     | 87 |

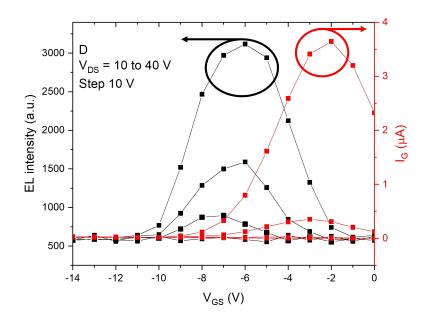

| 7.5 | Simultaneous measurements of EL and gate leakage current (I_G) in MIS-HEMT of                          |    |

|     | wafer D                                                                                                | 88 |

| 7.6 | Schematic of MIS-HEMT of wafer D and the 2DEG density profile when $V_{\rm DS}$ = 40 V                 |    |

|     | and $V_{GS}$ = -4 V                                                                                    | 89 |

| 7.7 | Band diagram under the MIS-gate with the electron and hole leakage current under                       |    |

|     | the semi-ON condition                                                                                  | 90 |

| 7.8 | Measured EL, gate leakage current (I $_{ m G}$ ), drain current (I $_{ m DS}$ ) and the potential drop |    |

|     | between gate and drain in MIS-HEMT of wafer D.                                                         | 90 |

#### INTRODUCTION

If has been dramatically changed since the information revolution as more than 7 billion people around the world are connected together through the internet. Nowadays, not only the human beings, but also machines, buildings, even animals and most of physical objects on the earth can be interacted through built-in sensors or chips theoretically, which is known as internet of things (IoT) [1]. This branch of fast growing technology gives more and more convenience for human's daily life since 21<sup>st</sup> century. How could it possibly happen? A big thanks goes to the invention of semiconductor devices.

The first semiconductor transistor, a bipolar point-contact transistor, was developed by John Bardeen, Walter Hauser Brattain and William Shockley at Bell Labs in 1947 [2, 3]. A transistor can either act as a switch or an amplifier and therefore, it helps to builds more complex circuits for more advanced applications. In the modern society, the big family of transistor has been classified into several categories according to the specific demands. Some of the transistors are fabricated into nano-range (gate pitch) to increase the density of integrated circuit (IC); Some of the transistors are made to be suitable for high frequency operation for 5G applications; Some of the transistors are designed to tolerate the high power environment for device charging. Sometimes different demands are mixed in some situations and the traditional silicon device faces strong challenges. Therefore, a lot of semiconductor materials (i.e. GaAs, SiC, GaN, Ga<sub>2</sub>O<sub>3</sub>...) have attracted the research community for investigation in order to meet the criteria of these complicated situations. In particular, AlGaN/GaN high electron mobility transistors (HEMTs) have exhibited both a high electron mobility (up to 2000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> [4]) due to the 2 dimensional electron gas (2DEG), and a high breakdown voltage (3 MV/cm [5]) due to the wide bandgap. All these features are making the GaN HEMT a promising candidate for high power and radio frequency (RF) applications.

### 1.1 Developments and Challenges for AlGaN/GaN HEMT

The development of AlGaN/GaN HEMTs has started since 1990s and many researchers have contributed their knowledge to it. In early 1990s, the study about how to grow the GaN thin film by molecular-beam epitaxy (MBE) and chemical vapor deposition (CVD) techniques was carried out [6], and it enabled the technologies about the growth of bulk GaN and the AlGaN/GaN heterojunction. Khan et al. [7] reported the first HEMT with AlGaN/GaN heterojunction in 1993 and it was grown on the sapphire. At that time, with a large dislocation density in the GaN epitaxy and a poor substrate thermal conductivity, making it unsuitable for real applications. Soon in 1997, the first GaN-on-SiC HEMT is developed by Binari et al. [8] in order to improve the device performance. The AlN nucleation layer was deposited above the SiC, which reduces the lattice mismatch between the substrate and the GaN layer, therefore, it successfully mitigates the dislocation density in GaN. On the mean time, the SiC substrate with a high thermal conductivity helps to improve the thermal dissipation rate. However, with a relatively high cost for the SiC substrate, the development of GaN HEMTs is mainly pushed by the defense industry. In 2001, Chumbes et al. [9] developed the first GaN-on-Si HEMT and a thin GaN layer was adopted to prevent the substrate cracking caused by the different thermal coefficients and the lattice mismatch. The AlN nucleation layer and the AlGaN strain relief layer are together to make the GaN layer strain-free in nowadays [10]. The major advantage of use the Si substrate is its low cost compared to SiC.

Despite the development in device fabrication of, there are other studies related to the device application and reliability. Khan et al. [11] developed the enhanced-mode (E-mode) GaN HEMTs, also known as the normally-off GaN HEMTs, with a thin AlGaN barrier (10 nm) in 1995. The major advantage of the E-mode device over the depletion-mode (D-mode) device is that it allows the amplifier circuit with single-polarity voltage supply [12]. The E-mode GaN HEMTs can also be achieved by the recessed gate[13], the Fluorine implantation [14] and the p-gate [15]. Carbon is doped to the GaN buffer layer to reduce the vertical leakage in power GaN devices [16, 17], as carbon acceptors in GaN pinned the Fermi level in the mid gap, and therefore increase the GaN buffer resistivity. However, carbon in the GaN buffer layer also induces the buffer charge trapping [18], which leads to the dynamic  $R_{ON}$  ( $R_{ON}$ ) increase, so it is a trade-off for the vertical leakage and the dynamic RON with a C-doped GaN buffer layer. Fe is also a common type of dopant to make the GaN buffer semi-insulating [19]. For the some RF GaN HEMTs, ensuring the linearity of waveform is more important than controlling the leakage, therefore, Fe is a better choice than C, as Fe will not lead to the significant dynamic R<sub>ON</sub> increase as C. GaN HEMTs used to suffer from the surface charge trapping as it acts as a virtual gate to deplete the 2DEG after stress. In 2001, Vetury et al. [20] found that by using the sillicon nitride passivation layer above the AlGaN barrier, the surface states in GaN HEMTs can be suppressed. To increase the breakdown voltage of the GaN HEMTs, Karmalkar et al. [21] used the field plate to smooth the electric field, avoiding the a field peak in vicinity of the gate edge in 2001.

In 2014, GaN material becomes a famous semiconductor since the invention of the blue LED by Akasaki, Amano and Nakamura, and a Nobel Price in Physics was awarded as it enables white light generation with a high efficiency [22]. This exciting news also attracted more researches on the GaN/HEMT technology in the following years. Recently, after nearly 30 years development of the AlGaN/GaN HEMTs technology, its commercialization path is mature and people all around the world have already benefited from it. According to the Yole Développement market report 2021 [23], the power GaN market has achieved around \$46 million in 2020 and will surpass \$1.1 billion in 2026, with a fast growing market in GaN-based chargers for consumers as well as for the telecom and automotive applications.

Several semiconductors have been considered for the power application, such as the power converter which modulate the voltage or power, a good transistor should have a low ON-resistance and a high breakdown voltage [24]. The device with a low ON-resistance will dissipate less heating energy during the ON-state and therefore increase the energy efficiency. The breakdown field of a semiconductor is associated with the band gap as it determines the energy required for triggering an electron from the valence band to the conduction band whereas the ON-resistance mainly depends on the carrier mobility and carrier density.  $\beta$  - Ga<sub>2</sub>0<sub>3</sub> is a potential semiconductor for the high power application which has a breakdown field around 8 MV/cm while the disadvantages of  $\beta$  - Ga<sub>2</sub>0<sub>3</sub> are the low electron mobility (300 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>) and low thermal conductivity (10 - 30  $W/(m \cdot k)$  [25, 26]. Therefore, it is only suitable for some specific applications and it is at the early stage of researching. Diamond shows both the high breakdown field (10 MV/cm) and the high electron mobility (4500 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>) simultaneously [27], making it the best material for the power application theoretically, but since it lacks of n-type dopants and has a relatively high resistance, it is unsuitable for making good power devices currently. For the RF application, such as the wireless networks, the ideal semiconductor should have a high carrier mobility to enable the fast switching with a low ON-resistance. GaAs and InP show electron mobilites of 8500 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> and 5400 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> respectively, making than suitable for working with a frequency range of GHz. However, they have much narrow bandgaps compared to GaN ( $E_{g, GaAs}$  = 1.42 eV,  $E_{g, InP}$  = 1.34 eV), which makes them more vulnerable for under the high voltage. Hence, GaN HEMTs are more suitable for the high power RF application (i.e. 5G base station).

Apart from the recent developments of the AlGaN/GaN HEMT technology, there is still some space for pushing the device performance to the limit of the GaN material. There are many challenges regarding the device reliability that wait to be solved, such as the dynamic  $R_{ON}$  increase (also known as the current collapse) after device stress [28], the instability of threshold voltage [29], the high channel temperature during the high power application [30].

## 1.2 Thesis Structure

This thesis mainly focuses on the the electric reliability issues of GaN HEMTs, such as hardswitching, buffer charge trapping and breakdown and also the physical mechanisms behind the gate leakage and electroluminescence (EL). Possible solutions on improve device performance have been outlined based on the analysis in the study. Both of power and RF devices are chosen for investigation.

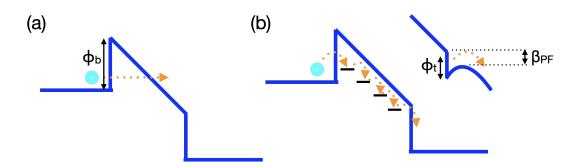

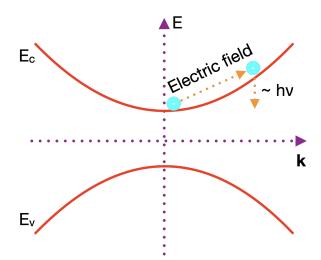

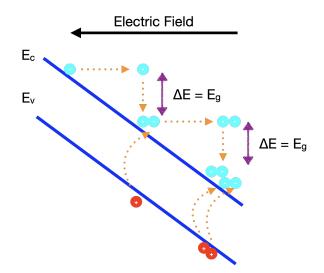

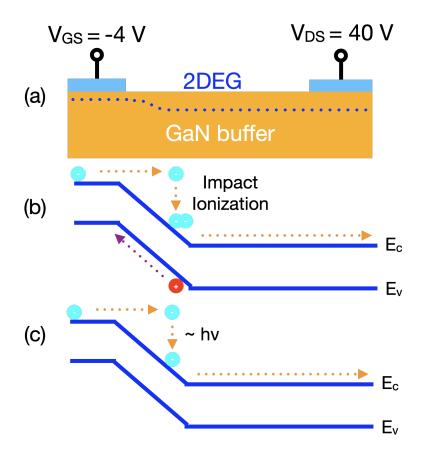

Chapter 2 introduces the theoretical background of AlGaN/GaN HEMTs and their applications. Chapter 3 covers the characterization techniques used in this thesis. In Chapter 4, a set of power AlGaN/GaN-on-Si HEMTs with different  $SiN_x$  stoichiometry for passivation layers are used for investigating the reliability issues for hard- and soft-switching conditions. The switching time in pulsed IV measurement has been controlled precisely to show how the dynamic RON is affected by the switching type. With the aid of simulation tools, the possible mechanism of self-heating effect is ruled out as it the temperature cools down very fast after hard-switching but the surface charge trapping is more likely to be present as it shows a small recovery time. The discussion of how to improve the device performance under hard-switching with a Si-rich passivation layer is presented in this study. In Chapter 5, the same set of devices from Chapter 4 are used to investigate the buffer charge trapping under different stress conditions. Three stress conditions are discussed in this chapter, including the OFF-state stress, ON-state stress and the back bias stress, and they show different types of R<sub>ON</sub> recovery curves. Based on the experimental results, analysis of the reason behind the possible trapping mechanisms is illustrated and it helps to show how to mitigate the dynamic R<sub>ON</sub> under stress conditions. Chapter 6 reports the breakdown mechanism in RF AlGaN/GaN-on-SiC HEMTs by adopting the drain injected technique, which helps to prevent a permanent device failure while observing how the drain breakdown voltage evolves with the gate voltages. The breakdown measurements show apparent two-stage breakdown behaviour and the electroluminescence measurements show aligned results. Throughout the analysis of measurements and simulation, a complete picture of two-stage breakdown mechanism is formed. The difference of carbon doping density is the primary reason while the localized leakage current path triggered under high voltages is the the side effect shown in the electroluminescence measurements. Breakdown is a crucial regime for transistor reliability and this study gives a hint of RF GaN HEMTs optimization. Chapter 7 discusses the origin of the gate leakage current in metal-insulator-semiconductor (MIS) GaN HEMTs, and its relationship with the electroluminescence. An additional  $SiN_x$  passivation layer is under the gate metal to suppress the gate leakage [31], thus leads to a big reduction in electron current through the gate but the hole current remains. The electrons pass the  $SiN_x$  through the Poole-Frenkel emission whereas the holes can pass freely into the gate with almost no barrier under the negative gate voltage. Therefore, the hole current reflects the impact ionization rate within the device. The electroluminescence has been proven to be a consequence of the Bremsstrahlung effect in GaN HEMTs [32]. The obvious mismatch of the bell shape curves between the electroluminescence

and gate leakage current against the gate voltages hint a physical mechanism behind the GaN HEMTs, that the Bremsstrahlung effect and the impact ionization effect occurs in different domains. The Bremsstrahlung effect is more likely to take effect when carrier density is low while the impact ionization effect becomes dominant when the carrier density is higher. This study improves the physical understanding of the electroluminescence and gate leakage in GaN HEMTs and gives a suggestions for controlling the gate leakage through MIS structures. Conclusions of this thesis and future outlook of research on GaN HEMTs are summarized in Chapter 8.

# **THEORETICAL BACKGROUND**

In this chapter, the physical background of gallium nitride properties and the structure of AlGaN/GaN HEMTs and device fabrication methodologies are presented. In order to explain the study on AlGaN/GaN HEMTs in later chapter, the device physics such as the electroluminescence, the trapping effect, the self-heating effect, the transport mechanism and impact ionization are included. Some relevant reliability issues and the industrial applications are also illustrated for understanding the major challenges in AlGaN/GaN HEMTs.

## 2.1 Gallium Nitride

#### 2.1.1 GaN Properties

Gallium nitride is a wide bandgap III-V semiconductor that has a crystal structure of zinc blende or wurtzite. In the zinc blende structure, the Ga atoms form a fcc lattice whereas the wurtzite structure shows a hcp lattice of Ga atoms. In both crystal structures, the N atoms occupy the tetrahedral vacancies as each N atoms have 4 nearest Ga neighbors in connection. The symmetry groups of zinc blende and wurtzite are  $F\bar{4}3m$  and  $P6_3mc$  respectively.

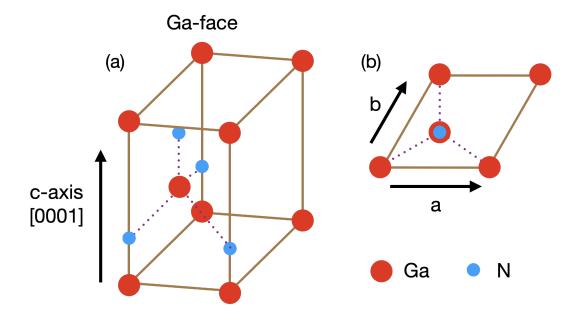

For GaN devices, the wurtzite structure is widely used as it is thermodynamically more stable than zinc blende, which is determined by the first-principles calculation [34]. The primitive cell of the wurtzite GaN crystal is depicted in Figure 2.1 and the structure has a six fold screw symmetry, a mirror plane and a glide plane. However, in wurtzite GaN structure, the crystal has no central symmetry which means that the crystal structure can not be recovered by exchanging the positions of atoms through a central inversion in a primitive cell. Considering that the electronegativity of Ga and N elements are different, the wurtzite GaN has an intrinsic polarization and is piezoelectric [35]. It also causes the differences of GaN growth on the (0001) and (000 $\overline{1}$ )

FIGURE 2.1. (a) Primitive cell of the hexagonal wurtzite GaN structure along the c-axis direction, showing the positions of Ga and N atoms. The Ga-face is on the top. (b) A top view of the primitive cell from the Ga-face.

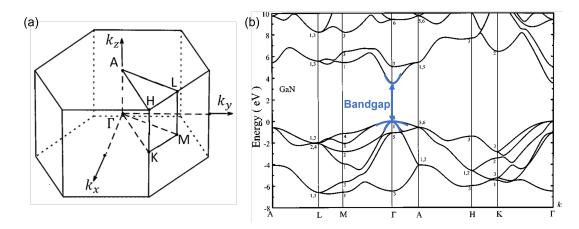

FIGURE 2.2. (a) First Brillouin zone of the wurtzite GaN structure with high symmetry points in reciprocal space. (b) Band structure of wurtzite GaN structure along high symmetry points. These two figures are adapted from [33].

plane. The [0001] direction and (0001) plane are referred as Ga-polar and Ga-face, whereas the  $[000\overline{1}]$  direction and  $(000\overline{1})$  plane correspond to N-polar and N-face respectively. GaN can be either grown on the Ga-face or the N-face as they show different surface chemical properties and adatom mobilities [36]. Most of GaN HEMTs are fabricated on the Ga-face with a few reports about N-face devices [37]. Throughout this thesis, the Ga-face HEMTs are used for study.

Many useful electronic properties of GaN can be obtained from the energy band structure.

In Figure 2.2 (a), the first Brillouin zone in reciprocal space (also known as **k** space) of GaN is illustrated. **k** is the wave vector of the electron wave in the periodical crystal structure. The  $\Gamma$  point has zero momentum. The band structure can be derived by solving the Schrödinger equation with the electron wave function and the periodical crystal potential field. The energy band structure of GaN along **k** with the high symmetry points highlighted is shown in 2.2 (b). The bandgap sits between the top of the valence band and the bottom of the conduction band. The wurtzite GaN has a direct bandgap just at the  $\Gamma$  point and the bandgap is 3.44 eV [38].

The carrier mobility  $\mu$  is an important parameter for semiconductor materials and it is determined by the equation below

$$\mu = \frac{e\tau_c}{m^*} \tag{2.1}$$

where e is the electron charge,  $\tau_c$  is the mean free time for the carrier,  $m^*$  is the effective mass. Therefore, the carrier mobility is inversely proportional to the effective carrier mass and the carrier mass is inversely proportional to the band curvature. For intrinsic bulk GaN, the effective electron masses differs along the  $\Gamma$ -M and  $\Gamma$ -A directions due to the different curvatures of the conduction band in Figure 2.2 (b). First-principles calculation shows that  $m_{e\perp}^* = 0.18 m_0$ ,  $m_{e\parallel}^* = 0.2 m_0$ , where  $m_{e\perp}^*$  is the electron mass along the  $\Gamma$ -M direction,  $m_{e\perp}^*$  is the electron mass along the  $\Gamma$ -A direction and  $m_0$  is the free electron mass [39]. The hole effective masses at the  $\Gamma$  point splits with the valence bands, and the holes are usually heavier than the electrons so they are not the minority carriers in GaN devices as they show relatively small mobilites.

Semiconductor materials also suffer from breakdown under a high electric field due to impact ionization. According to [40], the critical electric field of a direct bandgap semiconductor has been derived as a function of bandgap

$$E_c(V/cm) = 1.73 \times 10^5 E_{g}(eV)^{2.5}$$

(2.2)

where  $E_c$  is the value of critical electric field and  $E_g$  is the value of bandgap. GaN has a bandgap of 3.44 eV [38], and a critical electric field of 3 MV/cm [5]. It makes GaN suitable for high power applications.

#### 2.1.2 GaN and Other Semiconductors

Each semiconductor material has its own unique feature and can fit for different applications. For the power application, the transistor should have a high breakdown voltage and a low ONresistance, which demands the semiconductor to have a high critical field and a high carrier mobility. Many wide bandgap semiconductors have been investigated for power applications. The properties of major wide bandgap semiconductor materials are shown in Table 2.1. The semiconductors are usually described with the Baliga's figure of merit (BFOM) [41] as follows,

$$BFOM = \epsilon \mu E_c^{3} \tag{2.3}$$

|                                                                         | Si   | GaAs | 4H-SiC | GaN | $\beta$ - Ga $_20_3$ | Diamond |

|-------------------------------------------------------------------------|------|------|--------|-----|----------------------|---------|

| Bandgap (eV)                                                            | 1.1  | 1.4  | 3.3    | 3.4 | 4.9                  | 5.5     |

| Dielectric Con-<br>stant                                                | 11.8 | 12.1 | 10     | 9.5 | 10                   | 5.3     |

| Electron Mobility<br>(cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | 1350 | 8500 | 720    | 900 | 300                  | 4500    |

| Breakdown Field<br>(MV/cm)                                              | 0.3  | 0.4  | 2      | 3   | 8                    | 10      |

| Baliga figure of<br>merit (BFOM)                                        | 1    | 17   | 134    | 537 | 3444                 | 51627   |

Table 2.1: Comparison of bulk semiconductor material properties [5, 25, 27].

where c is the dielectric constant. In Table 2.1, BFOM is normalized to that of Si.

Si is the most common and widely used semiconductor, however, it is not good for high power application due to its relatively low breakdown field. GaAs has a higher electron mobility than other material with a low breakdown field, making it a suitable for the RF application. SiC has determined its advantages not only due to its cheap fabrication price, but also the high thermal conductivity. In some power switching circuits, the devices will generate a large amount of joule heating energy during the switching, thus they require a high thermal dissipation rate to stabilize the temperature. GaN is a more promising wide bandgap semiconductor than SiC in many circumstances. Although its bulk electron mobility is only around 900 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, the polarization nature of GaN crystal leads to the formation of 2DEG which has a electron mobility up to 2000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> at room temperature [4] and a high electron density. However, the GaN fabrication is expensive than the previous semiconductors, and it usually consists of a large dislocation density, making it hard for commercialization.  $\beta$  - Ga<sub>2</sub>0<sub>3</sub> is a potential semiconductor for future high power application which has a breakdown field around 8 MV/cm. The disadvantages of  $\beta$  - Ga<sub>2</sub>0<sub>3</sub> are the low electron mobility and low thermal conductivity. Therefore, it is only suitable for some specific applications and it is at the early stage of researching. Diamond materials have a high breakdown field and a high mobility simultaneously, making it the best material for the power application theoretically, but since it lacks of n-type dopants and shows a high resistance due to the 0.3 eV deep acceptor, it is hard to make good commercial devices yet.

For the RF application, the ideal semiconductor should have a high carrier mobility to enable the fast switching and low resistance. GaAs and InP (1.34 eV) have exhibited their advantages in the RF application due to their high electron mobility. However, with relatively low bandgaps, GaAs and InP (5400  $\text{cm}^2 \text{V}^{-1} \text{s}^{-1}$ ) are less appropriate for the high power RF application, such as the power amplifier used for 5G base station. Thanks to the wide bandgap of GaN and the high electron density within the 2DEG of AlGaN/GaN heterojunction, GaN becomes a promising candidate for the high power RF application. Micovic et al. have shown the GaN HEMTs with a cutoff frequency larger than 500 GHz and a similar RF gain with GaAs and InP in power

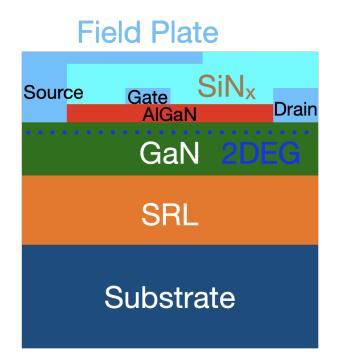

FIGURE 2.3. Schematic of a AlGaN/GaN HEMT structure.

amplifiers [42].

## 2.2 Structure of AlGaN/GaN HEMT

A typical AlGaN/GaN HEMT structure is shown in Figure 2.3. It consists of the substrate, the strain relief layer (SRL), the GaN epitaxy, the AlGaN/GaN heterojunction with 2DEG in between, the passivation layer (SiN<sub>x</sub>), contacts and field plates. There is also a thin GaN cap layer (1 - 2 nm) between the AlGaN barrier and the passivation layer, and a nucleation layer between the substrate and SRL (not shown in Figure 2.3).

#### 2.2.1 Substrate

There are multiple substrate choice for the GaN device epitaxy as shown in Table 2.2. The ideal substrate for GaN should have a high thermal conductivity, a small lattice mismatch with GaN, large wafer size availability and a low cost. Although the bulk GaN can be grown and fits with GaN epitaxy, it is hard to commercialize due to its high cost and small wafer size [44]. The Si wafer is a good substrate choice due to its mature fabrication process, the large wafer size and low cost. However, considering that GaN HEMTs are widely used for the power and RF applications and a high thermal conductivity of substrate is often required. Therefore, SiC becomes a better choice for GaN HEMTs not only due to its high thermal conductivity but also the small lattice mismatch with GaN. Meanwhile, the demand of a low substrate loss makes SiC better than Si

|                                     | GaN       | Si       | SiC  | Sapphire | Diamond           |

|-------------------------------------|-----------|----------|------|----------|-------------------|

| Bandgap (eV)                        | 3.4       | 1.1      | 3.3  | 9.9      | 5.5               |

| Thermal conduc-<br>tivity (W/(m·K)) | 2         | 1.5      | 4.9  | 0.35     | 180               |

| Lattice mismatch<br>with GaN (%)    | 0         | 17       | 3.5  | 14       | 89                |

| Size (mm)                           | 30        | 300      | 150  | 150      | 10                |

| Cost                                | Very high | Very low | High | Medium   | Extremely<br>high |

Table 2.2: Comparison of substrate material properties for the GaN device [43].

for RF operation [9]. Diamond benefits from its extremely high thermal conductivity and is a potential option for the next generation of GaN HEMTs [30].

#### 2.2.2 Nucleation and Strain Relief Layer

For GaN-on-Si devices, the lattice mismatch Si and GaN will results in a large dislocation density and even cracks on the wafer. AlN is a common choice for nucleation followed by the strain relief layer to mitigate the strain due to the lattice mismatch. The SRL can be either graded layer or superlattice. The Al concentration will be gradually decreased for the graded SRL during growth whereas in the superlattice structure, the AlGaN layers with high and low Al concentrations change periodically. A study showed that the superlattice SRL is capable of suppressing the dynamic  $R_{ON}$  increase compared to the step-graded SRL [45]. For GaN-on-SiC devices, AlGaN can be used as the nucleation layer with small lattice mismatch and then GaN can be grown on the AlGaN layer.

#### 2.2.3 GaN Epitaxy

The GaN epitaxy comprises of the doped GaN layer and the unintentionally doped (UID) layer. For power devices, the doped GaN layer is usually doped with carbon to reduce the vertical leakage down to the substrate, preventing the drain-source leakage through the vertical paths with the substrate. However, the deep acceptors in the GaN buffer due to carbon doping result in the dynamic  $R_{ON}$  increase. Therefore, it is a trade-off to control the dynamic  $R_{ON}$  with the vertical leakage by carbon doping. Fe doping is more common for RF devices, as the RF amplifier usually requires the device to have good linearity, which means there should be small RF-DC dispersion. Fe pins the Fermi level on the upper half of the forbidden band of GaN and does not lead to severe current collapse. Molecular beam epitaxy (MBE) and metal organic chemical vapour deposition (MOCVD) are two common types of growth techniques for semiconductor devices. Epitaxial process may induce impurities such as carbon and oxygen into GaN expitaxy even with an ultra high vacuum environment, results in the UID GaN layer.

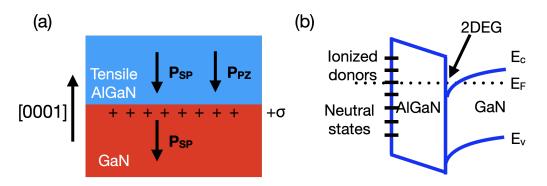

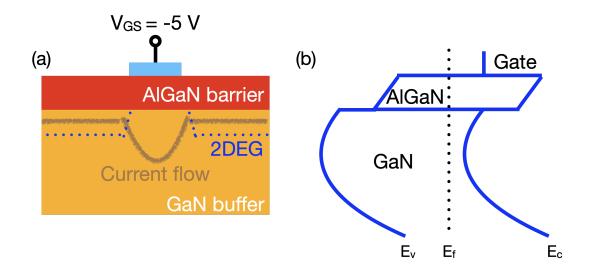

FIGURE 2.4. (a) AlGaN/GaN heterojunction with the spontaneous polarization ( $\mathbf{P_{SP}}$ ) and the piezoelectric polarization ( $\mathbf{P_{PZ}}$ ). The thin AlGaN layer is under the tensile stress and the bulk GaN is unstrained. (b) Band diagram of the AlGaN/GaN heterojunction with the formation of 2DEG. A part of donors on the AlGaN surface is ionized, proving the electron source for 2DEG.

#### 2.2.4 AlGaN/GaN Heterojunction and 2DEG

The AlGaN barrier is deposited above the GaN channel to form the AlGaN/GaN heterojunction in order to generate the 2DEG. For wurtzite GaN and AlN, there is spontaneous polarization ( $\mathbf{P_{SP}}$ ) along the [0001] direction, which is due to the non-centrosymmetric structure. The spontaneous polarization is AlGaN is between that of AlN and GaN [46]. If the AlGaN layer is grown on a bulk GaN, the lattice discontinuity will induce a tensile stress within the AlGaN layer, which is perpendicular to [0001] direction. The tensile stress results in the piezoelectric polarization ( $\mathbf{P_{PZ}}$ ) also along the [0001] direction. The schematic of polarization in AlGaN/GaN heterojunction is shown in Figure 2.4 (a). The net polarization charges on the AlGaN/GaN interface is described as

$$\sigma = P_{SP,AlGaN} + P_{PZ,AlGaN} - P_{SP,GaN} \tag{2.4}$$

where  $P_{SP,AlGaN}$  is the spontaneous polarization of AlGaN,  $P_{PZ,AlGaN}$  is the piezoelectric polarization of AlGaN and  $P_{SP,GaN}$  is the spontaneous polarization of GaN. Note that the spontaneous polarization of AlGaN is larger than that of GaN, so there will be net positive polarization charge on the AlGaN/GaN interface. The sign of the interface charge determines the band bending direction, as shown in Figure 2.4 (b). The conduction band of GaN near the interface is pushed down to the Fermi level due to the net positive polarization charge, which gives a rise to the 2DEG. However, due to the electron conservation, there should be an electron source providing the free electrons to 2DEG. According to [47], the surface donors of AlGaN take this role. The donors above the Fermi level become ionized and leave the positive charge on the AlGaN surface. It is the main reason for the formation of the 2DEG in the AlGaN/GaN heterojunction.

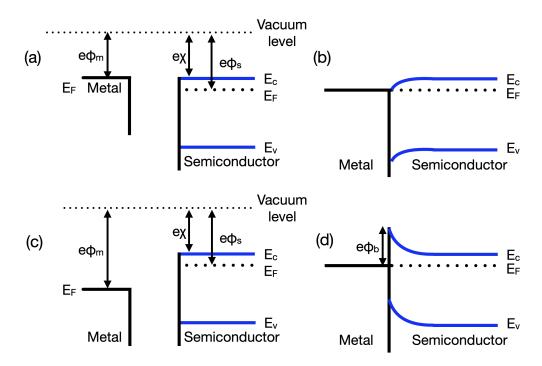

FIGURE 2.5. Ideal band diagrams of the Schottky contact and the Ohmic contact (n-type semiconductor). (a) Band diagram of a metal and semiconductor before contact ( $\phi_m < \phi_s$ ). (b) Band diagram of the Ohmic contact. (c) Band diagram of a metal and semiconductor before contact ( $\phi_m > \phi_s$ ). (d) Band diagram of the Schottky contact with a barrier ( $\phi_b$ ). These figures are adapted from [48].

#### 2.2.5 GaN Cap

A GaN cap layer with a thickness in a range 1 - 2 nm is usually grown on the AlGaN barrier to suppress the leakage current. Sheu et al. [49] discovered that the leakage current would be reduced by a factor of 3 - 4 in GaN Schottky barrier diode. The thickness of the GaN cap layer should be controlled as a too thick GaN layer will induce addition polarization charge which reduces the 2DEG density [50].

#### 2.2.6 Passivation

The passivation layer is deposited above the AlGaN barrier and the GaN cap to reduce the surface traps and the leakages. Without the passivation, charges will be stored on the AlGaN surface and act as a virtual gate to increase the channel resistance [51]. Arulkumaran et al. [52] compared different passivation options such as  $SiO_2$ ,  $Si_3N_4$  and SiON deposited by plasma enhanced chemical vapour deposition (PECVD) and it turned out that the  $Si_3N_4$  would suppress the surface traps most but also lead to a low breakdown voltage. Wang et al. [53] showed a robust  $SiN_x/AlGaN$  interface by depositing  $SiN_x$  with low pressure chemical vapour deposition (LPCVD) technique.

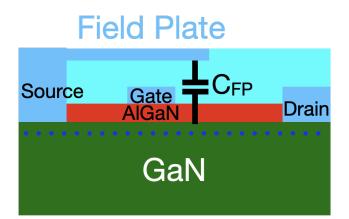

FIGURE 2.6. Schematic of the source field plate where the capacitance between the field plate and 2DEG is denoted as  $C_{FP}$ .

#### 2.2.7 Contacts

The metal-semiconductor junctions have two basic types, the Schottky contact and the Ohmic contact. The band diagrams of the Ohmic contact with a n-type semiconductor are depicted in Figure 2.5 (a) and (b).  $\phi_m$  is the metal work function,  $\phi_s$  is the semiconductor work function and  $\chi$  is the semiconductor electron affinity. After contact, the Ohmic contact will form if  $\phi_m < \phi_s$ , and it has a linear IV characteristics allowing the current flow in both direction. In GaN HEMTs, the source and drain are made with Ohmic contacts. The metal stack Ti/Al/Ni/Au is used for fabrication the Ohmic contact with GaN [54].

The band diagrams of the Schottky contact with a n-type semiconductor are depicted in Figure 2.5 (c) and (d). After contact, the Ohmic contact will form if  $\phi_m > \phi_s$ , it only allows single polar current direction from the metal to the semiconductor if the applied voltage is larger than  $\phi_b$ .  $\phi_b$  is calculated by

$$\phi_b = \phi_m - \chi \tag{2.5}$$

In GaN HEMTs, Ni/Au alloy is used to choose for the Schottky gate with a barrier height around 0.5 eV [55].

#### 2.2.8 Field Plate

The field plate is incorporated in order to reduce the field peak near the gate edge [56]. The field plate, the passivation layer, the AlGaN barrier and 2DEG together act as a capacitor ( $C_{FP}$ ). When a high drain bias ( $V_D$ ) is applied and the source is grounded, the potential drop across  $C_{FP}$  equals to 2DEG potential below the field plate  $V_{2DEG}$ . The maximum 2DEG potential below the field plate ( $V_{2DEG,max}$ ) is calculated by

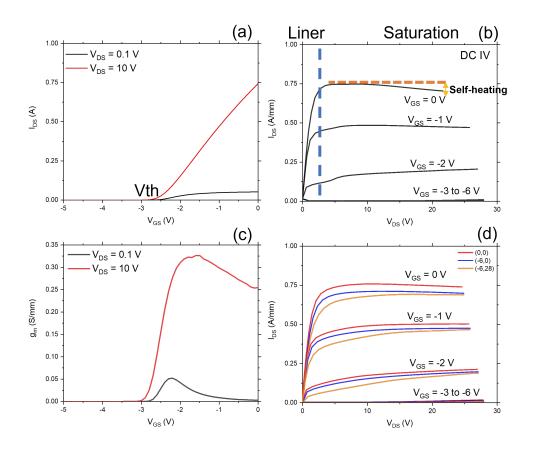

FIGURE 2.7. IV characteristics on a GaN-on-diamond HEMT. (a) Transfer characteristics. (b) DC IV output characteristics. (c) Transconductance characteristics. (d) Pulsed IV output characteristics ( $t_{ON}/t_{OFF} = 1 \ \mu s/1 \ ms$ ).

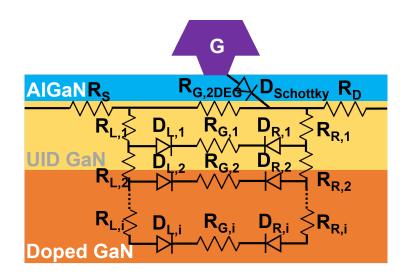

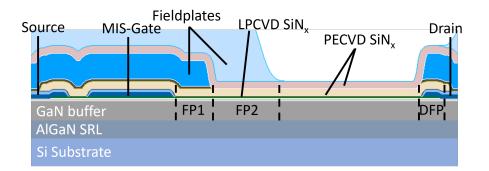

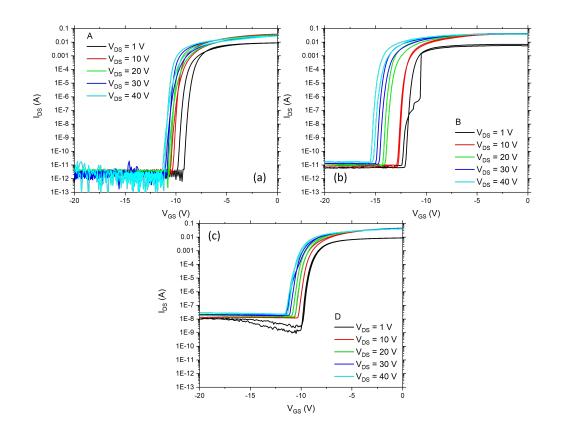

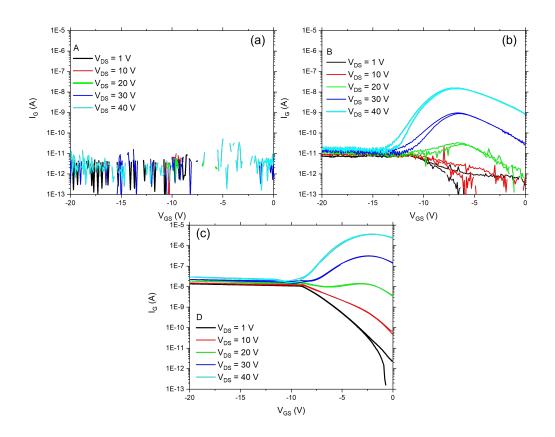

$$V_{2DEG,max} = \frac{en_{2DEG}}{C_{FP}} \tag{2.6}$$