# This electronic thesis or dissertation has been downloaded from Explore Bristol Research, http://research-information.bristol.ac.uk

Author:

Poenaru, Andrei

Modern vector architectures for high-performance computing

Access to the thesis is subject to the Creative Commons Attribution - NonCommercial-No Derivatives 4.0 International Public License. A copy of this may be found at https://creativecommons.org/licenses/by-nc-nd/4.0/legalcode This license sets out your rights and the restrictions that apply to your access to the thesis so it is important you read this before proceeding.

Some pages of this thesis may have been removed for copyright restrictions prior to having it been deposited in Explore Bristol Research. However, if you have discovered material within the thesis that you consider to be unlawful e.g. breaches of copyright (either yours or that of a third party) or any other law, including but not limited to those relating to patent, trademark, confidentiality, data protection, obscenity, defamation, libel, then please contact collections-metadata@bristol.ac.uk and include the following information in your message:

- · Bibliographic details for the item, including a URL

- An outline nature of the complaint

Your claim will be investigated and, where appropriate, the item in question will be removed from public view as soon as possible.

# Modern Vector Architectures for High-Performance Computing

Andrei Poenaru

A dissertation submitted to the University of Bristol in accordance with the requirements for award of the degree of Doctor of Philosophy in the Faculty of Engineering, Department of Computer Science.

June 2021

Word count: 42,675

#### Abstract

Recent generations of general-purpose central processing units (CPUs) for the high-performance segment have had to adopt new approaches in order to deliver increasing performance. Clock frequency has increased little, but the number of cores per chip has increased by several times in a single decade. Inside each core, single instruction, multiple data (SIMD) capabilities have also increased in capacity, resulting in modern vector processors that can achieve peak performance close to that of graphics processing units (GPUs), while maintaining the versatility of a general-purpose processor. These increases in compute power, however, have not been met with similar advances in memory performance.

These architectural changes have coincided with another change in the High-Performance Computing (HPC) landscape: Arm-based processor designs have made their way into supercomputer systems alongside commodity x86 processors. These designs have come in the form of custom implementations from several vendors, and they aim to address deficiencies in both compute and memory performance for the HPC environment. Arm's implementation of wide SIMD is called the Scalable Vector Extension (SVE), and it represents a modern implementation of ideas first seen in the vector architectures of the original Cray supercomputers of the 1970s. For memory bandwidth, the novelty of these Arm-based designs lies in a significant increase in the number of memory channels available, and even in bringing high-bandwidth memory from GPUs to CPUs.

This thesis is a study of modern CPU architectures for HPC. The focus of this research is on the efficacy of the vector capabilities in these new processors, which it investigates from the twin perspectives of performance and programmability. The initial experiments are performed in the context of the first Arm-based hardware adopted in HPC, building up to experiments in simulated and emulated environments on the challenges faced by a wide vector instruction set like SVE, and finally analysing the real-world performance of the first implementation of SVE in hardware. The thesis concludes with an outlook towards the next generations of high-performance processors, highlighting the need for co-design in the quest for performance, and suggesting future research avenues for a new generation of performance tools that can enable informed design decisions for upcoming hardware.

#### **Dedication**

Thank you to Prof Simon McIntosh-Smith for six years of guidance, inspiration, and support. You have been a great leader and mentor for my research projects, and I could not have asked for any more patience, flexibility, open-mindedness, or pragmatism from my supervisor. From you I have learned a composed, constructive, and realistic approach to unexpected circumstances that reaches beyond the scope of this thesis, and for that I am grateful.

Thank you to the Bristol HPC Group for treating me as one of their own from my very first day. Your comments, advice, and feedback have been most helpful as I've learned how to be a researcher, and our conversations have made pleasant journeys that were otherwise only long and tiring.

To my family and close friends, thank you for being by my side the whole way. Your continued reassurance and confidence in me have been invaluable throughout these four years.

Thank you to the many people at Arm who have worked with me throughout this PhD: Assad, Chris, David, John, Olly, Phil, Roxana, and Will. You have been nothing but welcoming, and you have made my journey more engaging, more valuable, more unique.

Finally, my thanks go to members of the Bristol Computer Science Department that have made me feel part of a big family throughout my time here: Ben, Bogdan, Dan, David B, David M, and Tilo. It has been a pleasant and rewarding journey being part of this department, learning from you, and later working alongside you. It was your energy and enthusiasm that helped me decide to pursue this PhD.

#### Acknowledgements

This thesis used the Isambard UK National Tier-2 HPC Service operated by GW4 and the UK Met Office, and funded by EPSRC (EP/T022078/1). Access to the Cray XC50 supercomputers Swan and Horizon was kindly provided by Cray through their Marketing Partner Network. Work in this thesis was carried out using the HPC Zoo, a research cluster run by the University of Bristol HPC Group. Some experiments were performed on the University of Bristol supercomputer systems BluePebble and Catalyst. Early work on the A64FX platform was possible thanks to a remote Early Access programme from Fujitsu.

This PhD was sponsored through a Doctoral Training Partnership studentship award by the Engineering and Physical Sciences Research Council (EPSRC) and the EPSRC National Productivity Investment Fund (NPIF). Some of this work was made possible though an Industrial CASE (ICASE) award in collaboration with Arm. In addition to project funding, Arm kindly provided early access to design documents, technical specifications, and developer tools that enabled research around their emerging Scalable Vector Extension (SVE) instruction set.

# Author's declaration

I declare that the work in this dissertation was carried out in accordance with the requirements of the University's Regulations and Code of Practice for Research Degree Programmes and that it has not been submitted for any other academic award. Except where indicated by specific reference in the text, the work is the candidate's own work. Work done in collaboration with, or with the assistance of, others, is indicated as such. Any views expressed in the dissertation are those of the author.

| SIGNED: | DATE: |

|---------|-------|

|---------|-------|

# Contents

| 1        | Intr | roduction                                           | 1  |

|----------|------|-----------------------------------------------------|----|

|          | 1.1  | Contributions                                       | 3  |

| <b>2</b> | Bac  | ekground                                            | 5  |

|          | 2.1  | Vectorisation                                       | 7  |

|          |      | 2.1.1 Generating and Running Vector Code            | 10 |

|          |      | 2.1.2 An Overview of Modern Vector Instruction Sets | 12 |

|          | 2.2  | Modern High-Performance CPU Architectures           | 15 |

|          | 2.3  | Programming Models and Performance Portability      | 16 |

|          | 2.4  | Common Classes of HPC Applications                  | 20 |

|          | 2.5  | Benchmarking                                        | 21 |

|          |      | 2.5.1 Mini-Apps                                     | 24 |

| 3        | Em   | erging CPU Architectures for HPC                    | 29 |

|          | 3.1  | High Performance Arm-based Systems                  | 31 |

|          |      | 3.1.1 The ThunderX2 Microarchitecture               | 31 |

|          | 3.2  | Benchmarks                                          | 34 |

|          | 3.3  | Experimental Set-Up                                 | 39 |

|          | 3.4  | Results                                             | 42 |

|          |      | 3.4.1 Best Application Performance                  | 42 |

|          |      | 3.4.2 Compiler Performance Comparison               | 50 |

|          |      | 3.4.3 Library Performance Comparison                | 55 |

### CONTENTS

|   | 3.5 | ThunderX2 Performance Summary                   | 57         |

|---|-----|-------------------------------------------------|------------|

|   | 3.6 | Reproducibility                                 | 58         |

| 4 | Nex | xt-Generation Vector Instruction Sets           | <b>5</b> 9 |

|   | 4.1 | Modern Vector Instructions Sets                 | 60         |

|   | 4.2 | SVE Evaluation Methodology                      | 61         |

|   | 4.3 | Results                                         | 63         |

|   |     | 4.3.1 Compiler Vectorisation Efficiency         | 63         |

|   |     | 4.3.2 Dynamic Instruction Analysis              | 65         |

|   |     | 4.3.3 SVE Vector Lane Utilisation               | 69         |

|   |     | 4.3.4 SVE Memory Operations                     | 71         |

|   | 4.4 | SVE Usage Discussion                            | 73         |

|   | 4.5 | Relevance of SVE for HPC                        | 77         |

|   | 4.6 | Towards Accurate Performance Modelling          | 78         |

|   | 4.7 | Reproducibility                                 | 79         |

|   | 4.8 | Conclusion                                      | 79         |

| 5 | The | e Effects on Cache of Wide Vector Operations    | 81         |

|   | 5.1 | Processor Cache Design Space                    | 83         |

|   | 5.2 | Cache Analysis Methodology                      | 84         |

|   | 5.3 | Results                                         | 88         |

|   |     | 5.3.1 Cache Parameters                          | 88         |

|   |     | 5.3.2 SVE Width                                 | 91         |

|   |     | 5.3.3 Lifetimes                                 | 93         |

|   |     | 5.3.4 Non-Contiguous Accesses                   | 95         |

|   | 5.4 | Implications for Vector Processors              | 98         |

|   | 5.5 | Towards Performance-Portable Application Design | 98         |

|   | 5.6 | Reproducibility                                 | 100        |

|   | 5.7 | Conclusion                                      | 100        |

| 6 | Nex | xt-Generation Vector Processors                 | 101        |

|   | 6.1 | Background                                      | 102        |

|   | 6.2 | Performance Evaluation Methodology              | 103        |

|   |     | 6.2.1 Randwidth-Round Renchmarks                | 104        |

|                  |      | 6.2.2 Compute-Bound Benchmarks                                  |

|------------------|------|-----------------------------------------------------------------|

|                  | 6.3  | Results and Performance Analysis                                |

|                  |      | 6.3.1 Benchmark Results                                         |

|                  |      | 6.3.2 Thread Placement on the A64FX 117                         |

|                  | 6.4  | Future Work                                                     |

|                  | 6.5  | Reproducibility                                                 |

|                  | 6.6  | Conclusion                                                      |

| 7                | Pro  | gramming Models for Modern HPC Architectures 123                |

|                  | 7.1  | Background                                                      |

|                  |      | 7.1.1 High-Performance Molecular Docking 125                    |

|                  |      | 7.1.2 Modern Parallel Programming Models 125                    |

|                  |      | 7.1.3 Performance Portability                                   |

|                  | 7.2  | Evaluation Methodology                                          |

|                  |      | 7.2.1 A BUDE Mini-App                                           |

|                  |      | 7.2.2 Performance Analysis                                      |

|                  | 7.3  | Results and Performance Analysis                                |

|                  |      | 7.3.1 CPUs                                                      |

|                  |      | 7.3.2 GPUs                                                      |

|                  | 7.4  | Towards Portable High-Performance Code                          |

|                  | 7.5  | Reproducibility                                                 |

|                  | 7.6  | Conclusion                                                      |

| 8                | Res  | earch for Future HPC Architectures 145                          |

|                  | 8.1  | Towards Accurate Performance Modelling                          |

|                  | 8.2  | Next-Generation Vector Processors                               |

|                  | 8.3  | Productivity in Modern Programming                              |

| 9                | Con  | aclusion 149                                                    |

| $\mathbf{A}_{]}$ | ppen | dix A Data 155                                                  |

|                  | A.1  | Chapter 3: Emerging CPU Architectures for HPC 155               |

|                  | A.2  | Chapter 4: Next-Generation Vector Instruction Sets 157          |

|                  | A 3  | Chapter 5: The Effects on Cache of Wide Vector Operations . 170 |

### CONTENTS

| A.4    | Chapter 6: Next-Generation Vector Processors               | 174 |

|--------|------------------------------------------------------------|-----|

| A.5    | Chapter 7: Programming Models for Modern HPC Architectures | 180 |

| Appen  | dix B Cache Simulator Design                               | 183 |

| B.1    | The Main Loop                                              | 183 |

| B.2    | Reading Execution Traces                                   | 184 |

|        | B.2.1 Efficient Reading of Traces                          | 185 |

| B.3    | Cache Models                                               | 186 |

|        | B.3.1 Capturing Simulation Data                            | 188 |

| B.4    | Configuration Files                                        | 188 |

| B.5    | Simulator Output                                           | 189 |

| B.6    | Testing                                                    | 190 |

| Acrony | vms                                                        | 191 |

| Refere | nces                                                       | 195 |

# List of Tables

| 3.1 | Processor model details and their peak performance                    | 40  |

|-----|-----------------------------------------------------------------------|-----|

| 3.2 | Compilers available for each platform                                 | 40  |

| 3.3 | Third-party libraries, the benchmarks that use them, and the          |     |

|     | available variants                                                    | 40  |

| 3.4 | Best compiler for each application on the platforms studied           | 51  |

| 3.5 | Initial TX2 compiler versions from 2018 compared to the latest        |     |

|     | available releases in 2021                                            | 54  |

| 4.1 | Number of loops vectorised by each compiler on the top loop-          |     |

|     | nests, selected by percentage of total run time on a Thunder<br>X2 $$ |     |

|     | processor, in the mini-apps studied. The results for AVX2 and $$      |     |

|     | AVX-512 were identical; here they share the $AVX$ label               | 64  |

| 5.1 | Cache configurations of current-generation server-class pro-          |     |

|     | cessors based on Arm architecture. Level 2 is shared on A64FX,        |     |

|     | but private on TX2; TX2 has a shared cache at Level 3                 | 86  |

| 5.2 | Percentage differences between data from simulation and equi-         |     |

|     | valent statistics obtained from querying hardware counters on         |     |

|     | real processors. The simulated results are within $10\%$ of the       |     |

|     | data collected from hardware                                          | 86  |

| 6.1 | Hardware specifications of the processors benchmarked                 | 105 |

| 7.1 | Hardware platforms used for evaluation                                | 129 |

### LIST OF TABLES

| 7.2   | Compilers used and their programming model and target plat-                                                       |

|-------|-------------------------------------------------------------------------------------------------------------------|

|       | form support                                                                                                      |

| A.1   | Data from Figure 3.1                                                                                              |

| A.2   | Data from Figure 3.4                                                                                              |

| A.3   | Data from Figure 3.5                                                                                              |

| A.4   | Data from Figure 3.6                                                                                              |

| A.5   | Data from Figure 3.8                                                                                              |

| A.6   | Data from Figure 4.1: Instruction count, grouped by instruc-                                                      |

|       | tion type, for the STREAM benchmark                                                                               |

| A.7   | Data from Figure 4.2: Instruction count, grouped by instruc-                                                      |

|       | tion type, for the BUDE benchmark                                                                                 |

| A.8   | Data from Figure 4.3: Instruction count, grouped by instruc-                                                      |

|       | tion type, for the TeaLeaf benchmark                                                                              |

| A.9   | Data from Figure 4.4: Instruction count, grouped by instruc-                                                      |

|       | tion type, for the CloverLeaf benchmark                                                                           |

| A.10  | Data from Figure 4.5: Instruction count, grouped by instruc-                                                      |

|       | tion type, for the MegaSweep benchmark                                                                            |

| A.11  | Data from Figure 4.6: Instruction count, grouped by instruc-                                                      |

| A 10  | tion type, for the MiniFMM benchmark                                                                              |

|       | Data from Figure 4.7                                                                                              |

| A.13  | Data from Figures 5.6, 5.7, and 5.8: Cache miss rates at                                                          |

|       | different SVE widths for the CloverLeaf, MegaSweep, and<br>MiniFMM benchmarks, respectively, on the ThunderX2 and |

|       | A64FX processors                                                                                                  |

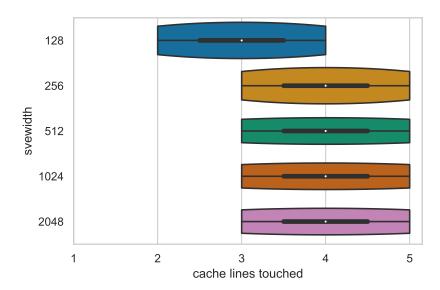

| A 14  | Data from Figure 5.9: Total number of non-contiguous ac-                                                          |

| 11,11 | cesses, grouped by the number of cache lines touched at each                                                      |

|       | SVE width for the CloverLeaf benchmark                                                                            |

| A.15  | Data from Figure 5.10: Total number of non-contiguous ac-                                                         |

|       | cesses, grouped by the number of cache lines touched at each                                                      |

|       | SVE width for the MiniFMM benchmark                                                                               |

| A.16  | Benchmark results for each compiler on each platform covered. 174                                                 |

| A.17 Data for Figure 6.11: Benchmark performance for different   |     |

|------------------------------------------------------------------|-----|

| run-time configurations on the A64FX                             | 179 |

| A.18 MiniBUDE performance data on all platforms studied, grouped |     |

| by programming model                                             | 180 |

# List of Figures

| 2.1 | Scalar (a) and vector (b) instructions                            | 8  |

|-----|-------------------------------------------------------------------|----|

| 2.2 | x86 vector register aliases: xmm and ymm refer to the lower 128   |    |

|     | and 256 bits, respectively, of the 512-bit ${\tt zmm}$ registers  | 13 |

| 2.3 | SVE vector registers. NEON (V) registers are aliased to the       |    |

|     | lower 128 bits of the full SVE (Z) registers. Additional predic-  |    |

|     | ate $(P)$ and control $(ZCR)$ registers also depend on the vector |    |

|     | length (VL). Source: Arm [127]                                    | 14 |

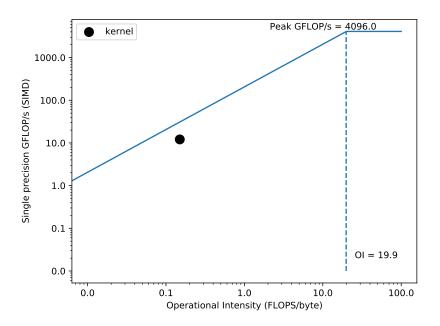

| 2.4 | Example of a roofline chart, a visualisation produced using the   |    |

|     | roofline model. The kernel's achieved performance is below the    |    |

|     | memory bandwidth roof                                             | 24 |

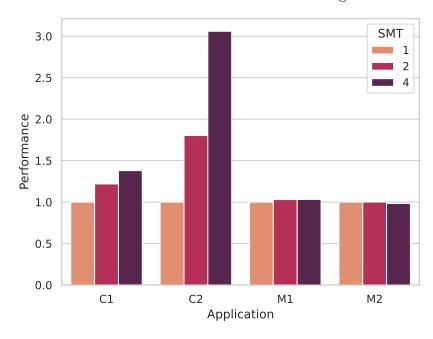

| 3.1 | Relative performance of four application on the different SMT     |    |

|     | settings of a TX2 node. Higher numbers represent faster run       |    |

|     | times                                                             | 32 |

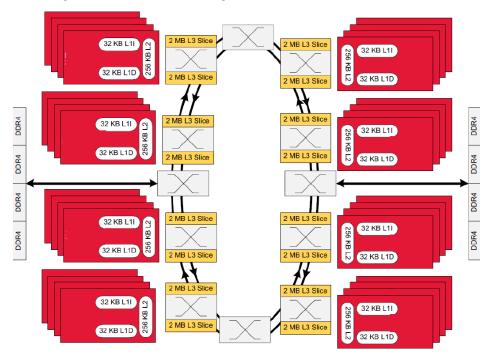

| 3.2 | The cache configuration of the 32-core ThunderX2 processor.       |    |

|     | Source: Cavium [16]                                               | 33 |

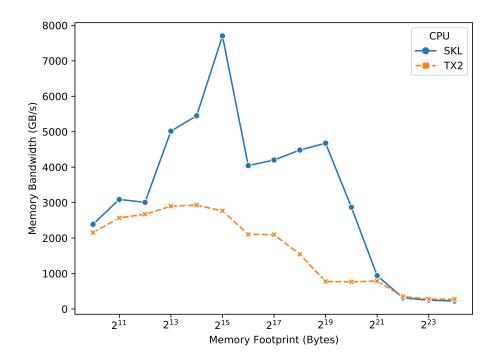

| 3.3 | Total (aggregate) cache bandwidth achieved on the Thun-           |    |

|     | der<br>X2 (TX2) and Intel Xeon Platinum 8176 (SKL)                | 34 |

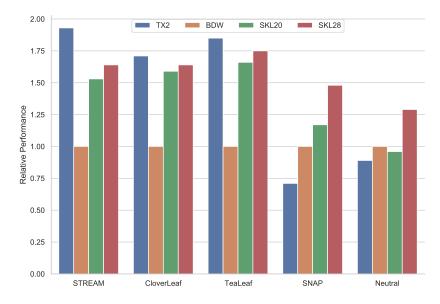

| 3.4 | Relative performance of mini-apps compared to Intel Broad-        |    |

|     | well. Higher numbers represent better performance                 | 42 |

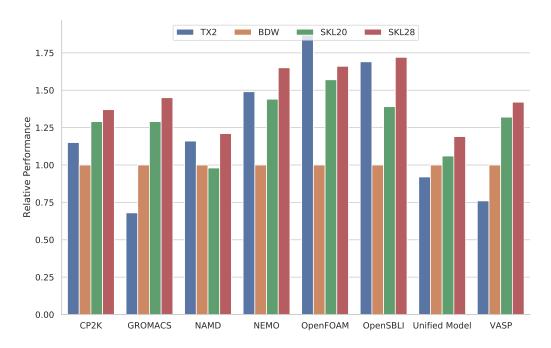

| 3.5 | Relative performance of applications compared to Intel Broad-     |    |

|     | well. Higher numbers represent better performance                 | 43 |

### LIST OF FIGURES

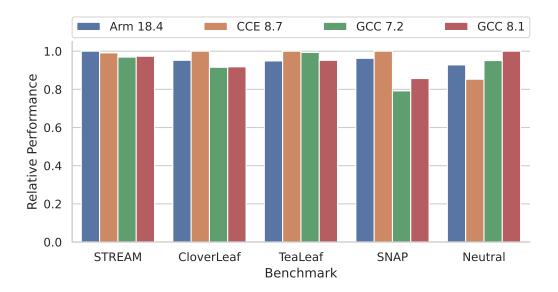

| 3.6 | Relative performance of mini-apps running on ThunderX2 when       |    |

|-----|-------------------------------------------------------------------|----|

|     | compiled with different toolchains                                | 52 |

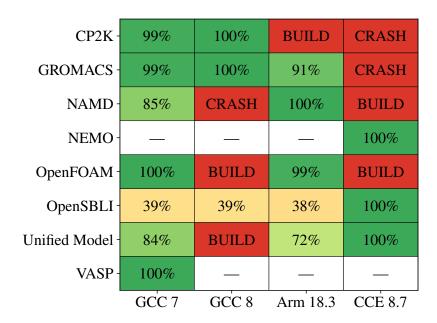

| 3.7 | Relative performance of full applications running on Thun-        |    |

|     | derX2 when compiled with different toolchains. For each ap-       |    |

|     | plication, the fastest result is labelled " $100\%$ ". Build- and |    |

|     | run-time errors are marked in red, and dashes indicate build      |    |

|     | configurations not supported at the time of writing               | 53 |

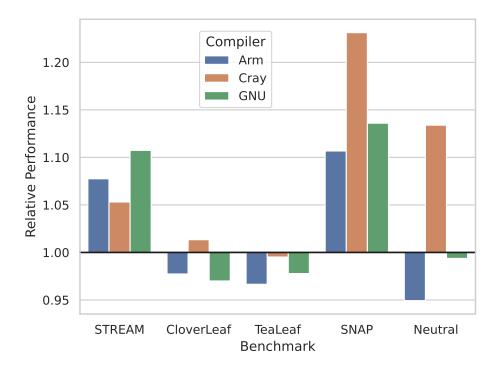

| 3.8 | Relative performance of the latest version of TX2 compilers in    |    |

|     | 2021 compared to the initial releases in 2018. Numbers above      |    |

|     | 1 represent an increase in performance                            | 54 |

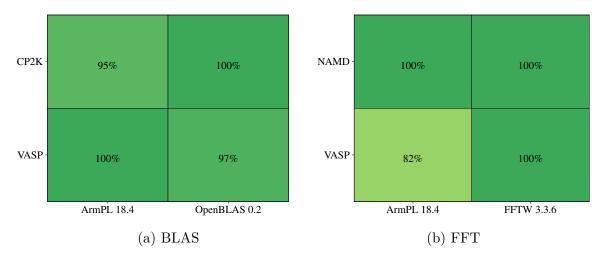

| 3.9 | Relative performance of optimised maths libraries on Thun-        |    |

|     | derX2                                                             | 56 |

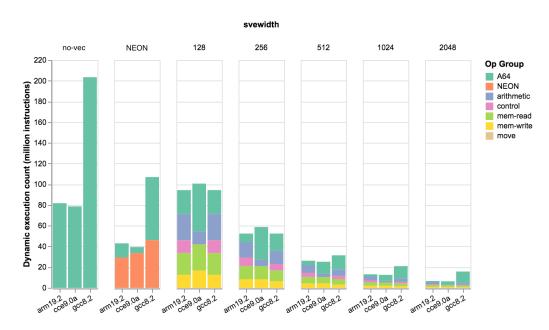

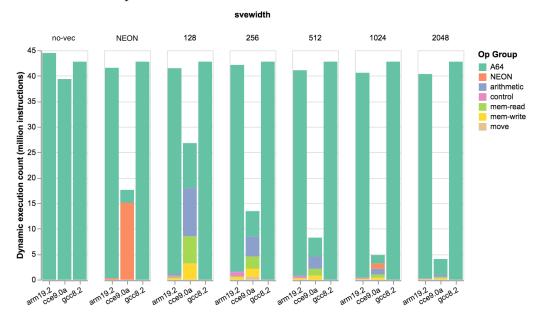

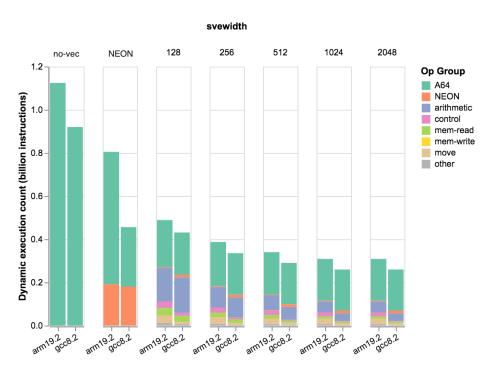

| 4.1 | Dynamic instruction count and grouping for STREAM. Lower          |    |

|     | is generally better. $A64$ refers to scalar instructions; $NEON$  |    |

|     | refers to base-AArch64 ASIMD vector instructions; the re-         |    |

|     | maining groups are all SVE instructions                           | 66 |

| 4.2 | Dynamic instruction count and grouping for miniBUDE. Lower        |    |

|     | is generally better. $A64$ refers to scalar instructions; $NEON$  |    |

|     | refers to base-AArch64 ASIMD vector instructions; the re-         |    |

|     | maining groups are all SVE instructions                           | 67 |

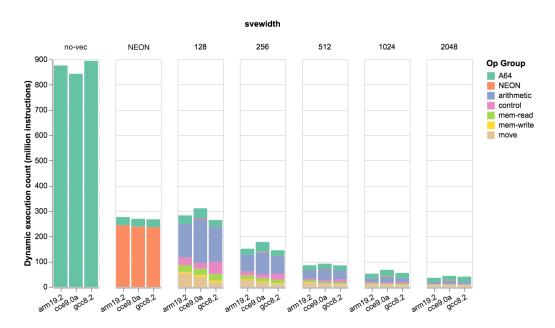

| 4.3 | Dynamic instruction count and grouping for TeaLeaf                | 68 |

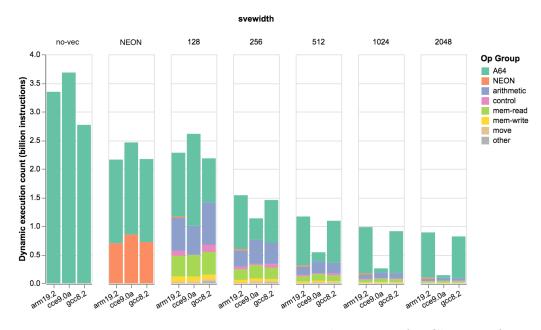

| 4.4 | Dynamic instruction count and grouping for CloverLeaf             | 68 |

| 4.5 | Dynamic instruction count and grouping for MegaSweep              | 69 |

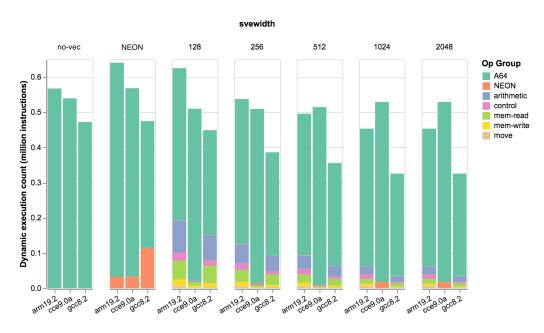

| 4.6 | Dynamic instruction count and grouping for MiniFMM                | 70 |

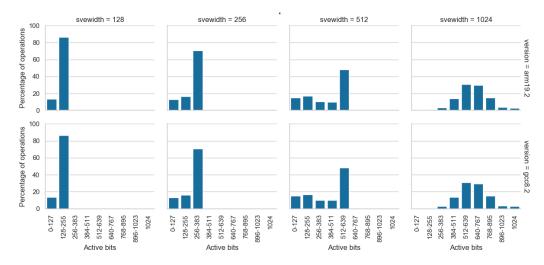

| 4.7 | Histogram showing the number of active bits in the SVE op-        |    |

|     | erations performed by MiniFMM. The application cannot sat-        |    |

|     | urate the full widths of the vectors when the SVE length is       |    |

|     | 512 bits or higher                                                | 71 |

| 4.8 | Histogram showing the number of active bits in the SVE op-        |    |

|     | erations performed by miniBUDE. Vectorisation is perfectly        |    |

|     | efficient at all SVE widths                                       | 72 |

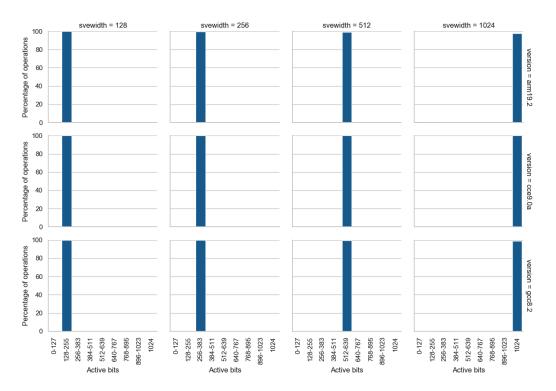

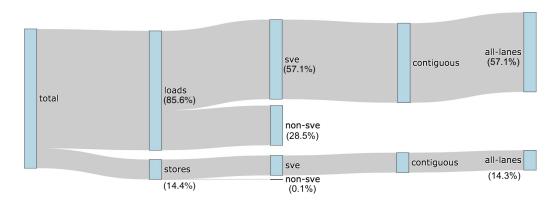

| 4.9  | Relative counts, by number of instructions, of memory operations in miniBUDE. All memory accesses are contiguous and most are performed through SVE instructions                                                                                                                                | 74 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.10 | Relative counts, by number of instructions, of memory operations in CloverLeaf. Memory accesses are split between SVE and non-SVE instructions. In the vast majority of cases where SVE is used, accesses are contiguous and all the lanes are being utilised                                   | 74 |

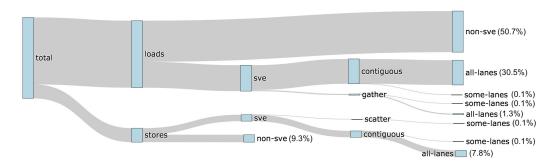

| 4.11 | Relative counts, by number of instructions, of memory operations in MiniFMM. This applications shows a mixture of SVE and non-SVE operations, and the SVE ones show a further split between contiguous and non-contiguous accesses. Not all lanes are always used in SVE operations for MiniFMM | 75 |

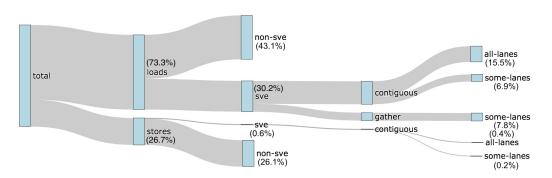

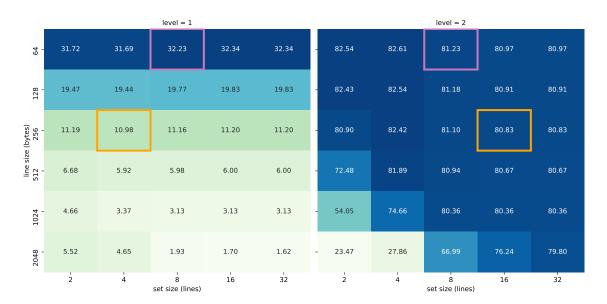

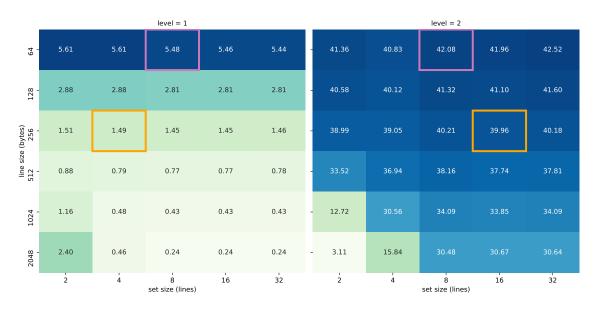

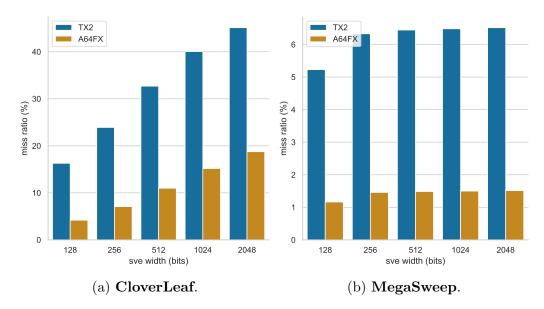

| 5.1  | Cache misses, as a percentage of total cache accesses, for CloverLeaf in different cache configurations, at the two levels of cache. The A64FX and TX2 configurations are highlighted in orange and pink, respectively                                                                          | 88 |

| 5.2  | Cache misses, as a percentage of total cache accesses, for <b>MegaSweep</b> in different cache configurations, at the two levels of cache                                                                                                                                                       | 89 |

| 5.3  | Cache misses, as a percentage of total cache accesses, for <b>MiniFMM</b> in different cache configurations, at the two levels of cache                                                                                                                                                         | 89 |

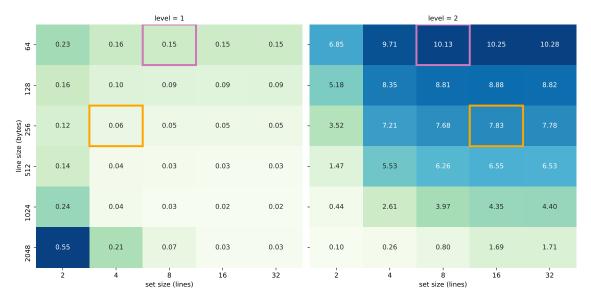

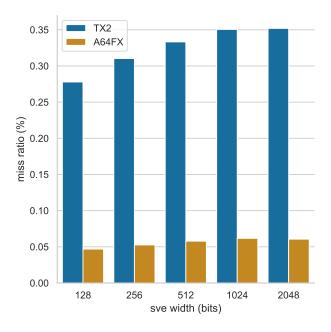

| 5.4  | Cache miss rates for at different SVE lengths, for the cache configurations in the Marvell ThunderX2 ( <b>TX2</b> ) and the Fujitsu A64FX ( <b>A64FX</b> )                                                                                                                                      | 91 |

| 5.5  | Cache miss rates for at different SVE lengths, for the cache configurations in the Marvell ThunderX2 ( <b>TX2</b> ) and the Fujitsu A64FX ( <b>A64FX</b> ) on the <b>MiniFMM</b> benchmark                                                                                                      | 92 |

### LIST OF FIGURES

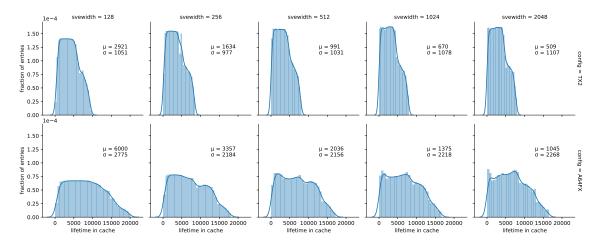

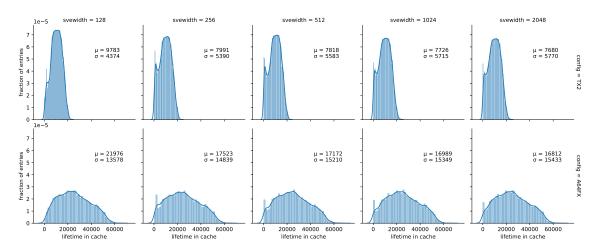

| 5.6  | Level 1 cache lifetimes for <b>CloverLeaf</b> at different SVE lengths under the configurations of the A64FX and the TX2. A higher |

|------|------------------------------------------------------------------------------------------------------------------------------------|

|      |                                                                                                                                    |

|      | mean $(\mu)$ shows more time spent in cache on average; $\sigma$ is the                                                            |

|      | standard deviation                                                                                                                 |

| 5.7  | Level 1 cache lifetimes for <b>MegaSweep</b> at different SVE lengths                                                              |

|      | under the A64FX and TX2 configurations                                                                                             |

| 5.8  | Level 1 cache lifetimes for <b>MiniFMM</b> at different SVE lengths                                                                |

|      | under the A64FX and TX2 configurations 95                                                                                          |

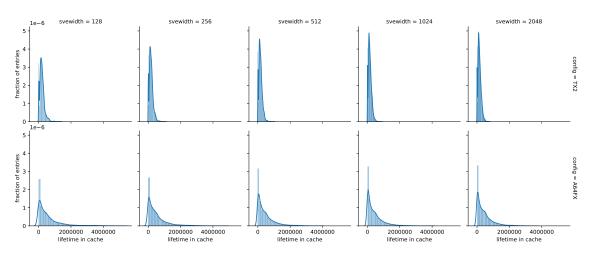

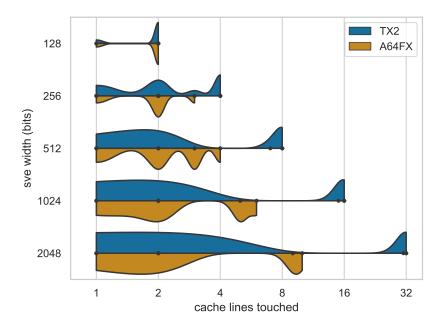

| 5.9  | Distribution of the numbers of cache lines touched by non-                                                                         |

|      | contiguous SVE memory accesses for <b>CloverLeaf</b> on the A64FX                                                                  |

|      | and TX2 cache configuration. Thicker bars represent more                                                                           |

|      | memory accesses                                                                                                                    |

| 5.10 | Distribution of the numbers of cache lines touched by non-                                                                         |

|      | contiguous SVE memory accesses for $\mathbf{MiniFMM}$ on the TX2                                                                   |

|      | cache configuration. On the A64FX configuration, all requests                                                                      |

|      | were services by 2 cache lines                                                                                                     |

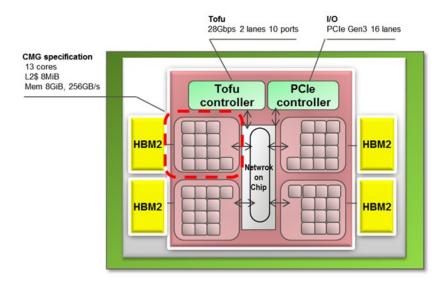

| 6.1  | A64FX block diagram. Source: Fujitsu [70] 103                                                                                      |

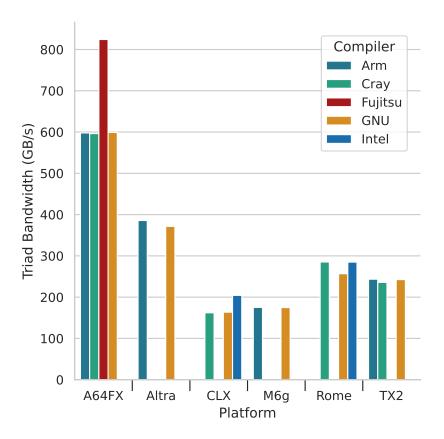

| 6.2  | Achieved bandwidth in BabelStream Triad. Higher numbers                                                                            |

|      | show better results                                                                                                                |

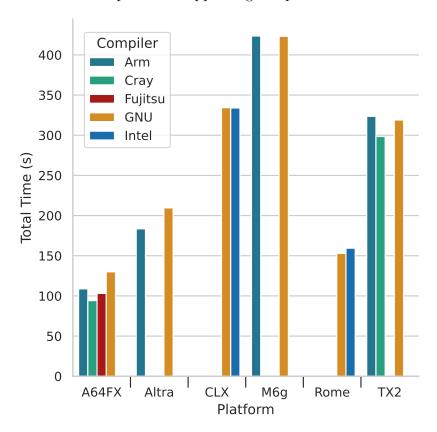

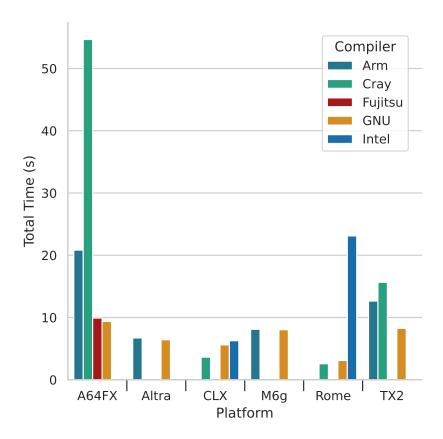

| 6.3  | TeaLeaf bm5 benchmark time. Lower numbers show better                                                                              |

|      | results                                                                                                                            |

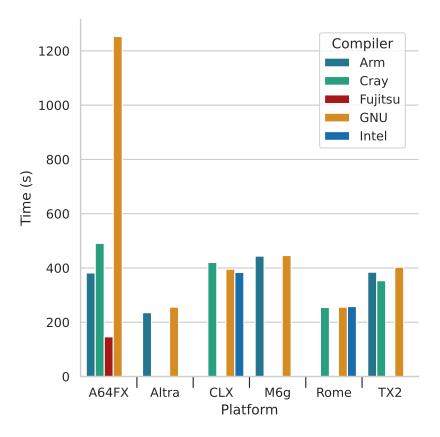

| 6.4  | CloverLeaf bm16 benchmark time. Lower numbers show better                                                                          |

|      | results                                                                                                                            |

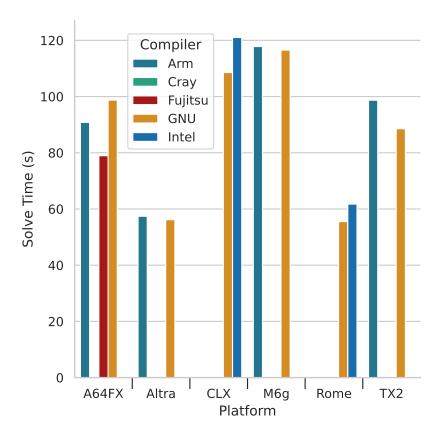

| 6.5  | OpenFOAM DrivAer solve time after 50 time steps. The time                                                                          |

|      | taken for the first step is excluded. Lower numbers show better                                                                    |

|      | results                                                                                                                            |

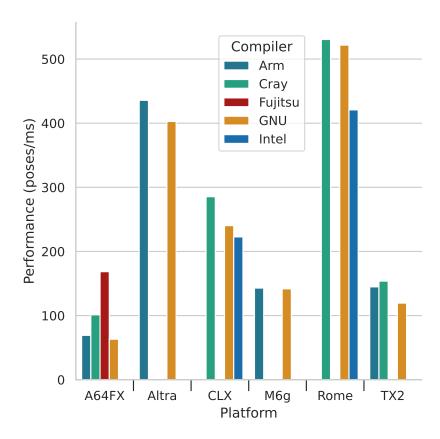

| 6.6  | Achieved performance in miniBUDE. Higher numbers show                                                                              |

|      | better results                                                                                                                     |

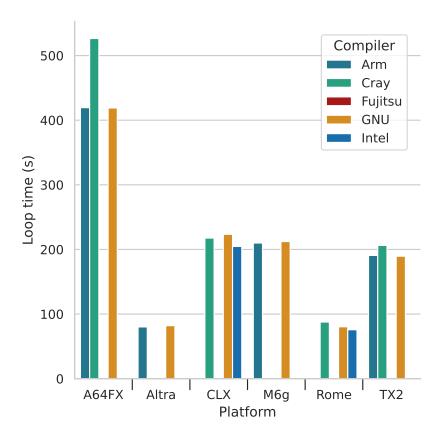

| 6.7  | SPARTA benchmark time using the collisional flow input, 10M                                                                        |

|      | cells, and 5000 iterations. Lower numbers show better results. 114                                                                 |

| 6.8  | MiniFMM benchmark time using a Plummer and the OpenMP                                                                              |

|      | tasks implementation. Lower numbers show better results. 115                                                                       |

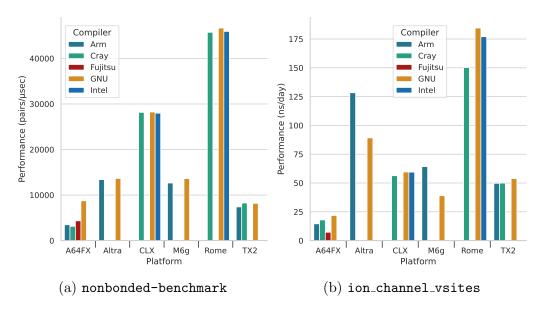

| 6.9  | Achieved performance in two GROMACS benchmarks. The                     |     |

|------|-------------------------------------------------------------------------|-----|

|      | open-source FFTW library was used with GCC and Fujitsu,                 |     |

|      | ArmPL was used with the ACfL, MKL with the Intel compiler,              |     |

|      | and Cray's optimised build of FFTW was used with CCE.                   |     |

|      | Higher numbers show better results                                      | 116 |

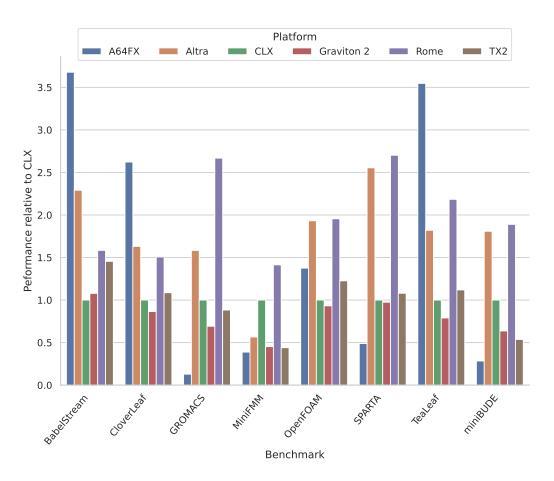

| 6.10 | Performance across all benchmarks, normalised to Intel Cas-             |     |

|      | cade Lake. The best compiler choice was used in each case.              |     |

|      | Higher numbers represent higher performance                             | 118 |

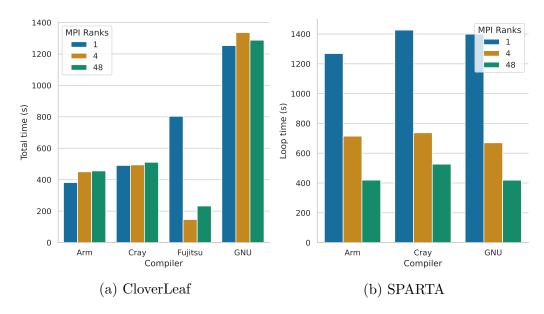

| 6.11 | Comparison of MPI–OpenMP run configurations on A64FX.                   |     |

|      | As many OpenMP threads were used as needed in each case                 |     |

|      | to fill all 48 cores. Lower numbers show better results. $\ \ldots \ .$ | 119 |

| 7.1  | Performance of the OpenMP implementation at different group             |     |

|      | sizes, normalised to the best result on each platform. Plat-            |     |

|      | forms are labelled using the abbreviations in Table 7.1 and             |     |

|      | the number of cores. Higher numbers, shown here in brighter             |     |

|      | colours, correspond to higher performance                               | 132 |

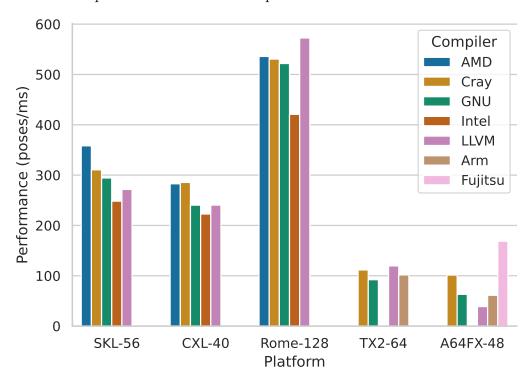

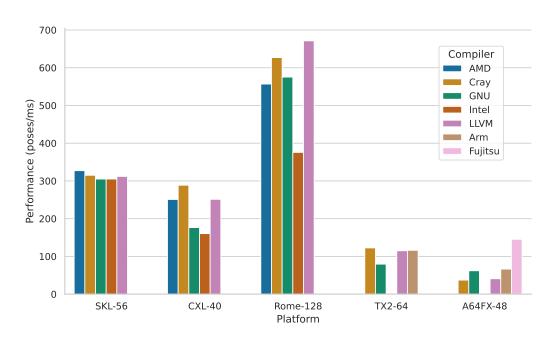

| 7.2  | Performance of the OpenMP implementation across systems                 |     |

|      | and compilers. Higher numbers represent faster execution. $$            | 133 |

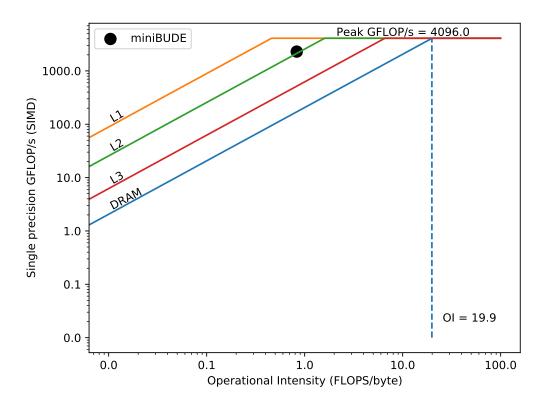

| 7.3  | Cache-aware roofline for the Cascade Lake platform showing              |     |

|      | the achieved performance for miniBUDE                                   | 134 |

| 7.4  | Performance of Kokkos with the OpenMP backend on the test               |     |

|      | platforms. Higher numbers represent faster execution                    | 135 |

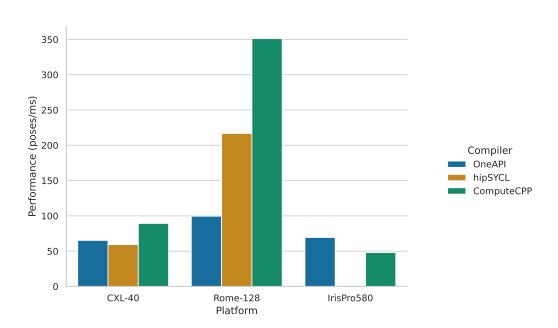

| 7.5  | Relative performance of SYCL implementations, on the plat-              |     |

|      | forms where more than one was available. Higher numbers                 |     |

|      | represent faster execution                                              | 136 |

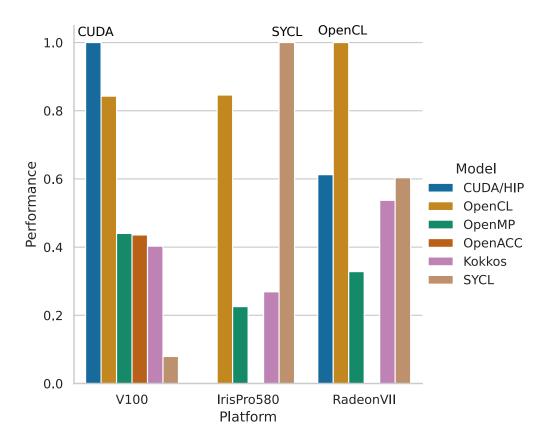

| 7.6  | Performance of the GPU implementations, normalized to the               |     |

|      | fastest result on each platform. The fastest model on each              |     |

|      | platform is labelled explicitly                                         | 140 |

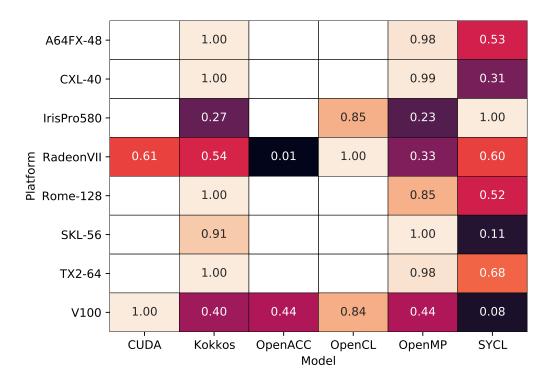

| 7.7  | Achieved performance across all programming models, norm-               |     |

|      | alised to the fastest result on each platform. Lighter colours          |     |

|      | correspond to higher relative performance; blank cells are im-          |     |

|      | nossible results                                                        | 141 |

### CHAPTER 1

#### Introduction

Computational science is an integral part of modern scientific research. It gives scientists tools for early and rapid experimentation at a cost far below what is possible without computer systems. Each scientific domain brings its own set of problem types and challenges to overcome, but the underlying systems have similar characteristics. The field that brings together these challenges and works to improve computational systems for the benefit of all areas of science is *High-Performance Computing (HPC)*.

HPC is concerned with architecting and exploiting computing systems to their fullest in scientific applications. The core research in HPC that eventually benefits the wider fields of science revolves around modelling computer architectures, understanding their weak and strong points, designing software to exploits those, and proposing improvements for future hardware generations. Since the times of the early Cray supercomputers in the 1970s [117], HPC hardware has taken many forms, but one core goal has stayed the same: designing architectures that bring maximum computational power to domain scientists, as effortlessly as possible.

The Cray-1 was a computer that utilised purpose-built hardware to achieve high performance. This approach was common in HPC even in the 2000s, but in the 1990s a different paradigm appeared: instead of large mainframes, powerful computational systems could be built from collections of smaller, general-purpose hardware. The new paradigm gained traction quickly, and by 2010 the majority of HPC systems were built from commodity hardware and

ran the same operating systems as servers and workstations everywhere [132, 64].

One part of the motivation behind this change was production costs, but another part was the increasing overlap with consumer hardware: processor features that were previously used in HPC found their use in home computers. Early examples of such features migrating from enterprise to consumer hardware are floating-point capabilities, error-correcting memory, and 64-bit word sizes; a more recent example is vector processing, the paradigm in which single instructions operate on several operands—or sets of operands—at the same time. The Cray-1 and the earlier systems TI-ASC from Texas Instruments and STAR-loo from Control Data Corporation were the first architecture to utilise vector processing [33], but by the year 2000 desktop processors included functional units for single instruction, multiple data (SIMD) [36] operations, which brought significant speed-up to multimedia applications. For video games and advanced video encoding/decoding, dedicated hardware was added to general-purpose processors: video cards, or graphics processing units (GPUs). The late 2000s then saw GPUs reach back into HPC through a model called general-purpose graphics processing units (GPGPUs), based on the observation that GPUs are at their core wide vector processors and, as had been correctly identified many decades before, scientific workloads can benefit from such processors.

GPUs saw a big rise in adoption over the following years [62], and since then the HPC community has focused on quantifying the benefit of wide vector processing and optimising application code to take advantage of it [65]. On the one hand, many Machine Learning (ML) applications were identified as prime use cases for GPUs, and today most research in the field of artificial intelligence (AI) uses GPUs [96, 54]. On the other hand, porting many traditional applications to GPUs has proved difficult, and so a middle-ground could be more favourable: a general-purpose central processing unit (CPU) with wide vector capabilities may bring a large portion of a GPUs benefit with few of the drawbacks. This design is prevalent in 2021, when all major vendors of high-performance processors integrate SIMD units in their CPUs,

and this hardware often has higher vector processing capabilities than GPUs themselves had a decade ago.

In 2016, Arm introduced the Scalable Vector Extension (SVE), a new vector instruction set that combines modern instruction set architecture (ISA) design with the classic idea of vector processing [128]. This announcement aligned with another step in unifying HPC and consumer-grade hardware: Arm-based CPUs making their way into the x86-dominated supercomputer world [112, 77, 115]. SVE is enabling Arm to exploit an industry-wide move towards accelerated vector computation inside CPUs [122, 31], and in 2020 the fastest supercomputer in the world was powered by this new architecture [119]. This incredible achievement was the result of many years of co-design, the process of iteratively making design decisions by considering all the hardware, software, and tooling components involved in a system all together, rather than each of them individually [51, 9]. It is a modern approach to HPC research, which benefits chip designers, software developers, and end-users alike, but holistically integrating the many aspects involved is an enormous challenge that uncovers the very limits of our tools and methodology. In this thesis, I explore co-design and its role in creating the next generations of HPC systems, from the hardware to the software used to program it.

#### 1.1 Contributions

This thesis makes several contributions:

- In Chapter 3 I discuss the implications of a diversified landscape of architectures in mainstream HPC and I evaluate the Arm-based ThunderX2 processor, the first general-purpose CPU to compete with the x86 architecture since its establishment in HPC more than ten years ago;

- Chapter 4 expands on top of strengths and weaknesses identified in the previous chapter to estimate the impact of next-generation instructions sets on the performance of scientific applications;

#### 1.1. CONTRIBUTIONS

- In Chapter 5 I present an in-depth exploration of the implications for the processor's memory subsystem of the wide vector operations available in contemporary vector instructions sets;

- Chapter 6 analyses the real-world performance of the first modern microarchitectural implementation of a scalable vector instruction set, which at the time of writing powers the machine ranked first in the TOP500;

- Chapter 7 surveys the software frameworks used in HPC and their efficacy at generating performant code on a wide range of modern architectures, including Arm- and x86-based CPUs, as well as GPUs from all major vendors;

- Finally, Chapter 8 gives an outlook towards further research tools and processes that are needed to enable accurate and relevant performance experiments in HPC, keeping to the overarching goals of co-design and performance portability.

### CHAPTER 2

## Background

Supercomputers, as we know them today, are the result of decades of ongoing research, technological advances, and engineering expertise. Between the 1970s and the mid 1990s, HPC systems were large monolithic machines, but nowadays they are collections of commodity processors, carefully coupled together to create performant machines that can split their computational capacity into arbitrary partitions on demand. In these systems, the smallest building block is a *node*, generally in the form of a blade or rack-mounted server. Nodes are joined together using a high-performance *interconnect*, thus creating clusters that can range in size from only a few nodes in a single rack to datacenter-sized systems comprising tens or hundreds of thousands of nodes, for which purpose-built facilities are needed. Such a design is scalable, cost-efficient, and failure-tolerant.

On the inside, each node is powered by hardware similar to what can be found in web-services datacenters: high-performance general-purpose central processing units (CPUs), often with high core counts, large pools of fast memory, and tiered storage that aims to strike a balance between capacity and speed. In the early 2000s, these processors were based on a number of different architectures, often each with its own operating system. More

recently, the x86-based chips from Intel and AMD¹ have dominated the supercomputer market, with some systems based on IBM's POWER architecture, and over the past few years also Arm-based designs from Fujitsu, Marvell, or Ampere. On the vast majority of systems, the operating system used is Linux [132]. This design has stayed relatively unchanged over the past decade; each component has become individually faster, but the way they are integrated together is similar.

Inside a node, mostly for cost and power efficiency reasons, it has been common for nodes to utilise a *dual-socket* configuration, in which two processors share a single motherboard. Single-socket configurations are used when the chosen CPU cannot be used in multi-socket systems, and some systems have four sockets per node, but more commonly vendors pack several motherboards inside a single blade rather than adding more sockets to a single motherboard [22].

In multi-socket systems, each CPU is connected directly to only a part of the system's main memory. To access memory attached to other (remote) sockets, the CPU must send a request over the inter-socket connection and wait to receive back the data. This gives rise to a non-uniform memory access (NUMA) architecture, in which the latency of accessing main memory depends on where the data is located. Because all NUMA accesses to other sockets share the same interconnect, the more remote requests are made concurrently, the slower they will perform.

For some workloads, specific types of co-processors can be employed alongside the CPU to improve performance. These are known as *accelerators*, of which common examples nowadays are general-purpose graphics processing units (GPGPUs), field-programmable gate arrayss (FPGAs), and high-performance network interface cards (NICs) with support for in-network computation. Accelerators are attached to a node's CPU, the latter being referred to as the *host* in such a configuration.

<sup>&</sup>lt;sup>1</sup>The term x86 is sometimes used to refer to the original 32-bit instruction set, which was expanded to 64 bits with x86\_64 or amd64. Because x86\_64 is a superset of the 32-bit x86, and 32-bit x86 systems are not in use any more in HPC today, it is common to use "x86" as shorthand for x86\_64. In this thesis, I do not use any 32-bit hardware, and the terms x86, x86\_64, and amd64 are used interchangeably.

At the CPU level, the last decade has brought many changes. In 2010, the top-end parts—sometimes referred to as stock keeping units (SKUs)—of high-performance processors had between 10 and 16 cores; in 2020, a single processor can house up to 64 cores. To support this 4× increase in core count, other components on and off the chip have also become bigger and faster: caches are larger and comprise several levels, interconnects—both within nodes (between sockets) and between nodes—have higher bandwidth and lower latencies due to increased optimisation and lower overhead, and main memory has increased in speed and capacity.

This increase in computation capacity has outlined, around the middle of the previous decade, the next milestone in the HPC world: exascale, the capacity to compute 10<sup>18</sup> floating-point operations within a second (1 EFLOP/s) in an individual system [92]. As systems have got closer to this milestone, which has not yet been reached as of mid-2021, the HPC literature speaks of "the road to exascale", referring to challenges encountered as bigger-and-bigger systems are commissioned, and suggesting potential solutions. Reaching exascale-level performance is such an enormous challenge that we need to be able to extract as much performance as possible from all of a system's components, while still maintaining a clean, productive application design. Thus, a balance needs to be reached between writing high-performance code and not over-specialising for current hardware, because the next iterations of the systems may use different architectures, potentially from different vendors, which might support different programming models.

Regardless of the architectures and configurations used in a supercomputer, one feature has been key for achieving high performance on virtually any recent CPU or GPU: vector processing, or *single instruction*, *multiple data* (SIMD) computation.

#### 2.1 Vectorisation

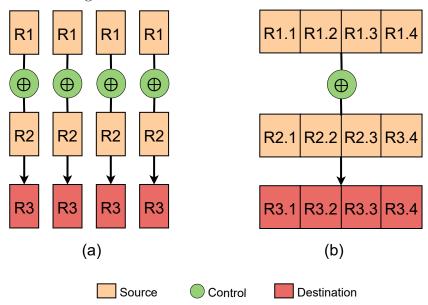

Almost all high-performance processors today include vector computing capabilities. Inside each core, dedicated functional units run a single instruction on a whole batch of operands simultaneously. This design allows a single source of control flow to be fed to several batches of data for each SIMD instruction, thus saving overhead by reducing the number of instructions that need to be decoded. On the other hand, the downside is lower flexibility: compared to a full (scalar) instruction set, generally only a subset of the instructions will be available in SIMD format. Figure 2.1 illustrates the operation of a generic SIMD instruction.

Figure 2.1: Scalar (a) and vector (b) instructions.

Some recent many-core architectures are designed from the ground up around SIMD computation: exploiting these capabilities is critical on GPUs [25] and the Intel Xeon Phi [101, 139], for example, even outside HPC workloads. Compared to general-purpose CPUs, individual cores in these devices are simpler and offer lower performance, but by employing a large number of them in efficient operations, the aggregate computational power of the device becomes substantial. However, with SIMD units having become commonly available in CPUs too, vector code is now important in all high-performance processors. Utilising the wide vector units in the latest generations of x86 processors, for example, is the only way to approach peak performance [46, 130].

In consumer-grade processors, SIMD instructions are often used for efficiency [98], for example in applications with structured computation pat-

terns, such as media processing and cryptographic ciphers. Here, SIMD provides a performance boost with a cost to the chip's surface area and power usage that is far smaller than adding whole additional general-purpose cores. These applications have supported the growth of SIMD extensions in common ISAs: x86-based designs started with the Streaming SIMD Extensions (SSE) in 1999 and later moved to the Advanced Vector Extensions (AVX), AVX, and AVX-512, and Arm designs offered the NEON multimedia extension in the ARMv7 architecture, which have become the Advanced SIMD (ASIMD) group of the latest ARMv8 ISA, recently joined by the Scalable Vector Extension (SVE). More recently, general-purpose SIMD capabilities have been used to implement high-precision floating point operations even when the underlying hardware only offers limited precision natively [73].

Scientific applications often exhibit well structured computation patterns [6, 81, and this makes them good candidates for vector processing. In many cases, they consist of a core piece of computation, sometimes referred to as the kernel, that is repeatedly applied to a large set of elements in a welldefined sequence. If the kernel can be applied multiple nearby elements simultaneously, then it is a good candidate to benefit from vectorised operations. This is easiest to achieve if the computation for each element does not depend on elements close to it and if elements are iterated through in a contiguous pattern. When successive elements located next to each-other in memory, accesses can be coalesced, such that a single memory request can return several contiguous element, but modern vector instruction sets offer alternative solutions when this is not possible. For example, gather operations enable data to be collected into a single vector register from arbitrary locations in memory, scatter operations provide the inverse functionality, and per-lane predication allows instructions to conditionally enable or disable individual operands, which can help work around data dependencies or uncommon access patterns.

#### 2.1.1 Generating and Running Vector Code

There are two common ways of producing vector machine code: manually, through in-line assembly code or compiler intrinsics that map almost-one-to-one onto machine instructions, or automatically, using a vectorising compiler. The former is more tedious and error-prone, because programming languages generally do not provide types that map onto hardware vectors, so it becomes the programmer's responsibility to pack and unpack vector registers. With all but simple applications, this is a very time-consuming task, and it has the major disadvantage that it makes the application code less portable, since intrinsics and assembly instructions are hardware-specific. The advantage of this approach, however, is that one can *ensure* vectors are being used optimally in the most performance-critical parts of the application, and if these parts are relatively small but very commonly used, it may be worth maintaining a version for each platform targetted [93]. This approach is commonly used in optimised maths libraries.

The option of relying on the compiler to auto-vectorise source code requires much less intervention from the programmer, with most modern compilers applying vector optimisation by default in many cases. The most common vector transformation is *loop vectorisation*, where consecutive loop iterations are packed together into vector operations, but some compilers also perform *superword-level parallelism (SLP) vectorisation*, in which groups of similar scalar operations are combined into vector operations. With a vectorising compiler, the same application source code can theoretically take advantage of vector features on any platforms for which a compiler exists. However, compilers are not perfect tools, and so they may not always succeed to automatically vectorise code wherever a skilled programmer could [8].

This latter point is very important for contemporary HPC research. Most applications rely on a compiler at some point in the build process, and the compiler's ability to generate code that is optimised for the target platform is directly linked with the application's run-time performance [150]. Vector optimisations are among the most difficult for compilers to apply, so one factor that often distinguishes compilers in HPC is their ability to under-

stand patterns in high-level source code and transform them into equivalent SIMD machine code. In addition to open-source compilers, of which the GNU Compiler Collection (GCC) and the LLVM Project are the best-known options, processor or system vendors sometime provide their own compiler, for free or under a licence, which in some cases can offer better performance. For example, Intel has held a long track record of providing a robust compiler with good vectorisation ability for its x86 processors, Arm offers the HPC Compiler with a particular focus on its SVE instruction set, and Cray ships the highly regarded Cray Compilation Environment (CCE) with its supercomputer systems. This wide range of choices has led to the standard practice in the field of HPC of benchmarking the different compiler options when running performance experiments, because even a simple code change may lead to vastly different performance effects with some compilers but not others.

Unfortunately, most optimising compilers are black boxes from the user's perspective. They are complex system that try to predict the performance of several possible transformations under a model of the target platform, in an attempt to choose the optimal one, but any oversight in either the transformation logic or the model itself can have far-reaching consequences for the generated code. Additionally, compilers will try to obtain the maximum level of performance, but they cannot sacrifice code correctness in this process, so before even attempting many optimisations, they will try to prove that other parts of the code will not be impacted by the changes. Such proofs are hard for human and machine alike, and when the result is uncertain, compilers must choose the cautious approach of disabling any optimisation that have the potential to lead to incorrect code. In practice, this often leads to programmers fighting against the optimising compiler, trying hard to demonstrate that optimisations are safe to apply, sometimes through techniques that reduce code clarity or inadvertently reference a specific machine's hardware parameters.

An exception to the two methods above, and in some ways a middleground between them, is higher-level programming with explicit vectorisation, as utilised in CUDA and OpenCL. In these languages, kernels are programmed from the point of view of the smallest work item, which is a vector lane in a SIMD processor. Loops over data structures are replaced with kernel invocations over a large thread space, and the programming model restricts the interactions possible within and between kernel instances. This frees the compiler from checking dependencies and promoting scalar code to vector code, with that task instead becoming the responsibility of the programmer. For GPUs, this model has been successful in obtaining high performance, at the cost of porting time when applications need to be converted between CUDA or OpenCL and traditional high-level languages. On CPUs, it is more common to use to libraries or domain-specific programming frameworks that help expose parallelism in the code, such as those built into or on top of modern C++, while leaving explicit vector code generation to the compiler.

#### 2.1.2 An Overview of Modern Vector Instruction Sets

**x86.** The x86 architecture first gained SIMD support with MMX, an early, 64-bit, integer-only vector instruction set. It was originally introduced for multimedia applications, but because of its overlap with GPU functionality and lack of floating-point support, it was not heavily utilised. In the following years, Intel introduced SSE, and its revisions SSE2, SSE3, and SSE4, which significantly expanded the range of operations supported, including covering floating-point arithmetic, and increased the vector width to 128 bits. More than ten years after SSE appeared, the AVX instruction set superseded it, adding further instructions and introducing 256-bit operations.

AVX came at a time critical for the importance of vector instructions in HPC. General-purpose compute on GPUs had started to grain traction, and compilers and programming models had matured enough to allow for good SIMD support, both through automatic vectorisation and explicit usage. But whereas GPUs ran *all* instructions as vectors, vector extensions on CPUs only covered a small subset of the instructions available. As a result, many computational patterns could only be partially vectorised or required additional code to set up the data in a form suitable for vector instructions.

Today, x86-based processors use AVX2 and AVX-512, expansions on AVX which are much more flexible than their early counterparts. When code is not vectorised, the cause is usually not the lack of suitable vector instructions, but rather the compiler's inability to understand the code's structure and transform it into vector form [109]. AVX-512 itself is divided into several sets of instructions, and each implementation can choose which part to support. Most operations are 512-bit-wide predicated instructions, but one of the sets, AVX-512VL, offers the same core instructions in 256-bit form too. It is easy to combine instructions from all versions of SSE and AVX up to the most recent supported one in an implementation, because vector registers are aliased: a CPU implementing AVX-512 will offer 512-bit registers, called zmm, and the ymm and xmm registers from earlier versions of the ISA simply reference the lowest 256 and 128 bits in the same registers, respectively. Figure 2.2 shows how the register aliases overlap.

| 511 256 | 255 128 | 127 0 | Bit number    |

|---------|---------|-------|---------------|

| zmm     | ymm     | xmm   | Register name |

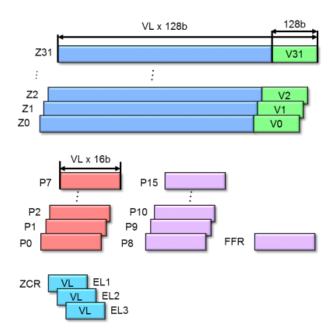

Figure 2.2: x86 vector register aliases: xmm and ymm refer to the lower 128 and 256 bits, respectively, of the 512-bit zmm registers.

The current generation of Intel processors, Cascade Lake, supports AVX-512, including AVX-512VL. The latest x86-based design from AMD, EPYC Rome, supports AVX2.

Arm. Arm processors have traditionally been applied more often in power-limited environments, such as embedded or mobile devices, rather than in high-performance computers. As such, vector extensions were introduced to improve efficiency and focused on media and signal processing, starting with the NEON extension in ARMv7. In ARMv8, NEON was renamed to ASIMD and integrated into the core AArch64 architecture, so it is available on all 64-bit Arm processors. Its origins, however, make it largely unsuitable for modern HPC applications, because it offers very few operations and a vector length of only 128 bits [104].

Figure 2.3: SVE vector registers. NEON (V) registers are aliased to the lower 128 bits of the full SVE (Z) registers. Additional predicate (P) and control (ZCR) registers also depend on the vector length (VL). Source: Arm [127].

The introduction of SVE changes this. SVE is a modern and flexible instruction set, with features relevant for HPC that are on par with AVX-512, such as predication, gather and scatter operations, varied data-type support, and instructions that implement operations across lanes [5]. Unlike the AVX variants, which have a pre-determined vector length, SVE allows each microarchitecture to choose its desired length, in multiples of 128 bits, between 128 and 2048 bits total. SVE code is then *vector-length-agnostic* (VLA) and special instructions are provided to obtain the implementation's chosen (hardware) width at run-time. This concept is illustrated in Figure 2.3, where register sizes depend on the VL parameter.

As is the case on x86, compiler support for automatic vectorisation is now the limiting factor in vectorising HPC applications on platforms that implement Arm SVE, rather than instruction availability. The Fujitsu A64FX, released in 2020, is the first processor to implement SVE.

# 2.2 Modern High-Performance CPU Architectures

Contemporary high-performance processors, while similar from many perspectives, have defining features that make each stand out in certain environments. In this section I introduce the main processor architectures used throughout the experiments in this thesis.

**Broadwell.** Intel's 5th generation Core architecture was widely used in HPC. Among its top features are 256-bit AVX2 vector instructions, 4 channels of DDR4 memory and up to 24 cores per socket. It features three levels of cache, of which only the last one is shared, with about 2.5 MB of cache for each core in the processor, in an inclusive configuration.

Skylake. Broadwell's successor brought 512-bit AVX-512 vectors to generalpurpose CPUs. Memory bandwidth was increased by supporting up to 6 DDR4 channels, and the top SKU offered 28 cores in a single socket. Since it offers more aggregate bandwidth than Broadwell, more cores can run at their full bandwidth; however, since there are also more cores overall, the available bandwidth per core is less than in Broadwell when all cores are used. The last-level cache configuration was changed to an exclusive victim cache, so it is only filled with data that is evicted from the second level, but the amount of last-level cache per core was decreased to 1.375 MB. When running AVX-512 instructions, Skylake decreases its clock frequency, which in practice means that applications need a high ratio of vectorisation to benefit from the 512-bit instructions. These different performance characteristics compared to the previous generation, and its increased price, resulted in slow adoption for Skylake, many centres still using Broadwell several years after the launch of the new architecture. Skylake was succeeded by Cascade Lake, an incremental improvement that did not bring significant new features.

**Rome.** AMD's first-generation EPYC processors, codenamed Naples, were used in datacenters, but less so in HPC; it was the second generation, Rome,

# 2.3. PROGRAMMING MODELS AND PERFORMANCE PORTABILITY

that gained traction. Rome uses the x86 instruction set and supports up to 64 cores per socket connected to 8 channels of DDR4. It brings a novel approach to microarchitectural design in which the chip is built from several *chiplets*, individual compute modules of 8 cores. This design is highly scalable, but because each chiplet is a separate NUMA node, it is also potentially more susceptible to latency issues. Rome supports x86 vector instructions up to 256-bit AVX2.

ThunderX2. Cavium—later acquired by Marvell—released a first generation of Arm-based processors for the datacenter with the ThunderX series. In HPC, these were used for some experiments, but it was only its successor, the ThunderX2, that gained popularity. Built on a design that originated at Broadcomm, the ThunderX2 includes up to 32 ARMv8 cores connected to 8 memory channels. Its memory bandwidth was superior to x86-based alternatives at the time, but its cache was relatively low at 1 MB per core, and it only offered 128-bit vectors.

# 2.3 Programming Models and Performance Portability

In HPC, programming languages and frameworks are slow-moving. Many applications that are still commonly used today were first released in the 1990s—some even earlier—and so they use some of the same programming languages, concepts, and techniques that were available then. Furthermore, because performance has always been critical in HPC by definition, the common programming languages used are those that incur the least amount of overhead. This has led to the C and Fortran languages being the most prevalent in the industry.

In the wider context, however, programming languages have evolved very rapidly over the past few decades. Advances in hardware and compilers mean that many things are possible now that were not before, but re-writing old applications in a new language is a daunting task. Not only do they involve codebases that have evolved over many years, but the existing versions have proved over the years that they are reliable and produce correct results; a modern port would need a long time to go through the same verification and validation processes, so that it provides the same level of confidence. Thus, HPC users have not benefited significantly from recent advances in programming [94, 126].

One slight exception to this observation is the C++ language. Some applications adopted C++ early, starting with its initial versions, hoping to utilise the higher level of abstraction to ease the burden on the programmer. But C++, unlike C and Fortran, has evolved very rapidly; C++11 is almost a completely different language from the C++ of the 1990s, and more recent versions such as C++17 and C++20 further bridge the gap in usability between C++ and much higher-level languages which rely on heavyweight runtimes and features like garbage collection in an attempt to provide an efficient programming experience. For applications already using C++, an improvement over time came naturally, at a much lower cost than switching languages altogether.

For the applications that were unable to replace the programming language used, there is still a desire to modernise code. In general, the longer a codebase is used, the larger and harder to maintain it becomes, so programmer productivity is reduced. As compilers have evolved, productivity can further be improved by offloading common tasks from the programmer to the machine. One way to achieve this is through new programming frameworks built on the same traditional languages.

HPC applications span many scientific domains, but one characteristic they share is the need to exploit parallelism to achieve high performance. Because this is a very common requirement, it is widespread practice to use libraries to parallelise code instead of implementing everything from scratch every time. Two of the most widely used parallelisation frameworks are the Message Passing Interface (MPI) and OpenMP [67]. Both of these natively support C and Fortran, and while there is some support for C++, often it only covers the language itself and not its standard library of data structures and algorithms. If a framework were to improve upon MPI or OpenMP,

# 2.3. PROGRAMMING MODELS AND PERFORMANCE PORTABILITY

delivering similar performance while improving programmer productivity, its impact would be significant.

To some extent, there have existed frameworks that delivered some of these goals. NVIDIA CUDA, followed later by OpenACC, provides a low-overhead toolchain that is efficient at extracting high performance from NVIDIA GPU hardware, for which it is heavily optimised. However, this comes at the cost of vendor lock-in: the future of these tools is entirely in the hands of the company behind them, unlike open standards for programming languages and open-source frameworks. This issue has deterred many developers from investing heavily into a vendor-controlled ecosystem, because their efforts may be wasted if future generations of supercomputers use different hardware, on which these frameworks cannot be used.

In addition to simplifying development of parallel code, there is another area with opportunities for novel programming frameworks to enhance productivity in HPC code: portability. In the second half of the previous decade, the HPC community has placed increasing importance on the performance portability of HPC code, with the goal to understand how to write applications in such a way that they achieve a large fraction of peak performance on many different platforms [29]. This endeavour originally appeared as code targeting GPUs — often written using frameworks such as CUDA, which cannot easily be run on CPUs—diverged more-and-more from CPU code, and has grown increasingly important in the context of the upcoming exascale systems, Frontier, El Capitan, Aurora, and Perlmutter, which together combine CPUs from two vendors and GPUs from three vendors, with no established programming framework able to target all these combinations. If code is not performance-portable, it needs to be refactored in large proportions, and sometimes completely rewritten using new libraries, when moving to a system that uses different hardware.

Recently, two frameworks have emerged that aim to improve the portability of HPC code, while maintaining performance and helping programmer productivity: Kokkos [32] and SYCL [45]. These are both frameworks that expand on top of modern C++ and can target both CPUs and GPUs without any change to the source code. They are of particular interest to the HPC

community because they may offer a solution to the fragmentation between hardware targets and programming languages they support. Their adoption is still early, but if it proves successful, another side effect will be increased migration to the C++ language, which some argue is a better choice for the longer term compared to older languages such as C and Fortran.

SYCL is an abstraction layer built on top of C++ that combines the functionality of OpenCL with a single-source approach. An OpenCL program contains two parts: a host program, usually written in C or C++, that initialises the OpenCL stack and compiles one or more kernels, then schedules them to be run on the target device, which may be an accelerator connected to the host, like a GPU or FPGA, or the same CPU as the host itself. In contrast, SYCL code is embedded in the C++ host code, eliminating the need for a kernel compiler that is invoked when the host program runs. This does mean that support for the target device must be present when compiling the SYCL application—as opposed to OpenCL, which only calls the kernel compiler and libraries when the host program is run, targeting the hardware present at that moment—but this is almost always the case in HPC systems. There are currently three major SYCL compilers: Intel DPC++, based on the new-generation Intel ICX compiler (itself based on LLVM), which supports several platforms through the OpenCL, CUDA, and Intel Level Zero backends; ComputeCPP, a compiler developed by Codeplay; and hipSYCL, an open-source implementation that supports CUDA, ROCm, and OpenMP for CPUs and GPUs as backends [3].

Kokkos is packaged as a C++ library. It is distributed as source code, integrated into the application's build process, and built at the same time and using the same compiler. This route has the advantage of not forcing the user to choose a particular compiler—any modern C++ compiler can compile Kokkos. The downside is that Kokkos itself must be updated to support new architectures, so it possible to reach situations in which the underlying compiler is aware of a target architecture, but Kokkos is not, and so the generated parallel code may not be fully optimised.

# 2.4 Common Classes of HPC Applications

Scientific computing applications are diverse and span a large number of domain sciences, but their computational patterns often fall into one of a few categories. It is common to speak of the "dwarfs" of HPC, each representing a class of common application types [6]. Each class has distinctive computation patterns, and similar algorithmic and optimisation strategies work well across applications within the same class.

From a performance point of view, applications are most often classified by the one factor that prevents the code from running faster. This is sometimes referred to as the *bottleneck* of the application and it represents the one resource which, if increased, would immediately improve the performance of the application. Most HPC applications are bound by one of the following factors:

- Raw arithmetic performance. These applications are called *compute-bound*. To improve their performance, the system needs to be able to perform more calculations—usually floating-point operations (FLOPs)—which implies either faster cores, e.g. through higher clock speeds or wider vectors, or a higher core count.

- Memory bandwidth. This is generally the largest class, because over the years compute performance has improved faster than memory performance in hardware. Depending on the size of the working set and the layout of the system's memory hierarchy, the bottleneck can be either one of the levels of cache (cache-bandwidth-bound) or, more commonly, the main memory (DRAM-bandwidth-bound or simply memory-bandwidth-bound).

- Latency. This bottleneck is most common for applications that perform small operations on many different objects, as opposed to batched computation on large, contiguous data. Examples of this class are graph applications, which are often bound by the latency of local memory as processing moves between vertices [71, 35, 40], and distributed FFT applications, which can be bound by the latency of the network in

all-to-all operations [17]. Latency bottlenecks can also appear in deep NUMA hierarchies, e.g. between NUMA nodes or between different levels of cache. This class is particularly hard to characterise and optimise.

In order to analyse the performance of systems and applications, and quantify the effect of optimisations, it is common to utilise *benchmarking*. The most commonly used HPC benchmarks have been developed to represent individual dwarfs, and because performance characteristics are often shared within classes of problems, they offer good indication of real-world application performance.

## 2.5 Benchmarking

Benchmarking is the process of a measuring a system's performance using well-defined metrics and test cases. In HPC, benchmarking is commonly used in three different situations:

- In evaluating a system's performance. Systems are often compared against one-another, for example to identify weaknesses or strengths of a different architecture, or to quantify performance improvements versus an older generation of the same system. When comparing between different systems, the benchmarks themselves are usually fixed. A range of benchmarks is chosen from different problem classes to cover as many aspects of the systems as possible—this ensures the benchmarks represent realistic use of the system.

- When selecting optimal configurations, parameters, and software components to solve a problem. For example, different algorithms or implementations could be chosen when using optimised math libraries, and different choices may be fastest on different systems.

- To quantify the performance improvements within an application following an optimisation attempt. In this case, the new version of the application is measured against a snapshot before the changes, recording the performance changes. Because there is a wide variety of HPC

systems available, it is highly valuable to benchmark optimisations on many different platforms, since not all systems will react in a similar way to the same code change.