# On-chip electrochemical capacitors and piezoelectric energy harvesters for self-powering sensor nodes

Agin Vyas

Department of Microtechnology and Nanoscience CHALMERS UNIVERSITY OF TECHNOLOGY Göteborg, Sweden 2022 On-chip electrochemical capacitors and piezoelectric energy harvesters for self-powering sensor nodes

AGIN VYAS

ISBN 978-91-7905-646-9

© AGIN VYAS, 2022.

Doktorsavhandlingar vid Chalmers tekniska högskola Ny serie nr 5112 ISSN 0346-718X

Department of Microtechnology and Nanoscience Chalmers University of Technology SE–412 96 Göteborg, Sweden Telephone + 46 (0) 31 – 772 1000

Cover: On-chip electrochemical capacitors and piezoelectric energy harvesters as self-powering sensor nodes for applications of the world.

Typeset by the author using LaTeX.

Printed by Chalmers Reproservice Göteborg, Sweden 2022

#### **Abstract**

On-chip sensing and communications in the Internet of things platform have benefited from the miniaturization of faster and low power complementary-metal-oxide semiconductor (CMOS) microelectronics. Micro-electromechanical systems technology (MEMS) and development of novel nanomaterials have further improved the performance of sensors and transducers while also demonstrating reduction in size and power consumption. Integration of such technologies can enable miniaturized nodes to be deployed to construct wireless sensor networks for autonomous data acquisition. Their longevity, however, is determined by the lifetime of the power supply. Traditional batteries cannot fully fulfill the demands of sensor nodes that require long operational duration. Thus, we require solutions that produce their own electricity from the surroundings and store them for future utility. Furthermore, manufacturing of such a power supply must be compatible with CMOS and MEMS technology. In this thesis, we will describe on-chip electrochemical capacitors and piezoelectric energy harvesters as components of such a self-powered sensor node. Our piezoelectric microcantilevers confirm the feasibility of fabricating micro electro-mechanical-systems (MEMS) size two-degree-of-freedom systems which can address the major issue of small bandwidth of piezoelectric micro-energy harvesters. These devices use a cut-out trapezoidal cantilever beam, limited by its footprint area i.e. a 1 cm<sup>2</sup> silicon die, to enhance the stress on the cantilever's free end while reducing the gap remarkably between its first two eigenfrequencies in the 400 - 500 Hz and in the 1 - 2 kHz range. The energy from the M-shaped harvesters could be stored in rGO based on-chip electrochemical capacitors. The electrochemical capacitors are manufactured through CMOS compatible, reproducible, and reliable micromachining processes such as chemical vapor deposition of carbon nanofibers (CNF) and spin coating of graphene oxide based (GO) solutions. The impact of electrode geometry and electrode thickness is studied for CNF based electrodes. Furthermore, we have also demonstrated an improvement in their electrochemical performance and yield of spin coated electrochemical capacitors through surface roughening from iron and chromium nanoparticles. The CVD grown CNF and spin coated rGO based devices are evaluated for their respective trade-offs. Finally, to improve the energy density and demonstrate the versatility of the spin coating process, we manufactured electrochemical capacitors from various GO based composites with functional groups heptadecan-9-amine and octadecanamine. The materials were used as a stack to demonstrate high energy density for spin coated electrochemical capacitors. We have also examined the possibility of integrating these devices into a power management unit to fully realize a self-powering on-chip power supply through survey of package fabrication, choice of electrolyte, and device assembly.

**Keywords:** Energy harvesting, Energy storage, MEMS, piezoelectric energy harvesters, 2DOF, Microsupercapacitors, graphene oxide, spin coating, sensor node

## Acknowledgments

On reminiscing my PhD journey, this thesis is only possible through ideas and encouragements of several outstanding individuals. First, I would like to acknowledge my deep gratitude towards Prof. Per Lundgren. He has helped me walk through the constant ups and downs of my PhD life. He has been a guiding light that has led me in the right direction. Also, I would like to thank him for deep discussions on scientific aspects of the projects, meetings, conferences, and exchanges of well being. I would like to thank and acknowledge Prof. Peter Enoksson for all the scientific discussions, ideas, projects, and lively car rides. He always has the right solution for the worst of issues. Thank you for putting your faith in me for all these years.

I would also thank Associate Prof. Anderson Smith for his advice and supervision in conducting research, development, and reporting. Thank you to Dr. Karin Hedsten for special training in the cleanroom. I would also like to thank Associate Prof. Peter Folkow, Associate Prof. Cristina Rusu, Dr. Henrik Staaf, Dr. Volodymyr Kuzmenko, Dr. Sofia Rahiminejad, and Dr. Amir Ghaderi for the training during my PhD. I would also like to extend a note of gratitude towards Dr. Daryoush Shiri, Lisa Nyström, Ola Stenlåås, David Bilby, Jaco Visser, and Prof. Reinoud Wolfenbuttel, and Prof. Johan Liu for giving me the chance to work in the exciting optical particle detection project.

This thesis would also not have been possible without the wonder materials from Dr. Ulises Mendez, Dr. Ergang Wang, Dr. Shameel Thurakkal, Dr. Xiaoyan Zhang, and Dr. Jinhua Sun. Furthermore, working with talented and gifted Fabio Cornaglia, Kejian Wang, Ruben Van den Eeckhoudt, Andres Velasco, and Simin Zare Hajibagher brought great joy to my life. I would also like to thank Johan Andersson, Viktor Sjöstrom, Gustav Forsberg, Bogdan Pamfil, and Richard Palm for the lively discussions and ideas to move the energy harvesting technology forward.

I would also like to thank my friends and colleagues Sadia Farjana, Mazharul Haque, Qi Li, Azega Rajaras, Bogdan Karpaik, Vivekanand Shukla, Adriana Canales, Ankit Bisht, Ankur Srivastav, and Apoorv Garg.

In the end, I would like to thank my family and my incredible wife, Smriti. She has supported me undeterred during my phases of despondency and hope alike.

Agin Vyas Göteborg, March 2022

## **List of Publications**

This thesis is based on the following appended papers:

- **Paper 1. Agin Vyas**, H. Staaf, C. Rusu, T. Ebefors, J. Liljeholm, A. D. Smith, P. Lundgren and P. Enoksson. *A Micromachined Coupled Cantilever for Piezoelectric Energy Harvesters*. Micromachines (ISSN 2072-6669), no. 5 (2018): 252.

- Paper 2. Agin Vyas, K. Wang, A. Anderson, A. Velasco, R. van den Eeckhoudt, M. Haque, Q. Li, A. Smith, P. Lundgren, and Peter Enoksson. Enhanced electrode deposition for on-chip integrated micro-supercapacitors by controlled surface roughening. ACS Omega 2020, 5 (10), 5219-5228

- **Paper 3. Agin Vyas**, K. Wang, Q. Li, A. M. Saleem, M. Bylund, R. Andersson, V. Desmaris, A. Smith, P. Lundgren and P. Enoksson. Impact of electrode geometry and thickness on planar on-chip microsupercapacitors. In *RSC Adv.*, 2020, 10, 31435

- **Paper 4. Agin Vyas**, S. Z. Hajibagher, Q. Li, M. Haque, A. Smith, P. Lundgren, and P. Enoksson. Comparison of Thermally Grown Carbon Nanofiber-Based and Reduced Graphene Oxide-Based CMOS-Compatible Microsupercapacitors. In *Phys. Status Solidi B2021,258, 2000358*

- **Paper 5. Agin Vyas**, S. Z. Hajibagher, U. A. Méndez-Romero, S. Thurakkal, Q. Li, M. Haque, R. K. Azega, E. Wang, X. Zhang, P. Lundgren, P. Enoksson, and A. Smith. Spin-coated Heterogenous Stacked Electrodes for Performance Enhancement in CMOS compatible On-chip Micro-supercapacitors. In *ACS Appl. Energy Mater.* 2022

Other relevant contributions co-authored by Agin Vyas:

- B. Pamfil, R. Palm, **Agin Vyas**, H. Staaf, C. Rusu, and P. D. Folkow. *Multi-Objective Design Optimization of Fractal-based Piezoelectric Energy Harvester*. In 2021 IEEE 20th International Conference on Micro and Nanotechnology for Power Generation and Energy Conversion Applications (PowerMEMS), pp. 96-99. IEEE, 2021.

- **Agin Vyas**, S. Z. Hajibagher, U. M. Romero, R. K. Azega, E. Wang, P. Lundgren, P. Enoksson, and A. D. Smith. *Alkyl-Amino Functionalized Reduced-Graphene-Oxide-heptadecan-9-amine-Based Spin-Coated Microsupercapacitors for On-Chip Low Power Electronics*. Physica status solidi (b) (2021): 2100304.

- A. Velasco, **Agin Vyas**, K. Wang, Q. Li, A. D. Smith, P. Lundgren, and P. Enoksson. *Investigation of vertical carbon nanosheet growth and its potential for microsuper-capacitors*. In Journal of Physics: Conference Series, vol. 1837, no. 1, p. 012006. IOP Publishing, 2021.

- Q. Li, A. D. Smith, **Agin Vyas**, F. Cornaglia, A. Anderson, M. Haque, P. Lundgren, and P. Enoksson. *Finger Number and Device Performance: A Case Study of Reduced Graphene Oxide Microsupercapacitors*. Physica status solidi (b) 258, no. 2 (2021): 2000354.

- **Agin Vyas**, Q. Li, R. van den Eeckhoudt, G. Geréb, A. Smith, C. Rusu, P. Lundgren, and P. Enoksson. *Towards Integrated Flexible Energy Harvester and Supercapacitor for Self-powered Wearable Sensors*. In 2019 19th International Conference on Micro and Nanotechnology for Power Generation and Energy Conversion Applications (PowerMEMS), pp. 1-6. IEEE, 2019.

- A. D. Smith, Q. Li, **Agin Vyas**, M. Haque, K. Wang, A. Velasco, X. Zhang, S. Thurakkal, A. Quellmalz, F. Niklaus, K. Gylfason, P. Lundgren, P. Enoksson. *Carbon-Based Electrode Materials for Microsupercapacitors in Self-Powering Sensor Networks: Present and Future Development*, Sensors 19.19 (2019): 4231.

- A. D. Smith, Q. Li, A Anderson, **Agin Vyas**, V Kuzmenko, M Haque, L. G. H. Staaf, P. Lundgren, P. Enoksson, *Toward CMOS compatible wafer-scale fabrication of carbon based microsupercapacitors for IoT*, IOP Conference Series: Journal of Physics: Conference Series 1052 (2018) 012143.

- **Agin Vyas**, F. Cornaglia, T. Rattanasawatesun, Q. Li, M. Haque, J. Sun, V. Kuzmenko, A. D. Smith, P. Lundgren, P. Enoksson. *Investigation of Palladium Current Collectors for Vertical Graphene-based Microsupercapacitors*, Journal of Physics: Conference Series. Vol. 1319. No. 1. IOP Publishing, 2019.

- Q. Li, A. D. Smith, M. Haque, Agin Vyas, V. Kuzmenko, P. Lundgren, P. Enoksson. Graphite paper/carbon nanotube composite: A potential supercapacitor electrode for powering microsystem technology, Journal of Physics: Conference Series, 922 (2017) 012014

## **List of Acronyms**

CMOS - Complementary metal-oxide-semiconductor

IoT – Internet of things

AIoT – Artificial Internet of things

MEMS – Micro-electromechanical systems

SoC – System on chip

FPGA – Field Programmable Gate Arrays ADC – Analog-to-digital converter

EDL – Electric double layer RF – Radio frequency PV – Photovoltaic

RFID - Radio frequency identification

DC – Direct current

PEH – Piezoelectric energy harvester

MPEH – Micro piezoelectric energy harvester

PZT – Lead zirconate titanate

MB – Micro-battery

MSC – Micro-supercapacitor

EDLC – Electric double layer capacitor

FEOL – Front-end-of-line BEOL – Back-end-of-line IC – Integrated circuit

VLSI – Very large scale integration

MOSFET - Metal oxide semiconductor field effect transistor

UV – Ultraviolet

2DOF – Two degrees of freedom

1DOF – One degree of freedom

nDOF – Multiple degrees of freedom

CNC - Computerized Numerical Control

FOM – Figure-of-merit

PDMS – Poly(dimethylsiloxane) PVDF – Polyvinylidene fluoride MKS – Mass spring damper

FUC – Frequency up-conversion DRIE – Deep reactive ion etching

SOI – Silicon on insulator

SiP – System-in-package PCB – Printed circuit board

EMIMAc – 1-Ethyl-3-methylimidazolium acetate

CV – Cyclic voltammetry

GCD – Galvanostatic charge-discharge EIS – Equivalent impedance spectroscopy

CVD - Chemical vapor deposition

MPCVD – Microwave Plasma-enhanced Chemical Vapor Deposition

SiNW – Silicon nanowire CNT – Carbon nanotubes

VACNT – Vertically aligned carbon nanotubes

rGO – Reduced graphene oxide

GO – Graphene oxide

PET – Polyethylene terephthalate

PANI – Polyaniline

CAD – Computer aided design

PEDOT:PSS – poly(3,4-ethylenedioxythiophene) polystyrene sulfonate

CNF – Carbon nanofibers

EPD – Electrophoretic deposition

ZIF – Zeolitic imidazolate framework

MOF – Metal organic frameworks

DVD – Digital Video Disc

LSG – Laser scribed graphene

CMEMS – Carbon micro-electromechanical systems

PPy – Polypyrrole

EMIM-TFSI – 1-Ethyl-3-methylimidazolium bis(trifluoromethylsulfonyl)imide

PVD – Physical vapor deposition

PVA – Poly(vinyl alcohol)

HMDS – Hexamethyldisiloxane

HD9A – Heptadecan-9-amine

ODA – Octadecanamine

TMP – Trimethylolpropane

PEGMA – Polyethylene glycol monomethacrylate

BEMA – Behenyl Methacrylate TMOS – Tetramethyl orthosilicate

## **Contents**

| Ał | ostra | et                                                           | V   |

|----|-------|--------------------------------------------------------------|-----|

| Ac | knov  | wledgments                                                   | vii |

| Li | st of | Publications                                                 | ix  |

| Li | st of | Acronyms                                                     | хi  |

| 1  | A se  | lf-reliant on-chip power supply                              | 1   |

|    | 1.1   | Introduction                                                 | 1   |

|    | 1.2   | Wireless sensor nodes                                        | 2   |

|    |       | 1.2.1 Power requirements for on-chip sensors and transducers | 4   |

|    | 1.3   | Energy harvesting                                            | 5   |

|    |       | 1.3.1 Solar energy harvesting                                | 5   |

|    |       | 1.3.2 Thermoelectric energy harvesting                       | 6   |

|    |       | 1.3.3 RF energy harvesting                                   | 7   |

|    |       | 1.3.4 Triboelectric energy harvesting                        | 8   |

|    |       | 1.3.5 Piezoelectric energy harvesting                        | 8   |

|    | 1.4   | Energy storage                                               | 10  |

|    |       | 1.4.1 Microbatteries                                         | 11  |

|    |       | 1.4.2 Microsupercapacitors                                   | 12  |

|    | 1.5   | Challenges                                                   | 14  |

|    |       | 1.5.1 Manufacturing for microelectronic compatibility        | 15  |

|    | 1.6   | Scope of the thesis                                          | 16  |

| 2  | Piez  | zoelectric vibrational energy harvesters                     | 19  |

|    | 2.1   | Introduction                                                 | 19  |

|    |       | 2.1.1 Challenges in power density                            | 21  |

|    |       | 2.1.2 Bandwidth improvement designs                          | 23  |

|    | 2.2   | Two-degrees of freedom (2DOF) design                         | 28  |

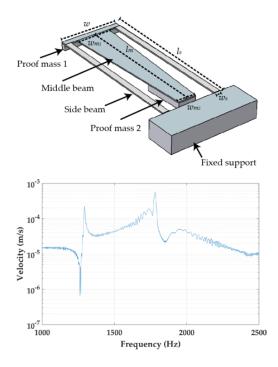

|    |       | 2.2.1 Operational bandwidth                                  |     |

|    |       | 2.2.2 Fabrication                                            | 30  |

|    |       | 2.2.3 Results                                                | 32  |

|    | 2.3   | Issues in fabrication                                        | 33  |

|    | 2.4   | Improving power density                                      | 36  |

|    |       | 2.4.1 Second generation harvesters                           |     |

CONTENTS CONTENTS

|          |          | 2.4.2 Third generation harvesters                                      |      |

|----------|----------|------------------------------------------------------------------------|------|

|          | 2.5      | Discussion and conclusion                                              | . 39 |

| 2        | N/1:-    |                                                                        | 40   |

| 3        |          | rosupercapacitors                                                      | 43   |

|          | 3.1      | Supercapacitor figures-of-merit                                        |      |

|          | 3.2      | Fabrication methodologies                                              |      |

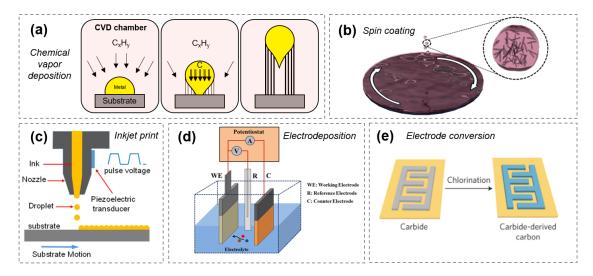

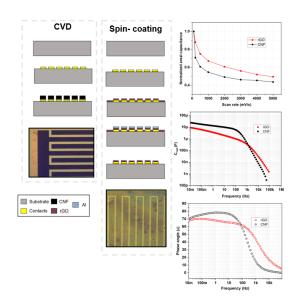

|          |          | 3.2.1 Chemical vapor deposition                                        |      |

|          |          | 3.2.2 Photolithography                                                 |      |

|          |          | 3.2.3 Inkjet printing                                                  |      |

|          |          | 3.2.4 Electrodeposition                                                |      |

|          |          | 3.2.5 Laser scribing                                                   |      |

|          |          | 3.2.6 Electrode conversion                                             | . 52 |

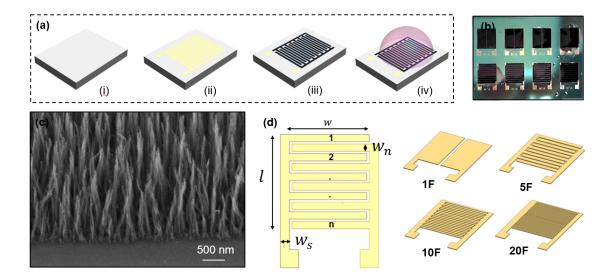

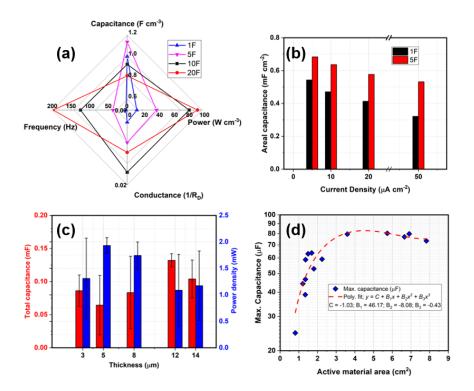

|          | 3.3      | Impact of electrode geometry                                           | . 53 |

|          | 3.4      | Spin coating technology for microsupercapacitors                       | . 57 |

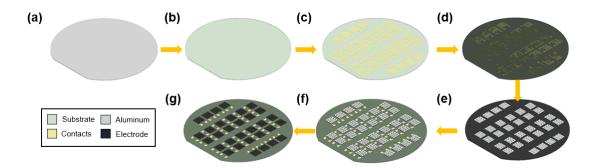

|          |          | 3.4.1 Fabrication                                                      | . 57 |

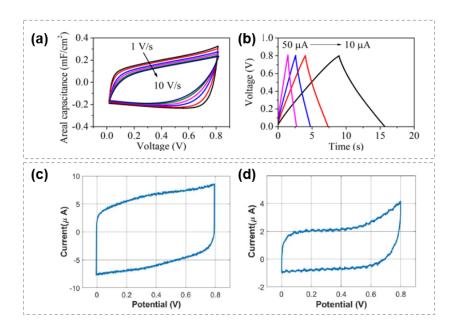

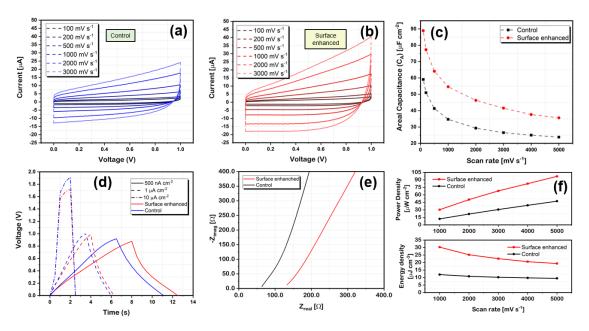

|          |          | 3.4.2 Results                                                          | . 59 |

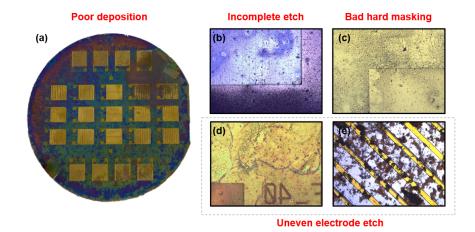

|          |          | 3.4.3 Issues in fabrication                                            | . 60 |

|          | 3.5      | Improving electrode deposition and device performance                  | . 62 |

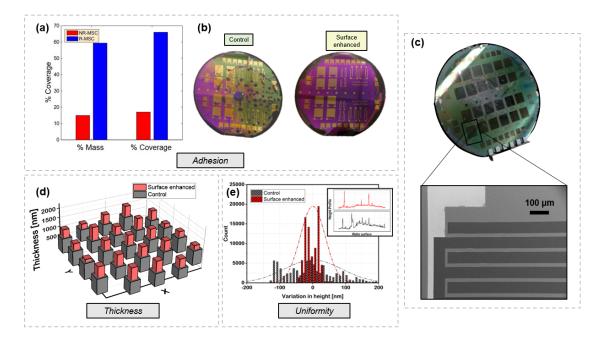

|          |          | 3.5.1 Enhanced spin coating                                            |      |

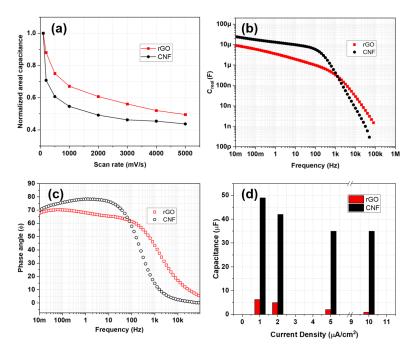

|          |          | 3.5.2 Comparison with CVD                                              |      |

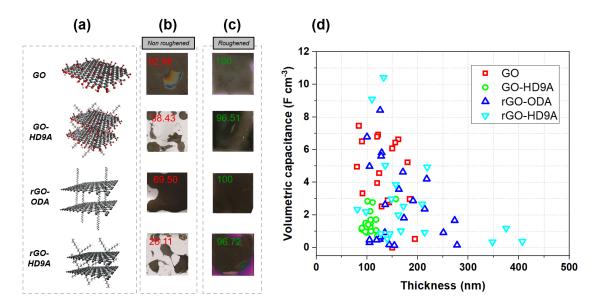

|          | 3.6      | Improving spin-coated electrode thickness                              |      |

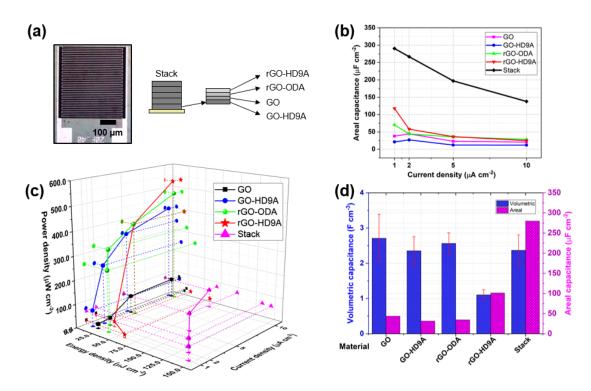

|          | 3.7      | Stacking materials                                                     |      |

|          | 3.8      | Discussion and conclusion                                              |      |

|          | 0.0      |                                                                        |      |

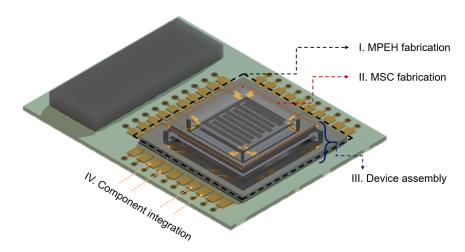

| 4        | On-      | chip integration                                                       | 73   |

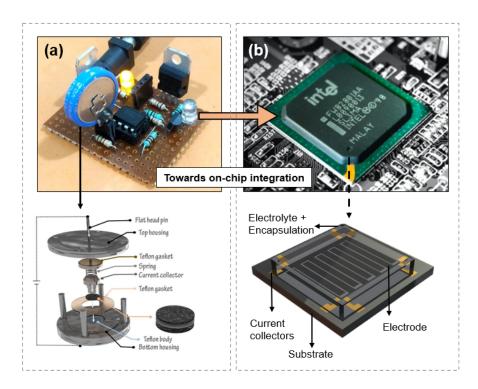

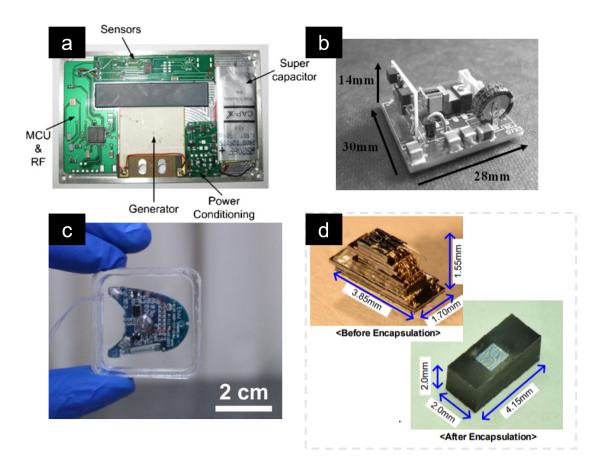

|          | 4.1      | Existing designs                                                       | . 73 |

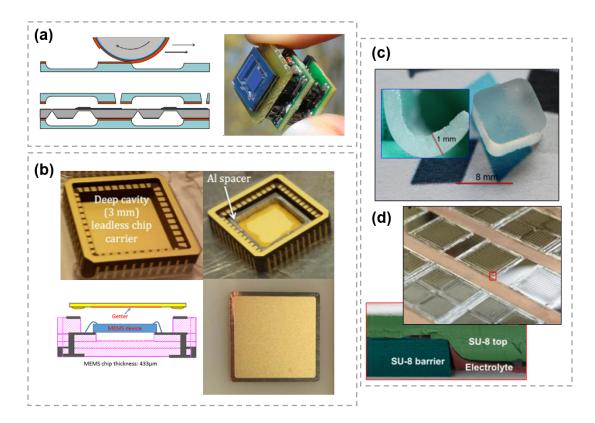

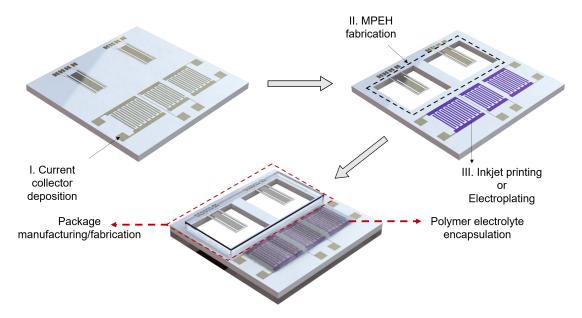

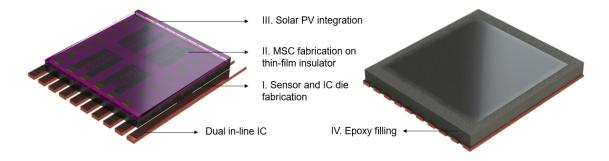

|          | 4.2      | Packaging and encapsulation of MPEH and MSC                            | . 75 |

|          | 4.3      | Potential integration strategies                                       | . 76 |

|          |          | 4.3.1 Component assembly                                               | . 77 |

|          |          | 4.3.2 FEOL integration                                                 | . 79 |

|          |          | 4.3.3 BEOL integration                                                 |      |

|          |          |                                                                        |      |

| 5        | Con      | clusion and summary of appended papers                                 | 83   |

| Ri       | hlioo    | graphy                                                                 | 91   |

| DΙ       | שטווט    | тарпу                                                                  | 31   |

| <b>T</b> | <b>A</b> |                                                                        | 117  |

| I        | Ap       | pended papers                                                          | 117  |

| 1        | A M      | icromachined Coupled Cantilever for Piezoelectric Energy Harvesters    | 119  |

| 2        | Enh      | nanced electrode deposition for on-chip integrated micro-supercapacito | ors  |

|          | by c     | controlled surface roughening                                          | 137  |

| 3        | Imp      | oact of electrode geometry and thickness on planar on-chip microsuper  | ca-  |

|          | _        | itors                                                                  | 151  |

CONTENTS CONTENTS

4 Comparison of Thermally Grown Carbon Nanofiber-Based and Reduced Graphene Oxide-Based CMOS-Compatible Microsupercapacitors 161

5 Spin-coated Heterogenous Stacked Electrodes for Performance Enhancement in CMOS compatible On-chip Microsupercapacitors 171

## Chapter 1

## A self-reliant on-chip power supply

#### 1.1 Introduction

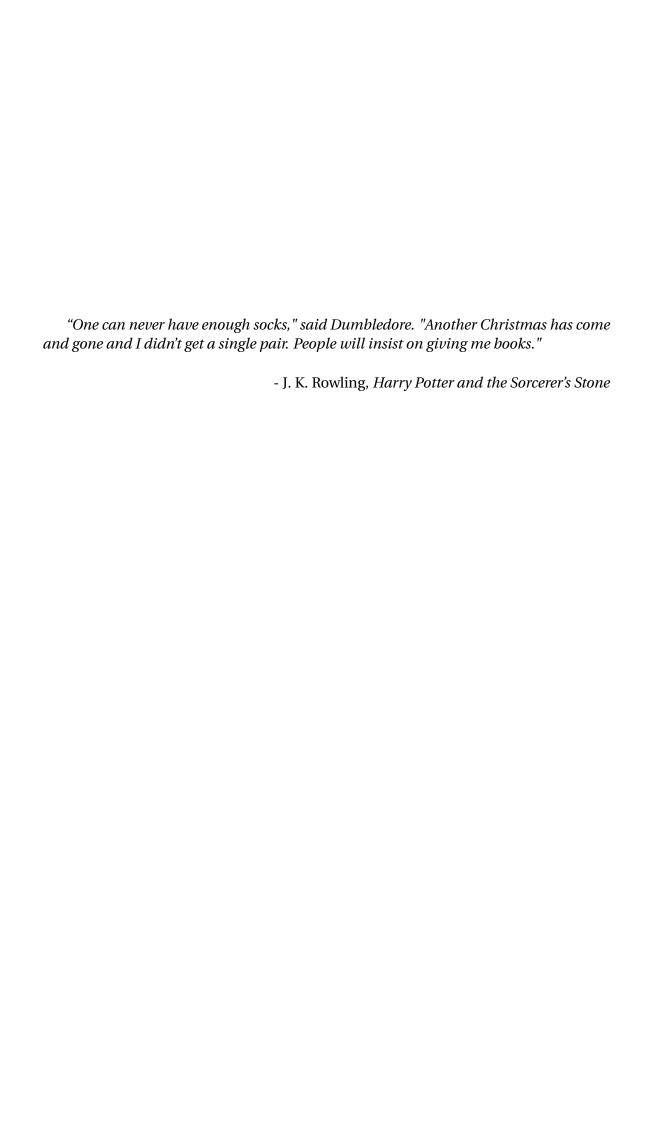

The advancements in microelectronics with the miniaturization of transistors through complementary metal-oxide-semiconductor (CMOS) technology have enabled the innovation of intelligent sensors and microprocessors as in mobiles, computers, cameras, and vehicles. These sensors can potentially communicate with each other forming a hive-like grid. Such a grid could constitute a part of the Internet of things (IoT) [1]. IoT can influence all sectors of life with application areas ranging from home, health, industry, transport, energy and construction (Figure 1.1). With the advent of fifth-generation wireless systems and artificial intelligence, IoT can make a combination of sensor networks into an artificial intelligence of things (AIoT) to collect, process, analyze, store, and control data [2].

Sensor networks are central to making decisions in complex systems that are designed to be intelligent [3]. These decisions are based on active measurement methods that are used in sensors. Such a procedure could be determining the change in electrical current based on the changes in physical conditions such as position, length, mass, resistance, and vibrations [4]. These physical conditions are manifestations of the environment surrounding the sensor. At home, our entertainment systems are using microsystems for communicating with our phones or controls that are powered (directly or indirectly) by our household electricity supplies [5].

Similarly, alarm systems and cameras are connected to phones and tablets of homeowners [6]. In healthcare, these networks can improve assisting patients in critical conditions in a more efficient manner [7]. Biological functions of the body can be measured during invasive surgeries in medicine [8]. Industries have already started adopting the IoT technology within the frames of another acronym called 'Industry 4.0'. Several reports address the importance of non-stop communication between automation, processes, and distribution while avoiding subjecting humans to the risks that such environments pose [9]. The sustainability of factories can be enhanced by measuring real-time environmental factors such as temperature, humidity, factory output, thereby potentially minimizing maintenance costs. Transportation is another area where IoT applications range from vehicles train condition monitoring to track and road sensing [10].

Figure 1.1: IoT applications that encompass our every day life.

The hardware implementation for these IoT applications varies depending on the application in question. It can vary from a circuit board implementation with a battery as power supply connected to a sensor and a micro-controller unit [11] to 3D stacking or chip-level integration of devices to complete system-on-a-chip hardware implementation [12]. As the trend of demands in technologies communicating with each other increases with wearable, smart-home, health, and manufacturing devices, the projected number is about 500 billion IoT devices by 2030 [13]. Wireless sensor networks will be pervasive with continued fast progress in developing miniaturized devices such as portable electronics, micro-electro-mechanical systems (MEMS), CMOS technology in nearly all aspects of our lives. The usefulness of these devices is, however, limited depending on their supply of power [14]. Devices powered by batteries require the replacement of the power supply if they are to continue operating beyond the battery's lifetime. Therefore, there is an increasing interest in self-powered sensors and communication devices with a lifetime that is not limited by their power supply. A review of capabilities of sensors and actuators designed through MEMS technology is presented in Wilson et al.[15].

#### 1.2 Wireless sensor nodes

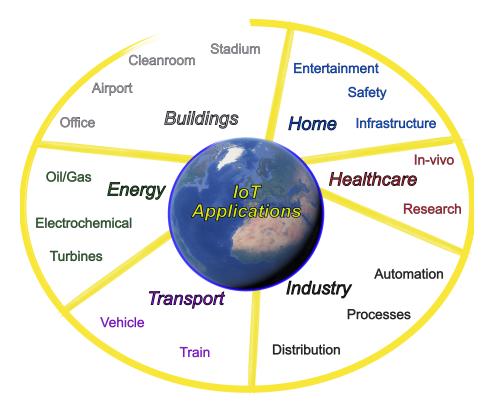

This section will describe the components of a wireless sensor node and their power requirements for autonomous sensing and data transfer. A sensor node is a composition of four units, as shown in Figure 1.2. These units can be categorized as follows -

Figure 1.2: Schematic of a wireless sensor node.

transceiver, processor, sensor, and power unit.

The transceiver combines a transmitter and a receiver that can send and receive signals. It is typically a high power consuming component of the sensor system. The transceiver is connected to a processing unit that comprises a system on chip (SoC) and storage. A processor performs the basic arithmetic, I/O operations, and logic operations alongside allocating commands for the different components running in the system. It is in charge of signal processing such as modulation, demodulation, compression and controls memory access, communication and power management. The processor unit is also connected to the sensing unit. The sensing unit is typically made up of a sensor and a unit that converts analog signals into digital called the analog-to-digital-converter (ADC). The sensor senses the physical information of its surrounding manifesting as an analog electrical signal. The digital information representation provided by the ADC is stored and processed in the processing unit. There can be other subunits, too, depending on the type of application. Through CMOS technology, the power consumption of sensor systems can be kept low while also enabling miniaturized devices.

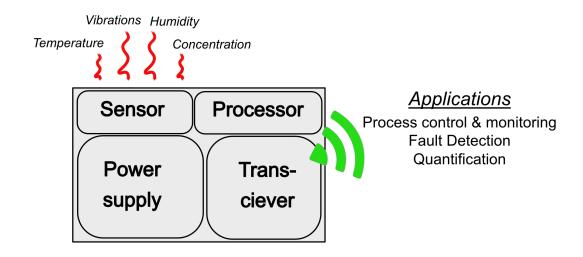

The final unit in the sensor node is the power unit. The power unit must be able to provide power to the sensor node subsystems during passive and active working hours. The utilization of batteries is often deterred by their short lifetimes. Therefore, there is a need for self-sustaining power supplies that harvest their energy from the surroundings and store it in electrochemical capacitors. This would ensure an independent maintenance-free, autonomous and continuously operating sensor node. Some configurations of a power supply can be combinations of various ambient energy harvesting and energy storage devices with a PMU connecting their respective output or input. Such a schematic can be seen in Figure 1.3.

Figure 1.3: Schematic of a power supply with various energy harvesting and energy storage technologies combined through a power management unit.

#### 1.2.1 Power requirements for on-chip sensors and transducers

This section discusses the power requirements of various micro-controller and communication units presented in the literature for on-chip sensor nodes. According to the overview of the field presented by Mayer [16], the power requirements for communication technologies to transmit information is 10 mW. With recent advancements in micro-controller technology, microelectronic circuits can operate at minimum power requirements of 100  $\mu$ W to 10 mW [17]. To further reduce the power requirements of the sensor nodes, various on-chip processors can be implemented to transfer the outcome of processing data collected rather than transmitting all of the raw data for analysis [16].

Traditionally, a sensor node requires power at all stages of operation - sensing, data processing, and data transfer mode. The fraction of total time required for sensing, processing, and delivery comprises the duty cycle of the sensor node. The sensor node is awakened intermittently to transmit information during the duty cycle while sleeping on other occasions. However, to capture real-time changes in the environment, an Always-ON fourth stage is suggested for the sensor node with an automatic surge in power input to the processing and transceiver units to notify the network of the detection of changes immediately. This requirement would require the sensor node to be self-powered with the challenge of delivering nW to mW power at all times.

Batteries are currently being used as power supplies in many different applications. These devices are desirable for their relatively high energy densities. More recently, work in microbatteries has resulted in significant advancements in their rate capability and power density. Electrochemical capacitors or supercapacitors, on the other hand, are governed by two differing mechanisms - electric double layer (EDL) or redox (pseudocapacitive) behavior [18]. These devices have very high power densities and extremely long lifetimes due to their non-reactive nature of storing charge. Supercapacitors, however, need an energy harvesting source to store electrical energy.

Based on the properties of the energy storage device, the energy harvesting system can be chosen based on the following key metrics - size, operation lifetime, frequency (in case of vibrational harvesters) and power. The self-sustaining power supply can function on two mechanisms - harvest environmental surplus energy and use directly or harvest, store and use later. In the former mechanism, the energy harvester powers the sensor units directly. This requires a harvester to function continuously and generate an electrical output resembling a direct current. Thus, with the latter, the harvested energy can be stored in electrochemical capacitors or charge a battery and then the stored energy is supplied to the sensor node for operation. The energy stored in the electrochemical capacitors can also be used in later cycles as per application requirements.

Energy harvesting can make use of energy present in the environment in the form of solar, wind, thermal, or vibrational energy and convert it into usable electrical energy [19]. These energy sources will never deplete as long as the earth is rotating and revolving around the sun. Energy storage units are any devices that can store this electrical energy in the form of charge and then supply it to the system when needed [20]. Since most common microelectronic devices used to construct a sensor node are fabricated through CMOS technology, it would be an advantage for prospects of integration, cost reduction and miniaturization if the power unit's fabrication process would be compatible with this technology.

Integration of such energy harvesting based power supplies into an IoT platform would be fully in line with the ambitions of providing a sustainable development [21, 22]. For energy harvesters and supercapacitors to be implemented in wireless sensor nodes, they must fulfill size, power density, performance, and lifetime requirements. First, they must be small enough, sometimes as small as a cubic centimeter [23] (and be light enough at the same time). Secondly, the supercapacitor should present low losses in power. Thirdly, they require sufficiently low production costs, and finally, as these sensor nodes are to be used in often inaccessible places, the lifetime of these devices must be prolonged.

#### 1.3 Energy harvesting

Let us consider the energy harvesting unit as the first component of the on-chip power supply. This unit converts forms of energy present in their environment into usable electrical energy through various physical mechanisms. These mechanisms can be, for example, photovoltaic (PV), piezoelectric, thermoelectric, triboelectric, or radio frequency (RF) [19]. This section will provide a concise summary of various energy harvesting technologies that are compatible with CMOS-MEMS technology. Based on their bendability, output power, conversion efficiency, ON/OFF times, size, and challenges, the harvesters will be compared.

#### 1.3.1 Solar energy harvesting

Solar energy is one of the most abundant forms of energy in our solar system. The conversion of light to electrical energy can be clean, non-destructive, and practically

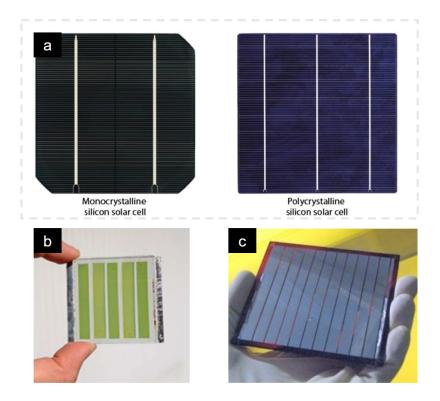

infinitely replenishing. When light is incident on a solar cell, electrical energy is released as an output from the absorption of a photon in the semiconductor lattice. This effect is called the photovoltaic effect. The efficiency of the solar cell is determined by the ratio of total output to input energy. Solar based energy harvesting has emerged as the most viable solution for ambient energy harvesting to supplement batteries and supercapacitors. There are three significant devices used for solar energy harvesting silicon-based solar cells, dye-sensitized solar cells, and organic solar cells, as shown in Figure 1.4.

Silicon solar cells are the most produced and commercialized devices efficiencies reported in research. The highest conversion factor is 25 %, while commercial devices report 15 - 18 % efficiency. These devices are fabricated in large-scale CMOS compatible processing labs. Their process plan uses photolithography, doping, and various other technologies to develop components with a high wafer yield on a silicon substrate. Figure 1.4(a) shows different silicon solar cells. Dye-sensitized solar cells are another form of solar harvesting device that has attracted some attention as promising candidates for alternates to silicon PVs. These devices are semi-flexible and semi-transparent, properties most suited for flexible electronics as shown in Figure 1.4(b). In practical applications, they have reported a maximum conversion efficiency of 15 %. Due to their flexible nature, the encapsulation of an aqueous electrolyte becomes a challenge that requires engineered solutions for further improvement. Organic solar cells are relatively new PV device which utilize polymeric chains of molecules in the light to electricity conversion to obtain low-cost photovoltaics, in Figure 1.4(c). They are rather easy to manufacture as they require vacuum evaporation or filtration as their methods of electrode deposition. They are also unstable, i.e. the organic photovoltaic material can degrade [24]. They are considered inefficient compared to PVs of hard materials, with their overall efficiency up to 10 %.

#### 1.3.2 Thermoelectric energy harvesting

Thermoelectric energy harvesting can use the waste thermal energy present in the surroundings of machines, mines, industries, and even the human body. There are two main principles of thermal energy harvesting. The first principle of harvesting involves the thermoelectric effect [28]. In this principle, the device utilizes the Seeback effect that drives the diffusion of electrons over a temperature gradient. The thermoelectric energy harvesters have been developed to produce energy from temperature gradients on human body. The harvester can reliably operate at ambient conditions while indicating  $20~\mu W~cm^{-2}$  [29]. The prototype could also demonstrate energy harvesting during nighttime conditions. This is a significant advantage over solar PVs.

Thermoelectric generators are easily fabricable, robust, compact, and fatigue proof as they do not involve any moving parts. These devices are desirable in areas where the thermal gradient is large. The second method of thermal harvesting involves the pyroelectric effect. This effect is a combination of charge generation due to polarization through temperature leading to a piezoelectric effect induced in the material [30].

Figure 1.4: (a) Silicon solar cells fabricated on mono and poly crystalline silicon, reproduced from Saga et al. [25], (b) Dye sensitized solar cell fabricated by Huaulme et al. [26], (c) Organic photovoltaic cell manufactured at Solarmer [27]. Images reproduced after permission from the respective authors or publishing agencies.

#### 1.3.3 RF energy harvesting

RF energy harvesting is yet another form of energy harvesting through RF waves present in the environment. The idea of limitless extraction of power from RF interactions has been quite widely adopted in radio frequency identification (RFID) badges. The same principle can be applied in the case of energy harvesting devices for IoT sensor nodes. [31]

The RF harvester is a circuit consisting of an antenna that receives the signal, followed by an impedance matching circuit and rectifier connected to an energy storage unit or sensor load. The antenna captures the RF signal propagating in a wireless transmission medium. Maximum power is extracted from the antenna through the impedance matching circuit and converted to direct current (DC) via the rectifier. If the voltage from the rectifier is lower than required, then the circuit can have a voltage multiplier as a component as well. The output from the rectifier is led to the storage unit of the sensor node. The largest RF harvested power of 62  $\mu$ W was verified through a ten capacitor circuit with a voltage multiplier [32]. The prototype could power a portable calculator at a low charging speed.

The RF harvesters can be used for short burst of power applications. Like the principle of RFID tag, the harvesters can be combined with various flexible electronics that can be used for smart skin health applications. Similarly, such devices can be used

in weather monitoring stations, or lighting LEDs.

#### 1.3.4 Triboelectric energy harvesting

Triboelectric energy harvesting is based on the contact electrification effect in which electrical energy is generated from mechanical contact of material surfaces. The material surface becomes electrically charged after coming in contact with another material surface. The charge transfer between the two materials is facilitated by friction between the surfaces. The transferred charge can then be collected at the current collectors through the induced potential difference. The electricity is generated by frequent contact between the two material surfaces [33].

There are four different operation modes for triboelectric harvesters based on their electrode configuration - vertical contact, lateral sliding, single electrode, and free-standing. In vertical contact mode, the two material surfaces interact with each other in-plane, normal to the direction of motion. Figure 1.5(a) shows one such triboelectric nanogenerator fabricated by Zhang et al. [34]. The device can produce up to 53 mW cm<sup>-3</sup>. One material interface moves in the plane direction parallel to the surface in lateral sliding mode. Pang et al. [35] designed a lateral triboelectric generator that was an acceleration sensor as well. Figure 1.5(b) shows the schematic image of the designed harvester/sensor. The single electrode method is similar to the contact mode method. However, it is applicable in certain areas where there is a requirement of only one electrode. Figure 1.5(c) shows a device demonstrated by Yang et al. [36] which can deliver up to 500 mW/m² from a force input of human touch. The free-standing mode, finally, is based on the principle of potential difference formed between the top and bottom material interface [37].

Figure 1.5: Various types of triboelectric energy harvesters (a) Vertical contact electrodes developed by Zhang [34], (b) lateral design from Pang et al. [35], (c) single electrode device by Yang et al. [36]. Images reproduced after permission from the respective authors or publishing agencies.

#### 1.3.5 Piezoelectric energy harvesting

Kinetic energy harvesting of mechanical energy to electrical energy can be implemented through the piezoelectric effect. The piezoelectric effect is present in many materials with a crystalline structure. The deformation of crystalline structure in the presence of stress or strain causes the electric charge propagation through changes in the charge

distribution of the piezoelectric material. The material is layered on a stressed structure. Therefore, piezoelectric vibrational harvesters are potential candidates for devices that can provide electrical energy for IoT sensor nodes.

While piezoelectricity is not the only conversion mechanism for mechanical to electrical energy, piezoelectric energy harvesters (PEH) have the maximum energy density and a high energy conversion efficiency [38] compared to other kinetic energy harvesting mechanisms such as electrostatic and electromagnetic transduction. They have a simple configuration that can utilize MEMS technology for their fabrication. PEHs also do not require any input voltage for starting up compared to the electrostatic and electromagnetic harvester [39, 40]. Thus, they can be considered potential candidates for powering miniature devices and wireless sensors.

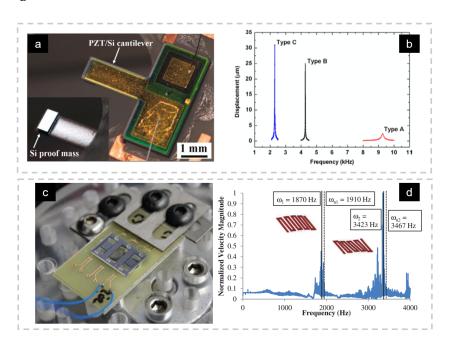

Figure 1.6: MEMS on-chip vibrational energy harvesters: (a) Single cantilever beam produced by Isarakorn et al. [41], (b) output of cantilever beams with 0.5  $\mu$ m epitaxial PZT layer. (c) Folded spring energy harvesters fabricated by Lueke et al. [42] (d) The harvester has the potential to generate energy over a wide range of vibrational frequencies. Images reproduced after permission from the respective authors or publishing agencies.

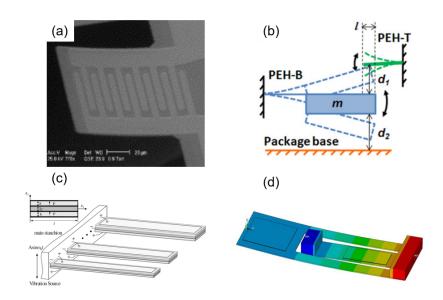

Micromachined piezoelectric energy harvesters (MPEH) can provide the necessary power to the sensor node in the presence of vibrations at its resonant frequency. PEHs usually consist of a free-standing cantilever beam fixed to one end. The beam surface is covered by piezoelectric material, either on both sides. Isarakorn et al. [41] fabricated and experimentally characterized a cantilever beam with a-Si proof-mass to generate an output of 13  $\mu$ W g<sup>-2</sup> at an output current of 48  $\mu$ A g<sup>-1</sup> at a resonant frequency of 2.3 kHz (Figure 1.6(a)) where g is the gravitational acceleration. The output of the energy harvester fabricated is shown in Figure 1.6(b). Although the energy harvester can provide the necessary output for charging sensor nodes, the q-factor of the output is too high. Any deviations from the natural frequency of the design would lead to a significant loss of output. Several solutions for solving this issue have been presented in the literature.

Among them, multi-degree-of-freedom cantilevers provide the necessary improvement in power bandwidth of the energy harvesters of the significant stress present on its surface over a range of frequencies, determined by the complex vibrational response of a system with many eigenmodes [42]. Folded spring harvester shown in Figure 1.6(c, d) can harvest electricity at frequencies from 45 Hz to 3.6 kHz. However, due to a thin lead zirconate titanate (PZT) layer, their maximum output could reach up to 0.6  $\mu$ W at 226 Hz.

#### 1.4 Energy storage

The second principal component of an on-chip power supply is the energy storage unit. The energy harvesters gather the energy from ambient sources in the surroundings and deliver it to the power conditioning unit. The energy storage unit is then connected to the output of the power conditioning circuit, which provides a steady DC output. First chosen as primary energy storage systems were rechargeable batteries such as NiMH [43] and Li-ion [44]. While rechargeable batteries show high capacity and low leakage, the wireless sensor life is limited by the cycle life of rechargeable batteries [45]. The cycle life of a battery is the number of charge-discharge cycles it can go through before its capacity drops below 80 % of its maximum capacity. The residues from the electrodeelectrolyte reaction age the device by increasing the internal resistance over a period of time. However, in reality, at the end of its cycle life, the battery's capacity can reach up to 50 % or even 20 % in some cases. Potential solutions to increase the lifetime, such as increased mass loading of the electrodes [46], reducing the reaction rate between the electrode and electrolyte [47] lead to an undue increase in the size of the device and also leads to potential trade-offs in various other sectors such as safety. Due to this, a WSN would require replacement after not even 1-2 years. Batteries also contain harmful chemicals resulting in environmental pollution [48]. However, various measures are being undertaken to mitigate these ill effects. Supercapacitors have emerged to be successful technological tools in storing charge. They have a higher cycle life than batteries, and in recent years, their energy storage performance has been confirmed to be equivalent to the low-end commercial batteries [49][50]. Supercapacitors can reduce the load on batteries by acting as a smoothing capacitor.

Batteries and supercapacitors, despite their trade-offs, can hold a sufficient application charge from the incoming power from energy harvesting sources. As there is a specific constraint on the size of the power supply intended for IoT sensor nodes, miniaturized devices called micro-batteries (MBs) and microsupercapacitors (MSCs) have the potential to be integrated into such systems. As the miniaturization concept of these devices is still in an exploratory phase, generally, these devices have a total footprint area from anywhere between 1 mm² to 10 mm². The same definition can be applied for flexible MBs and MSCs. However, to limit our deliberation, we will be focusing on solid-state solutions to manufacturing these devices. There are two main configurations of MBs and MSCs - stacked and planar. The electrolyte and separator are sandwiched between two electrodes deposited on the same footprint geometry in a stacked configuration. All the components lie on the substrate plane in the planar devices, and no separator is required, thanks to separation between the electrodes. The

following sections will describe MBs and MSCs that can be potentially integrated into an on-chip power supply with an energy harvesting unit.

#### 1.4.1 Microbatteries

MBs generally provide energy through reversible redox reactions, typically slow. The redox reactions can further be categorized into insertion, alloy, and conversion types reactions. MBs typically establish very high energy densities ranging from 20 to 200 mWh  $\rm cm^{-3}$  with a low self-discharge current.

Among the architectures, stacked and planar MBs, stack MBs were developed in the initial stages of technology development. The electrodes, electrolytes and separator are stacked over the same footprint area. The anodes typically require metal oxides such as V<sub>2</sub>O<sub>5</sub> or lithium transition metal-oxides (LiCoO<sub>2</sub>, LiMn<sub>2</sub>O<sub>4</sub>, LiNiCoO<sub>2</sub>), but polyanion compounds and olivine electrodes can also be considered as anodes. For the electrode that undergoes reduction when the battery delivers power (cathode), typical materials involve graphite or porous carbon like carbon-based materials. Silicon, lithium and titanium compounds such as TiO<sub>2</sub>, Li<sub>4</sub>Ti<sub>5</sub>O<sub>12</sub> are also applied as cathodes. Stacked MBs require solid-state or gel electrolytes for ion-conduction as liquid electrolytes run the risk of short circuits in an on-chip circuitry. Solid-state electrolytes for stacked MBs include lithium lanthanum titanium oxide compounds such as Li<sub>3x</sub>La<sub>2/3-x</sub>TiO<sub>3</sub>, lithium niobium silicon oxides (LiNbO<sub>3</sub>-SiO<sub>2</sub>,Li<sub>2</sub>-P<sub>2</sub>S<sub>5</sub>), lithium phosphates, lithium phosphorus oxynitrile (LiPON) and certain polymers as electrolytes [51]. Typically, the electrolytes have low ion conductivity, which is detrimental to power density. The materials for electrodes and electrolytes are traditionally deposited through micromachining processes such as sputtering [52], electron beam evaporation [53], chemical vapor deposition [54], sol-gel method [55] and atomic layer deposition [56].

Planar MBs have the electrodes parallel to each other on a substrate with a liquid or solid electrolyte for ion transportation. Typically, the electrodes are interdigitated patterns of metal current collectors on which the anode or cathode is deposited. This kind of electrode geometry allows for faster ion transportation related to redox reactions, thereby increasing the power density of the device. However, as the design is planar, the footprint area of the MBs is halved for a single electrode which leads to a reduction in energy density compared to stacked MBs. Typically the anodes and cathodes of planar MBs are deposited through electrodeposition [57] and electroplating [58]. Typical materials used for anodes involve nickel-tin alloys, nickel scaffolds,  $\text{Li}_4\text{Ti}_5\text{O}_{12}$ , or graphene while cathodes utilize, manganese oxide,  $\text{LiFePO}_4$ ,  $\text{MoS}_2$  as cathodes.

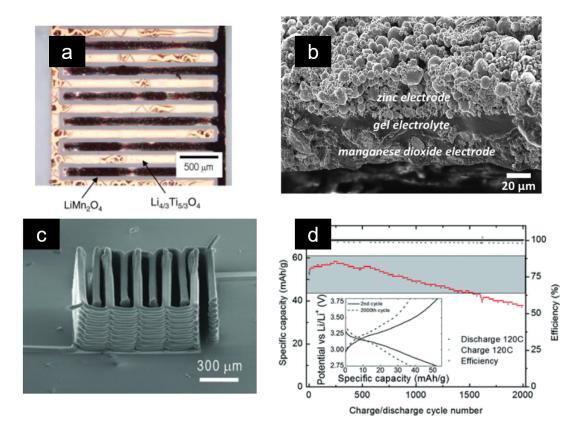

Some examples of MBs are shown in Figure 1.7. Nakano et al. [59] designed interdigitated cells for MBs using  $\text{LiMn}_2\text{O}_4$  and  $\text{Li}_{3/4}\text{Ti}_{5/3}\text{O}_4$  for the cathode and anode respectively. The MBs demonstrated an operational voltage of 2.45 V. The device is shown in Figure 1.7(a). An example of a stacked MB is shown in Figure 1.7(b). The authors in this work [60] deposited the materials bottom-up using a direct-write printing method. The discharge capacity was measured at 0.98 mAh cm<sup>-2</sup>. The energy density of the device was 1.2 mWh cm<sup>-2</sup>. 3D printed MBs using lithium tantalum oxide and LFP as electrodes were indicated by Sun et al. [61] using a 30  $\mu$ m printing nozzle.

Figure 1.7: Examples of MBs present in literature: (a) planar MB fabricated by Nakano et al [59] using solution based deposition of electrodes, (b) stacked MBs fabricated by Ho et al. [60] using screen printing, (c) 3D printed MB by Sun et al.[61]. (d) Example of poor cyclic capability of MBs with  $V_2O_5$  as electrodes. Images reproduced after permission from the respective authors or publishing agencies.

Although there have been significant advancements in MBs, several challenges require considerable attention for improvement in their power density and cyclic stability before being a viable solution for a self-reliant power supply. An example of the cyclic lifetime of a battery is shown in Figure 1.7(d). The  $\rm V_2O_5$  MB electrodes fabricated by Nilsen et al. [62] lose the specific capacity by 33 % by 1500 cycles. Suppression of redox reaction by-products such as the dendritic formation of lithium and zinc is also an issue that needs to be tackled [63]. Optimization of solid-state electrolyte ion conductivity, stability, and non-flammability are a few problems with current electrolytes applied in MBs. Thus, we require more sustainable and stable solutions for energy storage.

#### 1.4.2 Microsupercapacitors

MSCs are another form of supercapacitors that store or generate charge through electrical double layer capacitance (EDLC) or redox mechanism (pseudocapacitance) at the electrode-electrolyte interface. In the EDLC mechanism, the electrolyte ions are attracted to the positive and negative electrodes of the device, where they form nanocapacitors at the electrode interface with the electrode surface. During EDL behavior, the electrodes and electrolytes interact non-invasive to form nano-capacitors at their

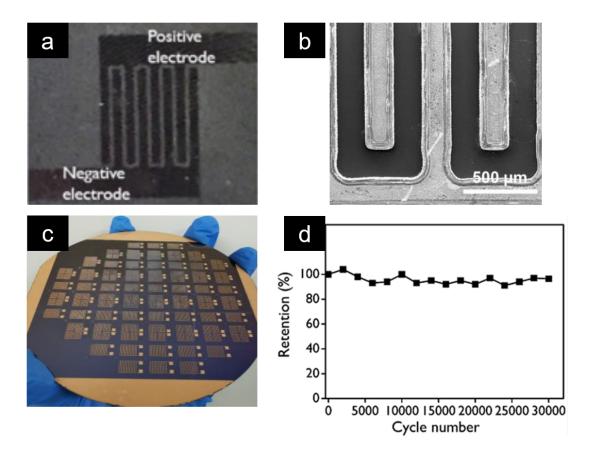

Figure 1.8: (a) Laser scribed graphene based MSC fabricated by Kim et al. [64] , (scale = 1  $\mu m$ ) (b - c) 3D mesoporous gold fabricated by electrodepostion by Wang et al. [65], (d) Example of cyclic stability of a MSC using C/MnO $_2$  as electrodes by Wang et al. [65]. Images reproduced after permission from the respective authors or publishing agencies.

interface. This allows the supercapacitor to store more charge per unit area than conventional capacitors. In pseudocapacitance, the electrode and electrolyte interact in the form of a redox reaction to store the input charge acquired from an energy harvesting/power conditioning output. MSCs are considered an alternative to MBs due to their extremely long cycle life (over  $10^6$  cycles) and high power density.

The architecture of MSCs is also similar to MBs, as discussed in the earlier section, categorized into the stack and planar structures. Stacked MSCs suffer from the problems encountered in stacked MBs, such as low ionic conductivity inability to utilize ionic or aqueous electrolytes. Similarly, issues with short-circuiting of electrodes are more evident in MSCs than MBs due to the porous nature of the electrodes. Several articles reveal the performance of pseudocapacitive material, such as  ${\rm RuO_2}$  as stacked electrodes with solid-state electrolytes such as LiPON [66]. More recently, 2D materials with high electrical conductivity enable ultrathin films to be used as stacked MSCs [50]. They can also be used as separators on their own after modulating their conductivity. Stacked MSCs are often utilized for flexible electronics with a smaller restriction on size. Stacked devices, however, are limited to ultrathin films as the thickness increases the resistance

1.5. Challenges

of ion-transportation paths. Thus, there needs to be a trade-off between footprint area and thickness.

Planar MSCs, on the other hand, can exhibit short ion transportation channels between the positive and negative terminals due to the geometric patterns of micrometer resolutions. Compared to stacked MSCs, planar devices demonstrate a drastically improved power and rate capability. The fabrication of planar devices on solid-state substrate reduces the issue of high resistance in thicker electrodes as the electrolyte is in contact with a larger surface area of electrodes. Planar MSCs are often fabricated using carbon, 2D material, pseudocapacitive, and polymer-based electrodes while using a gel, aqueous, or solid-state electrolyte. They are fabricated through a range of fabrication processes such as electrodeposition [67], photolithography [68], chemical vapor deposition [69], layer-by-layer [70], Inkjet printing [71], and laser scribing [72]. Among various viable techniques for fabrication, photolithography and chemical vapor deposition are some of the standard CMOS processes. Some examples of MSCs are shown in Figure 1.8.

Both planar and stacked MSC configurations have advantages and disadvantages, making them suitable for specific applications. Although MSCs have large power density, short charge-discharge cycles, and high cyclic stability, these devices also require attention on low energy density, high serial resistance, poor high-frequency behavior, and non-standardized front-end-of-line (FEOL) and back-end-of-line (BEOL) CMOS compatibility.

#### 1.5 Challenges

There are several challenges in implementing an on-chip self-sustaining power supply for IoT sensor nodes. The main challenge is the loss of power or energy due to a temporary lack of the expected or required physical conditions such as available sunlight or vibrations at the appropriate frequencies. A directly related challenge is the efficient storage of harvested energy in the energy storage system. Batteries typically have low leakage. However, the main concern with them is their cyclic stability. Therefore, they require to be swapped after short term usage. The high cost of manufacturing and disposal of batteries has become another critical issue. Therefore, they must be replaced entirely or complemented by electrochemical capacitors to improve upon their short lifetimes.

One main challenge currently presented for vibrational energy harvesters in their deployment is the lack of sufficient bandwidth in MEMS designs. Impedance mismatch is also an issue with vibrational harvesters as it can significantly impact the magnitude of the output harvested power. Although the fabrication methodology of these harvesters is well defined, there are several severe problems in their wafer-level fabrication that increase the total cost of manufacturing a single device, such as electrode retention, wafer-scale piezoelectric poling, and dicing, to name a few. A more comprehensive review addressing fabrication challenges of MPEHs is given by Rezaei et al. [73].

On the other hand, electrochemical capacitors suffer primarily from low energy density, high leakage current, and lack of proper CMOS compatible fabrication methodology. Most of the fabrication processes examined in literature for manufacturing MSCs

utilize different methodologies for various electrodes. In order to design the properties of energy storage devices, there must be a cohesive fabrication process that can incorporate any material essential for improving the device performance. Such a process should have high resolution and establish a high wafer yield comparable to the state-of-the-art sensor or CMOS technology.

#### 1.5.1 Manufacturing for microelectronic compatibility

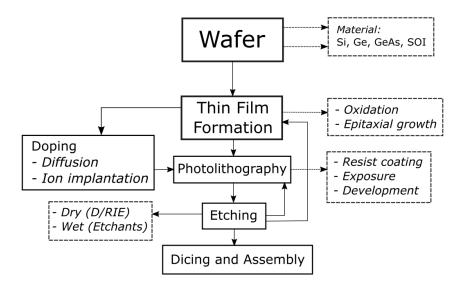

To understand the challenge of fabrication of on-chip vibrational energy harvester and CMOS compatible MSCs, we will review the standard processes used in microelectronic integrated circuits (IC) compatible fabrication processes. The standard process technology for ICs and very large scale integrated (VLSI) circuits is shown in Figure 1.9. The fabrication of these components starts on a wafer, a polished semiconductor substrate. The next step usually involves deposition or growth of thin films such as SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, polySi or dielectric films, and even metalized oxides. After the growth of thin films, the substrate undergoes doping through diffusion or ion implantation. This process is used in IC technology to fabricate pn junction diodes which can later be used in MOSFET (metal-oxide-semiconductor field-effect transistor) fabrication. Then, the substrate is subjected to photolithography, where a polymeric photoresist is spin-coated on it and then exposed in UV light through a special mask with a specific design. The photoresist is sensitive to UV light depending on its chemical structure. It is generally of two types positive and negative. In the case of the positive photoresist, the UV light breaks the linkages of the polymer exposed, while in the negative, the exposure strengthens the bonds of the polymer. During the development of the photoresist step, the weaker linkage polymers are etched out of the substrate while leaving the photoresist in the desired pattern. Depending on the process's requirement, the exposed surface is then used for further doping, film formation, or etching. The process is then repeated in several cycles depending on the total number of photolithographic masks [74].

However, there are several constraints in the IC fabrication process regarding the choice of material and equipment. The first significant constraint is the material for the wafer. An IC wafer should be mechanically robust with the required hardness to survive both automated and manual handling in all process steps. The second constraint comes in the form of radiation required for photolithography: optical and UV light, X-ray, and electron beam. The third constraint is in the form of metals used in IC fabrication. This list is restricted to Al, Au, Ag, Cr, Mo, W, Pt, Pd, Ta, and Ti [74]. Furthermore, the process is also dependent on the melting point of these metals. Among the used metals, Al has the lowest melting point at 660 °C. So, the fabrication of energy harvesters, supercapacitors, and subsequent integration should be conducted with the techniques within these constraints.

Fabrication of on-chip MPEHs requires photolithography, etching, metallization, doping, and deposition techniques. These processes are standard in micromachining techniques too. Furthermore, with improving MEMS technology, these processes have become highly developed in improved reliability, mass production, and cost reduction while achieving a high wafer yield. Therefore, energy harvesters that are fabricated

Figure 1.9: Main fabrication steps for a IC fabrication process. The dotted square boxes show the constrained variety of processes possible in a CMOS compatible fabrication facility.

through MEMS techniques can be easily integrated into a CMOS compatible fabrication process.

However, for the energy storage element, supercapacitors generally require a large physical size and specialized manufacturing techniques that make them hard to be integrable in microsystem electronics technology that requires semiconductor micromachining. Therefore, developing CMOS compatible fabrication processes has attracted much attention over the past few years [75, 76, 77, 64, 71].

Compared to other techniques to manufacture MSCs such as screen printing [78], inkjet printing [71], laser scribing [64], electrostatic spray deposition [77], electrophoretic deposition [79], chemical exfoliation [80] and doctor blade coating [81], the use of spin coating has the advantage of already being an established conventional part of standard CMOS processing, implying that it is as such inherently CMOS/MEMS compatible. Techniques that are not compatible with semiconductor device processing prohibit cost-effective integration and fabrication of on-chip harvesters and MSCs. Processes like inkjet printing and screen printing do not have an effective scaling down technique, while its raster-scanning process inhibits laser scribing. Thus, in view of the expected further automation in IC manufacturing [82], its compatibility advantage makes spin coating a strong candidate for being a preferred MSC manufacturing technique, provided it can validate that it can fabricate devices of sufficient quality and yield.

### 1.6 Scope of the thesis

In this thesis, we will discuss vibrational energy harvesters and electrochemical capacitors that can be fabricated through MEMS and CMOS compatible technology to develop an on-chip power supply for sensor nodes with an aim of extended lifetime. Chapter 1 introduced the concept behind a self-reliant on-chip power supply through

an evaluation of requirements necessitated by IoT applications. A concise summary of energy harvesting, micro-energy storage, and IC-compatible manufacturing process is presented.

Chapter 2 discusses the current status of piezoelectric energy harvesting technology. A formal theory is presented to motivate the choice of device design intended for onchip energy harvesting. The energy harvesters are categorized for various bandwidth improvement strategies and their performance metrics are examined with a state-of-the-art comparison of micro-electro-mechanical-systems (MEMS) piezoelectric micro-energy harvesters based on them. The two-degree-of-freedom (2DOF) structures are investigated further in Paper 1 through design and fabrication of cut-out cantilevers. The challenges of fabrication are summarized and the second and third generation of vibrational energy harvesters are presented and explained. A section on discussion of future of vibrational energy harvesters is presented.

In chapter 3, we focus on the energy storage component of a wireless sensor node, with MSC in focus. The chapter summarizes different figures of merit determining the charge storage and delivery capacity of the MSCs. The fabrication methodologies for manufacturing MSCs for on-chip electronics is considered in more detail with a comprehensive literature survey of electrode deposition processes such as chemical vapor deposition, photolithography, inkjet printing, electrodeposition, and electrode conversion. The impact of electrode geometry and thickness is investigated in Paper 3 through fabrication of CVD based carbon nanofiber (CNF) electrodes. Based on the results of electrode geometries, the spin coating process is explored as the viable option for CMOS technology integration of MSCs using graphene oxide (GO) based aqueous solution. The fabrication process and its shortcomings are examined in more detail. We introduce an enhanced spin coating process in Paper 2 and review the impact of surface roughening on the spin coating of electrodes. The CNF and rGO based devices are compared in Paper 4. Finally, we will discuss the results to improve the energy density of the MSCs using a variety of rGO based electrodes deposited through enhanced spin coating process described in detail in Paper 5.

Chapter 4 examines the challenges of on-chip integration of vibrational microenergy harvesters and MSCs for a self-reliant on-chip power supply. The packaging of both devices – harvesting and storage are examined. The experimental aspects of package fabrication, choice of electrolyte, and device assembly are considered. The strategies for on-chip integration are analyzed with a description of proposed experimental integration of on-chip power supply. In chapter 5, we will highlight the summary of the thesis and take up the aspects that can be explored in future work. Finally, a summary of appended papers is presented.

## Chapter 2

## Piezoelectric vibrational energy harvesters

#### 2.1 Introduction

Piezoelectric energy harvesting is a type of energy scavenging that uses the vibrations present in the environment as their source. Vibrations are ubiquitous in our body and surroundings ranging from heartbeats, traffic on roads and railway tracks, and industrial equipment in use. The mechanical energy is converted to electrical energy by a piezoelectric material layered on a cantilever. When the cantilever vibrates at a certain frequency, the vibrations produce a mechanical stress in its structure. The stress in the beams is transferred to the piezoelectric material present on the cantilever structure. This leads to accumulation of charge in the domains of the piezoelectric material. When the device is connected to a load, the circuit is complete and the output electrical energy is delivered in the form of an alternating current.

In comparison to various energy harvesters discussed in the introduction, MPEHs demonstrate considerable potential in charging energy storage devices for wireless sensor nodes owing to relatively high energy densities and possibilities for integration in MEMS and IC technologies. The presence of vibrations in harsh environments such as industries, mines, and deep-sea exploration are specially suitable for the application of vibrational energy harvesters. A model of an energy harvesting devices for the collection of vibrational energy from the surroundings was developed in 2000 [83]. This model was designed for the transfer of power to sensors in sensing networks. An analytical solution and experimental design of a bimorph, i.e., a cantilever containing piezoelectric material on both sides, was developed by Inman et al. [84], both with series and parallel connections of the piezoelectric layers. Since then, the PEH has been studied for ambient vibrations such as traffic [85], bridges [86], motors [87], air turbulence [88, 89], and human motion [90, 91, 92]. PEHs are also present as fabric composites that can be woven in e-textiles [93]. They can also be used to produce electrical energy from water flows [94], rain drops [95, 96, 97], and rotation- and flow- induced vibrations [98, 99, 100] that are present as outcomes of impact [101], friction [102] and random excitations [103]. There is additional benefit in miniaturizing the designs so they can be fitted in extremely narrow or small spaces. Such MPEHs can be integrated alongside

2.1. Introduction

energy storage units such as electrochemical capacitors through compact, high power miniaturized mechanical designs that can be integrated with sensors, transceiver, and IC processing units, on a  $1~\rm cm^2$  die footprint.

There are, however, two important challenges that restrict a scalable integration of MPEHs. Firstly, they must be able to produce enough energy to charge an electrochemical capacitor through either steady state- or intermittent charging. Steady state charging can be achieved by placing the MPEH in an environment that has vibrations in a certain frequency range with semi-infinite duration. Intermittent charging is more applicable where the MPEH transforms energy during a specific action in the environment, such as train passing over the sensor node fitted on a railway track, or the opening of heavy doors in shopping areas. In real life situations, the vibrations in both cases occur over a range of frequencies that should be compatible with the bandwidth of operation for the harvester. Typical vibrations in systems present in the environment such as traffic can range from 1 - 100 Hz. Similarly, ground borne vibrations, machinery, and acoustic vibrations can range from 1 to 500 Hz [104]. Thus, it is necessary for the MPEH to produce sufficient electricity over a large bandwidth of operation. If these devices can provide  $\mu$ W to mW power, they can be integrated to power sensor nodes in areas with access to high waste mechanical energy.

There are several mechanisms in the literature that improve the bandwidth of the MPEH. They can be broadly categorized in four categories - monostable or one-degree-of-freedom (1DOF) structures, multi-stable structures, frequency up-conversion mechanisms, and multiple-degrees-of-freedom (nDOF). These mechanisms are used extensively in macro-energy harvesters. We categorize macro-energy harvesters as structures that have been manufactured through conventional machining techniques such as high-precision lasers, lathe machines, computerized numerical controls (CNCs) and toolboxes. We shall review the MEMS compatibility of these mechanisms in this chapter followed by a comprehensive review of PZT based MPEHs using piezoelectric microcantilevers.

The mechanisms for vibrational energy harvesting utilize a variety of piezoelectric materials. Piezoelectric materials can be categorized into three different categories inorganic piezoelectric materials, piezocomposites, and voided charged polymers. Inorganic piezoelectric materials include PZT, ZnO, and AlN based materials. They generally possess a high figure-of-merit (FOM), a quantity used to characterize the piezoelectric response of a material. The FOM of piezoelectric materials can be defined as the ratio between the total electrical energy harvested over the total mechanical energy applied. It is denoted as  $k^2 = \frac{d^2}{s \times \epsilon}$  where  $d_{31,33}$  is the strain induced in the material normal (31) or parallel (33) to the applied force vector,  $s_{31.33}$  is the material compliance, and  $\epsilon$  is the relative permittivity. The inorganic piezoelectrics also have a high Curie temperature, the point at which the material loses its piezoelectric property. Piezocomposites are another category of piezoelectric materials that use materials such as multifunctional cellulose, ZnO with cellulose, Pt nanowires with polydimethysiloxane (PDMS) composites. They are similar in terms of FOM with the inorganic piezoelectrics however they possess a lower Curie temperature. Voided charged polymers are newly developed highly porous piezoelectric materials that use parlyene, PDMS, polyvinlydiflouride (PVDF) polymers. They generally possess quite low FOMs compared to the other piezoelectric material however their availability and ease of manufacturing bulk films makes them a competitive solution for use in energy harvesting.

The second challenge in integrating MPEH in wireless sensor nodes is the scalability of the fabrication process. Piezoelectric micro-cantilevers are already used in scanning tunneling microscopy to characterize the surface properties of devices and materials through electrical excitation at a particular resonating frequency [105]. However, these structures are designed for narrow bandwidths with a large quality factor. In order to fabricate devices with large bandwidths, there are several fabrication challenges that can impede the manufacturing process. We shall discuss these challenges in this chapter through experimental evaluation of the MEMS fabrication process performed in a state-of-the-art cleanroom facility.

### 2.1.1 Challenges in power density

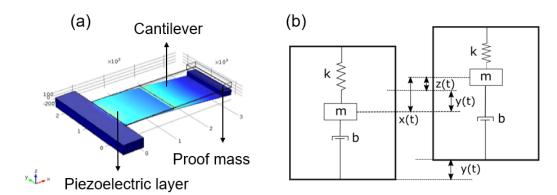

In order to understand the working mechanism of MPEHs, the device can be visualized as a mass-spring-damper (MKS) system, as seen in Figure 2.1. The mass of the device is m, y is the amplitude of displacement, k is the stiffness of the beam, y(t) is the displacement of the beam, z(t) is the relative position of the center of mass of the beam with respect to its displacement and  $b_m$  and  $b_e$  are the damping coefficients and  $b = b_m + b_e$ , where m and e are the mechanical and electrical indices respectively.

Figure 2.1: (a) Schematic of a typical single cantilever vibrational energy harvester. The gradient - light to dark blue represents descending order of stress on the beams, (b) Typical schematic of the MKS 1DOF system.

Let the displacement of the system  $y(t) = Y \sin(\omega t)$ . With that we get the transfer function as a second order differential equation

$$mz''(t) + bz'(t) + kz(t) = -my''(t)$$

(2.1)

Now in a standard form,

$$z''(t) + \frac{b}{m}z'(t) + \frac{k}{m}z(t) = -y''(t)$$

(2.2)

From the solutions of the second order differential equation, we know that

$$\frac{b}{m} = 2\zeta \omega_n \qquad \frac{k}{m} = \omega_n^2$$

22 2.1. Introduction

where  $\omega_n$  is the natural frequency of the undamped system, and  $\zeta$  is the damping ratio. So, from this, we get

$$\omega_n = \sqrt{\frac{k}{m}} \qquad \qquad \zeta = \frac{b}{2\sqrt{km}}$$

We can also derive a notation called the quality factor (Q) as

$$Q = \frac{\sqrt{km}}{b}$$

which can also written in terms of  $\omega_n$  as

$$Q \approx \frac{\omega_n}{\Delta \omega} \tag{2.3}$$

where  $\Delta \omega$  is the bandwidth of frequencies that have a power output of at least half the magnitude at the resonant frequency  $\omega_n$ . It is also denoted as the 3 dB bandwidth of any harvesting system. Considering our input signal y(t), the solution for average power related to mechanical losses and electrical output is

$$P(\omega) = \frac{m(\zeta_m + \zeta_e)Y^2(\frac{\omega}{\omega_r})^3 \omega^3}{[1 - (\frac{\omega}{\omega_r})^2]^2 + (2(\zeta_m + \zeta_e)\frac{\omega}{\omega_r})^2}$$

(2.4)

When the frequency of the system  $\omega$  is equal to the resonant frequency  $\omega_r$ , the power reaches its maximum which is

$$P = \frac{mY^2\omega_r^3}{4(\zeta_m + \zeta_s)} \tag{2.5}$$

On further analysis of equation 2.8, we figure out one main issue that needs to be optimized with the utilization of MPEHs in on-chip power units, i.e. narrow bandwidth.

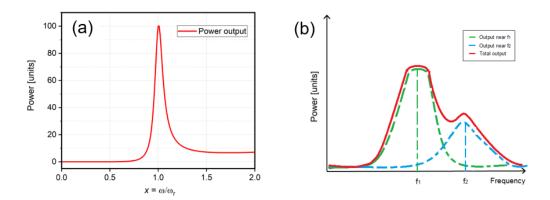

Considering  $\frac{\omega}{\omega_r} = x$  and keeping m, Y and  $\zeta_m$ ,  $\omega_r$ , and  $\zeta_e$  as arbitrary constants  $C_{1,2}$ , we get the equation 2.8 as

$$P = \frac{C_1 x^6}{(1 - x^2)^2 + C_2 x^2} \tag{2.6}$$

When we plot this equation in Figure 2.2(a), we see the reduction of output power at either side of  $\omega_r$ . Therefore, we need to find solutions for improving its bandwidth of frequencies by reviewing some of the pre-existing solutions in macro-energy harvesters. Such a desirable output is shown in Figure 2.2(b). These solutions must also be feasible for realization in a MEMS structure which can then further be integrated with an on-chip power supply.

Thus the development of MPEHs requires improvements in the design compared to a single cantilever to achieve a maximum power density. Even a slight variation in the vibrational frequency of the environment would result in the dramatic reduction of power output from MPEHs resulting in severe transduction inefficiency. Thus, there is a need to survey the existing literature for macro-energy harvesting mechanisms for improving bandwidth and design of an MPEH that can be fabricated in a scalable way through MEMS fabrication technology. In the next section, we shall discuss various mechanisms reported in the literature to improve the bandwidth of operation.

Figure 2.2: (a) Simulated power output of a generic single cantilever based energy harvester with respect to  $x = \frac{\omega}{\omega_r}$ , (d) Desirable wide bandwidth output power required from the energy harvester.

## 2.1.2 Bandwidth improvement designs

PEHs can generally be divided into four categories. The following section examines these categories and discusses the aspects of bandwidth improvements in these designs.

Figure 2.3: Techniques in macro-energy harvesting that are used for improving the device's bandwidth of frequencies: (a) A stress induced structure by Blystad et al. [106], (b) amplitude limiter, (c) array configuration by Xue [107], (d) 2DOF freedom structure by Wu et al. [108]. Images are reproduced after permission from the publishers.

#### Mono-stable or 1DOF structures

The first energy harvesting mechanism in MPEHs pertains to monostable or 1DOF oscillations. They require an external stimulus at their resonant frequency. After the

2.1. Introduction

input stimulus is switched off, they return to their equilibrium position. The power output of these designs depends on the amplitude of vibration, their natural frequency, and young's modulus E of the structure. Generally, cantilever beams with a proof-mass are used to produce high power output at their first natural frequencies. Figure 2.1(a) shows a typical cantilever design. Due to movement of the beams in only one direction, these designs are often referred to as 1DOF structures.

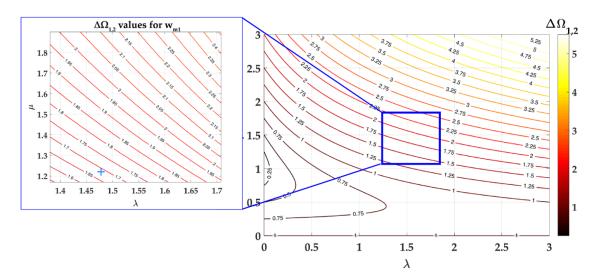

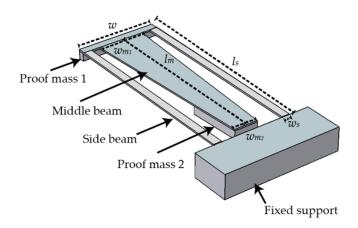

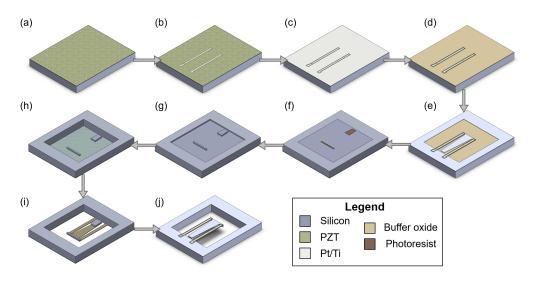

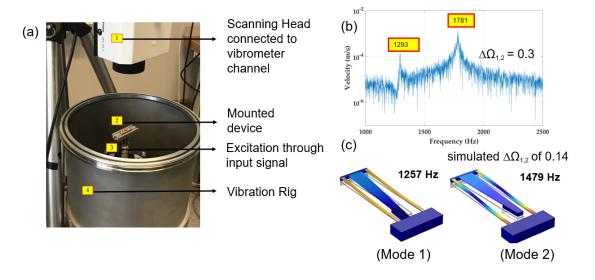

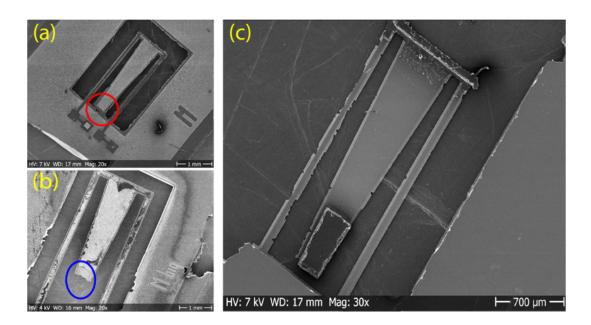

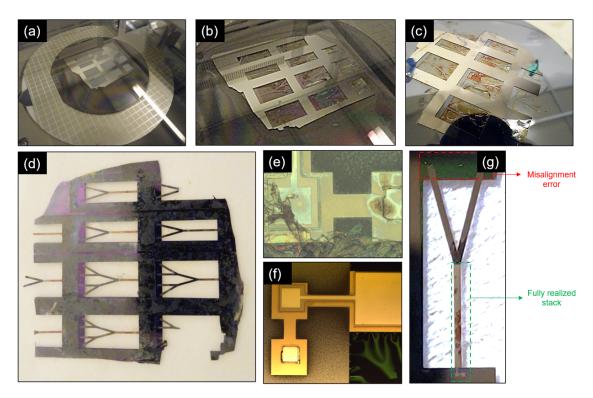

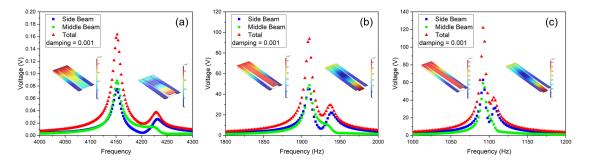

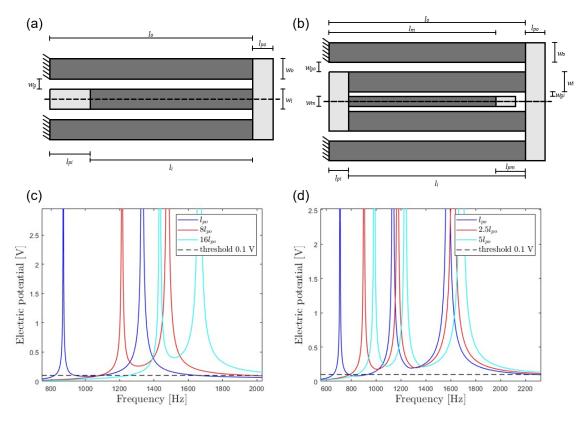

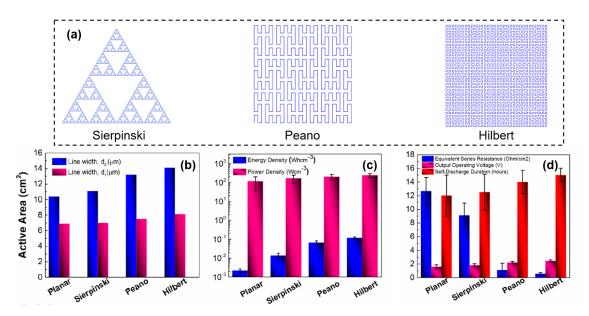

Surface micro-machining fabrication techniques have been used in manufacturing several 1DOF energy harvesters at a large scale [109]. They presented a single rectangular cantilever with a hanging proof-mass. The proof-mass is usually quite thick compared to the cantilever beam. The large proof-mass acts as a hanging mass to the spring system, thereby reducing its natural frequency. The proof-mass can be made during the micromachining process, or it can be added onto the fabricated structure. Jeon and Choi [110], [111] fabricated a  $\rm d_{33}$ , PZT-based vibrational harvester. The cantilever beam was composed of a thin  $\rm SiO_2/SiN_{\it x}$  layer with a diffusion barrier of ZrO\_2 separating PZT from the structure. The proof-mass was made up of SU-8 thick resist. Fang et al. [112] similarly created microcantilevers through micromachining techniques and added a Ni proof-mass post-processing. Due to Ni's higher density over Si (8.9 g/cm³ vs. 2.3 g/cm³), it reduces the resonance frequency of the device. We have examined several micro-energy harvesters in a more concise format in Paper 1. Also, the list of device performances can be found in Table 2.1.