# Design, Fabrication and Characterization of GaN HEMTs for Power Switching Applications

Björn Hult

### **CHALMERS**

Microwave Electronics Laboratory

Department of Microtechnology and Nanoscience

Chalmers University of Technology

Göteborg, Sweden, 2022

# Design, Fabrication and Characterization of GaN HEMTs for Power Switching Applications

BJÖRN HULT

#### © Björn Hult, 2022

Chalmers University of Technology Department of Microtechnology and Nanoscience - MC2 Microwave Electronics Laboratory SE-412 96 Göteborg, Sweden Phone: +46 (0) 31 772 1000

ISSN 1652-0769 Technical Report MC2 - 448

Printed by Chalmers Reproservice Göteborg, Sweden 2022

## **Abstract**

The unique properties of the III-nitride heterostructure, consisting of gallium nitride (GaN), aluminium nitride (AlN) and their ternary compounds (e.g. AlGaN, InAlN), allow for the fabrication of high electron mobility transistors (HEMTs). These devices exhibit high breakdown fields, high electron mobilities and small parasitic capacitances, making them suitable for wireless communication and power electronic applications. In this work, GaN-based power switching HEMTs and low voltage, short-channel HEMTs were designed, fabricated, and characterized.

In the first part of the thesis, AlGaN/GaN-on-SiC high voltage metal-insulatorsemiconductor (MIS)HEMTs fabricated on a novel 'buffer-free' heterostructure are presented. This heterostructure effectively suppresses buffer-related trapping effects while maintaining high electron confinement and low leakage currents, making it a viable material for high voltage, power electronic HEMTs. This part of the thesis covers device processing techniques to minimize leakage currents and maximize breakdown voltages in these 'buffer-free' MISHEMTs. Additionally, a recess-etched, Ta-based, ohmic contact process was utilized to form low-resistive ohmic contacts with contact resistances of 0.44-0.47 Ω·mm. High voltage operation can be achieved by employing a temperature-stable nitrogen implantation isolation process, which results in three-terminal breakdown fields of 98-123 V/μm. By contrast, mesa isolation techniques exhibit breakdown fields below 85 V/µm and higher off-state leakage currents. Stoichiometric low-pressure chemical vapor deposition (LPCVD) SiN<sub>x</sub> passivation layers suppress gate currents through the AlGaN barrier below 10 nA/mm over 1000 V, which is more than two orders of magnitude lower compared to Si-rich SiN<sub>x</sub> passivation layers. A 10% dynamic onresistance increase at 240 V was measured in HEMTs with stoichiometric  $SiN_x$ passivation, which is likely caused by slow traps with time constants over 100 ms. SiN<sub>x</sub> gate dielectrics display better electrical isolation at high voltages compared to  $HfO_2$  and  $Ta_2O_5$ . However, the two gate oxides exhibit threshold voltages  $(V_{th})$  above -2 V, making them a promising alternative for the fabrication of recess-etched normally-off MISHEMTs.

Reducing the gate length ( $L_g$ ) to minimize losses and increase the operating frequency in GaN HEMTs also entails more severe short-channel effects (SCEs), limiting gain, output power and the maximum off-state voltage. In the second part of the thesis, SCEs were studied in short-channel GaN HEMTs using a drain-current injection technique (DCIT). The proposed method allows  $V_{th}$  to be obtained for a wide range of drain-source voltages ( $V_{ds}$ ) in one measurement, which then can be used to calculate the drain-induced barrier lowering (DIBL) as a rate-of-change of  $V_{th}$  with respect to  $V_{ds}$ . The method was validated using HEMTs with a Fe-doped GaN buffer layer and a C-doped AlGaN back-barrier with thin channel layers. Supporting technology computer-aided design (TCAD) simulations indicate that the large increase in DIBL is caused by buffer leakage. This method could be utilized to optimize buffer design and gate lengths to minimize on-state losses and buffer leakage currents in power switching HEMTs.

**Keywords**: GaN HEMT, 'buffer-free', high voltage, isolation, passivation, gate dielectric, SCE, DIBL, DCIT

# List of Publications

## **Appended Publications**

This thesis is based on work contained in the following papers

- [A] B. Hult, M. Thorsell, J. T. Chen, N. Rorsman, "High Voltage and Low Leakage GaN-on-SiC MISHEMTs on a 'Buffer-Free' Heterostructure", *IEEE Electron Device Letters*, vol. 43, no. 5, pp. 781-784, May 2022

- [B] **B. Hult**, M. Thorsell, J. T. Chen, N. Rorsman, "AlGaN/GaN/AlN 'Buffer-Free' High Voltage MISHEMT with Si-rich and Stoichiometric SiN<sub>x</sub> First Passivation", accepted for a presentation at *Compound Semiconductor Week*, June 1-3, 2022

- [C] **B. Hult**, J. Bergsten, R. Ferrand-Drake Del Castillo, V. Darakchieva, A. Malmros, H. Hjelmgren, M. Thorsell, N. Rorsman, "Investigation of Electron Confinement in GaN HEMTs with a Drain Current Injection Technique", submitted to *IEEE Transaction on Electron Devices*, 2022

## Other Publications

The content of the following publication is out of the scope of this thesis

[a] A. Papamichail, A. Kakanakova, E. O. Sveinbjörnsson, A. R. Persson, B. Hult, N. Rorsman, V. Stanishev, S. P. Le, P. O. Å, Persson, M. Nawaz, J.-T. Chen, P. Paskov, V. Darakchieva, "Mg-doping and free-hole properties of hot-wall MOCVD GaN", accepted for publication in *Journal of Applied Physics*

# **Contents**

| Abstract                                                           | 3  |

|--------------------------------------------------------------------|----|

| List of Publications                                               | 5  |

| 1. Introduction                                                    | 7  |

| 2. 'Buffer-Free' GaN-on-SiC High Voltage HEMTs                     | 11 |

| 2.1 Device Fabrication                                             | 16 |

| 2.2 Ohmic Contacts                                                 | 19 |

| 2.3 Electrical Isolation                                           | 23 |

| 2.4 Passivation Layer                                              | 28 |

| 2.5 Gate Dielectric                                                | 33 |

| 3. A New Method to Characterize Short-Channel Effects in GaN HEMTs | 37 |

| 3.1 Heterostructure Design Variations                              | 40 |

| 3.2 Physics-Based Device Simulations                               | 43 |

| 4. Conclusions and Future Work                                     | 47 |

| Acknowledgements                                                   | 50 |

| Bibliography                                                       | 51 |

# Chapter 1

# Introduction

Power electronic converters play a vital role in the electrification of our increasingly energy-demanding society. Consumer electronics, motor drivers, renewable energy, and power grids require power conversion in the form of DC-DC (buck, boost), AC-AC, DC-AC (H-bridge), and AC-DC (three-phase). Two necessary building blocks in any power electronic converter are power electronic diodes and transistors, which act as passive and active switches. An ideal power electronic switch can conduct arbitrarily large currents with zero power dissipation in the onstate, block arbitrarily large voltages in the off-state, and switch between the two states at any frequency without dissipating any power. However, any realizable power electronic switch will exhibit on-state losses, switching losses and limitations to the off-state voltage. These constraints depend on the semiconductor material properties and the device design. Semiconductor materials with a high critical electric field are of primary interest since they allow for lateral and vertical downscaling, which reduces on-resistance (Ron) and, therefore, on-state losses [1]. The reduction of parasitic capacitances (Coss, Ciss) and gate charge is also highly important, since these quantities affect the transition time between on-state and offstate (and vice versa), which, in turn, impacts switching losses and switching frequency. Devices with higher switching frequencies also allow for downscaling of passive elements (e.g. inductors and capacitors) in power electronic circuits, reducing the overall module size further.

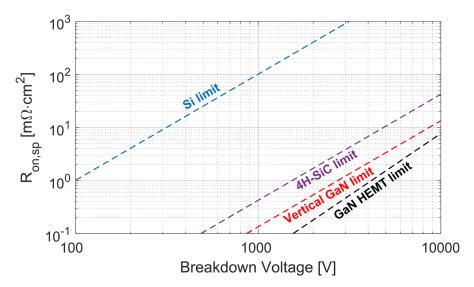

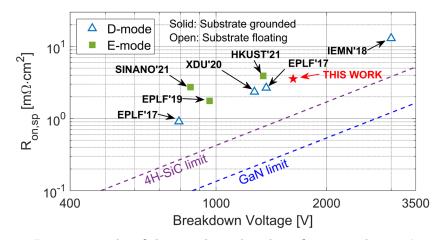

Si has been the most prevalent semiconductor since the onset of solid-state power conversion. However, the interest in wide bandgap semiconductors such as SiC and GaN has rapidly increased due to their high breakdown fields and high electron mobilities [2]. SiC power switching devices, including metal-oxide-semiconductor field-effect transistors (MOSFETs), junction FETs (JFETs), and insulated gate bipolar transistors (IGBTs), exhibit a smaller tradeoff between Ron and breakdown voltage (BV) compared to their Si counterparts (Figure 1.1). SiC IGBTs are typically suitable for power switching applications where the blocking voltage requirement is above 10 kV due to the smaller drift region thickness required for IGBTs compared to SiC MOSFETs [3]. These applications include high voltage transmission and

**Figure 1.1.** Ideal specific on-resistance for Si, 4H-SiC and GaN. The semiconductor properties of the respective materials were taken from [1], [2].

smart grids. On the other hand, MOSFETs tend to have better current handling capabilities at switching frequencies above 5 kHz [3]. Both MOSFETs and JFETs are more suitable for low voltage and medium-to-high frequency applications. In voltage classes up to 1200 V, SiC MOSFETs and JFETs are already commercially available [4]. These devices show lower switching and on-state losses compared to Si IGBTs to at least 100 kHz [5].

GaN-based semiconductors allow for the fabrication of power electronic devices with lower R<sub>on</sub> for a given breakdown voltage relative to their Si and SiC counterparts (Figure 1.1) [1], [6]. Furthermore, the high spontaneous and piezoelectric polarization in GaN and its alloy AlGaN can be utilized to form a two-dimensional electron gas (2DEG) at the interface of an AlGaN/GaN heterostructure. This, in turn, can be used for fabricating HEMTs, which exhibit high electron saturation velocities, high electron mobilities and high electron carrier concentrations [7]. Additionally, GaN HEMTs display lower parasitic capacitances, gate charge, and reverse recovery charge compared to conventional Si MOSFETs [8]–[11], and SiC MOSFETs [12]–[14] rated at, or below, 1200 V. This enables higher switching frequencies and reduces switching losses. In the first part of this work, power electronic GaN HEMTs operating above 1200 V are primarily studied.

Commercially available GaN-on-Si HEMTs typically operate in the 650 V and 1200 V voltage classes [15], [16]. Moreover, GaN-based HEMTs operating beyond 1200 V have been (and are still being) researched [17]–[20]. However, GaN-on-Si HEMTs are not without their disadvantages. The thermal and lattice mismatch between GaN and Si necessitates thick buffer layers to reduce the concentration of growth defects [2], [21]. Additionally, the buffer layer is typically doped with carbon or iron to suppress vertical leakage current [21]–[23], which is one of the limiting factors in GaN-on-Si high voltage HEMTs. An alternative to Si is semi-insulating (SI) SiC, which offers higher thermal conductivity, higher electrical resistivity, and a

lower lattice mismatch between SiC and GaN [2]. In GaN-on-SiC heterostructures, it is also common to grow highly resistive carbon or iron-doped buffers to reduce lateral leakage currents [24]–[26]. However, growing GaN with high carbon concentration leads to trapping states, which has a negative impact on dynamic onresistance (R<sub>on,dyn</sub>) and drain lag [24]–[26].

A new type of 'buffer-free' heterostructure deposited on a SI-SiC has been proposed [27], [28], which consists of a thin AlN nucleation layer, a thin unintentionally doped (UID) GaN layer, an AlGaN barrier, and a GaN capping layer. Together, they form a 2DEG with high electron confinement without needing any intentionally doped carbon buffer layer. Furthermore, the highly resistive SiC substrate effectively eliminates vertical leakage currents and breakdown at high voltages. This means that the high voltage capability and Ron,dyn are limited by the device processing, the quality of the AlN, GaN or AlGaN layers, or their interfaces. Processing parameters that can affect high voltage operation or Ron, dyn include source and gate-integrated field plates, the type of passivation, and the type of electrical isolation [19], [29]–[32]. However, to what extent these parameters impact the breakdown voltage,  $R_{on}$  and  $R_{on,dyn}$  in 'buffer-free' HEMTs are still relatively unexplored. In Chapter 2, different electrical isolations, SiNx passivation layers, and gate dielectrics are compared in terms of their impact on off-state leakage currents and breakdown voltages in 'buffer-free' HEMTs. In addition, a novel Ta-based ohmic contact metallization was employed on this type of heterostructure. This part of the work is used as a foundation for [Paper A-B].

GaN HEMTs have also played a major role in high power and high-frequency applications [33], [34]. In order to realize high-frequency operation, it is common to laterally downscale the transistor as much as possible to reduce losses and increase the current gain and power gain cut-off frequencies [35]. This involves gate length  $(L_g)$  reduction and minimization of the access regions. However, reducing  $L_g$  also entails more severe SCEs, which reduce gain, efficiency, and output power [35]. These effects give rise to DIBL, which is a negative shift of the  $V_{th}$  toward more negative values at high  $V_{ds}$ . DIBL is traditionally characterized by calculating the relative shift of two transfer curves at different values of  $V_{ds}$ . However, with this method it is difficult to track large, sudden changes in  $V_{th}$  with respect to  $V_{ds}$ .

In Chapter 3, an alternative technique will be presented in which  $V_{th}$  is measured for a large range of  $V_{ds}$  in a single measurement. From this measurement, it is possible to observe the evolution of DIBL as  $V_{ds}$  increases. This becomes useful when assessing a suitable bias range in HEMTs. This technique can also be applied to power switching HEMTs to optimize the gate length in terms of DIBL (at high voltages) and  $R_{on}$ . In this part of the thesis, the method is evaluated using HEMTs with short gate lengths and two types of epitaxial heterostructures. This is based on the work presented in [Paper C].

# Chapter 2

# 'Buffer-Free' GaN-on-SiC High Voltage HEMTs

The design goal of any power electronic HEMT is to maximize the off-state breakdown voltage while simultaneously minimizing  $R_{\text{on}}$ ,  $R_{\text{on,dyn}}$  and parasitic capacitances. One strategy for increasing the breakdown voltage is to scale up the component by increasing the gate-drain distance ( $L_{\text{gd}}$ ). In doing so, the access region increases in size, which leads to a higher  $R_{\text{on}}$  and, therefore, on-state losses. The lowest specific on-state resistance ( $R_{\text{on,sp}}$ ) in HEMTs for any given breakdown voltage follows the relation given by

$$R_{on,sp} = \frac{BV^2}{q\mu_n n_s E_{crit}^2} \tag{2.1}$$

where q,  $\mu_n$ ,  $n_s$ , and  $E_{crit}$  are the elementary charge, electron mobility, sheet carrier concentration, and critical electric field of GaN, respectively [1]. However, in a real device, there is a multitude of material growth and device processing parameters that can cause the  $R_{on,sp}$ -BV relation to deviate from the ideal relation in Equation 2.1. For instance, defects in the crystal structure, dopants, surface contaminants, and the quality of the dielectrics (and their interfaces) deposited on the III-nitride surface can negatively affect the device's breakdown voltage and the critical electric field of GaN. This can manifest as an elevated off-state leakage current, a dielectric breakdown, or a sudden current surge due to some unintentionally added leakage path in the III-nitride heterostructure.

In addition, trapping-related effects, which negatively impact the dynamic performance, are highly influenced by the quality of the heterostructure and the dielectrics deposited on it. During off-state stress, electrons can start to occupy acceptor-like states in the vicinity of the 2DEG at the heterostructure interfaces, in the buffer, or at the III-nitride surface. These traps can have a longer de-trapping time than the off-to-on state switching time. As a result, the 2DEG remains

partially depleted during the on-state, which reduces the on-state current. Therefore, optimizing both GaN material growth and device processing parameters is essential to reduce these unwanted effects.

#### Substrate Alternatives

The type of substrate on which the III-nitride heterostructure is grown strongly impacts the resulting semiconductor properties. Discrepancies in lattice constant and thermal expansion coefficients can give rise to dislocations, which can negatively affect electron mobility and maximum drain current in HEMTs [36], [37]. In addition, the bandgap and doping concentrations of the substrate affect the number of charge carriers, which, in turn, influences vertical leakage currents. Table 2.1 summarizes the properties of common substrates for GaN.

Si substrates are currently the most popular alternative for power electronic GaN HEMTs due to their low cost [38], [39]. However, the small bandgap of Si results in a high intrinsic carrier concentration and, therefore, a low resistivity. This leads to high vertical leakage currents during high voltage operations. Moreover, Si substrates typically require a strain relaxation layer to prevent large wafer bowing and cracks in the GaN epitaxial layers [40].

Sapphire (Al<sub>2</sub>O<sub>3</sub>) has traditionally been utilized for GaN growth in solid-state lighting applications due to its low cost, high-temperature stability, and high electrical resistivity [41]. However, the poor thermal conductivity and large lattice mismatch with GaN make sapphire less suitable for power switching HEMTs.

SiC and GaN substrates have emerged as two alternatives to Si and sapphire. Both offer a high electrical resistivity due to their large bandgaps, which reduce vertical off-state currents. The advantage of GaN substrates is that they do not require any nucleation layer to promote GaN growth, which removes any additional thermal boundary resistances between the III-nitride epi and the substrate. Additionally, GaN-on-GaN homoepitaxy can suppress dislocation densities below 10<sup>5</sup> [43], making it a preferred choice for lateral GaN devices. However, low growth rates currently limit the large-scale production of SI-GaN wafers, making it the most expensive and least accessible substrate among the four presented in Table 2.1.

Table 2.1. Material properties of substrates used for GaN HEMTs [2], [42].

| Parameter                     | Si   | Sapphire | 4H-SiC | GaN     |

|-------------------------------|------|----------|--------|---------|

| Bandgap (eV)                  | 1.12 | 8.1-8.6  | 3.26   | 3.39    |

| Thermal conductivity (W/cm·K) | 1.5  | 0.23     | 3.8    | 1.3 / 3 |

| Lattice mismatch (%)          | -17  | -16      | +3.5   | None    |

| Thermal mismatch (%)          | +116 | -25      | +33    | None    |

SiC substrates combine a high thermal conductivity with a low lattice mismatch to GaN. This makes SiC an excellent choice for both high power microwave HEMTs and power electronic HEMTs, as it allows for improved epitaxial crystal quality and heat dissipation. Furthermore, the increasing demand for GaN-on-SiC microwave HEMTs and SiC power devices has incentivized research into bulk n-type SiC and SI-SiC growth. Thus, GaN-on-SiC could become an alternative to GaN-on-Si for future power switching applications.

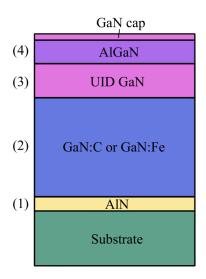

#### Conventional Buffer Designs

AlGaN/GaN-based heterostructures grown on foreign substrates mainly consist of four layers (Figure 2.1): (1) an AlN nucleation layer, (2) a thick GaN buffer layer, (3) a UID-GaN layer, and (4) an AlGaN barrier layer to form the 2DEG. A strain relief layer is sometimes also grown after the nucleation layer to reduce the stress in the GaN buffer.

The purpose of the nucleation layer is to facilitate the formation of GaN crystals and allow them to promote lateral growth [44]. This layer also reduces the dislocation density significantly compared to GaN grown directly onto a foreign substrate [45]. The thick buffer layer grown on top of the nucleation layer serves two functions: (a) to further reduce the impact of dislocations and other growth defects in the vicinity of the active areas [21], and (b) to reduce vertical leakage currents (mainly applicable for conductive substrates). In addition to being detrimental to the on-state performance of the HEMT, dislocations can serve as vertical leakage paths during high voltage operation [46]. When the III-nitride heterostructure is grown on a conductive substrate, these additional leakage paths can lead to premature breakdown.

When the buffer layer is grown using metalorganic chemical vapor deposition (MOCVD) or hydride vapor phase epitaxy (HVPE), O, Si and N vacancies are unintentionally introduced into the crystal structure. These act as donor states, which increases the electron carrier concentration and reduces the resistivity of the buffer layer [47]–[49]. As a consequence, the drain-source current can be canalized under the depleted channel region during high off-state drain biases. In order to counteract this effect, it is common to intentionally add deep-level acceptor states to compensate the donors in the crystal structure. This leads to a higher resistivity, which improves the electron confinement and reduces vertical leakage currents. The two most commonly used acceptors in GaN HEMT heterostructures are C and Fe.

Iron is typically incorporated into GaN by introducing ferrocene in MOCVD [22]. The Fe atoms predominantly substitute Ga (i.e. Fe<sub>Ga</sub>) due to its low formation energy [50], which leads to the creation of an acceptor level 0.5-0.7 eV below the conduction band edge (E<sub>c</sub>) [51], [52]. Fe-doped GaN provides good insulation with sheet resistances as high as  $7\cdot10^9$   $\Omega\cdot$ cm at a doping concentration of  $1.3\cdot10^{19}$  cm<sup>-3</sup> [22]. Furthermore, it has also been shown that GaN can reach lateral breakdown fields up to 2 MV/cm at high Fe-concentrations of  $4\cdot10^{20}$  cm<sup>-3</sup> [53]. However, the surface morphology can deteriorate at concentrations above  $10^{20}$  cm<sup>-3</sup> [22]. Iron-related traps also tend to cause  $R_{on,dyn}$  dispersion. Hilt et al. demonstrated that  $R_{on,dyn}$  increases more than twice the static value when an off-state drain bias of

**Figure 2.1.** A conventional AlGaN/GaN heterostructure with a thick C-doped or Fe-doped buffer layer.

600 V is applied [54], which is an unacceptably high increase of R<sub>on,dyn</sub>. However, Würfl et al. showed that HEMTs with Fe-doped buffers display lower R<sub>on,dyn</sub> dispersion than HEMTs with purely C-doped buffers [26].

Carbon is usually incorporated into GaN by changing the growth conditions in the MOCVD reactor [55]. However, increasing the C concentration using this approach can lead to poorer crystal quality by introducing more extended defects. A less common technique is to introduce a separate carbon precursor gas, such as propane or methane, together with the Ga and N precursor [56]. The carbon atoms substitute both Ga sites ( $C_{Ga}$ ) and nitrogen sites ( $C_N$ ) in the GaN crystal. As a result,  $C_N$  forms a deep acceptor level with ionization energy of 0.9 eV above the valance band edge ( $E_V$ ) [57], and  $C_{Ga}$  forms a shallow donor level. At high carbon concentrations, the semiconductor becomes semi-insulating since the  $C_N$  acceptors compensate the  $C_{Ga}$  donors and other donors in the crystal. Carbon doping is typically preferred over Fe doping in power switching HEMTs due to the high ionization energy of  $C_N$ , which leads to a higher resistivity and breakdown fields [26].

Carbon concentrations above  $10^{19}$  cm<sup>-3</sup> are typically needed to achieve sufficiently good isolation for power electronic devices. This enables vertical breakdown fields up to 2.3 MV/cm [21]. On the other hand, the GaN buffer becomes p-type at high concentrations due to the acceptor-like nature of  $C_N$  [58]. The p-n junction formed between the 2DEG and the buffer leads to a greater  $R_{on,dyn}$  dispersion at high drain biases [58]. Eldad et al. reported a large drain current lag for HEMTs with a highly C-doped GaN buffer on SI-SiC at a small drain quiescent of 30 V [25]. A high drain lag dispersion has been seen in other GaN-on-SiC HEMTs with a high C doping concentration as well [24]. Hilt et al. and Würlf et al. both demonstrated that C-doped buffers caused  $R_{on,dyn}$  to increase more than two times above the static values

[26], [59]. However, introducing an AlGaN back-barrier between the UID-GaN and the C-doped buffer layer can suppress the R<sub>on,dyn</sub> dispersion caused by the C acceptors, while maintaining a high lateral breakdown strength [26]. It has also been suggested that R<sub>on,dyn</sub> can be reduced by employing a stepped carbon profile instead of a sharp transition to the highly C-doped buffer [60]. Moreover, Uren et al. showed that the R<sub>on,dyn</sub> dispersion can be lessened by intentionally forming dislocation-induced leakage paths between the 2DEG and the traps in the buffer [58]. This allows trapped electrons to charge/discharge from the buffer layer, preventing charge build-up underneath the 2DEG.

In conclusion, incorporating high concentrations of Fe or C in the buffer layer to improve isolation is not without its complications. The growth process required to achieve high doping concentrations can impair the crystal quality. Additionally, the dopant atoms introduce trapping effects, necessitating careful control of the doping concentration, doping profile, or the concentration of dislocations to suppress  $R_{\rm on,dyn}$  while maintaining good isolation. A heterostructure that can combine high isolation without introducing deep-level traps would be preferable to the conventional heterostructures.

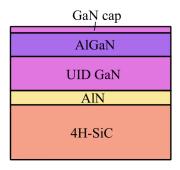

#### The 'Buffer-Free' Heterostructure

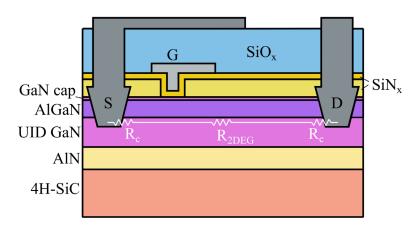

The negative effects caused by C or Fe can be avoided completely using a novel 'buffer-free' GaN-on-SiC growth technique. With this method, an AlN nucleation layer is grown on top of two intermediate atomic layers consisting of (from the SiC substrate surface) (Al<sub>1/3</sub>Si<sub>2/3</sub>)<sub>2/3+x</sub>N and (Al<sub>2/3</sub>Si<sub>1/3</sub>)<sub>1-x</sub>N [27]. The out-of-plane compositional gradient and in-plane vacancy ordering of these two layers enable a high crystal quality in the AlN layer. A UID-GaN is then grown on top of the AlN with low dislocation density (~10<sup>8</sup> cm<sup>-2</sup>) and C concentrations at 3·10<sup>16</sup> cm<sup>-3</sup>, without any intermediate resistive buffer layer (Figure 2.2). Removing the thick buffer layer from the heterostructure design also entails a lower thermal resistance between the active region and the SiC substrate, improving the heat dissipation. The thin UID-GaN layer grown on top of the AlN and SiC substrate results in a high electron confinement without additional deep-level traps added to the heterostructure [61]. Furthermore, the confinement can be improved by reducing the thickness of the

**Figure 2.2.** A 'buffer-free' heterostructure grown on 4H-SiC. Layer thicknesses are not to scale.

GaN layer. This prevents lateral leakage currents under the depleted channel region during high voltage operations. Moreover, the SiC provides good vertical isolation, suppressing leakage current and preventing vertical breakdown.

#### Off-State Breakdown Characterization

The breakdown voltage of a semiconductor device is defined as the voltage at which the impact ionization rate of charge carriers approaches infinity (avalanche breakdown), which leads to a rapid increase in current. However, it is more convenient for measurements to set an upper limit to the off-state current(s). The voltage at which this current criterion is exceeded at any terminal is defined as the breakdown voltage. This typically occurs through (a) a hard (or destructive) breakdown, where a sudden current surge exceeds the breakdown current criterion and destroys the device in the process, (b) a soft (or non-destructive) breakdown caused by a current surge through some unintentional current path, and (c) a soft (or non-destructive) breakdown where a raised leakage current exceeds the current criterion. In literature, the two commonly used breakdown criteria are 1 mA/mm, and 1 µA/mm for HEMTs [19], [20], [62]–[65]. In [Paper A], the lower criterion was employed to compare the 'buffer-free' HEMTs with HEMTs found in the literature. However, in this thesis, the 1 mA/mm current criterion is primarily utilized to explore the impact of different processing parameters on the catastrophic breakdown, which requires a higher tolerance for off-state current in some devices.

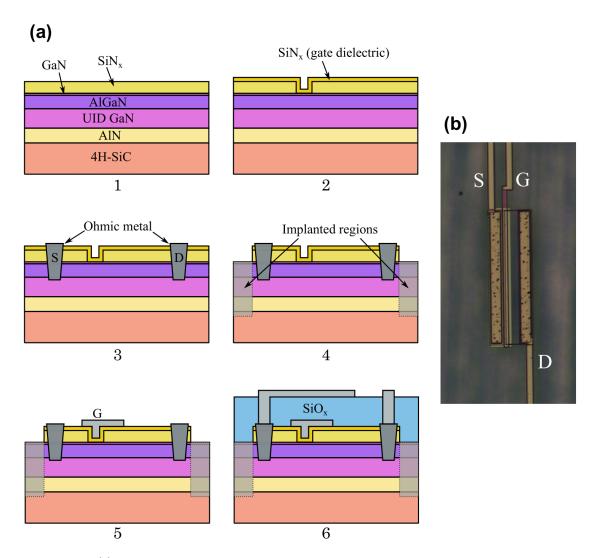

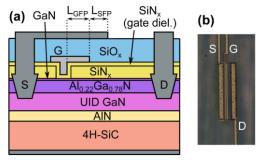

### 2.1 Device Fabrication

MISHEMTs were fabricated on a 'buffer-free' III-nitride heterostructure. The general outline of the device fabrication process will be presented in this subsection. However, individual process variations will be presented in subsections where it becomes relevant.

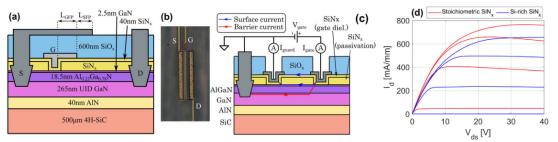

The 'buffer-free' heterostructure was grown using MOCVD by SweGaN AB, utilizing their QuanFINE® concept. The III-nitride stack consists of (from bottom to top layer) a 43 nm AlN nucleation layer, a 265 nm GaN layer, a 18.5 nm Al<sub>0.22</sub>Ga<sub>0.78</sub>N layer, and a 2.5 nm GaN capping layer (Figure 2.3a). The substrate is a 500  $\mu$ m thick high purity SI-SiC. The mobility and carrier concentrations were measured to 2018 cm²/Vs and  $7.1\cdot10^{12}$  cm² using contactless Hall measurement.

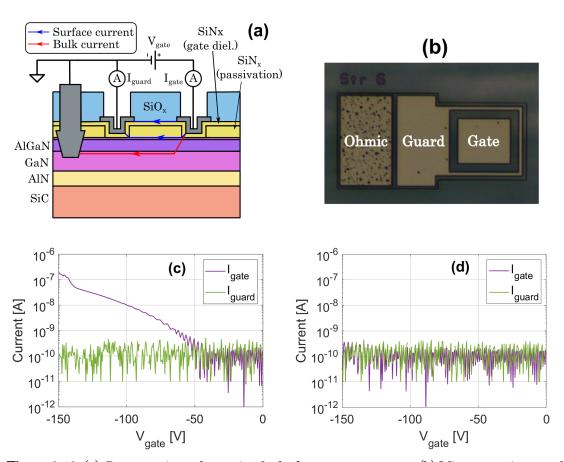

A schematic of the fabrication process flow and a top view microscope image of a completed MISHEMT can be seen in Figure 2.3a, and Figure 2.3b, respectively. The general process flow can be divided into six steps and are as follows:

- 1. The sample is immersed in (NH<sub>4</sub>)<sub>2</sub>OH:H<sub>2</sub>O 1:10 (SC1) and HCl:H<sub>2</sub>O 1:10 (SC2) to remove organic and metallic contaminants, respectively. Afterwards, a 100-177 nm SiN<sub>x</sub> layer is grown using LPCVD. Variations in the SiN<sub>x</sub> stoichiometry will be presented in section 2.4 and is a part of [Paper B].

- 2. A gate recess is defined using photolithography and NF<sub>3</sub>-based dry etching to remove  $SiN_x$  in the developed gate lithography openings. This step defines the gate length of the HEMT. Gate lengths of 2-4  $\mu$ m were included in the device design. An additional standard cleaning (SC1 and SC2) process is

- implemented, followed by an LPCVD deposition of a  $\sim 40$  nm stoichiometric  $SiN_x$ , which acts as a gate insulator.

- 3. Recess-etched ohmic contacts is formed. A Ta/Al/Ta metal stack is deposited using a physical vapor deposition (PVD) system with the same resist etch mask preserved (self-aligned process). A more detailed description of the ohmic process will be presented in section 2.2. This step also defines the gate-source distance ( $L_{\rm gs}$ ) and  $L_{\rm gd}$ . In this work, all HEMTs have a  $L_{\rm gs}$  of 2  $\mu$ m and a  $L_{\rm gd}$  between 12  $\mu$ m and 25  $\mu$ m.

- 4. The active area is defined. A thick photoresist is spun, baked, exposed and developed. After development, the resist protects the ohmic metal and the source-drain regions. The SiN<sub>x</sub> gate dielectric and passivation layer is dryetched using an NF<sub>3</sub>-based plasma, exposing the GaN cap layer. Afterwards, nitrogen implantation is employed. This act to electrically isolate the area surrounding the source, gate and drain contacts. Additional information on nitrogen implantation process will be presented in section 2.3.

- 5. A metal stack consisting of Ni/Pt/Au/Ti is deposited in the gate recess using a PVD system. In the same lithography step, a gate-integrated field plate is included. The lengths of the field plate ( $L_{\rm gfp}$ ) were designed to 0.75-5  $\mu m$  in this work.

- 6. A 600 nm SiO<sub>x</sub> layer is deposited using a plasma-enhanced chemical vapor deposition (PECVD) system. Afterwards, dielectric vias at the drain and source contacts are dry etched using a CHF<sub>3</sub>-based plasma. Lastly, a Ti/Au source connected field plate was deposited. Source field plate lengths (L<sub>sfp</sub>) between 0 μm and 5 μm were designed.

Results for mesa-isolated HEMTs are also presented in this thesis. When this isolation technique is employed, the  $SiN_x$  gate dielectric and passivation layers are deposited after the mesa etch to prevent the gate metal from directly contacting the sidewall formed by the etch. The ohmic metal is deposited after the mesa isolation.

**Figure 2.3.** (a) Schematic of the fabrication process of MISHEMTs on a 'buffer-free' heterostructure. (b) A top view microscope image of a MISHEMT.

### 2.2 Ohmic Contacts

A power electronic switch dissipates power when it (a) transitions between its two operating states (switching losses) and (b) when it's conducting current (onstate losses). The on-state losses depend on the series resistances in the channel and between the semiconductor and the metal (Equation 2.2).

$$P_{on} = D \cdot I_{on}^{2} \cdot R_{on} = D \cdot I_{on}^{2} \cdot (R_{2DEG} + 2R_{c})$$

(2.2)

where D is the duty cycle,  $I_{on}$  is the on-state current,  $R_{\rm 2DEG}$  is the resistance intrinsic to the 2DEG, and  $R_c$  is the contact resistance (Figure 2.4). The on-state resistance is primarily reduced by increasing the electron mobility in the channel, increasing the 2DEG carrier concentration, or by downscaling the component. However, achieving good ohmic contacts is essential for the transistor to function properly. Rectifying contacts can cause  $R_c$  to become the dominating term in Equation 2.2, resulting in large on-state power dissipation. This becomes even more crucial in low voltage classes, where 10-15% of the total on-resistance consists of the contact resistances from the source and drain contacts.

In GaN devices, it is more difficult to achieve contact resistances in the same range as Si due to the large bandgap of GaN [66]. Ti/Al-based ohmic contact metallization deposited directly on the barrier (or capping layer) surface is the most common approach for AlGaN/GaN HEMTs [67]–[69]. However, this technique requires post-deposition annealing temperatures of 700-890 °C [69], making it less suitable to use in conjuction with temperature-sensitive processing steps, such as implantation isolation and after deposition of Schottky gate metals.

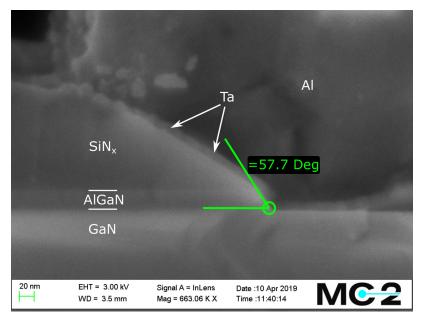

In the development of the MISHEMTs for [Paper A-B], a Ta/Al/Ta metallization technique was used [70], [71]. Prior to metal deposition, a recess etch is performed to remove the AlGaN barrier (Figure 2.4). This enables low R<sub>c</sub> using post-deposition annealing temperatures of 550-575 °C. Ta-based metallization also provides good surface morphology, sharp edge acuity and stability over time [71]. In addition,

**Figure 2.4.** A schematic of a MISHEMT with all on-state resistances included. Lengths and layer thicknesses are not to scale.

**Figure 2.5.** A cross-section scanning electron microscope image of a recess-etched Ta-based ohmic contact.

complications related to purple/white plague is avoided by excluding Au from the metal stack.

In this Ta-based metallization method, the photoresist acts as an etching mask and a lift-off resist for the metal (self-aligned process). The recess etch creates an inclined sidewall that facilitates contact between the bottom Ta layer and the 2DEG (Figure 2.5). After metal deposition, a Schottky barrier is naturally formed at the metal-semiconductor interface. This results in highly resistive, rectifying contacts. The rectifying behavior is effectively suppressed by annealing the sample at a sufficiently high temperature. This is thought to cause an out-diffusion of nitrogen atoms in the direct vicinity of the Ta/Al, which then forms TaN and AlN [70], [71]. The nitrogen vacancies left behind as a consequence of the migrating nitrogen atoms act as a thin, highly doped n-type layer. This, in turn, reduces the extent of the depletion region formed by the Schottky contact, which promotes electron tunnelling through the Schottky barrier. The elevated electron tunnelling results in an ohmic behaviour with low contact resistance. The relation between contact resistance and doping concentration in the semiconductor adjacent to the metal is given by

$$R_c \propto e^{\frac{\phi_B}{E_{00}}}, \qquad E_{00} \propto \sqrt{N_d}$$

(2.3)

where  $\phi_B$  is the Schottky barrier height, and  $N_d$  is the doping concentration close to the metal. Metals with low work functions are therefore preferable since they result in lower barrier heights. Ta and Ti exhibits work functions of 4.25 eV and 3.95 eV, respectively [72]. According to Uryu et al., the ohmic contact formation is not caused by a high donor density at the GaN surface [73]. Instead, the strain induced in the AlGaN barrier caused by the Ta/Al/Ta metal stack results in a change of the

polarization in the barrier, which leads to an effective doping concentration. This polarization-induced doping consequently increases the field emission between the metal and semiconductor, leading to a reduction of the contact resistance.

The fabrication of recess-etched Ta-based ohmic contacts started after the deposition of SiN<sub>x</sub> passivation and gate dielectric. Next, an AZ5214 image reversal photoresist was spun, soft-baked, exposed, reversal baked, flood exposed and lastly developed. The resist profile determines the inclination of the sidewall after the dry etch recess [70]. An Oxford Plasmalab 100 ICP/RIE system was used for dry etching the SiN<sub>x</sub> passivation in a fluorine-based plasma. The AlGaN barrier and ~10 nm of the UID-GaN layer were etched in a chlorine-based plasma. After the recess etch, the samples were immersed in a buffered oxide etch (BOE:H<sub>2</sub>O 1:10) for 4 min, and a hydrochloric acid etch (HCl:H<sub>2</sub>O 1:10) for 1 min prior to metal deposition. A metal stack consisting of 20/280/20 nm Ta/Al/Ta was deposited using a Lesker Spectros evaporator. Lastly, the ohmic contacts were annealed in an AccuThermal AW610 RTP system. The temperature of each annealing run was kept at 575 °C, and the annealing time varied between 1-8 min. All annealing steps were performed in a nitrogen ambient.

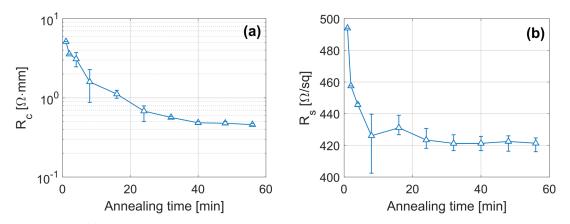

Contact resistances and sheet resistances were extracted using the transfer length method (TLM). With this method, the total resistance is calculated between two ohmic contacts with varying contact separations. The two components comprising the total resistance can be extracted through a linear extrapolation using the expression

$$R_{tot} = R_s L + 2R_c \qquad [\Omega \cdot mm] \tag{2.4}$$

where  $R_{tot}$  is the total resistance,  $R_s$  is the sheet resistance, and L is the contact separation. Both  $R_s$  and  $R_c$  were obtained after each annealing run. The annealing and TLM measurements were repeated for an aggregated time of 50-70 min. The contact resistance decreases and approaches a value of 0.44-0.47  $\Omega$ ·mm as the total annealing time is increased (Figure 2.6a). The sheet resistance shows a similar trend and reaches a value of 421  $\Omega$ /sq (Figure 2.6b), indicating that it is not negatively affected by the long annealing times. The contact resistance presented here is higher than what has been reported for other Ta-based, recess-etched, ohmic contacts (0.21-0.36  $\Omega$ ·mm) [70], which means further optimization of Ta layer thickness, annealing temperature, recess depth, and recess sidewall angle is needed. Nevertheless, Ta-based contacts display lower contact resistance compared to most other Ti/Al-based contacts used for high voltage AlGaN/GaN HEMTs in literature (Table 2.2).

**Figure 2.6.** (a) Contact resistance, and (b) sheet resistance as functions of total annealing time in the left and right figures, respectively.

Table 2.2. Examples of ohmic contacts for high voltage AlGaN/GaN HEMTs in literature.

| Reference | Metal stack    | Annealing temperature [°C] | $R_{c}\left[\Omega\cdot mm\right]$ |

|-----------|----------------|----------------------------|------------------------------------|

| This work | Ta/Al/Ta       | 575                        | 0.44-0.47                          |

| [17]      | Ti/Al/Ni/Au    | N/A                        | ~1                                 |

| [65]      | Ti/Al/Ni/Au    | 875                        | 1.4                                |

| [74]      | Si/Ti/Al/Mo/Au | 800                        | 0.5                                |

| [75]      | Ti/Al/W        | N/A                        | 0.93                               |

| [76]      | Ti/Al/Ni/Au    | 890                        | 1.12                               |

| [77]      | Ti/Al/Ni/Au    | 875                        | 0.35                               |

| [78]      | Ti/Al/Ni/Au    | 870                        | 0.6                                |

### 2.3 Electrical Isolation

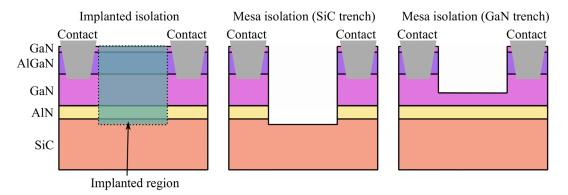

It is necessary to electrically isolate the area surrounding the active part of the device so that the gate can maintain control of the off-state current. Moreover, the critical electric field of the isolated regions must be as high as possible to prevent impact ionization and catastrophic failure at the edge of the gate contact. In general, there are two ways to achieve electrical isolation: (a) mesa isolation, or (b) implantation isolation. In this work, both isolation techniques have been studied for buffer-free' heterostructures.

The mesa isolation technique lowers the lateral conductivity by physically removing the AlGaN/GaN heterostructure and, therefore, the 2DEG. The resistivity is then determined by the bulk resistivity in the etched layer. In the 'buffer-free' heterostructure, the mesa isolation can be subdivided into two categories: (i) a trench that is etched down into the thin UID-GaN layer, and (ii) a trench that is etched down to the SiC substrate. The purpose of subdividing the two mesa structures is to characterize the electrical isolation of the UID-GaN and SI-SiC separately for this epitaxial design. Both mesa isolation types were tested. The mesa structures were formed with an Oxford Plasmalab 100 ICP/RIE system. A Cl<sub>2</sub>/Ar-plasma with a platen forward power of 100 W and an ICP power of 50 W etched the AlGaN, GaN and AlN layers. The depth of the GaN-mesa etch was approximately 180 nm, while the SiC-mesa was above 330 nm.

The main advantage of ion implantation is that a planar surface is maintained, which facilitates device processing and improves repeatability. Both light and heavy elements can provide a high resistivity by introducing point defects as a result of implantation damage, or through chemical reaction with the crystal atoms [79]. These defects and ions act as trapping centers, which compensate any preexisting donors in the crystal. A wide variety of ion species have been reported, such as H<sup>+</sup>,

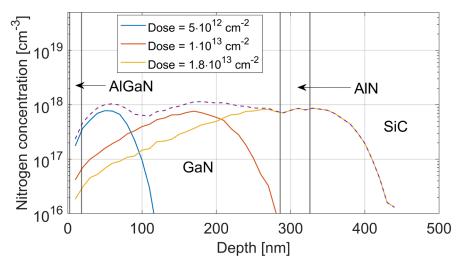

**Figure 2.7.** SRIM-calculated nitrogen implantation profiles in a buffer-free AlGaN/GaN heterostructure. The dashed purple line is the net concentration of nitrogen ions.

He<sup>+</sup>, N<sup>+</sup>, Kr<sup>+</sup>, Ar<sup>+</sup> and O<sup>+</sup> [80]–[83]. However, N<sup>+</sup>-implanted GaN can maintain a stable resistivity at temperatures up to at least 600 °C, making it preferable over other types of ion species [81], [84].

In this study, three N<sup>+</sup> implantation profiles were used. The SiN<sub>x</sub> passivation and SiN<sub>x</sub> gate dielectric films were deposited prior to implantation due to the high temperatures required ( $\geq 770$  °C) for LPCVD deposition. The N<sup>+</sup> implantation profiles were determined before implantation using the "Stopping and Range of Ions in Matter" (SRIM) software [85]. Three implantations were required to completely cover the depth of the AlGaN barrier and GaN channel with nitrogen atoms. The energy and doses for the three implantations used were 30 keV and  $5\cdot10^{12}$  cm<sup>-2</sup>, 100 keV and  $1\cdot10^{13}$  cm<sup>-2</sup>, 180 keV and  $1.8\cdot10^{13}$  cm<sup>-2</sup>, respectively. Their respective implantation profile can be seen in Figure 2.7 together with the total concentration of nitrogen ions.

#### 2.3.1 Two-Terminal Breakdown

The measurement structures to test the three different isolation techniques consists of two separated ohmic contacts (Figure 2.8), with distances between the contacts varying from 5-25 µm. The area between the contacts is isolated using N<sup>+</sup> implantation or mesa isolation. A voltage is applied between the two contacts and is swept from 0 V up to the maximum voltage of 3 kV with a step of 2 V. In the following results, only the destructive breakdown of the device has been considered.

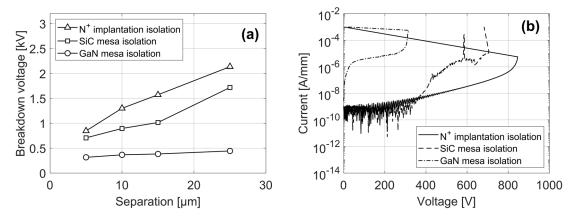

In Figure 2.9a, the breakdown voltage is displayed for contact separations between 5-25 µm for the three isolation techniques. The SiC trench isolation provides superior isolation compared to the shallow GaN trench isolation. Although GaN has a larger bandgap and a higher breakdown field compared to SiC in theory, it is likely that the lower breakdown voltages seen for the GaN trench isolation is due to the incorporation of donor-like impurities such as O or N-vacancies during the MOCVD growth. This consequently leads to a lower resistivity, which also explains why the leakage current is higher for the GaN trench samples (Figure 2.9b). Moreover, surface defects formed during the Cl-based dry etching could contribute more to the elevated leakage current in the GaN mesa isolation sample [86].

**Figure 2.8.** Schematic of implantation isolation and mesa isolation test structures. Dimensions are not to scale.

**Figure 2.9.** (a) Destructive breakdown voltage for mesa and nitrogen implantation isolation structures with separations between 5  $\mu$ m and 25  $\mu$ m. (b) Current-voltage characteristics of an isolation structure with a 5  $\mu$ m separation for mesa and nitrogen implantation isolation.

The planar isolation structures with implanted N<sup>+</sup> tended to have the highest breakdown voltages and the lowest leakage currents for all contact separations. Both the N<sup>+</sup>-implanted sample and the SiC-etched mesa isolation sample can suppress the leakage current to sub-nA/mm levels under biases of 350-700 V (depending on the separation). However, at higher voltages, the leakage increases by at least two orders of magnitude for the SiC-etched mesa isolation, which means that the SiC substrate is less resistive and has a lower breakdown field than implanted GaN. Also, the electric field tends to concentrate at the corners of the mesa trench [19], leading to a lower breakdown due to the smaller bandgap of SiC. By contrast, in the planar isolation structures, the peak electric field tends to concentrate at the edge of the ohmic contacts, where the properties of the implanted GaN limit the breakdown voltage. Similar to the GaN trench isolation, the Cl<sub>2</sub>/Ar plasma may have affected the SiC surface by introducing additional leakage paths at the surface. For these reasons, the highest breakdown voltage for the SiC trench isolation sample is limited to ~1700 V at 25 µm. On the other hand, the N+implantation can sustain voltages up to ~2100 V, making it more suitable for high voltage HEMTs.

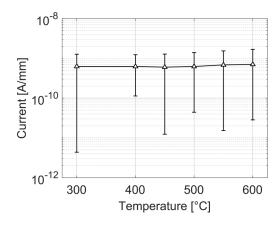

The N<sup>+</sup>-implanted sample was intentionally annealed using an AccuThermal AW610 rapid thermal processing (RTP) system to test its temperature stability. The sample was annealed at six different temperatures in the 300-600 °C range for 10 min each. The average leakage current between 150 V and 200 V for a 5  $\mu$ m contact separation is shown in Figure 2.10. No significant change in leakage current can be observed. The current remains at the nA/mm current level up to 600 °C, which is consistent with what has been reported elsewhere [81], [84].

**Figure 2.10.** Leakage current through the nitrogen implanted GaN sample between 150 V and 200 V (errorbars indicate variation in noise) after annealing the sample at 300-600 °C. The separation between the contacts is  $5 \, \mu m$ .

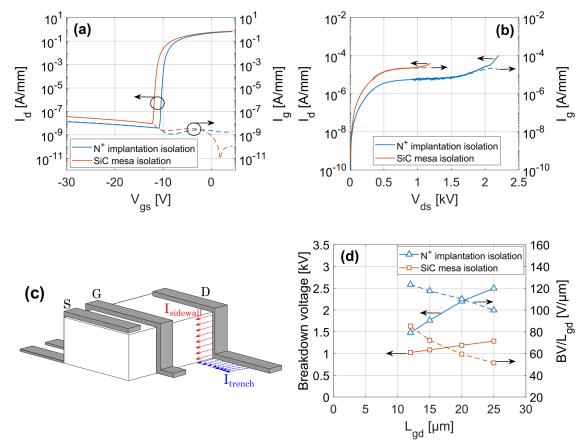

#### 2.3.2 Three-Terminal Breakdown

In this section, MISHEMTs with mesa isolation and  $N^+$  implantation isolation are compared. The results presented in the figures in this section are measured on MISHEMTs with a Si-rich LPCVD SiN<sub>x</sub> passivation and L<sub>g</sub>, L<sub>gd</sub>, L<sub>gfp</sub> and L<sub>sfp</sub> of 4  $\mu$ m, 12-25  $\mu$ m, 0.75  $\mu$ m, 0  $\mu$ m, respectively.

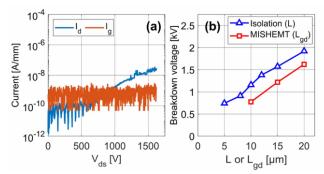

In Figure 2.11a, the subthreshold characteristics measured at  $V_{\rm ds}$  = 40 V are shown for the samples with SiC trench isolation and N<sup>+</sup> implantation isolation. The off-state drain and gate leakage current in the SiC trench isolation is higher by a factor of 2-3. However, at high  $V_{\rm ds}$ 's, the difference increases, and the leakage currents are higher by up to a factor of 6 (Figure 2.11b). In addition, catastrophic breakdown occurs at 1187 V and 2201 V in MISHEMTs with mesa isolation and N<sup>+</sup> implantation, respectively ( $L_{\rm gd}$  = 20  $\mu$ m in both devices). This shows that the N<sup>+</sup> implantation isolation is superior to SiC in limiting off-state leakage currents and increasing the maximum destructive breakdown. Moreover, damage formed by the Cl<sub>2</sub>/Ar etch could have created extra leakage paths along the mesa sidewall or at the SiC trench (Figure 2.11c). Etch-induced leakage paths have been observed in both GaN diodes and in AlGaN/GaN HEMTs [87]–[89]. For these reasons, N<sup>+</sup> implantation was used instead of mesa isolation when fabricating devices for [Paper A-B].

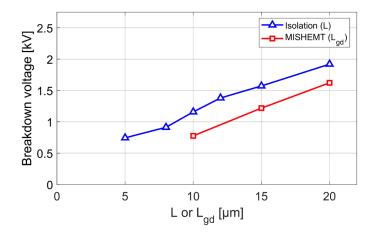

Breakdown voltages of MISHEMTs and isolation structures with varying  $L_{\rm gd}$  / contact separation for SiC trench isolation and N+ implantation isolation can be seen in Figure 2.11d. Overall, MISHEMTs with N+ implantation display higher off-state breakdown voltages for all  $L_{\rm gd}$  compared to SiC mesa isolation. A three-terminal breakdown between 1480 V and 2496 V was achieved for  $L_{\rm gd}$  = 12-25  $\mu m$ , corresponding to breakdown fields (BV/Lgd) between 123 V/ $\mu m$  and 0.98 V/ $\mu m$ . The SiC isolation limits the two-terminal and three-terminal breakdown, where breakdown fields below 80 V/ $\mu m$  could be obtained. Similar to the N+ implantation devices, the breakdown field tend to decrease with increasing  $L_{\rm gd}$ . Furthermore, the

**Figure 2.11.** (a) Subthreshold characteristics MISHEMTs with a SiC mesa isolation and N<sup>+</sup> implantation isolation. (b) Off-state breakdown characteristics for MISHEMTs with a SiC trench isolation and N<sup>+</sup> implantation isolation and  $L_{\rm gd} = 20~\mu m$ . (c) Schematic displaying potential leakage paths in a MISHEMT with mesa isolation. (d) Off-state destructive breakdown voltage and breakdown field of MISHEMTs with N<sup>+</sup> implantation and SiC mesa isolation with different  $L_{\rm gd}$ .

difference in breakdown voltage for the SiC-etched MISHEMTs and the SiC-etched isolation structures is less than 100 V for most  $L_{\rm gd}$ /contact separations. This indicates the same type of breakdown mechanism, which is probably caused by current paths formed at the mesa sidewall, at the SiC trench surface or in the SiC bulk material.

To conclude, N<sup>+</sup> implantation is the best technique to improve isolation, increase the breakdown field, and reduce the number of unintentional leakage paths induced by etching or other device processing steps. Additionally, the breakdown field could be further improved by increasing the implantation dose. Sun et al. used a higher N<sup>+</sup> dose for HEMTs with a C-doped buffer and could achieve a breakdown voltage of 1.8 kV at  $L_{\rm gd}$  = 10  $\mu$ m, but was limited to voltages below 2 kV due to vertical leakage current through the GaN buffer and Si substrate [19]. The 'buffer-free' HEMTs used in this work is not limited by vertical leakage currents. Therefore, it could be possible to obtain breakdown voltages above 2 kV with an  $L_{\rm gd}$  above 12  $\mu$ m. Although N<sup>+</sup> implantation can significantly improve the insulating properties of

GaN, leakage currents in the MISHEMT are two orders of magnitude higher than the two-terminal measurements. This means that the passivation layers, gate dielectrics and field plate need to be improved to reduce leakage currents and increase the breakdown voltage futher.

## 2.4 Passivation Layer

The passivation layer in GaN-based HEMTs has two major functions: (a) to protect the barrier layer (e.g. AlGaN) or capping layer surface from damage and adsorption of contaminants during the device processing, and (b) to reduce negative surface-related trapping effects [90], [91]. The choice of passivation is also important since different passivation affects the barrier surface – and therefore the electron transport properties – differently. One of the most popular passivation layers is SiN<sub>x</sub> due to its positive effects on channel carrier concentration and suppression of interface states and surface traps [92]–[95].

In general, SiN<sub>x</sub> is deposited using LPCVD, PECVD, or *in situ* MOCVD. The choice of deposition techniques has a large impact on device performance. LPCVD-SiN<sub>x</sub> displays a lower concentration of surface traps, higher interface quality, and lower leakage currents than PECVD-SiN<sub>x</sub> [96], [97]. MOCVD enables SiN<sub>x</sub> deposition without exposure to air or any contaminants (e.g. resist residues). Additionally, MOCVD-SiN<sub>x</sub> effectively reduces both leakage currents and R<sub>on,dyn</sub> dispersion [98]. However, MOCVD-SiN<sub>x</sub> has not yet been optimized for the type of heterostructures studied in this work. Therefore, LPCVD becomes the preferred choice.

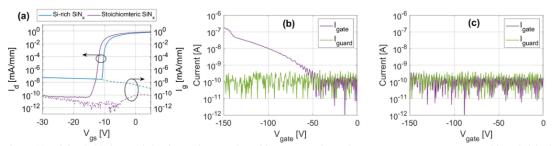

$SiN_x$  passivation layers with varying stoichiometries have been reported. Stoichiometric  $SiN_x$  passivation layers tend to be more resistive compared to Si-rich  $SiN_x$ , but have been associated with higher  $R_{on,dyn}$  [29]. Highly resistive passivation layers are preferable for high voltage devices since the electric field tends to concentrate at the edge of the gate at high voltages, leading to a high gate leakage current and a premature destructive breakdown. Therefore, the stoichiometry of the  $SiN_x$  has to be optimized to achieve a low  $R_{on,dyn}$  dispersion while maintaining a low gate leakage current.

In [Paper B], two types of LPCVD SiN<sub>x</sub> passivation layers are compared in terms of their impact on off-state leakage currents at high voltages in 'buffer-free' MISHEMTs. The two films were grown with different growth temperatures, reactant gas flow ratios, and deposition times, which resulted in a difference in thickness and stoichiometry. The reactant gases used in this LPCVD system are dichlorosilane (DCS) and ammonia (NH<sub>3</sub>). One layer was grown with a high Si content, while the other was grown to have a 3/4 ratio between Si and N (stoichiometric passivation). The Si-rich SiN<sub>x</sub> layer was deposited at a temperature of 820 °C, a pressure of 250 mTorr, and a DCS/NH<sub>3</sub> ratio of 224/23 sccm, while the stoichiometric SiN<sub>x</sub> was deposited at a temperature of 770 °C, a pressure of 250 mTorr and a DCS/NH<sub>3</sub> ratio of 98/360 sccm. Ellipsometry was used to estimate the stoichiometry of the films. A refractive index of 2-3 is typically seen for Si-rich films, while stoichiometric films have a refractive index of 2 [99]. The Si-rich and

stoichiometric films used in this study had a refractive index of 2.38 and 2.02, respectively. Additionally, the resulting thicknesses of the Si-rich and stoichiometric passivation layers were 177 nm and 100 nm, respectively.

A leakage test structure was fabricated (Figure 2.12a-b) [100]. This test structure consists of three terminals: a terminal connected to the 2DEG through an ohmic contact, and two terminals connected to the MIS structure formed by the gate metal, SiN<sub>x</sub> gate dielectric and GaN/AlGaN surface. The ohmic contact and one of the MIS-structure (the guard) are grounded, while the second MIS structure (the gate) has a negative bias applied to it. The current to the guard and gate terminals are monitored as the gate bias is ramped down from 0 V to -150 V. This test structure makes it possible to separate surface/interface-related leakage currents and leakage currents through the gate dielectric and barrier by observing the difference in the magnitude of the two leakage components. The separation between the gate and guard contacts is 10 μm in this test.

In Figure 2.12c, the two leakage components are shown for a sample with a Sirich  $SiN_x$  passivation layer. Both the gate and guard currents can maintain a current at (or below) the measurement limit (~100 pA) of the system between 0 V and -40 V. However, when the gate bias decreases from -40 V to -150 V, the gate

**Figure 2.12.** (a) Cross-section schematic of a leakage test structure. (b) Microscope image of a leakage test structure. (c-d) Leakage test structure results with (c) a Si-rich SiN<sub>x</sub> passivation layer and (d) a stoichiometric SiN<sub>x</sub> passivation layer [Paper B].

current increases by more than three orders of magnitude. In contrast, the guard current remains at (or below) the detection limit throughout the rest of the measurement interval. This implies that most of the leakage current flow from gate-to-2DEG through the  $SiN_x$  gate dielectric, passivation, and AlGaN barrier to the ohmic contact. On the other hand, the stoichiometric  $SiN_x$  passivation maintains a sub-nA guard and gate current in the whole measurement interval (Figure 2.12d), which is up to three orders of magnitude lower compared to the gate leakage current in the Si-rich  $SiN_x$  passivation.

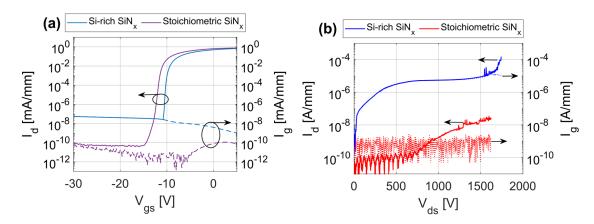

The impact of  $SiN_x$  stoichiometry on off-state characteristics of the MISHEMTs is seen in Figure 2.13. AlGaN/GaN MISHEMTs with gate lengths of 2  $\mu$ m and 4  $\mu$ m were fabricated for the Si-rich  $SiN_x$  and stoichiometric  $SiN_x$ , respectively. Gate-source distance, gate-drain distance, source field plate length, gate field plate length and gate width were designed to 2  $\mu$ m, 20  $\mu$ m, 5  $\mu$ m, 4  $\mu$ m and 100-200  $\mu$ m, respectively. Nitrogen implantation was used as isolation in both samples.

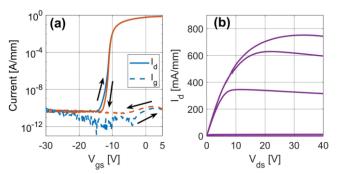

The gate and drain current were measured as  $V_{gs}$  was swept from -30 V to 5 V, and  $V_{ds} = 40$  V (Figure 2.13a). At  $V_{gs} = -20$  V, the drain current decreases from  $\sim 4.1 \cdot 10^{-8}$  A/mm to  $\sim 4.7 \cdot 10^{-11}$  A/mm when the stoichiometric SiN<sub>x</sub> passivation is employed. The off-state leakage current in MISHEMTs with a Si-rich SiN<sub>x</sub> passivation is limited by gate-drain leakage currents, which is likely caused by the poor insulating properties of the Si-rich SiN<sub>x</sub>, and not surface/interface currents, as was demonstrated in Figure 2.12c-d.

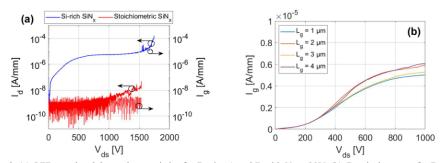

In Figure 2.13b, the off-state breakdown characteristics of MISHEMTs with Sirich and stoichiometric  $SiN_x$  passivations are shown. The drain and gate current were measured at  $V_{gs} = -20$  V and  $V_{gs} = -30$  V for the stoichiometric and Sirich passivation layers, respectively. MISHEMTs with a stoichiometric  $SiN_x$  passivation layer can maintain a gate leakage current below 10 nA/mm up until breakdown, which occurred at 1622 V ([Paper A]). The drain leakage current increase is likely caused by drain-to-source leakage paths between the source field plate and the drain contact or by current flowing under the depleted region at the gate.

**Figure 2.13.** (a) Subthreshold characteristics with  $V_{ds} = 40 \text{ V}$  for MISHEMTs with Si-rich and stoichiometric  $SiN_x$  passivation [Paper B]. (b) Off-state breakdown characteristics of MISHEMTs with Si-rich and stoichiometric  $SiN_x$  passivation [Paper A-B].

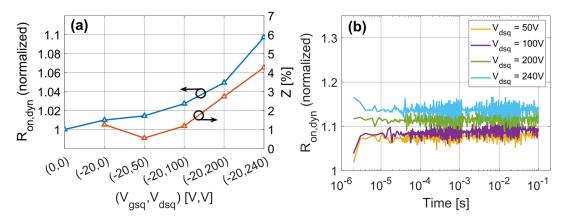

**Figure 2.14.** (a)  $R_{on,dyn}$  and slump ratio at different gate and drain quiescent bias points. (b) Time dependence of  $R_{on,dyn}$  after stress at gate quiescent  $V_{gsq} = -20$  V and at different drain quiescent [Paper A].

MISHEMTs with a Si-rich SiN<sub>x</sub> passivation layer exhibit an off-state breakdown voltage of 1742 V, but with a significantly higher gate-drain leakage current above 1  $\mu$ A/mm when V<sub>ds</sub> increases above 300 V. This increases up to 154  $\mu$ A/mm until breakdown occurs due to destructive gate-drain breakdown.

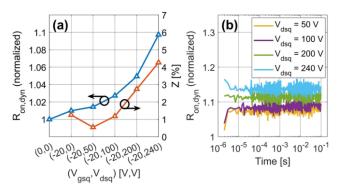

Passivation layers with a low Si/N ratio have previously been shown to cause large  $R_{\text{on,dyn}}$  dispersion in GaN-on-Si HEMTs with C-doped buffer layers [29], [30], [101]. However, this could not be observed for 'buffer-free' HEMTs with gate and source field plates presented in [Paper A]. The normalized  $R_{\text{on,dyn}}$  increases by up to a maximum of 10% when the drain quiescent voltage ( $V_{\text{dsq}}$ ) increases from 0 V to 240 V (Figure 2.14a). Here, the  $R_{\text{on,dyn}}$  was calculated using the drain current at  $V_{\text{ds}}$  = 1 V,  $V_{\text{gs}}$  = 0 V, and an on/off-state time of 1/99  $\mu s$ . Furthermore, the slump ratios, defined as

$$Z_g [\%] = \left| \frac{I_d(-20 V, 0 V) - I_d(0 V, 0 V)}{I_d(0 V, 0 V)} \right| \cdot 100$$

(2.5)

$$Z_d [\%] = \left| \frac{I_d(-20 V, V_{dsq}) - I_d(0 V, 0 V)}{I_d(0 V, 0 V)} \right| \cdot 100$$

(2.6)

was calculated using the drain current at  $V_{\rm ds}=25$  V,  $V_{\rm gs}=1$  V above the knee in the PIV characteristics. The ratios in Equation 2.5 and 2.6 estimates the decrease in current in the saturation region due to trapping effects (current collapse). The slump ratio  $Z_{\rm g}$  is less than 2% and  $Z_{\rm d}$  increases up to a maximum of 4% at a  $V_{\rm dsq}=240$  V. In the DCT characteristics (Figure 2.14b), the normalized  $R_{\rm on,dyn}$  is 4-7 percentage points higher compared to what can be seen in Figure 2.14a. This is most likely due to a longer stress time (on/off-state time of 100/100 ms). The  $R_{\rm on,dyn}$  does not significantly change in the 3  $\mu s$  - 100 ms interval for any quiescent  $V_{\rm dsq}$ . Therefore, traps with time constants above 100 ms are most likely causing the increase in  $R_{\rm on,dyn}$  in the Figure 2.14a. A further study of the off-state stress ( $V_{\rm gsq}$ ,  $V_{\rm dsq}$ ) and stress time at different temperatures is required better to understand the trapping effects in these heterostructures.

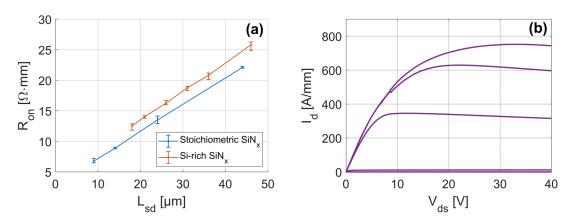

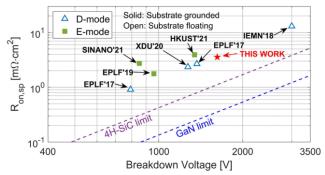

In conclusion, the LPCVD-grown stoichiometric SiN<sub>x</sub> is a promising alternative to Si-rich SiN<sub>x</sub> for high power MISHEMTs due to its good insulating properties. No large dispersive effects could be seen for the stoichiometric SiN<sub>x</sub> passivation in the measured bias range. Additionally, the stoichiometry of the SiN<sub>x</sub> does not seem to affect the static  $R_{on}$  (calculated using  $I_d(V_{ds} = 1 \text{ V}, V_{gs} = 0 \text{ V})$ ) to any significant degree (Figure 2.15a). The difference in R<sub>on</sub> between the two samples can be attributed to sheet resistance and contact resistance variations between the two samples. MISHEMTs with a stoichiometric  $SiN_x$  passivation layer and a 20  $\mu m$ gate-drain distance display a max current of 752 mA/mm (Figure 2.15b) and a  $R_{\text{on,sp}}$ of 3.61 mΩ·cm<sup>2</sup>, resulting in a BV<sup>2</sup>/R<sub>on,sp</sub> figure of merit (FOM) of 729 MW/cm<sup>2</sup>, using a breakdown voltage of 1622 V. The FOM is comparable to other HEMTs found in the literature, where values of 524-877 MW/cm<sup>2</sup> have been reported [20], [64], [102]-[105]. This can also be seen in the Ron,sp-BV plot in Figure 2.16, where the 1 μA/mm breakdown current criterion has been used instead of the 1 mA/mm criterion. Lastly, two-terminal breakdown voltages of 744-1920 V at contact separations of 5-20  $\mu$ m indicate that the power FOM could increase to ~1 GW/cm<sup>2</sup> by optimizing the field plate design and dielectric stack further (Figure 2.17).

**Figure 2.15.** (a) Static on-resistance measured at different source-drain separations. Three devices for each sample were used. (b) Output characteristics of MISHEMTs with a  $L_{\rm gd} = 20~\mu m$  and stoichiometric  $SiN_x$  passivation layer.

Figure 2.16.  $R_{on,sp}$  versus breakdown voltage benchmark, using the 1  $\mu A/mm$  breakdown criterion [Paper A].

**Figure 2.17.** Three-terminal breakdown voltage of MISHEMTs with stoichiometric passivation layer and varying  $L_{\rm gd}$ . Two-terminal (isolation) breakdown voltage is included as a comparison. The 1  $\mu$ A/mm current criterion has been used in these measurements [Paper A].

### 2.5 Gate Dielectric

Designing a HEMT with minimal gate leakage currents is essential to minimize losses and prevent the premature off-state breakdown of the device. A large peak electric field typically causes a high gate current and gate-drain breakdown at the drain side of the gate. Measures to reduce gate leakage involve depositing a high work function metal to form a Schottky barrier, or by depositing a thin intermediate insulating layer between the barrier (or capping) layer and the gate metal. Insulators can provide a larger energy barrier for the electrons compared to a Schottky gate. Moreover, the gate leakage can be further reduced by increasing the insulator thickness. Commonly used gate dielectrics include SiO<sub>x</sub> [62], SiN<sub>x</sub> [98], [106], and Al<sub>2</sub>O<sub>3</sub> [107], [108]. These insulators have a high critical electric field that can withstand the peak field caused by the high drain bias. Gate insulators such as HfO<sub>2</sub> and Ta<sub>2</sub>O<sub>5</sub> are less studied for GaN-based HEMTs. The potential advantage of these insulators is their high dielectric constants (high-x dielectrics) combined with good insulating properties. The high dielectric constant prevents the negative V<sub>th</sub>-shift, which can be seen in the following relation

$$V_{th} \propto -\frac{t_{in}}{\varepsilon_{in}} \tag{2.7}$$

where  $t_{in}$  and  $\epsilon_{in}$  represent the thickness and dielectric constants of the gate dielectric, respectively. This allows thicker gate dielectric layers to be grown without significantly decreasing the  $V_{th}$ . Moreover, depositing a gate dielectric with a high dielectric constant can be combined with gate recess-etched enhancement-mode HEMTs. For this purpose, it is necessary to have a high- $\kappa$  gate insulator to prevent  $V_{th}$  from becoming negative.

**Figure 2.18.** (a) Transfer characteristics of MISHEMTs with  $HfO_2$ ,  $Ta_2O_5$  and  $SiN_x$ , (b) Transfer characteristics before and after post-metallization anneal at 375 °C for 12 min for four MISHEMTs with  $HfO_2$  and  $Ta_2O_5$ .

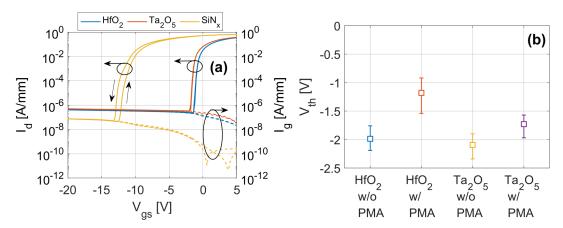

In this work,  $Ta_2O_5$  and  $HfO_2$  are compared with a stoichiometric  $SiN_x$  gate dielectric in terms of their impact on gate leakage currents and threshold voltage in MISHEMTs. The oxides were deposited after the deposition and annealing of the ohmic contacts. Both oxides have a thickness of 20 nm and were deposited using an Oxford FlexAI plasma-enhanced atomic layer deposition (PEALD). A post-metallization anneal (PMA) at 375 °C for 12 min was implemented after the gate metal deposition. The  $SiN_x$  gate dielectric has a thickness of 40 nm and was deposited using an LPCVD system. Mesa isolation and a Si-rich passivation were utilized for this study.

The transfer characteristics of all three MISHEMTs ( $L_{gd}$  = 30 µm,  $L_g$  = 4 µm) are shown in Figure 2.18a. The SiN<sub>x</sub> gate dielectric display a V<sub>th</sub> of -12.7-(-11.5) V and gate-drain leakage currents of 60-70 nA/mm range at V<sub>ds</sub> = 40 V. Gate leakage currents are higher by a factor of 6-7 in the devices with HfO<sub>2</sub> and Ta<sub>2</sub>O<sub>5</sub> insulators. This difference could partly be explained by the difference in thickness between the SiN<sub>x</sub>, and the two oxides. Annealing the oxides up to 375 °C after gate metallization did not significantly change the gate leakage current. However, V<sub>th</sub> (measured at ~10 µA/mm) increased from -2 V and -2.1 V to -1.2 V and -1.7 for the HEMTs with HfO<sub>2</sub> and Ta<sub>2</sub>O<sub>5</sub>, respectively (Figure 2.18b). This shows the impact of high- $\kappa$  gate dielectrics. In addition, the small hysteresis in MISHEMTs with oxide gate insulators indicates that the trap concentration in the oxides or at the metal-insulator interface is small (Figure 2.18a). The MISHEMT with a SiN<sub>x</sub> gate dielectric displays a small-to-moderate negative shift in the reverse sweep direction, which means some positive charges are present at the metal/SiN<sub>x</sub> or SiN<sub>x</sub>/GaN interfaces.

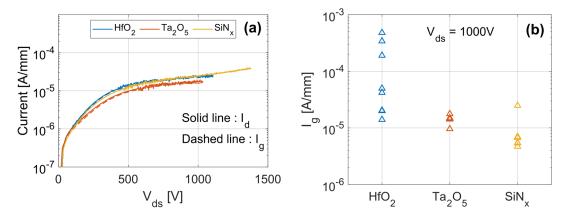

The three samples' leakage currents at high  $V_{ds}$  were also studied. The gate-source voltage was set to -20 V for the devices with  $SiN_x$  gate dielectric, and -10 V for the devices with the oxide gate dielectrics, respectively. MISHEMTs used for these measurements were designed with a  $L_{gd}$  = 20-30  $\mu$ m. The predominant leakage mechanism at high voltages in all three samples was gate-drain leakage (Figure 2.19a). MISHEMTs with a  $SiN_x$  insulator display the highest breakdown

Figure 2.19 (a) Off-state breakdown characteristics of MISHEMTs with HfO<sub>2</sub>,  $Ta_2O_5$  and  $SiN_x$  gate insulators ( $L_{gd} = 30 \mu m$ ). (b) Gate leakage current for eight HEMTs with Lgd = 20-30  $\mu m$  at measured at  $V_{ds} = 1000 V$  in the off state.

voltages and the lowest leakage currents on average (Figure 2.19b). However, the gate current through the  $Ta_2O_5$  is only higher by a factor of 2-3. Moreover, the samples with  $Ta_2O_5$  and  $SiN_x$  exhibit a smaller device-device variation. MISHEMTs with a  $HfO_2$  dielectric resulted in the highest gate currents overall and a gate current that varies from 10-500  $\mu$ A/mm between devices, which worsens the reproducibility.

This study facilitates the development of high voltage enhancement mode MISHEMTs, where the small negative  $V_{th}$ -shift resulting from the ALD-grown HfO<sub>2</sub> or  $Ta_2O_5$  can be combined with a partial recess etch into the barrier. This type of technique has been successfully implemented using  $SiO_2$  [20],  $Al_2O_3$  [109] and  $ZrO_2$  [110]. However, it has not yet been seen for ALD-grown HfO<sub>2</sub> or  $Ta_2O_5$ . Furthermore, gate leakage currents can be suppressed below  $10^{-10}$  A/mm for  $V_{ds} < 100$  V using sputtered HfO<sub>2</sub> [111], which is significantly lower than shown in Figure 2.18a. Therefore, ALD growth parameters could be optimized to achieve higher quality HfO<sub>2</sub>.

Realizing high voltage operation with sub-1  $\mu$ A/mm leakage current requires further reduction of gate leakage current. The gate leakage current is highly dependent on the type of passivation, as was demonstrated in section 2.4. A 2-3 order of magnitude decrease in gate leakage current should be possible by employing stoichiometric  $SiN_x$  passivation instead of a Si-rich passivation. However, the gate oxide quality could also be improved by optimizing the PEALD parameters, including Ta and Hf precursor gas flow, chamber temperature and chamber pressure to achieve better insulating properties.

## Chapter 3

## A New Method to Characterize Short-Channel Effects in GaN HEMTs

Downscaling the gate length of GaN HEMTs is one of the most common approaches when it comes to improving device performance, both in terms of increasing the operating frequency and in terms of reducing the power lost due to the channel resistance [112]. In HEMTs designed for microwave applications, the current gain cut-off-frequency ( $f_T$ ) and the maximum power-gain cut-off frequency ( $f_{max}$ ) are affected by  $L_g$  reduction through the expressions:

$$f_T = \frac{v_{sat}}{2\pi L_g} = \frac{g_m}{2\pi (C_{ad} + C_{as})}$$

(3.1)

$$f_{max} = \frac{f_T}{2\sqrt{(R_i + R_s + R_g)/R_{ds} + (2\pi f_T)R_g C_{gd}}}$$

(3.2)

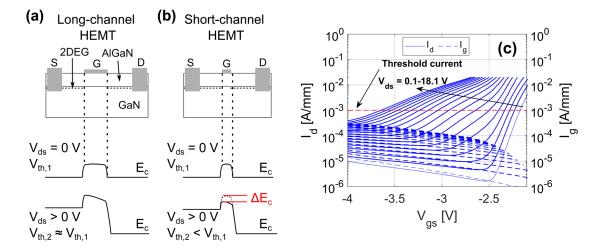

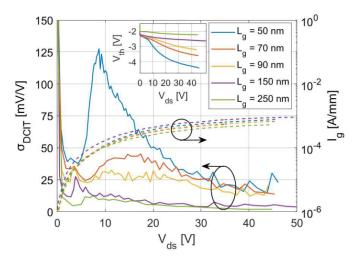

where  $v_{sat}$  is the electron saturation velocity,  $g_m$  is the transconductance,  $C_{gd}$  and  $C_{gs}$  are the gate-drain and gate-source capacitances, and  $R_i$ ,  $R_s$ ,  $R_g$ ,  $R_{ds}$ , are the gate-charging, source, gate and output resistances, respectively [113]. However, when the gate length is reduced below 100 nm, SCEs become apparent. These effects cause a reduction of the potential barrier formed under the gate in the off-state due to an applied  $V_{ds}$  [114]. In a long-channel HEMT, the energy barrier height reduction at the source side of the gate is typically negligible (Figure 3.1a), leading to a small drain-source leakage current. However, when the gate length is sufficiently short, the voltage applied at the drain contact can influence the barrier height at the source side of the gate (Figure 3.1b). In turn, electrons are capable of surmounting the energy barrier due to thermal excitations, resulting in an increased drain-source leakage current. This manifests as a negative shift of  $V_{th}$  in the device's transfer characteristics (Figure 3.1c), which is termed DIBL. The inability of the gate to

**Figure 3.1.** A schematic showing the conduction band profile close to the AlGaN/GaN interface at two drain biases for a (a) long-channel HEMT, and (b) short-channel HEMT. (c) An example of the transfer characteristics at different drain biases for a AlGaN/GaN HEMT with  $L_{\rm g} = 50$  nm.

modulate the electron concentration channel due to SCEs results in a reduction of  $g_m$ , which consequently reduces  $f_T$  and  $f_{max}$  (Equation 3.1-3.2). Additionally, as the  $V_{ds}$ -dependence of  $V_{th}$  becomes stronger,  $R_{ds}$  decreases, leading to a reduction of  $f_{max}$ .

In GaN-based HEMTs, DIBL can also be caused by a high leakage current through the buffer underneath the depleted gate region (punch-through) rather than at the AlGaN/GaN interface [115]. It is, therefore, important to increase the resistivity in the buffer layer so that the electron distribution is confined to a small region in the vicinity of the III-nitride interface. Another approach is to improve the electron confinement in the quantum well by incorporating a back-barrier with a larger bandgap (e.g. AlGaN). High electron confinement enables improved gate control, which effectively reduces DIBL. Gate modulation can also be enhanced by employing a lattice-matched InAlN, which enables a reduction of the barrier thickness while maintaining a high sheet carrier concentration [116]. This allows for further Lg reduction in GaN HEMTs.

Additionally, gate length downscaling of power switching HEMTs is necessary to minimize on-state losses. However, this eventually results in increased off-state drain-source leakage current at high voltage due to DIBL/punch-through, which lowers the breakdown voltage set by the breakdown current criteria. This especially becomes a problem in GaN power switching HEMTs operating voltages below 300 V, where  $L_{\rm gd}$  is less than 5  $\mu m$ . In these devices,  $L_{\rm g}$ -downscaling becomes even more important to reduce on-state losses. Optimization of  $L_{\rm g}$  in terms of  $R_{\rm on}$  and DIBL requires a measurement technique where  $V_{\rm th}$  shifts can be straightforwardly characterized at high voltages.

#### The Conventional Measurement Technique

When characterizing SCEs, it is common to use two measured transfer characteristics with different  $V_{ds}$  (as in Figure 3.1c). The threshold voltage is either defined as  $V_{gs}$  at some fixed threshold drain current density ( $I_{d,th}$ ), or at some fixed ratio of the maximum drain current. With two values of  $V_{ds}$  and  $V_{th}$ , the DIBL parameter ( $\sigma$ ) is calculated using

$$\sigma = -\frac{V_{th,high} - V_{th,low}}{V_{ds,high} - V_{ds,low}}$$

(3.3)

where  $(V_{th,low}, V_{ds,low})$  and  $(V_{th,high}, V_{ds,high})$  are the threshold and drain-source voltages for the first and second transfer curves, respectively. The downside of using this method is that it only captures  $V_{th}$ -shift for two (or a few)  $V_{ds}$ . This makes a comparison between different technologies difficult since the choice of reference voltages  $(V_{th,low}, V_{ds,low})$  and comparing voltages  $(V_{th,high}, V_{ds,high})$  is more or less arbitrary. Furthermore, to see the effect of DIBL over a large range of  $V_{ds}$  with small steps in between, one would have to measure the transfer characteristics for each step from the lowest  $V_{ds}$  to the highest, resulting in long measurement times.

#### The Drain Current Injection Technique

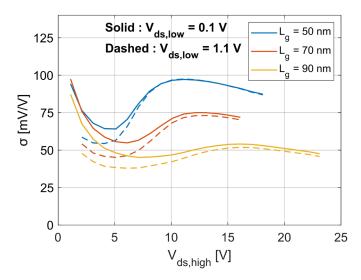

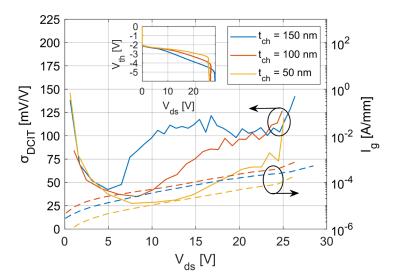

In [Paper C], an alternative measurement method is proposed. This method is based on the drain current injection technique (DCIT), which was introduced to characterize the off-state breakdown voltage of field-effect transistors [117]. With this measurement technique, the drain current used as the criterion for  $V_{th}$  is kept constant, while  $V_{gs}$  is decreased from an 'open channel' to a 'depleted channel' condition. As the channel becomes more depleted,  $V_{ds}$  increases to maintain a constant threshold current. This will yield a large range of  $V_{th}$ - $V_{ds}$  data in one measurement, which then can be used to calculate the DIBL parameter in Equation 3.3. Furthermore, the DIBL parameter can be expressed as a difference between any  $V_{th}$  data point  $(V_{th,i})$  and its neighboring data point  $V_{th,i-1}$ , divided by the difference between their respective  $V_{ds,i}$  and  $V_{ds,i-1}$ . This new definition of the DIBL parameter is given by

$$\sigma_{DCIT} = -\frac{\Delta V_{th}}{\Delta V_{ds}} \Big|_{I_d = I_{d,th}}$$

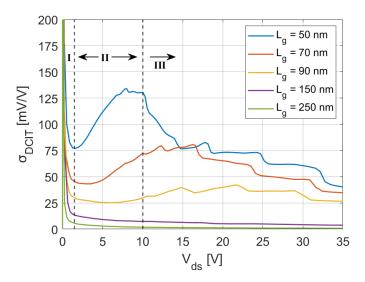

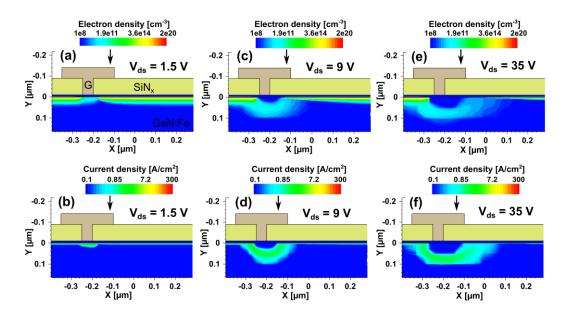

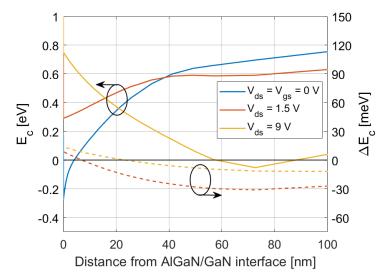

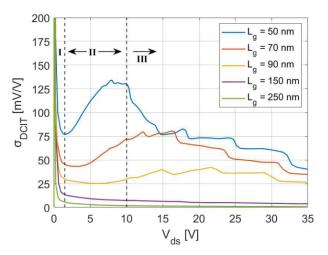

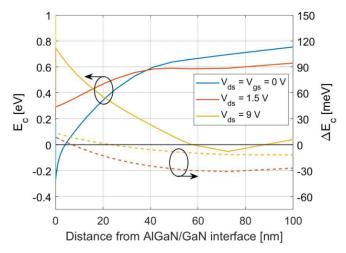

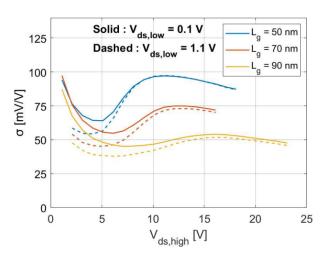

(3.4)