Traditio et Innovatio

# Model-based Symbolic Design Space Exploration at the Electronic System Level

-A Systematic Approach-

Dissertation zur Erlangung des akademischen Grades Doktor-Ingenieur (Dr.-Ing.) der Fakultät für Informatik und Elektrotechnik der Universität Rostock

> VORGELEGT VON: M.Sc. Kai Neubauer, geboren am 10.05.1991 in Demmin

> > EINGEREICHT AM: 17.08.2021

https://doi.org/10.18453/rosdok\_id00003664

UNIVERSITÄT ROSTOCK | FAKULTÄT FÜR INFORMATIK UND ELEKTROTECHNIK Institut für Angewandte Mikroelektronik und Datentechnik Richard-Wagner-Str. 31, 18119 Rostock-Warnemünde | Tel: +49 381 498-7251

Dieses Werk ist lizenziert unter einer Creative Commons Namensnennung - Keine Bearbeitungen 4.0 International Lizenz.

## Gutachter

- Prof. Dr.-Ing. habil. Christian Haubelt Lehrstuhl "Eingebettete Systeme" Institut f

ür Angewandte Mikroelektronik und Datentechnik Universit

ät Rostock

- Prof. Dr. Torsten Schaub

Wissensverarbeitung und Informationssysteme

Institut f

ür Informatik und Computational Science

Universit

ät Potsdam

- Prof. Dr.-Ing. Michael Glaß Institut für Eingebettete Systeme / Echtzeitsysteme Fakultät für Ingenieurwissenschaften, Informatik und Psychologie Universität Ulm

Datum der Abgabe:17.08.2021Datum der Verteidigung:11.03.2022

# Acknowledgments

For the past six and a half years, many people have accompanied and supported me in the creation of the present work. I would like to take the opportunity here to express my sincere gratitude to all of them.

First and foremost, I would like to thank Prof. Dr. Christian Haubelt for providing me with the opportunity to work on this thesis topic. His continuous support and supervision – already beginning with my bachelor and master theses – was and is particularly appreciated. Without his valuable input, this work would not have been possible. Furthermore, my thanks go to Prof. Dr. Torsten Schaub at the University of Potsdam for the co-supervision, the helpful discussions regarding ASP, and accepting to review the thesis. I would also like to thank Prof. Dr. Michael Glaß at the University of Ulm, who accepted to review the thesis as well.

Many thanks go to my colleagues at the Institute of Applied Microelectronics and Computer Engineering for the consistently pleasant working atmosphere and the support through uncountable discussions and activities – both work-related and non-work-related. In particular, but also representatively for the whole team, I would like to thank Dr. Florian Grützmacher, Dr. Henning Puttnies, Dr. Michael Rethfeldt, Daniel Gis, Benjamin Beichler, and Luise Müller for their valuable input regarding the present thesis and all related topics. Also, I would like to thank Philipp Wanko at the University of Potsdam for the fruitful cooperation in the mutual project that led to this thesis.

Finally, my special thanks go to my parents, Holger and Ramona Neubauer, and my friends for motivating and supporting me in many ways. In anticipation of forgetting someone important, I refrain from mentioning you explicitly. You know who you are!

- Thank you!

# Abstract

Today, computer systems are ubiquitously integrated in nearly all areas of everyday life. Well ahead of conventional general purpose computers, embedded systems are dominating the global market. They are present in telecommunication equipment, in current and future automotive and aviation technology, household appliances, and infrastructure. The design of those embedded computer systems is continuously becoming more complex as the requirements with respect to their functional and extra-functional properties grow steadily. Simultaneously, the adaption to technological progress demands for shorter development cycles. Hence, an efficient design process is imperative to fulfill these requirements. A bottom-up design strategy, where every detail of the system can be explored and evaluated, has not been viable for a long time now. Thus, the design process has been raised to higher abstraction levels, where largescaled decisions can be explored more effectively. Decisions are first explored at the electronic system level (ESL), before the results are refined at lower abstractions. However, even at the ESL, the exploration of design alternatives is not a trivial task. It has to be decided, which resources are allocated, where the functionality is implemented, and how the communication infrastructure is realized. Depending on these decisions, the properties of the design have to be determined and evaluated. Typically, an embedded computer system must fulfill several constraints and shall be optimal with respect to multiple objectives. These objectives are often conflicting with each other such that no single optimal solution but a set of compromise. e.g., Pareto-optimal, solutions exists. Therefore, the design of embedded computer systems is considered a multi-objective optimization problem. Automatic approaches are mandatory to obtain Pareto-optimal designs, as the manual exploration of the whole design space is not feasible. To this end, the problem is typically encoded through mathematical models that allow for the evaluation of desired properties. For the exploration, many approaches rely on population-based heuristics that traverse the design space on the basis of random decisions. While this methodology has been shown to work well for many scenarios, it holds significant disadvantages. First, as the search is generally not executed systematically, the approaches cannot guarantee to explore the entire design space and, therefore, may miss optimal solutions. Furthermore, the approaches usually cannot identify already explored solutions. That is, the same design candidates are re-visited again even if they already have been evaluated and found to be non-optimal before. Second, as most population-based approaches are based on the recombination of previously found solutions, they tend to run in saturation, exploring the same regions of design space over and over. Finally, the search is decoupled from the exploration. This prevents to exchange information between the individual steps that could allow to steer the search into more promising regions.

In this thesis, a novel, fully systematic approach is proposed that aims to address the outlined problems. The multi-objective optimization problem is encoded symbolically through a concise answer set programming (ASP) formulation. The programming paradigm ASP stems from the area of knowledge representation and reasoning and permits the systematic exploration of

#### Abstract

the search space. While linear feasibility constraints can be directly verified in ASP, nonlinear objectives are hard to formulate in standard ASP. Therefore, in the thesis at hand, several specialized solvers are tightly coupled as background theories with the foreground ASP solver under the ASP modulo theories (ASPmT) paradigm. The tight coupling of foreground and background theories allows the exchange of information between the previously isolated problems. That is, reasons for invalid design points found in one of the background theories are used to steer the search in the foreground theory and prune the search more effectively. Furthermore, the coupling of disparate solvers allows for the evaluation of partial assignments where only a subset of decisions has been made. This leads to an earlier detection of invalid regions in the search space. The conducted experiments show a significant advantage of using partial assignment checking when compared to an approach where only complete design can be evaluated. The ability to work on partial assignments not only benefits the evaluation of acquired solutions but also the Pareto-filtering as non-optimal solutions can be identified early.

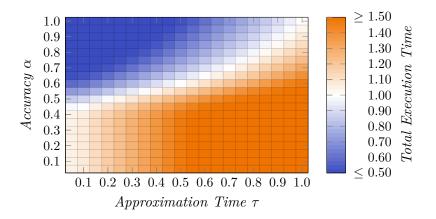

However, the utilization of partial assignments imposes disadvantages as evaluations and Pareto checks have to be executed more regularly. As a remedy, the thesis at hand proposes specialized archive management and evaluation methodologies, that aim at reducing this overhead. It is shown, only when a complete solution is checked for optimality, the entire Pareto filtering process has to be executed. This leads to a significant reduction in required operations for partial solutions while still maintaining correct results. Similarly, a specialized approximation technique is proposed that reduces the number of unnecessary expensive evaluations. With this approach, up to 98 % of all evaluations can be skipped and the overall performance of the design space exploration can be increased by up to six times for the considered use cases.

To summarize, the thesis at hand provides a holistic framework for designing embedded computer systems at the ESL. By utilizing the ASPmT paradigm, the search is executed entirely systematically and the disparate synthesis steps can be coupled to explore the search space effectively.

# Kurzfassung

Computersysteme sind heute allgegenwärtig und in fast allen Bereichen des täglichen Lebens integriert. Weit vor den herkömmlichen Allzweckcomputern dominieren eingebettete Systeme den Weltmarkt. Sie sind in Telekommunikationsgeräten, in der Automobil- und Luftfahrttechnik, in Haushaltsgeräten und in der Infrastruktur zu finden. Der Entwurf dieser eingebetteten Computersysteme wird immer komplexer, da die Anforderungen an ihre funktionalen und extrafunktionalen Eigenschaften stetig wachsen. Gleichzeitig verlangt die Anpassung an den technologischen Fortschritt nach kürzeren Entwicklungszyklen. Um diesen Anforderungen gerecht zu werden, ist ein effizienter Entwurfsprozess unabdingbar. Eine Bottom-up-Entwurfsstrategie, bei der jedes Detail des Systems exploriert und bewertet werden kann, ist schon seit langem nicht mehr praktikabel. Daher wurde der Entwurfsprozess auf höhere Abstraktionsebenen angehoben, auf denen Entscheidungen von großer Tragweite effektiver untersucht werden können. Entscheidungen werden zunächst auf der Systemebene untersucht, bevor die Ergebnisse auf niedrigeren Abstraktionsebenen verfeinert werden. Doch selbst auf der Systemebene ist die Exploration von Entwurfsalternativen keine triviale Aufgabe. Es muss entschieden werden, welche Ressourcen alloziert werden, wo die Funktionalität implementiert wird und wie die Kommunikationsinfrastruktur realisiert wird. Abhängig von diesen Entscheidungen müssen die Eigenschaften des Entwurfs bestimmt und bewertet werden. Typischerweise muss ein eingebettetes Computersystem mehrere Randbedingungen erfüllen und soll in Bezug auf mehrere Ziele optimal sein. Diese Ziele stehen oft in einem Konflikt zueinander, sodass keine einzelne optimale Lösung, sondern eine Menge von Kompromisslösungen, d.h. Pareto-optimale Lösungen, existieren. Daher wird der Entwurf von eingebetteten Computersystemen als ein mehrzieliges Optimierungsproblem betrachtet. Automatische Ansätze sind zwingend erforderlich, um alle Pareto-optimalen Entwurfspunkte zu erhalten, da die manuelle Exploration des gesamten Entwurfsraums nicht durchführbar ist. Zu diesem Zweck wird das Problem typischerweise durch mathematische Modelle modelliert, die die Auswertung der gewünschten Eigenschaften ermöglichen. Für die Exploration verlassen sich viele Ansätze auf populationsbasierte heuristische Verfahren, die den Entwurfsraum auf der Basis von Zufallsentscheidungen durchlaufen. Obwohl sich diese Methodik für viele Szenarien als gut geeignet erwiesen hat, birgt sie erhebliche Nachteile. Erstens können die Ansätze, da die Suche im Allgemeinen nicht systematisch ausgeführt wird, nicht garantieren, dass der gesamte Entwurfsraum durchsucht wird, und verpassen daher möglicherweise optimale Lösungen. Außerdem können die Ansätze oftmals keine bereits gefundenen Lösungen identifizieren. Das heißt, dieselben Entwurfskandidaten werden erneut untersucht, auch wenn sie bereits zuvor bewertet und als nicht optimal befunden wurden. Zweitens, da die meisten populationsbasierten Ansätze auf der Rekombination von zuvor gefundenen Lösungen basieren, neigen sie dazu, in die Sättigung zu laufen und dieselben Regionen des Suchraums immer wieder zu durchlaufen. Schließlich ist die Suche von der Exploration entkoppelt. Dies verhindert den Austausch von Informationen zwischen den einzelnen Schritten, die es erlauben könnten, die Suche in vielversprechendere Regionen zu lenken.

#### Kurzfassung

In dieser Arbeit wird ein neuartiger, vollständig systematischer Ansatz vorgeschlagen, der darauf abzielt, die skizzierten Probleme zu lösen. Das Mehrzieloptimierungsproblem wird symbolisch durch eine prägnante ASP-Formulierung kodiert. Das Programmierparadigma ASP stammt aus dem Bereich der Wissensrepräsentation und Logik und erlaubt die systematische Exploration des Suchraums. Während lineare Randbedingungen in ASP direkt verifiziert werden können, sind nicht-lineare Ziele in Standard-ASP schwer zu formulieren. Daher werden in der vorliegenden Arbeit mehrere spezialisierte Solver als Hintergrundtheorien eng mit dem Vordergrund-ASP-Solver unter dem ASPmT-Paradigma gekoppelt. Die enge Kopplung von Vordergrund- und Hintergrundtheorien ermöglicht den Austausch von Informationen zwischen den zuvor isolierten Problemen. Das heißt, Gründe für ungültige Entwurfspunkte, die in einer der Hintergrundtheorien gefunden werden, werden verwendet, um die Suche in der Vordergrundtheorie zu steuern und diese effektiver zu beschneiden. Darüber hinaus ermöglicht die Kopplung von disparaten Solvern die Auswertung von Teillösungen, bei denen nur eine Teilmenge von Entscheidungen getroffen wurde. Dies führt zu einer früheren Erkennung von ungültigen Regionen im Suchraum. Die durchgeführten Experimente zeigen einen signifikanten Vorteil der Prüfung von Teillösungen im Vergleich zu einem Ansatz, bei dem nur der komplette Entwurf ausgewertet werden kann. Die Möglichkeit, mit Teillösungen zu arbeiten, kommt nicht nur der Bewertung der gefundenen Lösungen zugute, sondern auch der Pareto-Filterung, da nicht-optimale Lösungen frühzeitig erkannt werden können.

Allerdings bringt die Verwendung von Teillösungen auch Nachteile mit sich, da Auswertungen und Optimalitätsprüfungen regelmäßiger durchgeführt werden müssen. Als Abhilfe schlägt die vorliegende Arbeit spezielle Archivverwaltungs- und Auswertungsmethoden vor, die darauf abzielen, diesen Overhead zu reduzieren. Es wird gezeigt, dass nur dann, wenn eine vollständige Lösung auf Optimalität geprüft wird, der gesamte Prozess der Pareto-Filterung ausgeführt werden muss. Dies führt zu einer signifikanten Reduktion der erforderlichen Operationen für Teillösungen bei gleichzeitiger Beibehaltung korrekter Ergebnisse. In ähnlicher Weise wird eine spezialisierte Approximationstechnik vorgeschlagen, die die Anzahl der unnötigen, teuren Auswertungen reduziert. Mit diesem Ansatz können bis zu 98 % aller Evaluationen übersprungen werden und die Gesamtleistung der Entwurfsraumexploration kann für die betrachteten Anwendungsfälle um das bis zu Sechsfache gesteigert werden.

Zusammenfassend lässt sich sagen, dass die vorliegende Arbeit einen ganzheitlichen Rahmen für den Entwurf von eingebetteten Computern auf der Systemebene bereitstellt. Durch die Verwendung des ASPmT-Paradigmas wird die Suche vollständig systematisch ausgeführt und die unterschiedlichen Syntheseschritte können gekoppelt werden, um den Suchraum effektiv zu durchsuchen.

# Contents

| Li | List of Figures vii |                                                                                                                                                                                                                                          |                                    |

|----|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Li | st of               | Tables                                                                                                                                                                                                                                   | ix                                 |

| Aι | Auth                | <b>r's Publications</b><br>hored                                                                                                                                                                                                         | <b>xi</b><br>xi<br>xiii            |

| 1  | Intr<br>1.1         | coduction<br>Contributions and Limitations                                                                                                                                                                                               | $egin{array}{c} 1 \ 3 \end{array}$ |

|    | $1.1 \\ 1.2 \\ 1.3$ | Thesis Overview          Funding and Cooperation                                                                                                                                                                                         |                                    |

| 2  | Mod                 | del-based Design                                                                                                                                                                                                                         | 9                                  |

|    | 2.1                 | Hardware/Software Co-design                                                                                                                                                                                                              | 9<br>10<br>11                      |

|    | 2.2                 | 2.1.3       Synthesis         Constraint Modeling and Checking                                                                                                                                                                           | 12<br>14<br>14<br>16               |

|    | 2.3                 | 2.2.3 Background Theory SolvingMulti-objective Optimization2.3.1 Quality Indicators2.3.2 Optimization Approaches                                                                                                                         | 19<br>21<br>24<br>28               |

|    | 2.4                 | 2.3.2       Optimization Approaches         Related Work                                                                                                                                                                                 | 28<br>33<br>33<br>37<br>38<br>41   |

| 3  | •                   | tem Synthesis with Partial Assignment Evaluation                                                                                                                                                                                         | 43                                 |

|    |                     | System Model       Synthesis Encoding         Synthesis Encoding       Synthesis Encoding         3.2.1       Encoding Allocation, Binding and Routing         3.2.2       Encoding Scheduling Constraints with Integer Difference Logic | 45<br>49<br>49<br>51               |

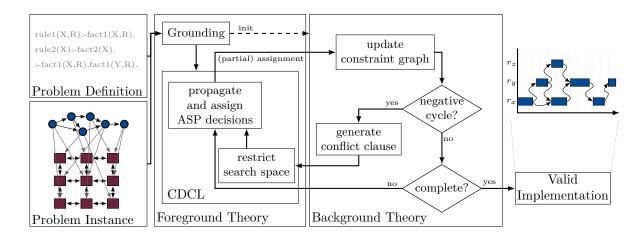

|    | 3.3                 | Theory Propagation                                                                                                                                                                                                                       | 62<br>62<br>63                     |

### Contents

| 3.4 Evaluation                                      | <br>66  |

|-----------------------------------------------------|---------|

| 3.4.1 Test case generation $\ldots$                 | <br>66  |

| 3.4.2 Experiments                                   | <br>72  |

| 3.5 Chapter Summary                                 | <br>75  |

| 4 Symbolic Design Space Exploration                 | 77      |

| 4.1 Search Space Pruning Through Pareto Filtering   | <br>79  |

| 4.1.1 Exploration Model                             | <br>79  |

| 4.1.2 Optimization Framework                        | <br>81  |

| 4.1.3 Evaluation $\ldots$                           | <br>87  |

| 4.1.4 Section Summary                               | <br>90  |

| 4.2 Archive Management                              | <br>91  |

| 4.2.1 Quad–Tree data structure                      | <br>92  |

| 4.2.2 Experimental Evaluation                       | <br>96  |

| 4.2.3 Section Summary                               | <br>99  |

| 4.3 Evaluation through Safe Approximations          | <br>99  |

| 4.3.1 Safe Approximations                           | <br>100 |

| 4.3.2 Approximating Symbolic DSE                    | <br>106 |

| 4.3.3 Experiments                                   | <br>110 |

| 4.3.4 Section Summary                               | <br>117 |

| 4.4 Chapter Summary                                 | <br>118 |

| 5 Conclusion                                        | 121     |

| 5.1 Limitations                                     | <br>122 |

| 5.2 Future Work                                     | 123     |

| A Appendix                                          | I       |

| A.1 Synthesis – Experimental Results                | Ī       |

| A.2 Design Space Exploration – Experimental Results | III     |

| A.3 Approximation – Experimental Results            | IV      |

| Bibliography                                        | VII     |

# **List of Figures**

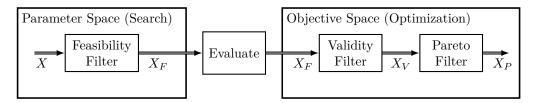

| 1.1  | Design Space Exploration as a filtering process                           |

|------|---------------------------------------------------------------------------|

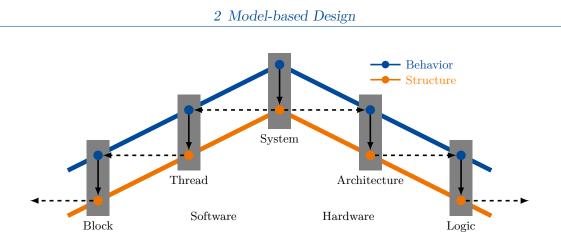

| 2.1  | Double roof model of systems design                                       |

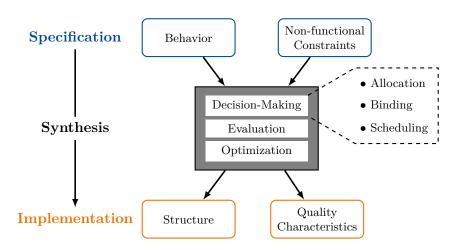

| 2.2  | X-Chart model of synthesis                                                |

| 2.3  | The basic DPLL algorithm                                                  |

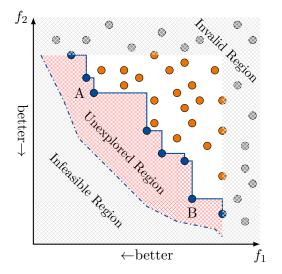

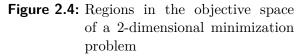

| 2.4  | Regions in the objective space                                            |

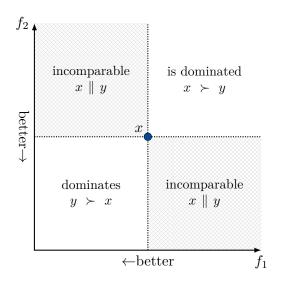

| 2.5  | Dominance relation of objective vectors                                   |

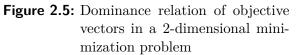

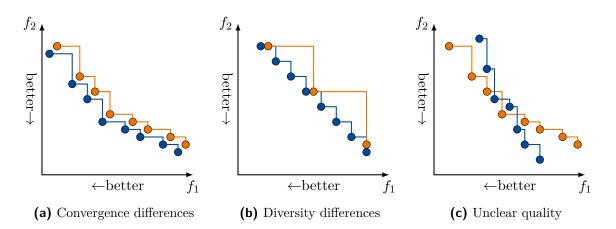

| 2.6  | Quality comparison of non-dominated fronts                                |

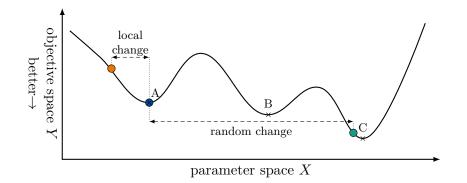

| 2.7  | Local optima of a single-objective minimization problem                   |

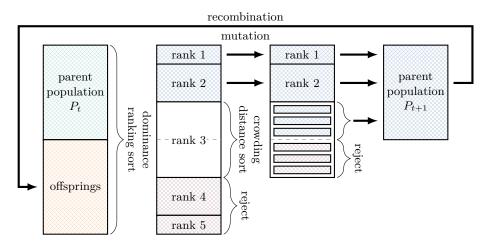

| 2.8  | Execution of one generation in NSGA-II                                    |

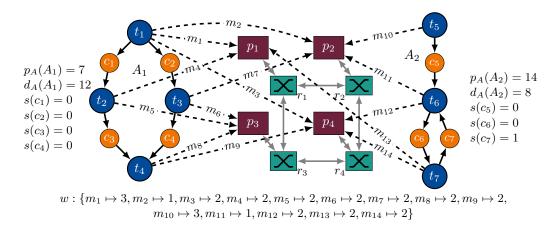

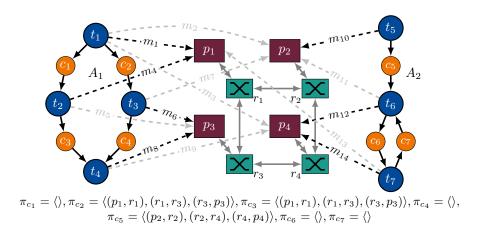

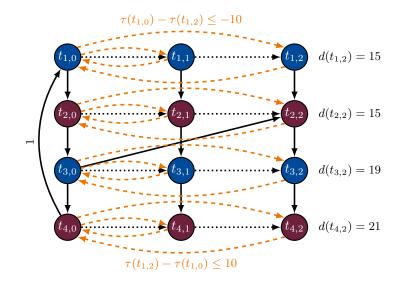

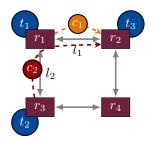

| 3.1  | Specification Graph                                                       |

| 3.2  | Encoding of application $A_1$                                             |

| 3.3  | Encoding of the hardware platform shown in Figure 3.1                     |

| 3.4  | Encoding of the mapping options specified in Figure 3.1                   |

| 3.5  | ASP encoding of allocation, binding, and routing decisions                |

| 3.6  | Feasible Binding and Routing51                                            |

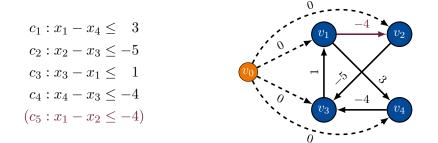

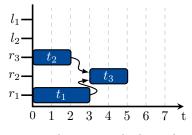

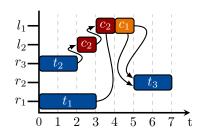

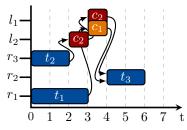

| 3.7  | QF–IDL Example with corresponding constraint graph                        |

| 3.8  | QF–IDL Theory definition in ASP with <i>clingo 5</i>                      |

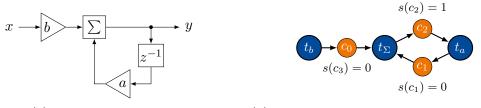

| 3.9  | First-order IIR filter                                                    |

| 3.10 | Encoding of Dependency Constraints                                        |

| 3.11 | Encoding of Resource Sharing Constraints                                  |

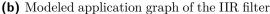

|      | Example specification with deadlines larger than the periodicity          |

| 3.13 | Adapted application graph                                                 |

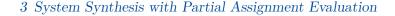

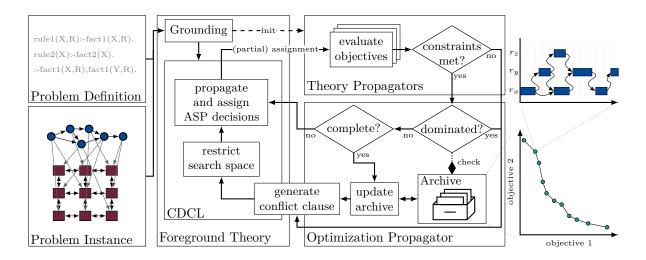

| 3.14 | Architecture Overview of the synthesis framework                          |

|      | Incremental consistency checking algorithm                                |

|      | Scheduling anomaly                                                        |

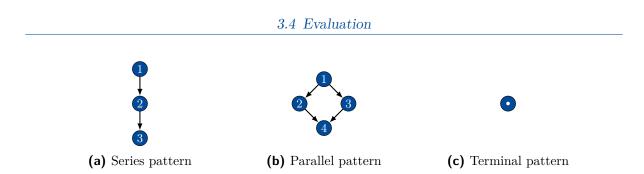

|      | Different patterns considered in the series-parallel graph generation     |

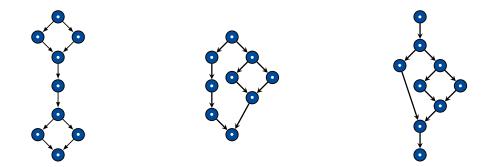

| 3.18 | Application Generator Module68                                            |

|      | Generated applications with similar characteristics                       |

| 3.20 | Architecture Generator Module                                             |

| 3.21 | Mapping Generator Module7070                                              |

| 4.1  | Overview of the Design Space Exploration Framework                        |

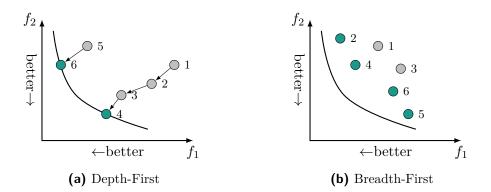

| 4.2  | Optimization Strategies                                                   |

| 4.3  | Exploration algorithm used by the optimization framework                  |

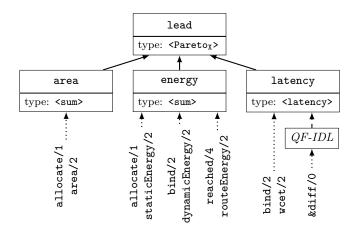

| 4.4  | Preference Graph of the optimization framework                            |

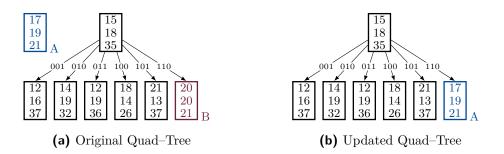

| 4.5  | Updating an archive based on the Quad-Tree                                |

| 4.6  | Recursive algorithm checking whether a partial assignment is dominated 94 |

### List of Figures

| 4.7  | Recursive algorithm to update the Quad–Tree after a complete assignment has       |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | been found                                                                        | 95  |

| 4.8  | Experimental Setup for archive management with Quad-Trees                         | 97  |

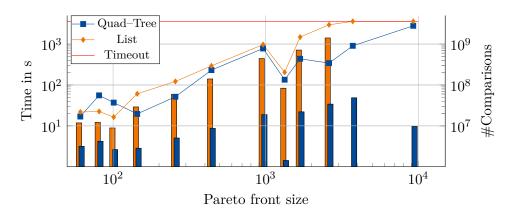

| 4.9  | Performance comparison of Quad-Tree and List-based archive                        | 98  |

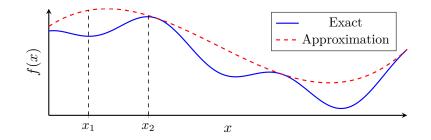

| 4.10 | Safe approximation of an analytical function.                                     | 101 |

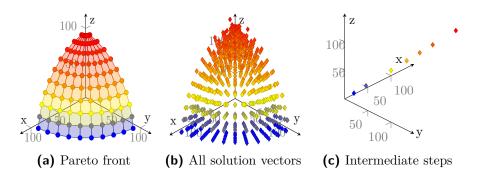

| 4.11 | Exact (blue) and approximated (orange) Pareto front                               | 102 |

| 4.12 | Under-approximations in minimization problems.                                    | 103 |

| 4.13 | The design flow of the proposed iterative DSE methodology                         | 104 |

| 4.14 | Impact of approximation accuracy and performance on overall runtime               | 105 |

| 4.15 | Different under-approximations for the calculation of the latency                 | 109 |

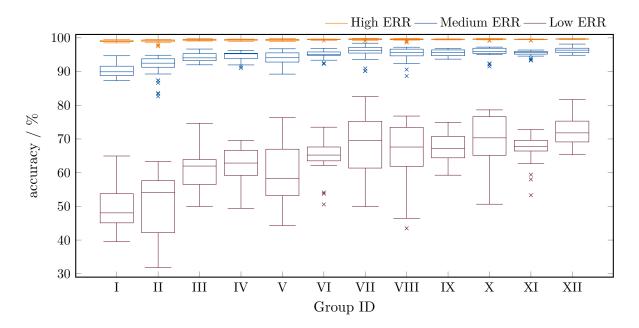

| 4.16 | Latency approximation accuracy for different complexity groups and ERRs. Blue     |     |

|      | corresponds to the original, red to a low ERR, and orange to a high ERR           | 112 |

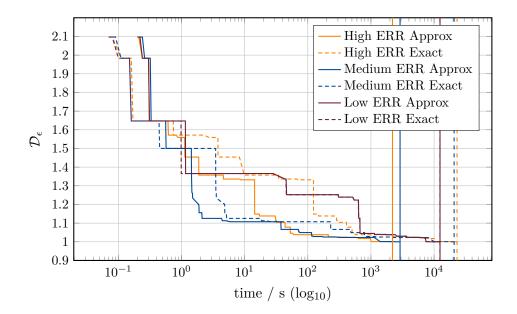

| 4.17 | Epsilon dominance over the runtime of the small instances                         | 114 |

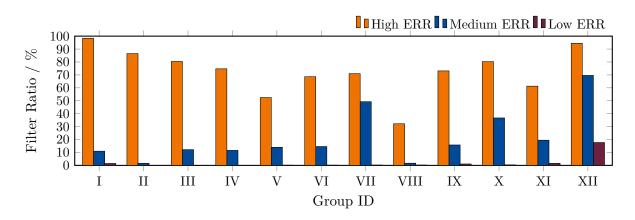

| 4.18 | The average Filter Ratio of the instances in the individual specification groups. | 115 |

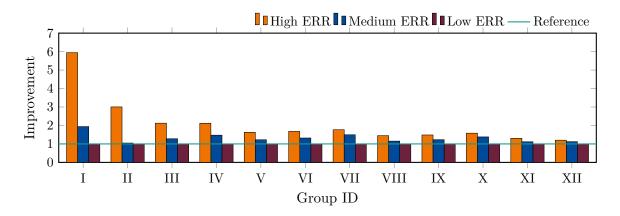

| 4.19 | The average performance improvement of the instances in the individual specifi-   |     |

|      | cation groups                                                                     | 117 |

|      |                                                                                   |     |

# **List of Tables**

| 2.1 | Encoding of the partitioning problem in SAT and ASP                           | 18  |

|-----|-------------------------------------------------------------------------------|-----|

| 2.2 | Classification of the dominance relations                                     | 23  |

| 3.1 | Problem instances for the synthesis benchmark                                 | 72  |

| 3.2 | Synthesis experimental results                                                | 74  |

| 4.1 | Quality for some test instances achieved by the different configurations      | 89  |

| 4.2 | Quality by search strategy                                                    | 90  |

| 4.3 | Quality by communication model                                                | 90  |

| 4.4 | Pareto front of Approximations as of Figure 4.11                              | 102 |

| 4.5 | Specification groups with its specific parameters                             | 111 |

| A.1 | Detailed results of the synthesis experiments for the full assignment runs    | Ι   |

| A.2 | Detailed results of the synthesis experiments for the partial assignment runs | II  |

| A.3 | Extended results of the evaluation of the optimization framework              | III |

| A.4 | Detailed data regarding the Filter Ratio                                      | IV  |

|     | Detailed data regarding the performance improvement                           | V   |

# **Author's Publications**

### Authored

Kai Neubauer, Christian Haubelt, and Michael Glaß. "Supporting Composition in Symbolic System Synthesis". In: International Conference on Embedded Computer Systems: Architectures, Modeling and Simulation (SAMOS). Samos, Greece, July 2016, pp. 132–139. DOI: 10.1109/SAMOS.2016.7818340.

**Abstract:** Typically, state-of-the-art approaches in system synthesis do not consider the trend in embedded systems design towards systems-of-systems where optimized subsystems exist from previous projects or as 3 rd party IP. In this paper, we propose a novel top-down system synthesis approach with additional support for the composition of subsystems that is based on the use of hierarchical mapping edges and a list-based scheduling algorithm using distributed priority queues. The proposed method not only enables composition of existing subsystems, but experimental results also show a significant reduction of the design space while maintaining a good quality of the implemented systems. Especially for large network-on-chip systems (NoC), our approach outperforms an existing top-down methodology in solving time by nearly 50% and in average quality by 11%.

[2] Kai Neubauer, Philipp Wanko, Torsten Schaub, and Christian Haubelt. "Enhancing Symbolic System Synthesis through ASPmT with Partial Assignment Evaluation". In: *Design, Automation and Test in Europe Conference (DATE)*. Lausanne, Switzerland, Mar. 2017, pp. 306–309. DOI: 10.23919/DATE.2017.7927005.

Abstract: The design of embedded systems is becoming continuously more complex such that efficient system-level design methods are becoming crucial. Recently, combined Answer Set Programming (ASP) and Quantifier Free Integer Difference Logic (QF-IDL) solving has been shown to be a promising approach in system synthesis. However, this approach still has several restrictions limiting its applicability. In the paper at hand, we propose a novel ASP modulo Theories (ASPmT) system synthesis approach, which (i) supports more sophisticated system models, (ii) tightly integrates the QF-IDL solving into the ASP solving, and (iii) makes use of partial assignment checking. As a result, more realistic systems are considered and an early exclusion of infeasible solutions improves the entire system synthesis.

[3] Kai Neubauer, Christian Haubelt, Philipp Wanko, and Torsten Schaub. "Utilizing Quad-Trees for Efficient Design Space Exploration with Partial Assignment Evaluation". In: 23rd Asia and South Pacific Design Automation Conference (ASP-DAC). Jeju, Korea, Jan. 2018, pp. 434–439. DOI: 10.1109/ASPDAC.2018.8297362.

**Abstract:** Recently, it has been shown that constraint-based symbolic solving techniques offer an efficient way for deciding binding and routing options in order to obtain a feasible system level implementation. In combination with various background theories, a feasibility analysis of the resulting system may already be performed on partial solutions. That is, infeasible subsets of mapping and routing options can be pruned early in the decision process, which fastens the solving accordingly. Allowing a proper design space exploration including multi-objective optimization also requires an efficient structure for storing and managing non-dominated solutions. In this work, we propose and study the usage of the Quad-Tree

data structure in the context of partial assignment evaluation during system synthesis. Out experiments show that unnecessary dominance checks can be avoided, which indicates a preference of Quad-Trees over a commonly used list-based implementation for large combinatorial optimization problems.

[4] Kai Neubauer, Philipp Wanko, Torsten Schaub, and Christian Haubelt. "Exact Multi-Objective Design Space Exploration using ASPmT". In: *Design, Automation and Test* in Europe Conference (DATE). Dresden, Germany, Mar. 2018, pp. 257–260. DOI: 10. 23919/DATE.2018.8342014.

Abstract: An efficient Design Space Exploration (DSE) is imperative for the design of modern, highly complex embedded systems in order to steer the development towards optimal design points. The early evaluation of design decisions at system-level abstraction layer helps to find promising regions for subsequent development steps in lower abstraction levels by diminishing the complexity of the search problem. In recent works, symbolic techniques, especially Answer Set Programming (ASP) modulo Theories (ASPmT), have been shown to find feasible solutions of highly complex system-level synthesis problems with non-linear constraints very efficiently. In this paper, we present a novel approach to a holistic system-level DSE based on ASPmT. To this end, we include additional background theories that concurrently guarantee compliance with hard constraints and perform the simultaneous optimization of several design objectives. We implement and compare our approach with a state-of-the-art preference handling framework for ASP. Experimental results indicate that our proposed method produces better solutions with respect to both diversity and convergence to the true Pareto front.

[5] Kai Neubauer, Christian Haubelt, Philipp Wanko, and Torsten Schaub. "Systematic Test Case Instance Generation for the Assessment of System-level Design Space Exploration Approaches". In: 21. Workshop Methoden und Beschreibungssprachen zur Modellierung und Verifikation von Schaltungen und Systemen (MBMV). Tübingen, Germany, Mar. 2018. DOI: 10.15496/publikation-25685.

Abstract: The design of embedded systems gets continually more arduous as the complexity of applications and hardware platforms advance to satisfy the increasing demands on functionality, performance, and power consumption. Mostly however, the concurrent fulfillment of those demands are impossible because quality parameters are usually conflicting with each other and cannot be guaranteed simultaneously. Thus, to find the best compromises of all possible solutions, an efficient Design Space Exploration (DSE) becomes imperative. While, in recent time, many DSE techniques to the system-level synthesis problem of embedded systems design have been proposed, a systematic approach on how to produce a viable set of variant test cases with definite similar properties is not available. In this work, we therefore propose a methodology for the test case generation for DSE techniques and present a versatile and easily expendable benchmark generator based on Answer Set Programming (ASP) that is able to produce hard synthesis problem instances.

[6] Kai Neubauer, Christian Haubelt, Philipp Wanko, and Torsten Schaub. "Work-in-Progress: On Leveraging Approximations for Exact System-level Design Space Exploration". In: International Conference on Hardware Software Codesign and System Synthesis (CODES/ISSS). Sept. 2018, pp. 1–2. DOI: 10.1109/CODESISSS.2018.8525974.

Abstract: In order to find good design points for embedded systems, an efficient exploration of the design space is imperative. The ever-increasing complexity of embedded systems, however, results in a deterioration of the overall exploration performance. The DSE essentially consists of two parts: (1) the search for feasible solutions and (2) the evaluation of found feasible solutions. While the search has been massively improved by ASPmT-based strategies, the evaluation emerges as the main bottleneck. Tragically, evaluating bad solutions takes as much time as evaluating good ones. Hence, in this paper we

study the utilization of approximations in the evaluation process integrated in an ASPmT-based DSE to identify bad solutions more quickly while still retaining the exact Pareto-front.

Kai Neubauer, Benjamin Beichler, and Christian Haubelt. "Exact Design Space Exploration Based on Consistent Approximations". In: *Electronics* 9.7 (June 2020), p. 1057. ISSN: 2079-9292. DOI: 10.3390/electronics9071057.

Abstract: The aim of design space exploration (DSE) is to identify implementations with optimal quality characteristics which simultaneously satisfy all imposed design constraints. Hence, besides searching for new solutions, a quality evaluation has to be performed for each design point. This process is typically very expensive and takes a majority of the exploration time. As nearly all the explored design points are sub-optimal, most of them get discarded after evaluation. However, evaluating a solution takes virtually the same amount of time for both good and bad ones. That way, a huge amount of computing power is literally wasted. In this paper, we propose a solution to the aforementioned problem by integrating efficient approximations in the background of a DSE engine in order to allow an initial evaluation of each solution. Only if the approximated quality indicates a promising candidate, the time-consuming exact evaluation is executed. The novelty of our approach is that (1) although the evaluation process is accelerated by using approximations, we do not forfeit the quality of the acquired solutions and (2) the integration in a background theory allows sophisticated reasoning techniques to prune the search space with the help of the approximation results. We have conducted an experimental evaluation of our approach by investigating the dependency of the accuracy of used approximations on the performance gain. Based on 120 electronic system level problem instances, we show that our approach is able to increase the overall exploration coverage by up to six times compared to a conservative DSE whenever accurate approximation functions are available.

### **Co-Authored**

[8] Christian Haubelt, Kai Neubauer, Torsten Schaub, and Philipp Wanko. "Design Space Exploration with Answer Set Programming". In: KI - Künstliche Intelligenz. Vol. 32.

2-3. Berlin Heidelberg: Springer Nature, May 2018, pp. 205–206. DOI: 10.1007/s13218– 018-0530-3.

**Abstract:** The aim of our project design space exploration with answer set programming is to develop a general framework based on Answer Set Programming (ASP) that finds valid solutions to the system design problem and simultaneously performs Design Space Exploration (DSE) to find the most favorable alternatives. We leverage recent developments in ASP solving that allow for tight integration of background theories to create a holistic framework for effective DSE.

[9] Joachim Falk, Kai Neubauer, Christian Haubelt, Christian Zebelein, and Jürgen Teich. "Integrated Modeling Using Finite State Machines and Dataflow Graphs". In: *Handbook of Signal Processing Systems*. Ed. by S.S. Bhattacharyya, E.F. Deprettere, R. Leupers, and J. Takala. Third Ed. Springer International Publishing, Oct. 2019, pp. 825–864. DOI: 10.1007/978-3-319-91734-4\_23.

Abstract: In this chapter, different application modeling approaches based on the integration of finite state machines with dataflow models are reviewed. Many well-known Models of Computation (MoC) that are used in design methodologies to generate optimized hardware/software implementations from a model-based specification turn out to be special cases thereof. A particular focus is put on the analyzability of these models with respect to schedulability and the generation of efficient schedule imple-

mentations. Here, newest results on clustering methods for model refinement and schedule optimization by means of quasi-static scheduling are presented.

[10] Luise Müller, Kai Neubauer, and Christian Haubelt. "Exploiting Similarity in Evolutionary Product Design for Improved Design Space Exploration". In: International Conference on Embedded Computer Systems: Architectures, Modeling and Simulation (SAMOS). July 2021.

Abstract: The design of new products is often an evolutionary process, where product versions are build on one another. This form of product generation engineering (PGE) reuses some parts of previously developed systems, while others have to be designed from scratch. In consideration of subsequent design steps, i.e., verification, testing, and production, PGE may lead to significant reduction of the time-to-market as these steps can be skipped for reused parts. Thus, deciding which components have to be replaced or added to meet the updated requirements while preserving as many legacy components as possible is one of the key problems in PGE. A further aspect of PGE is the potentially more efficient search for valid design candidates. An already optimized base system can be systematically extended by new functionality without the necessity to search the entire design space. To this end, in this work, we propose a systematic approach, based on Answer Set Programming, to exploit the ideas of PGE in electronic system-level design space ex- ploration. The idea is to gather information of the implementation of a previous design, analyze the changes to a new version, and utilize the information to steer the search towards potentially good regions in the design space. Extensive experiments show that the presented approach is capable of finding near-optimal design points up to 1,000 times faster than a conventional approach from scratch.

# 1 Introduction

Throughout the last decades, embedded systems have penetrated the whole spectrum of products in the market. They are nowadays ubiquitous and form with about 98 % [11, 12] the largest share of all microprocessor systems. Beside typical areas such as telecommunication, embedded systems are also utilized in traditionally mechanical sectors. Prominent examples include automobiles, airplanes, factory automation, clinical devices, and domestic appliances.

Embedded systems are characterized by a tight integration into a larger system where they fulfill a specific task and interact with the environment through sensors and actuators. They have to adhere to a number of constraints which can be roughly categorized into behavioral, functional, and extra-functional requirements. Behavioral constraints demand that the system behaves under all circumstances the same as specified for the desired task. On the example of a network router, the forwarding of a message to the correct destination is considered a behavioral constraint. Functional and extra-functional requirements, on the other hand, both refer to the properties of the system. While the former ones are imperative for error-free operation, the latter are considered quality constraints that are additionally imposed by the specification. Liveliness, e.g., an arrived message will eventually be forwarded by the aforementioned router, is a typical functional requirement while performance, area costs and power dissipation are typically considered to be extra-functional. However, the distinction between functional and extra-functional requirements is not always a clear cut but rather dependent on the specific case. In airbag controllers, for instance, the latency from sensing a collision to triggering the airbag must not exceed a few milliseconds to guarantee the desired functionality, i.e., save lives.

Additional to the compliance to the various constraints given by the specification, the time-to-market is an important factor in current and future designs of embedded systems. Due to worldwide competition, companies are forced to enhance design and decision processes in order to beat their competitors to new or optimized features. Simultaneously, more and more features with challenging requirements, both functional and extra-functional, increase the complexity of embedded systems constantly. Combined with the pressure on a short time-to-market, manual design is not viable anymore as the number of design options is too large.

Thus, automated approaches that are able to explore the vast search space and evaluate potential design candidates according to specified design constraints are needed for an efficient design. An important prerequisite for automated approaches is a formal description of the system that abstracts the properties and interaction of components of the system mathematically. This model-based design can be employed at various abstraction levels, i.e., depending on the required level of detail, properties of components are more or less precisely modelled. To date, most approaches explore the design space at high abstraction levels and only further refine potential candidates in lower abstraction levels. In the monograph at hand, automated approaches are investigated at the system-level. At the system-level, architectural decisions are

Figure 1.1: Design Space Exploration as a filtering process (inspired by [13])

made on the basis of task-level algorithmic descriptions of the system. Architectural decisions include the allocation of necessary hardware resources such as microprocessors, FPGAs, memories, and communication devices. Tasks are partitioned into hardware and software by binding them to the corresponding resources. The scheduling step finally determines the execution order of the tasks.

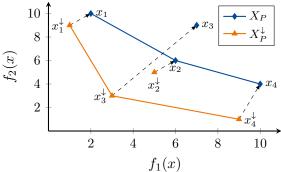

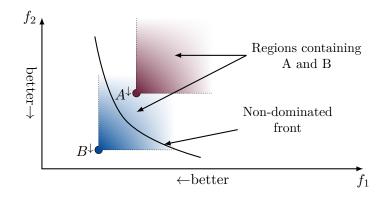

The results of the synthesis, i.e., all allocation, binding, and scheduling decisions that have been made, are considered as a design candidate that, subsequently, has to be evaluated. The entire process can be abstracted as a filtering process as depicted in Figure 1.1. The set of all potential design candidates X is first filtered by the feasibility filter. It guarantees that no designs with infeasible decision combinations are selected. This excludes, for example, solutions with unmapped or multiple mapped tasks, a broken communication infrastructure, and erroneous message routing. The set of feasible designs  $X_F$  is then evaluated with respect to specific objective functions. That is, the evaluation transforms the design from the parameter space into the objective space. In the objective space, the designs can subsequently be filtered by the validity filter resulting in the set  $X_V$ . A design candidate is considered valid if all specified constraints in the objective space are fulfilled. Beside the adherence to specified constraints, the desired result of a design space exploration (DSE) is often the optimization of its properties. In a typical embedded system, the optimization objectives are manifold and normally conflict with each other. As a result, there exists no single optimal design that dominates (i.e., evaluates better for all objectives) every other design. Instead, a set of Pareto optimal, mutually non-dominated design points (Pareto front  $X_P$ ) is obtained that renders the best compromise solutions to a given problem.

In summary, the challenges for an efficient design space exploration can be split into the modeling of the system, the evaluation of one design point, the coverage of the design space, and the optimization with respect to specified objectives:

**Modeling:** A formal model of the system is imperative for an automated design space exploration. It must be able to include all properties and constraints that are imposed by the specification. In this work, the first-order language of ASP is utilized to model both the specification and the rules that are implied by constraints and objectives. A synthesis problem is therefore split into two parts. First, the specific problem instance defines the properties of the individual parts of the system such as the existing task dependencies, hardware resources, and mapping options. Second, a general encoding defines rules for synthesizing the specification into an implementation. This leads to the advantage that the encoding can be utilized for every possible problem instance and does not have to be generated anew.

**Evaluation of Design Points:** The computational complexity of the evaluation step highly depends, among other factors, on the desired accuracy and the specific objective that has to be evaluated. At system-level, the primary goal is a fast exploration of the design space resulting

in a set of potential designs that are investigated further at lower abstraction levels (e.g., gate and transistor-level on the hardware side). While this indicates that the accuracy is of lower concern, excessively increasing the evaluation performance at the expense of accuracy may introduce non-optimal designs. Thus, a good evaluation constitutes a compromise to allow for good accuracy while maintaining high performance.

Covering the Design Space: Although the decreased level of detail at the system-level narrows the number of design decision significantly, the complexity of medium to large systems restricts the exhaustive exploration of the entire design space even at high abstraction levels. Hence, finding promising regions of the design space that contain feasible, valid, and ultimately optimal design candidates proves to be hard. Traditionally, population-based heuristics were employed to search for these regions. They start with an initial randomized population of individual design decisions whose parameters are subsequently combined and altered in order to create new design candidates. In general, this produces diverse and good solutions. There are, however, two main disadvantages with these strategies. First, as the initial population is created by a randomized process, finding regions with valid design points becomes a problem for stringently constrained environments. Second, because the search is generally not executed systematically but based on combining previously found solutions, heuristics tend to run into saturation and stop finding novel solutions after an arbitrary number of iterations. Thus, giving a guarantee that the whole design space will be explored is nearly impossible even when they are run indefinitely. Therefore, a formal approach is examined in this thesis that explores the design space systematically. With solving techniques derived from Boolean satisfiability problem (SAT) and satisfiability modulo theories (SMT) solvers, finding regions with potentially good design points is accelerated and the exploration coverage is, at least in theory, guaranteed to be complete. Especially if the constraints are too stringent, the problem can be proven to be unsatisfiable.

**Optimization:** Obtaining the set of Pareto-optimal designs points implies comparing each valid design candidate with every other design candidate. This can be done by first saving all valid designs with subsequent filtering of non-dominated ones or by only saving non-dominated solutions in the first place. For medium to large systems, the former method is not viable, as there might be billions of valid designs that only differ in marginal details. The latter, on the other hand, demands continuous comparisons of new design points with previously found ones which could influence the exploration speed negatively if the underlying archive is not managed efficiently. Independent of the specific method used, the optimization approach has to guarantee for a correct and complete result even if not the entire search space could have been explored. That is, with respect to all explored designs, the Pareto-set must not contain any dominated solutions (correctness) and has to include all non-dominated ones (completeness).

### 1.1 Contributions and Limitations

In this section, the main contributions and limitations of the thesis at hand within the individual areas described above will be collated. In summary, the result is a novel methodology for designing embedded systems at the system-level that parts from traditional heuristics by proposing an automated DSE that is based on ASP.

**Optimization** The main contribution of the thesis at hand is the successful merger of the two, previously isolated problems searching for Pareto-optimal design points and defining a feasibility preserving encoding. This has been accomplished by the tight integration of background theories into the solving process of the foreground logic solver under the programming paradigm of ASPmT. This way, the Boolean ASP solver automatically ensures feasibility constraints while non-linear objectives and the optimization are executed by specialized propagators. The main benefit of the proposed approach is the shared utilization of decision variables by both foreground and background solvers. That is, compared to separated or only loosely coupled solvers, conflicting decisions as well as dominated design candidates detected by the background propagators can be used to directly steer the search and prune invalid and dominated designs from the search space. Furthermore, the logical connection of both steps permits a succinct encoding. Instead of separated input languages, the thesis at hand proposes a uniform formulation of the entire DSE problem. Hence, feasibility and validity constraints can be encoded side by side and, more importantly, share information on decisions imposed by other constraints. Finally, as variables are shared in the foreground and background solvers, the repeated exploration of the same design points is actively prevented. Due to the strict systematic search, decisions that are shown to be infeasible or invalid by the ASP engine and background propagators, respectively, are definitively removed from search. While this can also be achieved with disjoint solvers, the shared variables provide the opportunity for the specialized propagators to obtain minimal reasons. Hence, larger regions of the design space can be pruned compared to individual solutions that are evaluated externally without shared variables.

The main limitation of the proposed optimization approach stems from the complexity of the considered systems. As the system synthesis is proven to be NP-complete, the time required to solve an instance grows exponentially with its size. Although the approach guarantees finding each solution theoretically, in reality, a complete exploration of the search space is generally not viable in a reasonable amount of time.

**Evaluation** In order to obtain valid solutions to a specific synthesis problem, an evaluation has to be performed for every explored design candidate. Typically, a design candidate can only be evaluated for validity if a complete assignment is available. In this thesis, a novel approach allowing the evaluation of partial assignments is proposed. Enabled by the tight integration of the search and optimization through the ASPmT paradigm, as described above, design candidates can be checked early for constraint violations. That is, as the variables are shared between foreground and background theory, whenever a Boolean decision is taken, the specialized propagators can check whether the solution can still be satisfied. This allows for the detection of invalid regions early during the search and, thus, the pruning of entire invalid and dominated regions of the design space. Experimental results (q.v., Section 3.4.2) show the superiority of the proposed approach. While with an evaluation of full assignments only, less than 25 % of all problem instances have been solved, the proposed approach utilizing partial assignment checking has yielded a success rate of more than 90 %.

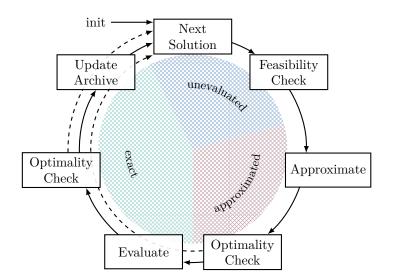

As partial assignment checking imposes a larger number of evaluations to be carried out, the evaluation is identified as a bottleneck of the DSE. Therefore, the thesis at hand proposes the utilization of approximations for the majority of evaluations before exact evaluations are only executed for promising candidates. The proposed approach builds upon the use of safe approximation. As such, compared to previous work, the correctness and completeness of the obtained non-dominated solutions can be guaranteed although only a fraction of all designs is evaluated exactly. The approach is experimentally evaluated and is shown to accelerate the DSE by up to one magnitude for the considered instances and objectives.

Similar to the evaluation, the number of necessary dominance checks also increases with the partial assignment checking. To tackle this problem, the thesis proposes an archive management technique that can be used to relay expensive operations to when the solution is completely decided. The remaining checks conducted for the partial assignments require significantly reduced dominance checks while retaining completeness and correctness. Compared to a traditional management structure, the proposed approach shows an improvement of both filtering time and the number of necessary comparisons by about one and two orders of magnitude, respectively.

The evaluation is executed on the basis of abstract properties that are annotated within the specification model. In reality, these properties have to be obtained through thorough investigation. The execution time of a task on different resources, for instance, can be obtained by compiling the task for different architectures. While realistic assumptions are aspired, the data source of these properties is not the primary scope in this thesis. It is assumed that the properties are known when starting the design space exploration. A second limitation is the restriction of partial assignment checking for assignment monotonic objective functions. That is, with every additional decision, the evaluation result must constantly move into the same direction for one objective. All objective functions used here are assignment monotonic. The utilization of safe approximations is, in addition to the requirement of assignment monotony, restricted to objectives that can be consistently approximated. If no such approximation can be determined, the DSE is equivalent to a traditional approach that has to exactly evaluate all design candidates.

**Guided Decoding** The design space of realistically sized problem instances is essentially constituted of vast numbers of mapping, routing, and scheduling options. In general, feasible design candidates are located within narrow and separated regions of the design space. That is, many combinations of the individual decisions may either lead to infeasible or similar design candidates. The main goal of the DSE is therefore twofold. First, pruning infeasible regions from the search and second, finding disconnected regions to obtain diversified designs. In contrast to previous approaches, in the present work, the DSE is carried out strictly systematically. Hence, advancing from one solution to another is steered by the previously found solution, the encountered conflicts, and dominance checks. This is different to the mainly heuristic approaches advancing entirely or at least partially randomly through the design space. The proposed approach has the advantages that no design candidate is explored twice and that every design point is eventually found in finite time. Furthermore, invalid regions, if detected, are not considered for further exploration as they are automatically pruned from the search.

At the downside, the strictly systematic search may prevent finding diverse solutions fast. The strict systematic Boolean search tends to vary subsequent solutions only marginally as small changes in the individual decisions, equally yield small changes in the resulting solutions. Especially, complex problem instances contain large amounts of designs that are technically different but are characterized by similar properties. Thus, the escape from local optima during the search is generally less effective when compared to approaches where optimization and encoding is logically separated and applies random decision into the search. **Modeling** The central contribution of the thesis at hand is the overall methodology. However, to evaluate the proposed methods regarding the DSE at the ESL, an appropriate specification model is imperative. This monograph does not develop a completely novel model but instead builds upon well-established, graph-based models at the ESL. Therefore, a model is chosen that permits the definition of task-level applications, a hardware platform template implementing a network on chip (NoC) and mapping options connecting the previous two. In the context of evaluation, a methodology is proposed to systematically generate problem instances to test the proposed approaches with defined problem classes.

The selection of the specification model implies some limitations on its own. First, the applications are statically defined. That is, no dynamic information such as data-dependent behavior, interrupts or sporadicity is supported. That is, all information that is specified in the model has to be known at design time. This includes the availability of hardware resources, task dependencies, and mapping options. Furthermore, no automatic dynamic reconfiguration is possible if unforeseen events such as resource failure happen at runtime of the system. In this case, a new synthesis had to be carried out.

### **1.2 Thesis Overview**

Most of the approaches proposed in this monograph have previously been published by the author at peer-reviewed conferences, workshops, and journals. This monograph aggregates the results of the respective works and puts them into the context of a holistic view on the DSE at the ESL. To this end, the formulation is unified, refined, and extended by more extensive experimental evaluations. In the following, the structure of the remainder of this monograph is outlined.

Prior to the main chapters, the fundamental concepts of model-based design are presented. Chapter 2 deals with all topics that are necessary to fully comprehend the subsequent chapters. The introduction of the general process of system design is followed by the necessary definitions regarding model-based constraint checking with logic solvers and the basics of multi-objective optimizations. The chapter concludes with an elaborate discussion of related work, where existing approaches are compared to the proposed solutions in the thesis at hand.

Chapter 3 addresses the synthesis at the ESL. It is based on the work, that was previously published in [2] and [5]. The system model is defined and the integration of background theories under the ASPmT paradigm is discussed. Orthogonal to the proposed ASPmT-based synthesis framework, a methodology for a modular test case generation is proposed. This is subsequently used to evaluate the developed framework.

The holistic DSE is elaborated in Chapter 4. It extends the proposed synthesis framework with multi-objective optimization and is primarily based on the work in [4]. After the evaluation of different approaches to the DSE problem regarding the obtained quality of the non-dominated front, improvements to the substeps dominance checking and evaluation are proposed. The former is based on the methods proposed in [3] and aims in reducing the complexity of the Pareto filter by utilizing specialized data structures. The latter has been previously published in [6] and [7]. Here, the use of safe approximations is proposed that aim at accelerating the evaluation of a design candidate while retaining the correctness of the obtained front.

The thesis concludes with Chapter 5, where the contributions and limitations of the proposed approaches are summarized and an outlook of future work is given.

### 1.3 Funding and Cooperation

The monograph at hand is part of the result of the cooperation between the chair of *Embedded* Systems at the University of Rostock and the chair of Knowledge Processing and Information Systems at the University of Potsdam. It was funded by the German Science Foundation (DFG) under the grants HA 4463/4-1 (Rostock) and SCHA 550/11-1 (Potsdam) with the title Scalable Design Space Exploration with Answer Set Programming (original title: Skalierbare Entwurfsraumexploration mit Antwortmengenprogrammierung) [14].

In this cooperation, the work was essentially split into the enhancement of the utilized ASP solver clingo and the application to the problem at hand contributed by the University of Potsdam and the design space exploration methodology contributed by the University of Rostock. The spent effort of the University of Rostock was mainly accomplished by the author of this monograph. The work on the solver includes the development and integration of the ASPmT paradigm and the implementation of a dedicated integer difference logic solver. Therefore, the internal realization and theory of the ASP solving mechanisms have not been contributed by the author of this monograph but instead by the cooperating partners at the University of Potsdam. It shall be noted, however, that the basics of the implementation are also discussed in the monograph at hand (see Sections 3.2 and 3.3) as the systems will be used as a tool in further considerations.

While the ASPmT technology developed in context with this work has a more general application, the main focus of the work conducted by the author has been related to domain specific problems. This includes both the definition and encoding of necessary parameters of the specification as well as the necessary information that shall be considered for optimal design points (i.e., objective functions). In addition, non-ASP related optimizations to the design space exploration have been studied by the author of this monograph. In particular, this concerns the archive management technique based on Quad–Trees (see Section 4.2) and the proposal for the use of safe approximations (see Section 4.3) to accelerate the Pareto filtering and evaluation substeps, respectively. Furthermore, the conceptual design of the conducted experiments within the individual sections and chapters as well as the generation of test cases (see Section 3.4) have been realized by the author.

The synthesis and optimization architectures, proposed in Sections 3.3 and 4.1, respectively, are the result of the combined efforts of both project partners. They are build on both the developed internal solver mechanisms and the design space exploration methodology. Hence, these architectures provide the common result of the cooperation between the University of Potsdam and the University of Rostock in this project.

# 2 Model-based Design

The work at hand cannot be considered in isolation but is instead embedded in a much wider context in the area of design space exploration at the electronic system level (ESL). It is based on well established concepts that are partly combined and extended particularly towards exact design exploration methodologies. To motivate these general concepts, the goal of the present chapter is the introduction of model-based design techniques and theory solvers.

Therefore, first, the typical design flow of digital systems is described, detailing design steps at different levels of abstraction from system level to logic and instruction levels. Here, it will be shown that commencing at system level benefits the entire design process regarding exploration speed and coverage. In the second part of the chapter, well established concepts regarding multi-objective optimization that are utilized throughout this work are outlined. Within this section, exact solving approaches are motivated and expounded why they are especially well suited for highly constraint design problems. Finally, an extensive investigation of related work is presented at the end of this chapter where main contributions of the work at hand are elaborated and set into context.

### 2.1 Hardware/Software Co-design

The design of application-specific embedded computer systems is an intervoven process of simultaneous hardware and software development. The development of such systems has a tradition of over 70 years now. Starting with the first universally programmable computers Z1 (1938) to Z4 (1945) [15], through computer-aided space exploration to current systems in everyday life, the complexity has been risen constantly. Today, billions of nanoscaled interconnected devices are integrated in only a few square centimeters that run software that has to fulfill strict performance and power constraints. Such complexity necessitates highly automated approaches.

However, even with modern high-performance computers and algorithms, the vast design space is often too large to optimize every least detail of the system. Thus, a system is typically grouped into larger building blocks that abstract various details and are used to minimize the overall design complexity. For example, individual transistors are grouped into logic gates, logic gates into functional units, and finally functional units into processing and communication resources. At software side, individual instructions are clustered into basic blocks, functions, and finally abstract tasks. As a result, the design space of a digital system defined with the largest building blocks is smaller and can be explored faster. The downside is that many details cannot be expressed at the highest abstraction levels. Hence, current design methodologies utilize different abstraction levels and consequently refine the resulting system gradually throughout the design process.

Figure 2.1: Double roof model of systems design (adapted from [16]).

#### 2.1.1 Design Process

The employment of different abstraction levels in the design process is typically a top-down process. The double roof model of design [16], as depicted in Figure 2.1, is a concrete methodology implementing such a process. It is divided into a hardware and a software side with both meeting at the center, where the system level is located. Hardware and software are in turn divided into further abstraction levels, that involve the respecting building blocks as described above. Within each abstraction level, the goal is the transformation from a behavioral specification into a structural implementation which involves decision-making and optimization. These steps are indicated by the vertical arrows in Figure 2.1. The horizontal arrows, on the other hand, represent the refinement steps from one abstraction level to the next. Here, the structural implementation as the result of a higher abstraction level is (partially) transformed into a behavioral description and used as input at a lower abstraction level. This way, the design process gets gradually more detailed until the system description is detailed enough to manufacture the hardware and execute the software as machine code on the corresponding computational resources.

At system level, the fundamental design decisions are made. The decision-making process includes the allocation of available computational and communication resources, the partitioning of functionality into hardware and software, and the task scheduling, i.e., the order of task executions and identification of serial and parallel structures. The structual implementation reflects the taken design decisions and can further be represented as transaction-level system simulation models or as as graph-based models. Subsequently, the result of the design is then split into hardware and software, and relayed to the subsequent thread and architecture abstraction levels, respectively. At thread level on the software side, communicating processes/tasks have to be bound to available processors and scheduled according to the underlying operating systems. The software synthesis at the thread level typically results in source code, structured into classes, functions, and basic blocks. It is subsequently used for compilation in the final step at the software side. At block level, the previously generated source code is compiled and linked and results in machine-readable code for the respective processors. On the hardware side, first the computation and communication is implemented at the architecture level. That is, tasks and desired capabilities of the system that have been decided to be implemented as hardware accelerators are elaborated. Mainly, the selection and interconnection of various memories, arithmetic logical units (ALUs), and communication infrastructures is subject at this level of abstraction. This synthesis step can also be automated, which is commonly known as high level synthesis. The resulting register transfer level (RTL) description is often realzied in form of hardware description languages such as VHDL [17] or Verilog [18]. At the logic level, the lowest abstraction on the hardware side, the register transfer level (RTL) description is transformed into logic gates like flip-flops, inverters, and Boolean gates. Admittedly, the hardware synthesis continues even further at transistor level (not shown in Figure 2.1). Here, the Boolean logic is compiled into individual transistors, wires, and their spacial placement necessary for the final physical implementation on the die.

Beginning the design process at the highest level of abstraction, the system level, is largely motivated by two considerations. First, the high abstraction at system level conceals details of specific parts of the digital system. Hence, the focus is shifted towards more fundamental decisions which can be explored and evaluated more quickly which, in turn, increases the exploration coverage. That is, decisions made at system level have potentially the largest impact on the final design as they define the golden reference of all subsequent steps. Second, while in traditional approaches, the firmware and software development is dependent on the hardware design process, both design steps can be started concurrently on the basis of the system-level implementation (e.g., represented by a virtual prototype). Although the overhead of obtaining this implementation may be significant, it can reduce the overall development time. Moreover, as first evaluations of the system properties are already applied here, potential flaws in the specification resulting in over- or underdesigned systems can be detected. This helps to prevent late errors that are, in general, harder to fix and result in longer turn around times.

Note that a strict top-down approach is not always possible nor desirable in real world designs of digital systems. A company may use subsystems available from previous projects or may choose to obtain parts of the system as 3rd-party intellectual property (IP). These parts do not have to be designed again and can directly be used in new systems resulting in a hybrid approach. For example, a processor is typically not designed from scratch, but instead bought as an off-the-shelf subsystem with predefined properties and interfaces. On the other hand, design-specific functionalities such as sensor subsystems might not be available through 3rd-party IP and have to be designed in a top-down process. This hybrid strategy is, however, not in conflict with the general approach. Moreover, the known properties of existing parts can be utilized to simultaneously increase the evaluation accuracy in high abstraction levels and decrease the time-to-market of the digital system.

#### 2.1.2 Modeling Approaches

In order to allow a holistic specification and an automated design of digital systems, a sophisticated design methodology is needed. In principle, there are two different ways to specify digital systems. First, language-based approaches and, second, model-based approaches [16]. Language-based approaches are, generally speaking, dedicated to specific abstraction layers of the design process. The hardware design is mostly exclusively executed with the hardware description languages (HDL) Verilog and VHDL as they provide solutions from the architectural view to the logic level of the system. Typical HDL often do not support the same tool-supported development processes as modern high-level languages in software development. As a result, development of complex software in VHDL or Verilog is often error-prone and time-consuming. Therefore, they are less suitable for the software design process. Here, high-level languages such as C, C++, and Java (among others) are more prominently used. Yet, without modifications,

they lack the concept of concurrency and do not cover timing behavior and are therefore not adequate for the description of hardware. System-level design languages (SLDLs) (e.g., SpecC and SystemC) aim at a combined specification of both hard- and software. SystemC [19], for example, is an extension library to C++ and contains structures for specifying concurrency and timing constraints while maintaining compatibility to standard C++. An event-based simulator can be used to evaluate the design for correctness regarding behavior and timing constraints. Furthermore, there exist high-level compilers that allow to translate a subset of SystemC into RTL descriptions and synthesize it into logic. While the language-based design is highly expressive, i.e., various behaviors can be specified with a limited set of basic elements, it generally lacks of clearly defined formal semantics. Both, the high expressiveness and the absence of formal semantics often deteriorate the analyzability of extra-functional properties such as timing, cost, or energy consumption of the specified system. In turn, this disqualifies language-based approaches for automated exploration, especially at high levels of abstraction.

In contrast, model-based approaches offer strict formal semantics. They are abstracted through mathematical models that reduce the expressiveness and, thus, allow for an improved analyzability. Typical approaches for modeling systems include finite state machines (FSMs), Petri nets, timed automata, and dataflow models. In the area of transformative embedded system design, dataflow models are often used as parallelism of the underlying application can be easily identified [20]. Dataflow models consist of individual actors that communicate over channels. The actors model the behavior of processes and consume and produce data (i.e., tokens) from and to connected channels, respectively. This way, especially streaming applications can be naturally modeled. Besides the modeling of the functional behavior of an application, the formal semantics of synchronous dataflow models<sup>2-1</sup> also allow for the evaluation of extra-functional properties. Especially, the buffer size (for FIFO channels) and the maximum throughput analysis are well studied throughout literature (e.g., [21–23]). Although hierarchical dataflow models can be used to represent mapping and scheduling decisions (e.g., [20]), dataflow typically only models the behavior of an application.

Again, the hardware is typically abstracted and is reduced to the properties that are needed to evaluate the desired properties such as individual costs, power consumption, and processing abilities. While both hard- and software models can be extended with respect to their expressiveness, especially at ESL, this hinders automated design space exploration (DSE) as evaluation performance and analyzability will deteriorate with increasing model complexity.

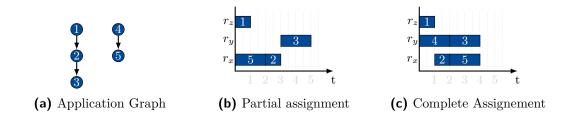

#### 2.1.3 Synthesis