# Condition Monitoring of Power Electronic Systems through Data Analysis of Measurement Signals and Control Output Variables

Firat Yüce and Marc Hiller, Member, IEEE

Abstract-A major disadvantage of existing condition monitoring methods is the need for additional sensors and measuring equipment. In this work, this disadvantage is eliminated by completely avoiding additional hardware. Instead, software-based methods from the field of machine learning are used. Therefore, measurement signals and control output variables are utilized which are acquired and processed in any power electronic system for the purpose of converter control. The publication focuses on two main converter components: power semiconductors and DC link capacitor. For each component, the aging mechanisms that have been studied in the literature are explained. Based on the aging mechanisms, the degradation indicators are identified. Then, a converter model is built that allows the variation of degradation indicators in order to analyze their effects on the available data set. These findings form the basis for mathematical models, which detect future failure mechanisms of this type during converter operation. The test setup must offer the possibility of generating reproducible failure cases in various components with the aid of additional failure equipment. Finally, failure mechanisms are intentionally introduced at the test bench in order to validate the methodology of the developed approach.

Index Terms—Condition Monitoring, Machine Learning, Reliability, Power Semiconductors, DC Link Capacitor.

### I. INTRODUCTION

OWER ELECTRONICS is a key technology for sustainable energy generation and environmentally friendly mobility. Power converters are used to transform regeneratively generated energy from wind and sun to the power grid or to transmit electrical energy over long distances with highvoltage direct current transmission. Thanks to modern power electronics, it is possible to convert energy very efficiently over a wide power range - from a few watts in the power supply of cell phone chargers to many megawatts in the energy sector. Power converters are also a central component of any electric, variable-speed drive system. In industry, electric drive systems play an essential role. Factories are equipped with numerous electrically driven machine tools and industrial drives, which increase the degree of automation of many processes and improve productivity. The increasing share of renewable energies in power generation, the growing share of electric vehicles in private transport and the modernization of existing industrial plants are leading to a growing number of power converters.

The requirements for power electronics in energy and drive

technology are becoming more challenging. In addition to power density, functionality and energy efficiency, the reliability of power electronic systems is playing a significant role. The reliability of a system is the probability that an item will perform its intended functions for a specified time interval under specified conditions [1]. In the following, the concept of maintenance-based reliability improvement is presented.

# A. Maintenance-based Increase in Reliability

One way to increase the reliability of a system is to use maintenance, which is performed during the operational phase. In maintenance-based reliability, we distinguish between preventive and predictive maintenance. In the former, maintenance is performed at fixed time intervals. Often, these time intervals are based on the experience of plant experts who estimate the natural lifetime of a component. In predictive maintenance, the time for maintenance is based on the condition of the asset. This requires knowledge about the condition of the system, which condition monitoring is intended to provide. Condition monitoring is a monitoring concept that aims to detect the condition of a system during operation and thus, provide early information for necessary repair and maintenance work. The information provided by condition monitoring enables the selection of optimal maintenance intervals and the reduction of downtimes of the system. The present publication is in this subject area.

## B. State of the Art

There are three principal approaches of condition monitoring of power converters. The approaches are illustrated here based on the component power semiconductor devices. They can also be applied to other components of the power converter system.

1) Monitoring of Degradation Indicators: On the one hand, degradation indicators can be monitored. Degradation indicators provide information about the condition of the converter. A degradation indicator can be captured using both direct and indirect methods. Direct methods make use of a measurement circuit, while indirect methods use model estimations. Usually, both methods make use of additional measurement equipment. The following are some examples of this approach which utilize various degradation indicators. In [8], a measurement circuit was developed that measures the collector-emitter voltage of the IGBT in the on state in order to detect the aging mechanism *bond wire lift-off.* In [7], a method is presented

F. Yüce and M. Hiller are with the Department Institute of Electrical Engineering, Karlsruhe Institute of Technology, 76137 Karlsruhe, Germany e-mail: (firat.yuece@kit.edu; marc.hiller@kit.edu).

IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS 2021

to detect the aging mechanisms solder fatigue and bond wire lift-off by online monitoring of the two degradation indicators: thermal resistance between junction and heatsink  $R_{\rm th}$  and differential resistance of the collector-emitter path  $r_{\rm CE}$ . The parameters are estimated by an indirect method using a measurement circuit. In [22], the chip temperature is estimated using an analog measurement circuit that evaluates the turn-off time of the IGBT with the aim of detecting wearrelated aging mechanisms. Additionally to the forementioned, the contamination of the cooling system is investigated in [23]. Therefore, low-frequency power losses are applied to the IGBT for a short time during operation. Then, the temperature cycles are determined and the chip temperatures are calculated using a thermal model. With this, the maximum and minimum values of the chip temperature are evaluated. An increase in the maximum temperature indicates the aging mechanism solder fatigue and an increase in the minimum temperature indicates the aging mechanism contamination of the cooling system [23].

2) Aging-based Modeling: Another approach is modelbased aging prediction. This approach models a specific aging mechanism that leads to converter failure. Therefore, detailed knowledge of the aging process is required. For example, the aging mechanism loss of blocking capability due to increased leakage currents because of *humidity* can be modeled using thermo-mechanical and electrochemical models [24]. In order to estimate the remaining lifetime the load cycles are counted during converter operation. This usually acts as an input variable for the developed aging models.

3) Software-based methods: A major disadvantage of the two methods presented so far is the need for additional sensors and measuring equipment, which entails additional costs and sources of failure. The software-based approach overcomes this disadvantage and operates without additional hardware. This results not only in a cost advantage, but also in a higher reliability of the power converter system due to the removing of additional potential failure sources.

In [26], 224 MOSFET power semiconductors from 10 different manufacturers are undergone to a radiation test in the laboratory in order to collect data. Both the static behavior and the dynamic behavior of the devices when they experience thermal and radiological stress are considered. These collected data are used for the training process of machine learning algorithms. Several algorithms such as logistic regression, random forest and gradient boosting classification are evaluated. Failure-In-Time (FIT) is calculated as an output quantity, which indicates the expected failure rate per time unit.

There are also publications that have focused on system identification to determine the condition of components. [27] focuses on system identification and briefly discusses how to use system identification for health monitoring and fault detection. In [28], it is discussed in detail how a system identification can be used in order to apply a fault detection of the components of a DC-DC converter. The publication deals with fault detection using a model-based state estimator approach. The error residuals based on signals from the converter and the state estimator output are evaluated. For each system component (capacitance, series resistance, power devices) fault signatures are collected. The procedure is validated with the

help of an experiment, also analyzing the dynamics and the speed of the procedure.

2

Publication [29] focuses on high frequency Gallium Nitride (GaN)-based power converters. Especially, the aging mechanism *solder fatigue* is considered. As a failure precursor of GaN devices, the drain source resistance  $R_{ds,(on)}$  is evaluated. In converter operation, the data is collected by monitoring voltage, temperature and current. From the captured data  $R_{ds,(on)}$  is identified by using an algorithm that follows Bayes theorem. Thereby, the probability density of the unknown model parameters are calculated, with which the resistance  $R_{ds,(on)}$  is determined.

Recently, several publications have been published in the field of digital twins of power converter systems. A digital twin is a virtual representation that operates as the real-time digital model of a physical object.

In [30], the application of a digital twin based on a general methodology for maintenance optimization is studied. The objective is to find the most cost-effective maintenance strategy for an operational lifetime. Therefore, a real-world power converter use case is investigated.

In [31], a digital twin of a DC-DC converter is established with the aim for condition monitoring of the system components. Firstly, the DC-DC converter is modelled with unknown parameters. In order to estimate the unknown model parameters a Particle Swarm Optimization (PSO) algorithm is applied. The algorithm uses an objective function, which calculates the difference between the model results of the digital twin and the measurement results with regards to the output quantities as inductor current and output voltage. The aim is to minimize the objective function by means of the PSO algorithm and thus to determine the model parameters which act as health indicators. By observing the health indicators, the degradation trends of the system components such as capacitor and MOSFET can be detected.

In [32], a digital twin of a of a PV energy conversion unit which consists of a PV source and a power converter is designed. In the operational phase, the difference between the estimated and measured output is evaluated in order to generate an error residual. Similar to [28], this so-called fault signature is detected in order to identify the fault type. The detection and identification of ten different faults are shown by means of experimental results.

In order to classify the proposed approach between the mentioned publications, the most important characteristics and features are listed here. The special feature of the proposed approach is that it operates on system level. Since the controller output variables are used for the analysis, it is theoretically possible to detect all changes at system level. However, this is coupled with the requirement that the different aging mechanisms and the effects on the investigated data must be differentiated. The publication focuses on the two converter components power semiconductors and dc link capacitor, whereby the approach can be extended to other system components such as the current sensors, the cooling system and mechanic components. As failure mechanisms, the heating of the power semiconductor chips and the capacitance loss of the dc link capacitors are investigated.

In this proposed approach, the power converter model is not used as a virtual representation, however, it is used in order to perform aging simulations and thus to create new models that recognize certain patterns in the existing data. This means that there is no requirement that the power converter model must have the exact same output results as the real-world converter like in the digital twin method. Since the presented approach works with data sets, methods and tools from data analysis are used. Hence, the proposed method is a hybrid of data-based and model-based approach. For data collection, outlier detection, and anomaly detection, data-based methods are used. For the root cause detection, the knowledge of aging simulation is used to generate mathematical models.

#### II. PROPOSED APPROACH

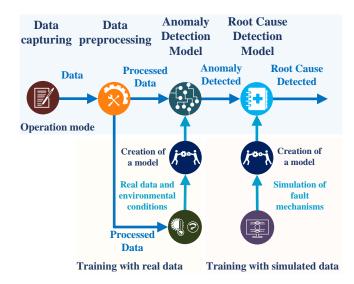

In this work, an approach to condition monitoring is developed that does not require additional sensors and only uses the available data. The block diagram of the approach is shown in Fig. 1.

Fig. 1. Approach to condition monitoring consisting of four steps: data capturing, data preprocesing, anomaly detection and root cause detection

The first step of the approach is data capturing. Here, the data relevant for condition monitoring are saved. In the context of this work, all output control variables of the control system are collected. The next step is data preprocessing. Statistical methods are used to detect outlier data points [20][21]. Those points are eliminated from the data set. Then, the processed data is passed to the data analysis, which consists of a two-step procedure: anomaly detection and root cause detection. In order to distinguish distinguish between aging mechanisms of the power electronic components and changes in the operational or environmental conditions a preliminary stage of anomaly detection is implemented. The anomaly detection model aims to detect an anomaly within the data set. This

model aims to detect an anomaly within the data set. This algorithm is trained with real data. The underlying algorithm is a computation paradigm that determines the severity of an anomaly. The procedure can be considered as a kind of data library. In the training phase, this data library is filled with

the data of the converter reference behavior with inclusion of operational and environmental conditions. Environmental conditions can be any parameters such as outdoor temperature, humidity, vibration, etc., depending on the practical application. For the purpose of this publication, the power module temperature has been included into the data set. Since power electronic components such as power semiconductor devices are very sensitive to temperature, this information is necessary. In the training process, the normal behavior is described by means of a mathematical model. During converter operation, the new incoming operating data is collected and compared with the data from the data library, which was recorded during the training phase, including all relevant environmental and operating conditions. This ensures that a correct comparison is made between the data recorded in the training process and the new incoming data set.

3

If an anomaly is detected, the data set is passed to the root cause detection model. The goal of the root cause detection model is to locate the cause of aging as well as determine the severity of aging. The root cause detection model is a machine learning algorithm trained with simulation data from different failure cases. Machine learning generates knowledge from experience by learning patterns based on existing data. These identified patterns can be generalized and applied to a new, unknown data set in order to make predictions. For the data generation, simulation models are required that are able to simulate failure cases at different levels. The application of this principle for the early detection of power converter failures is the focus of this publication.

The data preprocessing and the anomaly detection have been introduced in our previous publication [2]. Therefore, these aspects will not be described further in this current publication. The root cause detection has already been discussed in our publication [3]. In this publication, however, a more detailed explanation is given by specific examples in chapter VI-B.

## A. Following Structure

In the chapter IV, a simulation model is developed, which is used to simulate specific failure cases. In section IV-A, the converter is modeled with ideal components. In the section IV-B, the model will be extended to include degradation indicators. This will enable the simulation of various failure scenarios. Before that, however, the aging mechanisms and the corresponding degradation indicators will be determined in section III.

Then, the correlations between the degradation indicators and the available data are evaluated in chapter VI-B. For each aging mechanism, patterns are identified that represent a specific feature of the failure case that has occurred. Such specific patterns, which can be used to determine the failure case, are called features in the field of machine learning. A feature denotes a characteristic attribute or property of a observed phenomenon. Features provide an indication of the failure case and allow differentiation between different failure cases.

Based on the determined correlations, suitable mathematical models are trained in chapter VI-B. These models are capable

of detecting failure cases using the available data. In order to test these created models, specific changes and manipulations are induced to the converter system at the test bench as given in chapter VII.

# III. AGING MECHANISMS AND DEGRADATION INDICATORS

The publication focuses on two converter components:

- 1) Power Semiconductors

- 2) DC Link Capacitor

For each component, we will explain several aging mechanisms that have been studied in the literature. Based on the aging mechanisms, the degradation indicators are identified.

# A. Power Semiconductors

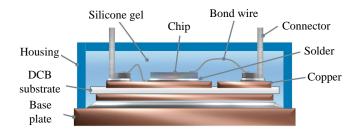

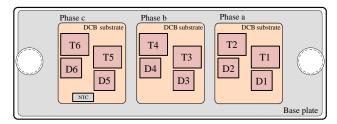

In commercial markets, three-phase bridges are nowadays offered in compact, so-called power semiconductor modules. This type of housing was first introduced to the market by the manufacturer Semikron in 1975 [4]. The required IGBTs and diodes are integrated into one housing. The structure of a power semiconductor module is shown in Fig. 2.

Fig. 2. Structure of a power semiconductor module [5]

Many aging mechanisms of power semiconductors occur at the module level [6]-[12]. The reason for this is the layered structure. Different materials are used for the individual layers, which have to fulfill various tasks and conditions [12][13]. As a result, the thermal expansion coefficients of the involved materials used can differ. During load cycles, temperature cycles occur, which lead to different expansions of the individual materials and thus also to thermo-mechanical stresses at the interfaces. Over time, this leads to cracks and fractures at the interfaces.

The interface between the bond wires and the semiconductor chips is a failure-prone spot. The bond wires of the power semiconductor module are usually made of aluminum and the semiconductor chips of silicon. The thermal expansion coefficients of the two materials differ by a factor of almost eight [6]. Aging mechanisms at this spot are referred to in the literature as bond wire failure [7]-[9]. This failure mechanism is divided into the two subgroups bond wire cracking and bond wire lift-off, depending on whether a fracture or a complete separation of the bond wire has occurred.

The separation of a bond wire results in a smaller crosssection area for the current and therefore to a larger ohmic resistance. This relationship is further investigated in [7] in which individual bond wires are cut off and the increase in differential resistance is detected. In section IV-B, the differential resistance of the conduction characteristics is explained and then integrated into the converter model from section IV. Another wear-out failure describes the aging of the solder and is called solder fatigue [10]-[12]. According to Fig. 2, the solder is the connecting link between the semiconductor and the copper metallization. This junction, which consists of the material tin, is prone to failure. Due to the differences in thermal expansion coefficients, thermo-mechanical stresses occur at the solder when temperatures fluctuate, leading to cracks and delamination over time.

4

There are two degradation indicators that provide information about solder fatigue. In [10], it is shown that solder fatigue leads to a change in conduction characteristics of the collectoremitter path. Furthermore, in [7] the correlation between the thermal resistance from the chip to the heat sink and the condition of the solder is determined.

# B. DC Link Capacitor

There are three different capacitor types: electrolytic, film and ceramic capacitors [14]. The material used for the dielectric medium is the crucial component that determines the performance and properties of the capacitor. In this publication, the film capacitor is investigated in more detail. Film capacitors provide a balanced performance in terms of cost, equivalent series resistance (ESR), capacitance, ripple current and reliability [14]. However, the low operating temperature must be considered since polypropylene has a low melting temperature of around  $165 \,^{\circ}$ C [25].

An essential degradation indicator that provides information about the condition of a capacitor is its value of the capacitance [14][15][16]. This applies to all capacitor types. In terms of reliability, film capacitors have an important unique characteristic of self-healing capability. Locally occuring dielectric breakdowns (e.g., due to overvoltage) of a film capacitor can be eliminated with the capacitor regaining its full operational capability except for a negligible reduction in capacitance. However, the total capacitance may be reduced over time due to an increase in such damaged areas. It is assumed that 95% - 98% of the original capacitance value is the limit for the usability of a film capacitor [14].

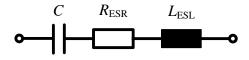

In addition, the ESR can also be used to estimate the condition of a capacitor [17][18][19]. Figure 3 shows the simplified impedance model of a capacitor, which consists of three components: the capacitance, the ESR and the equivalent series inductance (ESL).

Fig. 3. Simplified impedance model of a capacitor

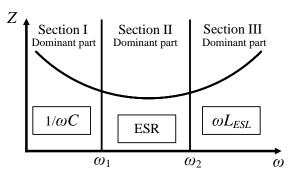

Figure 4 illustrates the corresponding frequency diagram, which is determined by these three components and can therefore be divided into three frequency ranges. Depending on the frequency, one or the other component such as the capacitance, the ohmic resistance or the inductance is the dominating component. For electrolytic capacitors the degradation limit

IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS 2021

is reached, when the ESR doubles [14].

Fig. 4. Simplified impedance diagram of a capacitor

# IV. MODELING

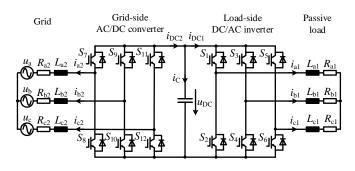

In this publication, an inverter with three-phase rectifier, a DC link and a DC/AC inverter on the output side is investigated. Figure 5 shows the circuit topology. This circuit is one of the most important circuits in the field of power electronics. It is used in many important applications, for instance, in the field of industrial robots and renewable energies.

Fig. 5. Inverter with rectifier, a DC link and a DC/AC inverter

This circuit is described with the use of differential equations. Subsequently, these equations are transformed into the state space equation. In chapter IV-A, the components of the power electronic system are considered ideal. Accordingly, the power semiconductor components behave like ideal switches, which assume the value S = 1 when the switch is closed and S = 0 when the switch is open. In chapter IV-B, the degradation indicators are additionally considered and implemented in the converter model.

# A. Converter Model

The state space representation is described by the first order state differential equation (1) and by the output equation (2).

$$\dot{x} = A \cdot \vec{x} + B \cdot \vec{u} \tag{1}$$

$$\vec{y} = C \cdot \vec{x} \tag{2}$$

Here,  $\vec{x}$  denotes the state variable,  $\vec{y}$  the output variable and  $\vec{u}$  the input variable. The coefficients A, B and C are matrices. The state variable  $\vec{x}$  contains the load-side and gridside currents as well as the DC link voltage (3). The output variable  $\vec{y}$  is identical with the state variable  $\vec{x}$  - consequently the matrix C represents the unit matrix. The grid voltages  $u_{\rm a}$ ,  $u_{\rm b}$  and  $u_{\rm c}$  represent the input variable of the system  $\vec{u}$ .

$$\vec{x} = \begin{pmatrix} i_{a1} \\ i_{b1} \\ i_{c1} \\ i_{b2} \\ i_{b2} \\ i_{c2} \\ u_{DC} \end{pmatrix} \qquad \vec{y} = \begin{pmatrix} i_{a1} \\ i_{b1} \\ i_{c1} \\ i_{c2} \\ i_{b2} \\ i_{c2} \\ u_{DC} \end{pmatrix} \qquad \vec{u} = \begin{pmatrix} u_{a} \\ u_{b} \\ u_{c} \end{pmatrix} \quad (3)$$

To identify the two matrices A and B, the state space equation is multiplied by the matrix E. This results in equation (4).

$$E \cdot \vec{x} = F \cdot \vec{x} + G \cdot \vec{u} \tag{4}$$

The two matrices to be identified are shown in equation (5).

$$A = E^{-1} \cdot F \qquad \qquad B = E^{-1} \cdot G \tag{5}$$

A total of seven differential equations are set up - four voltage equations, two current equations and one equation describing the DC link voltage. Each three of these equations refer to one three-phase bridge circuit.

First, the load-side converter will be considered here. The voltage equation, which represents the mesh between phase a and phase b, is described by the voltage  $\frac{(S_1-S_2)-(S_3-S_4)}{2} \cdot u_{DC}$ . The right side of the equation is formulated by the voltage drop across the individual components. The equation results in (6).

$$\frac{(S_1 - S_2) - (S_3 - S_4)}{2} \cdot u_{\rm DC} =$$

<sub>a1</sub> ·  $i_{a1} + L_{a1} \cdot \frac{\mathrm{d}i_{a1}}{\mathrm{d}t} - R_{b1} \cdot i_{b1} - L_{b1} \cdot \frac{\mathrm{d}i_{b1}}{\mathrm{d}t}$

(6)

Now the mesh equation between phase b and phase c is set up (7), which is analogous to equation (6).

R

$$\frac{(S_3 - S_4) - (S_5 - S_6)}{2} \cdot u_{\rm DC} =$$

$$R_{\rm b1} \cdot i_{\rm b1} + L_{\rm b1} \cdot \frac{\mathrm{d}i_{\rm b1}}{\mathrm{d}t} - R_{\rm c1} \cdot i_{\rm c1} - L_{\rm c1} \cdot \frac{\mathrm{d}i_{\rm c1}}{\mathrm{d}t}$$

(7)

The voltage equation describing the relationship between phase a and phase c is intentionally not included, since this information is contained in the two equations before and is therefore redundant. To include this equation would have the consequence that the matrices E and F would become singular. A singular matrix is not invertible. However, this property is a requirement for the matrix E in order to solve the equations in (5).

Analogous to the procedure just described, the two voltage equations that are related to the grid-side converter can be set up. The two voltage equations are the same as the equations (6) and (7) only with the exception that the grid voltages have to be included in the formulas. That is why the formulas are not further elaborated here.

Now the current equations are set up. For this purpose, Kirchhoff's  $1^{st}$  law is used, which states that in a node of an electrical network, the sum of the inflowing currents is equal to the sum of the outflowing currents. In terms of the load-side converter, the equation (8) can be obtained from this,

IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS 2021

since the three phase currents flow to a node and their sum must therefore equal zero.

$$i_{\rm a1} + i_{\rm b1} + i_{\rm c1} = 0 \tag{8}$$

However, this equation would create a zero row in the matrix E from (5), which would make this matrix singular and thus not invertible. To solve this problem, the equation (8) is derived. By derivation, the equation does not lose its validity. Hereafter the equation (9) results, which is considered in the state space representation.

$$i_{\rm a1} + i_{\rm b1} + i_{\rm c1} = 0 \tag{9}$$

Similarly, the equation (10) applies to the power converter on the line side.

$$\dot{i}_{a2} + \dot{i}_{b2} + \dot{i}_{c2} = 0$$

(10)

To couple the load-side with the grid-side, an equation is needed that describes the DC link voltage as a function of the load and line currents. The general equation for determining the voltage across a capacitor with constant electrical capacitance  $C_{\rm DC}$  is:

$$u_{\rm DC}(t) = u_{\rm DC}(0) + \int_0^t \frac{i_{\rm C}}{C_{\rm DC}} \,\mathrm{d}t = u_{\rm DC}(0) + \int_0^t \frac{i_{\rm DC2} - i_{\rm DC1}}{C_{\rm DC}} \,\mathrm{d}t \tag{11}$$

The current flowing through the DC link capacitance is described by the difference of the two DC currents  $i_{DC2}$  and  $i_{DC1}$  (11). These are determined by the phase currents and by the transistor switching states (12).

$$u_{\rm DC}(t) = u_{\rm DC}(0) + \int_0^t \frac{(S_2 \cdot i_{a1} + S_4 \cdot i_{b1} + S_6 \cdot i_{c1}) - (S_7 \cdot i_{a2} + S_9 \cdot i_{b2} + S_{11} \cdot i_{c2})}{C_{\rm DC}} \,\mathrm{d}t \tag{12}$$

After transforming the equations to the state space representation (4), we obtain the matrices shown in (13) - (16).

$$E = \begin{pmatrix} L_{a1} - L_{b1} & 0 & 0 & 0 & 0 & 0 \\ 0 & L_{b1} & -L_{c1} & 0 & 0 & 0 & 0 \\ 1 & 1 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & L_{a2} - L_{b2} & 0 & 0 \\ 0 & 0 & 0 & 0 & L_{b2} & -L_{c2} & 0 \\ 0 & 0 & 0 & 0 & 1 & 1 & 1 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 1 \end{pmatrix}$$

(13)

$$C = \begin{pmatrix} 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 1 \end{pmatrix}$$

(14)

$$G = \begin{pmatrix} 0 & 0 & 0 \\ 0 & 0 & 0 \\ 0 & 0 & 0 \\ -1 & 1 & 0 \\ 0 & -1 & 1 \\ 0 & 0 & 0 \\ 0 & 0 & 0 \end{pmatrix}$$

(16)

# B. Converter Model with Degradation Indicators

So far, ideal converter components were assumed for modeling the converter. However, in order to enable a systematic investigation of aging mechanisms, model parameters are required that describe specific aging mechanisms. Such parameters are termed as degradation indicators or sensitive parameters. These parameters can be used for condition monitoring in converter operation. The aim of this chapter is now to extend this model by the degradation indicators. Therefore, these degradation indicators are integrated into the differential equations. Subsequently, the differential equations are transferred into the state space representation.

1) Power Semiconductors: The conduction characteristic of the power semiconductor devices was simulated by the two parameters  $r_{\rm CE}$  and  $U_{\rm f}$ .

- Differential resistance of the collector-emitter path  $r_{\rm CE}$

- Threshold voltage of the collector-emitter path  $U_{\rm f}$

The  $i_{\rm CE}$  -  $u_{\rm CE}$  conduction characteristic of a power semiconductor device can be described by equation (17).

$$u_{\rm CE} = U_{\rm f} + r_{\rm CE} \cdot i_{\rm CE} \tag{17}$$

6

These parasitic effects are considered by including the formula (17) for every power semiconductor of the converter topology from Fig. 5. This results in the state space representation (18), which has the additional term Z.

$$E \cdot \vec{x} = F \cdot \vec{x} + G \cdot \vec{u} + Z \tag{18}$$

The matrices F and Z result in (19) to (20), while the matrices E, C and G remain the same as in (13), (14) and (16).

$$F = \begin{pmatrix} -R_{a1} - F_{a1} & R_{b1} + F_{b1} & \dots & \dots & \dots & \dots & \dots \\ \vdots & -R_{b1} - F_{b1} & R_{c1} + F_{c1} & \dots & \dots & \dots & \vdots \\ \vdots & \dots & \dots & \dots & \dots & \dots & \dots & \vdots \\ \vdots & \dots & \dots & \dots & \dots & \dots & \dots & \vdots \\ \vdots & \ddots & \ddots & \ddots & \ddots & -R_{b2} - F_{b2} & R_{c2} + F_{c2} \vdots \\ \vdots & \ddots & \ddots & \ddots & \ddots & \dots & \dots & \vdots \\ \dots & \dots \end{pmatrix}$$

(19)

$Z = \begin{pmatrix} Z_1 - Z_2 \\ Z_2 - Z_3 \\ 0 \\ Z_4 - Z_5 \\ Z_5 - Z_6 \end{pmatrix}$ (20)

Unlike the matrices (13) - (16) from equation (4), the matrices (19) - (20) have additional terms which contain the information about the conduction characteristics of the power semiconductors. These terms depend on the sign of the phase current. A case distinction must be made for different signs of the phase currents, since either the IGBT or the diode conducts depending on the current sign.

2) DC Link Capacitor: Now the same principle from section IV-B1 is applied to the degradation indicators of the DC link capacitor. The following two degradation indicators are integrated into the existing model from section IV-A.

- Capacitance value  $C_{\rm DC}$  of the DC link capacitor

- Equivalent series resistance  $R_{\rm ESR}$  of the DC link capacitor

<sup>2168-6777 (</sup>c) 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information Authorized licensed use limited to: KIT Library. Downloaded on June 14,2022 at 09:46:17 UTC from IEEE Xplore. Restrictions apply.

The parameter  $C_{\rm DC}$  is already included in the matrix F as shown in (15). The parameter  $R_{\rm ESR}$  is integrated into the equivalent circuit according to Fig. 3. This results in the extended matrix E with the additional parameter  $R_{\rm ESR}$  (21). The other matrices G, F and Z remain unchanged.

$$E = \begin{pmatrix} L_{a1} & -L_{b1} & 0 & 0 & 0 & 0 & 0 \\ 0 & L_{b1} & -L_{c1} & 0 & 0 & 0 & 0 \\ 1 & 1 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & L_{a2} & -L_{b2} & 0 & 0 \\ 0 & 0 & 0 & 0 & L_{b2} & -L_{c2} & 0 \\ 0 & 0 & 0 & 0 & 1 & 1 & 0 \\ S_{2} \cdot R_{ESR} S_{4} \cdot R_{ESR} S_{6} \cdot R_{ESR} - S_{7} \cdot R_{ESR} - S_{9} \cdot R_{ESR} - S_{11} \cdot R_{ESR} & 1 \end{pmatrix}$$

(21)

Now, the degradation indicators have been integrated into the converter model. The goal of chapter VI-B is to vary these degradation indicators and to investigate the effects on the available variables of a power electronic system. Before that, however, the next chapter V introduces the test bench, which forms the basis for the data capturing.

## V. TEST BENCH

The test bench represents the topology from Fig. 5. In section V-B, the test bench is extended by fault devices to allow implementation of intentional fault cases and manipulations on the power converter system.

# A. Structure of the Test Bench

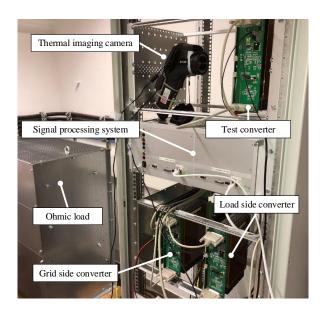

The test bench consists of a rectifier which converts the 3phase grid voltage provided by the grid into a DC voltage. This DC voltage is transformed again into a 3-phase AC voltage by another power converter. It results in an overall topology that can transform the grid voltage into an output voltage that is variable in amplitude and frequency. A passive load is used, consisting of an ohmic resistor and an inductor. The physical test bench setup can be seen in Fig. 6.

## Fig. 6. Test bench

The same type of converter is used for both the grid-side

rectifier and the load-side inverter. The inverter is equipped with the EconoPack2 FS75R12KT4 (1200 V/75 A) IGBT module from Infineon and can provide a rated power of 30 kW. The test bench has a measurement system for each of the 3-phase output currents, the heat sink temperature and the DC link voltage. In addition, the module temperature can be measured using an NTC resistor which is located in the power semiconductor module.

7

# B. Failure Devices

The test bench is extended in such a way that intentional implementation of failure cases is possible.

For investigations on the power semiconductor chips, an additional power supply is used. This power supply is connected to the DC link to provide a more constant DC link voltage and thus, to decouple the grid-side by the high-capacitance of the power supply in order to allow a more isolated investigation of the power semiconductors. The power supply EA-PSB 9200-140 is used, which can deliver a maximum voltage of 200 V and a maximum current of 140 A. The maximum power is 10 kW.

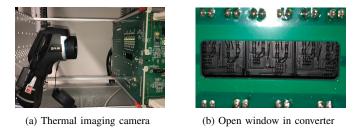

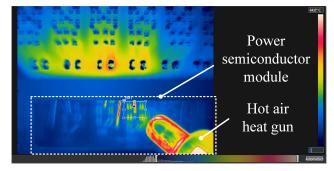

1) Power Semiconductors: In the power section board an open viewing window has been designed (Fig. 7). This enables the implementation of failure cases in the power semiconductors. For example, it is possible to heat individual semiconductor chips using a hot air gun and to cut off individual bond wires (bond wire lift-off). In addition, the open viewing window allows the chip temperature to be measured using the FLIR E60 thermal imaging camera during converter operation. Black-painted power modules are used, which allow a more accurate detection of chip temperature through the thermal imaging camera.

Fig. 7. Test arrangement for gaining access to power semiconductor devices

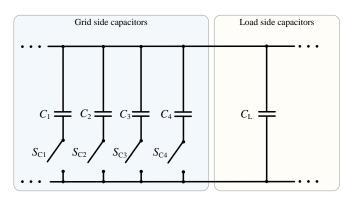

2) DC Link Capacitor: A circuit board has been designed that allows the variation of the degradation indicators of the DC link capacitor in converter operation (Fig. 8). This additional board is attached to the power section board of the converter. The capacitance and the ESR of the DC link capacitor can be changed. Individual DC link capacitors can be connected and disconnected using MOSFETS in order to change the total capacitance of the DC link. The board consists of four film capacitors with the brand name ICEL MHBS505500, which can be added separately. The dielectric is made of the material polypropylene. The nominal value of the capacitance is  $50 \,\mu\text{F}$  with a tolerance of  $10 \,\%$ .

The nominal ESR of an inserted capacitor is  $2.8 \text{ m}\Omega$  at a switching frequency of 1 kHz. In addition, the DC link board

IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS 2021

can connect an additional ohmic resistor in each path. The additional ohmic path is activated by a MOSFET as well. The value of the additional ohmic resistor is  $280 \text{ m}\Omega$ . This approximately doubles the initial ESR, which consists of the nominal ESR of the capacitor as well as the resistance of the activated MOSFET.

(a) Layout of the circuit board

(b) Circuit in the real application

Fig. 8. DC link capacitor circuit board that allows the variation of the degradation indicators of the DC link capacitor in converter operation

# VI. ALGORITHM TO CONDITION MONITORING

This chapter deals with the machine learning algorithm shown in Fig. 1. The first step of the machine learning algorithm is the data capturing, which is explained in section VI-A. In section VI-B, the created root cause detection models are described.

# A. Data Capturing

In this section the data that is used for condition monitoring is explained. It is the first step of the machine learning algorithm. In section VI-A1, the data for analyzing the power semiconductor is studied, then in section VI-A2 the data used for monitoring of the DC link capacitors is investigated.

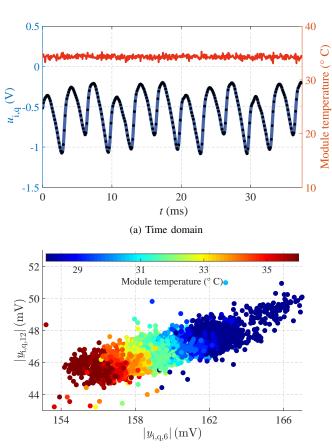

1) Power Semiconductors: In this work, the controller output variables are considered, since the controller always reacts to changes of the system. This means that the controller also reacts to aging of the system components. This principle is used to detect aging mechanisms that have occurred during operation. In [2], the current control system is shown. The output voltages and can be divided into a d- and a qcomponent, which represent the d- and q-axis in the rotational reference system. In addition, the output variables of the control are divided into proportional and integral components. As an example, in Fig. 9 (a) the integral part of the current controller output in q-axis is shown. The module temperature is also recorded. The temperature is included in order to be able to differentiate between temperature-related effects and aging.

The signals are analysed in the frequency domain. For this purpose, a Fast Fourier Transformation (FFT) is performed for each electrical period to transform the voltages from the time domain to the frequency domain. The operating point is given in Table I.

The data set consists of 3031 data points since this is the number of electrical periods that are captured, which corresponds to a total duration of 60 seconds. Figure 9 (b) shows the  $6^{\text{th}}$ and  $12^{\text{th}}$  harmonic of the integral part of the controller output in q-axis for the investigated operating point. In addition, the

8

(b) Frequency domain with module temperature dependence

Fig. 9. Measurement results: Integral part of the current controller output in q-axis

TABLE I PARAMETER SET OF OPERATING POINT

| Parameter                                         | Value           |

|---------------------------------------------------|-----------------|

| Current d-axis $i_{\rm d}$                        | 10 A            |

| Current q-axis $i_{q}$                            | 0 A             |

| DC link voltage $U_{\rm DC}$                      | $200\mathrm{V}$ |

| Electrical frequency $f_{\rm el}$                 | $50\mathrm{Hz}$ |

| Sampling frequency $f_{\rm S}$                    | 16 kHz          |

| Ohmic resistors $R_{\rm a}, R_{\rm b}, R_{\rm c}$ | 2.1 Ω           |

| Load inductors $L_{\rm a}, L_{\rm b}, L_{\rm c}$  | 2 mH            |

information about the module temperature is included in the data points. A temperature fluctuation can be observed, which is caused by the fan, whose electrical power is not always constant in steady-state operation.

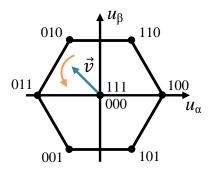

Furthermore, Fig. 9 (b) shows that power semiconductor effects affect the 6<sup>th</sup> harmonic and its multiples in the dq coordinate system. The temperature-related changes in the power semiconductors with regard to the conduction characteristics lead to changes in the sixth and twelfth harmonics of the controller outputs. This can be explained graphically with the hexagonal space vector diagram (Fig. 10). The space vector diagram can be divided into six sectors. In a three-phase system there are six different states, which sign the three output currents can have (+--, ++-, -+-, -++, --+, +-+). The two states ++ and -- are not possible. Depending on which state is present, the parasitic effects of the power

semiconductors add or subtract to the ideal fundamental wave. When a fundamental wave is passed through, the total of six different states occur exactly once, forming a  $6^{\rm th}$  harmonic.

Fig. 10. Space vector diagram with the associated switching states of the power devices

In order to illustrate the principle, Fig. 11 shows simulation results of the output vector in the  $\alpha\beta$ -frame for numerous electrical periods. In the simulation framework, the power semiconductor devices show parasitic effects, whereby a voltage drop of 6 V is assumed here as an example in order to show the principle. It can be observed that the provided output vector of the controller does not correspond to an ideal circular shape, but for each of the six states an elevation of the vector can be seen as the parasitic effects of the power semiconductors are compensated by the controller.

Fig. 11. Simulation results of the controller output voltage in the  $\alpha\beta$ -frame when a voltage drop is assumed across the power semiconductors. State number refers to which sign the output currents have as described above.

The sampling frequency is  $f_{\rm S} = 16$  kHz. Thus, the controller receives a measured value at time intervals of  $T_{\rm S} = 62.5$  µs. From this value, a controller output variable is calculated, which is represented by one data point. This results in one data point for each time period.

The sampling rate of the AD card is 5 Msps. For the measured data recorded by the AD card, the average value is calculated for each time period of  $T_{\rm S} = 62.5 \,\mu \text{s}$  and fed to the controller. For instance, for a sample rate of 5 Msps and a sampling frequency of  $f_{\rm S} = 16 \,\text{kHz}, \lfloor \frac{5 \cdot 10^6}{16000} \rfloor = \lfloor 312.5 \rfloor = 312$  values can be measured each time period. From this, an average

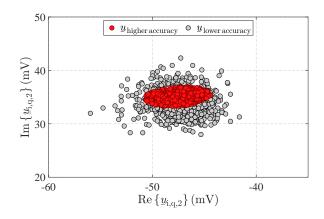

value is calculated and sent to the controller. As the sampling rate or the number of data points involved in the mean value calculation increases, the noise decreases and thus the scatter in the data cloud decreases. In Fig. 12, the relationship between the number of the points included in the mean value calculation in the AD card and the accuracy of the recorded data is shown. The red data points refer to a mean value calculation with 312 data points of the AD card, whereby the grey data points correspond to 32 data points. As an example, the second harmonic is shown in Fig. 12. After collecting data points of the controller output voltages, the mean value of the data cloud can be evaluated. Figure 12 indicates that there is only a marginal difference in the center points of the data clouds, when the accuracy in the data acquisition differs, however, when fewer data points for the mean value calculation in the AD card are considered, the accuracy is lower and the noise is higher.

9

Fig. 12. Measurement results: relationship between the number of the points included in the mean value calculation in the AD card and the accuracy of the recorded data. Red data points refer to a higher accuracy by taking 312 data points into account when averaging the measured data. Grey data points refer to a lower accuracy by considering 32 data points.

However, time can compensate a lower sampling rate. Even with low sampling rates and large scatter in the data cloud, statements can be made about aging, but more time is then required so that the data clouds are sufficiently compacted. The more time passes during the data acquisition, the more the data cloud is compressed. If a sufficient number of data points are recorded, the center of the data cloud is evaluated, which means that the scatter of the data cloud does not play a significant role in the data evaluation. Even if measurement accuracy is low and noise is high, taking more time can compensate these shortcomings.

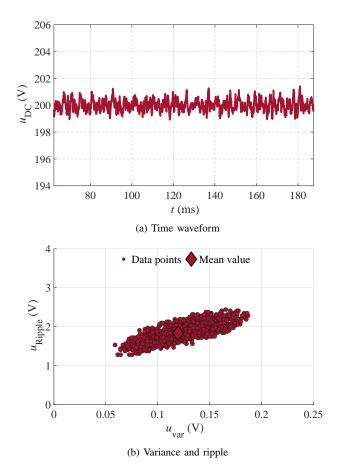

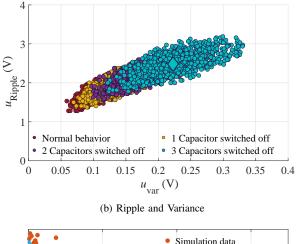

2) DC Link Capacitor: For the analysis of the DC link capacitor the DC link voltage as a function of time is considered (Fig. 13 (a)). For every electrical time period from Table I, this curve can be transformed into the diagram in Fig. 13 (b). Fig. 13 (b) shows the data points of ripple and variance of the DC link voltage which are calculated according to the formulas (22) and (23). In order to calculate the ripple, the maximum and minimum values are determined for every section of an electrical period (22).

$$u_{\text{Ripple}} = \max(u_{\text{DC},N}) - \min(u_{\text{DC},N})$$

(22)

For the calculation of the variance, the difference from the mean value is calculated and squared (23). N indicates the amount of data for the evaluated section of an electrical period.

$$u_{\rm var} = \frac{1}{N-1} \cdot \sum_{i=1}^{N} |u_{{\rm DC},i} - \text{mean}(u_{{\rm DC},N})|^2$$

(23)

These data clouds can be represented by a mean value, which is based on the mahalanobis distance. Unlike the euclidean distance, the mahalanobis distance also takes the different variances of the two axes into account by considering the covariance matrix [20][21]. For calculating the mean value of data clouds a special variant of the mahalanobis distance is used, which is not distorted by the outlier data points. It is called robust robust mahalanobis distance and is further desribed in [20].

Fig. 13. Measurement results of the DC link voltage

#### B. Creation of a Root Cause Detection Model

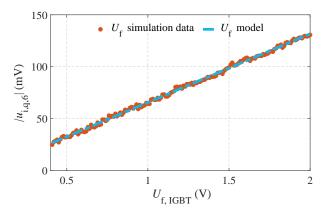

In this chapter, the models from chapter IV are used to vary the degradation indicators in a simulation framework. The correlations between the degradation indicators and the available data are evaluated. Based on this, suitable mathematical models are created that are capable of detecting these failure cases. 1) Power Semiconductors: As an example, the creation of such a model will be shown using the threshold voltage of the IGBTs in the collector-emitter path. First, the threshold voltages of all six IGBTs  $U_{\rm f}$  of the load-side inverter from Fig. 5 are equally varied according to Table II.

10

TABLE II VARIATION OF THE IGBT THRESHOLD VOLTAGES

| Number of simulations |                                                 | 160              |

|-----------------------|-------------------------------------------------|------------------|

|                       | Value range threshold voltage IGBT $U_{f,IGBT}$ | 0.41 V - 2 V     |

|                       | Step size threshold voltage IGBT $U_{f,IGBT}$   | $0.01\mathrm{V}$ |

The simulation results show that the magnitudes of the sixth harmonics of the controller outputs correlate with the simulated threshold voltages of the IGBTs. The same correlation is also observed for the multiples of the sixth harmonics (12<sup>th</sup>, 18<sup>th</sup>, 24<sup>th</sup>, etc.). Figure 14 shows the diagram of the sixth harmonic of the integral component of the q-axis over the simulated threshold voltage of the IGBTs.

Fig. 14. Simulation results and the corresponding model of the sixth harmonic of the integral component of the q-axis over the simulated threshold voltage of the IGBTs

The figure indicates a linear relationship between the two variables. Therefore, a linear model is used in order to replicate the simulation results which is shown in (24).

$$|u_{i,q,6}| = a \cdot U_{f,IGBT} + b \tag{24}$$

The coefficients are calculated by using the least square method with the aim of minimizing the error squares between model and simulation. The coefficients of the model are determined to a = 0.066 and  $b = -2.77 \cdot 10^{-4}$  with a coefficient of determination that results in  $R^2 = 0.9978$ .

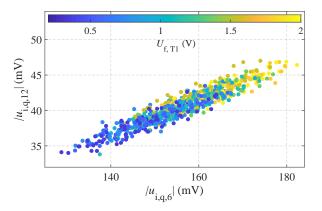

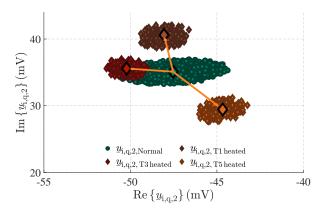

In this simulation, all six IGBTs of a three-phase bridge circuit were increased simultaneously. In practice, changes in individual power semiconductor chips can also occur. To investigate this aspect as well, the variation of the threshold voltage of one single IGBT is evaluated. As an example, this is changed for the positive IGBT of phase a. Figure 15 shows the sixth and twelfth harmonic of the integral component of the q-axis as a function of the varied threshold voltage  $U_{\rm f,T1}$  of IGBT  $T_1$ .

The increase of the threshold voltage  $U_{f,T1}$  yields an increase of the sixth and twelfth harmonics of the integral component

IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS 2021

Fig. 15. Simulation results of the sixth and twelfth harmonic of the integral component of the q-axis as a function of the varied threshold voltage  $U_{\rm f,T1}$  of IGBT  $T_1$

of the q-axis. In addition, the relationship is valid for the other multiples of the sixth harmonic not shown here.

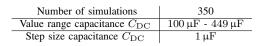

The variation of only one phase yields an asymmetry, which affects the second harmonic in the dq-frame. Here, the IGBTs  $T_1$ ,  $T_3$  and  $T_5$  were changed according to Table III. The threshold voltages of the three upper IGBT, which cause a positive phase voltage, were modified individually.

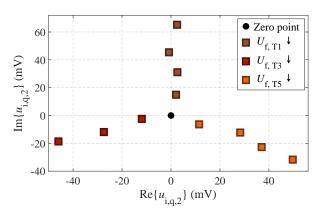

TABLE III Variation of the individual threshold voltages of the IGBTs  $U_{\rm f,T1,T3,T5}$

| Number of simulations        | 10                                      |

|------------------------------|-----------------------------------------|

| Zero point $U_{f,T1,T3,T5}$  | $1.2365\mathrm{V}$                      |

| Value range $U_{f,T1,T3,T5}$ | $0.6365\mathrm{V}$ - $1.2365\mathrm{V}$ |

| Step size $U_{f,T1,T3,T5}$   | $0.2\mathrm{V}$                         |

Figure 16 shows the results of this simulation series. The complex plane of the second harmonic of the integral component in the q-axis is illustrated. Starting from the zero point, where there is no asymmetry, a shift of the second harmonic can be observed. The magnitudes of the second harmonic increase with growing asymmetry. In addition, the phase angle of these harmonics changes depending on which IGBT has changed its threshold voltage. The phase angles of the three upper IGBTs have an angular difference of about  $120^{\circ}$  to each other. Especially this correlation can be used to determine which power semiconductor chip exactly is damaged.

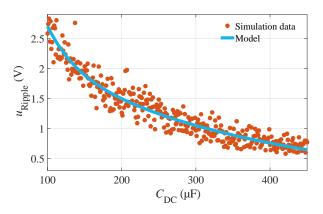

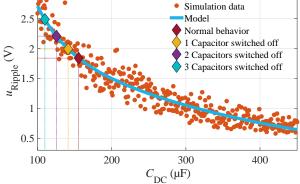

2) DC Link Capacitor: For creating a root cause model for the DC link capacitor, the converter model of section IV-B is used. A degradation indicator is the value of the capacitance  $C_{\rm DC}$ . In the following, this variable is simulated according to Table IV.

TABLE IV Variation of DC link capacitance

The simulation results are shown in Fig. 17. The correlation between the ripple and the simulated capacitance value can be

11

Fig. 16. Simulation results: complex plane of the second harmonic of the integral component in the q-axis as a function of the individual threshold voltages of the positive IGBTs

seen. An exponential relationship is assumed between the two variables.

Fig. 17. Simulation results of the relationship between ripple voltage and the value of the capacitance and the corresponding fitted model of the capacity

Therefore, a 2<sup>nd</sup> degree exponential function according to (25) is used to reproduce the simulation results.

$$u_{\text{Ripple}} = a \cdot e^{b \cdot C_{\text{DC}}} + c \cdot e^{d \cdot C_{\text{DC}}}$$

(25)

In the training process of the algorithm, the coefficients are chosen using the least square method so that the error squares between model and simulation are minimized. Using the MATLAB fitting tool, the coefficients of the model can be determined to a = 9.68, b = -26160, c = 2.76 and d = -3236. The coefficient of determination results in  $R^2 = 0.9149$ .

#### VII. EXPERIMENTS AND MEASUREMENT RESULTS

#### A. Power Semiconductors

First, individual chips of the power semiconductor module are heated through the open viewing window of the circuit board (Fig. 7) using a hot air gun. Figure 18 shows the heating of IGBT  $T_3$  from phase c. In Fig. 18 (c), the structure of the power semiconductor module and the chip names are illustrated.

IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS 2021

(a) Heating with hot air heat gun

(b) Recording with thermal camera

(c) Chip names of the power semiconductor module

(d) Results of the thermal imaging camera

Fig. 18. Heating of individual chips of the power semiconductor module

The temperature range of the power semiconductor chips of the operating point from Table I is  $40 \degree C - 45 \degree C$ . The module temperature is approximately  $35 \degree C$ . Chip  $T_3$  is heated to a maximum temperature above  $80 \degree C$ .

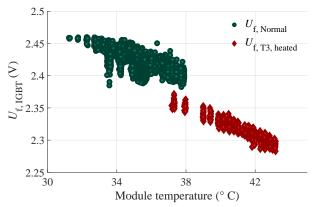

The model results of the root cause detection are evaluated, while the IGBT chip is heated. Therefore, the captured data with the representation form of Fig. 9 (b) is transferred to the degradation indicator  $U_{\rm f}$  using the correlation determined in formula (24). The model results of the on state threshold voltage  $U_{\rm f}$  of the collector-emitter path for the heated and unheated chip as a function of the measured module temperature are shown in Fig. 19.

The model results show a temperature dependence. The module temperature is measured by using the NTC resistor within the module. The on state threshold voltage  $U_{\rm f}$  of the collectoremitter path decreases with increasing temperature. The on state collector-emitter voltage is a suitable indicator for detecting certain aging mechanisms such as solder fatigue, which is discussed in [10]. In addition, other aging mechanisms can in principle also be identified. All aging mechanisms that lead to the change of the investigated degradation indicators can be covered. One example is the heating of individual chips, which is the focus of this publication. In our previous publication [2] also the aging mechanism bond wire lift-off is considered by

12

Fig. 19. Model results of the threshold voltage  $U_{\rm f}$  when the IGBT chip  $T_3$  is heated up

using the same method but investigating the mean value of the controller output variable.

However, it must be noted that the value calculated by the model does not necessarily have to correspond to the real, physical value. Due to many power converter effects that are not taken into account, such as turn-on and turn-off times, model inaccuracies result. Nevertheless, the value could be used as an indicator for certain aging mechanisms. Furthermore, the limits from which value of the threshold voltage the power converter is still considered functional and from which value the power converter must be replaced has to be determined by extensive field or laboratory tests.

In addition, the second harmonic of the controller output is considered in the complex plane. In Fig. 20, the measurement results of the individual chip heating are evaluated. Unlike in the simulation, the normal behavior in the second harmonic already has a value that is not equal to zero. This is due to the fact that there is an initial asymmetry in the system, which comes primarily from the passive load.

As the chips are heated up, a shift in the data cloud can be observed. The phase angles of the three upper IGBTs  $T_1$ ,  $T_3$ and  $T_5$  show an angular difference of about  $120^{\circ}$  to each other as also previously observed in the simulation in Fig. 16. Deviations in the angle may result from the fact that completely isolated heating of one chip is not possible in the practical example shown. Starting from the centers of the data clouds, difference vectors are identified, which calculate the shift of the initial data cloud. This allows to determine which power semiconductor chip is heated up.

# B. DC Link Capacitor

According to Fig. 21 (a), the individual capacitors are switched off and the resulting effects are detected. The changes that occur are recorded in the diagrams in Fig. 21 (b). This diagram indicates that the ripple and the variance of the DC link voltage increase as the number of connected capacitors decreases since it can be observed that the data cloud shifts towards higher ripples and variances. By calculating the robust mahalanobis mean value for every data cloud and by inserting this value into the capacitor model of equation (25), a value IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS 2021

Fig. 20. Measurement results of the second harmonic of the integral component in the q-axis for the single chip heating

of the capacitance can be calculated. The model is capable of detecting the decrease of the DC link capacitance only by means of the DC link voltage time waveform of Fig. 13 (a). As in section VII-A explained, the calculated value of the capacitance may differ from the real value due to model inaccuracies. Still, the model is capable of detecting the decrease in the capacitance with the available data in converter operation. An outlook is to improve and optimise the model in order to get closer to the real value. This can be done, for instance, by including the effects of the digital-analog converter into the model to take the noise into account.

## VIII. CONCLUSION

In this publication, a new approach to condition monitoring of power electronic systems is presented. This approach does not require additional sensors and only uses data that is already available during operation. A complete approach is presented, including the aspects of data acquisition, preprocessing and analysis. The publication focuses on the two power converter components: power semiconductor devices and DC link capacitor. For these, the aging mechanisms and corresponding degradation indicators are determined. Subsequently, a power converter model is build that includes these degradation indicators. This model is used to analyze the effects of the degradation indicators on the available data.

The overall converter test bench is presented. Afterwards, the extension of the test bench is explained, which allows intentional implementation of failure cases at different levels. In the last section, the failure devices are used to implement intentional modifications to the power converter system that represent specific failure mechanisms. Here, the results of the algorithm are evaluated. For the detection of semiconductor failures, the output control variables of the control and their relevant harmonic oscillations are analyzed. Thereby, the multiples of the sixth harmonic are used. Mathematical models are created which can calculate the failure severity based on these variables. Furthermore, by considering the second harmonic, it can be determined in which power semiconductor chip exactly the failure is occurred.

The same principle was applied to the DC link capacitor

13

(a) Block diagram of the switchable capacitors in the capacitor board

(c) Model results when value of capacitance is reduced

Fig. 21. Measurement and model results depending on the number of switched off capacitors

component. Here, the time signal of the DC link voltage was converted into a different representation form with ripple and variance. The mathematical model created can calculate capacitance changes of the DC link capacitor during converter operation. One outlook is the further improvement and optimization of the converter model in order to bring the calculated degradation parameters closer to reality. This allows more accurate predictions of when an aging component needs to be replaced, which forms the basis of predictive maintenance.

IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS 2021

#### REFERENCES

- V. Pickert and B. Mecrow, "Overview Fault-tolerant Systems", ECPE Workshop: Availability of Power Electronics by Fault-Tolerant Designs in Automotive and Aircraft, Leinfelden-Echterdingen, Jul. 2019.

- [2] F. Yüce and M. Hiller, "Investigation of Bond Wire Lift-Off by Analyzing the Controller Output Voltage Harmonics for the Purpose of Condition Monitoring", *The 22<sup>nd</sup> European Conference on Power Electronics and Applications EPE'20 ECCE Europe*, 2020.

- [3] F. Yüce and M. Hiller, "Condition Monitoring of Power Semiconductors by Means of the Controller Output Voltage Harmonics", *PCIM Europe* digital days 2021; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 2021.

- [4] J. Lutz, "Halbleiter-Leistungsbauelemente Physik, Eigenschaften, Zuverlässigkeit", Springer Vieweg, 2012.

- [5] M. Sattler, "Materiallösungen für die Leistungselektronik Bedeutung der Aufbau- und Verbindungstechnik", ATZelektronik, Aug. 2016.

- [6] M. Ciappa, "Selected failure mechanisms of modern power modules", *Microelectronics Reliability*, 2002.

- [7] M. Eleffendi and M. Johnson, "In-Service Diagnostics for Wire-Bond Lift-off and Solder Fatigue of Power Semiconductor Packages", *IEEE Transactions on Power Electronics*, 2017.

- [8] U. Choi, F. Blaabjerg, S. Jørgensen, S. Munk-Nielsen, and B. Rannestad, "Reliability Improvement of Power Converters by Means of Condition Monitoring of IGBT Modules", *IEEE Transactions on Power Electronics*, 2017.

- [9] B. Ji and V. Pickert, "In Situ Diagnostics and Prognostics of Wire Bonding Faults in IGBT Modules for Electric Vehicle Drives", *IEEE Transactions* on Power Electronics, 2013.

- [10] N. Patil, D. Das, K. Goebel and M. Pecht, "Failure Precursors for Insulated Gate Bipolar Transistors (IGBTs)", *IET Seminar Digest*, Jan. 2008.

- [11] O. Schilling, M. Schäfer, K. Mainka, M. Thoben and F. Sauerland, "Power cycling testing and FE modelling focussed on Al wire bond fatigue in high power IGBT modules", *Special Issue 23rd European Symposium on the Reliability of Electron Devices, Failure Physics and Analysis*, 2012.

- [12] A. Morozumi, K. Yamada, T. Miyasaka and Y. Seki, "Reliability of power cycling for IGBT power semiconductor modules", *Conference Record of the 2001 IEEE Industry Applications Conference. 36th IAS Annual Meeting*, 2001.

- [13] X. Perpiñàl, L. Navarro, X. Jordàl, M. Vellvehi, J. Serviere and M. Mermet-Guyennet, "Reliability and Lifetime Prediction for IGBT Modules in Railway Traction Chains", *Reliability and Lifetime Prediction* for IGBT Modules in Railway Traction Chains, Mar. 2012.

- [14] H. Wang and F. Blaabjerg, "Reliability of Capacitors for DC-Link Applications in Power Electronic Converters: An Overview", *IEEE Trans*actions on Industry Applications, 2014.

- [15] A. Wechsler, B. Mecrow, D. Atkinson, J. Bennett and M. Benarous, "Condition Monitoring of DC-Link Capacitors in Aerospace Drives", *IEEE Transactions on Industry Applications*, 2012.

- [16] G. Buiatti, J. MartÍn-Ramos, A. Amaral, P. Dworakowski and A. Cardoso, "Condition Monitoring of Metallized Polypropylene Film Capacitors in Railway Power Trains", *IEEE Transactions on Instrumentation* and Measurement, 2009.

- [17] P. Venet, F. Perisse, M. El-Husseini and G. Rojat, "Realization of a smart electrolytic capacitor circuit", *IEEE Industry Applications Magazine*, Aug. 2002.

- [18] X. Pu, T. Nguyen, D. Lee, K. Lee and J. Kim, "Fault Diagnosis of DC-Link Capacitors in Three-Phase AC/DC PWM Converters by Online Estimation of Equivalent Series Resistance", *IEEE Transactions* on Industrial Electronics, Sep. 2013.

- [19] A. Imam, D. Divan, R. Harley and T. Habetler, "Real-Time Condition Monitoring of the Electrolytic Capacitors for Power Electronics Applications", APEC 07 - Twenty-Second Annual IEEE Applied Power Electronics Conference and Exposition, 2017.

- [20] M. Hubert and M. Debruyne, "Minimum covariance determinant", 2009 John Wiley and Sons, 2010.

- [21] K. Backhaus, B. Erichson, W. Plinke and R. Weiber, "Multivariate Analysemethoden - Eine anwendungsorientierte Einführung", *Springer Gabler*, 2018.

- [22] S. Weber, M. Schlüter, D. Borowski and A. Mertens, "Simple Analog Detection of Turn-Off Delay Time for IGBT Junction Temperature Estimation", 2016 IEEE Energy Conversion Congress and Exposition (ECCE), 2016.

- [23] M. Denk, M. Bakran and S. Schafferhans, "Case Sensitive Condition Monitoring of an IGBT Inverter in a Hybrid Car", CIPS 2016; 9th International Conference on Integrated Power Electronics Systems, 2016.

- [24] A. Brunko, W. Holzke, H. Groke, B. Orlik and N. Kaminski, "Model-Based Condition Monitoring of Power Semiconductor Devices in Wind Turbines", 2019 21st European Conference on Power Electronics and Applications (EPE '19 ECCE Europe), 2019.

- [25] P. Eyerer and H. Schüle, "Polymer Engineering 1", *Springer Vieweg*, Oct. 2020.

- [26] C. Olivares, R. Rahman, C. Stankus, J. Hampton, A. Zedwick and M. Ahmed, "Predicting Power Electronics Device Reliability under Extreme Conditions with Machine Learning Algorithms", *IEEE Transactions on Device and Materials Reliability*, Jul. 2021

- [27] M. Al-Greer, M. Armstrong, M. Ahmeid and D. Giaouris, "Advances on System Identification Techniques for DC–DC Switch Mode Power Converter Applications", *IEEE Transactions on Power Electronics*, Jul. 2019

- [28] J. Poon, P. Jain, M. Ahmeid, I. Konstantakopoulos, C. Spanos, S. Panda and S. Sanders, "Model-Based Fault Detection and Identification for Switching Power Converters", *IEEE Transactions on Power Electronics*, Feb. 2017

- [29] M. Biglarbegian, S. Mostafavi, S. Hauer, S. Nibir, N. Kim, R. Cox and B. Parkhideh, "On Condition Monitoring of High Frequency Power GaN Converters with Adaptive Prognostics", 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), Mar. 2018

- [30] L. Felsberger, B. Todd and D. Kranzlmüller, "Power Converter Maintenance Optimization Using a Model-Based Digital Reliability Twin Paradigm", 2019 4th International Conference on System Reliability and Safety, 2019

- [31] Y. Peng, S. Zhao and H. Wang, "A Digital Twin Based Estimation Method for Health Indicators of DC–DC Converters", *IEEE Transactions* on Power Electronics, Feb. 2021

- [32] P. Jain, J. Poon, J. Singh, C. Spanos, S. Sanders and S. Panda, "A Digital Twin Approach for Fault Diagnosis in Distributed Photovoltaic Systems", *IEEE Transactions on Power Electronics*, Jan. 2020

**Firat Yüce** received the B. Sc. and M. Sc. degrees in electrical engineering and information technology from Karlsruhe Institute of Technology, Karlsruhe, Germany, in 2014 and 2017, respectively. He is currently with the Institute of Electrical Engineering, Karlsruhe Institute of Technology, as Research Associate and Ph.D. student. His research interests include reliability and condition monitoring of power device and converter.

**Marc Hiller** received the Dipl.-Ing. degree in Electrical Engineering from the Technical University of Darmstadt, Germany in 1999, and the Ph.D. degree in Electrical Engineering from the University of Federal Armed Forces Munich, Germany in 2008. In 1999, he was with the Traction converter R&D department of the Siemens AG in Erlangen, Germany as a R&D engineer working on high power drives for freight locomotives. From 1999 to 2004, he was with the Department of Electrical Engineering, University of Federal Armed Forces Munich, as a PhD student.

From 2005 to 2015, he was with Siemens Industry in Nuremberg, Germany as project manager and head of power section development in the R&D department for low and medium voltage converters for energy and industrial applications. He is currently with the Karlsruhe Institute of Technology KIT, Germany, as Full Professor for Power Electronic Systems and head of the Institute of Electrical Engineering, ETI. His current research interests include the areas of design and control of advanced high-power electronics systems and high performance drives. He has authored or coauthored 50+ scientific publications and has filed 25+ patents. He has received the VDE/ETG Best Paper Award in 2005 and received the award as Inventor of the year of Siemens AG in 2009.

2168-6777 (c) 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information. Authorized licensed use limited to: KIT Library. Downloaded on June 14,2022 at 09:46:17 UTC from IEEE Xplore. Restrictions apply.

<sup>14</sup>