# Fault Attack Resilience on Error-prone Devices

A study into the effects of error injection on micro-controllers and software security strategies to recognise and survive attacks

Martin S. Kelly

A thesis presented for the degree of Doctor of Philosophy

Information Security Group Royal Holloway, University of London

# Declaration

These doctoral studies were conducted under the supervision of Prof. Keith Mayes.

The work presented in this thesis is the result of original research carried out by myself, in collaboration with others, whilst enrolled in Royal Holloway's Information Security Group as a candidate for the degree of Doctor of Philosophy. This work has not been submitted for any other degree or award in any other university or educational establishment.

Martin S. Kelly January, 2022

# Acknowledgments

The work described in this report would not have been possible without the assistance of **John Walker**, ex of SiVenture Ltd. John's help in preparing samples, along with his infectious enthusiasm for sharing and passing on knowledge and skills, made the early lab-work educational and entertaining. In a similar vein, my thanks and gratitude are due to **Prof. Keith Mayes** who supervised this project. Keith's patience and support have been very much appreciated as work here progressed in fits and starts while being interleaved with full-time employment. The third individual worthy of special thanks is **Julian Brown** of Nexus Electronics, Cambridge. Julian's suggestions and corrections for some of the circuit boards developed for this study saved countless hours and helped avoid expensive revisions.

All three of the above have my eternal thanks and gratitude. Without them, this work would not have been completed.

Additional thanks are also due to **Prof. Konstantinos Markantonakis** and to **Dr. Raja Akram** for their ad-hoc advice, encouragement and recommendations, as this project progressed.

This list would be incomplete without expressing my gratitude to **Dr. David Everett**, ex of NatWest Development Team, and **Dato' "Tony" Lee Kwee Hiang**, founder of Iris Technologies Sdn. Bhd., both of whom gave me free rein to cause electronic trouble with chips while working on groundbreaking smartcard initiatives. Their encouragement and trust led to a career in implementing defensive code that ultimately resulted in this study.

All of the above have been friends as well as colleagues throughout this project, and I hope, at some point, to be able to return the favours.

## Thank you all!

Acknowledgements and thanks are also due to the following organizations for the use of their images and code. The images' copyrights remain the property of the organizations and individuals listed below.

- Figure 2-9 Nanoscope Services Ltd., Bristol, BS15 4PJ.

- Figures 2-5 & 2-6 draw heavily on Roberto Avanzi's original work in "TikZ for Cryptographers", https://www.iacr.org/authors/tikz/.

- AVR Speck implementation by LuoPeng [10], used in Section 4.3.

- Digital Locksmiths Ltd., Cambridge. For access to a back catalogue of commercially developed and security certified smartcard applications, funding these studies, and paying for all of the hardware developed during this investigation.

### Abstract

This thesis demonstrates a new practical approach to understanding a micro-controller's behaviour when subjected to error inducing attacks. It also shows a novel mechanism for understanding the effects of errors and the efficacy of counter-measures. The insights gained enabled the development and evaluation of a new C compiler capable of inserting effective counter-measures that could not otherwise be realised via off-the-shelf tools.

While conducting this research, we identified properties of the equipment used to induce errors that enabled us to construct a new, very flexible, low-cost error injection workstation. The new tools provide a framework for accurately injecting perturbation errors and for retrieving the resulting device state. This demonstrates the ease with which an adversary can attack a target and provides the ability to self-test one's defences.

The findings of this study have particular relevance in the field of general-purpose micro-controllers. These devices are playing an ever-increasing role in everyday life, for example, home automation gadgets in the Internet-of-Things. The consequence of this increased diversity of application is that products are often specified and commissioned without considering the vulnerabilities of stand-alone micro-controllers. Similarly, the development and programming tasks are often delegated to engineers who are unfamiliar with the coding disciplines required to resist attack.

This study shows that the tools and techniques required to protect such devices can be made readily available and are not the sole preserve of well-funded laboratories or big corporations.

# Contents

|          |       |                          | Page |

|----------|-------|--------------------------|------|

| C        | over  |                          | 1    |

|          | Decl  | aration                  | . 1  |

|          | Ackı  | nowledgements            | . 3  |

|          | Abs   | tract                    | . 5  |

| C        | onter | nts                      | 7    |

|          | List  | of Contents              | . 7  |

|          | List  | of Tables                | . 10 |

|          | List  | of Figures               | . 12 |

|          | List  | of Abbreviations         | . 17 |

| Fo       | rwar  | <sup>•</sup> d           | 25   |

| 1        | Intr  | roduction                | 27   |

|          | 1.1   | Research Questions       | . 30 |

|          | 1.2   | Methodology              | . 33 |

|          | 1.3   | Significance             | . 34 |

|          | 1.4   | Structure of this Thesis | . 37 |

| <b>2</b> | Bac   | kground                  | 39   |

|          | 2.1   | Threats                  | . 41 |

|          | 2.2   | Attacks                  | . 48 |

|          | 2.3   | Errors                   | . 68 |

|          | 2.4   | Defence Techniques       | . 88 |

|          | 2.5   | Observations             | . 91 |

| 3        | Cat   | egorising Errors         | 93   |

|          | 3.1   | Fault Models             | . 96 |

|               | 3.2                                                  | Test Strategy                                 | 99                                            |

|---------------|------------------------------------------------------|-----------------------------------------------|-----------------------------------------------|

|               | 3.3                                                  | Experiments                                   | 106                                           |

|               | 3.4                                                  | Data and Interpretation                       | 136                                           |

|               | 3.5                                                  | Summary                                       | 136                                           |

| 4             | A N                                                  | New Laser Workstation                         | 139                                           |

|               | 4.1                                                  | Components                                    | 141                                           |

|               | 4.2                                                  | Multi-Pulse Proof of Capability               | 152                                           |

|               | 4.3                                                  | Creeping Barrage - Blind Attack on Known Code | 158                                           |

|               | 4.4                                                  | Summary                                       | 161                                           |

| 5             | Test                                                 | ting Security Defences                        | 163                                           |

|               | 5.1                                                  | Practicalities                                | 166                                           |

|               | 5.2                                                  | Defences                                      | 169                                           |

|               | 5.3                                                  | Results and Analysis                          | 181                                           |

|               | 5.4                                                  | Application                                   | 188                                           |

|               | 5.5                                                  | Summary                                       | 190                                           |

| 6             | Aut                                                  | omating Defence Generation                    | 193                                           |

|               | 6.1                                                  | Background                                    | 197                                           |

|               | 6.2                                                  | Defensive C Compiler                          | 201                                           |

|               | 6.3                                                  | Defending Execution Path                      | 203                                           |

|               | 6.4                                                  |                                               |                                               |

|               | 0.1                                                  | Code Efficiency                               | 224                                           |

|               | 6.5                                                  | Summary                                       | 224<br>230                                    |

| 7             | 6.5                                                  |                                               |                                               |

| 7             | 6.5                                                  | Summary                                       | 230                                           |

| 7             | 6.5<br><b>Sec</b> 1                                  | Summary                                       | 230<br><b>233</b>                             |

| <b>7</b><br>8 | 6.5<br>Sect<br>7.1<br>7.2                            | Summary                                       | 230<br><b>233</b><br>235                      |

|               | 6.5<br>Sect<br>7.1<br>7.2                            | Summary                                       | 230<br>233<br>235<br>244                      |

|               | 6.5<br>Sector 7.1<br>7.2<br>Con                      | Summary  urity Impact  Implications           | 230 233 235 244 247                           |

|               | 6.5<br>Sector 7.1<br>7.2<br>Com<br>8.1               | Summary  Arity Impact  Implications           | 230 233 235 244 247 250                       |

| 8             | 6.5<br>Sector 7.1<br>7.2<br>Com<br>8.1<br>8.2<br>8.3 | Summary  arity Impact  Implications           | 230<br>233<br>235<br>244<br>247<br>250<br>258 |

|              | A.1  | Components                 | 280 |

|--------------|------|----------------------------|-----|

|              | A.2  | Roles and Responsibilities | 282 |

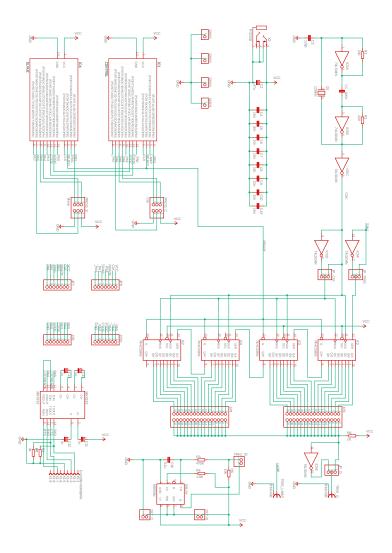

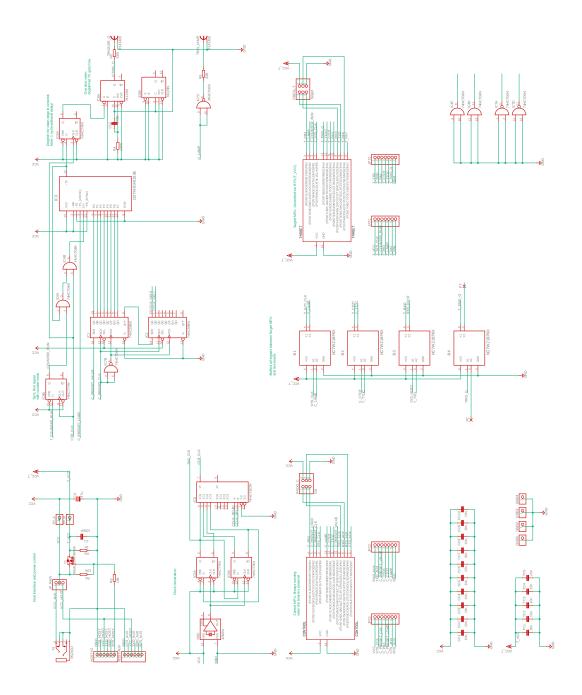

| В            | Test | Circuit Boards             | 287 |

|              | B.1  | Purpose                    | 288 |

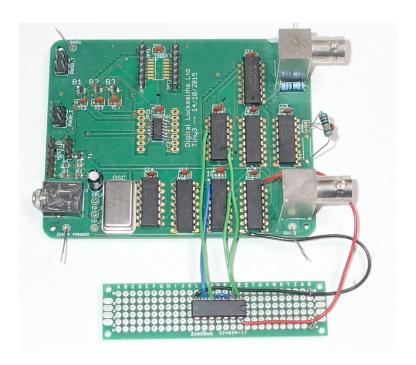

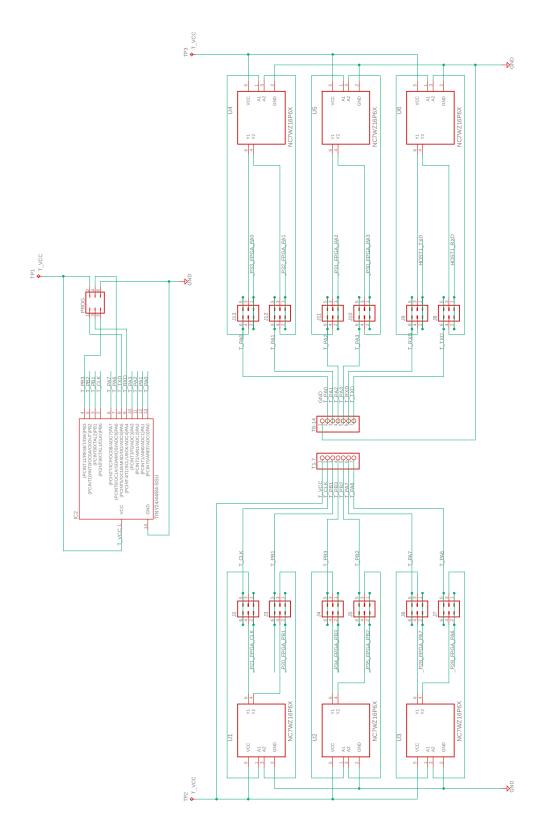

|              | B.2  | Board 1                    | 288 |

|              | В.3  | Board 2                    | 291 |

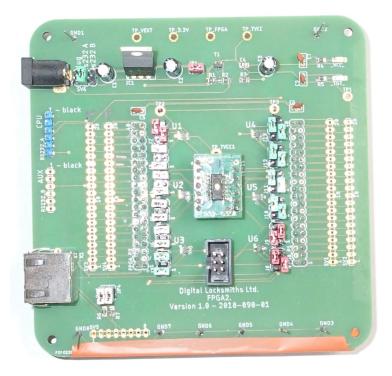

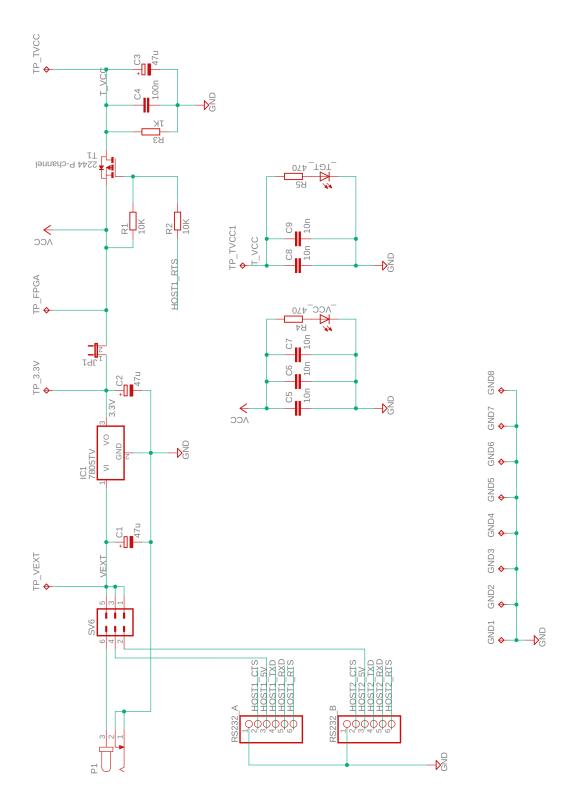

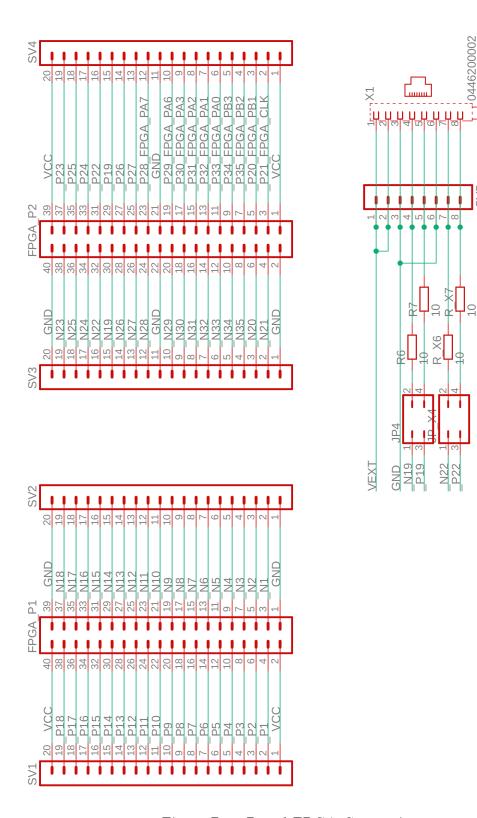

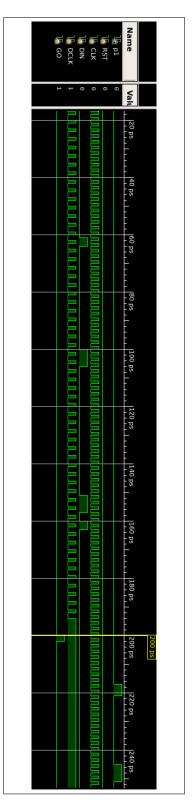

|              | B.4  | Board FPGA                 | 294 |

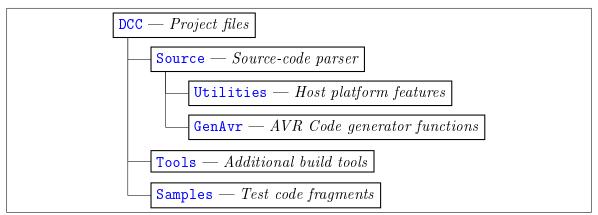

| $\mathbf{C}$ | Defe | ensive C-Compiler          | 301 |

|              | C.1  | Operation                  | 303 |

|              | C.2  | Samples                    | 304 |

# List of Tables

| 2.1  | Key Nulling Exploit                                                    | 74         |

|------|------------------------------------------------------------------------|------------|

| 3.1  | ATTiny841 Features                                                     | 102        |

| 3.2  | No Operation Results                                                   | 120        |

| 3.3  | Inc/DecNo Operation Results                                            | 121        |

| 3.4  | Arithmetic Operation Results                                           | 122        |

| 3.5  | Observed laser induced errors on load/store operations                 | 123        |

| 3.6  | Conditional branch                                                     | 124        |

| 3.7  | Laser induced errors                                                   | 125        |

| 3.8  | Branch Test Results                                                    | 129        |

| 3.9  | Branch Test Results, fixed location, Third Q-cycle                     | 130        |

| 3.10 | Errors by Power and Aperture                                           | 135        |

| 4.1  | Test Pulses, Permutations and Time. $(n = 32, at  4  Samples  s^{-1})$ | 156<br>157 |

|      | Jump Matrix Termination States                                         |            |

| 4.3  | Speck Round Attack                                                     | 160        |

| 5.1  | Test Roles                                                             | 182        |

| 5.2  | Test Samples                                                           | 184        |

| 5.3  | Hybrid Defence Test                                                    | 190        |

| 6.1  | Triple Values                                                          | 205        |

| 6.2  | Call/Return - Single Pulse Attack                                      | 213        |

| 6.3  | Call/Return - Double Pulse Attack                                      | 215        |

| 6.4  | Conditional Branches - Single Pulse Attack                             | 219        |

| 6.5  | Conditional Branches - Double Pulse Attack                             | 221        |

| 6.6  | Macro Defended Conditionals                                            | 223        |

| 6.7  | Code Volume                                                            | 225        |

| 6.8  | Bootstrap - Code Compilation                                           | 229        |

# List of Figures

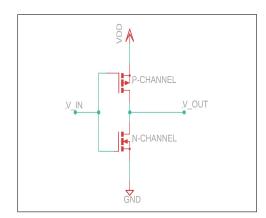

| 2-1  | CMOS Inverter                 | 58  |

|------|-------------------------------|-----|

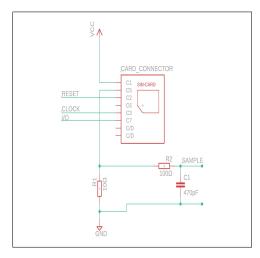

| 2-2  | Power Measurement             | 59  |

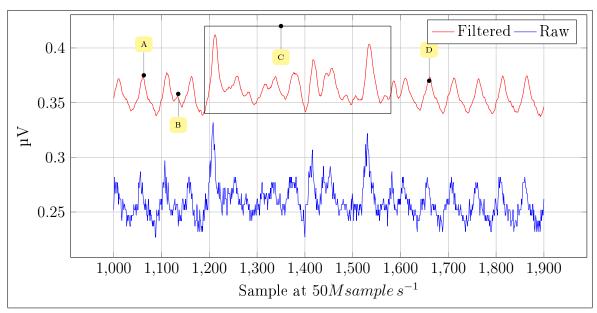

| 2-3  | Typical Power Waveform        | 60  |

| 2-4  | Crude Exponentiation          | 61  |

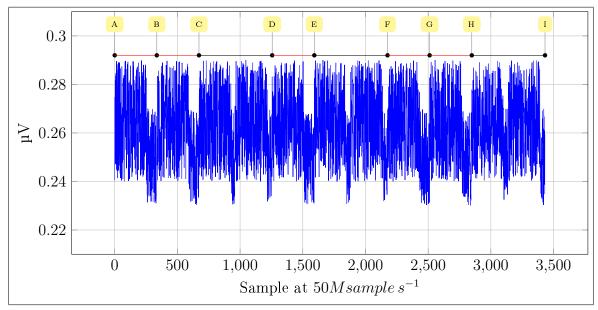

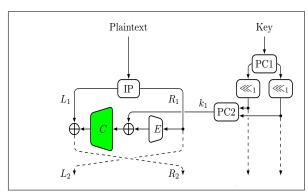

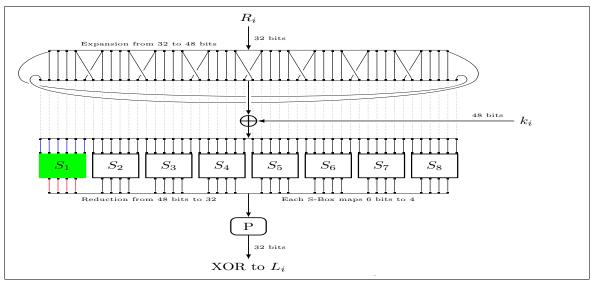

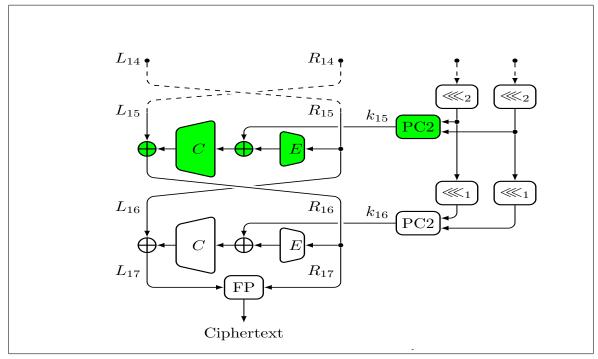

| 2-5  | DES Round 1                   | 63  |

| 2-6  | DES S-Box Structure           | 64  |

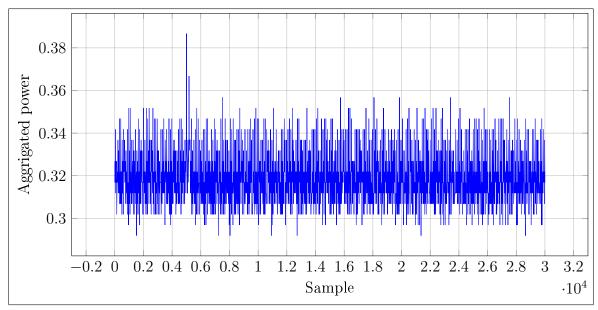

| 2-7  | DPA Accumulated Trace         | 64  |

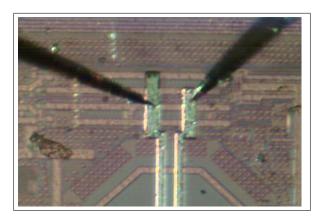

| 2-8  | ePassport Chip                | 66  |

| 2-9  | Chip Probing                  | 66  |

| 2-10 | DES Final Rounds              | 72  |

| 2-11 | Java Source Code              | 75  |

| 2-12 | Java bytecode                 | 75  |

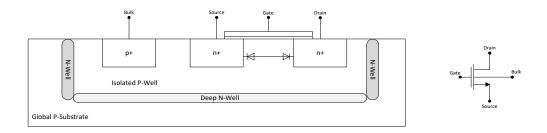

| 2-13 | Body Bias Transistor          | 79  |

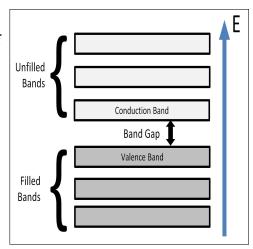

| 2-14 | Semiconductor Band Structure  | 81  |

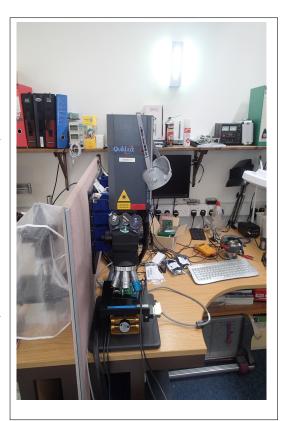

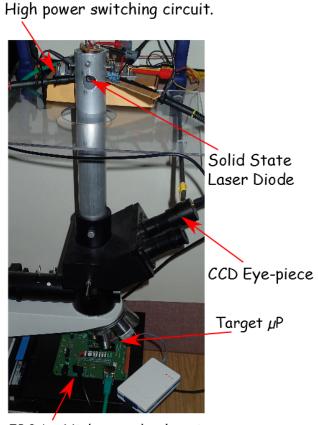

| 2-15 | Laser workstation             | 83  |

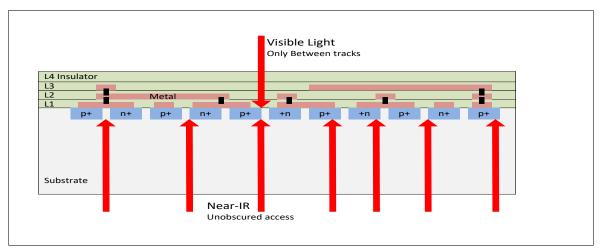

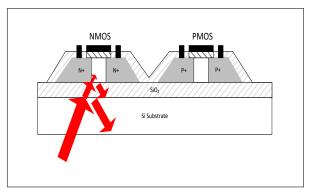

| 2-16 | Frontside and Rearside Attack | 84  |

| 2-17 | Etched Package                | 84  |

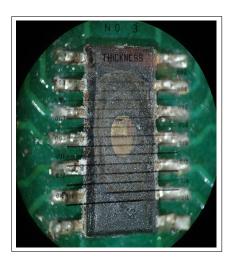

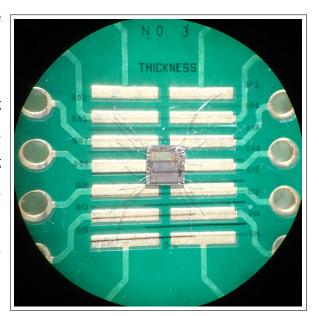

| 2-18 | Rebonded IC                   | 85  |

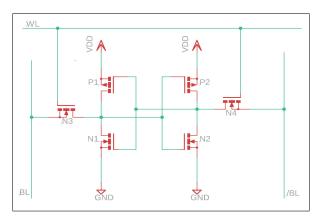

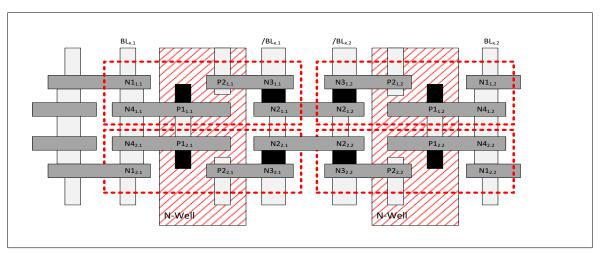

| 2-19 | Static RAM, Single Bit        | 86  |

| 2-20 | Simplified SRAM Layout        | 86  |

| 2-21 | AVR Registers                 | 87  |

| 2-22 | Silicon on Insulator          | 89  |

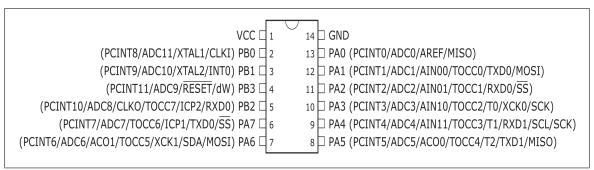

| 3-1  | ATTiny851 Pin-Out             | 102 |

| 3-2  |                               | 102 |

| 3-3  |                               | 108 |

| 3-4  |                               | 110 |

|      |                               | 111 |

| 99   |                               |     |

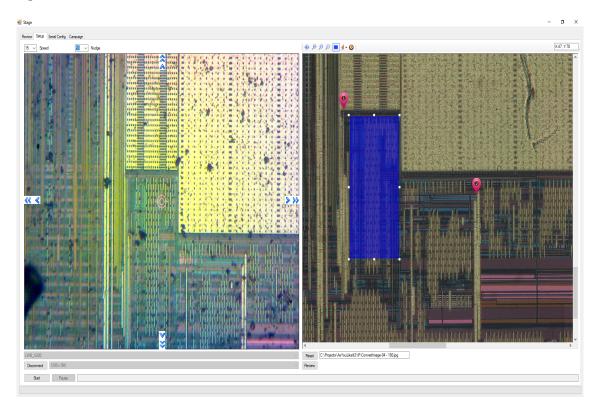

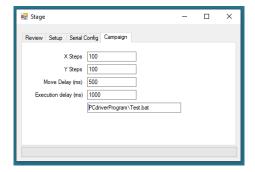

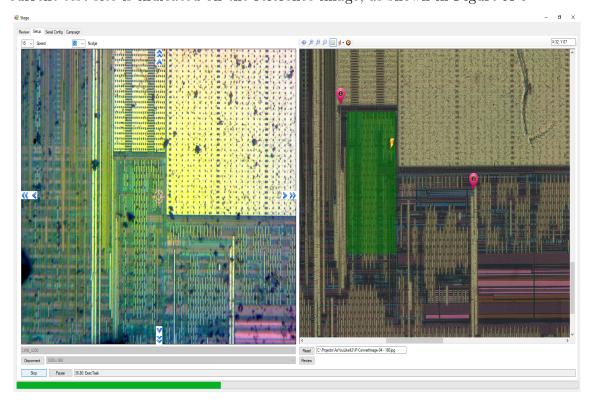

| 3-6  | Test Campaign Configuration        | 113               |

|------|------------------------------------|-------------------|

| 3-7  | Test Program 1                     | 114               |

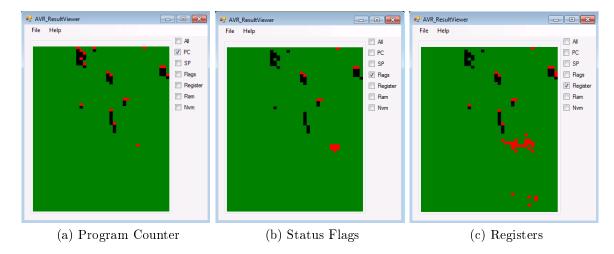

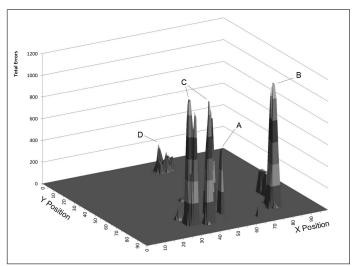

| 3-8  | Error Distribution Plots           | 115               |

| 3-9  | Lock-up Error                      | 115               |

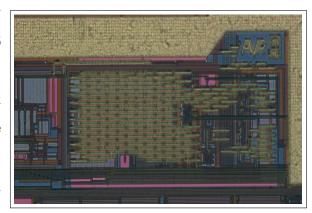

| 3-10 | DUT support, Board 2               | 117               |

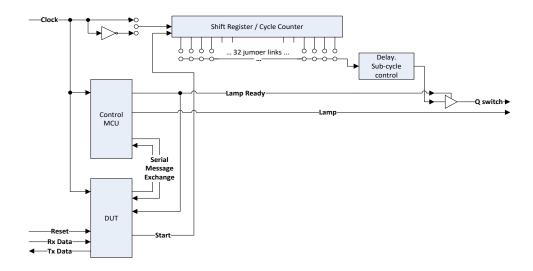

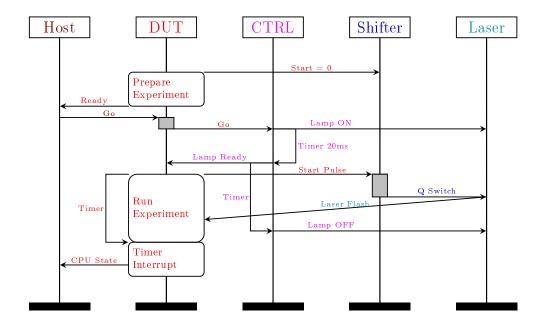

| 3-11 | Board 2 Control Logic              | 117               |

| 3-12 | Instruction Test                   | 118               |

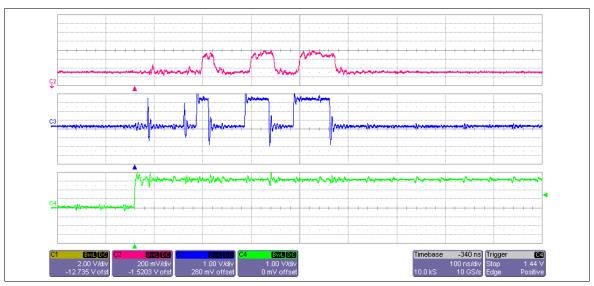

| 3-13 | Laser Firing                       | 119               |

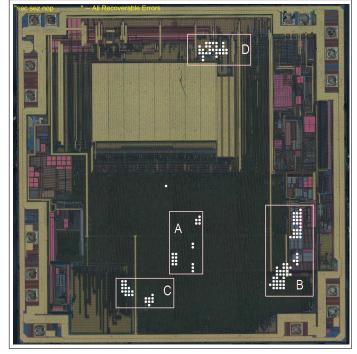

| 3-14 | Error Locations                    | 125               |

| 3-15 | Error Sensitivity Map              | 127               |

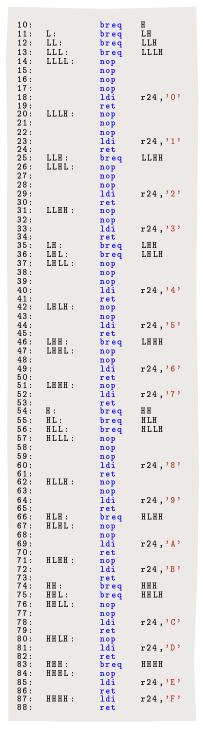

| 3-16 | Branch Test Code                   | 128               |

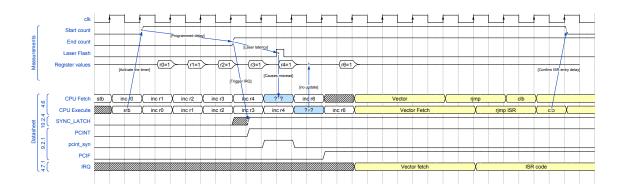

| 3-17 | Pre-Fetch Test                     | 131               |

| 3-18 | Signal Timing                      | 132               |

| 3-19 | Power and Aperture Test            | 133               |

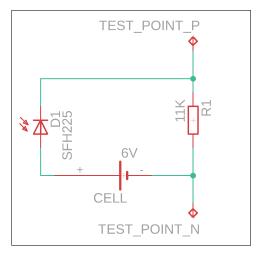

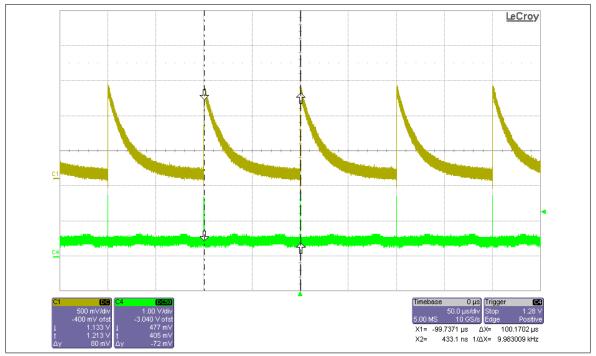

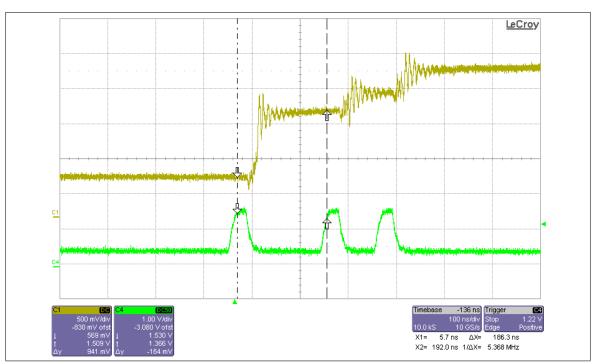

| 4-1  | Laser Diode with Heatsink and Lens | 142               |

| 4-2  |                                    | 142               |

| 4-3  |                                    | 145               |

| 4-4  |                                    | 145               |

| 4-5  |                                    | 146               |

| 4-6  |                                    | $\frac{147}{147}$ |

| 4-7  |                                    | 148               |

| 4-8  | 11                                 | 148               |

| 4-9  |                                    | 149               |

| 4-10 |                                    | 149               |

|      |                                    | 150               |

|      |                                    | 150 $152$         |

|      |                                    | 152 $153$         |

|      |                                    | 155<br>155        |

|      |                                    |                   |

| 4-15 | Speck Encryption                   | 159               |

| 4-16 | Speck Test Control                | 160               |

|------|-----------------------------------|-------------------|

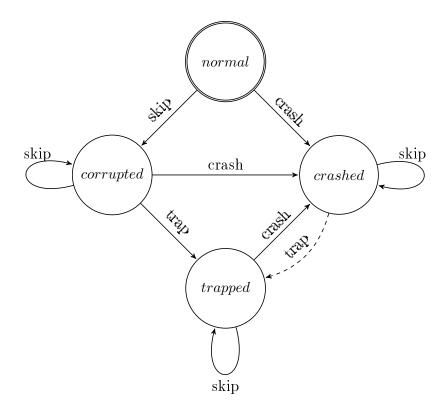

| 5-1  | Execution States                  | 168               |

| 5-2  | Unprotected                       | 171               |

| 5-3  | Double Test                       | 171               |

| 5-4  | Retest at Destination             | 172               |

| 5-5  | Inverse Test                      | 173               |

| 5-6  | Double Data                       | 174               |

| 5-7  | Data Inverse                      | 174               |

| 5-8  | Checksum Data                     | 175               |

| 5-9  | Redundant Representation          | 176               |

| 5-10 | Repeat Calculation                | 176               |

| 5-11 | Modified Compensated              | 177               |

| 5-12 | Alternative Algorithm             | 178               |

| 5-13 | Inverse Calculation               | 178               |

| 5-14 | Jump Id                           | 179               |

| 5-15 | Waymark, Late Test                | 180               |

| 5-16 | Waymark, On the Fly               | 180               |

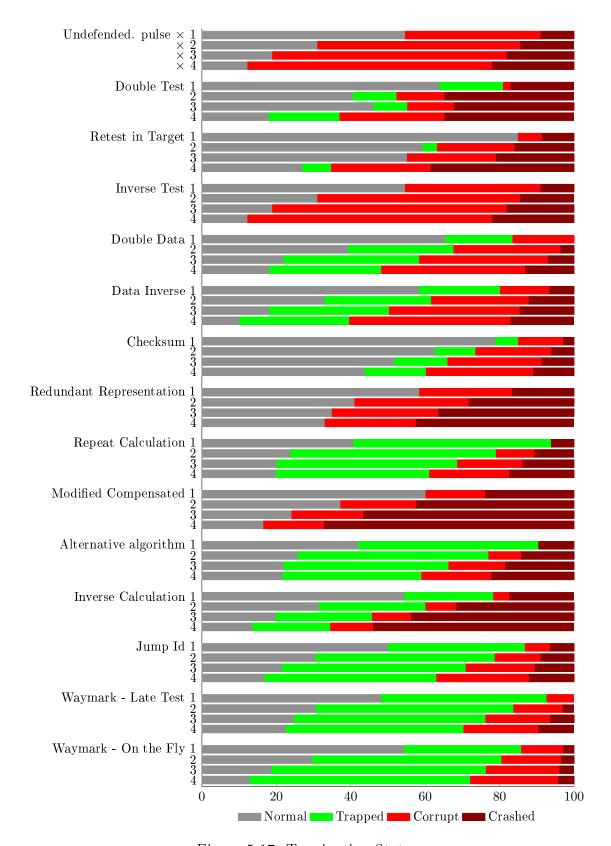

| 5-17 | Termination States                | 185               |

| 5-18 | Disassembled Double Test          | 187               |

| 5-19 | Disassembled Inverse Test         | 187               |

| 5-20 | Hybrid Defence                    | 189               |

| 5-21 | Hybrid Defence Termination States | 190               |

| 6-1  | Simple Double Test Source         | 195               |

| 6-2  | Accidental Optimised Output       | 195               |

| 6-3  | Optimised Output                  | 196               |

| 6-4  | Unoptimised Output                | 197               |

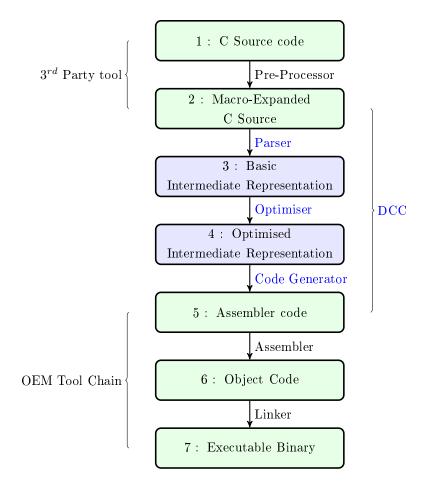

| 6-5  | Compilation Stages                | $\frac{101}{202}$ |

| 6-6  | Test Structure                    | 204               |

| 6-7  | Triple Update                     | 204               |

| ~ .  |                                   |                   |

| 6-8  | Defended Call                                | 207  |

|------|----------------------------------------------|------|

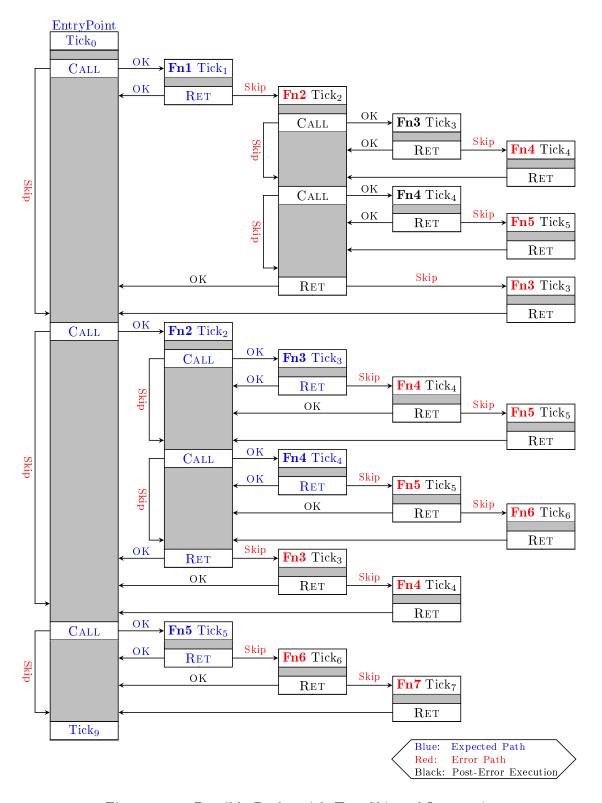

| 6-9  | Defended Entry/Exit                          | 208  |

| 6-10 | Call/Return Test Program                     | 209  |

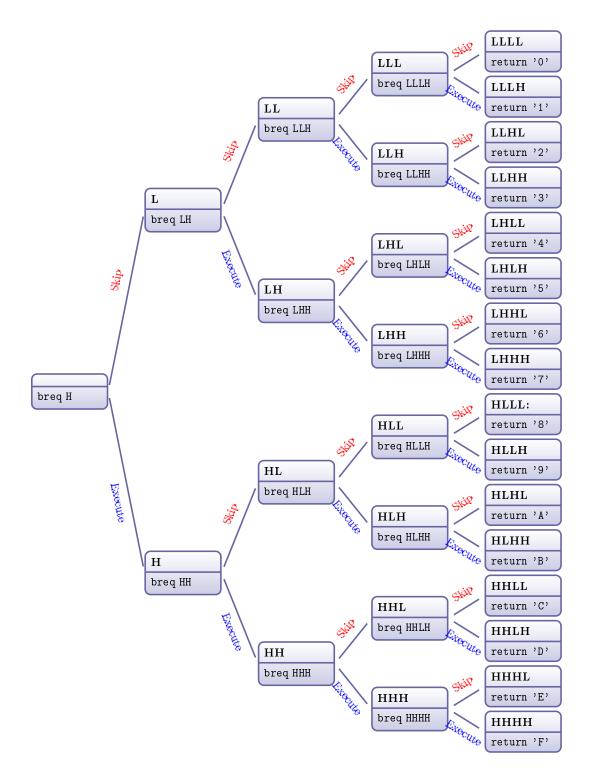

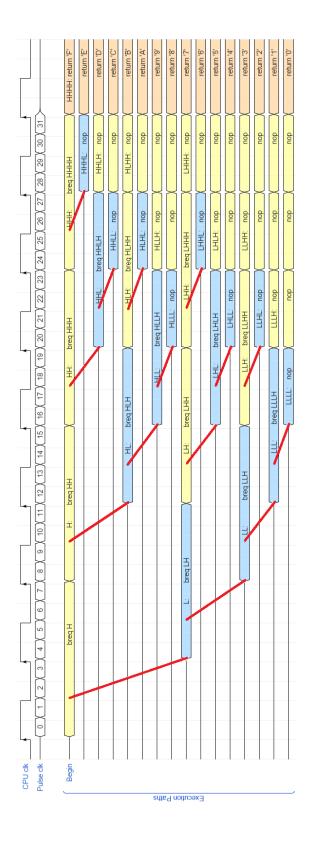

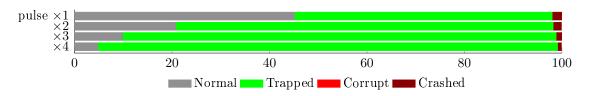

| 6-11 | Possible Paths with Two Skipped Instructions | 211  |

| 6-12 | Defended Branch                              | 217  |

| 6-13 | Branching Test Program                       | 218  |

| 6-14 | Double Checking Macros                       | 222  |

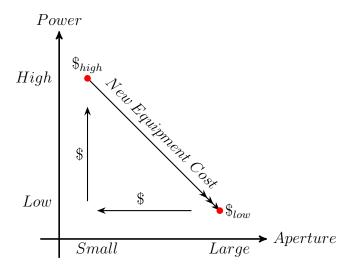

| 7-1  | Equipment Availability                       | 236  |

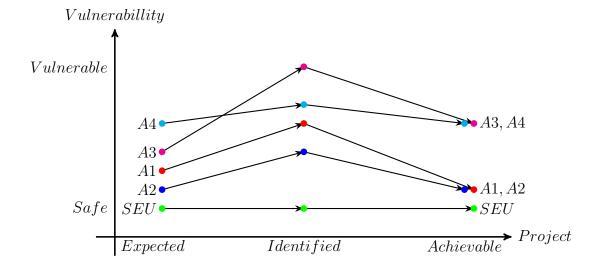

| 7-2  | Device Vulnerability                         | 240  |

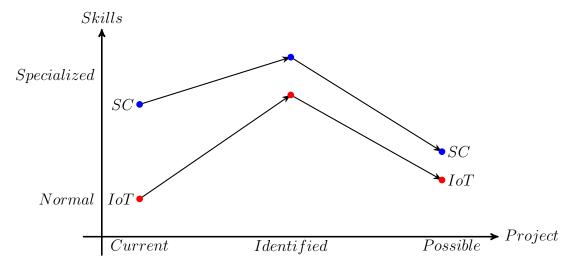

| 7-3  | Development Skills                           | 242  |

|      |                                              |      |

| A-1  | Test Rig Schematic                           | 280  |

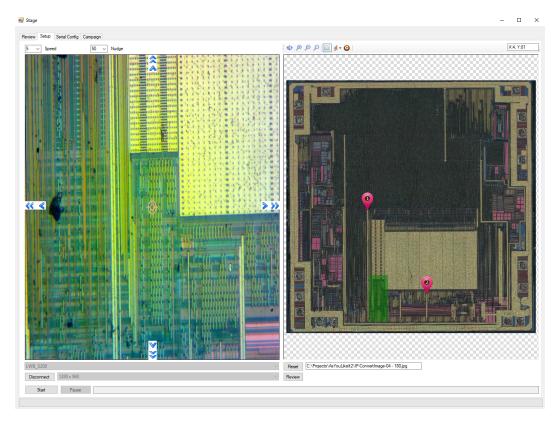

| A-2  | Sample Alignment                             | 282  |

| A-3  | Zone Identification                          | 283  |

| A-4  | Campaign Parameters                          | 284  |

| A-5  | Test Script                                  | 285  |

| A-6  | Campaign Progress                            | 285  |

| B-1  | Board 1 Populated                            | 289  |

| B-2  | Board 1 Schematic                            | 290  |

| B-3  | Board 2 Populated                            | 292  |

| B-4  | Board 2 Schematic                            | 293  |

| B-5  | Board FPGA                                   | 295  |

| B-6  | Board FPGA Rear                              | 295  |

| B-7  | Board FPGA Power Schematic                   | 296  |

| B-8  | Board FPGA DUT                               | 297  |

| B-9  | Board FPGA Connections                       | 298  |

| B-10 | Simulation                                   | 299  |

| Q 1  |                                              | 9.00 |

|      | DCC Project Directory Structure              | 302  |

| C-2  | Call & Return — Source Code                  | 304  |

## List of Figures

| C-3 | Call & Return — Undefended Output  | 305 |

|-----|------------------------------------|-----|

| C-4 | Call & Return — Defended Output    | 306 |

| C-5 | Branching Test — Source Code       | 307 |

| C-6 | Branching Test — Undefended Output | 308 |

| C-7 | Branching Test — Defended Output   | 309 |

| C-8 | Variable Declaration — Source Code | 310 |

| C-9 | Variable Declaration — Output      | 310 |

# List of Abbreviations

|     | - Micro-Controller.                                                                                             |

|-----|-----------------------------------------------------------------------------------------------------------------|

|     | A small computer on a single integrated circuit chip 29–32, 34, 35                                              |

|     | $40-43,\ 45-49,\ 53-55,\ 58,\ 60,\ 62,\ 63,\ 76,\ 78,\ 80,\ 87-92,\ 95-97,\ 99-101,\ 103,\ 106$                 |

|     | $110,\ 111,\ 115,\ 116,\ 118-120,\ 126,\ 127,\ 130,\ 137,\ 146,\ 152,\ 162,\ 164-167,\ 174$                     |

|     | $183,\ 192,\ 203,\ 204,\ 207,\ 225,\ 231,\ 238,\ 242-245,\ 249,\ 252,\ 254,\ 256$                               |

| AES | - Advanced Encryption Standard.                                                                                 |

|     | A standardized symmetric encryption algorithm designed as a replacement for                                     |

|     | DES                                                                                                             |

| API | OU - Application Protocol Data Unit.                                                                            |

|     | The communication packets exchanged between a smartcard reader and a smart                                      |

|     | card                                                                                                            |

| CA  | - Certification Authority.                                                                                      |

|     | The issuer of digital certificates.                                                                             |

|     | The issuer of digital certificates.                                                                             |

|     | Digital certificates attest to the relationship between a public key, the named                                 |

|     |                                                                                                                 |

| CC  | Digital certificates attest to the relationship between a public key, the named                                 |

| CC  | Digital certificates attest to the relationship between a public key, the named subject associated with the key |

|     | Digital certificates attest to the relationship between a public key, the named subject associated with the key |

|     | Digital certificates attest to the relationship between a public key, the named subject associated with the key |

|     | Digital certificates attest to the relationship between a public key, the named subject associated with the key |

| CCI | Digital certificates attest to the relationship between a public key, the named subject associated with the key |

| CCI | Digital certificates attest to the relationship between a public key, the named subject associated with the key |

| CFI                      | - Control Flow Integrity.                                                        |

|--------------------------|----------------------------------------------------------------------------------|

|                          | Ensuring program flow control transfers are deliberatly instigated by the exe-   |

|                          | cuting program and not a consequence of faulty execution. 199, 203, 207, 230,    |

|                          | $231,\ 243,\ 245,\ 257,\ 260$                                                    |

| CM                       | OS - Complementary metal—oxide—semiconductor.                                    |

|                          | The principle technology used in integrated circuit manufacture 79               |

| CPA                      | - Correlation Power Analysis.                                                    |

|                          | An enhancement on DPA involving a model of a device's power consumption          |

|                          | to augment trace categorization process                                          |

| CPU                      | J - Central Processing Unit.                                                     |

|                          | The main processor responsible for executing program code. 98, 111, 116, 132,    |

|                          | $157,\ 165,\ 190,\ 191,\ 209,\ 251,\ 252,\ 260,\ 289,\ 302$                      |

| CRT                      | ' - Chinese Remainder Theorem.                                                   |

|                          | A theorem which gives a unique solution to simultaneous linear congruences       |

|                          | with coprime moduli. It is of particular interest when applied to RSA as it      |

|                          | significantly reduces computer execution time when performing exponentiation     |

|                          | to large moduli                                                                  |

| CSV                      | - Comma-Separated Value.                                                         |

|                          | An ASCII text file in which each record occupies a single line and each field in |

|                          | the record is separated by a comma (or similar punctuation)                      |

| DCC                      | C - Defensive C Compiler.                                                        |

|                          | The experimental code generator written for this investigation. 201, 203, 210,   |

|                          | $212,\ 216-218,\ 222,\ 224-228,\ 230-232,\ 256,\ 257,\ 302$                      |

| $\mathbf{D}\mathbf{D}$ o | S - Distributed Denial of Service.                                               |

|                          | An synchronised attack, coming from multiple sources, with the intention of      |

|                          | making the target unusable or unobtainable                                       |

| DES            | - Data Encryption Standard.                                                                       |

|----------------|---------------------------------------------------------------------------------------------------|

|                | A widely deployed standardised symmetric encryption algorithm. It has been                        |

|                | superseded by AES                                                                                 |

| DFA            | - Differential Fault Analysis.                                                                    |

|                | A cryptographic attack performed by comparing the erroneous output from a                         |

|                | cryptographic process                                                                             |

| DIL            | - dual in-line package.                                                                           |

|                | Chip packaging that uses two parallel rows of pins with 2.54 mm pin to pin                        |

|                | separation $(0.1 \text{ inch})$                                                                   |

| DPA            | - Differential Power Analysis.                                                                    |

|                | Statistical analysis of side-channel leakage relating the power consumption of a                  |

|                | device                                                                                            |

| DUT            | $\Gamma$ - Device under test.                                                                     |

|                | The sample being investigated or attacked                                                         |

|                | $38,\ 50,\ 55,\ 59,\ 97,\ 99,\ 103-116,\ 119,\ 132,\ 133,\ 137,\ 138,\ 141-146,\ 150,\ 151,\ 158$ |

|                | $159,\ 165,\ 166,\ 169,\ 192,\ 226,\ 234,\ 238,\ 244,\ 250,\ 251,\ 253,\ 254,\ 256,\ 257,\ 259$   |

|                | 280–284, 287–289, 291, 294, 299                                                                   |

| $\mathbf{EM}$  | - Electro Magnetic Radiation.                                                                     |

|                | Waves in the electro-magnetic field propagating through space 54, 238                             |

| EMY            | V - Europay Mastercard Visa.                                                                      |

|                | The industry standard for bank cards and payment terminals. 74, 95, 106, 169                      |

| $\mathbf{FIB}$ | - Focused Ion Beam.                                                                               |

|                | A device, similar in operation to an electron microscope, that uses a focused                     |

|                | beam of ions for deposition or ablation of material                                               |

| FPG            | <b>A</b> - Field-Programmable Gate Array.                                                         |

|                | Configurable integrated circuit that is customisable in-circuit 146, 150, 294                     |

|                | 299                                                                                               |

| GCC - the GNU Compiler Collection.                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Open source compiler tools originally written as the compiler for the GN operating system 172, 173, 192, 198, 202, 210, 217, 222, 224–228, 232, 256 257 |

| GIGO - Garbage in, Garbage Out.                                                                                                                         |

| Unexpected results derived from calculations on unexpected data 2                                                                                       |

| GPIO - General Purpose Input Output.                                                                                                                    |

| Uncommitted digital signal pins on a $\mu C$ that may be configured to interact                                                                         |

| with external peripherals                                                                                                                               |

| HDL - Hardware Description Language.                                                                                                                    |

| A computer language used to describe the structure and behaviour of electronic                                                                          |

| circuits. E.g. Verilog and VHDL                                                                                                                         |

| IC - Integrated Circuit.                                                                                                                                |

| Otherwise known as a silicon chip. 44, 50, 58, 59, 62, 67, 68, 74, 77, 79–89, 97, 99, 100, 107, 112, 125–127, 134, 249                                  |

| IoT - Internet of Things.                                                                                                                               |

| A network of physical devices with embedded $\mu C$ s capable of exchanging data                                                                        |

| $35,\ 46-48,\ 99,\ 101,\ 137,\ 243,\ 261$                                                                                                               |

| IR - Intermediate Representation.                                                                                                                       |

| Internal data structures created by a compiler after parsing the source code                                                                            |

| $200-202,\ 260,\ 261,\ 302,\ 303$                                                                                                                       |

| ISA - Instruction Set Architecture.                                                                                                                     |

| An abstract definition of instruction behaviour that does not depend on the                                                                             |

| characteristics of the implementation                                                                                                                   |

| ISR - Interrupt Service Routine.                                                                                                                        |

| Code invoked in response to an interrupt signal                                                                                                         |

| JTAG - Joint (European) Test Access Group.                                             |

|----------------------------------------------------------------------------------------|

| A hardware debugging interface to electronic components 107, 109                       |

| LIDAR - Laser Imaging, Detection, and Ranging.                                         |

| Range determination using time-of-flight of reflected laser pulses $144, 253$          |

| <b>LLVM</b> - The LLVM Compiler Infrastructure Project.                                |

| The name "LLVM" itself is not an acronym; it is the full name of the project. 256, 257 |

| LSI - Large Scale Integration.                                                         |

| Whole circuits, or ICs, on silicon as opposed to individual components 97              |

| LVDS - Low-voltage differential signaling.                                             |

| Data signalling by transmiting information as the voltage difference between           |

| two adjacent wires                                                                     |

| MAC - Message Authentication Code.                                                     |

| A cryptographic checksum used to confirm the integrity, and sometimes also             |

| the origin, of a message                                                               |

| MitM - Man in the Middle.                                                              |

| An agent who is invisibly placed between both parties in a conversation who            |

| has the opportunity to read and modify messages before forwarding them to              |

| the intended recipient                                                                 |

| NDA Non-Disclosure Agreement.                                                          |

| A legally binding contract defining a confidential relationship whereby the sign-      |

| ing parties agree that sensitive information they share will not be made passed        |

| on third parties without the original owner's consent 99, 100, 225                     |

| NIR - Near Infra Red.                                                                  |

| The electromagnetic spectrum between 780 nm and 2500 nm. 83, 84, 87, 101               |

| $133,\ 143,\ 258$                                                                      |

| OBIC - | Optical | Beam | Induced | l Current. |  |

|--------|---------|------|---------|------------|--|

|        |         |      |         |            |  |

A laser injection technique to induce current flow within a semi-conductor. 81, 82

#### PCB - Printed Circuit Board.

#### PKI - Public Key Infrastructure.

The set policies, processes and procedures using asymmetric cryptographic algorithms to manage, distribute, and verify digital certificates and public keys.

52

#### **ROP** - Return Oriented Programming.

#### **RSA** - Rivest Shamir Adleman.

A public key cryptographic algorithm used for encryption and digital signature. 69, 70

#### **SER** - Soft Error Rate.

The probability of a Single Event Upset (SEU) occurring. . . . . . . . 68, 69

#### **SEU** - Single Event Upset.

A transient error in a silicon device caused by and external ionizing event. 68, 69, 77, 235, 241

#### SMID - Single Instruction Multiple Data.

Parralel operation of the same instruction on multiple data points. . . . 100

| SOI            | C - Small outline integrated circuit.                                                              |

|----------------|----------------------------------------------------------------------------------------------------|

|                | A surface-mounted integrated circuit package with pin separation of 1.27 mm                        |

|                | (0.05  inch)                                                                                       |

| $\mathbf{SPA}$ | - Simple Power Analysis.                                                                           |

|                | Analysis of a devices power consumption to infer internal behaviour 60, 62,                        |

|                | 91, 137, 192                                                                                       |

| TTL            | - Transistor-Transistor Logic.                                                                     |

|                | Defines the threshold voltages for digital logic implemented with $3.3\mathrm{V}$ or $5\mathrm{V}$ |

|                | devices                                                                                            |

| USB            | - Universal Serial Bus.                                                                            |

|                | A definition for cables, protocols and power, standardizing the connection of                      |

|                | peripherals and computers                                                                          |

| VHI            | <b>DL</b> - VHSIC Hardware Description Language.                                                   |

|                | Language to model the behavior of digital systems                                                  |

| VHS            | IC - Very High-Speed Integrated Circuits Program.                                                  |

|                | A United States Department of Defense research program to develop very high                        |

|                | speed integrated circuits                                                                          |

| VLS            | I - Very Large-Scale Integration.                                                                  |

|                | The process of integrating hundreds of thousands of transistors on a single                        |

|                | microchip                                                                                          |

| VM             | - Virtual Machine.                                                                                 |

|                | Software emulation of a machine or computer                                                        |

| WO             | RM - Self replicating computer program.                                                            |

|                | A program that propagates through a network by duplicating itself and execut-                      |

|                | ing on neighbouring machines                                                                       |

$\mathbf{YAG}$  - neodymium-doped yttrium aluminium garnet Nd:YAG.

A crystal used as the laser medium for medium power solid-state lasers. 105, 134, 138, 141, 142, 144, 145, 150, 151, 161, 192, 252, 259, 288, 291, 294

### **Forward**

In 1997 I found myself debugging some curious production-line failures. The world's first ePassport was due to be launched in Malaysia, and while production of the inlays was gearing up, the unit failure rate became alarmingly high. It was my code and, therefore, my problem. Each unit consisted of two integrated circuits and, when tested after assembly, some responded with unexpected data. The issue was traced back to the bonding machine supervisor, who, worried about production reliability, frequently inspected the alignment of the wire bonding machine. High failure counts coincided with these inspections. The inspection light was the root cause of the issue. The chip's internal program was corrupting its memory because of this light. The immediate solution was to perform electrical tests in the dark; the long term solution was to modify the internal program to survive execution errors. This fix was not a defence against software bugs or unanticipated data crashing an application. It was a defence against the CPU itself not reliably running its program. This was my first exposure to Defensive Programming, and at this time, we considered errors to be a nuisance rather than a threat.

Two years later, in 1999, while working on MyKad, Malaysia's project for an electronic national I.D. card, we saw the software partner responsible for the e-Purse element attacking our code with a camera flash-gun. Flashes of light were being used to induce errors deliberately. The defensive code behaviour needed to be extended to cover all life-cycle states of the application. Defensive programming was needed to protect assets, not just to improve production line efficiency.

It was not until 2002 that "Optical Fault Induction Attacks" were first publicly described. Earlier theoretical papers on the consequences of errors could now be combined with a reliable mechanism to induce them. What had been an open secret in the industry was now public knowledge. Every smartcard application from here on would need to be defensively coded and tested for fault resilience.

Over the following years, it became apparent that testing fault-tolerance was a poorly understood art. I was responsible for getting multiple smartcard applications evaluated for security certification, and evaluators for ePassport, EMV, and JavaCard/Global-Platform sometimes had conflicting views regarding defensive code strategies. It appeared that the error effects, and consequently defences, were driven by folk-lore and tradition. Apparently, nobody knew the best approach. This uncertainty was expensive for me as a developer. One application, in particular, was problematic. A single ROM-Mask, implementing the EMV payment card protocols, was intended to be configurable to be either MasterCard or Visa as a production line option.

The security evaluators assessing the MasterCard related code behaviour insisted on a particular style of defence. The assessors of the Visa components insisted on another. It was impossible to satisfy both at the same time.

This study was born out of a desire to shed light on that confusion, improve the effectiveness of defensive code, and simplify its deployment.

# Chapter 1

# Introduction

| Contents |                                         |  |  |  |  |  |  |

|----------|-----------------------------------------|--|--|--|--|--|--|

| 1.1      | Research Questions                      |  |  |  |  |  |  |

|          | 1.1.1 Nature of Errors                  |  |  |  |  |  |  |

|          | 1.1.2 Practicalities of Error Induction |  |  |  |  |  |  |

|          | 1.1.3 Defences                          |  |  |  |  |  |  |

|          | 1.1.4 Deployment                        |  |  |  |  |  |  |

| 1.2      | Methodology                             |  |  |  |  |  |  |

| 1.3      | Significance                            |  |  |  |  |  |  |

|          | 1.3.1 Publications                      |  |  |  |  |  |  |

| 1.4      | Structure of this Thesis                |  |  |  |  |  |  |

Errors in software, and computers in general, are ubiquitous. Human error, manufacturing defects and misunderstood problems introduce uncertainty into what is widely perceived to be prescriptive or predictable behaviour. These errors can take multiple forms and can have serious repercussions; they may be the consequences of poor program design, implementation bugs, or, most dangerously, being deliberately induced by an attacker.

- First of all, there is the simple case of inaccurate coding. Here typographical mistakes by the programmer lead to erroneous results. Sometimes these errors can go undetected through many rounds of debugging and testing but still have catastrophic effects, for example, NASA's Mariner 1 spacecraft [122]. Here a missing hyphen [123] lead to the destruction of the launch vehicle and its payload.

- There is flawed logic or faulty algorithms where accurate implementation still yields erroneous results because of a flawed recipe. Such bugs may take years to manifest themselves as problems. A pertinent example would be the Julian calendar's algorithm for inserting leap years and its subsequent replacement with the Gregorian calendar one and a half millennia later [60]. Similar rounding errors were responsible for an accumulated 50% inaccuracy in the Vancouver Stock Exchange's index of leading shares [142], and for the failure of a missile defence system [189] resulting in the loss of 28 lives.

- Another source of errors is faulty input data. There are two categories of this type of error;

- Unexpected structure of data may cause internal buffers to overflow and corrupt neighbouring data. In extreme examples, the effect can be exploited to run unauthorised software on a computer [11]. These bugs arise when the data receiver fails to check the size and syntax of the incoming data.

- Well-formed but erroneous data may also be presented to a computer.

Commonly referred to a Garbage In Garbage Out (GIGO) errors, they can have equally devastating effects; most famously when metric and imperial units were transposed in navigation software on NASA's Mars Climate Orbiter [35].

- Broken or faulty hardware can prevent a computer from performing correctly. Such errors usually prevent the use of the device until the issue has been physically identified and fixed. A dead moth obstructing a mechanical relay in an early computer is credited as being the original computer bug and its removal the origin of the term debugging [161].

- Finally, we have transient effects. Here bug-free code, processing well-formed data and executing on an undamaged processor, may momentarily be influenced to perform a faulty operation before resuming normal processing behaviour. The effects of this transient error may then propagate in much the same way GIGO errors do. These transient effects may be attributed to 'acts of god' or cosmic rays [26], or may have been deliberately induced by an attacker [75].

Deliberate induction of errors in an otherwise healthy Micro-Controller ( $\mu C$ ) is the focus of this thesis. Commonly referred to as perturbation errors or *Glitch Attacks*, the adversary attempts to make the chip perform unauthorised functions or disclose secret information. The mechanisms available to perform glitch attacks are diverse, and the consequences can be significant. These are discussed in detail in Chapter 2.

Error induction is perceived as challenging to perform and leads to a degree of complacency, with many developers believing the obstacles to an attack provide sufficient defence for their products. This remains a valid argument when the attack's cost significantly outweighs the value of the information gained. However, a close eye needs to be kept on the evolving repertoire of attacks and their implementation costs.

Where the value of the information within a device is high, the device itself must take steps to recognise the attack and take defensive action. This is commonly referred to as *Defensive Programming*. Unfortunately, defensive code comes with penalties in

terms of performance degradation, additional code volume and additional development effort. It has led many developers to focus on critical functions within the system as they juggle the competing drivers of security, performance and time to market.

The design of efficient defences requires an understanding of the properties of the induced errors. Personal experience of the EMV code-review and penetration testing process [66] suggests that much folk-law, instinct and wishful thinking exists. Contradictory advice from different testing laboratories relating to the same piece of code was the trigger that initiated this body of research.

## 1.1 Research Questions

In this study, we address four basic questions about device security. In particular, we look at the implications for devices deployed in the low-cost consumer electronics field, where users increasingly and unwittingly place their trust in an ever-expanding array of intelligent devices.

- RQ1 Do induced errors have repeatable characteristics that would assist developers in predicting a device's likely modes of failure?

- RQ2 Is it practical for attackers to induce multiple errors into software executing on a  $\mu C$  and exploit their effects without needing access to sophisticated laboratory equipment?

- RQ3 Can a better understanding of a device's modes of failure be translated into improved security via targeted software countermeasures?

- RQ4 Is it practical to automate the generation of defensive measures within a  $\mu C$ 's software development tools?

#### 1.1.1 Nature of Errors

RQ1 — Do induced errors have repeatable characteristics that would assist developers in predicting a device's likely modes of failure?

This is a simple question in principle, but several complicating factors need to be addressed. A representative target must be identified that is unencumbered by preexisting defences that will skew observed behaviour or result in the device's destruction. We must also find a viable mechanism for capturing the internal state of the Device Under Test (DUT) immediately after the induction of an error. The intention is to do this using a normally executing  $\mu C$ , removing the potential effects debug mode may have and making the attack scenario as similar as possible to typical deployment. Finally, many samples and experiments will be required. The process will involve creating many test scenarios and repeating these tests while directing the attack onto different physical locations on the surface of a  $\mu C$ . Automation of the data collection process will be essential, and tools will need to be built to do this.

#### 1.1.2 Practicalities of Error Induction

RQ2 — Is it practical for attackers to induce multiple errors into software executing on a  $\mu C$  and exploit their effects without needing access to sophisticated laboratory equipment?

The repertoire of attack techniques is wide, as discussed below in Section 2.2, and some of them require very expensive, difficult to access equipment. Some other attacks have been demonstrated in laboratory settings, but it may be possible to replicate them with modest resources and without privileged access to laboratory services. Reducing the cost and logistical difficulties associated with attacking a device has implications for a wide range of devices that have hitherto been assumed to be not worth attacking. Consequently, the software they run will need to implement additional defences.

#### 1.1.3 Defences

RQ3 — Can a better understanding of a devices' modes of failure be translated into improved security via targeted software countermeasures?

The deployment of defences is always a compromise between application efficiency and security. Speed, code size and development effort compete with the ability to resist a range of attacks. The tools and techniques used to characterise glitch errors will also be suitable for evaluating the efficacy of defences. The expectation is that the knowledge gained about the glitch errors' nature will assist the definition of optimal defences. This will be achieved by identifying techniques to recognise errors and assessing their impact.

Removing the guesswork from the application of defences addresses the initial motivation for this study.

### 1.1.4 Deployment

RQ4 — Is it practical to automate the generation of defensive measures within a  $\mu C$ 's software development tools?

It is already understood that some defences are complicated, intricate to deploy, and difficult to test. This factor makes it unlikely that the required knowledge and skills will be available in most development teams, particularly in the less security conscious but potentially vulnerable consumer products market. Ideally, it will be possible to encapsulate the required knowledge into development tools to include appropriate defences automatically. Such a tool will improve the security of simple products without the need to educate and retrain developers. For high-security products and skilled developers, it will complement the programmers' skills, reduce the opportunity for defence omission by human error, and simplify the slow and expensive process of independent code review.

Turning the laboratory results into a practical tool completes this mission.

# 1.2 Methodology

To a large extent, the strategy used to answer the research questions was dictated by those same questions.

An initial investigation was carried out to identify prior art, relevant tools, and operating parameters. In particular, reports of attempts to categorise errors and measure the efficacy of defences would be sought out. This review would ensure the relevance of the proposed research questions and identify the appropriate equipment to use as the starting point for this investigation. This equipment would need to enable controlled generation of error stimuli, need minimal manual input and be capable of running uninterrupted for long periods.

The first requirement was to create a fault induction system that could be used to evaluate the error responses from a DUT. This step involved removing unrelated obstacles that complicate data collection without affecting those data. These obstacles add complications to the implementation of an attack, and each could be considered, to a degree, a defence in its own right, adding cost to an attack's implementation. These obstacles are unrelated to the effects this study targets, so, where possible, their elimination is required to simplify access to the features of interest. This simplification would be achieved by developing bespoke circuit boards to control the environment the DUT operates in and by careful choice of DUT.

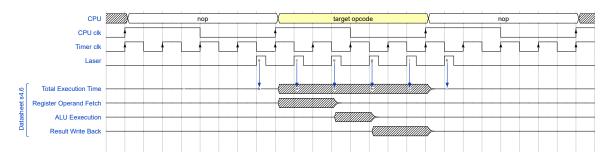

The follow on requirement was to collect data from the DUT while subjecting it to attack with the test rig. This blitz of error induction would be time-consuming, as many processor instructions would need to be exhaustively attacked and the results collected. The variable parameters included the physical position of the laser focus on the DUT's surface, the timing of the attack relative to the execution of an instruction, as well as the power and size of the laser pulse. The data collected through this process would then need to be analysed to identify characteristics that could be exploited. Bespoke tools would need to be written to coordinate experiments, collect data and analyse them.

The techniques for characterising error responses also apply to testing the effi-

cacy of programmed defences. Other researchers have attempted defence testing via simulation, but we would be able to obtain real-world results with the envisaged equipment. This equipment would enable a relatively straightforward evaluation of defences and would also answer the first of the research questions (RQ1).

The properties of the induced errors, and the complications observed while collecting them, would lead to optimisations in the attack mechanism and the development of a low-cost, more capable replacement for the test rig. This improved test rig would answer the second research question (RQ2).

Searching for and recognising identifiable characteristics in the DUT's error induced behaviour should also suggest new and more robust defences, specifically optimised for the DUT; this would provide the answer to the third of the research questions (RQ3).

Finally, after identifying demonstrably strong defence techniques, the viability of automatic generation of defensive code would be investigated. The intention would be to extend the behaviour of a compiler by applying appropriate defences during its object code generation stage. The efficacy of this code generator would be tested with the tools and techniques developed previously. This tool would answer the last of the original research questions (RQ4).

## 1.3 Significance

There is no doubt that error-free computation is critical to the security of devices such as smartcards. Errors are not just an inconvenience that crashes a device or causes embarrassment by failing to permit an authorised action. Errors can be exploited. As far back as 1997, Boneh et al. [37], and Biham et al. [32], demonstrated how to recover keys from encrypted data if an arithmetic error occurs during the encryption process.

Errors are easy to induce. All  $\mu C$ 's come with a datasheet that explains the safe working ranges for properties such as supply voltage, signal frequencies and, operating temperature. Exceed these limits, and errors will occur. Also, by controlling when

and how long these limits are exceeded, an attacker can localise errors to specific parts of an algorithm. Very fine control of error injection in terms of physical location on a chip and the moment of an attack can be achieved with a focused laser beam. This technique has been in the public domain since Skorobogatov and Anderson [165] published details in 2002.

Defences against errors can be added to the  $\mu C$ 's hardware. Sensors to detect input signals that deviate from the specification and sensors for light are relatively common in security chips. In some  $\mu C$ s, duplicate CPUs simultaneously performing identical actions can detect errors by continuously comparing the cores' states. This level of defence is reserved for the highest security devices such as Infineon's SLE78 family [88].

For many  $\mu C$ s designed for consumer electronics, and for the burgeoning Internetof-Things (IoT) market, such hardware security augmentation is rare or non-existent.

Instead, the programmer needs to write self-checking code, which involves anticipating

attacks and coding defences that detect abnormal behaviour within a program. These

coding techniques require a skill set that is not common amongst those tasked with

developing software for consumer electronic devices. However, as is detailed by Desai

[61], such devices are increasingly being trusted with personal information and have

access to private networks.

Defences have a cost of their own. Development time increases, execution speed degrades, and code volume expands. Redundant code fragments that cannot be exercised under normal operating conditions further complicate the testing process.

In the following chapters, we describe a technique that we developed to identify the effects of induced errors. Understanding these effects is a critical first step in defining efficient software defences. Furthermore, our discoveries about the nature of the errors indicated that this process did not require particular specialist equipment. We went on to develop a low-cost alternative error injector with superior capabilities. This equipment was then used to measure the efficacy of a range of defensive code structures, an exercise previously only seen in simulation, for example, by Theissing [173].

Knowledge of the nature of errors and the best ways to defend against them is of great value if it can be deployed in fields where such techniques are frequently neglected. We developed a C-compiler that automatically inserts defensive code to demonstrate that this is possible. This tool has multiple and wide-ranging advantages.

- 1. It makes the techniques available to a wider audience without the need to retrain an army of developers.

- It ensures systemic coverage of defences. Often defences are only placed in code

that the programmer perceives as vulnerable, overlooking equally vulnerable

support functions.

- 3. Defences that cannot be described in the syntax of the source-code language can be inserted.

- 4. Even for high-security applications where specifically skilled programmers are deployed, this tool can remove the opportunity for the accidental omission of defences. It is expected that this would also reduce the time required to review and certify code that is destined for scheme accreditation [66] or Common Criteria certification [53]. The focus of code reviewing can shift to the characterisation of errors and efficacy of defences. This process is more straightforward and less error-prone than searching an application's source code for overlooked opportunities to add defences or where defences are incorrectly implemented.

#### 1.3.1 Publications

The following publications have been produced during the course of this investigation. Each paper covers the major phases of this investigation.

1. Characterising a cpu fault attack model via run-time data analysis.

Published 2017 - IEEE International Symposium on Hardware Oriented Security and Trust (HOST).

doi: http://dx.doi.org/10.1109/HST.2017.7951802

### 2. High precision laser fault injection using low-cost components.

Published 2020 - IEEE International Symposium on Hardware Oriented Security and Trust (HOST).

doi: http://dx.doi.org/10.1109/HOST45689.2020.9300265

In addition, the experimental defensive compiler developed as part of this study can be found in a public repository: https://github.com/digitallocksmiths/DCC.

## 1.4 Structure of this Thesis

Chapter 2 describes the background to the issues addressed in this study. It provides a history of the evolution of attacks targeting execution errors and the mechanisms by which such errors can be induced. It describes the threats posed by such errors and the arsenal of countermeasures available. It describes the practical issues encountered when attempting to induce erroneous execution and the choices available to a would-be attacker.

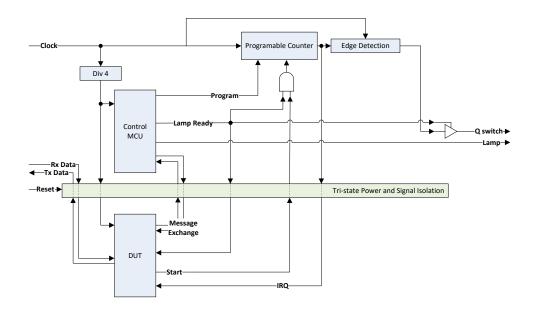

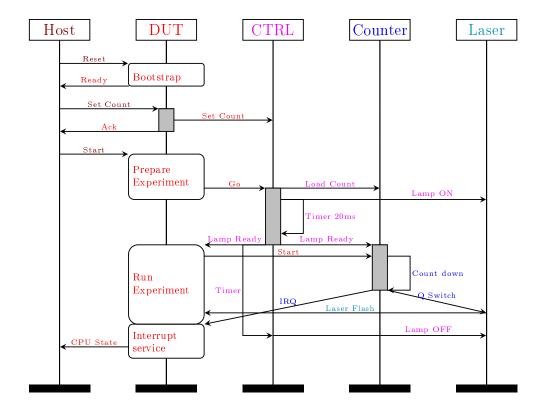

Chapter 3 describes the technique we devised for determining the effects of induced errors. It describes the collection data relating to the internal state of the DUT and the categorisation of the effects of the errors. Finally, it draws conclusions that guide the development of new test equipment.

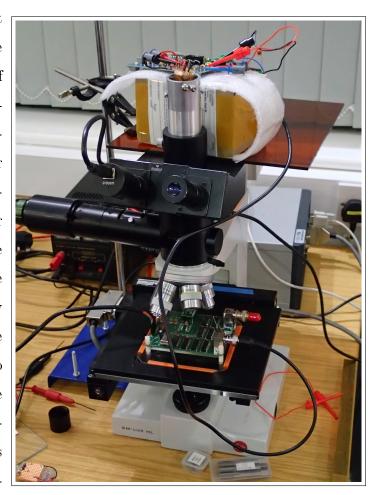

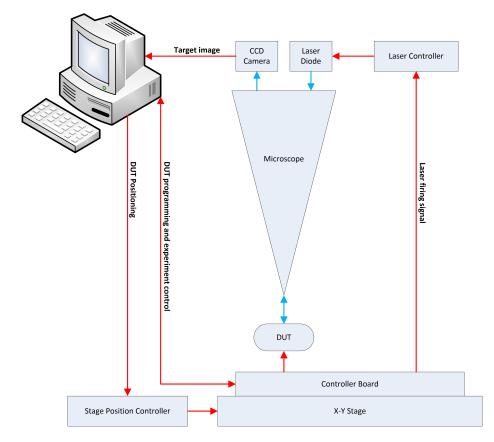

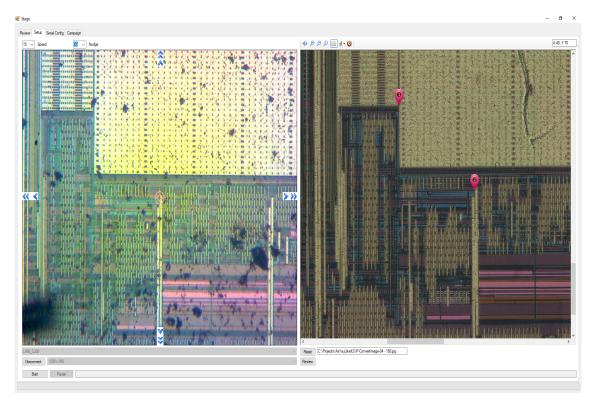

The development of a new laser fault injection workstation is described in Chapter 4. This chapter covers the components used, the new device's capabilities, and the engineering obstacles overcome during its development. It ends with experimental results showing that it is more capable than the commercially obtained device it replaces.

Chapter 5 shows how we used the new laser workstation to evaluate a range of software defences. We demonstrate its use to quantify the efficacy of defences and measure the cost of these defences in terms of performance penalties and code volume. The ability of the fault injector to automate data collection was invaluable. It greatly simplified testing of the output of a defensive code generator in the form of a new C-compiler, which forms the subject matter for Chapter 6.

The impact of a more realistic perception of vulnerabilities and the improved opportunities for defence deployment is considered in Chapter 7.

The conclusions drawn from this study and further work opportunities are presented in Chapter 8.

Finally, the appendices describe the significant components developed during this investigation. Most of the work presented in this section relates to engineering and development; however, the functional objectives were guided by the research requirements. These appendices demonstrate the capabilities of the tools and their modes of use. They are primarily of interest to anyone intending to build upon the results presented here. Appendix A describes the test harness that coordinates the microscope, laser, test sample and data collection. Appendix B covers the circuit boards developed to support the DUT and synchronise the laser pulses with the executing test programs. Appendix C covers the features of the new Defensive C-compiler, management of its source code, its output and how to use it or modify it.

# Chapter 2

# Background

# Contents

| 2.1 | Threats                                   |

|-----|-------------------------------------------|

|     | 2.1.1 Motivation                          |

|     | 2.1.2 Mitigation                          |

|     | 2.1.3 Relevance                           |

| 2.2 | Attacks                                   |

|     | 2.2.1 Logical Attacks                     |

|     | 2.2.2 Side-Channel Attacks                |

|     | 2.2.3 Physical Attacks                    |

| 2.3 | Errors                                    |

|     | 2.3.1 History of Fault Attacks Techniques |

|     | 2.3.2 Consequences of Faulty Execution 69 |

|     | 2.3.3 Mechanisms of Fault Injection       |

|     | 2.3.4 Lasers                              |

| 2.4 | Defence Techniques                        |

| 2.5 | Observations                              |

This chapter describes a broad spectrum of attacks that a  $\mu$ C is vulnerable to and the relative ease with which they can be performed. It highlights that the cornerstone of effective defences lies not in ever more ingenious cryptography but through reliable execution of relatively simple code. Humble operation of basic arithmetic and branching guards the most valuable assets within a  $\mu$ C. It leads to the question, what is required to make these operations trustworthy?

It has been a popular misconception that a bug-free program, implementing a carefully defined protocol, executing on a well-maintained computer would provide all that was necessary for reliability and security. The implicit assumption is that the computer will reliably do what it is told to do and, so long as the task defined has no logical weaknesses, the outcome will be entirely deterministic. The only risks worth considering were physical. There is the risk that the device, or its sub-components, may be stolen; the defence against this is akin to having a safe, making it very heavy and bolting it to the office floor. Similarly, there is the risk that it may be attacked insitu; the defence here for a safe is to reinforce it to make it resist attempts to break it open. For silicon chips, this meant adding physical barriers to prevent micro-probing.

This thesis is about what happens when one cannot fully trust a device to execute a program and what programmers can do to mitigate this threat. It is about the effects such errors have, the consequences of those effects, and programable defensive strategies to mitigate them.

Defences need to consider the other risks threatening an application and not unwittingly introduce new weaknesses. An awareness of the potential vulnerabilities, why they exist, how they are exploited, and the defences required in compensation is essential when considering new defences.

This chapter gives a broad overview of a  $\mu C$ 's vulnerabilities and the range of attacks available to an adversary. It also highlights that underpinning all the sophisticated cryptography is a fundamental reliance on trustable execution.

# 2.1 Threats

Why would a micro-controller be attacked?

The form factor of a  $\mu C$ s invariably leaves it exposed to the possibility of attack, and it must therefore be considered vulnerable. Vulnerability in its own right is not a problem so long as adequate defences are used to mitigate the consequences of an attack. The required strength of those defences depends on multiple factors, primarily the ease with which an attack can be performed and the potential benefits gainable

by a would-be attacker. So, to answer this question, we need to consider the services that a  $\mu C$  provides and the environment it operates in.

$\mu C$ s, in their many guises, provide a service for, and look after interests of, various parties. For example, a  $\mu C$  in a domestic appliance may be responsible for ensuring an optimal wash cycle in a washing machine or preventing an oven from burning your dinner. Here it acts as its owner's agent, it protects its owner's interests, and an owner-attacker will gain no benefit by compromising its operations. If they had access to it, a third party attacker would gain nothing either, unless their interest was in causing frustration or inconvenience. Even though an attack might be easy to perpetrate, it will be unlikely, and the consequences would be bearable if it were to happen.

Alternatively, a  $\mu C$  may manage a burglar alarm. In this scenario, its purpose is to protect its owner's interest, and that owner is interested in ensuring it is physically protected. A thief, however, would have a lot to gain if they could disable it or compromise its operations; such a device is an attractive target. It is in the owner's interest to keep it away from attackers, and it is reasonable to expect that the device will perform self-tests and summon assistance if it detects intrusion.

The third type of device provides one party with a service while protecting a third party's interests. A bank card, for example, provides a convenient way for an individual to access their money while simultaneously ensuring they cannot spend more than the bank allows. Such a  $\mu C$  is an exceptionally attractive target and requires robust defences because it is deployed outside of the control of its primary beneficiary.

These roles give us a concept of a target's low, medium and high attractiveness to an attacker.

• For devices with a **Low** attack attractiveness, attacks are unlikely, other than by those motivated by curiosity or possibly by competitors seeking to clone a device or discredit rivals. As a result, it is unlikely the device owner will pay any attention to securing access to the device or consider special options for disposal at the end of the product's life.

- Devices with a **Medium** level of attack attractiveness can expect a degree of physical protection to be provided by its beneficial owner. The threats here are logical ones that can be perpetrated remotely, for example, vulnerable passwords or remote software upgrades. For these devices, attacks requiring access to the device are unlikely but still require consideration, particularly to avoid the risk of tampering or substitution within the supply chain.

- Devices categorised as **High** on this attractiveness scale require extensive defences at all points in the product life-cycle. Manufacturers need to consider defences starting within their development environments and treat all participants in the product's implementation, construction, delivery, use, and disposal, as adversaries. These threats include insiders adding trap-door functions, assemblers building clones, tampering, substitution or theft during delivery and attacks by the end recipient.

#### 2.1.1 Motivation

In performing its tasks, a  $\mu C$  is expected to fulfill two primary functions.

- **Protect secrets**. Secret keys, for example, if disclosed, enable an attacker to impersonate the  $\mu C$  and to obtain services fraudulently. A secure device must keep the important data secret from everybody and only use these secrets on behalf of the legitimate owner.

- Control access to its services. Possession of a device is not enough to prove a legitimate right to its services. Devices need to authenticate the user, and this role is just as crucial as protecting secrets. Additionally, it may need to prove its identity to let the user know it is a genuine article.

The benefits of an attack on a  $\mu C$  are varied but can be distilled down to four categories [164].

• Theft of Service. Cloning PayTV access cards was one of the first widespread frauds perpetrated against smart cards. PayTV operators even hacked rival's

cards in order to starve them of revenue and ultimately bankrupt them [172]. Similar risks exist for transport operators and their "smart tickets", although, to date, such subterfuge has not been detected.

- Access to Information. Identification theft. The ability to clone passports or even create fraudulent ones would give criminals a lucrative illicit income. Similarly, unauthorised access to devices such as password vaults would enable hackers to access information and services they had no right to access.

- Cloning or Overbuilding. Counterfeit products, e.g. printer cartridges. As supply chains globalise, increasing efforts are being expended to ensure subcontractors in the manufacturing chain cannot create additional stock and illicitly sell it into the market. Increasingly these defences involve intelligent Integrated Circuits (ICs), and the security of these components is the keystone in the defences.

- Denial of Service. Or, anti-competitive practices. If devices can be disabled or broken, the device holder will lose access to a service. And, since glitch attacks typically leave no trail, users will attribute blame for a product's reliability issues to the device itself or its retailer. To prevent reputational damage and to avoid the cost of replacing broken devices, the devices need to be robust against such attacks.

## 2.1.2 Mitigation

A product owner should seek to eliminate, or at least reduce, the motivation for an attack. This is achieved by obstructing attacks and reducing the rewards gained from a successful attack. The three main mechanisms available to the product owner are physical, cryptographic and logical.

The role of physical defences is to ensure that an attacker cannot extract secrets from the device. This is sometimes called *Hardening* and aims to prevent an attacker from dismantling the chip, monitoring or injecting signals within it, and manipulating

the operating environment. These attacks mechanisms are described in Section 2.2.