# OPTIMIZATION OF SIMPLIFIED SHALLOW WATER OPENCL APPLICATION ON FPGA

A DISSERTATION SUBMITTED TO THE UNIVERSITY OF MANCHESTER FOR THE DEGREE OF MASTER OF SCIENCE IN THE FACULTY OF SCIENCE AND ENGINEERING

2019

By Ruiqi Ye 10292968 Supervisor: Graham Riley School of Computer Science

# Content

| Abstract                                                           | 9    |

|--------------------------------------------------------------------|------|

| Declaration                                                        | 10   |

| Copyright                                                          | 11   |

| Acknowledgement                                                    | 12   |

| Glossary                                                           | 13   |

| Chapter 1 Introduction                                             |      |

| 1.1. Project Aims                                                  | 19   |

| 1.2. Project Objectives                                            | 19   |

| Chapter 2 Background                                               | 21   |

| 2.1. FPGA Background                                               | 21   |

| 2.2. OpenCL Background                                             | 22   |

| 2.2.1. Platform Model                                              | 22   |

| 2.2.2. Execution Model                                             | 23   |

| 2.2.3. Kernel Programming Model                                    | 24   |

| 2.2.4. Memory Model                                                | 25   |

| 2.3. Other Programming Models                                      | 26   |

| 2.4. SDx Background                                                | 27   |

| 2.5. Stencil Computation Background                                |      |

| 2.5.1. Shallow Water Forecasting Model Background                  | 29   |

| 2.5.2. The Simplified Shallow Water Application Used in this Proje | ct29 |

| 2.6. Optimization Methods for OpenCL Application on Xilinx FPG.    | A31  |

| 2.6.1. Kernel Optimizations                                        | 31   |

| 2.6.2. Host Optimizations                                          | 35   |

| 2.6.3. SDx-related Optimizations                                   |      |

| 2.7. Literature Review                                             |      |

| 2.7.1. Papers Focused on Performance Modelling                     |      |

| 2.7.2. Papers Focused on Performance Optimization                  |      |

| 2.7.3. Paper Focused on Overhead Analysis                          | 45   |

| 2.8. Summary                                                       | 46   |

| Chapter 3 Research Methodology                                     | 47   |

| 3.1. Performance Estimation                                        | 47   |

| 3.2. Overhead Analysis                                             | 48   |

| 3.3. Overhead Minimization                                         | 48   |

| 3.4. The Principle of Applying Optimization Method                 | 49   |

| 3.5. A Method of Efficient FPGA Programming                        |      |

| 3.6.         | Execution Time Acquisition                                                      | 52  |

|--------------|---------------------------------------------------------------------------------|-----|

| 3.7.         | Summary                                                                         | 53  |

| Chapte       | r 4 Experiments with Basic Optimization Methods                                 | 54  |

| 4.1.         | Baseline                                                                        | 55  |

| 4.2.         | The Unreliable Emulator                                                         | 57  |

| 4.3.         | Iteration 1: -O3 Optimization                                                   | 57  |

| 4.4.         | Iteration 2: Loop Pipelining                                                    | 58  |

| 4.5.         | Iteration 3: Using Local Memory and Burst Memory Transfer                       | 59  |

| 4.6.         | Iteration 4: Loop Unrolling                                                     | 60  |

| 4.7.         | Summary                                                                         | 61  |

| Chapte       | r 5 Experiment with Advanced Optimization Methods                               | 62  |

| 5.1.         | Iteration 5: Array Partitioning                                                 | 62  |

| 5.2.         | Iteration 6: Data Vectorization                                                 | 63  |

| 5.3.         | Iteration 7: Overlapping Data Transfer with Kernel Computation                  | 64  |

| 5.4.         | Iteration 8: Restrict Keyword and Concurrent Execution of Kernels               | 66  |

| 5.5.         | Iteration 9: Dataflow and Function Inline                                       | 68  |

| 5.6.<br>Kern | <i>Iteration 10</i> : Merging Array Update Kernel with Periodic Continuation el | 69  |

| 5.7.         | Summary                                                                         | 71  |

| Chapte       | r 6 Experimental Data Analysis                                                  | 72  |

| 6.1.         | Latency and Loop Information Interpretation                                     | 73  |

| 6.2.         | The Scalability Model                                                           | 74  |

| 6.3.         | Why Emulator is unreliable                                                      | 75  |

| 6.4.         | Data from Experiments with Basic Optimizations                                  | 78  |

| 6.5.         | Data from Experiments with Advanced Optimizations                               | 86  |

| 6.5          | .1. Iteration 5, 6 and 7                                                        | 86  |

| 6.5          | .2. Iteration 8                                                                 | 90  |

| 6.5          | .3. Iteration 9                                                                 | 93  |

| 6.5          | .4. Iteration 10                                                                | 97  |

| 6.6.         | Comparison between Estimated Speedup and Achieved Speedup                       | 97  |

| 6.7.         | Data with Bigger Problem Size                                                   | 98  |

| 6.8.         | Performance Comparison among CPU, GPGPU and FPGA                                | 99  |

| 6.9.         | Summary                                                                         | 102 |

| Chapte       | er 7 Conclusion and Future work                                                 | 104 |

| 7.1.         | List of Contributions                                                           | 104 |

| 7.2.         | Future Work                                                                     | 105 |

| Bibliog      | raphy                                                                           | 107 |

Word Count: 21195 (Main body only)

# **List of Figures**

| Figure 2.1: FPGA Structure (Waidyasooriya et al., 2018)                     | 21    |

|-----------------------------------------------------------------------------|-------|

| Figure 2.2: OpenCL Platform Model (Waidyasooriya et al., 2018)              |       |

| Figure 2.3: OpenCL Execution Model (Waidyasooriya et al., 2018)             |       |

| Figure 2.4: OpenCL Kernel Programming Model (Waidyasooriya et al., 2018     |       |

| Figure 2.5: OpenCL Memory Model (Waidyasooriya et al., 2018)                | ·     |

| Figure 2.6: Host Code of Kernel Execution.                                  |       |

| Figure 2.7: Kernel Code of Kernel L100                                      |       |

| Figure 2.8: Kernel Code of Kernel L100 pc                                   |       |

| Figure 2.9: Execution of Function Calls L100_read(), L100_calc()            |       |

| L100_write() after Applying Dataflow Directive                              |       |

| Figure 3.1: Flow Chart of a Method of Efficient FPGA Programming            |       |

| Figure 4.1: Example Code Snippet of Kernel foobar with a Local Work Group   | Size  |

| of 128 * 64 * 8 (Gorlani, 2017)                                             |       |

| Figure 4.2: Kernel foobar being Compiled (Gorlani, 2017)                    |       |

| Figure 4.3: Baseline Host Code of the Initialization of Command Queue, Bu   |       |

| and Kernels, plus Data Copy                                                 |       |

| Figure 4.4: Baseline Host Code of Kernel Execution and the Copy-Back of     |       |

|                                                                             |       |

| Figure 4.5: Timing Function based on gettimeofday()                         |       |

| Figure 4.6: Kernel Code of Loops in Kernel L200 Being Manually Pipelined    |       |

| Figure 4.7: Kernel Code of Loops in Kernel L200_pc Being Manually Pipe      |       |

|                                                                             |       |

| Figure 4.8: Kernel Code of Local Memory and Burst Memory Transfer Being     |       |

| in Kernel L100                                                              |       |

| Figure 4.9: Kernel Code of Local Memory and Burst Memory Transfer Being     | Used  |

| in Kernel L100_pc                                                           | 59    |

| Figure 4.10: Kernel Code of the Inner Loop in Kernel L100 Being Compl       | etely |

| Unrolled                                                                    | 60    |

| Figure 4.11: Kernel Code of the Loops in Kernel L100_pc Being Compl         | etely |

| Unrolled                                                                    |       |

| Figure 5.1: Kernel Code of the Local Arrays in Kernel L100 Being Partitione | d.62  |

| Figure 5.2: Kernel Code of the Local Arrays in Kernel L100_pc Being Partiti | oned  |

|                                                                             | 63    |

| Figure 5.3: Kernel Code of the Local Arrays in Kernel L100 Being Vecto      | rized |

| Automatically                                                               |       |

| Figure 5.4: Kernel Code of the Local Arrays in Kernel L100_pc Being Vecto   | rized |

| Automatically                                                               |       |

| Figure 5.5: Host Code of Using enqueueMigrateMemObjects() to Overlap        | Data  |

| Transfer with Kernel Computation                                            | 65    |

| Figure 5.6: Kernel Code of Kernel L100 Being Optimized by Using F           | ewer  |

| async_work_group_copy()                                                     |       |

| Figure 5.7: Host Code of Conducting Concurrent Execution of Kernels by U    |       |

| One Out-of-Order Command Queue                                              |       |

| Figure 5.8: Host Code of Executing Kernels Concurrently by Using One Ou     |       |

| Order Command Queue                                                         |       |

| Figure 5.9: Host Code of Conducting Concurrent Execution of Kernels by U    | -     |

| Two In-Order Command Queue                                                  | 67    |

| Figure 5.10: Host Code of Executing Kernels Concurrently by Using Two In-Order  |

|---------------------------------------------------------------------------------|

| Command Queue                                                                   |

| Figure 5.11: Kernel Code of Kernel L100_cu Being Optimized by Using Keyword     |

| "restrict"                                                                      |

| Figure 5.12: Kernel Code of Packing async_work_group_copy() into "write_u_p"    |

| Function                                                                        |

| Figure 5.13: Kernel Code of Packing async_work_group_copy() into "read_u_p"     |

| Function                                                                        |

| Figure 5.14: Kernel Code of Packing Array Update Code into "Calculation"        |

| Function                                                                        |

| Figure 5.15: Kernel Code of Using Function Calls in Kernel L100_cu, as well as  |

| Function Calls Pipelining and Function Inline69                                 |

| Figure 5.16: Host code that shows Periodic Continuation Kernels are merged with |

| Array Update Kernels70                                                          |

| Figure 5.17: Kernel Code of Periodic Continuation Operation merged into Kernel  |

| L100 cu70                                                                       |

### List of Tables

| Table 4.1: Summary of Experiments Described in Chapter 4                       | 61                   |

|--------------------------------------------------------------------------------|----------------------|

| Table 5.1: Summary of the Experiments Described in Chapter 5                   | 71                   |

| Table 6.1: Latency Information of Kernel L100 of the Baseline Code             | 73                   |

| Table 6.2: Loop Information of Kernel L100 of the Baseline Code                | 73                   |

| Table 6.3: Hardware Resource Utilization of the Baseline Code                  | 74                   |

| Table 6.4: Partial Loop Information of Iteration 2                             | 82                   |

| Table 6.5: Partial Loop Information of Iteration 3                             | 82                   |

| Table 6.6: Speedup of Main Loop and the Throughput of <i>Iteration 3 and 4</i> | 85                   |

| Table 6.7: Partial Loop Information of Iteration 5*                            | 87                   |

| Table 6.8: Average Latency Reported for each Kernel in Iteration 7 and 8       | 91                   |

| Table 6.9: Average Latency and Start Interval of Kernel L100_cu in Iteration   | <b>9</b> 94 <b>9</b> |

| Table 6.10: Start Interval and Average Latency of Kernel L100 and L100_        | cu of                |

| Baseline and <i>Iteration 1, 2, 3, 4, 5, 6, 7, 8 and 9</i>                     | 94                   |

| Table 6.11: Specifications of Intel i7-6700 CPU and Nvidia GT730 GPGPU.        | 100                  |

| Table 6.12: The Speedup of Main Loop and the Throughput of Baseline            | e and                |

| Iteration 1, 2, 3, 4, 5, 6, 7, 8, 9 and 10                                     | 102                  |

|                                                                                |                      |

# **List of Diagrams**

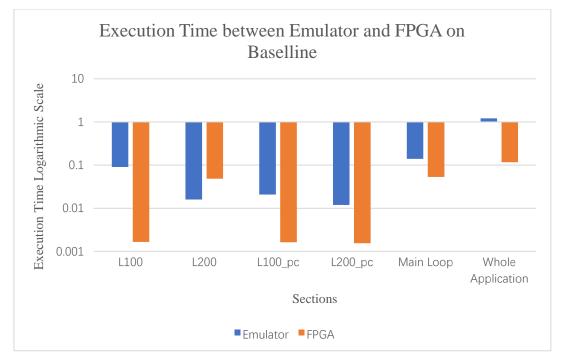

| Diagram 6.1: Execution Time of Different Section of the Baseline Code between<br>Emulator and FPGA                      |

|-------------------------------------------------------------------------------------------------------------------------|

| Emulator and FPGA                                                                                                       |

| Diagram 6.3: The Execution Time of each Kernel of the Baseline Code on FPGA                                             |

| Diagram 6.4: Execution Time of Different Section between the Baseline Code and <i>Iteration 3</i> on Emulator           |

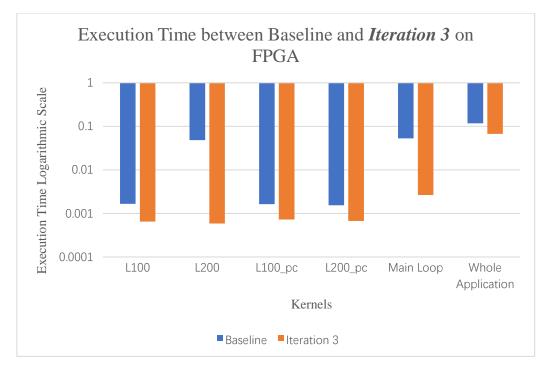

| Diagram 6.5: Execution Time of Different Section between the Baseline Code and <i>Iteration 3</i> on FPGA               |

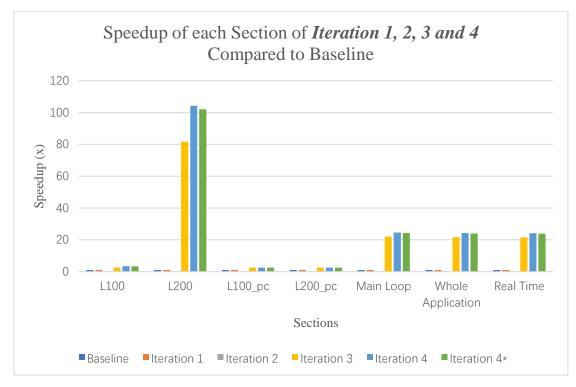

| Diagram 6.6: Speedup of each Section of <i>Iteration 1, 2, 3 and 4</i> Compared to Baseline                             |

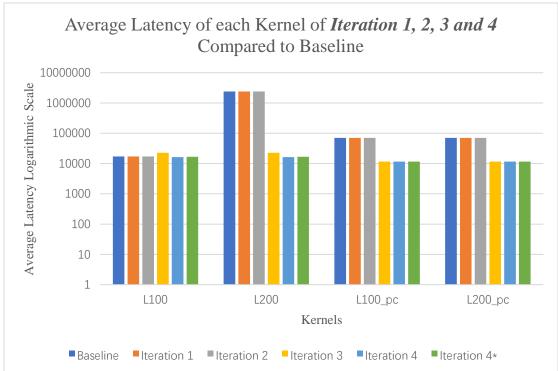

| Diagram 6.7: Average Latency of each Kernel of <i>Iteration 1, 2, 3 and 4</i> Compared to Baseline                      |

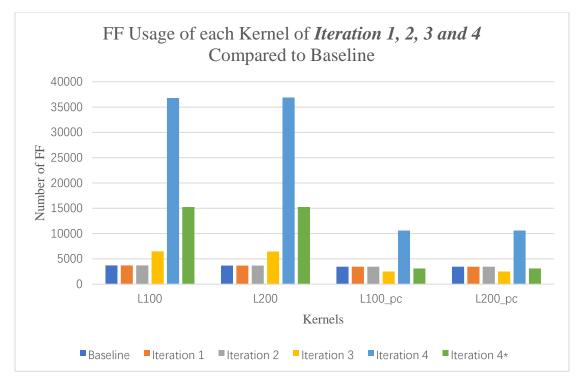

| Diagram 6.8: FF Usage of each Kernel of <i>Iteration 1, 2, 3 and 4</i> Compared to Baseline                             |

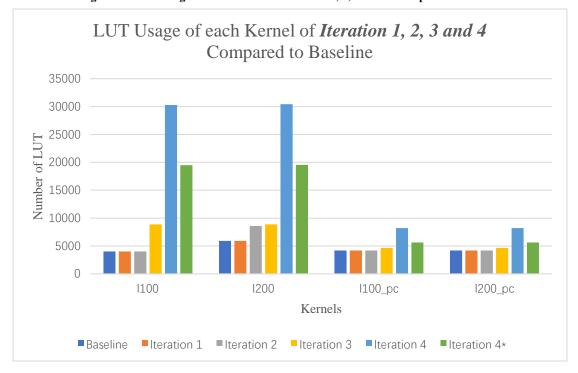

| Diagram 6.9: LUT Usage of each Kernel of <i>Iteration 1, 2, 3 and 4</i> Compared to Baseline                            |

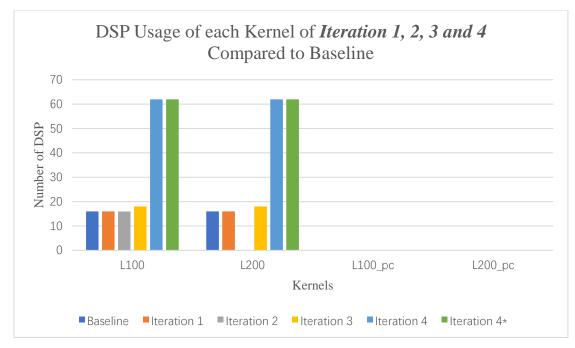

| Diagram 6.10: DSP Usage of each Kernel of <i>Iteration 1, 2, 3 and 4</i> Compared to Baseline                           |

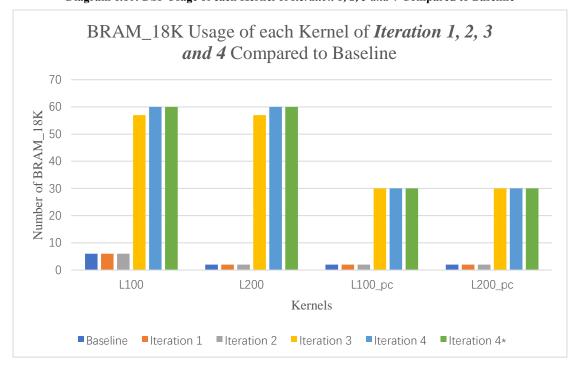

| Diagram 6.11: BRAM_18K Usage of each Kernel of <i>Iteration 1, 2, 3 and 4</i><br>Compared to Baseline                   |

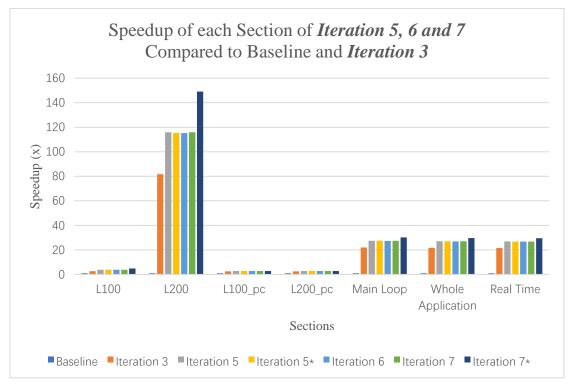

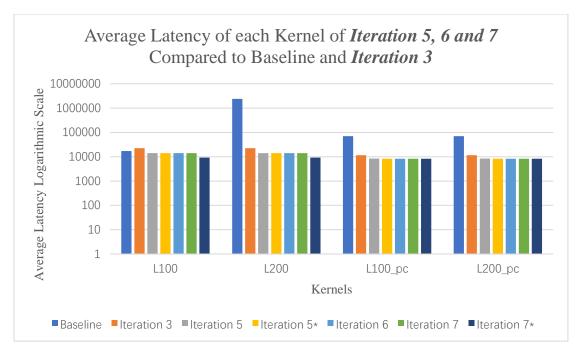

| Diagram 6.12: Speedup of each Section of <i>Iteration 5, 6 and 7</i> Compared to Baseline and <i>Iteration 3</i>        |

| Diagram 6.13: Average Latency of each Kernel of <i>Iteration 5, 6 and 7</i> Compared to Baseline and <i>Iteration 3</i> |

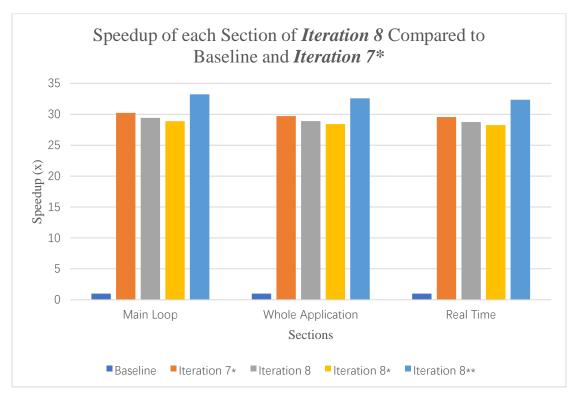

| Diagram 6.14: Speedup of each Section of <i>Iteration 8</i> Compared to Baseline and <i>Iteration 7</i> *               |

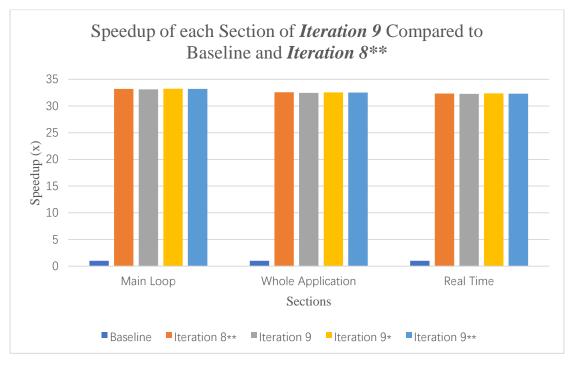

| Diagram 6.15: Speedup of each Section of <i>Iteration 9</i> Compared to Baseline and <i>Iteration 8**</i>               |

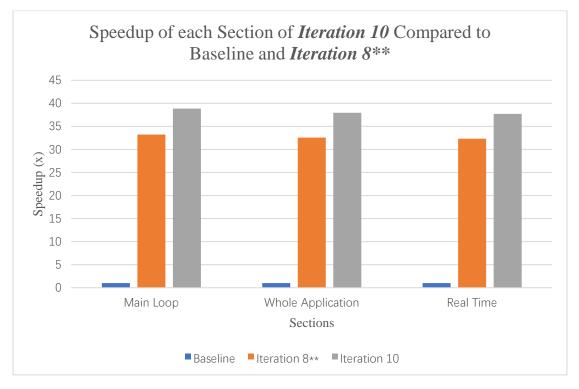

| Diagram 6.16: Speedup of each Section of <i>Iteration 10</i> Compared to Baseline and <i>Iteration 8**</i>              |

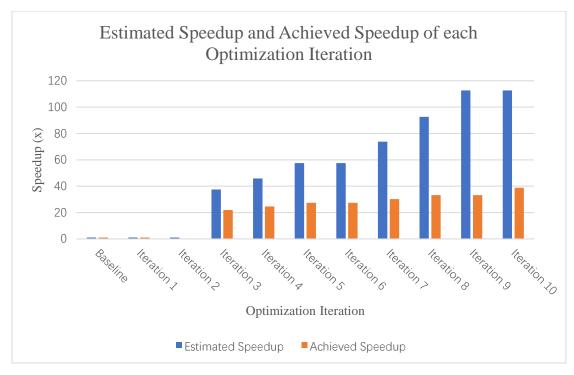

| Diagram 6.17: Estimated Speedup and Achieved Speedup of each Optimization<br>Iteration                                  |

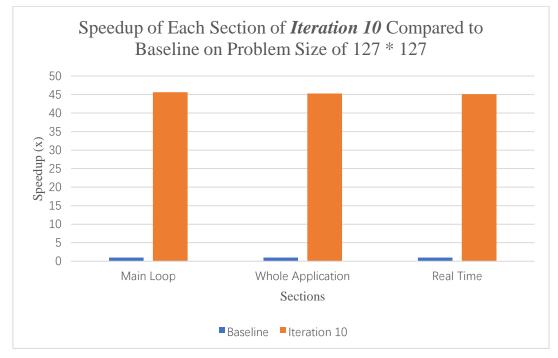

| Diagram 6.18: Speedup of Each Section of <i>Iteration 10</i> Compared to Baseline on<br>Problem Size 127 * 127          |

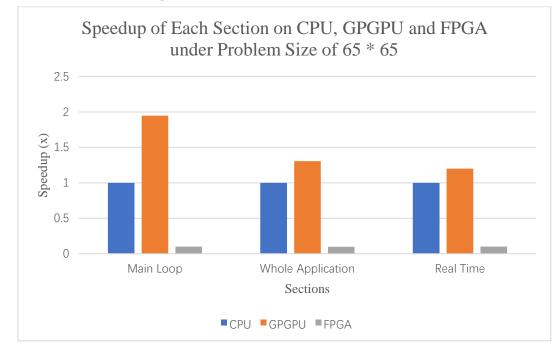

| Diagram 6.19: Speedup of Each Section on CPU, GPGPU and FPGA under<br>Problem Size 65 * 65                              |

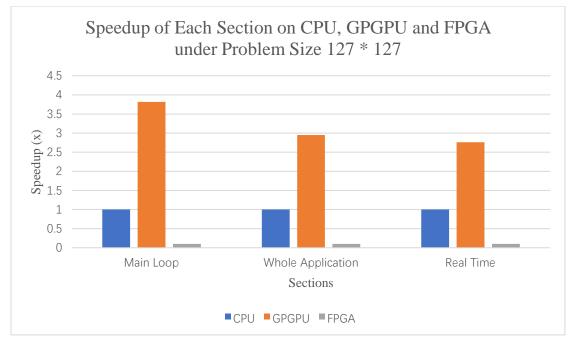

| Diagram 6.20: Speedup of Each Section on CPU, GPGPU and FPGA under<br>Problem Size 127 * 127                            |

### Abstract

High-performance computing has attracted more and more attention due the increasing computation power needs in areas like machine learning, big data processing and analysis. Heterogenous systems that use GPGPUs as accelerators are common candidates for high-performance computing these days. However, the power consumption of GPGPU has become a significant problem when it comes to scalability, for example, to build a supercomputer that can perform exascale computing. Therefore, FPGAs, which have a better power efficiency and flexible hardware architecture, have become the new candidate of the accelerator of heterogenous systems.

A simplified shallow water application developed using OpenCL is implemented and optimized on a Xilinx FPGA in this project. A series of experiments that consist of overhead analysis and overhead minimization are conducted. An overhead analysis that divides overheads into five different categories is applied to the baseline version of the code first. Then a series of optimization methods including loop pipelining, loop unrolling, burst memory transfer and using on-chip BRAM as cache are applied to the baseline, based on the result of overhead analysis. A principle which describes how to apply the optimization are iterative processes, they only stop after certain requirements are met. Furthermore, an experiment that aims to prove the Xilinx emulator is unreliable in terms of execution time prediction and performance improvement indication is also conducted. Two methods of efficient FPGA programming and correct execution time acquisition during experiments are proposed as well.

A method of interpreting the latency and loop information provided in the Xilinx HLS tool report is explained. A simple scalability model is also proposed for experimental data analysis. Result shows a maximum speedup of around 45x is achieved on the main computation loop of the simplified shallow water application, compared to the baseline. However, the highly optimized, simplified shallow water application that runs on a midrange FPGA is still significantly outperformed by a not highly optimized simplified shallow water application are also provided.

## Declaration

No portion of the work referred to in this dissertation has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

### Copyright

1. The author of this dissertation (including any appendices and/or schedules to this dissertation) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

2. Copies of this dissertation, either in full or in extracts and whether in hard or electronic copy, may be made only in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has entered into. This page must form part of any such copies made.

3. The ownership of certain Copyright, patents, designs, trademarks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the dissertation, for example graphs and tables ("Reproductions"), which may be described in this dissertation, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

4. Further information on the conditions under which disclosure, publication and commercialisation of this dissertation, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http://documents.manchester.ac.uk/display.aspx?DocID=24420), in any relevant Dissertation restriction declarations deposited in the University Library, and The University Library's regulations.

### Acknowledgement

I would like to express my gratitude to my supervisor Mr. Graham Riley for his invaluable support, motivation, guidance, and feedback throughout this project. His constant motivation and enthusiasm encouraged me to produce my best work.

I would also like to thank my family and friend for the constant support without which this work would not have been possible.

### Glossary

Accelerator It is a hardware device that accelerate the computation. Common accelerators including GPGPU, FPGA and Intel Xeon Phi. Accelerator is part of the heterogenous computing system.

**API** Application Programming Interface. It is "a set of subroutine definitions, communication protocols, and tools for building software. In general terms, it is a set of clearly defined methods of communication among various components." (Application programming interface, 2019)

BRAM Block RAM. It is a type of on-chip memory used on FPGA.

**Core** It is a hardware component that can execute instructions while load and store data between itself and memory.

**CPU** Central Processing Unit. It is a hardware that can perform arithmetic, logic, control and I/O operation.

**CU** Compute Unit. It refers to a collection of processing elements according to the OpenCL platform model. A work group is executed on one compute unit.

**Data Parallelism** It refers to a type of parallelism that allows different cores access and process different data simultaneously.

**DSP** Digital Signal Processor. It is a type of hardware that specialized in digital signal processing. In FPGA, DSP is responsible for the execution of floating-point operation. Parallel computing can also be conducted using DSP by utilizing the SIMD instructions.

**FF** Flip-Flop. It is a circuit that have two states and can store state information. Its state can be changed by applying signals on to it. Flip-Flops usually have at least one input and one output. Flip-Flop is one of the most important components of FPGA.

**FPGA** Field Programmable Gate Array. It is a programmable hardware which consists of processing system and programmable logic. Different kind of IP block will be generated within the programmable logic, based on the algorithm.

**Global Work Item Size** It refers to the number of work items of all work groups. In short, it is the total number of work items that executes one kernel.

**GPGPU** General Purpose Graphical Processing Unit. It is an accelerator which is originally designed for processing and displaying 2D and 3D computer graphics. It is called "general purpose" because it can be utilized to process general data efficiently thanks to its SIMD architecture.

**HDL** Hardware Description Language. It is a programming model that precisely describes the structure and behaviour of the circuits.

**Heterogeneous Computing** A computing method that use different types of hardware. For example, CPU plus accelerators.

**Homogeneous Computing** A counterpart of heterogenous computing, which refers to computation that use only one type of hardware. For example, CPU.

**HLS** High Level Synthesis. It is a process that transform the high-level programming language like Java and C++ to hardware description language.

**HPC** High-Performance Computing. It is a practice that focus on solving the computation-intensive or data-intensive tasks efficiently.

**IC** Integrated Circuit. It is a collection of circuits that integrated on a small piece of silicon.

**IDE** Integrated Development Environment. It is a type of software which aims to facilitate the process of software development for developers. In general, IDE includes source code editor, debugger, compiler and building tools.

**II** Initial Interval. It refers to the time needed between the execution of the first iteration and the second iteration.

Iteration Latency It refers to the time needed for one iteration to complete.

**Kernel** It refers to a function executed on one compute unit according to the OpenCL execution model.

**Local Work Item Size** It refers to the number of work items within one work group. It also refers to the number of dimensions as well as the magnitude of each dimension of one work group.

LUT Look Up Table. It is one of the most important components of FPGA. Look up table is a truth table that store the results of Boolean operations, based on the inputs. It makes the execution of Boolean operation more efficient because the result can be obtained simply by checking the loop up table.

Memory Latency It refers to the time needed for accessing external, off-chip memory.

**Multi-core** It is a type of hardware that consists of multiple cores, for example, multi-core CPU.

**NDRange** It is an index space that describes the total number of work items which execute the kernel. The NDRange can either be 1-Dimensional, 2-Dimensional or 3-Dimensional.

**OpenCL** Open Computing Language. It is a programming model which is widely used in heterogenous computing. It can produce code that can be executed on CPU, GPGPU and FPGA.

**PCIe** Peripheral Component Interconnect express. It is a standard for high-speed serial computer bus interface. Hardware like accelerators and hard drives can be connected using the PCIe on motherboard.

**PE** Processing Element. A counterpart of core. According to the OpenCL platform model, multiple processing elements are included in one compute unit

**Start Interval** It refers to the time between the invocation of the first function call and the second function call.

Trip Count It refers to the size of iteration space.

**VHDL** Very High-Speed Integrated Circuit Hardware Description Language. It is one of the major HDL.

Vivado It is an HLS tool provided by Xilinx, which is integrated within SDx.

**Work Group** It refers to a collection of work items that are executed on one compute unit, in the OpenCL programming model.

Work Item It is equivalent to thread according to the OpenCL programming model.

**SDAccel** Software-Defined Accelerator. It is an IDE that targets the application development for Xilinx accelerators.

**SDSoC** Software-Defined System on Chip. It is an Eclipse-based IDE that targets the embedded C/C++/OpenCL application development for heterogenous Zynq SoC and MPSoC (Multi-Processor SoC) system.

**SDx** It is an Eclipse-based IDE provided by Xilinx.

**SIMD** Single Instruction, Multiple Data. An architecture that allows different cores access different data but process them in the same way simultaneously. In short, different data will be processed using the same instruction on different core simultaneously. SIMD is common in GPGPU.

**Task Parallelism** It refers to a type of parallelism that allows different cores execute different tasks simultaneously.

### **Chapter 1 Introduction**

As we have entered the era of big data, high-performance computing has become increasingly important, since nowadays computation-intensive and data-intensive applications like weather forecasting must be computed within a limited amount of time. One popular way of achieving high-performance is "going parallel", meaning using processors with multiple cores instead of the one with single core, because it is more and more difficult to achieve higher performance on a single core by simply increasing the clock frequency. However, even if the performance is achieved, the power consumption will be intolerable.

It has been found that homogenous multicore architectures, for example multicore CPU, are not the best candidate for high-performance computing. Multicore CPU is suitable for executing control-dominant problems, but it does not perform well on problems that need only little control flow and synchronization with other threads or tasks, compared to GPGPU. Therefore, heterogeneous architecture, for example CPU-GPGPU, becomes popular these days, because it can utilize the advantages of different homogeneous architectures while hiding most of their disadvantages.

In a heterogeneous system, devices like GPGPU, FPGA and Intel Xeon Phi are called accelerators. In this project, FPGA is chosen as the accelerator instead of GPGPU. This is because the hardware architecture of FPGA is more flexible, and the energy efficiency of FPGA is better compared to CPU and GPGPU, this is also mentioned in the work of (Georgopoulos et al., 2019). In addition, recent developments have made FPGAs easier to program.

This project aims to implement and optimize a simplified shallow water application developed using OpenCL, on an ARM CPU-FPGA heterogenous system. A series of optimization methods selected from literatures are applied to the code one after another following a certain principle, which will be discussed later. Performance estimation as well as overhead analysis are be conducted. Other contributions of this project including a method of efficient FPGA programming, a way of measuring correct and accurate execution time of the kernels executed on the FPGA, a detailed explanation regarding

how to interpret the latency and loop information given in the system estimate report and HLS report produced when building a FPGA solution, and a model to evaluate the scalability of each optimization method.

This dissertation is organized as follows. Chapter 2 provides some backgrounds on FPGA, OpenCL (the programming language used), SDx (the Xilinx tool with the SDSoC environment supporting FPGA development), stencil computation (as used in the simplified shallow water application) and optimization methods for FPGA applications developed using OpenCL. The literature review is also included. The research methodology is presented in Chapter 3, where a description regarding how the project is implemented is provided. Chapter 4 presents the description of a series of experiments with basic optimization methods. Chapter 5 describes a series of experiments with more advanced optimization methods. Experimental data are analysed in Chapter 6. Finally, Chapter 7 concludes the whole dissertation and identifies some future works.

#### 1.1. Project Aims

The aims of this project are to implement a simplified but high-performance shallow water weather & climate forecasting application using OpenCL on an ARM CPU-FPGA heterogeneous system, while trying to program the FPGA efficiently from a high-level programmer's perspective.

#### **1.2. Project Objectives**

In order to achieve these aims, the following objectives must be accomplished, one after another.

- Understand FPGA programming using OpenCL and SDSoC of the Xilinx FPGA available for this project.

- Getting familiar with the HLS tools which makes FPGA programming easier.

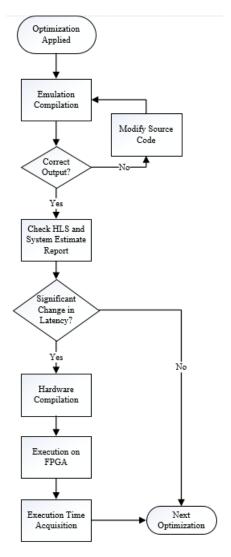

- Develop a methodology which includes performance estimation, overhead analysis, overhead minimization, execution time acquisition, a principle for applying optimization methods and a method for efficient FPGA programming.

- Implement a shallow water weather & climate forecasting application using

OpenCL and execute it on a single FPGA, then apply the methods to obtain high performance.

### **Chapter 2 Background**

This chapter introduces the essential background knowledge that is necessary for this project. Section 2.1 provides a general description of FPGA. Section 2.2 introduces the OpenCL programming language, including its platform model, execution model, kernel programming model and memory model. In Section 2.3, the IDE used in this project, called SDx, is introduced. Section 2.4 describes the principle of stencil computation, along with the basic idea of the shallow water weather & climate forecasting model, and the simplified shallow water application used in this project. Section 2.5 summarizes a series of optimization method for FPGA application developed in OpenCL. Section 2.6 provides a literature review of the papers that are key to this project.

#### 2.1. FPGA Background

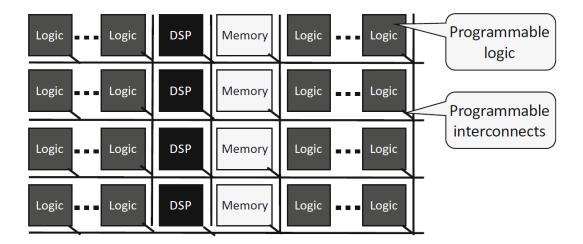

#### Figure 2.1: FPGA Structure (Waidyasooriya et al., 2018)

FPGA is a type of hardware that is programmable even after it is manufactured. "It contains programmable logic gates and programmable interconnects, as well as configurable memory modules and DSPs" (Waidyasooriya et al., 2018). The programmable logic, interconnects, memory modules and DSPs can be utilized to create any arbitrary circuits. This enables FPGA to "become" different processors and accelerators, for example GPGPU. A processing system is also included in the FPGA. Figure 2.1 shows the structure of FPGA.

#### 2.2. OpenCL Background

"OpenCL is a framework for writing programs that execute across heterogeneous platforms consisting of CPUs, GPGPUs, DSPs, FPGAs and other processors or hardware accelerators." (OpenCL, 2019). OpenCL consists four models, namely the platform model, execution model, kernel programming model and memory model. Section 2.2.1 provide a brief description of the platform model while Section 2.2.2 explains the execution model. Section 2.2.3 describes the kernel programming model briefly and Section 2.2.4 demonstrates the memory model.

#### 2.2.1. Platform Model

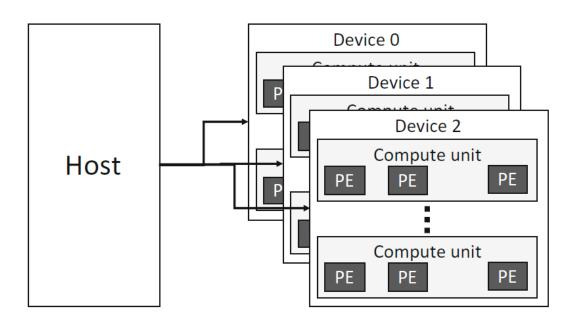

Figure 2.2: OpenCL Platform Model (Waidyasooriya et al., 2018)

As can be seen from Figure 2.2, in a CPU-FPGA heterogeneous system, CPU is the host while FPGAs are the devices. There are multiple compute unit within the devices and there are multiple processing elements (PE) within one single compute unit. PEs and CPU cores are counterparts. Multiple devices can be controlled by one host.

#### **2.2.2. Execution Model**

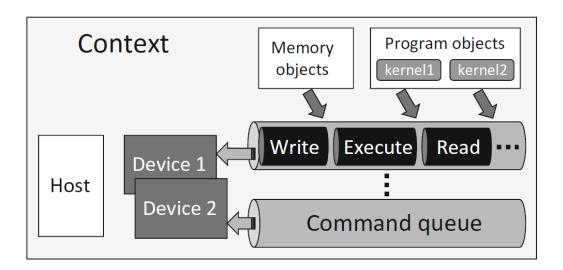

Figure 2.3: OpenCL Execution Model (Waidyasooriya et al., 2018)

Figure 2.3 explains the OpenCL execution model. A context is created for one or multiple devices. Each device can have one or multiple command queues. Command queues are used for communications between host and devices, commands will be issued by host and passed to devices through command queue. There are two types of objects that can be put into the command queue, memory object and program object. Memory objects are the objects that related to the read and write of the memory, while program objects are kernels which needs to be executed. Command queue can be either in-order or out-of-order. Each kernel can be executed by either one or multiple compute units. If the single work item kernel is used, then there is only one work group with one work item in one compute unit. If NDRange kernel is used, then all the following situations are possible depends on the global work item size and the local work item size.

- One work group with multiple work items in one compute unit.

- Multiple work groups each with multiple work items in one compute unit.

- Multiple work groups each with one work item in one compute unit.

#### 2.2.3. Kernel Programming Model

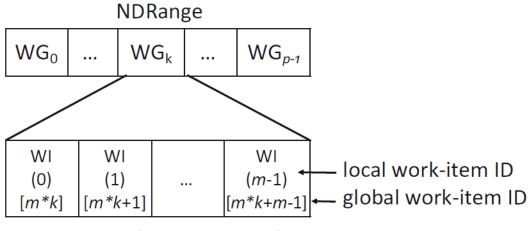

WG : work group WI : work item

#### Figure 2.4: OpenCL Kernel Programming Model (Waidyasooriya et al., 2018)

Figure 2.4 demonstrates the OpenCL kernel programming model. Functions executed on device are called kernel. Another new concept is called NDRange kernel. As can be seen from Figure 2.4, a NDRange kernel can be made up of multiple work group while a work group can consist multiple work item. Work groups and work items in a single NDRange kernel can be divided into N dimension, where the maximum number of N is three. "The size of NDRange and work groups can be specified by host program." (Waidyasooriya et al., 2018). The work items are tagged with both local ID and global ID, the local ID of work items in different work group might be the same but the global ID is unique for different work items. "The local ID is to identify the work items within a work group while global ID is to identify the work items within the NDRange" (Waidyasooriya et al., 2018).

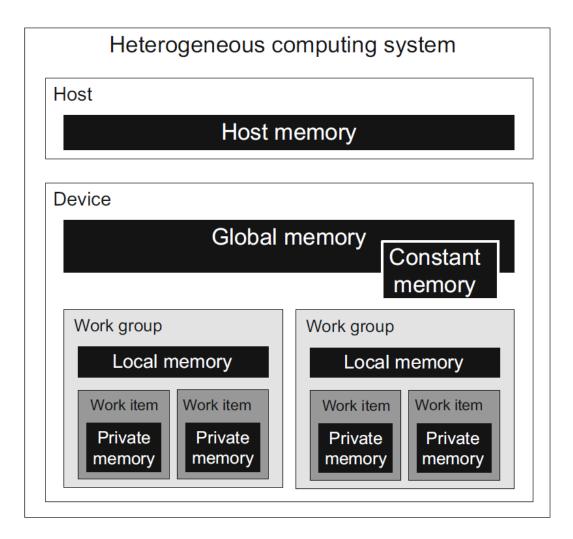

#### 2.2.4. Memory Model

Figure 2.5: OpenCL Memory Model (Waidyasooriya et al., 2018)

The OpenCL memory model is described in Figure 2.5. Host and devices have separate memory, called host memory and device memory respectively. Devices cannot access host memory, so the data in host memory must be transferred to the global memory before it can be processed by device. Global memory can be accessed by both host and device. Constant memory is a read-only memory. Each work group has its own local memory and cannot be accessed by other work groups, but it can be accessed by all the work items within the same work group. Each work item also has its own private memory, which cannot be accessed by other work items. On the FPGA board used in this project, both host memory and global memory refer to the same external and off-chip DDR memory, while local and private memory refer to the on-chip memory.

#### **2.3. Other Programming Models**

- OmpSs. OmpSs is a directive-based programming model developed by the Barcelona Supercomputing Centre which aims to extend OpenMP by adding new directives to support asynchronous parallelism and heterogenous computing. "It can also be understood as new directives extending other accelerator-based APIs like CUDA or OpenCL.". ("The OmpSs Programming Model | Programming Models @ BSC," n.d.) Asynchronous parallelism is supported in OmpSs by utilizing data dependencies between different tasks of the program. While heterogenous computing is supported by using a newly-introduced construct called the target construct. Architectures supported by OmpSs including Intel 32-bit and 64-bit platforms, IBM Power8 platforms and ARM 32-bit and 64-bit platforms.

- Maxeler high-performance dataflow computing system. Maxeler technology is a company that focus on the domain of high-performance computing. Maxeler highperformance dataflow computing system is one of the software they developed, which consist of MaxIDE, MaxCompiler, MaxOS and MaxGenFD. MaxIDE is an Eclipsed-based IDE, which means the programs execute on the Maxeler system can be developed in Java. The MaxCompiler splits an application into three parts, namely kernel, manager configuration and CPU application, to allow the application utilize the dataflow engine configuration. Kernels implement the computational component of the application. Manager configuration connects kernels to CPU, RAM, other kernels and dataflow engines. CPU application interacts with the dataflow engine to read and write data to kernels and RAM. "MaxelerOS provides the data choreography needed to balance resources, maximize utilization, minimize overheads, and manage the application acceleration process at runtime.". ("MaxelerOS | Maxeler Technologies," n.d.) "Maxeler MaxGen systems are domain-specific compilers that enable programmers to easily harness the full power of Maxeler solutions without needing a detailed understanding of the underlying hardware.". ("MaxGenFD | Maxeler Technologies," n.d.)

- Vivado HLS. Vivado HLS "accelerates IP creation by enabling C, C++ and System C specifications to be directly targeted into Xilinx programmable devices without the need to manually create RTL" (Vivado High-Level Synthesis, 2019)

VHDL. "VHDL is an HDL used in electronic design automation to describe digital and mixed-signal systems such as FPGA and IC. VHDL can also be used as a general-purpose parallel programming language." (VHDL, 2019)

#### 2.4. SDx Background

SDx is an IDE provided by Xilinx for SDSoC and SDAccel development. SDx includes HLS tools like Vivado and is made for Zynq<sup>®</sup> UltraScale+<sup>™</sup> available for this project. SDx has significantly eased the burden of software engineers for programming FPGA. Because Vivado can translate high-level language like C and Java to HDL, a process which is known as high level synthesis. Then the bitstream which builds the hardware architecture of FPGA can be generated by the compiler. The existence of Vivado enables software engineers to program FPGA without using HDL like Verilog, and learning lots of hardware knowledge. Emulators are also provided in SDx to emulate application in a hardware or software environment, in order to verify the functional correctness. It also provides reports regarding performance estimate and hardware resource utilization.

Two reports are provided by SDx, namely the system estimate report and the HLS report. System estimate report provides the estimated clock frequency for execution, hardware resource utilization and latency information of each kernel. It should be noted that the estimated clock frequency doesn't necessarily equal to the clock frequency set in the SDx project setting page. Hardware resource utilization contains information of the usage of FF, LUT, DSP and BRAM\_18K of each kernel. Latency information includes the start interval, best case latency, worst case latency and average case latency of each kernel. Start interval means "the amount of clock cycles that has to pass between invocations of a compute unit for a given kernel." While the best, average and worst case latency refer to "how much clock cycles it takes the compute unit to generate the results of one NDRange data tile for the kernel" ("SDAccel Environment Profiling and Optimization Guide," 2019). The best, worst and average case latency will be the same if there are no dependencies between loop iterations.

One HLS report will be generated for each kernel. The HLS report not only provide the hardware resource utilization and the latency information for the given kernel, it also

provides an analysis of the loops within the kernel. The following information are given in the analysis,

- Latency, which represent the total number of clock cycle that is needed for the whole iteration to complete.

- Iteration latency, which means the clock cycle needed for a single iteration to complete.

- Trip count, which describes the size of the iteration space.

- Initial interval (II), which explains the number of clock cycles needed for a loop iteration to start executing, after the previous iteration starts. It is worth noting that both achieved II and target II are provided here. The target II will also be 1, which is the optimum II.

- The "pipelined" indicates whether the loop is pipelined or not.

#### **2.5. Stencil Computation Background**

Stencil computation is widely used in domains like computational fluid dynamics, electromagnetic simulation based on the finite-difference time-domain methods, and iterative solvers of linear equation systems (Sano et al., 2014). Stencil computation means update the value of a certain point on a grid, based on the value of its neighbours. Stencil itself is an area consists of multiple grid point.

There are different methods to compute a stencil, for example Jacobi iteration and Gauss Seidel iteration. Jacobi iteration only needs the values of the grid point from the previous iteration to calculate the new one, which exposes more parallelism by eliminating data dependency. Unlike Jacobi iteration, Gauss Seidel iteration needs both values from the previous and current iteration of the grid point for the computation, which makes it more difficult to be parallelized.

Both Jacobi iteration and Gauss Seidel iteration are so-called "iteration to converge" computation, meaning the result will converge eventually after multiple iterations, and only one grid array is needed for computation. However, there are other kinds of stencil computation which needs multiple grid arrays. For example, "time-stepping" computation like shallow water equation.

Section 2.5.1 provides a description of the common shallow water weather & climate forecasting model, while Section 2.5.2 describes the simplified shallow water application used in this project in details, with the help of the code snippet.

#### 2.5.1. Shallow Water Forecasting Model Background

"The shallow water equations are a set of hyperbolic partial differential equations (or parabolic if viscous shear is considered) that describe the flow below a pressure surface in a fluid (sometimes, but not necessarily, a free surface)." (Shallow water equations, 2019). Shallow water algorithm is a "time-stepping" stencil computation which requires multiple grid arrays. The update of the value at each grid point relies on the values of the previous updated grid array. After all the grid arrays are updated, the first grid array will be updated again, and so on. Shallow water weather & climate forecasting model is an example of sophisticated weather and climate prediction model.

#### 2.5.2. The Simplified Shallow Water Application Used in this Project

```

computation_start = lr_tim();

for (ncycle=1;ncycle<=ITMAX;ncycle++)</pre>

L100 start = lr tim();

kernel_l100 (cl::EnqueueArgs(q, cl::NDRange(1,1,1), cl::NDRange(1,1,1)), buffer_u, buffer_p, buffer_cu, buffer_h);

q.finish();

L100_end = lr_tim();

time_spent_l100 = time_spent_l100 + (L100_end - L100_start);

L100_pc_start = lr_tim();

kernel_1100_pc (cl::EnqueueArgs(q, cl::NDRange(1,1,1), cl::NDRange(1,1,1)),buffer_cu, buffer_h);

q.finish();

L100_pc_end = lr_tim();

time_spent_l100_pc = time_spent_l100_pc + (L100_pc_end - L100_pc_start);

L200_start = lr_tim();

kernel_L200 (cl::EnqueueArgs(q, cl::NDRange(1,1,1), cl::NDRange(1,1,1)),buffer_u, buffer_p, buffer_cu, buffer_h);

q.finish();

L200_end = lr_tim();

time_spent_l200 = time_spent_l200 + (L200_end - L200 start);

L200_pc_start = lr_tim();

kernel_l200_pc (cl::EnqueueArgs(q, cl::NDRange(1,1,1), cl::NDRange(1,1,1)),buffer_u, buffer_p);

q.finish();

Quintsh(),

L200_pc_end = lr_tim();

time_spent_l200_pc = time_spent_l200_pc + (L200_pc_end - L200_pc_start);

time = time + dt;

a.finish():

q.linish(),

computation_end = lr_tim();

time_spent_computation = time_spent_computation + (computation_end - computation_start);

q.enqueueReadBuffer(buffer_u, CL_TRUE, 0, vector_size_bytes, source_u.data());

q.enqueueReadBuffer(buffer_p, CL_TRUE, 0, vector_size_bytes, source_p.data());

Full_APP_end = lr_tim();

time_spent_Full_app = time_spent_Full_app + (Full_APP_end - Full_APP_start);

Figure 2.6: Host Code of Kernel Execution

```

Figure 2.7: Kernel Code of Kernel L100

```

attribute ((reqd work group size(1, 1, 1)))

kernel void l100 pc( global float *cu, __global float *h)

{

int i,j;

for (j=0;j<N;j++)

{

cu[(0)*M_{LEN} + (j)] = cu[(M)*M_{LEN} + (j)];

h[(M)*M \ \overline{LEN} + (j)] = h[(0)*M \ L\overline{EN} + (j)];

}

for (i=0;i<M;i++)</pre>

{

cu[(i + 1)*M LEN + (N)] = cu[(i + 1)*M LEN + (0)];

h[(i)*M LEN + (N)] = h[(i)*M LEN + (0)];

}

cu[(0)*M LEN + (N)] = cu[(M)*M LEN + (0)];

h[(M)*M LEN + (N)] = h[(0)*M LEN + (0)];

}

```

#### Figure 2.8: Kernel Code of Kernel L100\_pc

The basic idea behind the simplified shallow water application is quite straight-forward. Figure 2.6 demonstrates how it is implemented. The elements of array cu and array h will first be updated in kernel L100, based on the elements of array u and array p. The periodic continuation operation of array cu and array h will then be conducted in kernel L100\_pc. After that, the elements of array u and array p will be updated based on the elements of array cu and array p will be conducted in kernel L200\_pc. After that, the elements of array u and array p will be conducted in kernel L200\_pc. After all this, the elements of array cu and array h will be updated again. This process will keep iterating until the value of the elements in array u and array p is converged. The update of array cu and array h, as well as the update of array u and array p, can be done in parallel. This is because Jacobi iteration is used here, which means, for example, in iteration 2, the update of array cu and array h only required the array u and array p from iteration 1, which is already available. The situation is similar for the update of array u and array p in iteration 2.

Figure 2.7 and Figure 2.8 provides more details regarding how the update of array cu and array h, as well as their periodic continuation operation are implemented. For example, the update of grid point cu(1, 0) is based on grid point p(1, 0), p(0, 0), p(1, 1)and u(1, 0). The update of grid point h(0, 0) is based on grid point u(1, 0) and p(0, 0). Periodic continuation operation is basically the copy of grid point. In kernel L100\_pc, the values of the last row in array cu will be copied to the first row, then the values of the left-most column in array cu will be copied to the right-most column. After that the grid point cu(65, 0) will be copied to cu(0, 65). In terms of array h, the values of the first row in array h will be copied to the last row, then the values of the right-most column in array h will be copied to the left-most column. After that the grid point h(0, 65) will be copied to h(65, 0). The update as well as the periodic continuation operation of array u and array p is similar with the one of array cu and array h.

Periodic continuation operation leads to "halo", which is an extra circle of data surrounding the original array. Therefore, the problem size is different from the array size. The existence of halo is to provide a better memory access pattern for the system with cache. For example, without halo, if grid point cu(0, 0) needs to be updated, it will require the value from grid point p(0, 0), p(64, 0), p(0, 1) and u(0, 0). It is obvious that the access to grid point p(64, 0) is not a stride-1 access, and the value of grid point p(64, 0) is not likely to be in the cache as well. However, if halo is available, then the update of grid point cu(0, 0) will become the update of grid point cu(1, 0) which is based on grid point p(1, 0), p(0, 0), p(1, 1) and u(1, 0). Although the access to grid point p(0, 0) is still not stride-1 access, the value of grid point p(0, 0) is very likely to be in the cache, which still provides a better memory access pattern compared to the one without halo.

# 2.6. Optimization Methods for OpenCL Application on Xilinx FPGA

This section summarizes a series of methods, learned from the literature, for optimizing FPGA application developed using OpenCL. The literature from which these methods are derived is summarized in Section 2.7.2. Section 2.6.1 describes the optimizations used in kernel code. Section 2.6.2 demonstrates optimizations used in host code. Section 2.6.3 explains optimizations that are related to the IDE SDx.

#### 2.6.1. Kernel Optimizations

A series of methods that can be used to optimize kernel code are listed as follows,

On-chip memory. Using on-chip memory as cache can reduce the memory access latency. This means storing data in BRAM, which is also known as local memory in the OpenCL memory model. This can be implemented by declaring the variable as "\_\_local".

- Burst memory transfer. The burst mode can be triggered when copying data between off-chip memory and on-chip memory. Burst memory transfer aims to improve the data transfer efficiency by combining multiple consecutive memory access into one. Hence, the memory bandwidth can be utilized in a more efficient way. This can be implemented by using function async\_work\_group\_copy().

- Loop unrolling. Loop unrolling can improve the parallelism between iterations. It can achieve a better throughput compared to loops that are not unrolled. This can be implemented by using directive "opencl\_unroll\_hint(n)". The unrolling factor can be specified by changing parameter n. If n is not specified, the loop will be completely unrolled by default. The directive needs to be put ahead of the loop body.

- Loop pipelining. Loop pipelining can improve the parallelism between iterations. According to Fifield et al (Fifield et al., 2016), loop pipelining can achieve the best throughput. This can be implemented by using directive "xcl\_pipeline\_loop". Section 4.4 provides a detail explanation regarding where to put the "xcl\_pipeline\_loop" directive in a nested loop.

- Array partitioning. By partitioning the array, the number of logics which can access (read/write) data simultaneously in each clock cycle can be increased. For example, each BRAM block has two data ports, meaning that a maximum of two logics can access data simultaneously in each clock cycle. However, if it is partitioned using directive (cyclic, 2), then each BRAM block will have four data ports, because the array data is distributed to two physical memories. This means that a maximum of four logics can access data simultaneously in each clock cycle.

This can be implemented using directive "xcl\_array\_partition(type, factor, dimension)". There are three types of array partitioning method, namely cyclic, block and complete. The type of array partitioning can be specified by changing the "type" parameter. "The original array will be split into equally sized blocks of consecutive elements of the original array, if it is partitioned in a block way. The original array will be split into equally sized blocks interleaving the elements of the original array, if it is partitioned in a cyclic way. The default operation of complete partition is to split the array into its individual elements. This means implementing the array as a collection of registers" ("SDSoC Profiling and

Optimization Guide," 2019). It should be noted that there is an array size threshold of 1024 for complete partition, meaning that arrays with size larger than 1024 cannot be partitioned in a complete way. The factor parameter "can be used to specify the number of arrays which are created for block and cyclic partition. This parameter is not applicable in complete partition. For multi-Dimensional arrays, the dimension option can be used to specify which dimension is partitioned." ("SDSoC Profiling and Optimization Guide," 2019). The directive needs to be placed after the declaration of a variable.

- Data vectorization. Data vectorization can utilize memory bandwidth in a more efficient way by transferring multiple data, instead of one, each clock cycle. This can be implemented either automatically by using directive "vec\_type\_hint(type)", or manually by declaring variables as, for example, float2, float4, float8 or float16. The type parameter of the "vec\_type\_hint" directive represent the type of data (double, float and etc) that needs to be vectorized. The directive needs to be placed ahead of the function body.

- The restrict keyword. According to (Zohouri et al., 2016), the restrict keyword can be used so that compiler will avoid making conservative decision like pointer aliasing. Hence, compiler will be able to parallelize loops if there are no dependencies exist. This can be implemented by declaring a pointer as "\_\_restrict".

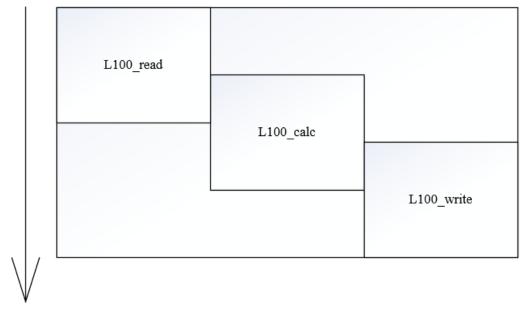

- Dataflow directive. The dataflow directive can pipeline the execution of the function calls in each kernel. This can be implemented by using directive "xcl\_dataflow". The directive needs to be placed ahead of the function body. Figure 2.9 below demonstrates how function calls L100\_read(), L100\_calc() and L100\_write() are pipelined inside kernel L100\_cu.

Figure 2.9: Execution of Function Calls L100\_read(), L100\_calc() and L100\_write() after Applying Dataflow Directive

- Function inline. Instead of making function calls, function inline will replace the function call with the function body itself. This may increase the code size, but it also eliminates the time using for function calls, hence improves the performance. This can be implemented by using directive "always\_inline". The directive needs to be placed ahead of the function body.

- Work item pipelining. The work items in a NDRange kernel can be pipelined by using directive "xcl\_pipeline\_workitems". It should be noted that this optimization is only available when using NDRange kernel.

- Optimum local work group size specification. The local work group size of a NDRange kernel that yields the best performance will always be the problem size. For example, for problem size of 65 \* 65, the local work group size with best performance will be a two-Dimensional work group with size of 65 on each dimension. However, a smaller local work group size will consume fewer hardware resource, which is useful since the hardware resource on a single FPGA is limited. Hence, the optimum work group size should be chosen carefully if applicable. It should be noted that this optimization is only available when using NDRange kernel.

- Pipe. Pipe is a FIFO memory object in the OpenCL programming language, it is very useful when it comes to streaming data between kernels. When the BRAM is not big enough to cache all the data, it will be a good idea to stream data from host

memory to device memory directly without using external memory, in order to minimize data access latency. Pipe can be implemented by using directive "xcl\_reqd\_pipe\_depth(n)", along with function write\_pipe\_block() and read\_pipe\_block(). Parameter n defines the size of the pipe. It should be noted that when pipe is utilized to stream data, it is assumed implicitly that the work items are executed sequentially.

- Zero copy of data. "The ZERO\_COPY pragma means that the hardware function accesses the data directly from shared memory through an AXI master bus interface." ("SDx Pragma Reference Guide," 2019). This can be done by using pragma "#pragma SDS data zero\_copy()". The pragma should be placed ahead of the function body.

- Merging array update kernel with periodic continuation kernel. The array update kernel can be merged with the periodic continuation kernel if the whole array is cached in BRAM, to reduce memory access overhead. For example, kernel L100\_cu and kernel L100\_pc\_cu can be merged. This allows periodic continuation operation to be conducted immediately after array update is complete, to avoid unnecessary data transfer.

#### 2.6.2. Host Optimizations

A series of methods that can be used to optimize host code are listed as follows,

- Overlapping data transfer between host memory and device memory, with the kernel computation. This be implemented by using function can enqueueMigrateMemObjects(). Function enqueueWriteBuffer() and enqueueReadBuffer() need to be replaced by enqueueMigrateMemObjects(). It should be noted that synchronization is needed when using enqueueMigrateMemObjects() in order to obtain the correct result. The parameter "CL MEM USE HOST PTR" is also be needed when declaring the buffers used by enqueueMigrateMemObjects().

- Concurrent execution of kernels. This can be implemented by using either multiple in-order command queues or one out-of-order command queue. Parameter "CL\_QUEUE\_OUT\_OF\_ORDER\_EXEC\_MODE\_ENABLE" will be necessary when declaring the command queue, if out-of-order command queue is used.

- OpenCL API execution model. Different API should be used to reduce overhead of

kernel enqueuing. "For the data parallel case, use the clEnqueueNDRange API. For the task parallel case, use the clEnqueueTask API." ("SDAccel Environment Profiling and Optimization Guide," 2019)

#### 2.6.3. SDx-related Optimizations

A series of methods that are related to SDx are listed as follows,

- The number of compute unit. The number of compute unit can be specified for each kernel in the project setting page. The number of compute unit available for each kernel ranges from 1 to 60.

- The data motion network clock frequency. The data motion network clock frequency can be set in the project setting page. The clock frequency available ranges from 75MHz to 600MHz.

- The port data width. The port data width for each kernel can be set in the project setting page. The width available ranges from 32 bits to 512 bits. The data width can also be set as auto.

- Dedicated memory port for each global array. This can be implemented by ticking the "Max Memory Port" option in the project setting page for each kernel. After this option is selected, each global array within that certain kernel will be assigned with a dedicated memory port.

#### 2.7. Literature Review

This section provides a detailed review to the papers that are key to this project. Papers in Section 2.7.1 mainly focused on performance modelling. Section 2.7.2 reviews the papers that conduct performance optimization to FPGA application. Section 2.7.3 provide a review on a paper that carried out some good overhead analysis. It should be noted in Section 2.7.2, the papers written by Sano et al and Mondigo et al provides both performance optimization and model for performance estimation.

#### 2.7.1. Papers Focused on Performance Modelling

da Silva et al. (da Silva et al., 2013) have proposed a performance model for FPGA by combing the traditional roofline model with the HLS tools. The roofline model provides a performance estimation of the target algorithm by considering the computational

performance (CP), memory bandwidth (BW) and computational intensity (CI). The CP refers to the maximum number of floating-point operations that the processor can achieve. While CI refer to algorithm complexity, which is the number of operations executed per byte access from memory. CP and BW is related to the hardware architecture itself while CI is related to the application.

However, traditional roofline model cannot be applied to estimate the performance of FPGA, because the hardware architecture of FPGA is not fixed and can be influenced by the application. This means CP in this case is directly relates to CI. By connecting the computational power with the resource consumption, an extended roofline model is introduced. A new concept called the scalability (SC) is introduced as well. The SC refer to the number of PE, which can be obtained by dividing the available resources on FPGA by the resources each PE consumes. The performance of a FPGA can then be acquired by multiply SC with the performance of PE. The computation of CI is also modified by dividing the number of operations in one iteration, with the number of memory access for input and output values.

HLS tools play an important role in the extended roofline model. Because they provide optimizations and information like FPGA resource utilization, latency, and throughput. A class of window-based image processing applications along with two different HLS tools are served as case study in their work. They demonstrated that the extended roofline model is accurate enough to estimate the performance of FPGA based on the information provided by the HLS tools. The extended roofline is also flexible enough to be combined with any HLS tools.

Parker (Parker, 2017) has shed some lights on the topic of how to calculate the peak floating-point capabilities of DSP, GPGPU and FPGA in this white paper. One common way of determining the peak FLOPS (floating-point operation per second) rate is to multiply the sum of the adders and multipliers by the maximum operation frequency. Because FLOP is defined as an addition or multiplication of single or double precision number. Other operations like division, square root, FFT (fast Fourier transform) and matrix operation needs to be constructed using adders and multipliers as well.

However, when it comes to FPGA, the method mentioned above might not be able to produce the reliable peak FLOPS rate, due to the following challenges. First, the floating-point precision level implemented on FPGA is not restricted to the industrial-standard single and double precision. In fact, multiple precision levels are implemented. Another challenge is that it is difficult to determine the routing resources that is needed to implement the floating-point operation. While things like large barrel shifter which consumes a large amount of programmable routing are required when implementing floating-point operation. In addition, not all the programmable logic on FPGA can be fully utilized, since it will lead to the reduction of the clock frequency.

In order to calculate the peak FLOPS on FPGA, Parker has proposed two methods. The first one is to use the benchmark provided by the FPGA vendors. Another way is to use only add or subtract function, and build as many adders as possible using DSP48E, then build the remaining adders using pure logic, in order to maximize the floating-point rating. However, he also mentioned that the second method is not a benchmark that is recognized by the industry, and such design has no application benefits. Parker also believed that for FPGA without hard floating-point circuits, using the vendor-calculated theoretical GFLOPS numbers is quite unreliable.

In summary, Parker believed that in order to obtain the peak FLOPS performance of devices with different architectures, for simplicity, it can be done by multiplying the sum of the adders and multipliers by the maximum operation frequency. But ultimately, relevant benchmark provided by the vendors should be used for a more accurate FLOPS performance result.

Some other performance modelling includes a performance modelling of the 3-Dimensional stencil computation on a stream-based FPGA, proposed by (Dohi et al., 2013), a performance modelling of pipelined linear algebra architectures on FPGAs developed by (Skalicky et al., 2013) and a method of evaluating FPGAs for floatingpoint performance proposed by (Strenski et al., 2008).

### 2.7.2. Papers Focused on Performance Optimization

Cong et al. (Cong et al., 2018) have proposed a best-effort guideline for improving

FPGA programming productivity as well as FPGA accelerator performance. The guideline makes FPGA programming easier by easing the burden of the software programmers, allowing them to learn fewer hardware knowledge.

Furthermore, the guideline improves the performance of the FPGA accelerator by using five refinement steps of HLS, namely explicit data caching, pipelining, processing element duplication, computation overlapping and scratchpad reorganization. Explicit data caching means explicitly copy the data for the computation to the BRAM of the FPGA. Here BRAM is considered as the cache of FPGA. Pipelining is similar with CPU pipelines. However, FPGA designers can construct very deep pipeline with hundreds or even thousands of stages. Processing element duplication is similar with multithreading programming. The processing units of FPGA and CPU cores is counterparts. Computation overlapping in this case means constructing a three-stage coarse-grained pipeline for better resource utilization. Scratchpad reorganization refers to the using of larger-width data type to better utilize memory bandwidth.

They demonstrated that by applying their guideline, the performance of the FPGA accelerator can be 42~29,030x faster, compared to the performance of the non-optimized, naïve FPGA accelerator. The optimized FPGA accelerator is also up to 112.8x faster than a single Xeon CPU core.

Targett et al. (Targett et al., 2015) have proposed a method of accelerating C-grid shallow water model by using lower precision variable and FPGA. They tried to stop using double precision floating point variable and represent the variable with less bits. By reducing the mantissa length of the variables, the spare computing resources can be used to simulate climate change at a higher resolution, which may eventually improve accuracy.

They also proposed an accuracy verification method, to make sure the accuracy will be acceptable after the precision is lowered. This is accomplished by first calculating the mean and standard deviation of the fields, then the mean and standard deviation of the errors. After that the maximum value of mean and standard deviation is picked out and compared with the acceptable mean and standard deviation. They demonstrated that the mantissa length of the variable can be reduced to 14 bits while maintaining an acceptable error. Their reduced precision FPGA implementation runs 5.4x faster than the double precision FPGA implementation, and 12x faster than the multi-threaded CPU implementation. What's more, their reduced precision FPGA implementation uses 39 times less energy than the CPU implementation. For the same power consumption, the reduced precision FPGA implementation can compute a 100\*100 grid while the CPU implementation can only compute a 29 \* 29 grid.

Düben (Düben, 2018) has proposed a method to reduce the overall data usage and data volume by using a new number format which exploits the similarities between ensemble member. The data usage is reduced by reducing the number of bits that represent the information required for the forecasting model. The ensemble mean is removed from the ensemble data and is combined with a normalization by local ensemble range. By doing this the precision is reduced so does the number of bits which represents the number.

The new number format is realized in a standard shallow water model using Fortran. It performs well for long-term, climate-type simulations. However, disadvantages still exist. When utilizing the new number format, ensemble members will be combined into one single simulation which make it impossible to parallelize them. Another disadvantage is that a single simulation with the new number format will take more time compared to the calculation of a single ensemble member. What's more, the total number of floating-point operations is likely to be increased for the entire ensemble forecast.

Sano et al. (Sano et al., 2014) have proposed a custom computing machine (CCM) called scalable streaming-array (SSA) for conducting stencil computation over multiple FPGAs.

The scalable streaming-array is made up of multiple FPGA, with one master FPGA and multiple slave FPGAs. On each FPGA, there is one ISRU (Input Stream Routing Unit), one OSRU (Output Stream Routing Unit) and multiple PSM (Pipelined Stage Model). Each PSM consists of multiple PE, which forms an array connected by a bidirectional

1-Dimensional torus network. The SSA is literally a linear array of PSM, the input values streaming through the ISRU and are assigned to the PEs of the first PSM. Each PE will calculate several stencils base on the value they receive and the value stored in their local buffer. After the calculation is completed, the result will be sent to the corresponding PEs in the next following PSM. The PEs in the same PSM will also needs to communicate with the above and lower PEs to exchange the value they received, since each PE doesn't have all the value it needs to finish the stencil computation. The final output will come from the OSRU which is a single stream.

The scalable streaming-array is designed in this way due to the low operational intensity of stencil computation, as well as the number of iterations needed for allowing the result to converge. Since FPGA is famous for its deep pipeline, each PSM is responsible for the calculation of one iteration. In this way, all the iterations are pipelined, which means multiple iteration computation can be done using a single data stream, and no large memory bandwidth will be needed. Hence, memory access latency is concealed.

A performance model is also proposed for estimating peak performance, scalability and speedup. They demonstrated their scalable streaming-array architecture on multiple high-end and low-end FPGAs. Both 2-Dimensional and 3-Dimensional Jacobi computation are used as benchmark. Their design showed a good agreement with the performance model, and achieved performance of 260 GFlop/s and 236 GFlop/s for 2-Dimensional and 3-Dimensional Jacobi computation, which are 87.4% and 83.9% of the peak performance respectively, with a memory bandwidth of only 2.0 GB/s. In terms of power consumption, the scalable streaming-array architecture provided excellent performance per power of 1.30 GFlop/s/W and 1.07 GFlop/s/W for the 2-Dimensional and 3-Dimensional Jacobi computation respectively. Their design also showed good scalability.

Mondigo et al. (Mondigo et al., 2019) proposed a scalable architecture with deep pipelined stream. What they proposed in this paper is based on the one developed by (Sano et al., 2014). The major contribution of this paper is as follows, it first explained how temporal and spatial parallelism can be achieved, then it presents an inter-FPGA communication subsystem. Finally, it perfected the performance model Sano et al

proposed by considering the inter-FPGA communication overhead, overheads introduced by the temporal parallelism and spatial parallelism.

Temporal parallelism can be achieved by cascading multiple SPE (Streaming Processing Element) to form a deep pipeline. Spatial parallelism can be achieved by having multiple parallelized unit pipelines in each SPE.

The inter-FPGA communication subsystem proposed in this paper is implemented base on a FC (Flow Control) core and a Serial-Lite III (SL3) core. FC core includes TX buffer, RX buffer and credit counter to deal with incoming data stream and backpressure. Both link latency and the depth of the communication buffers will affect the inter-FPGA communication overhead. While the deep pipeline introduced by the temporal parallelism will also lead to overhead. Furthermore, the wider input/output data stream bandwidth introduced by the spatial overhead will cause overhead if either the memory bandwidth or communication link bandwidth is insufficient. By taking all these factors into consideration, the performance model can estimate the theoretical performance accurately. The theoretical performance is different from peak performance by considering the overheads.

They demonstrated their design on multiple cascaded Arria 10 FPGAs using tsunami simulation as benchmark. They found out that the highest scaled performance for 8 cascaded Arria 10 FPGAs is achieved with a single pipeline of 5 SPEs, which obtained a scaled performance of 2.5 TFlops and a parallel efficiency of 98%.

Fifield et al (Fifield et al., 2016) have proposed several methods for optimizing OpenCL application on Xilinx FPGA. In their slide, they first introduced the FPGA architecture and its difference between CPU and GPGPU. Then they talked about the difficulties for programming FPGA.

They proposed several ways of optimizing OpenCL kernels running on Xilinx FPGA, including common optimization like loop unrolling, loop pipelining, work item pipelining, data vectorization, burst memory transfer, array partitioning and the usage of local memory instead of global memory. However, they also proposed some other

unique optimization methods. For example, specifying a better local work group size, using pipes to stream data between kernels and using multiple external memory DDR banks.

Muslim et al (Muslim et al., 2017) has presented an HLS-based FPGA implementation of several algorithms, including KNN (K-Nearest Neighbour) algorithm, Monte Carlo methods for financial models and bitonic sorting algorithm. They also conducted a performance comparison between FPGA and some high-end GPGPU in terms of execution time and power consumption.

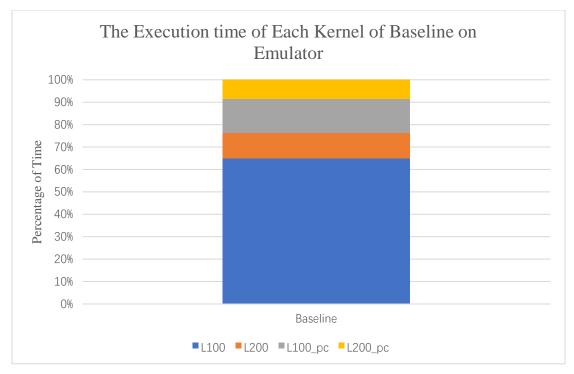

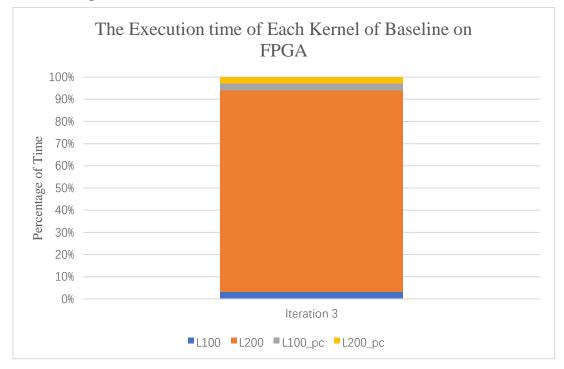

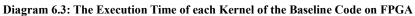

The optimizations they used including work item pipelining, loop pipelining, loop unrolling, burst memory transfer, using on-chip memory, using on-chip pipes for interkernel communication, using multiple compute units and using dedicated memory port for each global array. Besides, Muslim et al also tried optimizing the algorithm itself. For example, they developed two version of the KNN algorithm. The first version only implemented the distance calculation in the kernel. In the second version however, they implemented both the distance calculation and the nearest neighbour estimation in two different kernels. Muslim et al believed FPGA will perform better for applications that doesn't require too many accesses to slow external DRAM, due to its limited memory bandwidth with it. (compared to GPGPU which has a larger memory bandwidth interface with external DRAM). They also believed that loop pipelining will yield a better performance than loop unrolling since the number of memory port is limited. They claimed that optimizing FPGA application is about guiding the compiler to generate optimized code and memory architecture for each kernel.