# EXPLORING PHOTONIC BENEŠ SWITCHING FABRICS FOR FUTURE HPC AND DATACENTRES

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN THE FACULTY OF SCIENCE AND ENGINEERING

2022

Markos Kynigos

Department of Computer Science

## Contents

| ostrac | t                                                                                                   |                                                                                                                                                                                                                                                                                                                                                           | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| eclara | tion                                                                                                |                                                                                                                                                                                                                                                                                                                                                           | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| opyrig | ght                                                                                                 |                                                                                                                                                                                                                                                                                                                                                           | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| know   | ledgem                                                                                              | ients                                                                                                                                                                                                                                                                                                                                                     | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| crony  | ms                                                                                                  |                                                                                                                                                                                                                                                                                                                                                           | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Intro  | oductio                                                                                             | n                                                                                                                                                                                                                                                                                                                                                         | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1.1    | Motiva                                                                                              | ation                                                                                                                                                                                                                                                                                                                                                     | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1.2    | Thesis                                                                                              | Contributions                                                                                                                                                                                                                                                                                                                                             | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1.3    | Public                                                                                              | ations                                                                                                                                                                                                                                                                                                                                                    | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1.4    | Outlin                                                                                              | e                                                                                                                                                                                                                                                                                                                                                         | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SiPh   | IC Re                                                                                               | view                                                                                                                                                                                                                                                                                                                                                      | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.1    | Introdu                                                                                             | uction                                                                                                                                                                                                                                                                                                                                                    | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.2    | Nome                                                                                                | nclature                                                                                                                                                                                                                                                                                                                                                  | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.3    | Anator                                                                                              | my of a Silicon Photonic Pathway                                                                                                                                                                                                                                                                                                                          | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.4    | Switch                                                                                              | ning & Multiplexing Techniques                                                                                                                                                                                                                                                                                                                            | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 2.4.1                                                                                               | Buffered vs. Bufferless                                                                                                                                                                                                                                                                                                                                   | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 2.4.2                                                                                               | Circuit Switching                                                                                                                                                                                                                                                                                                                                         | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 2.4.3                                                                                               | Time Division Multiplexing                                                                                                                                                                                                                                                                                                                                | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 2.4.4                                                                                               | Wavelength Division Multiplexing                                                                                                                                                                                                                                                                                                                          | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.5    | Silicor                                                                                             | Photonic Devices                                                                                                                                                                                                                                                                                                                                          | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 2.5.1                                                                                               | Lasers                                                                                                                                                                                                                                                                                                                                                    | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 2.5.2                                                                                               | Modulators                                                                                                                                                                                                                                                                                                                                                | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | 2.5.3                                                                                               | Waveguides                                                                                                                                                                                                                                                                                                                                                | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        | eclara<br>opyrig<br>eknow<br>eronyr<br>1.1<br>1.2<br>1.3<br>1.4<br>SiPh<br>2.1<br>2.2<br>2.3<br>2.4 | Introductio         1.1       Motiva         1.2       Thesis         1.3       Public         1.4       Outlin         SiPh       IC Re         2.1       Introduction         2.2       Nomen         2.3       Anator         2.4       Switch         2.4.1       2.4.2         2.4.3       2.4.4         2.5       Silicon         2.5.1       2.5.2 | eclaration         pyright         eknowledgements         eronyms         Introduction         1.1       Motivation         1.2       Thesis Contributions         1.3       Publications         1.4       Outline         2.1       Introduction         2.2       Nomenclature         2.3       Anatomy of a Silicon Photonic Pathway         2.4       Switching & Multiplexing Techniques         2.4.1       Buffered vs. Bufferless         2.4.3       Time Division Multiplexing         2.4.4       Wavelength Division Multiplexing         2.5       Silicon Photonic Devices         2.5.1       Lasers         2.5.2       Modulators |

|   |      | 2.5.4   | Switching Devices                                                    | 40 |

|---|------|---------|----------------------------------------------------------------------|----|

|   |      | 2.5.5   | Detection                                                            | 43 |

|   | 2.6  | Photor  | nic Losses & Power Penalty                                           | 44 |

|   |      | 2.6.1   | Insertion Loss                                                       | 45 |

|   |      | 2.6.2   | Crosstalk                                                            | 46 |

|   |      | 2.6.3   | Inter-channel Crosstalk                                              | 46 |

|   |      | 2.6.4   | Intra-channel Crosstalk                                              | 48 |

|   |      | 2.6.5   | Photonic Power Penalty                                               | 50 |

|   | 2.7  | Multi-  | Stage Switch Fabric Network Topologies                               | 50 |

|   | 2.8  | Target  | Switch Fabric                                                        | 56 |

|   |      | 2.8.1   | Optimising the Power Penalty in Photonic Switching Fabrics .         | 58 |

|   | 2.9  | Desigr  | n Challenges                                                         | 58 |

| 3 | Eval | uation  | Methodology                                                          | 61 |

|   | 3.1  |         | nic Interconnection Network Simulation                               | 62 |

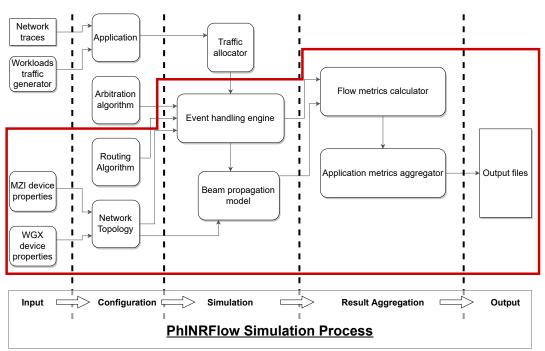

|   | 3.2  | Introdu | uction to PhINRFlow                                                  | 64 |

|   |      | 3.2.1   | Bufferless Photonic Switch Simulation                                | 64 |

|   |      | 3.2.2   | Simulator Structure                                                  | 65 |

|   |      | 3.2.3   | Extensions conducted for PSF Modelling                               | 69 |

|   | 3.3  | Model   | ling the Beneš Switch Fabric                                         | 71 |

|   | 3.4  | Model   | ling Photonic Losses and Switching Energy in PhINRFlow               | 73 |

|   |      | 3.4.1   | Insertion Loss & Crosstalk                                           | 74 |

|   |      | 3.4.2   | Required Laser Power                                                 | 75 |

|   |      | 3.4.3   | Switching Energy                                                     | 75 |

|   | 3.5  | Photor  | nic Loss Simulation Comparison                                       | 75 |

|   |      | 3.5.1   | Simulating Light Propagation in a $16 \times 16$ EOMZI Switch Fabric | 76 |

|   |      | 3.5.2   | Simulating Light Propagation in a $16 \times 16$ TOMZI Switch Fabric | 78 |

|   | 3.6  | PhINR   | Prove Routing Models                                                 | 80 |

|   |      | 3.6.1   | The Looping Algorithm                                                | 81 |

|   |      | 3.6.2   | Challenges of the Looping Algorithm in Photonic Beneš Switch-        |    |

|   |      |         | ing Fabrics                                                          | 82 |

|   |      | 3.6.3   | Hardware-Inspired Routing Strategies                                 | 83 |

|   | 3.7  | Impac   | t of Routing Algorithm Choice on Photonic Metrics                    | 86 |

|   |      | 3.7.1   | Experiment Design                                                    | 86 |

|   |      | 3.7.2   | Impact on Highest Crosstalk                                          | 89 |

|   |      | 3.7.3   | Impact on Aggregate Crosstalk per Port                               | 93 |

|        |                                                                       | 3.7.4 Impact on Optical Power Penalty                                                                 | 97                                            |  |

|--------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------|--|

|        |                                                                       | 3.7.5 Impact on Laser Power                                                                           | 100                                           |  |

|        | 3.8                                                                   | Known Modelling Limitations                                                                           | 103                                           |  |

|        | 3.9                                                                   | Summary                                                                                               | 104                                           |  |

| 4      | Pap                                                                   | er 1: Scalability Analysis of optical Beneš networks based on The                                     | ſ <b>-</b>                                    |  |

|        | mall                                                                  | ly/Electrically Tuned Mach-Zehnder Interferometers                                                    | 106                                           |  |

| 5      | Pap                                                                   | er 2: On the Routing and Scalability of MZI-based Optical Beneš Ir                                    | 1-                                            |  |

|        | terc                                                                  | onnects                                                                                               | 113                                           |  |

| 6      | Paper 3: Power and Energy Efficient Routing forMach-Zehnder Interfer- |                                                                                                       |                                               |  |

|        | ome                                                                   | ter based Photonic Switches                                                                           | 137                                           |  |

|        |                                                                       |                                                                                                       |                                               |  |

| 7      | Pap                                                                   | er 4: Understanding the Impact of Arbitration in MZI-based Bene                                       | eš                                            |  |

| 7      | -                                                                     | er 4: Understanding the Impact of Arbitration in MZI-based Bene<br>tching Fabrics                     | eš<br>151                                     |  |

| 7<br>8 | Swit                                                                  |                                                                                                       |                                               |  |

|        | Swit                                                                  | tching Fabrics                                                                                        | 151                                           |  |

|        | Swit<br>Con                                                           | tching Fabrics<br>clusions                                                                            | 151<br>165                                    |  |

|        | Swite<br>Con<br>8.1                                                   | tching Fabrics<br>clusions<br>Epilogue                                                                | <b>151</b><br><b>165</b><br>165               |  |

|        | Switt<br>Con<br>8.1<br>8.2                                            | tching Fabrics clusions Epilogue                                                                      | <b>151</b><br><b>165</b><br>165<br>165        |  |

|        | Swite<br>Con<br>8.1<br>8.2<br>8.3                                     | tching Fabrics         clusions         Epilogue         Summary of Contributions         Future Work | <b>151</b><br><b>165</b><br>165<br>165<br>169 |  |

|        | Swite<br>Con<br>8.1<br>8.2<br>8.3                                     | tching Fabrics         clusions         Epilogue                                                      | <b>151</b><br><b>165</b><br>165<br>169<br>170 |  |

Word Count: 57049

## **List of Tables**

| 2.1 | Most commonly adopted topologies for multi-stage switching fabrics          |     |

|-----|-----------------------------------------------------------------------------|-----|

|     | based on $2 \times 2$ switches.                                             | 51  |

| 3.1 | I/O Permutations served by the "all-cross" and "all-bar" States             | 76  |

| 3.2 | A permutation example for Looping Algorithm setup                           | 81  |

| 3.3 | Photonic parameters for simulation.                                         | 89  |

| 3.4 | Percentage of simulations in which $XT_{i,j} \ge 0.25$ at least once        | 96  |

| 4.1 | Optical loss and power consumption.                                         | 110 |

| 4.2 | DSENT simulation parameters                                                 | 110 |

| 4.3 | Number of flows per workload                                                | 110 |

| 5.1 | State-of-the-art photonic network proposals.                                | 117 |

| 5.2 | Component scalability and area estimation.                                  | 118 |

| 5.3 | Number of "cross"/"bar" MZIs and waveguide crossings encountered            |     |

|     | by flows with each routing strategy in a $32 \times$ Beneš, when exposed to |     |

|     | a Bisection workload                                                        | 120 |

| 5.4 | Number of flows per workload                                                | 121 |

| 5.5 | Insertion loss and power consumption                                        | 122 |

| 5.6 | DSENT simulation parameters.                                                | 127 |

| 6.1 | TDM segment size & slot duration                                            | 142 |

| 6.2 | Number of flows per workload                                                | 143 |

| 7.1 | Power and energy consumption of switches.                                   | 154 |

| 7.2 | Simulation parameters.                                                      | 158 |

# **List of Figures**

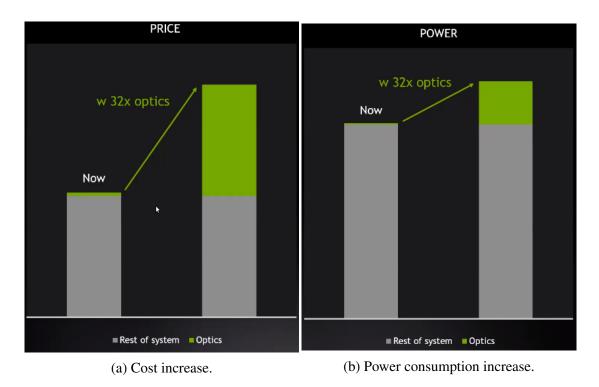

| 1.1  | A qualitative comparison of the price and cost increases associated                                 |    |

|------|-----------------------------------------------------------------------------------------------------|----|

|      | with improving pluggable optics. Image copied from [SZC <sup>+</sup> 21]. $\ldots$                  | 21 |

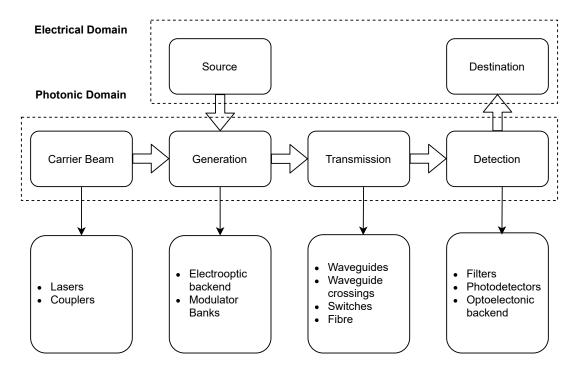

| 2.1  | High-level depiction of photonic communication.                                                     | 31 |

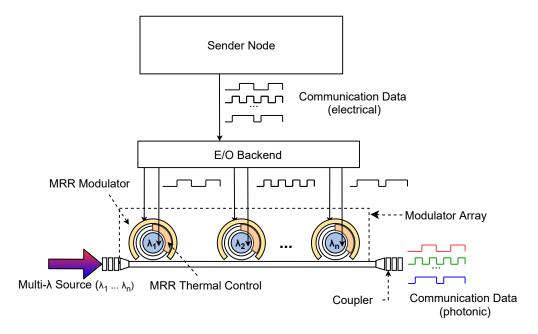

| 2.2  | Structure of photonic signal generation based on MRR modulators                                     | 39 |

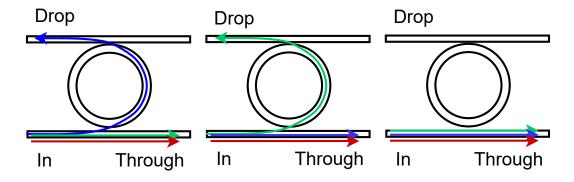

| 2.3  | A $2 \times 2$ wavelength-selective switch formed with an MRR. Image adapted                        |    |

|      | from [BCB <sup>+</sup> 14]. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 41 |

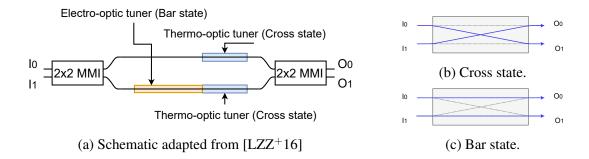

| 2.4  | A $2 \times 2$ EO/TO MZI switch with associated states                                              | 42 |

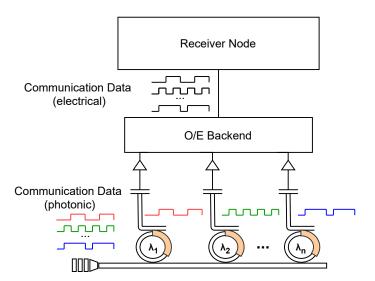

| 2.5  | Structure of a photonic receiver based on MRR filters                                               | 44 |

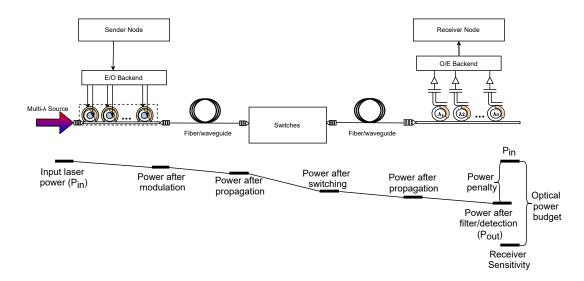

| 2.6  | Evolution of the power penalty in a photonic pathway                                                | 45 |

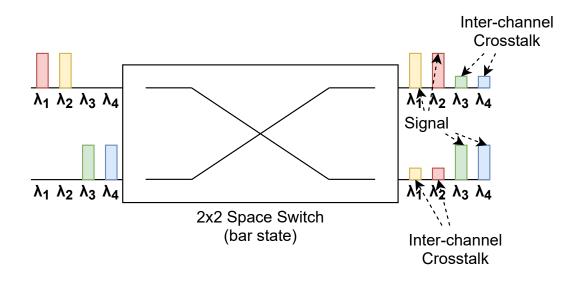

| 2.7  | Inter-channel crosstalk in a 2 $\times$ 2 Space switch in the bar state                             | 47 |

| 2.8  | Intra-channel crosstalk in a $4 \times 4$ switching fabric                                          | 48 |

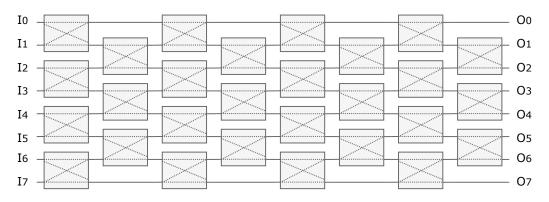

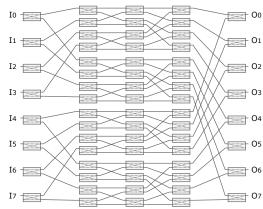

| 2.9  | An $8 \times 8$ Banyan network                                                                      | 52 |

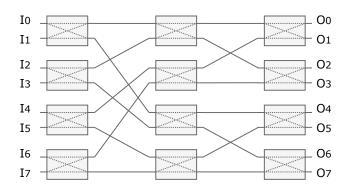

| 2.10 | An $8 \times 8$ Beneš network                                                                       | 52 |

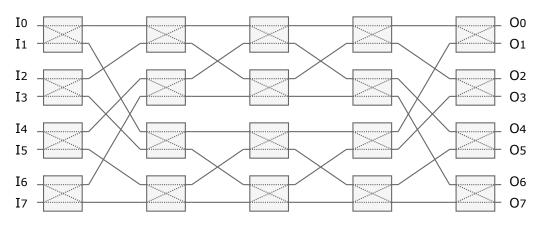

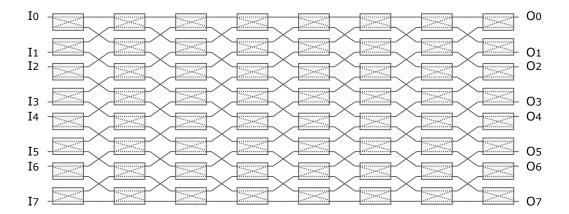

| 2.11 | An $8 \times 8$ Dilated Beneš network                                                               | 53 |

| 2.12 | An $8 \times 8$ N-stage-planar network                                                              | 53 |

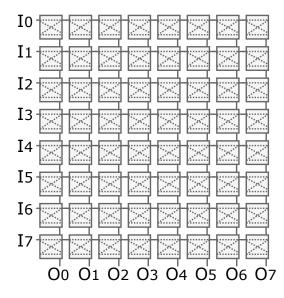

| 2.13 | An $8 \times 8$ crossbar network                                                                    | 54 |

| 2.14 | An $8 \times 8$ PILOSS network                                                                      | 54 |

| 2.15 | An $8 \times 8$ Switch-and-Select network                                                           | 55 |

| 2.16 | An $8 \times 8$ DLN network                                                                         | 55 |

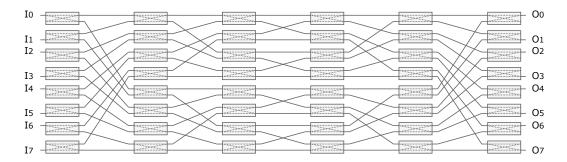

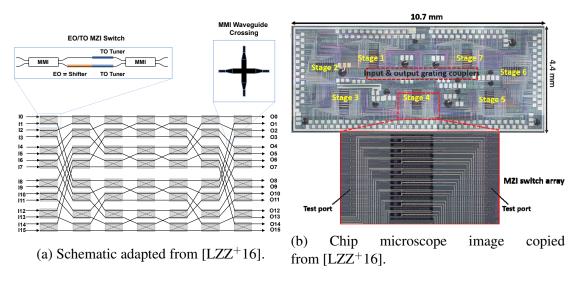

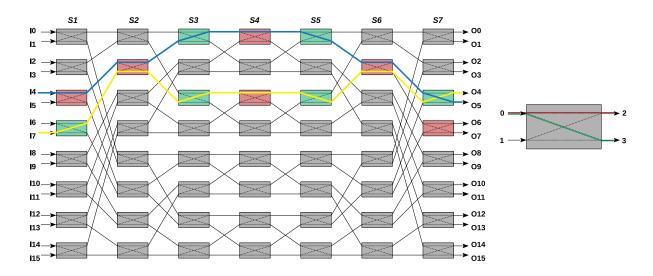

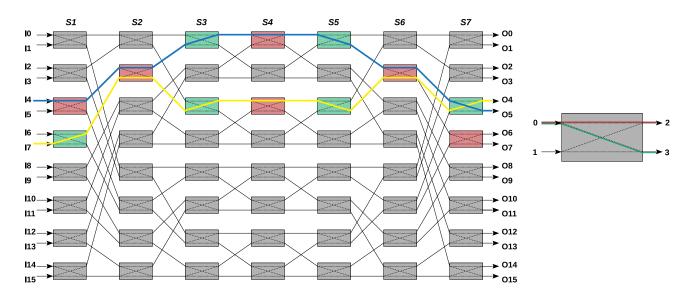

| 2.17 | $16 \times 16$ EO/TO Beneš switch fabric.                                                           | 57 |

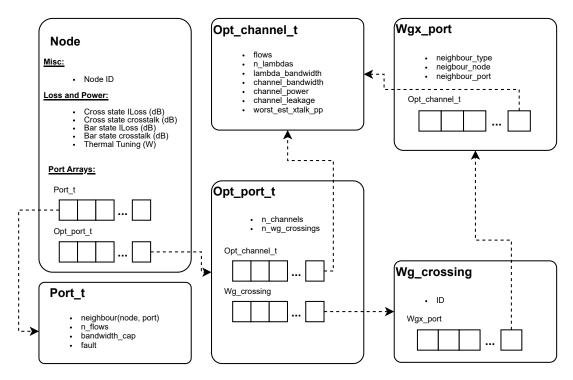

| 3.1  | Structures used for modelling photonic nodes                                                        | 66 |

| 3.2  | Structures used for modelling photonic nodes                                                        | 70 |

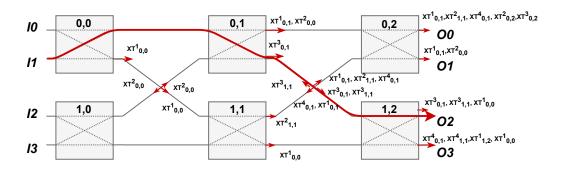

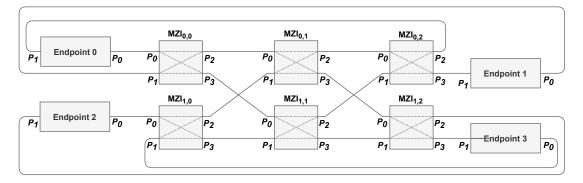

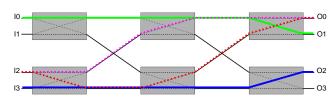

| 3.3  | A 4-endpoint Beneš network with connected endpoints                                                 | 72 |

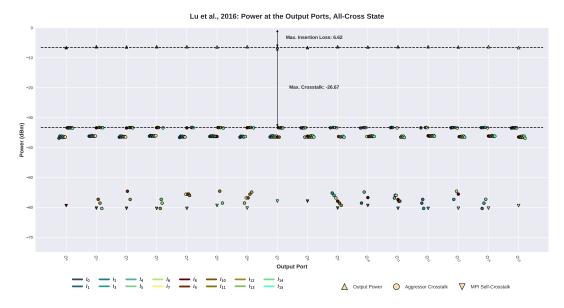

| 3.4  | Simulated power and leakage values for the "all-cross" state at 1560 nm.                            | 77 |

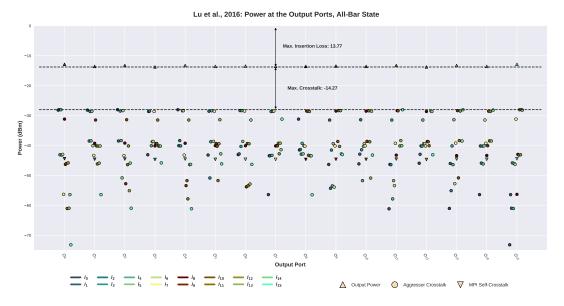

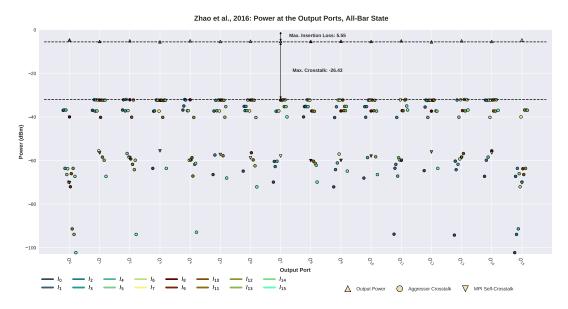

| 3.5  | Simulated power and leakage values for the "all-bar" state at 1560 nm.                              | 78 |

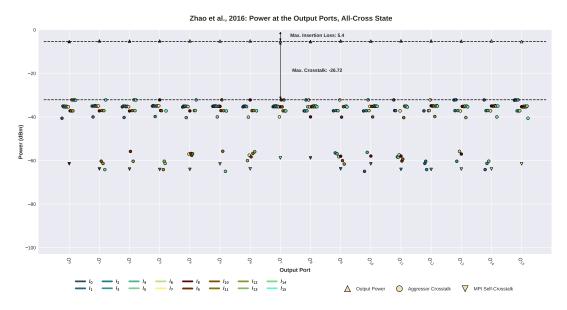

| 3.6  | Simulated power and leakage values for the "all-cross" state at 1560 nm.                            | 79 |

| 3.7  | Simulated power and leakage values for the "all-bar" state at 1560 nm.                                                                                 | 80  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

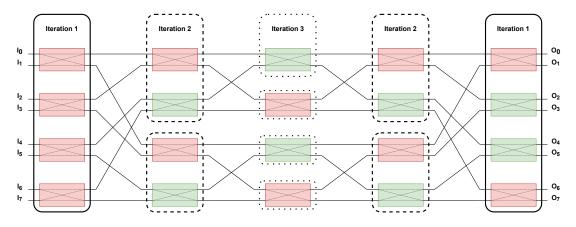

| 3.8  | Recursive switch state setup in the Looping Algorithm                                                                                                  | 81  |

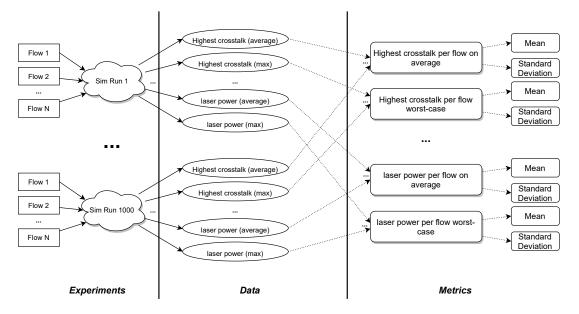

| 3.9  | The process of composing simulation data into metrics                                                                                                  | 87  |

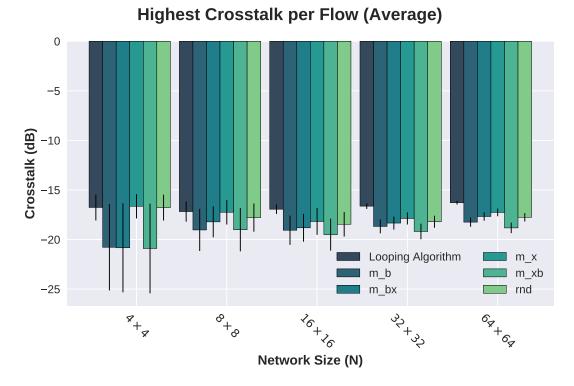

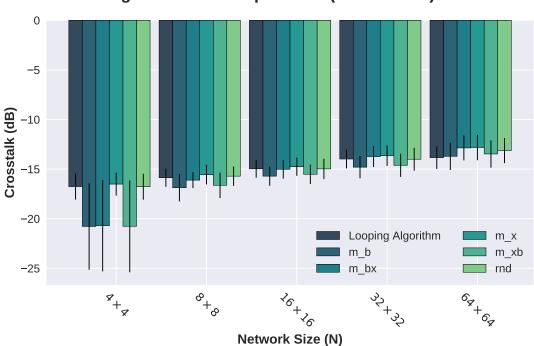

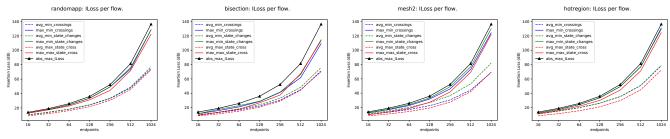

| 3.10 | Highest crosstalk per flow on average. Lower is Better                                                                                                 | 90  |

| 3.11 | Highest crosstalk per flow in the worst case. Lower is Better                                                                                          | 91  |

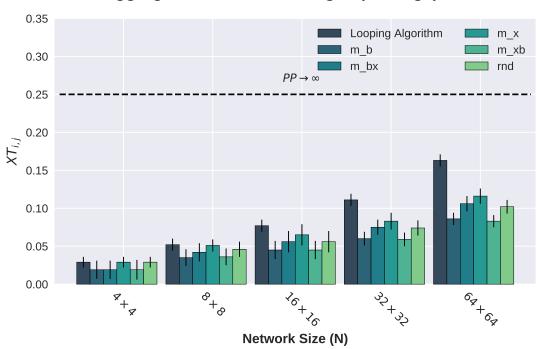

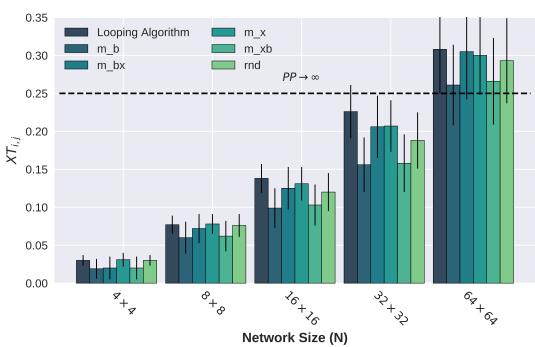

| 3.12 | Aggregation of crosstalk on average (a). Lower is Better                                                                                               | 94  |

| 3.13 | Aggregation of crosstalk in the worst case (b). Lower is Better                                                                                        | 95  |

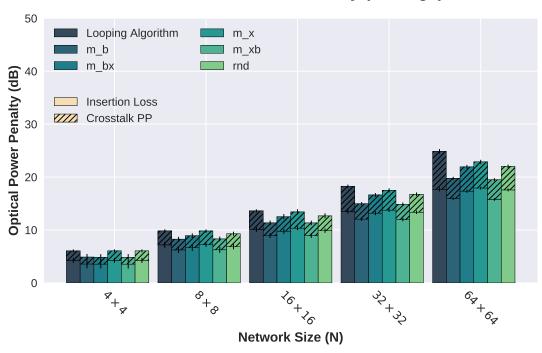

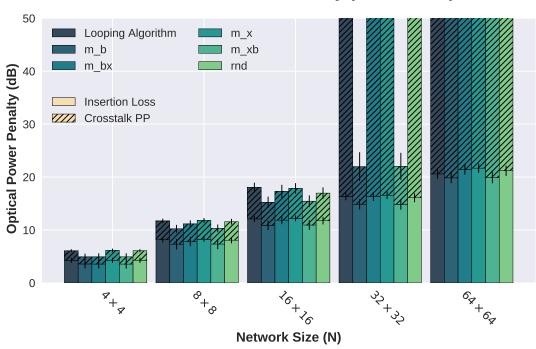

| 3.14 | Insertion Loss and Power Penalty on average. Lower is Better                                                                                           | 97  |

| 3.15 | Insertion Loss and Power Penalty in the worst case. Lower is Better                                                                                    | 99  |

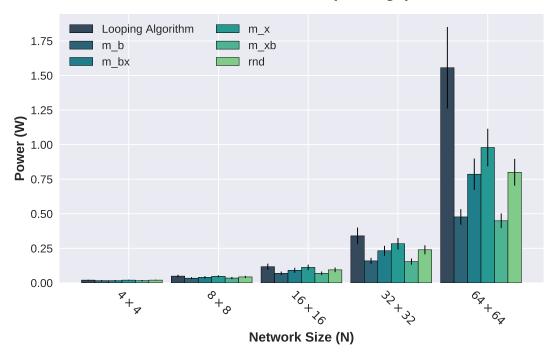

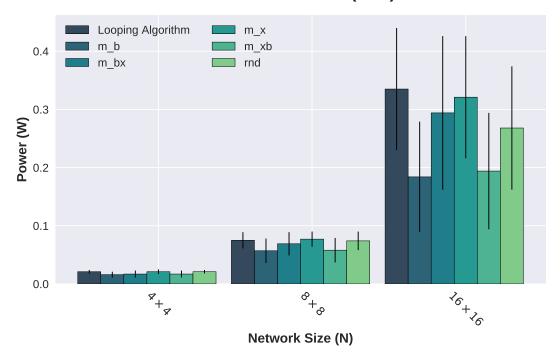

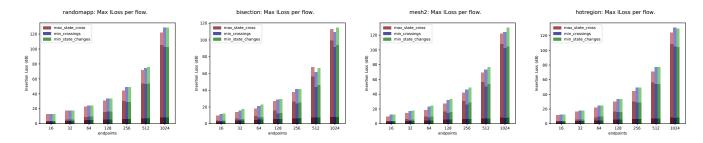

| 3.16 | Required laser power per port in the average case. Lower is Better                                                                                     | 101 |

| 3.17 | Required laser power per port in the worst case. Lower is Better                                                                                       | 102 |

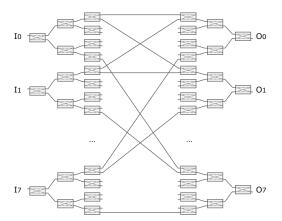

| 4.1  | Topology diagram of the $16 \times 16$ Beneš network and an MZI with port                                                                              |     |

|      | numbers                                                                                                                                                | 108 |

| 4.2  | Insertion loss (dB).                                                                                                                                   | 110 |

| 4.3  | Maximum insertion loss breakdown (dB)                                                                                                                  | 111 |

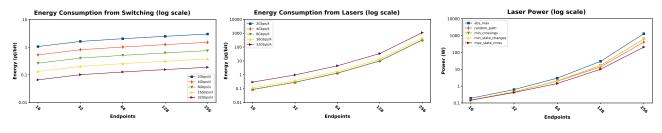

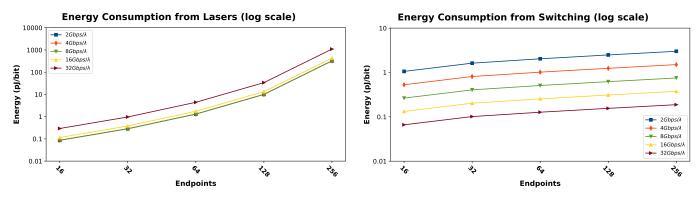

| 4.4  | Energy consumption from lasers and switching                                                                                                           | 112 |

| 4.5  | Laser power                                                                                                                                            | 112 |

| 5.1  | Topology diagram of the $16 \times 16$ Beneš network and an MZI with port                                                                              |     |

|      | numbers                                                                                                                                                | 118 |

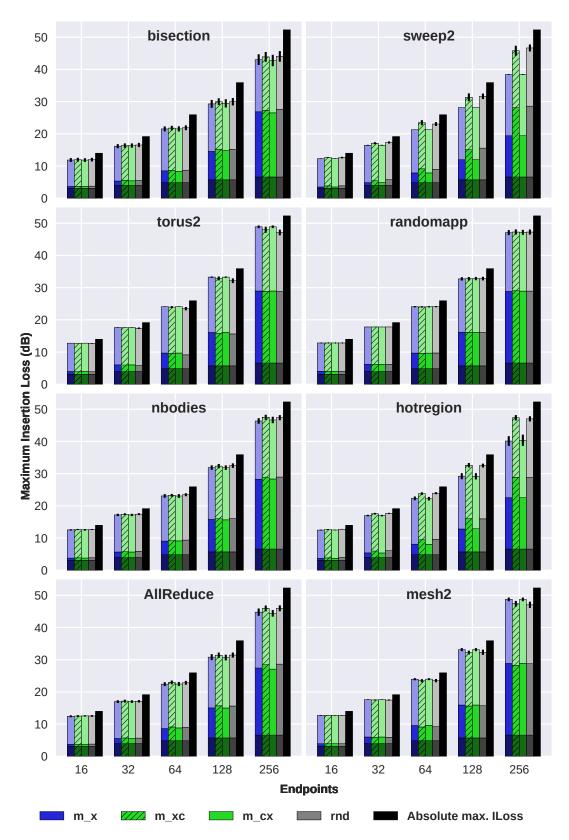

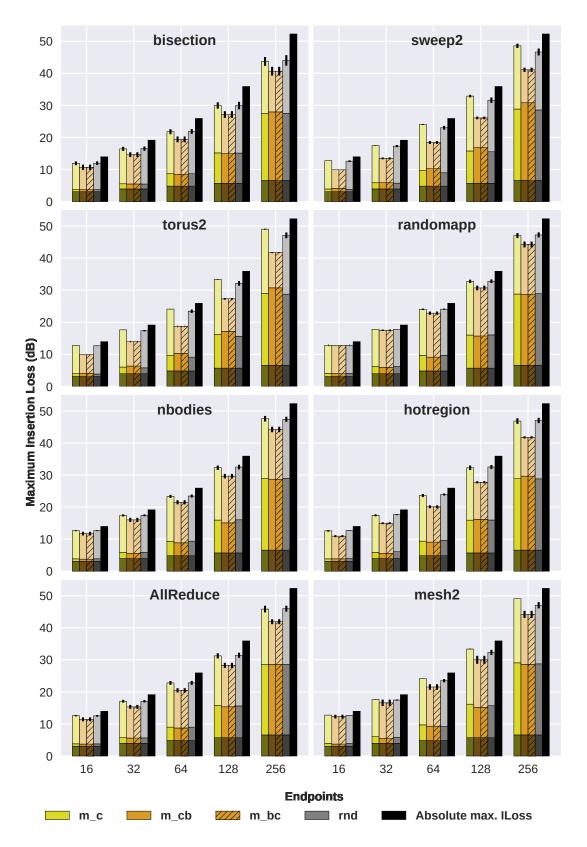

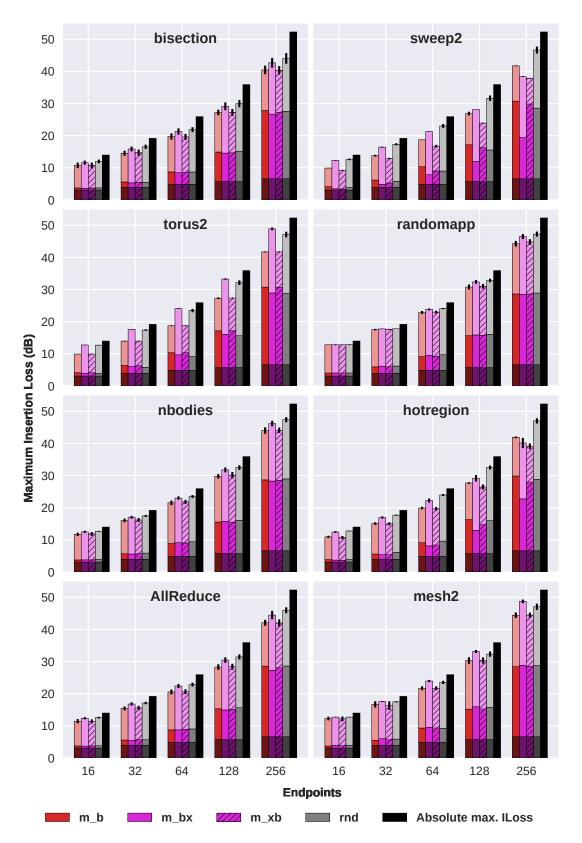

| 5.2  | Maximum insertion loss breakdown (dB) using the $m_x$ , $m_xc$ , $m_cx$<br>and <i>rnd</i> routing strategies.                                          | 123 |

| 5.3  | Maximum insertion loss breakdown (dB) using the $m_{-c}$ , $m_{-c}b$ , $m_{-b}c$                                                                       | 123 |

| 5.5  |                                                                                                                                                        | 124 |

| 5.4  | and <i>rnd</i> routing strategies                                                                                                                      | 127 |

| Ј.т  | and <i>rnd</i> routing strategies. $\dots \dots \dots$ | 126 |

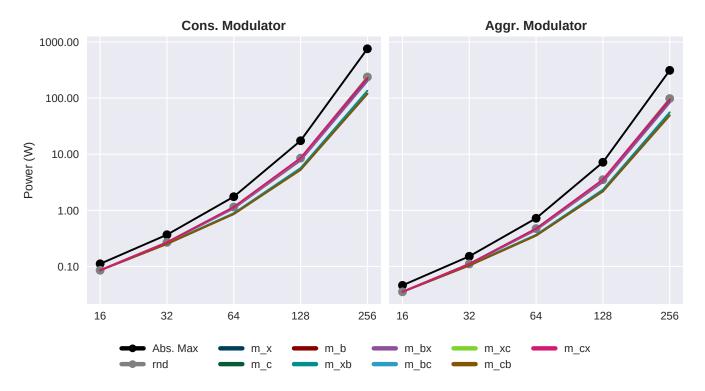

| 5.5  | Energy consumption (pJ/bit) from lasers and switching                                                                                                  | 127 |

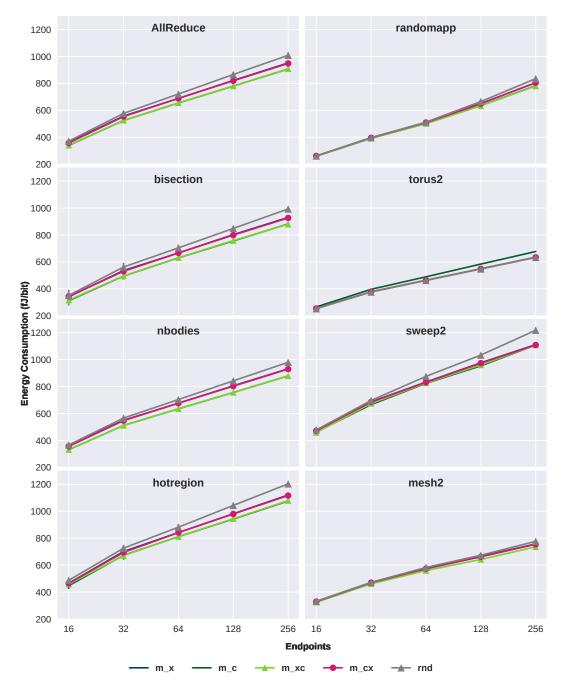

| 5.6  | Switching energy consumption (fJ/bit) for the $m_x$ , $m_c$ , $m_xc$ , $m_cx$                                                                          |     |

|      | and <i>rnd</i> routing strategies                                                                                                                      | 128 |

| 5.7  | Switching energy consumption (fJ/bit) for the <i>m_b</i> , <i>m_xb</i> , <i>m_bx</i> , <i>m_cb</i> ,                                                   |     |

|      | $m\_bc$ and $rnd$ routing strategies                                                                                                                   | 129 |

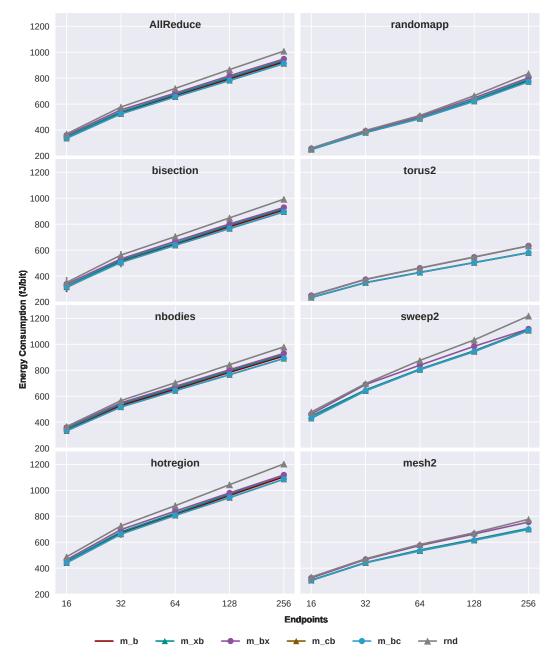

| 5.8  | Execution time relative to <i>rnd</i> for all strategies                                                                                               | 131 |

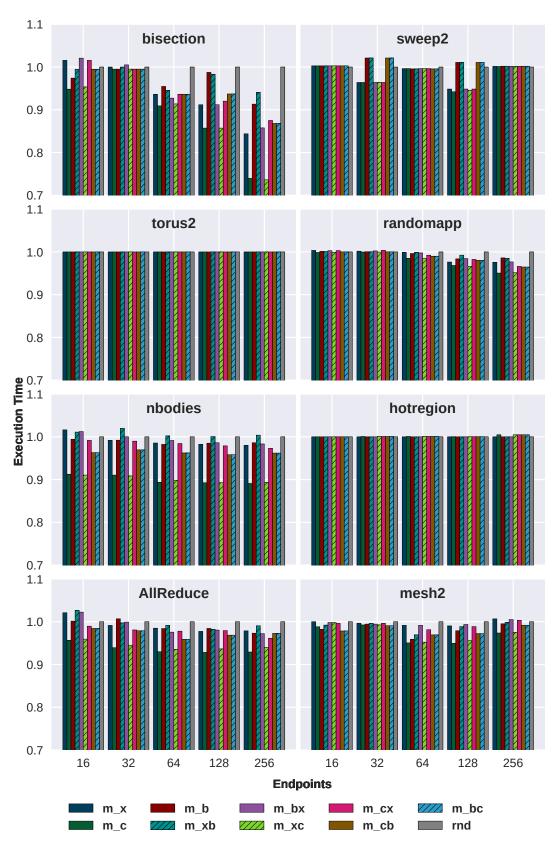

| 5.9  | Required power per laser. Left: conservative modulator. Right: ag-                                                                                     |     |

|      | gressive modulator.                                                                                                                                    | 133 |

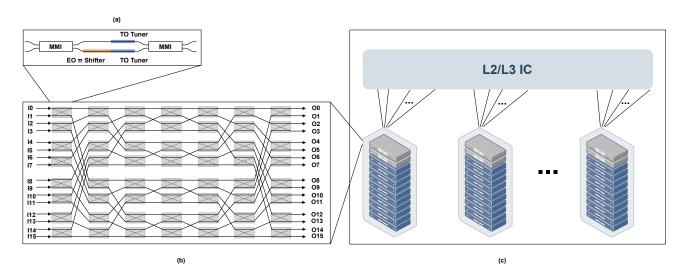

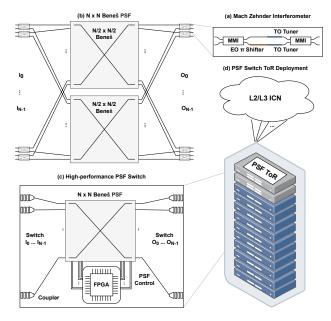

| 6.1  | (a) Schematic of a $2 \times 2$ EO/TO MZI Switch. (b) A Beneš-based ToR        |     |

|------|--------------------------------------------------------------------------------|-----|

|      | switch formed with MZI switches (c) A hypothetical photonic inter-             |     |

|      | connect with photonic ToR switches.                                            | 139 |

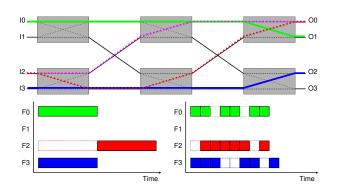

| 6.2  | Example of switch fabric contention in a small $4 \times 4$ Beneš network      |     |

|      | and communication timeline using CS and TDM                                    | 141 |

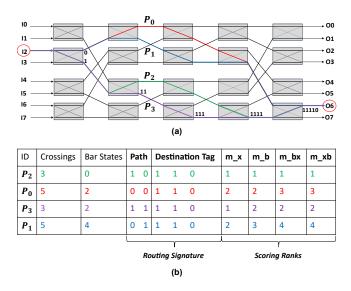

| 6.3  | Depiction of path diversity and routing signatures in an $8 \times$ Beneš net- |     |

|      | work                                                                           | 141 |

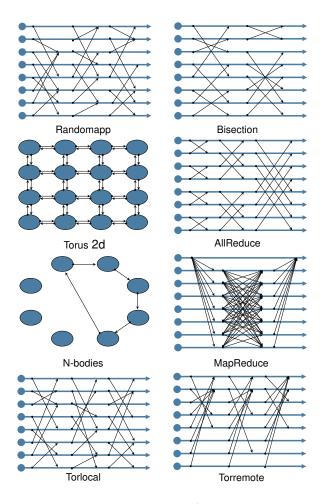

| 6.4  | Schematic representation of the eight workloads used                           | 143 |

| 6.5  | Percentage of flows that suffer switch fabric contention                       | 144 |

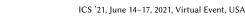

| 6.6  | Normalised communication time for CS and TDM                                   | 145 |

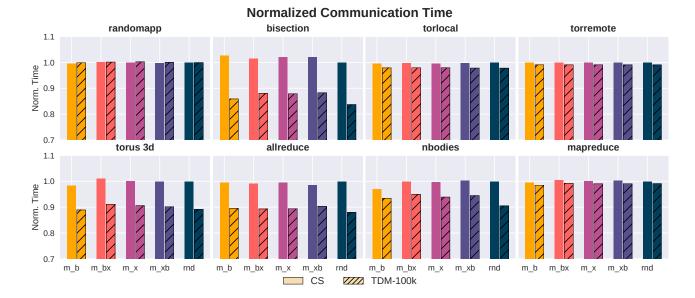

| 6.7  | Normalized communication time for various flow segment sizes                   | 146 |

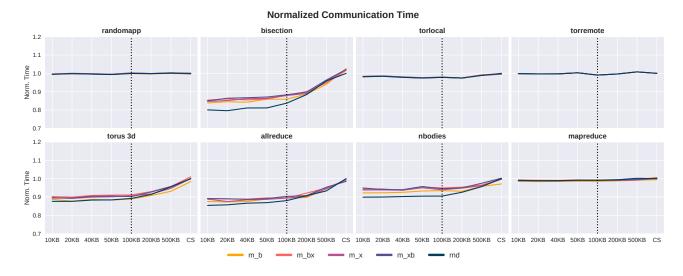

| 6.8  | Worst-case exhibited ILoss for circuit-switching and TDM                       | 147 |

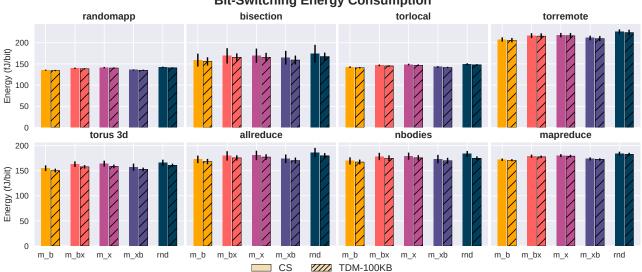

| 6.9  | Bit-switching energy consumption for circuit-switching and TDM                 | 148 |

| 7.1  | (a) Schematic of a 2 × 2 EO/TO MZI switching element. (b) An $N \times N$      |     |

|      | MZI Beneš PSF. (c) A high-performance switch containing the FPGA-              |     |

|      | controlled PSF. (d) Deployed ToR switch within a DC or HPC rack. $\$ .         | 153 |

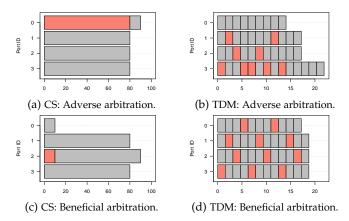

| 7.2  | Example of switch fabric contention in a $4 \times 4$ Beneš network            | 153 |

| 7.3  | xamples of beneficial and detrimental flow scheduling in CS (left) and         |     |

|      | TDM (right) with a 4-port Beneš switch.                                        | 153 |

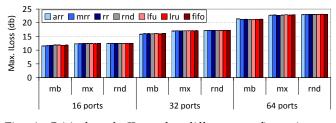

| 7.4  | Critical path ILoss for different configurations –Routing Algorithms .         | 158 |

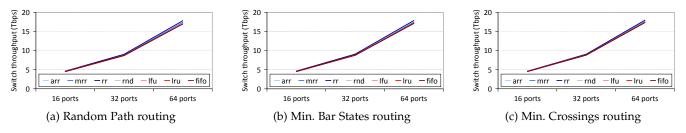

| 7.5  | Aggregated switch bandwidth with uniform traffic                               | 159 |

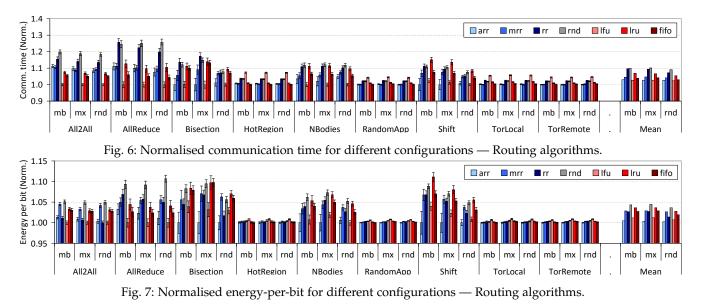

| 7.6  | Normalised communication time for different configurations — Rout-             |     |

|      | ing algorithms                                                                 | 159 |

| 7.7  | Normalised energy-per-bit for different configurations — Routing al-           |     |

|      | gorithms.                                                                      | 159 |

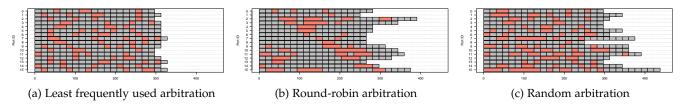

| 7.8  | Timeline of All2All with Random routing. Time ( $\mu$ s) flows from left       |     |

|      | to right. Grey: transmitting. Red: blocked                                     | 160 |

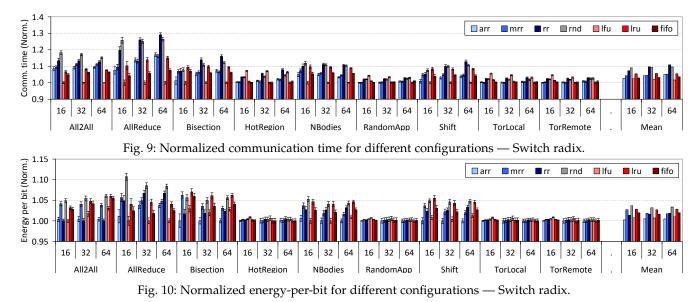

| 7.9  | Normalized communication time for different configurations — Switch            |     |

|      | radix                                                                          | 160 |

| 7.10 | Normalized energy-per-bit for different configurations — Switch radix.         | 160 |

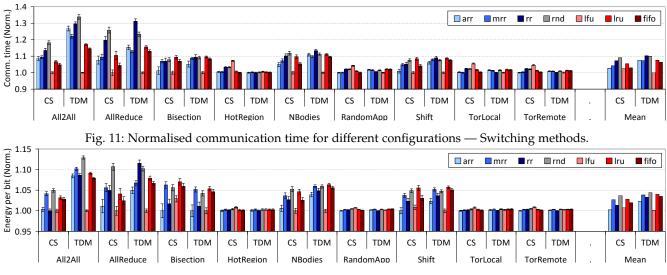

| 7.11 | Normalised communication time for different configurations - Switch-           |     |

|      | ing methods                                                                    | 161 |

| 7.12 | Normalised energy-per-bit for different configurations — Switching             |     |

|      | methods                                                                        | 161 |

### Abstract

### EXPLORING PHOTONIC BENEŠ SWITCHING FABRICS FOR FUTURE HPC AND DATACENTRES Markos Kynigos A thesis submitted to The University of Manchester for the degree of Doctor of Philosophy, 2022

Scalable photonic interconnection networks are highly desirable for both the High-Performance Computing (HPC) and the datacentre domains. Their potential energy efficiency and increased bandwidth capacity compared to networks based on electronics are the appeal. One of the main challenges in realising large-scale photonic interconnection networks is the adoption of network switches that can internally employ (1) high-port-count, and (2) fast, broadband photonic switching fabrics (PSFs). These fabrics are created by composing multiple stages of individual photonic devices which, when controlled with thermal or electrical tuning, can act as network switches.

Including PSFs at any level of the network still faces many obstacles, related both to photonic device design, and to control functionality for the switching fabric. This thesis contributes to the latter. It presents a simulation-based, network-traffic driven evaluation of PSFs, that are constructed using electrically/thermally tuned Mach-Zehnder Interferometers (MZIs), and formed using the Beneš network topology. These MZIs are broadband and fast switching, as they exhibit switching behaviour in *ns*-time across a continuous 30*nm* spectral segment. The Beneš topology requires the fewest MZIs, thereby reducing the PSF control complexity and increasing the photonic performance. Furthermore, the thesis enables simulating the deployment of such switching fabrics in the context of future HPC systems and datacentres.

First, the thesis discusses the main concepts enabling photonic communication, as well as the state-of-the-art in PSFs, and outlines the design challenges related to photonic switching.

It then describes a simulation-driven methodology for evaluating the relationship among communication traffic configuration, PSF-internal routing algorithm and photonic performance for a given PSF. The methodology is evaluated by simulating two state-of-the-art PSFs selected from the literature, and comparing with their reported performance. The simulation accuracy is established against the published data (insertion loss within 0.05 dB, photonic crosstalk within 3 dB).

The thesis then proposes the concept of "Hardware-Inspired Routing strategies" (HIRs), which are a collection of routing algorithms for the studied PSFs. They leverage both the state-based asymmetry in device photonic performance and the path-based asymmetry offered by the switch fabric topology, to reduce photonic losses and switching energy-per-bit when using Circuit Switching (CS). Depending on the communication traffic configuration, the two best HIRs can be effective at reducing the photonic losses which compose the combined photonic power penalty. The power penalty determines the required signal power for the PSF and therefore the energy efficiency. Compared to the state-of-the-art "Looping Algorithm," the HIRs can reduce the photonic power penalty by  $\sim 15 - 20\%$  on average and by  $\sim 19 - 15\%$  in the worst case as the PSF size increases. When considering an on-chip deployment scenario, this can lead to laser power savings between  $\sim 20 - 77\%$  on average and  $\sim 24 - 42\%$  in the worst case.

It then proposes augmenting the HIRs with Time-Division Multiplexing (TDM), and investigates deploying a 16  $\times$  16 PSF, which is selected from the literature, within a top-of-rack switch. When using TDM, flows are partitioned into equal-sized segments, which are then interleaved by the PSF controller to reduce the timing penalty of switch fabric contention incurred by CS. The simulations show that when employing TDM, communication time within the PSF can be reduced by up to  $\sim$  20% compared to CS, depending on the employed workload, while not affecting insertion loss or switching energy per bit.

The thesis concludes by investigating the joint impact of traffic arbitration policy, PSF-internal routing algorithm and workload on the switch performance (insertion loss, communication time within the PSF, switching energy per bit). The results indicate that communication time is affected the most by the arbitration policy with differences generally at ~ 10% and, in some extreme cases, over 30%. Switching energy per bit is affected less significantly, with differences around ~ 4 - 5% (at most 15%), while insertion loss is negligibly affected. These indicate that arbitration in these PSFs could be designed independently from routing. The least-frequently used policy was found to be the best overall and particularly with regular workloads, in which tasks progress at the same pace, with clear communication phases of fixed size. In these, the communication time is reduced by the arbitration policy by ~ 30%, while in irregular workloads the communication time is increased due to the policy by ~ 6%. On the other hand, one of the novel policies proposed, accelerated round-robin, excels with irregular workloads; in these, tasks progress at a pace dictated by traffic causality.

## Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

## Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- ii. Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made **only** in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- iii. The ownership of certain Copyright, patents, designs, trade marks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http://documents.manchester.ac.uk/DocuInfo.aspx? DocID=24420), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see http://www.library. manchester.ac.uk/about/regulations/) and in The University's policy on presentation of Theses

## Acknowledgements

First and foremost, I thank my mother and father, who offered me every opportunity under the sun. Your nurture and ongoing support thereafter have helped me become the person I am today. Thank you both for teaching me how to think critically, to behave with integrity, to interact with empathy and, most importantly, to persevere. Special thanks also to my brother, David, whose supportive words helped me throughout this journey. We may be far apart in distance, but never in spirit.

I also thank my supervisors. Dr. Javier Navaridas, even during the adversity of the pandemic, offered me continuous support and direction. I thank you for your dedication, for uncounted hours of discussion, for teaching me how to become a researcher and for constantly encouraging me to push myself and grow. Prof. Mikel Luján, who stepped in as main supervisor in the middle of my PhD, supported me throughout. I thank you for your reviews of my work, your assistance in focusing it and your support with with the submission.

Many thanks also to Jose Pascual for his technical assistance and long discussions, which significantly helped with the direction of my thesis.

I thank Prof. Keren Bergman from the Lightwave Research Lab at Columbia University, for enabling me to collaborate with her team, as well as Richard Dai and Kristoff Yan, whose discussions greatly improved my understanding on the physical layer of silicon photonics.

I thank everyone from the APT group for making it a great place to pursue research and for their support and friendship, both in and outside of the university. Special thanks to Nikos Kyparissas, Konstantinos Iordanou and Kyriakos Paraskevas for their help in reviewing chapters of the thesis and, of course, Luca Perez, for the coffee breaks which kept us sane during the final semester.

Last but in no way least, I thank my partner, Katerina, for her never-ending support. I thank you for sharing my successes and failures, for being there for me every single day and through every adversity. You are extraordinary and I hope to be as steadfast when you submit your thesis.

## Acronyms

#### Arrayed Waveguide Grating Coupler (AWGR)

A passive photonic device used to interconnect multiple endpoints.

#### **Bit-error Rate (BER)**

The number of bit errors per unit time, where bit errors are received bits which have been altered due to noise, interference, distortion or synchronisation errors.

#### **Circuit Switching (CS)**

A switching technique which allocates the entire set of required resources to the transmitted traffic for the required time of transmission, and blocks requests for allocated resources.

#### **Coarse Wavelength-division Multiplexing (CWDM)**

A form of wavelength division multiplexing which employs few wavelengths (less than 8), differing significantly in frequency.

#### Complementary metal-oxide-semiconductor (CMOS)

A family of processes used to fabricate integrated circuits.

#### Datacentre (DC)

A facility which is composed of interconnected compute, storage and network infrastructure, with the purpose of delivering shared applications and data.

#### **Datacentre Network (DCN)**

An interconnection network used to connect compute and storage machines within a datacentre.

#### Dense wavelength-division Multiplexing (DWDM)

A form of wavelength-division multiplexing, in which the employed wavelength channels align to a standardized frequency grid.

#### **Electro-optic (EO)**

Used to refer to electro-optic tuning, which employs the free-carrier dispersion effect to induce phase change or resonance.

#### **Electro-Optically tuned Mach-Zehnder Interferometer (EOMZI)**

A Mach-Zehnder Interferometer that employs electro-optical tuning to change state.

#### Hardrare-Inspired Routing Strategies (HIRs)

A set of path-wise routing strategies which select paths through switches based on the properties or state of the underlying traversed photonic medium.

#### **High-Performance Computer (HPC)**

A special-purpose computer composed of multiple servers, connected using an interconnection network.

#### **Insertion Loss (ILoss)**

Power attenuation incurred by the photonic carrier as it traverses a photonic medium.

#### **Interconnect (IC)**

Used to describe a communication link (e.g. copper or fibre cable, waveguide) that connects compute or memory resources to each other.

#### Mach-Zehnder Interferometer (MZI)

A photonic device consisting of two inputs and two outputs, which can be used as a switching cell.

#### **Microring Resonator (MRR)**

A photonic device formed using a circular silicon waveguide structure, used to change the propagation direction of traversing light, based on resonance mechanics.

#### Acronyms

#### Multi-mode Interferometer (MMI)

A photonic device with two inputs and two outputs, which can be used as a coupler within switching devices or as a waveguide crossing.

#### **Multipath Interference (MPI)**

Refers to a type of crosstalk, which is generated by delayed versions of a photonic signal leaked through multiple physical paths through a photonic medium.

#### Network-on-Chip (NoC)

A network which interconnects multiple chip components.

#### Non-Return-to-Zero (NRZ)

A binary line code in which ones are represented by one significant condition and zeroes by some other significant condition, with no other neutral or rest condition.

#### **On-Off Keying (OOK)**

A modulation scheme which represents digital data as the presence or absence of a carrier wave.

#### **Optical Interconnection Network (OIN)**

An interconnection network which employs optical links and electronic switches.

#### **Optical Network-on-Chip (ONoC)**

An optical network which interconnects multiple chip components.

#### **Photonic Integrated Circuit (PIC)**

An integrated circuit containing at least two optical devices.

#### **Photonic Interconnection Network (PIN)**

An interconnection network in which traffic does not suffer electro-optic or optoelectric conversion in intermediate network nodes.

#### **Photonic Switching Fabric (PSF)**

A collection of active photonic devices tiled and interconnected by passive photonic devices, with the purpose of performing switching functionality.

#### Rearrangeably non-blocking (RNB)

A network topology which can route arbitrary input-output connection permutations, but incremental route allocation may cause some pre-allocated connections to require rerouting.

#### Return-to-Zero On-Off Keying (RZ-OOK)

On-off keying modulation using a return-to-zero binary line code.

#### Signal-to-Noise Ratio (OSNR)

The measure of the ratio of signal power to noise power in an optical channel.

#### Silicon Photonics (SiPh)

A material platform which uses silicon-on-insulator, from which photonic integrated circuits can be made.

#### Space Division Multiplexing (SDM)

A multiplexing technique for optical data transmission where multiple spatial channels are utilized.

#### Strictly non-blocking (SNB)

A network topology in which the connections of any input-output permutation can be allocated incrementally, without rerouting pre-allocated connections.

#### Switching Element (SE)

A device that performs switching.

#### Thermo-optic (TO)

Used to refer to thermo-optic tuning, with which the refractive index of a waveguide is modified to induce a phase change or resonance.

#### **Time-Division Multiplexing (TDM)**

A communication channel sharing technique, in which the channel capacity is partitioned into time-slots, with competing traffic being transmitted using interleaving.

#### Acronyms

#### Top-of-Rack (ToR)

Used to refer to a switch, a Top-of-Rack switch connects in-rack servers to the interconnection network.

#### Vertical Cavity Surface-emitting Laser (VCSEL)

A type of laser.

#### Wavelength-division Multiplexing (WDM)

A multiplexing technique through which a data stream is split and encoded on multiple wavelengths traversing the same photonic medium.

## Chapter 1

## Introduction

### **1.1 Motivation**

The field of High-Performance Computing (HPC) is transitioning into the "exa-scale" era, in which large-scale, special-purpose computers have the ability to reach peak performances of  $\geq 1$  *EFLOPS*. The Fugaku supercomputer [Don20], deployed in 2020, Japan, is currently the most powerful HPC system and can achieve ~ 415 *PFLOPS* peak performance, while the United States of America aims to deploy two exa-scale HPC systems, Frontier and Aurora, by 2023 [(OL21, SRM<sup>+</sup>19].

HPC systems rely on massive parallelism, enabled by high-performance interconnection networks, to distribute compute tasks to the system nodes and to communicate data among them. Performance tends to be reported using benchmark applications, such as LINPACK [DLP03], which is a computation-heavy workload, or HPCG [DHL16], which stresses the communication to memory and, to an extent, the interconnection network. The performance of Fugaku under the LINPACK benchmark is 80.9% of peak performance; however, its performance under the HPCG benchmark is 2.8% of the peak. While this is still the best performance for HPCG globally, the mismatch in performance between the two benchmarks highlights the growing gap in resource provision between computation and communication capability in current HPC systems [Ber21]. This occurs due to the increasing cost and power consumption of the interconnection network. As HPC performance becomes increasingly dependent on data communication efficiency, it is expected that future highperformance interconnects will require a paradigm shift in order to meet communication demands [RNH<sup>+</sup>15].

At the same time, the data centre world has transitioned into the "Zettabyte era",

#### 1.1. MOTIVATION

Figure 1.1: A qualitative comparison of the price and cost increases associated with improving pluggable optics. Image copied from [SZC<sup>+</sup>21].

in which large-scale Data Centres (DCs) are tasked with serving ever-growing Internet Protocol (IP) traffic, which has already surpassed 2 *Zettabytes/year* [Net17]. This demand, driven by both increasing video traffic and use of AI, is substantially increasing the power consumption of data centres. In spite of significant advances in DC energy efficiency, they are projected to consume between 3 - 13% of global power production by the year 2030 [AE15, GKL<sup>+</sup>21].

In spite of their differences, both HPCs and DCs rely on interconnection networks, which are composed of copper or optical links, and electronic packet routers and switches. In both cases, the number of employed switches grows with the scale of the system, and therefore the power consumption for switches increases. In addition, optical cables are being used more frequently, as the demand for more bandwidth within HPCs and DCs increases. Pluggable optical cables, however, are costly and further increase power consumption [SZC<sup>+</sup>21]; this is depicted in Fig. 1.1, which qualitatively shows the price and power consumption increase when improving the capabilities of current pluggable optical cables. Communicating data must be transformed from the electrical domain, where the data is switched at every hop within electronic packet switches, to the optical domain for transmission and vice versa (O/E/O conversion),

a process which consumes power and prohibits scaling. This in turn enforces a dependency between electronic switches and pluggable optics; switches must either be upgraded at every optical cable data rate generation to support new transceivers, which perform O/E/O conversion, or transceivers must be constrained by legacy capabilities.

Augmenting interconnection networks by employing photonic switches is considered a highly promising approach for surmounting many of the challenges examined above [NRC<sup>+</sup>15]. On one hand, this could reduce the dependency on pluggable optics and therefore O/E/O conversions. On the other hand, recently demonstrated photonic switches employing Silicon Photonics technology (SiPh) can be highly power efficient, thereby reducing the power consumption of the interconnection network. SiPh devices, most notably Microring Resonators (MRRs) and Mach-Zehnder Interferometers (MZIs) are capable of switching multiple wavelengths simultaneously in the  $\mu s - ns$  scale, thereby allowing for data rate scaling using Dense-wavelength-Division Multiplexing (DWDM), and can be cascaded to form photonic switching fabrics, thereby increasing the port count. These switching fabrics can then be used to either augment current interconnection networks by providing efficiency through new capabilities (e.g. bandwidth steering [MST<sup>+</sup>19]), or to potentially replace some electronic packet switches, thereby forming hybrid electronic/photonic interconnection networks [FPR<sup>+</sup>10].

However, many challenges still exist in using photonic switching fabrics within high-performance network switches, such that they can compete with standard electronic packet switches. The lack of practical data buffering in the optical domain makes packet switching challenging, necessitating the use of circuit switching at the transmission level. This in turn affects the complexity of the switching fabric controller and routing algorithm internal to the switch, which is responsible for providing uninterrupted lightpaths from a source to a destination port. At the same time, optical losses which are inherent to the device technology, namely insertion loss and photonic crosstalk, limit the scalability of switching fabrics [DL17].

This thesis examines the challenges outlined above, in the context of rearrangeablynon-blocking photonic switching fabrics formed with MZIs. In addition, it improves on the state-of-the-art by proposing a set of routing techniques which can be used to optimise the photonic power penalty, while not prohibitively increasing switch controller complexity.

### **1.2 Thesis Contributions**

This thesis examines the potential of photonic switching fabrics formed with thermally/electrically tuned MZIs using the Beneš network topology, for their deployment in future HPCs and datacenters. The **research question** that is addressed by this thesis comprises of the following components:

- 1. What are the limitations of these photonic switching fabrics in terms of scalability, photonic metrics (insertion loss, photonic crosstalk, power budget and required signal power) and performance, that is communication time?

- 2. Can the properties of the adopted topology and underlying technology be leveraged by intra-switch routing algorithms to reduce the photonic power penalty, switching energy, signal power and therefore required laser power? As required laser power is the main limitation in scalability, can the use of these routing algorithms reduce required signal power enough for larger switching fabrics to become realistic?

- 3. What is the impact of network traffic configuration on photonic metrics (insertion loss, optical crosstalk, photonic power penalty, signal power, switching energy) and performance metrics (blocking in the form of contention, communication time)? How is this impact affected by routing algorithm selection?

- 4. How does the performance of the proposed routing algorithms evolve with the network size, with respect to the metrics under consideration?

- 5. The routing algorithms proposed to optimise for photonic metrics introduce blocking in the form of contention in the switch, thereby decreasing the performance of the fabric. Can time-division multiplexing ameliorate the performance degradation? To what degree and under which traffic conditions?

To address the research question, this thesis makes the following **contributions**:

It proposes a methodology and tool for evaluating the interactions between network traffic configuration, internal routing algorithm selection and photonic metrics (exhibited insertion loss, photonic crosstalk, signal power). To the best of the author's knowledge, the use of network traffic-driven simulation consisting of causality-enabled traffic models as a tool for evaluating the performance of photonic switching fabrics, and assessing the above interactions has not been previously investigated. The methodology, as well as the simulation framework that has been developed to support it, are described in Chapter 3. The methodology's use is involved in addressing all the components of the research question.

- 2. It contributes to the state-of-the-art in routing algorithms for the internals of photonic Beneš switching fabrics based on thermally/electrically tuned MZIs by proposing a set of circuit-switched Hardware-Inspired Routing strategies (HIRs). These routing strategies leverage the inherent asymmetry in the state-based insertion loss, crosstalk and tuning energy of this type of MZI to provide loss-optimised paths inside the switching fabric. This contribution comprises of the following parts:

- (a) The first part consists of the routing strategies discussed in Chapter 4. Each routing strategy proposed here optimises against a single criterion, namely minimizing the number of waveguide crossings, minimizing the number of required state changes, and minimizing the number of MZIs in the "bar" state. The *rnd* strategy, which randomly selects a potential path, also belongs here.

- (b) The second part consists of the hybridised routing strategies proposed in Chapter 5. These routing strategies combine the optimisation criteria used in the previous to elicit further improvements in the considered metrics.

Compared to the state-of-the-art Looping algorithm [Ben64], most HIRs show significant reductions on signal power, aggregate crosstalk, insertion loss and switching energy exhibited per flow, both on average and in the worst case. This contribution, discussed in Chapters 3-5, addresses the second and third components of the research question. It also address the fourth component, by focusing on insertion loss, switching energy and communication time for Chapters 4 & 5. It is noted that the latter two chapters do not focus on photonic crosstalk, as the crosstalk model was developed after the finalisation of the publications they contain.

3. The proposed HIRs introduce a trade-off, as they select loss-optimised paths by sacrificing the non-blocking characteristics of the Beneš network, thereby introducing contention in the fabric. To address this, the third contribution of this thesis is the augmentation of HIRs with time-division multiplexing (TDM), rather than circuit switching. Circuit switching and TDM are defined in Sections 2.4.2 and 2.4.3, while their application to the PSF is detailed in Chapter 6. The contributed technique ameliorates the effects of contention while maintaining the insertion loss savings of the HIRs. This approach is evaluated using the proposed methodology and considering a  $16 \times 16$  Beneš switching fabric deployed at the top-of-rack level. The findings show that employing TDM can reduce communication time by up to 20% in the best case compared to CS, thereby decreasing the impact of contention, while having minimal impact on the exhibited critical path insertion loss (~ 0.5*dB* increase) and average required switching energy (~ 5% decrease). A trade-off analysis is also performed with respect to TDM segment size, finding that it can be increased tenfold with negligible performance impact, thereby reducing constraints in path computation time. This contribution addresses the fifth component of the research question.

In addition to the above, the thesis includes an investigation on the role of arbitration algorithms in the control of the photonic switching fabrics under investigation. This investigation has been submitted for publication in the Journal of Optical Communication Networks (JOCN). The thesis author has contributed to this research article by co-authoring the paper, in particular sections 1-4 of the paper, as well as providing assistance for the simulation experiments contained in the work and their analysis. The domain investigated in the article is an evolution of the thematics of this thesis and is based on the methodology proposed as a thesis contribution. However, as the thesis author did not develop the arbitration algorithms examined in the article, it is not considered to be within the thesis authors' contributions and is therefore not included above.

### **1.3** Publications

As this thesis is organized in the journal format, the majority of the contained work has either been published or submitted as the following research articles: