School of Engineering and the Built Environment

## Hardware Architectures for Infrared Pedestrian Detection Systems

by

Robert Walczyk

A thesis submitted in partial fulfilment of the requirements of Edinburgh Napier University, for the award of Doctor of Philosophy

May 2013

$Contact: \ r.walczyk@napier.ac.uk$

This document was set with the help of  $\mathsf{KOMA}\text{-}\mathsf{Script}$  and  $\texttt{I}^{\!\!A}T_{\!\!E}\!X$

## Abstract

Infrared pedestrian detection systems struggle with real-time processing performance. Known solutions are limited to either low resolution systems with basic functionality running at full frame rate, or software based techniques featuring higher detection rates with full set of features, however running only in off-line mode for statistical analysis. Here, a comprehensive solution for real-time pedestrian detection is described.

This research project includes investigation of possible solutions, design, development and implementation of a pedestrian detection system, processing data from infrared video source in real-time. Design requirements include processing at full frame rate as well as low memory and system resource consumption. The memory utilization is one of the major concerns since high demand for memory resources is a critical aspect in most image processing applications.

For the purpose of this task, a number of general purpose image processing techniques were revised, taking into consideration the suitability for infrared pedestrian detection. These tasks include background separation, acquisition noise removal and object detection through connected component labelling. They are discussed and addressed in individual chapters.

Various techniques for background segmentation are discussed. A chronological review of popular techniques is provided. The proposed architecture for background subtraction is based on selective running average for adaptive background model, supported by adaptive thresholding based on histogram calculation. In order to remove acquisition noise, a dual decomposed architecture was introduced, based on mathematical morphology and basic set theory definitions. It includes both erosion and dilation performed in a pipeline. For the purpose of object detection and feature extraction, a connected component labelling technique was employed, based on a single pass approach to fulfil real-time processing requirement.

The system was implemented, verified and tested on XUP FPGA Development Board with Virtex-II Pro XC2VP30 chip from Xilinx. Details and limitation of the specific implementation are discussed. An overview of experimental pedestrian detection results is provided. The thesis concludes with system analysis and suggestions for future work.

## Acknowledgements

I would like to express my gratitude to all the people who have contributed towards this research or completion of this thesis. In particular, I would like to give thanks to the following:

To my university supervisors Dr T. David Binnie and Dr Alistair Armitage. For your advice and continued encouragement throughout this research. I appreciate your feedback and value the time you have spent on reading and correcting this thesis.

To my line manager from Cambridge Silicon Radio, Dr Tim Clapp, for generous study-leave allowance and flexible working hours during last months of my study.

To Stefan Maagh for valuable advice and effort when creating this thesis template.

To Piotr Wojtczuk for your contribution to this project in various aspects. Also, for our long night FPGA-whisky sessions, which I consider to be one of best experiences during my academic years.

To Alexander Balazs, for your contribution while working on the implementation of tracking algorithms on embedded processor core. It was a great experience for me to act as a teacher and supervisor. I am glad this cooperation was concluded with joint research paper presented at the 2011 IET Irish Signals and Systems Conference (ISSC 2011) in Dublin.

To my family, including my parents and sister in law - Krystyna, Janusz and Karolina Kołodziejczak, for your continuous support.

To my mother and father Lucyna and Waldemar, for your effort into my life-long education. I hope, after all these years, you can be proud of me.

Special thanks to my wife Ania and our little baby girl Zosia. This research project has affected your life as much as mine. I believe only you know how much effort I have made towards the completion of this thesis. There is no words to express my gratitude for your support, understanding and patience.

Robert Walczyk

I acknowledge that some of the work presented in this thesis has been presented or published at or in the following places:

[1] R. Walczyk, A. Balazs, A. Armitage, T.D. Binnie, "System architectures for infrared pedestrian tracking," in: *IET Irish Signals and Systems Conference (ISSC 2011)*, June 2011, Dublin, Ireland

[2] R. Walczyk, A. Armitage, T.D. Binnie, "Comparative Study on Connected Component Labeling Algorithms for Embedded Video Processing Systems," in: *Proceedings of the International Conference on Image Processing, Computer Vision, and Pattern Recognition (IPCV'10)*, July 2010, Las Vegas, NV, USA

[3] R. Walczyk, A. Armitage, T.D. Binnie, "FPGA Implementation of Hot Spot Detection in Infrared Video," in: *IET Irish Signals and Systems Conference (ISSC 2010)*, June 2010, Cork, Ireland

[4] R. Walczyk, A. Armitage, T.D. Binnie, "FPGA Implementation of Pedestrian Detection System using Infrared Image Sequences," in: *Faculty of Engineering & Computing Postgraduate Research Conference (FECCI 2010)*, May 2010, Edinburgh, UK

[5] R. Walczyk, A. Armitage, T.D. Binnie, "An Embedded Real-Time Pedestrian Detection System Using an Infrared Camera," in: *IET Irish Signals and Systems Conference (ISSC 2009)*, June 2009, Dublin, Ireland

# Contents

|   | Abs  | stract   |                                            | iii            |

|---|------|----------|--------------------------------------------|----------------|

|   | Ack  | nowle    | dgements                                   | iv             |

|   | List | t of Fig | gures                                      | x              |

|   | List | of Ta    | bles                                       | xiii           |

|   | List | t of Ab  | obreviations                               | $\mathbf{xiv}$ |

| 1 | Inti | roduct   | ion                                        | 16             |

|   | 1.1  | Motiva   | ation                                      | 17             |

|   | 1.2  | Resear   | rch Objective                              | 18             |

|   | 1.3  | Contri   | ibution to Knowledge                       | 19             |

|   | 1.4  | Outlin   | ne of the Thesis                           | 19             |

| 2 | Ima  | age Pro  | ocessing for Infrared Pedestrian Detection | <b>21</b>      |

|   | 2.1  | Infrare  | ed Detectors                               | 22             |

|   |      | 2.1.1    | Infrared Radiation                         | 22             |

|   |      | 2.1.2    | Thermal Sensors                            | 23             |

|   |      | 2.1.3    | Thermographic Cameras                      | 24             |

|   |      | 2.1.4    | Applications                               | 25             |

|   | 2.2  | Digita   | l Image Processing                         | 25             |

|   |      | 2.2.1    | Digital Image                              | 26             |

|   |      | 2.2.2    | Raster Scan                                | 27             |

|   |      | 2.2.3    | Pixel Neighbourhood                        | 27             |

|   |      | 2.2.4    | Pixel Connectivity                         | 28             |

|   |      | 2.2.5    | Connected Components                       | 28             |

|   |      | 2.2.6    | Scan Mask                                  | 29             |

|   |      | 2.2.7    | Labelling                                  | 30             |

|   |      | 2.2.8    | Run Length Encoding (RLE)                  | 30             |

|          | 2.3               | Hardw  | vare Development and Implementation                                                                                                         |

|----------|-------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------|

|          |                   | 2.3.1  | Processing Unit                                                                                                                             |

|          |                   | 2.3.2  | Design Flow                                                                                                                                 |

|          |                   | 2.3.3  | Development Platform                                                                                                                        |

|          | 2.4               | Pedest | trian Detection                                                                                                                             |

|          |                   | 2.4.1  | Segmentation                                                                                                                                |

|          |                   | 2.4.2  | Object detection                                                                                                                            |

|          |                   | 2.4.3  | Classification and Tracking                                                                                                                 |

|          | 2.5               | Conclu | usions $\ldots \ldots 40$                        |

| <b>0</b> | р.                | 1      | 1.0                                                                                                                                         |

| 3        | <b>Вас</b><br>3.1 | 0      | nd Segmentation       41         uction       41                                                                                            |

|          |                   |        |                                                                                                                                             |

|          | 3.2               |        |                                                                                                                                             |

|          |                   | 3.2.1  | v 0                                                                                                                                         |

|          |                   | 3.2.2  | Temporal Difference   46                                                                                                                    |

|          |                   | 3.2.3  | Background Modelling                                                                                                                        |

|          | 3.3               | -      | thm Overview                                                                                                                                |

|          |                   | 3.3.1  | Background Modelling                                                                                                                        |

|          |                   | 3.3.2  | Histogram Calculation                                                                                                                       |

|          |                   | 3.3.3  | Feedback Loop Control   58                                                                                                                  |

|          | 2.4               | 3.3.4  | Algorithm Pseudo Code    60                                                                                                                 |

|          | 3.4               |        | vare Implementation                                                                                                                         |

|          |                   | 3.4.1  | Architecture                                                                                                                                |

|          | 3.5               | Conclu | usions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $64$                                                                                             |

| <b>4</b> | Mo                | rpholo | gy Filtering 67                                                                                                                             |

|          | 4.1               | Introd | Luction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $68$                                                        |

|          | 4.2               | Mathe  | ematical Morphology                                                                                                                         |

|          |                   | 4.2.1  | Set Theory                                                                                                                                  |

|          |                   | 4.2.2  | Structuring Element                                                                                                                         |

|          |                   | 4.2.3  | Erosion  .  .  .  .  .  .  .  .  .                                                                                                          |

|          |                   | 4.2.4  | Dilation $\ldots \ldots 72$ |

|          |                   | 4.2.5  | Opening and Closing                                                                                                                         |

|          |                   | 4.2.6  | Duality                                                                                                                                     |

|          |                   | 4.2.7  | Decomposition                                                                                                                               |

|          |                   | 4.2.8  | Summary                                                                                                                                     |

|          | 4.3               | Implei | mentation $\ldots \ldots .$                      |

|          |                   | 4.3.1  | Introduction                                                                                                                                |

|          |                   | 4.3.1  | Introduction                                                                                                                                |

|   |     | 4.3.2  | Previous Work                                                                                                                                     |

|---|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|   |     | 4.3.3  | System Requirements                                                                                                                               |

|   |     | 4.3.4  | Architecture                                                                                                                                      |

|   |     | 4.3.5  | Module Instantiation                                                                                                                              |

|   |     | 4.3.6  | Results and Performance                                                                                                                           |

|   | 4.4 | Concl  | usions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $91$                                                                                                   |

| 5 | Со  | nnecte | d Component Labelling 94                                                                                                                          |

|   | 5.1 |        | luction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $35$                                                                                                  |

|   |     | 5.1.1  | Labelling                                                                                                                                         |

|   |     | 5.1.2  | Label Collision                                                                                                                                   |

|   |     | 5.1.3  | Feature Extraction                                                                                                                                |

|   | 5.2 | Litera | ture Review                                                                                                                                       |

|   |     | 5.2.1  | Labelling Algorithms                                                                                                                              |

|   |     | 5.2.2  | Summary                                                                                                                                           |

|   | 5.3 | Algori | ithm Analysis $\ldots \ldots 102$ |

|   |     | 5.3.1  | Classical Algorithm                                                                                                                               |

|   |     | 5.3.2  | Contour Tracing Algorithm                                                                                                                         |

|   |     | 5.3.3  | Single Pass Algorithm                                                                                                                             |

|   |     | 5.3.4  | $Conclusions \dots \dots$                   |

|   | 5.4 | Imple  | mentation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $111$                                                           |

|   |     | 5.4.1  | Introduction                                                                                                                                      |

|   |     | 5.4.2  | Single Pass Algorithm                                                                                                                             |

|   |     | 5.4.3  | Architecture                                                                                                                                      |

|   |     | 5.4.4  | Module Instantiation                                                                                                                              |

|   |     | 5.4.5  | Results and Performance                                                                                                                           |

|   | 5.5 | Concl  | usions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $128$                                                                                                  |

|   |     |        |                                                                                                                                                   |

| 6 | v   |        | ntegration 130                                                                                                                                    |

|   | 6.1 |        | opment Platform Overview 131                                                                                                                      |

|   |     | 6.1.1  | XUP V2P Development Board131                                                                                                                      |

|   |     | 6.1.2  | FPGA Chip with Embedded PowerPC                                                                                                                   |

|   |     | 6.1.3  | Video Decoder 132                                                                                                                                 |

|   |     | 6.1.4  | System Peripherals                                                                                                                                |

|   |     | 6.1.5  | IR Camera                                                                                                                                         |

|   | 6.2 | Video  | Data Acquisition from IR Camera                                                                                                                   |

|   |     | 6.2.1  | Analogue to Digital Video Conversion                                                                                                              |

|   |     | 6.2.2  | PAL to Progressive Scan Conversion                                                                                                                |

|          |                                                                                         | 6.2.3                                                                            | Active Data Extraction                                             | 135                                                         |

|----------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------|

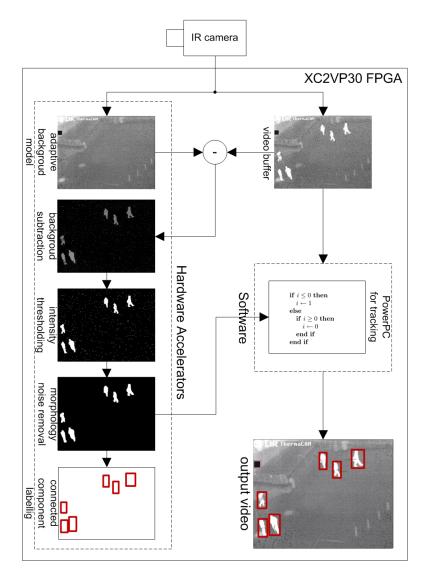

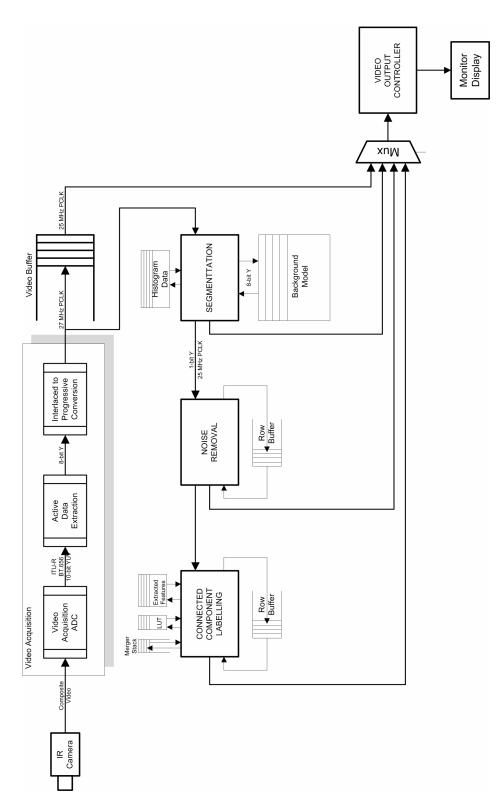

|          | 6.3                                                                                     | System                                                                           | n Architecture                                                     | 136                                                         |

|          |                                                                                         | 6.3.1                                                                            | Design Goals                                                       | 136                                                         |

|          |                                                                                         | 6.3.2                                                                            | Data Flow                                                          | 137                                                         |

|          |                                                                                         | 6.3.3                                                                            | Summary                                                            | 139                                                         |

|          |                                                                                         | 6.3.4                                                                            | Tracking on PowerPC                                                | 141                                                         |

|          |                                                                                         | 6.3.5                                                                            | Synthesis and Resource Utilization                                 | 141                                                         |

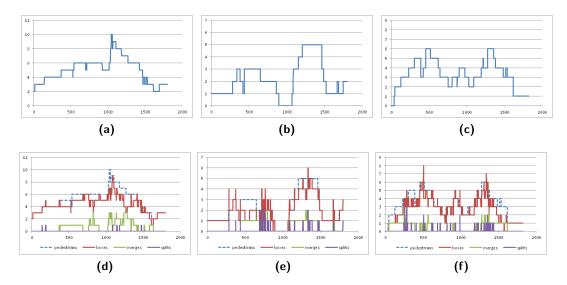

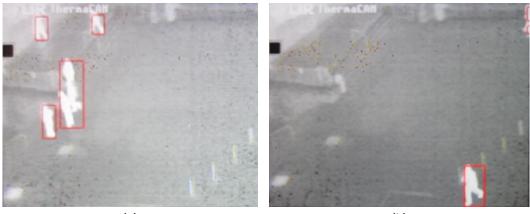

|          | 6.4                                                                                     | Exper                                                                            | imental Detection Results                                          | 144                                                         |

|          |                                                                                         | 6.4.1                                                                            | Performance Comparison                                             | 147                                                         |

|          | 6.5                                                                                     | Conclu                                                                           | usions                                                             | 148                                                         |

| -        | D.                                                                                      | .:                                                                               | Research and Conclusions                                           | 150                                                         |

| <b>7</b> | Rev                                                                                     | lew of                                                                           | Research and Conclusions                                           | 150                                                         |

| 7        | <b>Rev</b><br>7.1                                                                       |                                                                                  |                                                                    |                                                             |

| 7        |                                                                                         | Review                                                                           |                                                                    | 151                                                         |

| 7        | 7.1                                                                                     | Review<br>Conclu                                                                 | w of Research                                                      | 151<br>152                                                  |

| 7        | $7.1 \\ 7.2$                                                                            | Review<br>Conclu<br>System                                                       | w of Research                                                      | 151<br>152                                                  |

| 7        | <ol> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> </ol>                          | Review<br>Conclu<br>System                                                       | w of Research          usions          ns of Today          e Work | 151<br>152<br>155                                           |

|          | <ul><li>7.1</li><li>7.2</li><li>7.3</li><li>7.4</li><li>Ref</li></ul>                   | Review<br>Conclu<br>System<br>Future                                             | w of Research                                                      | 151<br>152<br>155<br>155                                    |

|          | <ul><li>7.1</li><li>7.2</li><li>7.3</li><li>7.4</li><li>Ref</li></ul>                   | Review<br>Concle<br>Syster<br>Future<br><b>Terence</b><br>Appen                  | w of Research                                                      | 151<br>152<br>155<br>155<br><b>157</b>                      |

|          | <ul> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>Ref</li> <li>An</li> </ul> | Review<br>Conclu<br>Syster<br>Future<br><b>čerence</b><br><b>Apper</b><br>Impler | w of Research                                                      | 151<br>152<br>155<br>155<br><b>157</b><br><b>169</b><br>169 |

# List of Figures

| 2.1  | The electromagnetic spectrum characterised by the wavelength $\lambda$ and the      |    |

|------|-------------------------------------------------------------------------------------|----|

|      | frequency $\nu$                                                                     | 22 |

| 2.2  | Example images taken by IR camera                                                   | 24 |

| 2.3  | An example image frame from IR video surveillance system                            | 25 |

| 2.4  | Digital image raster scan grid                                                      | 26 |

| 2.5  | Pixel neighbourhood                                                                 | 27 |

| 2.6  | Pixel connectivity                                                                  | 28 |

| 2.7  | Connected components labelled with 4 and 8-connectivity                             | 29 |

| 2.8  | Scan mask                                                                           | 29 |

| 2.9  | Run Length Encoding                                                                 | 30 |

| 2.10 | FPGA design flow                                                                    | 35 |

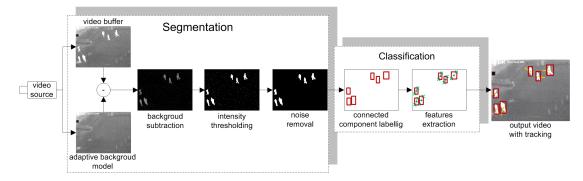

| 2.11 | A block diagram of the data flow for a conceptual surveillance system $\ . \ . \ .$ | 38 |

| 3.1  | A block diagram of the data flow for a conceptual surveillance system $\ . \ .$     | 43 |

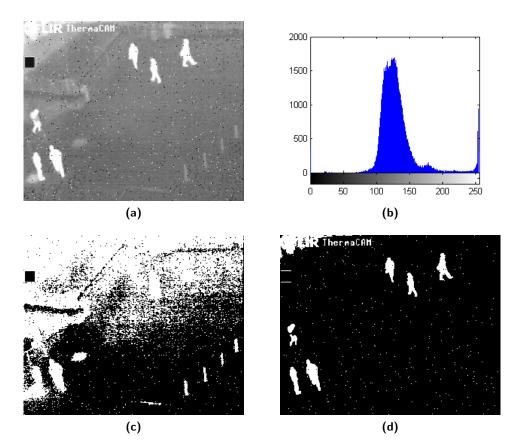

| 3.2  | Background segmentation based on intensity thresholding                             | 45 |

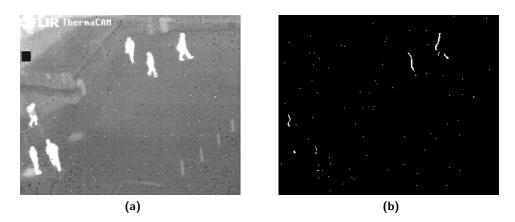

| 3.3  | An example of segmentation output using temporal difference                         | 47 |

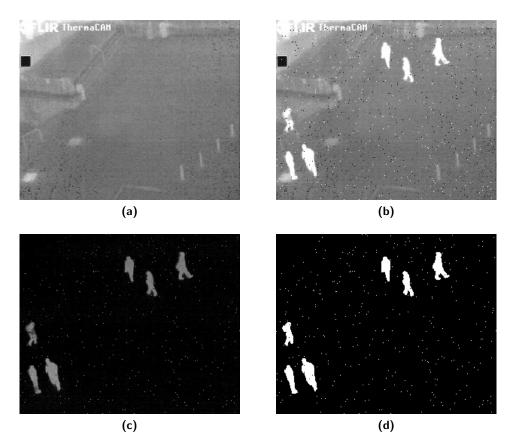

| 3.4  | Segmentation based on the background modelling                                      | 49 |

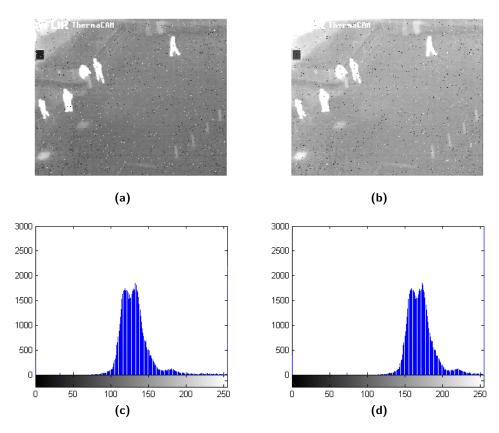

| 3.5  | Two frames of IR video sequence with corresponding histograms. $\ldots$ .           | 57 |

| 3.6  | Background subtraction and intensity thresholding of images with different          |    |

|      | brightness levels                                                                   | 58 |

| 3.7  | Histograms of the images after background subtraction                               | 59 |

| 3.8  | Background subtraction at a properly calibrated system for different tem-           |    |

|      | perature scenarios                                                                  | 60 |

| 3.9  | A conceptual block diagram of the background segmentation and model                 |    |

|      | updating process                                                                    | 62 |

| 3.10 | A block diagram of the feedback loop adaptive thresholding element $\ldots$         | 63 |

| 3.11 | A cut-off region for simplified histogram analysis                                  | 64 |

| 4.1  | Set Theory Concepts                                                                 | 69 |

| 4.2  | Set Operations                                                                      | 70 |

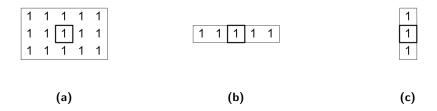

| 4.3 Structuring Element                                                                                          |            |

|------------------------------------------------------------------------------------------------------------------|------------|

| 4.4 Erosion and Dilation                                                                                         | $71 \\ 73$ |

|                                                                                                                  | 73<br>74   |

| <ul> <li>4.5 Opening and Closing</li></ul>                                                                       | 74<br>75   |

|                                                                                                                  |            |

| 4.7 Erosion using decomposed Structuring Element                                                                 | 76         |

| 4.8 Boundary padding problem                                                                                     | 78         |

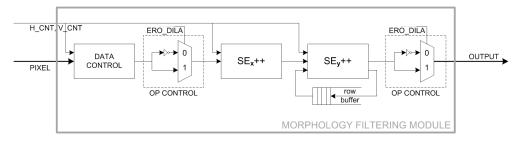

| 4.9 System architecture for morphological filtering applications                                                 | 79         |

| 4.10 Architecture of the delayed element based erosion unit                                                      | 80         |

| 4.11 Rectangular filter mask $(SE)$ for pedestrian detection applications                                        | 81         |

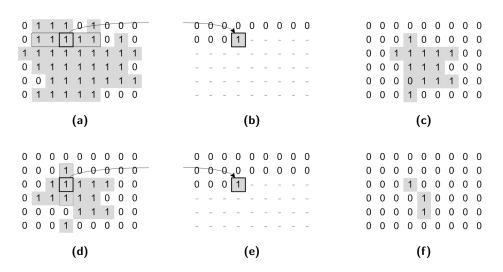

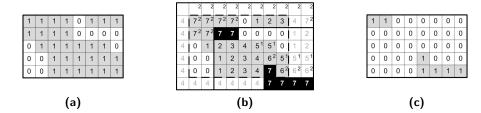

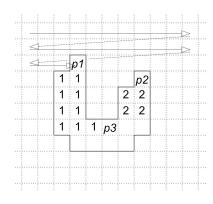

| 4.12 Block diagram of the decomposed dual system architecture                                                    | 82         |

| 4.13 An erosion data flow for decomposed dual system architecture using $3 \times 5$ SI                          |            |

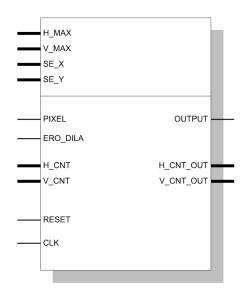

| 4.14 Morphology filtering module block                                                                           | 86         |

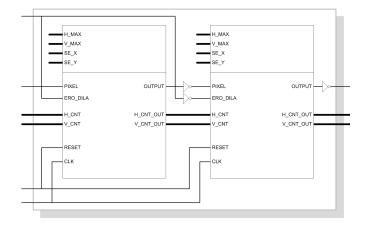

| 4.15 Block diagram of the implemented system architecture for morphology openin                                  | g 87       |

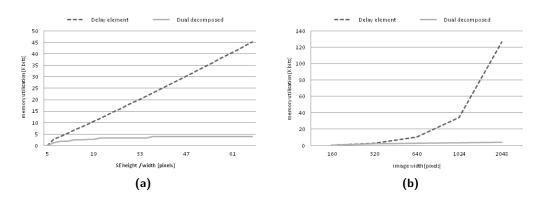

| 4.16 Memory requirement for both delayed element and dual decomposed system                                      |            |

| architectures                                                                                                    | 89         |

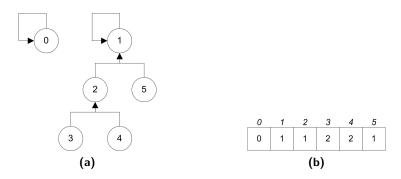

| 5.1 A turning label collision                                                                                    | 96         |

| 5.1 A typical label collision                                                                                    |            |

| 5.2 An example connected component with extracted binary features $\ldots$                                       | 98<br>100  |

| 5.3 Equivalence labels encoding                                                                                  | 100        |

| 5.4 Classical approach for CCL                                                                                   | 103        |

| 5.5 Contour tracing approach for CCL                                                                             | 106        |

| 5.6 Classical algorithm memory requirement                                                                       | 108        |

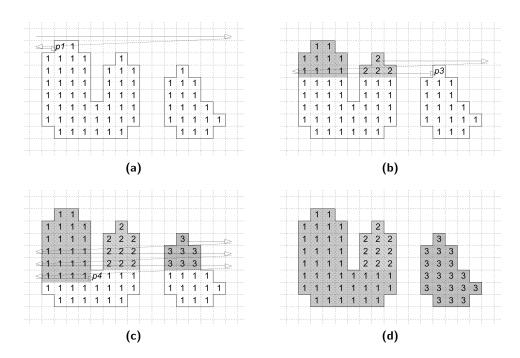

| 5.7 Single pass approach for CCL                                                                                 | 109        |

| 5.8 Memory requirements for labelling algorithms                                                                 | 111        |

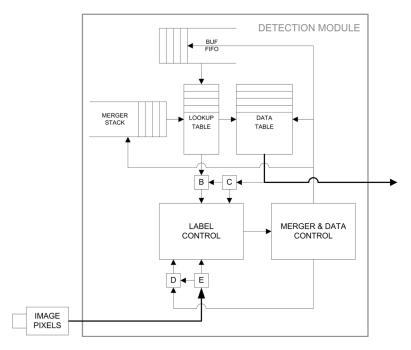

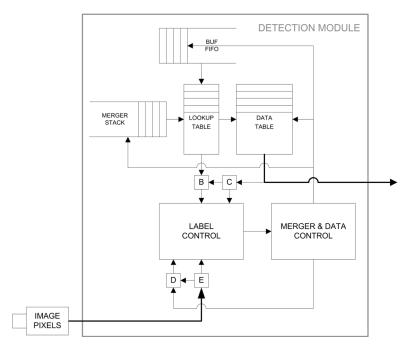

| 5.9 System architecture block diagram                                                                            | 113        |

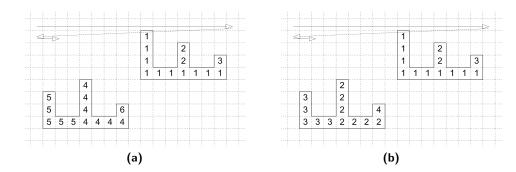

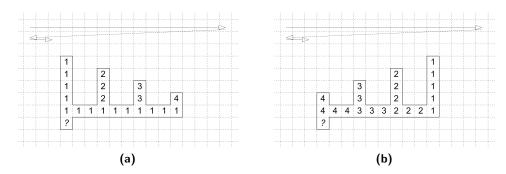

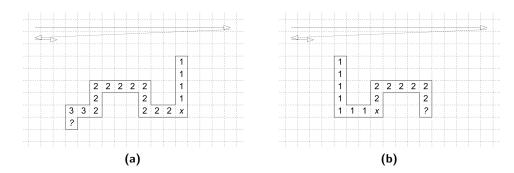

| 5.10 Multiple label merge in a single line scan                                                                  | 114        |

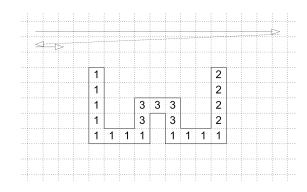

| 5.11 "W" shaped object $\ldots$ | 115        |

| 5.12 Merger chain $\ldots$      | 116        |

| 5.13 System architecture block diagram $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$          | 117        |

| 5.14 LOOKUP and STACK based merging                                                                              | 121        |

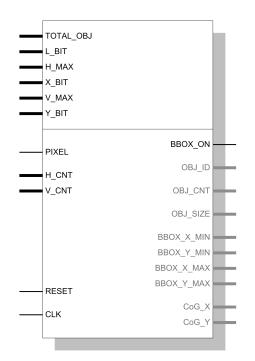

| 5.15 Object detection module block                                                                               | 124        |

| 5.16 Binary image frame with multiple mergers                                                                    | 125        |

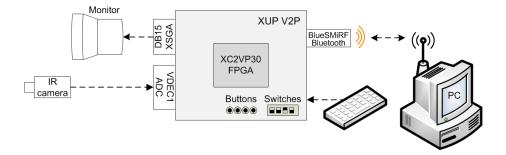

| 6.1 An overview of processing platform together with auxiliary system component                                  | s131       |

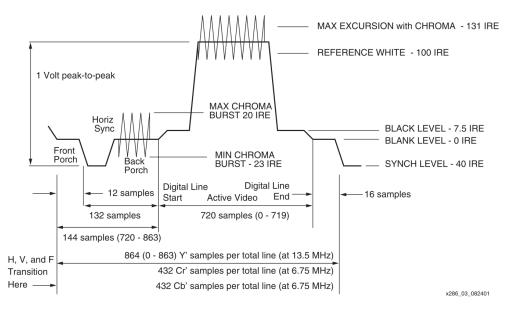

| 6.2 Horizontal scan line for composite PAL                                                                       |            |

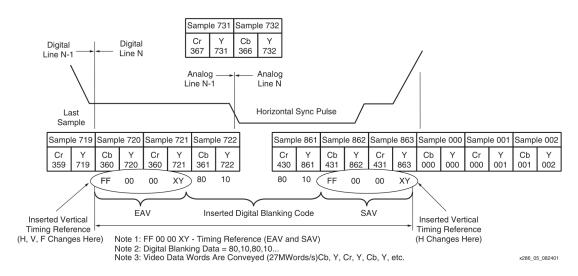

| 6.3 Horizontal scan line codes in ITU-R BT.656 standard                                                          | 135        |

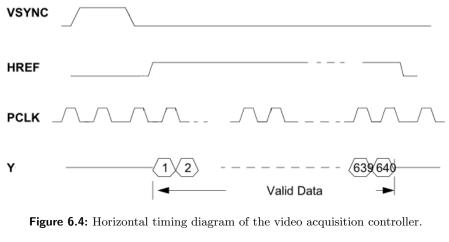

| 6.4 Horizontal timing diagram of the video acquisition controller                                                | 136        |

| 6.5 Vertical timing diagram of the video acquisition controller                                                  |            |

| 6.6 | IR Pedestrian detection system architecture. Top-level hierarchy block diagram               | n138 |

|-----|----------------------------------------------------------------------------------------------|------|

| 6.7 | Multi-window view on the monitor output                                                      | 140  |

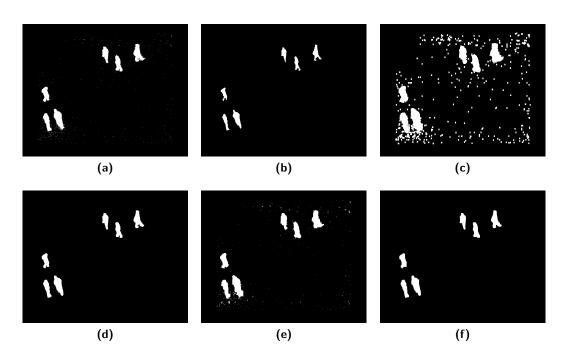

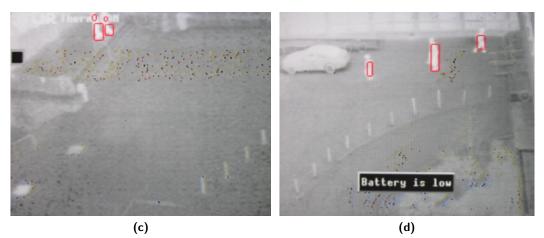

| 6.8 | Results of the experimental pedestrian detection $\ldots \ldots \ldots \ldots \ldots \ldots$ | 145  |

| 6.9 | Samples from test video sequences                                                            | 146  |

|     |                                                                                              |      |

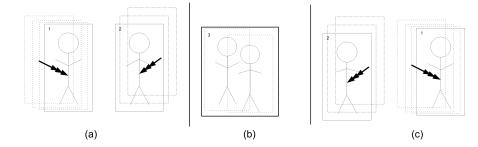

| A.1 | Merging pedestrians                                                                          | 170  |

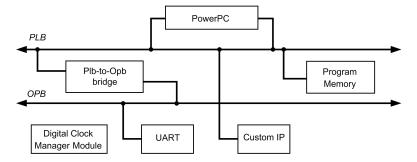

| A.2 | A block diagram of the top-level system hierarchy including processor buses                  | 171  |

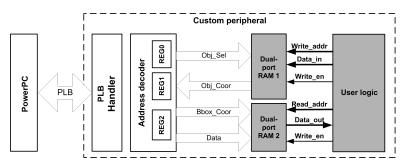

| A.3 | Register level interface                                                                     | 171  |

|     |                                                                                              |      |

## List of Tables

| 2.1 | Comparison of different technologies for signal processing development         | 33  |

|-----|--------------------------------------------------------------------------------|-----|

| 3.1 | Comparison of background segmentation algorithms based on background modelling | 54  |

| 4.1 | Resource utilisation for morphology erosion implementation on XC2VP30          |     |

|     | FPGA                                                                           | 91  |

| 5.1 | Equivalence table                                                              | 103 |

| 5.2 | Classical algorithm memory requirement                                         | 104 |

| 5.3 | Contour tracing algorithm memory requirement                                   | 107 |

| 5.4 | Single pass algorithm memory requirement                                       | 110 |

| 5.5 | CCL algorithms comparison table                                                | 110 |

| 5.6 | Video sequence analysis                                                        | 126 |

| 5.7 | Implementation and resource utilisation for the XC2VP30 FPGA implemen-         |     |

|     | tation                                                                         | 127 |

| 6.1 | Vertical timing reference in ITU-R BT.656 standard                             | 134 |

| 6.2 | Detailed synthesis report part 1                                               | 141 |

| 6.3 | Detailed synthesis report part 2                                               | 142 |

| 6.4 | Detailed synthesis report for chosen subsystems                                | 143 |

| 6.5 | Synthesis report for the entire system                                         | 143 |

| 6.6 | Experimental Detection and Error Rates                                         | 145 |

# List of Abbreviations

| ADC  | Analogue Digital Conversion             |

|------|-----------------------------------------|

| ASIC | Application-Specific Integrated Circuit |

| BRAM | Block RAM                               |

| CCD  | Charge-Coupled Device                   |

| CCL  | Connected Component Labelling           |

| CMOS | Complementary Metal-Oxide Semiconductor |

| CPU  | Central Processing Unit                 |

| CoG  | Centre of Gravity                       |

| DCM  | Digital Clock Manager                   |

| DSP  | Digital Signal Processing               |

| EDK  | Embedded Development Kit                |

| FIFO | First-In First-Out                      |

| FIR  | Finite Impulse Response                 |

| FOV  | Field of View                           |

| FPGA | Field-Programmable Gate Array           |

| FPS  | Frames per Second                       |

| FSM  | Finite State Machine                    |

| FWFT | First-Word Fall-Through                 |

| GCLK | Global Clock                            |

| GPP  | General Purpose Preprocessor            |

| GPU  | Graphics Processing Unit                |

| HREF | Horizontal Reference                    |

| HW   | Hardware                                |

| IC   | Integrated Circuit                      |

| IOB  | Input/Output Block                      |

| IP   | Intellectual Property                   |

| IPIC | IP Interconnect                         |

| IR   | Infrared                                |

| ISE  | Integrated Software Environment         |

|      |                                         |

| LIFO  | Last-In First-Out                                                 |

|-------|-------------------------------------------------------------------|

| LUT   | Look-Up Table                                                     |

| OCM   | On-Chip Memory                                                    |

| OPB   | On-chip Peripheral Bus                                            |

| PAR   | Place and Route                                                   |

| PCLK  | Pixel Clock                                                       |

| PLB   | Processor Local Bus                                               |

| RAM   | Random Access Memory                                              |

| ROI   | Region of Interest                                                |

| SE    | Structuring Element                                               |

| SW    | Software                                                          |

| TRS   | Timing Reference Signal                                           |

| UART  | Universal Asynchronous Receiver/Transmitter                       |

| UML   | Unified Modelling Language                                        |

| VGA   | Video Graphics Array                                              |

| VHDL  | Very-High-Speed Integrated Circuits Hardware Description Language |

| VSYNC | Vertical Synchronization                                          |

|       |                                                                   |

## **CHAPTER** 1

## Introduction

Pedestrian detection is an active research area. There is a number of publications related to algorithmic development of computer vision application. They report increasing segmentation rates as well as improvements in classification and tracking. However, since they are mostly oriented on algorithmic development, they are targeted for implementation in software or simulation environments running on General Purpose Processing (GPP) platforms. This approach reduces the development time as well as provides extensive simulation capabilities, however places heavy demand on computer power and memory resources. Although the amount of computing power provided by GPP allows for basic real-time video processing (early days of 2008), due to high bandwidth imposed by video source and limited interfacing capabilities of ADC boards, video analysis is limited to post-processing in off-line mode. This is caused by the lack of designated video bus between ADC and PC.

Due to prohibitive costs, the use of infrared (IR) cameras, featuring wavelengths: 8- $14\mu$ m, was limited mainly to military purposes. Recently, they have become viable for

commercial use allowing the detection and tracking of pedestrians to offer an alternative technical approach to the one based on traditional CCD or CMOS sensors. Thanks to the thermal detection capability, the video acquisition is based on emitted thermal radiation rather than reflected as in visible images. Since the amount of emitted radiation is highly related to the temperature, detection of pedestrians, often featuring higher temperature than the surrounding background, will benefit from this technology. Moreover, although the thermal background is not constant, it varies gradually compared to sudden changes caused by ambient lighting in visible detection. On the other hand, due to different clothing styles, detected objects tend to form various shapes, they also may have separated body parts caused by occlusions. Moreover, thermal camera provides limited information about the spatial content of the scene, hence reduced number of image processing techniques can be applied.

### 1.1 Motivation

Pedestrian detection has a number of applications in security, safety as well as in retail and transportation sectors. Applications vary from post processing analysis of pedestrian movement to accurately studying shop footfall, to real-time surveillance applications, aimed at determination of suspicious behaviour or accidents. When considering retail applications, the high performance is not as relevant. They are mostly used for studying customers' moving patterns to optimize the flow in order to optimize the layout of shop isles or to appropriately position products with highest profit margin. However, real-time performance and good accuracy are critical for security systems to guarantee prompt reaction to accidents or crimes. Such systems operate on-line to detect the presence, unexpected behaviour or measure activity of pedestrians. In critical cases such applications can safeguard human beings. This is a rapidly growing market with a high potential for improvements.

With increasing popularity of Closed Circuit Television (CCTV) cameras, there is a strong demand for supervised detection or, ideally, fully automated systems. With current technology, a single human operator of CCTV control panel is capable of monitoring multiple cameras. However, an increasing number of cameras makes the task more difficult and prone to detection errors, hence the need for process automation. The automation of pedestrian detection is relevant to several areas in security or safety. It would allow reduce the cost of running system by removing the need for human operator, however, the main benefit is elimination of the human-factor causing detection errors due to long shifts or late working hours.

Since pedestrian detection systems become more important in critical applications such as surveillance or people counters employed for evacuation purposes in emergency situations, there is a need for high accuracy of the detection. Vision systems based on traditional cameras employ higher resolution devices. This involves problems related to high bandwidth imposed by video source. For the purpose of pedestrian detection and tracking, a different technical approach such as infrared cameras with wavelengths  $8-14\mu$ m can be considered.

Segmentation and classification techniques employed within the area of pedestrian detection feature good detection rates, however, due to high complexity they put strong demand on computing power and memory resources. In order to speed up development process, tests and verification, they are often implemented in software, therefore real-time processing from camera streaming live is difficult to achieve on commercially available GPP platforms. Hence, an implementation on application specific device such as Field-Programmable Gate Array (FPGA) shall be considered. This requires optimization of known techniques for pedestrian detection in order to allow implementation in hardware. Moreover, due to omnipresent miniaturization requirement, such implementation shall use limited amount of system resources and memory to keep the package in small size, hence further customization is required.

### 1.2 Research Objective

The objective of the research presented in this thesis is to develop a self-contained system capable of real-time ( $\geq 25 fps$ ) pedestrian detection from infrared video stream. This involves an investigation into segmentation and classification techniques suitable for such implementation. Due to limitations imposed by GPP platforms, the system shall be implemented in hardware using a FPGA device. The implementation shall be small enough to fit a single device with limited memory resources. The architecture developed for this task shall be flexible and prone to further expansion. A modular design approach shall be considered to allow individual processing modules to be used as hardware accelerator within other processing systems.

In particular, this research explores the following areas:

- review of popular algorithms for pedestrian detection,

- Infrared camera utilization to gain detection rates and support light independent environmental scenarios,

- investigation into techniques suitable for hardware implementation,

- development of custom solutions to support real-time detection rates,

- development, test and verification of the digital design architecture for the purpose of self-contained IR pedestrian detection system for real-time video processing.

### 1.3 Contribution to Knowledge

The main contribution is the digital architecture designed, developed and implemented for IR pedestrian detection system, capable of processing video streams in real-time. As well as the architecture, there is the analysis and evaluation of the algorithms and design decisions that support and justify the digital design. Although the system can be used for surveillance applications as an off-the-shelf solution, an emphasis was placed on further expansion, for instance to support tracking applications as a hardware accelerator. The system was designed in a modular approach where individual modules act as hardware accelerators for particular processing tasks. They were developed based on available solutions reported in the literature. For implementation purposes, they are enhanced by custom solutions allowing the real-time performance of the entire system.

### 1.4 Outline of the Thesis

In addition to this introduction, the remainder of this thesis is split amongst six chapters, organized as follows:

Chapter 2: This chapter gives an introduction into the field of **Infrared Radiation** and **Image Processing** techniques used for the purpose of this research. An overview of technology employed for the task of system implementation is also provided.

Such introduction will be given in the following order:

- 1. Infrared Detectors

- 2. Digital Image Processing

- 3. Hardware Development and Implementation

- 4. Pedestrian Recognition

The theoretical background into the area of IR radiation is given including the definition of IR radiation followed by brief discussion on thermal sensors. An overview of thermal cameras is provided together with popular applications for such devices.

The second section gives an introduction into common digital image processing concepts, further referenced in this thesis.

This is followed by an overview of technology employed for the purpose of the final implementation. A description of the design flow is also included.

The last section of this chapter gives a general overview of the pedestrian detection processing flow. A typical data flow is included to introduce the reader to terminology and processing steps, further described in individual chapters. This chapter does not provide a coherent literature-review for the entire research project. Instead, the literature-review was split and included within individual chapters.

Chapter 3: This chapter provides an introduction and detailed analysis of popular **Background Segmentation** techniques. It is supported by an extensive literature-review into the area, followed by a summary and discussion on techniques employed for this project. The second part of the chapter gives an overview of the custom algorithm. This is followed by a description of the architecture developed for the purpose of background segmentation.

Chapter 4: An introduction into **Morphological Noise Removal** is provided in this chapter. The literature-review includes set theory concepts and mathematical morphology definitions, further used in the chapter when formulating the algorithm. The implementation details are provided following an overview of popular techniques within this area. The chapter is concluded with a discussion on execution time and memory requirement imposed by the architecture.

Chapter 5: This chapter gives an extensive analysis on **Connected Component Labelling** algorithms, commonly used in modern vision systems. A detailed discussion on three chosen algorithms is provided to investigate the one suitable for this particular application. The second part of the chapter gives details on the architecture developed for this task together with discussion on resource utilization and the overall performance.

Chapter 6: In this chapter the **System Integration** is discussed. The top-level architecture for the entire system is provided. An overview of system components used for tests and verification is given. A brief description of the video acquisition module implementation is also provided together with data handling tailored for the purpose of this project. The data flow is described in detail pointing modules on the critical path. An introduction into tracking as a natural extension to this project is also provided. The chapter concludes with a summary on synthesis and resource utilization. Experimental detection results are also discussed. This is followed by performance comparison and suggestions for future work.

Chapter 7: This chapter provides a critical **Review of the Research**. It provides final conclusions and suggestions for future work.

## **CHAPTER 2**

## Image Processing for Infrared Pedestrian Detection

Infrared pedestrian detection is an active research area with a long research history at Edinburgh Napier University. Researchers from both Department of Engineering and the School of Computing were investigating efficient techniques for pedestrian detection and tracking using IR sensors. Due to a number of limitations imposed by available computing power, such processing was mostly limited to basic pyroelectric detectors or low resolution IR cameras. This thesis focuses on pedestrian detection using higher resolution cameras.

In this chapter an introduction into the field of infrared radiation and image processing techniques as well as technology used for this task will be provided. Such introduction will be given in the following order:

- 1. Infrared Detectors

- 2. Digital Image Processing

- 3. Hardware Development and Implementation

- 4. Pedestrian Recognition

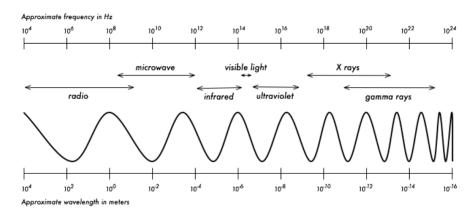

**Figure 2.1:** The electromagnetic spectrum characterised by wavelength  $\lambda$  and frequency  $\nu$  [3].

### 2.1 Infrared Detectors

In this subsection a brief overview of infrared radiation and its applications will be provided. The main purpose is to introduce the reader to IR radiation and its capabilities for thermal detection.

#### 2.1.1 Infrared Radiation

"... There are rays coming from the sun... invested with a high power of heating bodies, but with none of illuminating objects... The maximum of the heating power is vested among the invisible rays.... It may be pardonable if I digress for a moment and remark that the foregoing researches ought to lead us on to others..." [1].

Sir William Herschel.

These are the words of Sir William Herschel, Royal Astronomer to King George II of England, who was the first to reveal the existence of invisible partial radiation which nowadays is referred to as infrared portion of the spectrum. He was the first researcher who in 1800 found that there is a part of radiation which brings heat but is invisible. In 1801 he referred to it in two papers but did not work on his discovery ever again. Nowadays, all the characteristics of IR are broadly known and will be presented below.

IR radiation is an electromagnetic radiation with wavelength  $\lambda$  longer than visible light ( $\lambda = 0.75 \mu m$ ), but shorter than microwaves (1000 $\mu$ m). The visible range of spectrum is relatively short - in between 0.4 $\mu$ m and 0.75 $\mu$ m [2]. The electromagnetic spectrum can be seen in Figure 2.1.

The source of electromagnetic radiation can be any object at a temperature above absolute zero ( $-273^{0}$ C). The amount of emitted radiation and the wavelength distribu-

tion depend on the temperature and emissivity of the body [4]. Each object even at a low temperature of a few Kelvins emits electromagnetic radiation in the range of the far infrared, see Figure 2.1. Human bodies emit the radiation at a wavelength close to  $10\mu$ m, whereas warmer objects emit more radiation with the shorter wavelength.

A unique feature of IR is the material transparency, being one of the most distinctive differences compared to visible light. For instance, semiconductor materials such as germanium and silicon, opaque in the visible, are transparent in the infrared region beyond  $1.8\mu$ m and  $1\mu$ m. On the other hand clear glass, transparent for visible light in its whole spectrum, it is opaque for infrared radiation for wavelengths over  $2.5\mu$ m.

#### 2.1.2 Thermal Sensors

Thermal sensors can be categorized into one of the following groups: those with cooled infrared image detectors or sensors with uncooled detectors.

#### **Cooled Infrared Detectors**

The main feature of cooled infrared detectors is they are usually contained in a vacuumsealed case cryogenically cooled. It is necessary to cool them down to temperatures in the range of 4K - 110K. This allows to achieve desired sensitivity through increased temperature contrast between the sensor and the object meant to be detected. In general, cooled infrared detectors are very expensive to manufacture and run because of their exploitation requirements. On the other hand, they are able to achieve higher resolution with better image quality. Due to their capabilities and high cost, they are mainly used for astronomy and military purposes.

#### **Uncooled Infrared Detectors**

Uncooled infrared detectors are more popular than cooled equivalents mostly due to lower costs and smaller sizes. There are a number of advantages over cooled detectors: they are portable, easy to set-up and ready to work in just a few seconds. There is no need to cool them down since they operate at ambient temperature with the use of additional temperature control elements.

The technology employed is a subject to a target market. Most popular are pyroelectric sensors due to lower cost, although the number of applications is very limited - the electric charge on the output reflects to the change in temperature hence the continuous movement is desired. Moreover they are often limited to operate in low resolutions. These problems do not apply to detectors based on microbolometer technology. Bolometers change their resistance according to the heating source giving spatial image of the scene. Although they are more expensive, for certain applications such as detecting loss

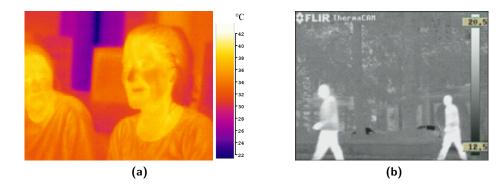

Figure 2.2: Example images taken by IR camera. (a) Colour coded temperature scale. (b) Grey-scale temperature representation.

in insulated systems, observing the blood flow under the skin or overheating of electrical apparatus, they cannot be replaced by pyroelectric equivalents.

#### 2.1.3 Thermographic Cameras

The difference in infrared radiation is transferred to the change of resistance, voltage or current, which is then compared with the value of operating temperature of the sensor. These values form a new infrared image which is then transferred from the camera using one of the available transmission protocols. A thermographic camera, also referred to as an infrared camera, is a device that forms spatial images based on IR radiation. Thanks to the ability to convert infrared energy onto an image, IR cameras can operate even in total darkness since the radiation of ambient light does not apply. Example pictures taken by IR camera can be seen in Figure 2.2.

Thermographic cameras are more expensive compared to traditional visible light cameras with the operating resolution considerably lower (typically at  $160 \times 120$ ,  $320 \times 240$ ). Thermal detectors from FLIR operating in  $320 \times 240$  as of July 2011 are often priced above £5000 [5]. Modern detectors support resolutions up to  $640 \times 480$  with the high end models operating in  $1024 \times 768$  [6], aimed only for military and research purposes.

To make the visualisation of infrared imaging systems more clear and accessible for further processing, it is common practice to use density slicing and interpolation techniques [5]. Since the output of the infrared camera reflects the temperature changes in the FOV, colour coding applied corresponds to different temperature ranges and is a result of a post-processing operation, see Figure 2.2.

Figure 2.3: An example image frame from IR video surveillance system.

#### 2.1.4 Applications

Until recently, thermal imaging using infrared cameras has been limited to military purposes. The first applications were developed for the Korean War in the second half of previous century [7]. Thanks to advanced optics, dynamically developed interfaces, rapidly falling prices and their increased portability, IR cameras are becoming much more popular for typical surveillance and control applications. There are a number of other applications where IR cameras can be efficiently used, for example detecting loss in insulated systems, tracing the source of heat in electrical apparatus or improving night vision.

An infrared camera is an excellent choice for they purpose of people detection. Many surveillance and control applications are based on infrared people detection since they are capable of working in low-light conditions. Moreover, they provide more accurate information for computer vision (easier to distinguish pedestrians, see Figure 2.3), comparing with cameras operating on the visible portion of the spectrum. They are widely used in security applications where permanent surveillance in both day and night time is needed [8]. Other useful applications are emergency systems for people counting in low or zero light conditions [9].

### 2.2 Digital Image Processing

This section gives a brief introduction to digital image representation and image processing techniques. Definitions and concepts used in this section are referred from [10, 11]. They shall be used as a theoretical background for the remainder of this document.

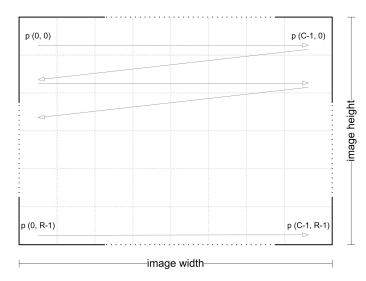

Figure 2.4: Digital image raster scan grid

#### 2.2.1 Digital Image

Digital images are a pictures that have been converted into a binary format consisting of logical 0s and 1s. These images are represented by pixels aligned to a grid with rows and columns. The number of pixels in a row (R) and the number of pixels in a column (C) defines the image resolution. The value of pixel p located at (x, y) corresponds to the colour intensity of the picture at this particular location. Colour image analysis is beyond the scope of this thesis, only grey-scale images will be taken into consideration. In grey-scale images each pixel is assigned with a set of discrete values  $I \in \{i_{min}, i_{max}\}$ representing different grey-scale levels from black to white. For an image with 8-bit grey-scale depth, each pixel is assigned with a value within a range from  $2^0 - 1 = 0$  to  $2^8 - 1 = 255$ . Binary (morphological) images are particular case of grey-scale images where each pixel is represented by one bit: binary-0 or binary-1 corresponding to black and white respectively.

Based on to the information listed above, it is possible to calculate the weight of this particular digital image to check how much memory is required to keep the image within a digital system. The image size is defined by the number of R rows multiplied by the number of C columns (image resolution), multiplied by its grey-scale depth. An example QVGA image with 8-bit grey-scale would require  $320 \times 240 \times 8 = 614400$  bits of memory. The same size binary image would require only  $320 \times 240 \times 1 = 76800$  bits of memory. Memory requirements are often an issue for image processing embedded systems due to limited resources. This aspect will be discussed in detail further in this thesis.

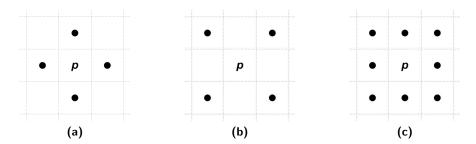

Figure 2.5: Pixel neighbourhood. (a) Horizontal and vertical neighbours of pixel p denoted by  $N_4(p)$ . (b) Diagonal neighbours of pixel p denoted by  $N_D(p)$ . (c) All the 8-neighbours of pixel p denoted by  $N_8(p)$ .

#### 2.2.2 Raster Scan

Due to the nature of video processing systems, digital images are scanned pixel by pixel in raster scan mode. A raster scan is a popular scanning technique for raster graphics images. The scanning starts from the first pixel aligned in the top-left corner of the image with coordinates (0,0). It runs from the left to the right, line by line, until the last (bottom-right) pixel (R, C) is reached. An example of raster grid can be seen in the Figure 2.4. The raster scan is of key importance for all video processing embedded systems. Since image data provided to the system is aligned with raster scan, it would be a natural to process the data on active sample simultaneous with image acquisition. Further details on image acquisition and data handling will be provided in subsequent chapters.

#### 2.2.3 Pixel Neighbourhood

According to the raster grid, pixel p at location (x, y) has two horizontal and two vertical neighbouring pixels at locations:

$$(x-1, y), (x+1, y), (x, y-1), (x, y+1),$$

these are called 4-connected of p and are denoted as  $N_4(p)$ . This can be seen in Figure 2.5(a). The pixel p at location (x, y) has also 4 diagonal neighbours at locations:

$$(x-1, y-1), (x-1, y+1), (x+1, y-1), (x+1, y+1),$$

which can be denoted as  $N_D(p)$ . This was illustrated in the Figure 2.5(b). Both horizontal and diagonal neighbouring groups of pixels are called 8-connected of p and denoted as  $N_8(p)$ , where  $N_8(p) \in N_4(p) \cup N_D(p)$ . When one or both coordinates (x, y) of pixel p are equal to 0, R or C, some of its neighbours fall outside scope of  $N_4$  or  $N_8$ . This issue will be addressed further in this thesis.

Figure 2.6: Pixels connectivity. (a) An arrangements of pixels. (b) Pixels 8-connectivity, connections shown by dashed line. (c) Connection ambiguities solved by m-connectivity

#### 2.2.4 Pixel Connectivity

There are three different kinds of pixel connectivity (adjacency) for binary images between two pixels  $p_1$  and  $p_2$ :

- 4-connectivity when  $p_1 = p_2 = 1$  and  $p_1 \in N_4(p_2)$

- 8-connectivity when  $p_1 = p_2 = 1$  and  $p_1 \in N_8(p_2)$

- m-connectivity (mixed connectivity) when  $p_1 = p_2 = 1$  and  $p_1 \in N_4(p_2)$  or when  $p_1 \in N_D(p_2)$  and  $N_4(p_1) \cap N_4(p_2) \in \phi$

Mixed connectivity, a modification of 8-connectivity, prevents ambiguities which arise when 8-connectivity is used. An example of this type situation can be seen in Figure 2.6(b). Mixed connectivity eliminates multiple path connections and the result of its use can be seen in Figure 2.6(c).

In most applications for computer vision systems, only 4 and 8-connectivities are taken into consideration. Two examples of component labelling with 4-connectivity and 8-connectivity applied to the binary data from Figure 2.7(a) can be seen in Figure 2.7(b) and Figure 2.7(c) respectively.

#### 2.2.5 Connected Components

Two pixels  $p_1$  and  $p_2$  are part of an L connected component in a B binary image when there is a path of connected pixels between pixels  $p_1$  and  $p_2$ . The blob created by all the pixels within the set of pixels connected to  $p_1$  and  $p_2$  is called a connected component. Examples of connected components can be seen in Figure 2.7(b) and Figure 2.7(c).

| 1       1       0       0       1       L2       L2       L2       0       0       L3         0       1       0       0       0       0       L2       L2       L2       0       0       L3         0       1       0       0       0       L2       0       0       0       0         0       0       1       1       0       0       0       L4       L4       0         0       0       0       1       1       0       0       0       L4       L4       0 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       1       0       0       1       L2       L2       L2       0       0       L3         0       1       0       0       0       0       L2       L2       L2       0       0       L3         0       1       0       0       0       L2       0       0       0       0         0       0       1       1       0       0       0       L4       L4       L4       0                                                                                    |

| 1       1       0       0       1       L2       L2       L2       0       0       L3         0       1       0       0       0       0       L2       L2       0       0       L3                                                                                                                                                                                                                                                                             |

| 1 1 1 0 0 1 <i>L2 L2 L2</i> 0 0 <i>L3</i>                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0 1 0 0 0 1 0 <i>L</i> 2 0 0 <i>L</i> 3                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0 0 0 1 1 0 0 0 0 <i>L1 L1</i> 0                                                                                                                                                                                                                                                                                                                                                                                                                               |

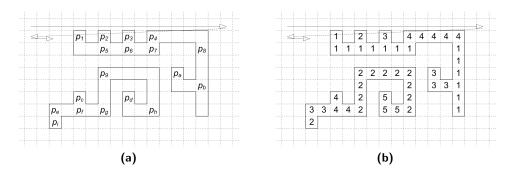

Figure 2.7: Connected Components (CC) labelled with 4 and 8-connectivity. (a) Binary image. (b) CC labelled with 4-connectivity. (c) CC labelled with 8-connectivity.

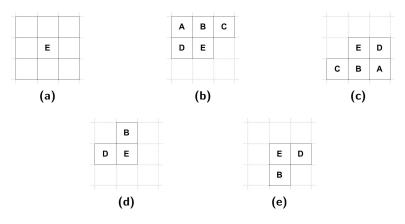

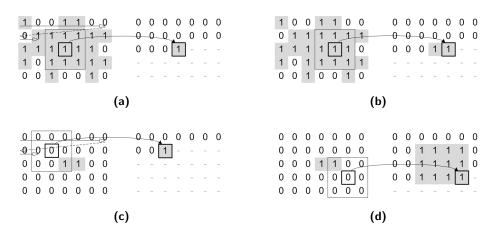

Figure 2.8: Scan mask. (a) 8-connected neighbourhood mask. (b) Forward 8-connected scan mask. (c) Backward 8-connected scan mask. (d) Forward 4 - connected scan mask. (e) Backward 4-connected scan mask.

#### 2.2.6 Scan Mask

In order to create connected components in computer vision, an image has to be scanned through and all the adjacent pixels have to be detected. For this task, a scan mask is employed. The structure of 8-connected neighbourhood mask can be seen in Figure 2.8(a). The centrally placed point E refers to the pixel p located at (x, y) within the binary image B. All the other points are its 8-connected neighbours and are checked for adjacency. The scan mask is being shifted pixel by pixel, line by line - according to the raster scan. Recent algorithms for connected component analysis have reduced structure of the scan mask. The aim is to minimize the number of pixel operations. Scan masks for 8-connected and 4-connected analysis can be seen in Figures 2.8(b), 2.8(c) and Figures 2.8(d), 2.8(e) respectively.

| pixel no. | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | run length code      |

|-----------|---|---|---|---|---|---|---|---|----------------------|

|           | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | (0, 0) (3, 4) (7, 7) |

|           | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | (0, 0) (2, 5)        |

|           | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | (0, 7)               |

|           | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | (0, 5)               |

|           | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | (1, 4) (7, 7)        |

|           | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | (2, 3) (6, 7)        |

Figure 2.9: Run Length Encoding

#### 2.2.7 Labelling

It is a fundamental feature of the computer vision system to be able to assign unique identifiers (labels) to different, disjoint connected components. In this process, all the pixels within the binary image B are analyzed in order to distinguish disjoint points between separate connected components. The classic connected component labelling technique employs the following steps:

- assign a label 0 if the pixel forms part of the background (pixel binary-0);

- if only pixel E was found as a foreground element (binary-1), assign a new label;

- if only one of the neighbouring pixels to the E = 1 was already labelled, assign its label to the current pixel;

- if two or more of the neighbouring pixels were already assigned with different labels, these labels need to be merged.

The labelling technique together with detailed description of popular algorithms for connected component analysis will be presented further in this thesis.

#### 2.2.8 Run Length Encoding (RLE)

Run length encoding is an approach for encoding connected pixels (*runs*) within a single row of a binary image. Each run is represented as a starting and ending point within particular row. RLE was introduced as an approach to reduce the amount of data required for the processing. The main assumption is that binary-0 and binary-1 pixels continue within a row without a change over longer sections, therefore it is suitable for higher resolution images. An example of encoded data using RLE technique can be seen in Figure 2.9. The RLE-based approach can be also used to represent connected components.

### 2.3 Hardware Development and Implementation

There are a number of choices facing system designer while developing a video processing system. Hardware development requires multiple electronics devices such as Analogue to Digital and Digital to Analogue Converters (ADC and DAC respectively), processing unit, storage memory as well as Input/Output (IO) peripherals e.g. push buttons, slide switches, keyboard, monitor display.

The key element of the entire design is a processing unit. There is no ideal technology, it is always the matter of a trade-off between flexibility and performance. In this section alternative solutions will be presented and an overview of development process will be given.

#### 2.3.1 Processing Unit

There is a wide range of processing units utilizing different technologies available on the market. Most common are listed below:

- 1. General Purpose Processor (GPP)

- 2. Digital Signal Processor (DSP)

- 3. Field-Programmable Gate Array (FPGA)

- 4. Application Specific Integrated Circuit (ASIC)

Each of the technologies has a specific set of features since they were designed for different purposes and certain type of applications. They differ in price, size, power consumption as well as development effort and processing power.

#### GPP

General Purpose Processors are commonly used in personal computers and mobile devices [12]. They support floating point operations, allow to run different software packages, including operating systems. Hence, they constitute great means as development platforms for system prototyping. Programming in one of the high level programming/scripting languages (C, C++, Matlab) is fast and supported with efficient debugging tools. If there is a need for further code optimization, critical code can be implemented at a lower abstraction level, e.g. C, C++ for Matlab or assembly for C, C++. However, this comes at a cost of flexibility and development effort.

#### DSP

Digital Signal Processors feature similar principle compared to GPPs with advanced architecture and additional instruction set for signal processing operations such as Multiply and Accumulate (MAC) or memory read with simultaneous addition [13]. An extended instruction set is a great advantage when comparing with GPPs. They are also smaller in size and feature lower power consumption therefore oriented on specific application within embedded system.

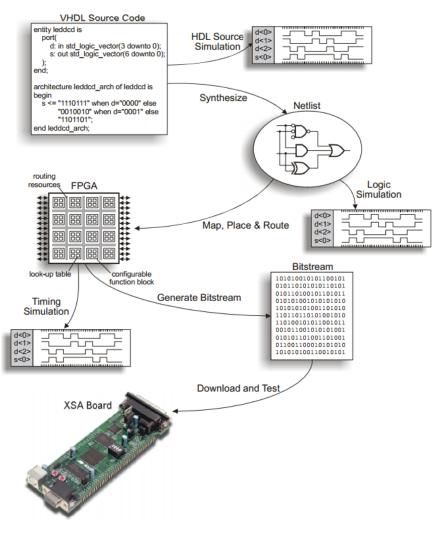

#### FPGA

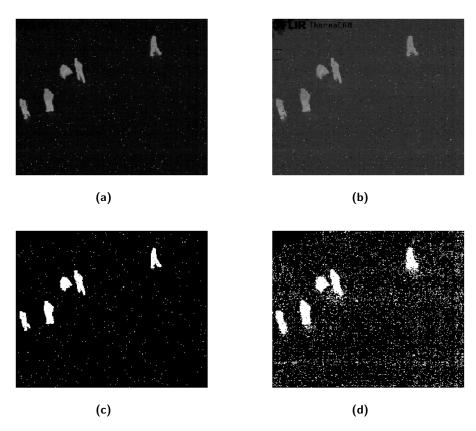

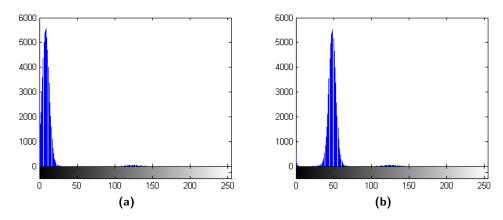

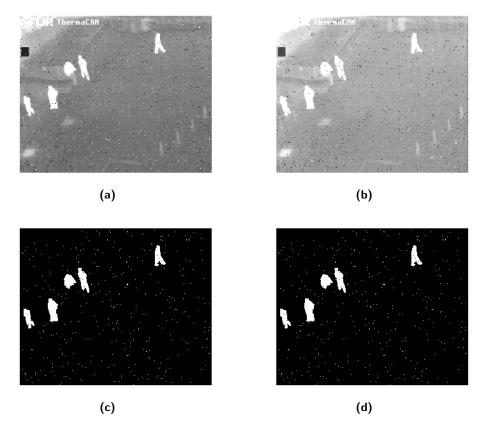

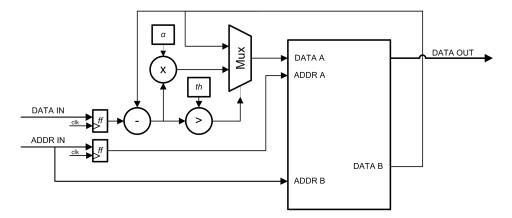

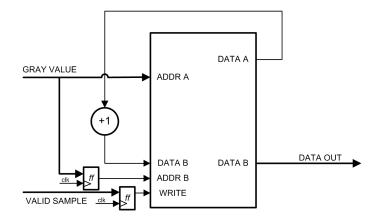

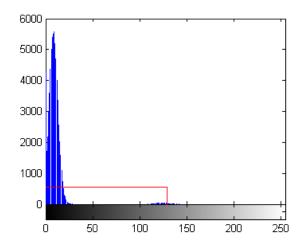

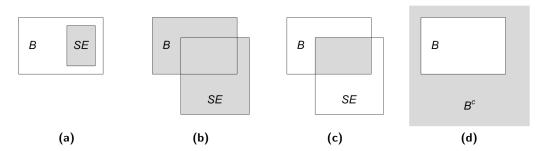

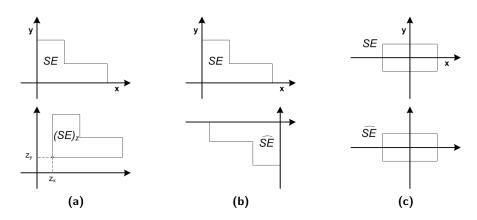

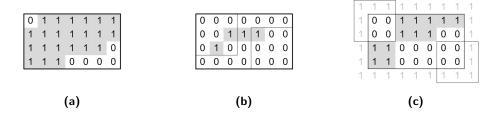

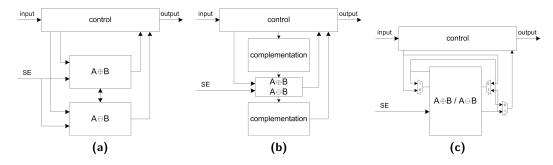

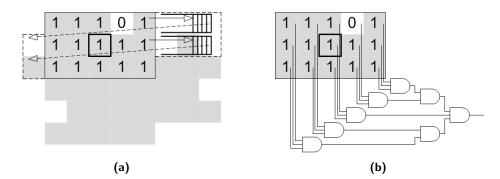

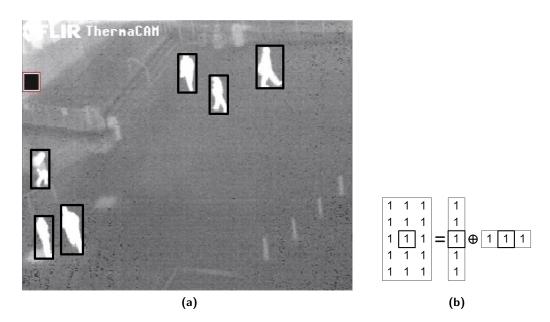

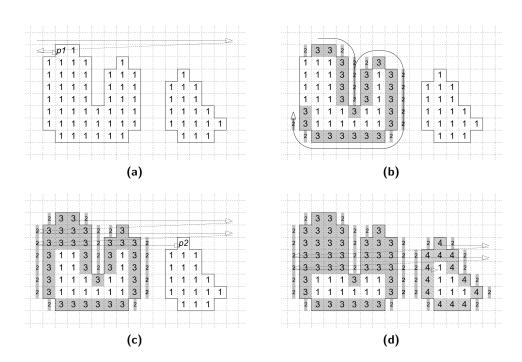

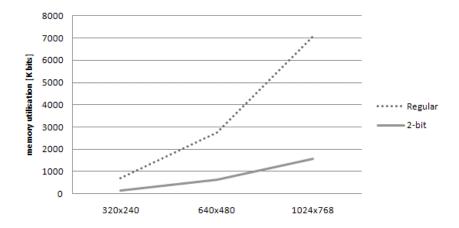

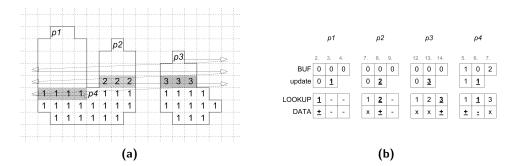

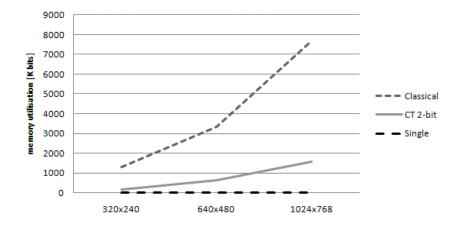

Field-Programmable Gate Arrays are digital Integrated Circuits (ICs) containing configurable (programmable) blocks of logic along with configurable interconnects in between [14]. Hardware Description Language (HDL) and FPGA devices allow designers to quickly develop and simulate a sophisticated digital circuit, run it on a prototyping device, and verify the operation of the physical implementation [15]. Thanks to embedded macro blocks such as multipliers, dual port memory blocks and even embedded processor cores, signal processing algorithms may be implemented more efficiently compared to DSPs. Moreover, Hardware/Software (HW/SW) workload can be partitioned to run house-keeping tasks in software, whereas signal processing in parallel and pipelined fashion on hardware.