# Applications in Electronics Pervading Industry, Environment and Society Sensing Systems and Pervasive Intelligence

Edited by Sergio Saponara, Alessandro De Gloria and Francesco Bellotti Printed Edition of the Special Issue Published in *Sensors*

www.mdpi.com/journal/sensors

# Applications in Electronics Pervading Industry, Environment and Society—Sensing Systems and Pervasive Intelligence

# Applications in Electronics Pervading Industry, Environment and Society—Sensing Systems and Pervasive Intelligence

Editors

Sergio Saponara Alessandro De Gloria Francesco Bellotti

MDPI • Basel • Beijing • Wuhan • Barcelona • Belgrade • Manchester • Tokyo • Cluj • Tianjin

*Editors* Sergio Saponara Università di Pisa Italy

Alessandro De Gloria University of Genoa Italy Francesco Bellotti University of Genoa Italy

Editorial Office MDPI St. Alban-Anlage 66 4052 Basel, Switzerland

This is a reprint of articles from the Special Issue published online in the open access journal *Sensors* (ISSN 1424-8220) (available at: https://www.mdpi.com/journal/sensors/special\_issues/applepies).

For citation purposes, cite each article independently as indicated on the article page online and as indicated below:

LastName, A.A.; LastName, B.B.; LastName, C.C. Article Title. *Journal Name* Year, *Volume Number*, Page Range.

ISBN 978-3-0365-0478-0 (Hbk) ISBN 978-3-0365-0479-7 (PDF)

© 2021 by the authors. Articles in this book are Open Access and distributed under the Creative Commons Attribution (CC BY) license, which allows users to download, copy and build upon published articles, as long as the author and publisher are properly credited, which ensures maximum dissemination and a wider impact of our publications.

The book as a whole is distributed by MDPI under the terms and conditions of the Creative Commons license CC BY-NC-ND.

### Contents

| About the Editors                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sergio Saponara, Alessandro De Gloria and Francesco BellottiRecent Trends on Applications of Electronics Pervading the Industry, Environment and SocietyReprinted from: Sensors 2020, 20, 7295, doi:10.3390/s202472951                                                                                                             |

| Francesco Bellotti, Nisrine Osman, Eduardo H. Arnold, Sajjad Mozaffari, Satu Innamaa,<br>Tyron Louw, Guilhermina Torrao, Hendrik Weber, Johannes Hiller, Alessandro De Gloria,<br>Mehrdad Dianati and Riccardo Berta<br>Managing Big Data for Addressing Research Questions in a Collaborative Project on Automated                |

| Driving Impact Assessment<br>Reprinted from: <i>Sensors</i> <b>2020</b> , <i>20</i> , <i>6773</i> , doi:10.3390/s20236773 7                                                                                                                                                                                                        |

| <b>Xuliang Lu, Zhongbin Wang, Chao Tan, Haifeng Yan, Lei Si and Dong Wei</b><br>A Portable Support Attitude Sensing System for Accurate Attitude Estimation of Hydraulic<br>Support Based on Unscented Kalman Filter                                                                                                               |

| Reprinted from: Sensors 2020, 20, 5459, doi:10.3390/s20195459 25                                                                                                                                                                                                                                                                   |

| Danilo Monda, Gabriele Ciarpi and Sergio Saponara         Analysis and Comparison of Rad-Hard Ring and LC-Tank Controlled Oscillators in 65 nm for         SpaceFibre Applications         Reprinted from: Sensors 2020, 20, 4612, doi:10.3390/s20164612                                                                           |

| Replined noni. <i>50,5075</i> <b>2020</b> , 20, 4012, doi:10.5570/320104012                                                                                                                                                                                                                                                        |

| Marco Mestice, Bruno Neri, Gabriele Ciarpi and Sergio Saponara         Analysis and Design of Integrated Blocks for a 6.25 GHz Spacefibre PLL         Reprinted from: Sensors 2020, 20, 4013, doi:10.3390/s20144013                                                                                                                |

| Fouad Sakr, Francesco Bellotti, Riccardo Berta and Alessandro De Gloria         Machine Learning on Mainstream Microcontrollers         Reprinted from: Sensors 2020, 20, 2638, doi:10.3390/s20092638                                                                                                                              |

| Luca Baldanzi, Luca Crocetti, Francesco Falaschi, Matteo Bertolucci, Jacopo Belli,<br>Luca Fanucci, and Sergio Saponara                                                                                                                                                                                                            |

| Cryptographically Secure Pseudo-Random Number Generator IP-Core Based on SHA2<br>Algorithm                                                                                                                                                                                                                                         |

| Reprinted from: <i>Sensors</i> <b>2020</b> , <i>20</i> , 1869, doi:10.3390/s20071869                                                                                                                                                                                                                                               |

| Milena Andrighetti, Giovanna Turvani, Giulia Santoro, Marco Vacca, Andrea Marchesin,<br>Fabrizio Ottati, Massimo Ruo Roch, Mariagrazia Graziano, Maurizio Zamboni<br>Data Processing and Information Classification— An In-Memory Approach<br>Reprinted from: <i>Sensors</i> <b>2020</b> , <i>20</i> , 1681, doi:10.3390/s20061681 |

| Mauro D'Arco, Ettore Napoli and Efstratios ZacharelosDigital Circuit for Seamless Resampling ADC Output StreamsReprinted from: Sensors 2020, 20, 1619, doi:10.3390/s20061619                                                                                                                                                       |

| <b>Fabio Rossi, Paolo Motto Ros, Ricardo Rosales, Danilo Demarchi</b><br>Embedded Bio-Mimetic System for Functional ElectricalStimulation Controlled by<br>Event-Driven sEMG                                                                                                                                                       |

| Reprinted from: Sensors 2020, 20, 1535, doi:10.3390/s20051535                                                                                                                                                                                                                                                                      |

| Marco Cococcioni, Federico Rossi, Emanuele Ruffaldi and Sergio Saponara<br>Fast Approximations of Activation Functions in Deep Neural Networks when using<br>Posit Arithmetic<br>Reprinted from: <i>Sensors</i> <b>2020</b> , <i>20</i> , 1515, doi:10.3390/s20051515 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Riccardo Peloso, Maurizio Capra, Luigi Sole, Massimo Ruo Roch, Guido Masera,<br>Maurizio Martina                                                                                                                                                                      |

| Steerable-Discrete-Cosine-Transform (SDCT): Hardware Implementation and Performance Analysis                                                                                                                                                                          |

| Reprinted from: Sensors 2020, 20, 1405, doi:10.3390/s20051405                                                                                                                                                                                                         |

| Francesco Guzzi, Luca De Bortoli, Romina Soledad Molina, Stefano Marsi, Sergio Carrato<br>and Giovanni Ramponi                                                                                                                                                        |

| Distillation of an End-to-End Oracle for Face Verification and Recognition Sensors                                                                                                                                                                                    |

| Reprinted from: <i>Sensors</i> <b>2020</b> , <i>20</i> , 1369, doi:10.3390/s20051369                                                                                                                                                                                  |

| Marco Bassoli, Valentina Bianchi and Ilaria De Munari<br>A Model-Based Design Floating-Point Accumulator. Case of Study: FPGA Implementation of a                                                                                                                     |

| Support Vector Machine Kernel Function                                                                                                                                                                                                                                |

| Reprinted from: <i>Sensors</i> <b>2020</b> , <i>20</i> , 1362, doi:10.3390/s20051362                                                                                                                                                                                  |

### About the Editors

Sergio Saponara is an Italian scientist, engineer, and entrepreneur. He is Full Professor of Electronics at the University of Pisa, Italy, where he is also President of the BSc and MSc degree programs in Electronic Engineering. He got his Master and PhD degrees cum laude in Electronic Engineering in 1999 and 2003, respectively. He started his research activities in the fields of digital electronics in 1999, first with a research grant from the National Research Council and then a grant from STMicroelectronics. In 2002, he was a Marie Curie Research Fellow at IMEC, Leuven, Belgium. Since 2005, he has been responsible for the teaching of courses in Automotive Electronics and Electronic Systems for Robotics and Automation at the University of Pisa, where he contributed to the foundation of the MSc degree in Cybersecurity, being responsible for HW and Embedded Security. Since 1999, he has also taught Electronics at the Italian Naval Academy. As an entrepreneur, he co-founded the company IngeniArs in 2014, winner of several innovation prizes such as the H2020 SME Instrument. Since 2016, he has been the founder and director of the Summer School in Enabling Technologies for Industrial IoT, awarded in 2017 and 2018 by the IEEE CAS society. Since 2020, he has been director of the Automotive Electronics and Powertrain Electrifications specialization course. He has co-organized more than 150 conferences and he is Associate Editor of the journals Energies, Sensors, Designs, IEE Electronic Letters, Springer Nature Journal of Real Time Image Processing, IEEE Canadian Journal of Electrical and Computer Engineering, IEEE Consumer Electronics Magazine, and IEEE Vehicular Technology Magazine. Currently, he coordinates the University of Pisa in the H2020 European Processor Initiative, where he is WP leader for security HW implementation and member-elected of the steering committee. He also has ongoing projects with MIT on power converters and e-drives for electric/hybrid vehicles. He has co-authored around 300 scientific articles, 5 books, 10 journal special issues, and 20 patents. In his technology transfer activity, he has collaborated with Marelli, Maserati, STMicroelectronics, Renesas, Intel, Huawei, Infineon, Ericsson, P2P, Solari, Trenitalia, AMS, RiCo, INTECS, IDS, Sitael, and Leonardo. He has worked as an evaluator for R&D projects for the governments of Italy, Romania, Kazakhstan, and the European Commission. He is an expert of the European Institute for Science Media and Democracy and has been included in Stanford University's list of the world's top 2% scientists.

Alessandro De Gloria is Full Professor in Electronic Engineering at the University of Genoa, where he leads the ELIOS Lab research group at the Dept. of Naval, Electrical, Electronic and Telecommunications Engineering (DITEN). He graduated cum laude in Electronic Engineering and received his PhD from the University of Genoa. His main research interests are in the field of modeling and simulation, virtual reality, game technologies, computer architectures, and human–machine interaction. He is Editor in Chief and founder of the International Journal of Serious Games, and the founder of the Serious Games Society. He is part of the "Società Italiana di Elettronica" (SIE), the Italian association of Electronic Engineering university professors. He has been responsible for the Applications and Systems sector at a national level, and for the overall Genoa local unit. He was one of the Genoa University Advanced Simulation and Education Service Center (SIMAV). He has been responsible for more than 30 research projects in the fields of automotive, game technologies, and technology-enhanced learning. He has authored more than 250 papers in international scientific journals and conferences.

**Francesco Bellotti** is Associate Professor at DITEN, University of Genoa, teaching Cyberphysical systems and Edge computing on the MSc course in Electronic Engineering. He received his MSc in Electronic Engineering (cum laude) and PhD in Electrical Engineering from the University of Genoa. He is on the didactic board of the Interactive Cognitive Environments PhD program. His main research interests concern intelligent transportation systems; edge computing; Internet of Things; cyberphysical systems; human–computer interaction. He has been responsible for the WPs of several industrial research projects particularly in intelligent transportation systems. He is on the editorial board of MDPI's *Energies and Sensors*, Hindawi's aHCI, and the *Int J. Serious Games*.

Editorial

# **Recent Trends on Applications of Electronics Pervading the Industry, Environment and Society**

Sergio Saponara <sup>1,\*</sup>, Alessandro De Gloria <sup>2</sup> and Francesco Bellotti <sup>2</sup>

- <sup>1</sup> DII (Dipartimento di Ingegneria della Informazione), University of Pisa, via G. Caruso 16, 56122 Pisa, Italy

- <sup>2</sup> DITEN (Electrical, Electronics and Telecommunication Engineering and Naval Architecture Department), University of Genoa, via Opera Pia 11/a, 16145 Genoa, Italy; adg@elios.unige.it (A.D.G.); franz@elios.unige.it (F.B.)

- \* Correspondence: sergio.saponara@unipi.it

Received: 10 December 2020; Accepted: 13 December 2020; Published: 18 December 2020

This Editorial analyzes the manuscripts accepted, after a careful peer-reviewed process, for the Special Issue "Applications in Electronics Pervading Industry, Environment and Society—Sensing Systems and Pervasive Intelligence" of the Sensors MDPI journal. The Special Issue was co-organized by the University of Pisa (Professor Sergio Saponara at the Department of Information Engineering) and University of Genoa (Professors Alessandro de Gloria and Francesco Bellotti at the Department of Electrical, Electronics and Telecommunication Engineering and Naval Architecture) in Italy. Most of the papers were selected as the best papers of the 2019 edition of the "Applications in Electronics Pervading Industry, Environment and Society" (Applepies) Conference that was held in Pisa in September 2019. All these papers were significantly enhanced with novel experimental results, as we show in the following.

The selected papers give an overview of the trends in research and development activities about the pervasive application of electronics to the industry, environment and society. The focus of the papers is on cyber physical systems (CPS) with research proposals for new sensor acquisition and ADC (analog-to-digital converter) methods, high-speed communication systems, cybersecurity and data processing, including emerging machine-learning techniques.

For each paper, the physical implementation aspects are always discussed, as well as the trade-off to be found between functional performances and hardware costs is exhaustively analyzed.

The Special Issue is characterized by 13 original research papers [1–13] that we briefly introduce in the following.

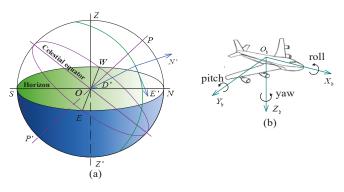

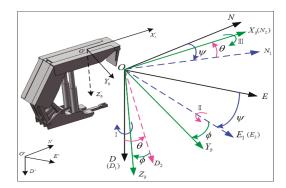

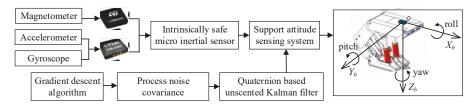

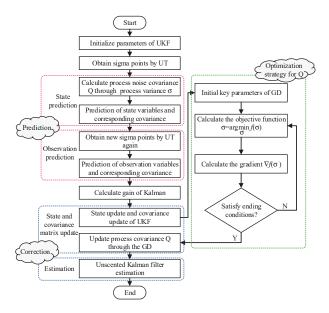

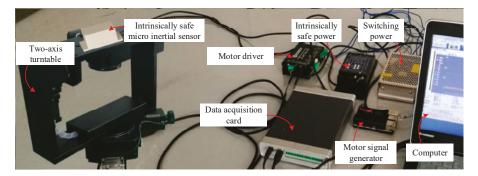

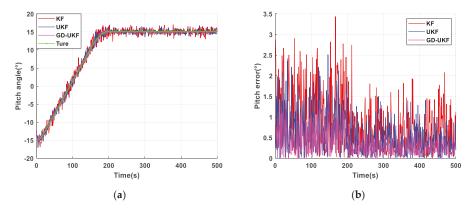

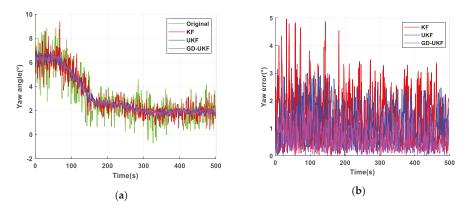

The first paper [1] is entitled "A Portable Support Attitude Sensing System for Accurate Attitude Estimation of Hydraulic Support Based on Unscented Kalman Filter", written by Xuliang Lu, Zhongbin Wang, Chao Tan, Haifeng Yan, Lei Si and Dong Wei from the School of Mechatronic Engineering, China University of Mining and Technology, Daxue Road, Xuzhou 221116, China.

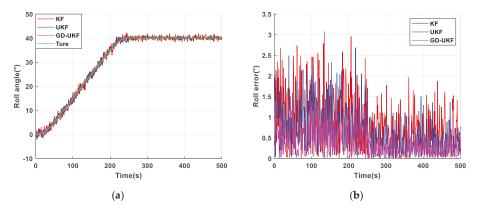

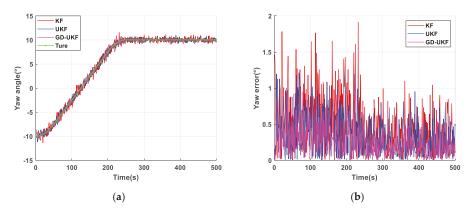

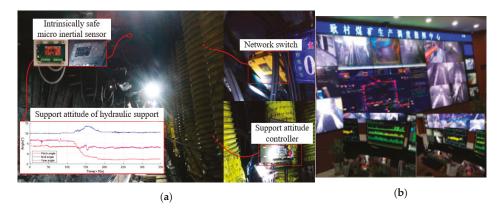

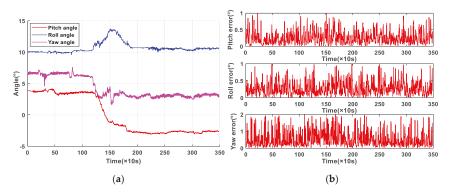

The paper proposes the design of a support attitude sensing system composed of an inertial measurement unit (IMU) with MEMS (microelectromechanical system) sensors. In the classis attitude, a control system's yaw angle estimation with magnetometers is disturbed by the perturbed magnetic field generated by a coal rock structure and by high-power equipment. On the other hand, roll and pitch angles are often estimated using a MEMS gyroscope and accelerometer, and the accuracy is not reliable with time, usually due to long-term bias instability problems. In order to eliminate the measurement error of the sensors and to obtain an accurate attitude estimation, the paper proposed the use of an unscented Kalman filter based on quaternion, according to the characteristics of complementation of the magnetometer, accelerometer and gyroscope. Then, the gradient descent algorithm is used to optimize the key parameter of the unscented Kalman filter—namely, processing the noise covariance—to improve the accuracy of the attitude calculation. An industrial application shows that the average

measurement error of the yaw angle is less than 2° and that of the pitch angle and roll angle are less than 1°, which proves the efficiency and feasibility of the proposed cyber physical system.

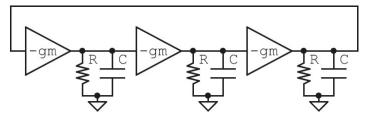

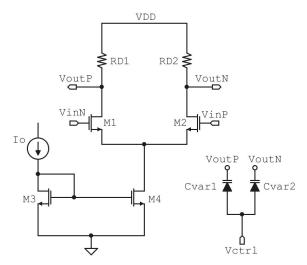

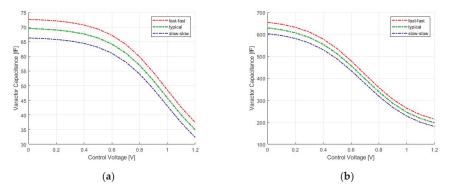

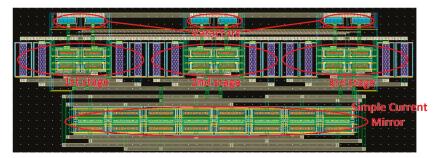

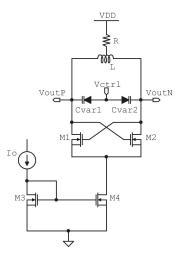

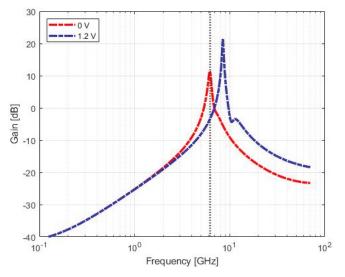

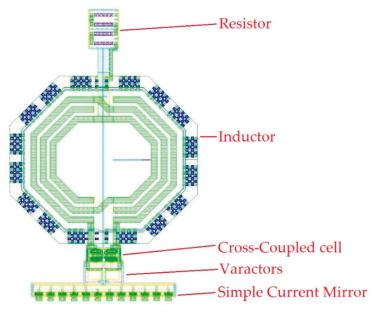

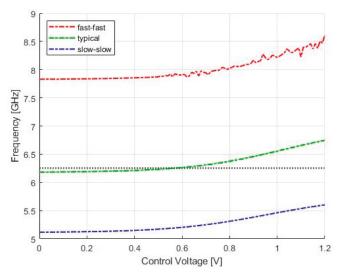

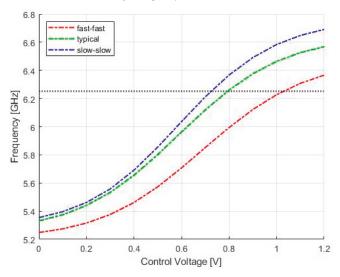

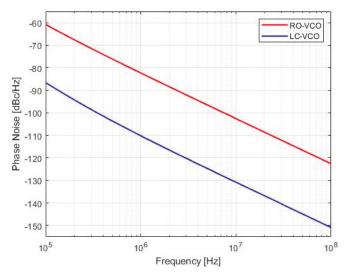

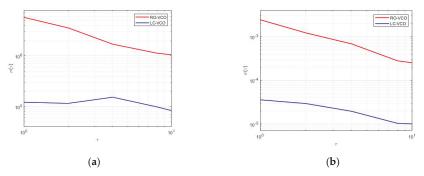

The second paper [2] is entitled "Analysis and Comparison of Rad-Hard Ring and LC-Tank Controlled Oscillators in 65 nm for SpaceFibre Applications", written by D. Monda et al. from the University of Pisa and by INFN (the Italian National Institute for Nuclear Physics).

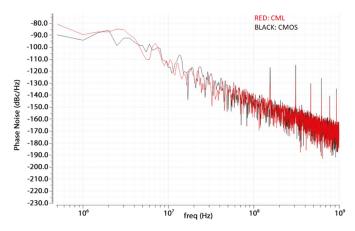

This work presents a comparison between two voltage-controlled oscillators (VCOs) designed in a commercial 1.2-V 65-nm CMOS (complementary metal oxide semiconductor) technology to address the needs of SpaceFibre, a recent standard for high-speed communications in space applications. The first architecture based on a ring oscillator (RO) was designed using three current mode logic (CML) stages connected in a loop, while the second one was based on an LC-tank resonator. This analysis aimed to choose a VCO architecture able to be integrated into a rad-hard phase-locked loop to meet the specifications of the SpaceFibre protocol, supporting frequencies up to 6.25 GHz. The paper presents the full custom schematic and the layout designs. The single-event effect simulation results, performed according to an IMEC (Interuniversity MicroElectronics Center, Belgium) model with a double-exponential current pulses generator, are also discussed. The performance of the RO-VCO are quite attractive in terms of technology scaling and reduced area occupation. However, the RO-VCO solutions suffer from larger frequency spreading due to process variations and due to operations in harsh space conditions. On the contrary, the LC-VCO solution is characterized by a lower sensitivity to PVT (process–voltage–temperature) variations. Hence, the LC-VCO architecture is the one selected to fulfill the specifications of the new SpaceFibre aerospace standard.

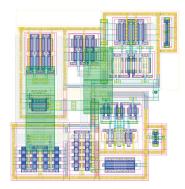

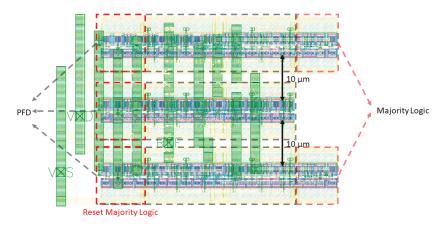

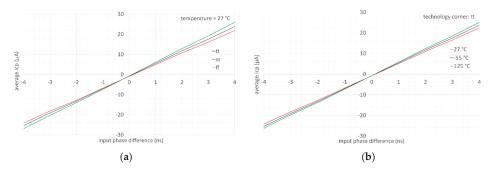

The third paper [3] is entitled "Analysis and Design of Integrated Blocks for a 6.25 GHz SpaceFibre PLL" and is written by M. Mestice at al., with authors from the University of Pisa and by INFN (the Italian National Institute for Nuclear Physics).

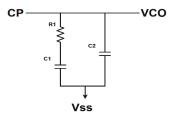

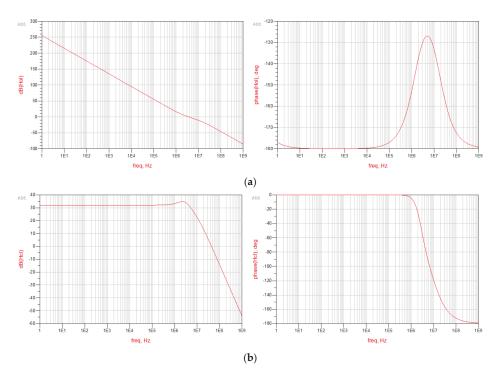

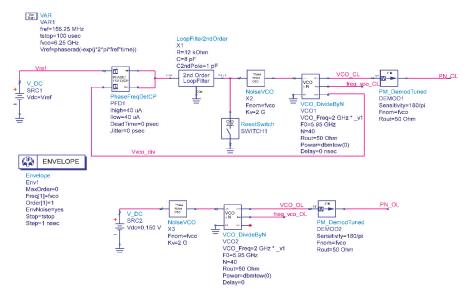

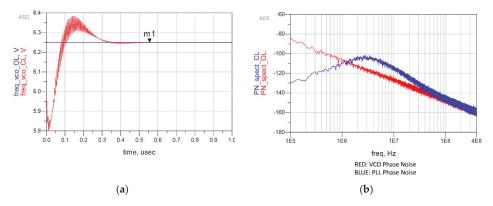

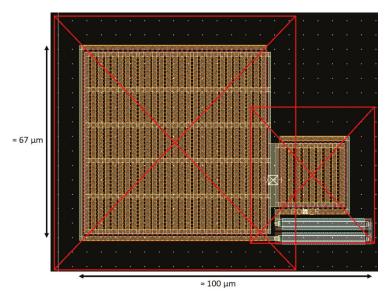

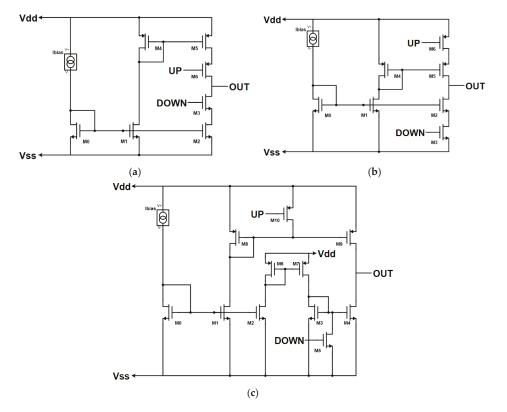

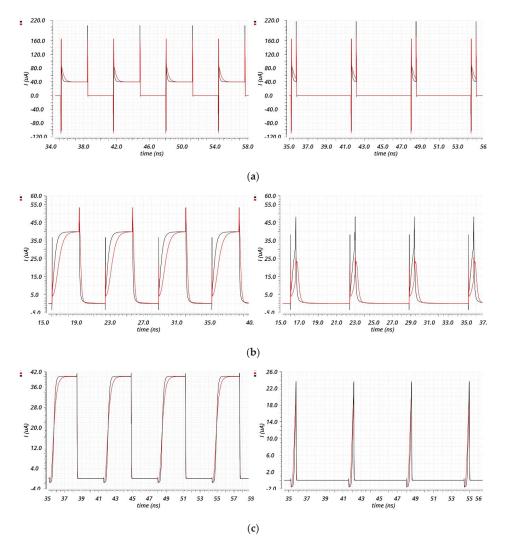

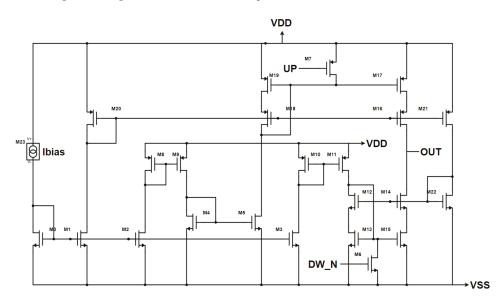

Additionally, this paper refers to the SpaceFibre standard for high-speed communication in space applications and presents the design of the key blocks for a phase-locked loop (PLL) to generate the clock reference up to 6.25 Gbps: triple-modular redundancy phase/frequency detector, charge pump and a passive loop filter. Modeling and simulation activities were carried out in the ADS (Advanced Design System) RadioFrequency environment and in the Cadence Virtuoso environment. The results achieved proved that the PLL can be fully integrated on-chip in a commercial 1.2-V 65-nm CMOS technology with an area size dominated by the passive loop filter. Both system-level and layout-level rad-hard techniques were proposed. The results achieved showed that a compact (0.09 mm<sup>2</sup>) and low-power (about 10 mW) dead zone-free and rad-hard PLL can be obtained with a phase noise below -80 dBc/Hz @ 1 MHz and targeting the 6.25-Gbps maximum data rate of the SpaceFibre standard.

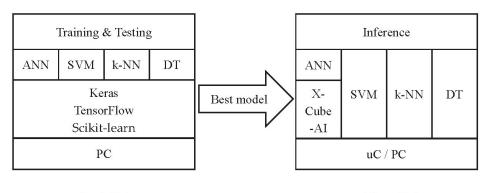

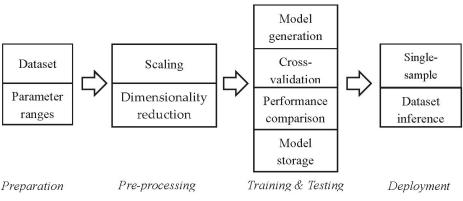

The fourth paper [4] is entitled "Machine Learning on Mainstream Microcontrollers" and is authored by F. Sakr at al. from University of Genoa.

This work addresses the emerging problem of implementing machine-learning (ML) techniques in edge devices. More in detail, the paper introduces the edge-learning machine (ELM), a machine-learning framework for edge devices. The goal is managing the ML training phase on a desktop computer, while the inference phase is implemented on a STM32 (STMicroelectronics 32-bit) microcontroller. By using a platform-independent C language, the paper deals with several supervised ML algorithms (a support vector machine with a linear kernel, k-nearest neighbors and decision tree) and exploits the capability of the STM X-Cube AI to implement artificial neural networks (ANNs) on STM32 Nucleo boards. Multiple datasets are considered for classifications and regression. The results of the research work prove that the edge platforms reach the same performance score of a desktop computing platform with a similar time latency. To support the community of developers and makers, the ELM framework is released as an open source.

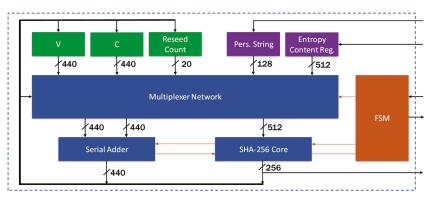

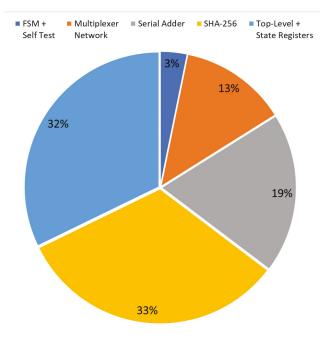

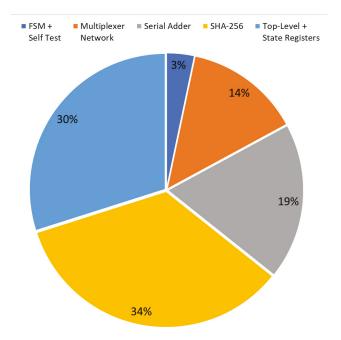

The fifth paper [5] deals with cybersecurity. It is entitled "Cryptographically Secure Pseudo-Random Number Generator IP-Core Based on SHA2 Algorithm" by L. Baldanzi et al., a group of authors from the University of Pisa.

The adoption of advanced sensors and systems for autonomous driving, combined with an increased connectivity of vehicles, robots and drones, is increasing the importance of embedding security features in computing and communication platforms. To this aim, RNG (random number generation) has a crucial role in ensuring the robustness of the security chain. RNG is a key technology to generate the encryption keys to be used for ciphers. Hence, any weakness in the key generation process will lead to leaks of information and will increase the probability to breach even the strongest cipher. More in detail, the paper shows the architecture of a CSPRNG (cryptographically secure pseudo-random number generator) macrocell that was validated by using the official Statistical Test Suite of the NIST (National Institute for Standard and Technology) to assess the degree of randomness of the numbers generated. The proposed CSPRNG macrocell was characterized by both FPGA (field-programmable gate array) and ASIC (application-specific integrated circuit) standard-cell technologies.

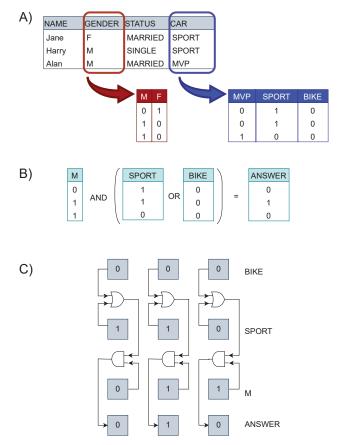

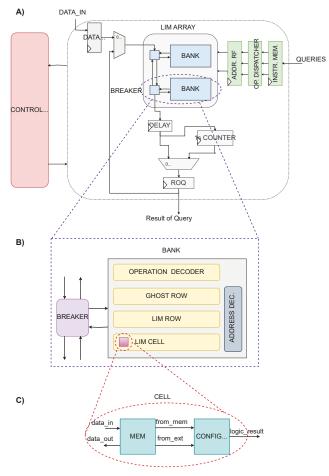

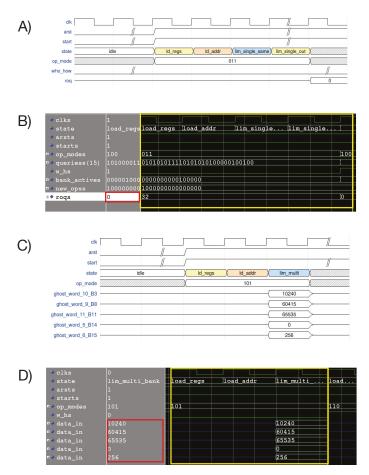

The sixth paper [6] is entitled "Data Processing and Information Classification—An In-Memory Approach" and is authored by M. Andrighetti et al. from Politecnico di Torino.

In the Internet of Things (IoT) era, an enormous amount of data, generated by billions of electronic devices full of sensors that constantly acquire data, must be processed and classified. A classic approach is transferring these data to servers that elaborate them remotely in the cloud. This approach is energy-inefficient (there is a huge battery drain due to the high amount of information to be transferred) and is affected by latency problems in safety-critical time-sensitive applications. Data may be processed locally in edge devices, near the sensor itself, but this solution requires a high-performance computation (HPC) and memory capability that is often missing in mobile microprocessors and microcontrollers. To address these issues, the paper presents a PIM (processing-in-memory) approach where new memories are designed to elaborate the data inside them, overcoming the well-known "memory wall" issue. More in detail, the work, with reference to a bitmap indexing case study, presents a hardware accelerator designed in CMOS technology around the PIM approach. The hardware accelerator is capable of implementing the bitmap indexing algorithm and can also be reconfigured to implement other tasks. The achieved results show that the PIM approach allows to process and classify huge amounts of data locally, with a very low power consumption.

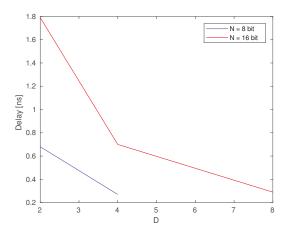

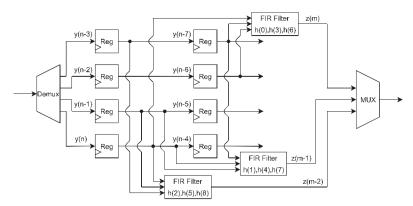

The seventh paper [7] is entitled "Digital Circuit for Seamless Resampling ADC Output Streams" and is authored by M. D'Arco et al. from the Federico II University of Naples.

This work first presents DSP (digital signal processing) techniques to change the sampling rate of digital storage oscilloscopes (DSOs) by means of digital resampling approaches. Then, it proposes a new digital circuit to be included in the acquisition channel of a DSO, between the internal analog-to-digital converter (ADC) and the acquisition memory, that allows the user to select any sampling rate lower than the maximum one with fine resolution. The new circuit exploits both digital-filtering techniques with dynamically generated coefficients and ad-hoc memory management strategies. For the circuit, both FPGA and ASIC implementations are evaluated.

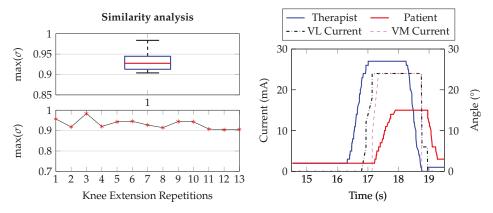

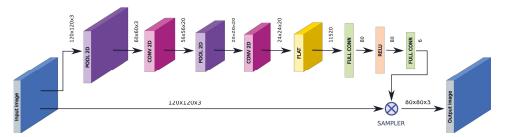

The eighth paper [8] is entitled "Embedded Bio-Mimetic System for Functional Electrical Stimulation Controlled by Event-Driven sEMG" and is authored by F. Rossi et al., a group of authors from Politecnico di Torino.

This paper deals with an assistive technology application and, particularly, with the surface electromyographic (sEMG) signal for controlling the functional electrical stimulation (FES) therapy, a technique that is being widely accepted as an active rehabilitation method for the restoration of neuromuscular disorders. To this aim, the paper proposes an embedded implementation of the average threshold crossing (ATC)-FES control system. The system was characterized and validated by analyzing the computing core and memory usage in different operating conditions, as well as measuring the system latency. Experimental results on a testing population of 11 subjects was also carried out.

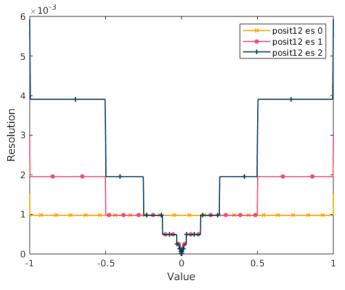

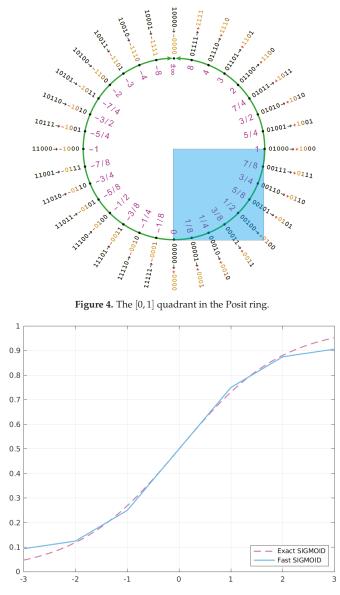

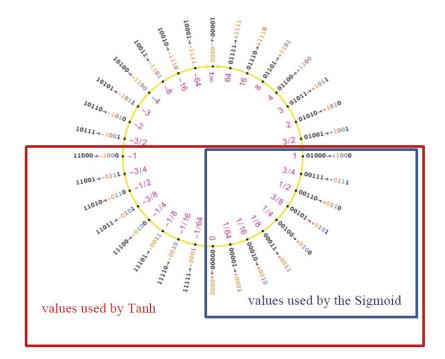

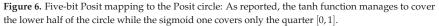

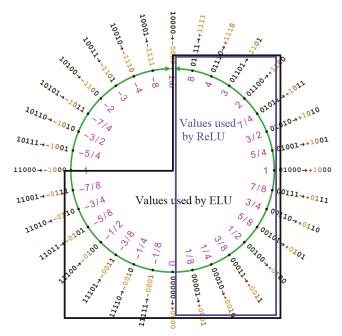

The ninth paper [9] is entitled "Fast Approximations of Activation Functions in Deep Neural Networks when using Posit Arithmetic" and is authored by M. Cococcioni et al., a group from the University of Pisa and the company MMI srl.

The paper addresses the problem of an arithmetic format to achieve real-time computing for deep neural networks (DNNs). Overcoming the limits of a classic IEEE 754 standard floating-point representation, the paper presents a new numerical format called Posits. While waiting for the widespread availability of hardware-native Posit Processing Units, the paper shows that it is possible to exploit the Posit representation and the currently available arithmetic-logic unit (ALU) in every microprocessor to speed up DNNs by manipulating the low-level bit string representations of Posits. To this aim, the paper presents a new class of Posit operators called L1 operators, which consists of fast and approximated versions of existing arithmetic operations or functions, such as the hyperbolic tangent (TANH) and the extended linear unit (ELU), while being adopted as activation functions in DNNs. The achieved results show that using either 64-bit ARM processors or x86 Intel 10-bit Posits can represent an exact replacement for 32-bit floats, while 8-bit Posits could be an interesting alternative to 32-bit floats, since their performances are a bit lower, but their high-speed and-low storage properties are very appealing. This size reduction will lead to a lower bandwidth demand and more cache-friendly codes. Moreover, with only 8- or 10-bit Posit operations, they can be tabulated in a very efficient way.

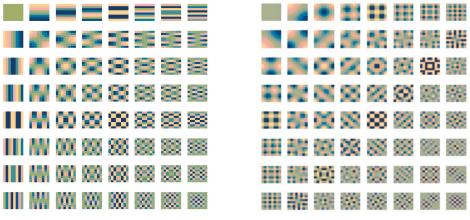

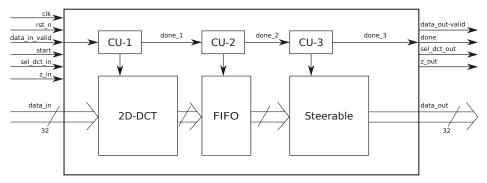

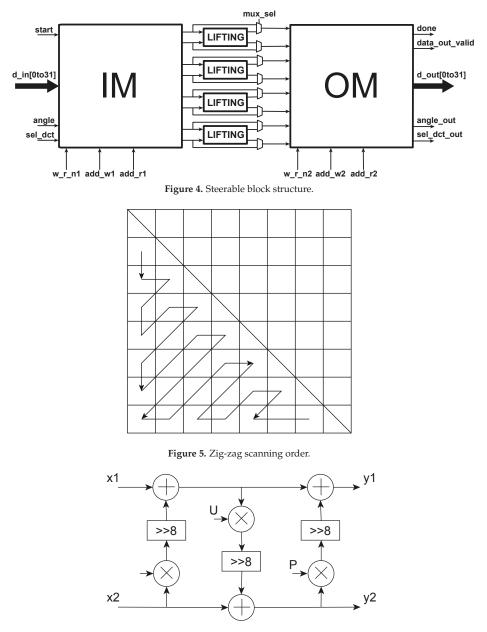

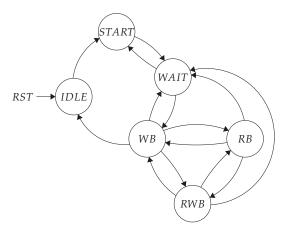

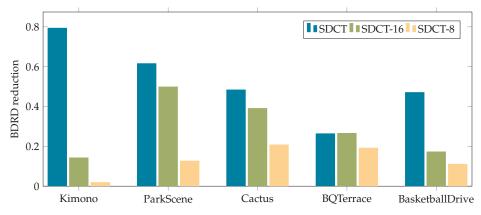

The tenth paper [10] is entitled "Steerable-Discrete-Cosine-Transform (SDCT): Hardware Implementation and Performance Analysis" and is from R. Peloso et al., a group of authors from Politecnico di Torino.

This paper deals with the hardware acceleration of new, efficient video compression methods and, particularly, the steerable discrete cosine transform (SDCT) that were proposed to exploit directional DCT using the basis of having different orientation angles. With respect to classic solutions, the SDCT leads to a sparser representation and, hence, to an improved compression efficiency. The hardware accelerator for SDCT processing proposed in this paper is able to work at about 200 MHz with a throughput of 3G sample/s and can support an 8k UHD (ultra-high definition) format at 60 frames per second.

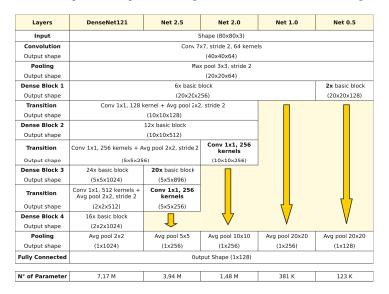

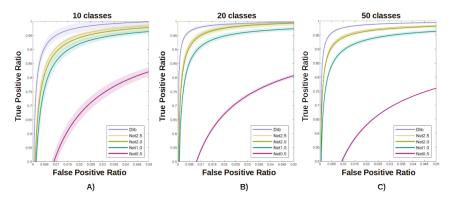

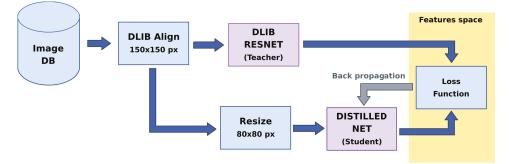

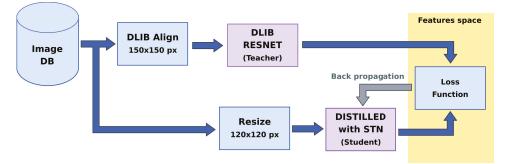

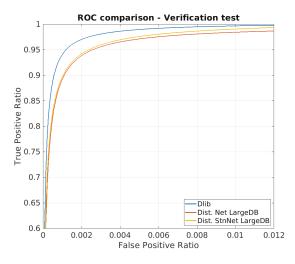

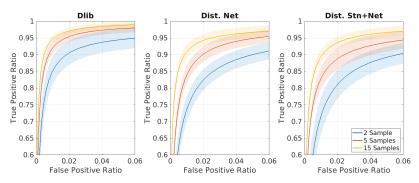

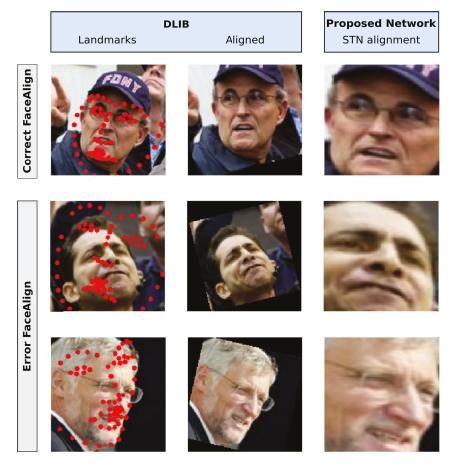

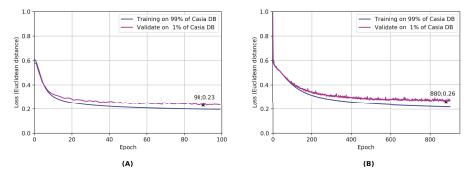

The eleventh paper [11] is entitled "Distillation of an End-to-End Oracle for Face Verification and Recognition Sensors" and is authored by F. Guzzi et al., a group of authors from the University of Trieste, the Elettra Sincrotrone Trieste S.C.p.A and the Abdus Salam International Centre for Theoretical Physics.

This paper deals with face recognition functions that are important for many applications, including security systems, inclusion devices and others. In this work, a distillation technique is applied to a complex model to enable fast recognition on low-complex hardware face recognition sensors. The proposed biometric systems are examined for the two problems of face verification and face recognition in an open set by using training/testing methodologies and datasets.

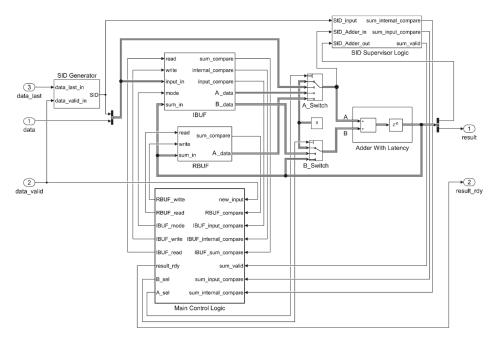

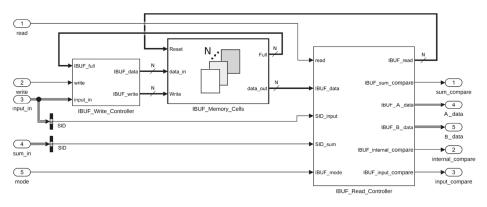

The twelfth paper [12] is entitled "A Model-Based Design Floating-Point Accumulator. Case of Study: FPGA Implementation of a Support Vector Machine Kernel Function" and is authored by M. Bassoli et al., a group of authors from the University of Parma.

This paper presents a novel model-based floating-point accumulation circuit (relying on the state-of-the-art delayed buffering algorithm) to accelerate ML functions, such as the kernel function of support vector machines. The proposed model was implemented in a Simulink environment and then implemented, by means of an HDL (hardware description language) design, in FPGA technology. The simulation results showed that it has a better performance in terms of speed and occupied area when compared to other solutions. To better evaluate its figure, a practical case of a polynomial kernel function was considered.

Finally, paper thirteen [13], "Managing Big Data for Addressing Research Questions in a Collaborative Project on Automated Driving Impact Assessment", is authored by Bellotti et al., an international group of researchers collaborating in the L3Pilot project, which is the piloting of Society of Automotive Engineers (SAE) level 3 automated vehicle functions.

The paper presents the development of a set of tools for a big data management process involving several project actors (vehicle manufacturers, research institutions, suppliers and developers), with different perspectives and requirements. In order to implement a reference methodology, the authors highlight the importance of (i) a common data format to process all the source data coming from proprietary sources, (ii) a measurement-oriented application programming interface (API) for storing and retrieving data and of a tool to synthetize meaningful data from the original, proprietary vehicular time series.

Author Contributions: All guest editors contributed equally to this editorial. All authors have read and agreed to the published version of the manuscript.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- Lu, X.; Wang, Z.; Tan, C.; Yan, H.; Si, L.; Wei, D. A Portable Support Attitude Sensing System for Accurate Attitude Estimation of Hydraulic Support Based on Unscented Kalman Filter. Sensors 2020, 20, 5459. [CrossRef] [PubMed]

- 2. Monda, D.; Ciarpi, G.; Saponara, S. Analysis and Comparison of Rad-Hard Ring and LC-Tank Controlled Oscillators in 65 nm for SpaceFibre Applications. *Sensors* **2020**, *20*, 4612. [CrossRef]

- Mestice, M.; Neri, B.; Ciarpi, G.; Saponara, S. Analysis and Design of Integrated Blocks for a 6.25 GHz Spacefibre PLL. Sensors 2020, 20, 4013. [CrossRef]

- Sakr, F.; Bellotti, F.; Berta, R.; De Gloria, A. Machine Learning on Mainstream Microcontrollers. Sensors 2020, 20, 2638. [CrossRef]

- Baldanzi, L.; Crocetti, L.; Falaschi, F.; Bertolucci, M.; Belli, J.; Fanucci, L.; Saponara, S. Cryptographically Secure Pseudo-Random Number Generator IP-Core Based on SHA2 Algorithm. *Sensors* 2020, 20, 1869. [CrossRef]

- Andrighetti, M.; Turvani, G.; Santoro, G.; Vacca, M.; Marchesin, A.; Ottati, F.; Roch, M.R.; Graziano, M.; Zamboni, M. Data Processing and Information Classification—An In-Memory Approach. *Sensors* 2020, 20, 1681. [CrossRef] [PubMed]

- D'Arco, M.; Napoli, E.; Zacharelos, E. Digital Circuit for Seamless Resampling ADC Output Streams. Sensors 2020, 20, 1619. [CrossRef] [PubMed]

- Rossi, F.; Ros, P.M.; Rosales, R.M.; Demarchi, D. Embedded Bio-Mimetic System for Functional Electrical Stimulation Controlled by Event-Driven sEMG. Sensors 2020, 20, 1535. [CrossRef] [PubMed]

- Cococcioni, M.; Rossi, F.; Ruffaldi, E.; Saponara, S. Fast Approximations of Activation Functions in Deep Neural Networks when using Posit Arithmetic. *Sensors* 2020, 20, 1515. [CrossRef] [PubMed]

- Peloso, R.; Capra, M.; Sole, L.; Roch, M.R.; Masera, G.; Martina, M. Steerable-Discrete-Cosine-Transform (SDCT): Hardware Implementation and Performance Analysis. *Sensors* 2020, 20, 1405. [CrossRef] [PubMed]

- 11. Guzzi, F.; De Bortoli, L.; Molina, R.S.; Marsi, S.; Carrato, S.; Ramponi, G. Distillation of an End-to-End Oracle for Face Verification and Recognition Sensors. *Sensors* **2020**, *20*, 1369. [CrossRef] [PubMed]

- Bassoli, M.; Bianchi, V.; De Munari, I. A Model-Based Design Floating-Point Accumulator. Case of Study: FPGA Implementation of a Support Vector Machine Kernel FunctionH. Sensors 2020, 20, 1362. [CrossRef] [PubMed]

- Bellotti, F.; Osman, N.; Arnold, E.H.; Mozaffari, S.; Innamaa, S.; Louw, T.; Torrao, G.; Weber, H.; Hiller, J.; De Gloria, A.; et al. Managing Big Data for Addressing Research Questions in a Collaborative Project on Automated Driving Impact Assessment. *Sensors* 2020, 20, 6773. [CrossRef] [PubMed]

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

# Managing Big Data for Addressing Research Questions in a Collaborative Project on Automated Driving Impact Assessment

Francesco Bellotti <sup>1,\*</sup>, Nisrine Osman <sup>1</sup>, Eduardo H. Arnold <sup>2</sup>, Sajjad Mozaffari <sup>2</sup>, Satu Innamaa <sup>3</sup>, Tyron Louw <sup>4</sup>, Guilhermina Torrao <sup>3</sup>, Hendrik Weber <sup>5</sup>, Johannes Hiller <sup>5</sup>, Alessandro De Gloria <sup>1</sup>, Mehrdad Dianati <sup>2</sup> and Riccardo Berta <sup>1</sup>

- <sup>1</sup> Department of Electrical, Electronics and Telecommunication Engineering and Naval Architecture (DITEN), University of Genova, 16145 Genova, Italy; Nisrine.Osman@elios.unige.it (N.O.); alessandro.degloria@unige.it (A.D.G.); riccardo.berta@unige.it (R.B.)

- <sup>2</sup> Warwick Manufacturing Group (WMG), University of Warwick, Coventry CV4 7AL, UK; E.Arnold@warwick.ac.uk (E.H.A.); Sajjad.Mozaffari@warwick.ac.uk (S.M.); M.Dianati@warwick.ac.uk (M.D.)

- <sup>3</sup> VTT Technical Research Centre of Finland Ltd., P.O. Box 1000, FI-02044 VTT Espoo, Finland; Satu.Innamaa@vtt.fi (S.I.); Guilhermina.Torrao@vtt.fi (G.T.)

- <sup>4</sup> Institute for Transport Studies, University Road, University of Leeds, Leeds LS2 9JT, UK; T.L.Louw@leeds.ac.uk

- <sup>5</sup> Institute for Automotive Engineering, RWTH Aachen University, Steinbachstr 7, 52074 Aachen, Germany; hendrik.weber@ika.rwth-aachen.de (H.W.); johannes.hiller@ika.rwth-aachen.de (J.H.)

- \* Correspondence: franz@elios.unige.it

Received: 28 September 2020; Accepted: 19 November 2020; Published: 27 November 2020

Abstract: While extracting meaningful information from big data is getting relevance, literature lacks information on how to handle sensitive data by different project partners in order to collectively answer research questions (RQs), especially on impact assessment of new automated driving technologies. This paper presents the application of an established reference piloting methodology and the consequent development of a coherent, robust workflow. Key challenges include ensuring methodological soundness and data validity while protecting partners' intellectual property. The authors draw on their experiences in a 34-partner project aimed at assessing the impact of advanced automated driving functions, across 10 European countries. In the first step of the workflow, we captured the quantitative requirements of each RQ in terms of the relevant data needed from the tests. Most of the data come from vehicular sensors, but subjective data from questionnaires are processed as well. Next, we set up a data management process involving several partners (vehicle manufacturers, research institutions, suppliers and developers), with different perspectives and requirements. Finally, we deployed the system so that it is fully integrated within the project big data toolchain and usable by all the partners. Based on our experience, we highlight the importance of the reference methodology to theoretically inform and coherently manage all the steps of the project and the need for effective and efficient tools, in order to support the everyday work of all the involved research teams, from vehicle manufacturers to data analysts.

**Keywords:** research data collection and sharing; connected and automated driving; deployment and field testing; vehicular sensors; impact assessment; knowledge management; collaborative project methodology

#### 1. Introduction

Solving grand challenges, such as automated connected driving, often requires collaboration across multiple domains and technical areas. A key factor in the success of collaborative research projects is the methodology and the relevant tools used to address the challenges. Some collaborative tools are well established (e.g., for managing the project and its risks, sharing documentation and source code, etc.), while others are less general and more related to application-specific tasks. The literature is rich in guidelines, techniques and tools for general project challenges (e.g., [1,2]), but there is a lack of specific information and tools for different partners to deal with sensitive data in order to answer a set of research questions (RQs) at project level. This task is gaining relevance in the current industrial research context, where there is a growing focus on big data, especially from ever more pervasive and sophisticated sensors and on extracting meaningful information from them. However, while there is significant work published on application-oriented data analysis (e.g., [3]), we found a lack in data management for assessing the impact of the new technologies' adoption.

We thus intend to investigate how to organize a robust workflow for quantitatively addressing RQs in a collaborative project sharing sensitive data among various partners, while ensuring methodological soundness and data validity and protecting partners' intellectual property (IP).

We think that the automated driving sector represents a highly significant investigation domain given the huge amount of research that is being carried out in the field (e.g., [4–6]). As an example use case, we thus discuss our experience in a 34-partner EU-funded project, L3Pilot, which is assessing the impact of Society of Automotive Engineers (SAE) Level 3 (L3) and Level 4 (L4) automated driving functions (ADFs). Tests are being conducted in pilots in 10 European countries, with vehicles provided by 13 vehicle owners (original equipment manufacturer (OEM), suppliers or research facilities).

The L3Pilot RQs cover different leading-edge ICT adoption impact assessment areas, including (i) technical performance of the tested L3 ADFs, (ii) user acceptance and behaviour, (iii) impact on traffic and mobility and (iv) societal impacts (see L3Pilot Deliverable D3.1 [7]). This paper presents how we implemented a reference methodology for large scale pilots and field operational automotive tests—namely Field opErational teSt support Action (FESTA) [8]—in order to get the quantitative information needed to answer the project's research questions (RQs). A key novelty in this process is the use of the Consolidated Database (CDB), which allows data from all the pilot sites to be shared anonymously and securely amongst project partners to facilitate data analysis aimed at answering the project's RQs.

This paper presents the challenges we have faced in implementing the methodology and consequently developing a coherent, robust workflow. First, we needed to quantitatively capture each RQ's requirements in terms of raw data to be collected during the tests, so as to allow a proper investigation. Then, we set up the needed tools in an iterative development process involving several partners (vehicle manufacturers, research institutions, suppliers and developers), with different perspectives and requirements. Finally, we deployed the system so that it is fully integrated within the project's data toolchain and usable by all the partners.

It is important to highlight that this paper focuses on the method, workflow and tools and does not discuss the actual domain-specific data, which will be the subject of another publication.

The remainder of the paper is organized as follows. Section 2 gives an overview of the related work, while Section 3 presents the methodology and the consequent specifications for the target process. Section 4 presents the design and implementation of the CDB. Section 5 discusses what we have learnt from the deployment of the system, while Section 6 draws the final conclusions.

#### 2. Related Work

Beside the general overviews cited in the Introduction, there is a rich literature on privacy and risk management in projects. For instance, [9] deal with Risk Assessment in Multi-Disciplinary Engineering Projects, [10] with privacy risks when sharing data on information systems. Furthermore, [11] investigates the validity of sharing privacy-preserving versions of datasets. They propose a

Privacy-preserving Federated Data Sharing (PFDS) protocol that each agent can run locally to produce a privacy-preserving version of its original dataset. The PFDS protocol is evaluated on several standard prediction tasks and experimental results demonstrate the potential of sharing privacy-preserving datasets to produce accurate predictors. In addition, [12] provides an extensive review of data analytic applications in road traffic safety, with particular attention to crash risk modelling.

Furthermore, [13] deals with integrating diverse knowledge through boundary spanning processes, with a particular focus on multidisciplinary project teams. The concept of a Project Consortia Knowledge Base (PC-KB) is presented in [14] in an integration framework based on semantic knowledge that facilitates project-level communication as well as access to project data across tool and partner boundaries.

Commercial companies (e.g., Amazon, Microsoft, Google) have established efficient cloud ecosystems for data management providing very powerful services, but they rely on proprietary technologies, with very limited interoperability and development opportunities for third parties. However, we could not find in the literature guidelines on how to exploit these cloud technologies to support project partners in processing big data to address quantitative research questions.

In recent years, a number of field operational tests (FOTs) have been executed to test new Advanced driver-assistance systems (ADAS) in authentic traffic conditions, involving thousands of drivers (e.g., euroFOT [15,16]). With a view to ensure scientific soundness, the Field opErational teSt support Action (FESTA) project developed a methodology for field operational tests (FOTs), with three main focuses: user, vehicle, context [8]. This methodology is described in the FESTA Handbook which has been frequently updated according to the latest lessons learned [17]. It records lessons learned and provides best practices collected in several European FOTs in the last ten years. L3Pilot decided to adopt this methodology, as illustrated in the next section.

Several collaborative industrial research projects have been conducted in Europe addressing the first levels of automated driving. The AdaptIVe project developed several functionalities providing various levels of driver assistance, such as partial, conditional and high automation [18]. Drive C2X investigated cooperative awareness, which was enabled by periodic message exchange between vehicles and roadside infrastructure [19,20]. The FOT-Net Data project prepared the Data Sharing Framework, which provides hands-on recommendations on how to manage data sharing of data from the transportation research area [21]. The TEAM project developed an app suite for supporting collaborative road mobility [22].

#### 3. Methodology

#### 3.1. Overview

The RQs for all impact areas in the L3Pilot project (listed in the Introduction, see also [7]) were generated through the top-down approach recommended by the FESTA Handbook [17]. The process began with a review of the descriptions of automated driving functions (ADFs) that were going to be piloted during the project. Therefore, in the early stages, only high-level RQs (Levels 1 and 2 in Table 1 example) were defined, to meet the project objectives.

| Item                                   | Example                                                                                                                                                                                                                   |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Evaluation area                        | Technical and traffic                                                                                                                                                                                                     |

| RQ level 1                             | "What is the impact of the ADF on driving behaviour?"                                                                                                                                                                     |

| RQ level 2                             | "What is the ADF impact on driven speed in different scenarios?"                                                                                                                                                          |

| RQ level 3                             | "What is the ADF impact on driven speed in driving scenario X?"                                                                                                                                                           |

| Hypothesis                             | Example 1: "There is no difference in the driven mean speed for the ADF compared to manual driving."<br>Example 2: "There is no difference in the standard deviation of speed for the ADF compared to<br>manual driving." |

| Required Performance indicators (PIs)  | Mean speed, standard deviation of speed, max speed, plot (speed/time)                                                                                                                                                     |

| Logging requirements/sensors available | CAN bus of vehicle: Ego speed in x direction                                                                                                                                                                              |

Table 1. An example on definition of logging requirements for a hypothesis [7].

In such a top-down approach, the generation RQs and hypotheses typically is based on theoretical understanding of the mechanisms how different impact areas are influenced. Thus, the process was started with an extensive literature review, which aimed to identify the key elements related to different impact areas. In addition, the review aimed to find knowledge gaps. The process was iterative (generate RQs, review them) to ensure that all major topics were covered and RQs were well formulated. In this step, a wide range of RQs was created, not limiting them by means of any single data collection method. The RQs were simply based on literature and the experience of the project members in previous, related work. The generation of the first (higher) level of research questions was structured according to the four L3Pilot evaluation areas. The second stage involved the development of more detailed RQs related to specific components of the higher-level questions, where appropriate. For each RQ, the underlying hypothesis is then made explicit. Table 1 provides an example in the Technical and Traffic area.

The top-down approach to setting RQs was followed by a bottom-up revision. In that phase, the RQs were cross-checked for their feasibility in terms of the data generation, a suitable experimental procedure at the pilot sites and availability of evaluation methods and tools [23]. RQs were prioritized based on test site characteristics, data coding and processing demand, ethical constraints, resources and time available in the project and importance for the research. In this phase, some of the first two levels of RQs were updated to be in line with the evaluation possibilities in the project.

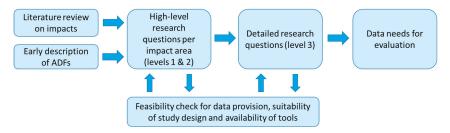

In line with the FESTA Handbook, the next steps after generation of the hypotheses concerned the definition of the relevant performance indicators (we cover them in detail in the next subsections) and of the logging needs related to them. Here, we differentiated the subjective and objective data [7]. Questionnaires would collect subjective data across test participants (drivers and possible passengers), and objective data would be collected mostly from the data loggers of the test vehicles, additional cameras installed on them, and, when necessary, from external data sources (e.g., weather information, road type, etc.) [24]. Figure 1 provides an overview of the RQ definition and implementation workflow.

Figure 1. Overview of the research questions (RQ) definition and implementation workflow.

#### 3.2. Objective (Vehicular) Data

The adopted methodology requires defining (i) the performance indicators (PIs) through which the RQs can be answered, (ii) the derived measures that are needed to calculate these indicators, and (iii) the actual vehicular signals that are needed to calculate these measures (see the full process in [24]). Beside the standard vehicular signals (e.g., speed, acceleration, pedal activity, etc.), source data come also from state-of-the-art automated driving sensors, such as cameras, Light Detection and Ranging (lidars) and radars. As a single PI may be derived from different alternative derived measures—and a single measure from different alternative signals—a collaboration was set up among the evaluation team (who express the data needs), the vehicle owners (who provide and share the data) and those responsible for developing the processing tools. The collaboration aimed at defining performance indicators (PIs) and derived measures for all RQs [7], as illustrated in the Table 1 example. The overall analysis defined a set of signals to be provided by all the vehicle owners that are specified in a common data format [25].

Four different types of PIs (Table 2) were defined to be computed from the vehicular signals and stored in the Consolidated database (CDB) as the factual basis for answering the RQs. PIs are

typically constituted by statistical aggregations (e.g., avg/std/min/max) in significant intervals of a trip. Two PI types are computed at trip level: while Trip\_PIs are general indicators synthetizing a trip, ScenarioSpecific\_TripPIs are computed aggregating trip segments from a specific scenario only. The other two PI types (namely, ScenarioInstance\_PI and Datapoints) are much more specific, as they are computed for each instance of a given driving scenario detected during a trip. Table 2 provides an overview of the L3Pilot vehicular PI types, with some examples. The table reports only two Datapoint types, as examples, since there is one datapoint type for each driving scenario type.

| PI Type                                              | Description                                                                                                                                                                                                 | Example of PIs                                                                                        |  |  |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|

| Trip PI                                              | PIs computed at trip level                                                                                                                                                                                  | Mean (stdev) longitudinal<br>acceleration, percentage of time<br>elapsed per driving scenario type    |  |  |

| Scenario specific Trip PI                            | PIs computed at trip level but only when a specific driving scenario occurs.<br>Example of driving scenarios, described later, are: driving in a traffic jam,<br>lane change.                               | Mean duration of sections with speed lower than a threshold                                           |  |  |

| Scenario instance PI                                 | PIs computed for each instance of a driving scenario. The same PIs are computed in each type of scenario                                                                                                    | Mean (stdev) time headway,<br>mean(stdev) position in lane                                            |  |  |

| Datapoint for a Following<br>a lead vehicle scenario | Datapoint PIs are computed for each instance of a driving scenario. Different types of scenario have a different datapoint structure. Here we report two examples.                                          | Mean (stdev) relative velocity,<br>Time headway at minimum time<br>to collision                       |  |  |

| Datapoint for Approaching<br>a traffic jam scenario  | Datapoints are used as input for the impact assessment by either resimulating driving scenarios or constructing artificial scenarios based on statistical analyses of scenarios encountered during piloting | Vehicle speed at brake or steering<br>onset, Longit. position of object at<br>brake or steering onset |  |  |

Table 2. An overview of the L3Pilot vehicular sensor data performance indicators (PI) types.

Several research questions required analysing context data beyond the actual vehicular signals and questionnaire answers. Context data were useful, particularly to segment information so to allow comparisons and more focused analysis. Among context data we highlight:

- Experimental conditions. Different conditions have to be considered, such as: baseline, ADF not available, ADF off, ADF on.

- Road types. Tests are performed on various road types, such as: motorways, major urban arterials, other urban roads.

- Driving scenarios. The system has to track different types of driving scenarios, that are typical driving situations, such as uninfluenced driving, lane change, lane merge, following a lead vehicle, etc. Scenarios are computed by the L3Pilot data toolchain, processing the vehicular time series [26].

So, Trip PIs are to be computed for different segments, based on the actual experimental condition (i.e., baseline, ADF off, ADF on) and road type; and Scenario Instance PIs are to be segmented not only on the basis of the scenario type itself, as per definition, but also considering the different experimental conditions and road types.

Other metadata were mandated as well, such as driver type (professional or ordinary), temperature and speed limits, in order to better characterize the context of each PI measurement.

#### 3.3. Confidentiality

There are several external factors that impact the extent to which the project RQs can be addressed. For example, when assessing the effects of the ADFs on driving (i.e., observed differences between the ADF and human driver with respect to, e.g., car-following behaviour), the maturity of the system is important to take into account and whether the test vehicle represents the driving experience of a mature product. In addition, to get the open road testing permission for an ADF, public authorities demand safety of testing. The details of the driving dynamics can also be a sensitive topic to the manufacturers. For that reason, it is important to make sure that vehicle telemetry data are kept confidential, and that the manufacturers or their tested systems cannot be identified, ranked or compared from any information shared within the project or with others, as their competitiveness at a crucial development stage would be compromised. Another challenge for gaining a good understanding of the impacts of ADFs is that the data is limited to specific test routes, speed ranges and weather conditions, which are defined by the function's Operational Design Domains (ODD). All pilot studies must also adhere to the rules of respective OEM and to national regulations on testing of automated driving, like the mandatory use of safety drivers in certain situations. Therefore, all this limits the possibilities of the project to address all of the RQs set for evaluation. To address these limitations, L3Pilot has specified a common methodology, data format and analysis toolkit, which will be used across all pilot sites and for evaluation of different ADFs [26]. Other solutions include the use of a dedicated research partner for analysis of data from a single pilot site to ensure that the access to commercially sensitive data is controlled and that data is pseudonymised before uploading to the CDB and shared among partners.

The CDB includes aggregated data from several sites in such a manner that commercially sensitive information is protected. A key requirement for being able to merge data is, that, in addition to protecting the privacy of manufacturers, the result is meaningful for the user of the result as such or those performing the following evaluation steps. In other words, the results must describe the impacts of automated driving but without compromising this privacy. The merging of data from different sites also leads to the outcome where the L3Pilot results do not represent the impact of single (OEM)-specific ADFs but the generic impacts that can be expected once these systems are introduced to the road [27].

As confidentiality is a key requirement when sharing valuable data, three main constraints were applied to data uploaded to the CDB:

- It should not be possible to identify which pilot site the data came from. For example, attention was paid not to insert metadata, such as temperature and date, that might hint to identify the location of the pilot site.

- No personal data about the driver, passengers nor other test participants.

- No possibility to characterize in detail the behaviour of ADFs. This was achieved by the fact that vehicular sensor data are not uploaded to the CDB as time series but as summarised performance indicators, which are described later.

As an ID of the trip and of the user was considered necessary to allow data owners to track their data in the CDB (also to update or delete them, if needed), an SHA-256 hashing-based pseudonymization was implemented [26]. Knowing the encrypted IDs, the data owners can track their data in the CDB, while such IDs are not decipherable by the other users.

Despite these constraints, there is no 100% guarantee that data cannot be linked to a pilot site, if malicious and highly sophisticated techniques we did not foresee are applied to the data.

#### 3.4. Subjective Data

While until now we have focused on vehicular sensor data, a complete assessment of ADF functions also requires processing subjective data. One of the primary sources of data for the user and acceptance evaluation within L3Pilot is a pilot site questionnaire, which gathers subjective data from participants at the various pilot sites (for the full questionnaire see [23]). L3Pilot tests four different types of Automated Driving Functions (ADFs), including motorway, traffic jam, urban and parking. We developed a base questionnaire for background information, including questions related to sociodemographic factors, vehicle use and purchasing decisions, driving history, in-vehicle system usage, activities while driving, trip choices and mobility patterns. The data collected in the first part will be used to create different user groups for the user and acceptance evaluation. We also included questions specific to the ADF. For example, these questions assess various aspects of participants' initial reactions to using the particular ADF. To understand whether having daily access to the ADF might change any decisions or behaviours, they were reasked questions about vehicle use and purchasing decisions, driving tasks, trip choices and mobility patterns.

#### 3.5. Workflow Requirements

From a process viewpoint, requirements included efficiency of workflow, and in particular, upload and download of data to/from the CDB. We highlight in particular:

- Recursive upload. The user should define the source directory and the system should automatically detect the files to be processed and do the upload of their contents to the CDB. All the subdirectories should be recursively explored.

- CSV download. The system should allow the possibility of downloading contents in either ison or .csv format, which is the typical input format for the statistical processing packages used by the analysts. The granularity of download is at the feature level. That is, a user should be able to download all the measurements of all the accessible features (Trip\_PI, Scenario\_Instances, Datapoints, etc.) or only some of them.

- Postediting of the performance indicators. Once the performance indicators for a trip are computed, the data provider should be able to check and edit them before the upload to the CDB.

The above requirements were typically defined during the development, in an iterative fashion, as the data providers and analysts suggested improvements based on their working experience.

#### 4. Design and Implementation of the Consolidated Database (CDB)

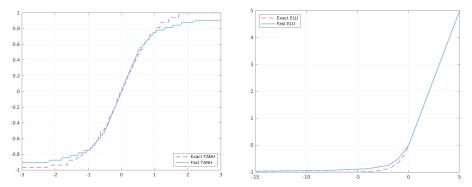

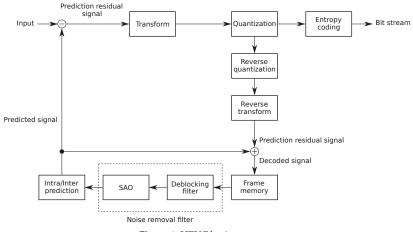

In order to meet the above presented methodological goals, L3Pilot defined a data flowchart (Figure 2), which is the basis for the system architecture. The workflow starts with data collection at the pilot sites and ends with data analysis by impact experts. At the beginning there is a different processing for vehicular sensor data (Section 4.1) and subjective data (Section 4.2), then these data are managed seamlessly. The first, fundamental step consists in translating all the heterogeneous data sources in the Common Data Format (CDF), which has been described in [25] and made publicly available [28]. The CDF postprocessing phase is described in detail in [26], while this paper focuses on the CDB. In the CDF postprocessing, the project's analysis partners use the Derived Measures—Performance Indicator Framework (DM-PI-Framework) to enrich the vehicular signal time series from a vehicle's trip with the computed derived measures (DM) and the detected driving scenarios, which are fundamental for the computation of CDB PIs, as described in the next subsection.

Figure 2. L3Pilot data workflow.

#### 4.1. CDB PI Computation for Vehicular Sensor Data

The CDB PI computation step consists in synthesizing the vehicular time series so that the CDB stores only high-level information that allows tackling the project RQs, without compromising the confidentiality of the single-vehicle owner companies. This stage is undertaken by the CDB Aggregator module, which processes HDF5 files (one per each trip), containing the original time series formatted in CDF and enriched by the DM-PI-Framework's, as mentioned above. The output of the CDB Aggregator module is represented by a set of .json files storing the computed PIs. Processing an input HDF5 file, the Aggregator produces one .json file for each one of the four PI types defined in Table 3 (i.e., Trip PI, Scenario Instance PI, etc.). The .json files are ready to be uploaded to the CDB, for instance through a well-established Application Programming Interface (API) client such as Postman, or, better, through the Uploader, a dedicated module described in Section 4.3. The same information contained in the .json files is also saved in corresponding .csv files, that are more easily readable by the analysts.

| Role      | Description                                                                                                                       | L3Pilot Configuration/Notes                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Providers | Provider users are data owners.<br>They can upload data and retrieve<br>only their own data.                                      | In L3Pilot, Providers are vehicle owners or their in-depth analysis partner for vehicular sensor data and pilot leaders for subjective data                                                                                                                                                                                                                                                        |

| Analysts  | Analyst users cannot upload data<br>but can see all the data of their<br>typology.                                                | In L3Pilot, analysts are the experts responding to the research questions.<br>Utilizing the Measurify's Right resource, we have implemented three<br>typologies, matching the type of relevant data: Technical and Traffic<br>analysts, that access all vehicular sensor data apart from the Datapoints;<br>Impact analysts, that access Datapoints; User analysts, that access<br>subjective data |

| Admin     | The admin configures the CDB<br>(e.g., setting up the users and<br>rights) and can see (only in case of<br>need) all data entries | Given the adopted ID pseudonymization, the admin cannot resolve IDs (i.e., relating a data entry with its vehicle owner or driver).                                                                                                                                                                                                                                                                |

Table 3. Measurify user roles and rights. General description and mapping in the L3Pilot case.

The CDB Aggregator module consists of a set of Matlab scripts. Figure 3 provides a high-level outlook of the programme, with three main phases: initialization, reading signals from the input HDF5 file; processing loop; and a final saving of the four types of PIs. The processing loop is the core of the programme, as it processes the time series and segments the computation of the PIs according to the context information presented in Section 3.2. First, the experimental condition is considered. Then, for each identified segment, the road type is considered. This level of segmentation leads to the computation of Trip PIs. Computation of Scenario Instance PIs and Datapoints requires further segmentation of the timeline based on the detected driving scenarios. Scenario Specific Trip PIs introduce the need for accumulating the indicator values across all the scenario instances in the trip. Similarly, the length of each scenario instance is needed for the Trip PI indicator reporting the percentage of time passed in each scenario within the trip.

Figure 3. Flowchart of the vehicular sensor data processing Matlab scripts.

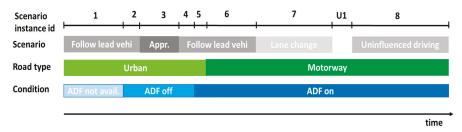

An example of the resulting segmentation is reported in Figure 4, where we can see eight different scenario instance PIs computed. A slice, indicated as Unrecognized 1 (U1), will not produce Scenario Instance PI, nor Datapoints, nor Scenario Specific Trip PI, as a scenario could not be detected there. However, the signal values contained in that segment will contribute to the Trip PI indicators in the ADF on condition.

Figure 4. Example of scenario segmentation during a trip.

#### 4.2. Subjective Data Processing

When conducting studies across multiple sites, it is essential that any data collection methodologies are applied uniformly. For example, the pilot site questionnaires are administered across all pilot sites, which vary in many respects (e.g., country language), but most relevant here is the interexperimenter variability. Therefore, to control for this variability, the questionnaire was implemented using the online tool LimeSurvey, where the only task for the pilot site staff was to transfer the translated versions of the questionnaire into the online LimeSurvey platform, enabling the administration of the questionnaire via laptops or mobile tablet computers. The use of LimeSurvey also ensures that the data output aligns with the CDF used by a consortium-wide consolidated database.

The imported surveys may then be customised and translated versions can be implemented accordingly. Pilot sites are then able to export their newly generated surveys and/or to export their results to CSV or SPSS format (Statistical Package for the Social Sciences). Note: the SPSS output of the reference version of the questionnaire is in line with the common data format requirements for the consolidated database. Although selected partners/pilot sites responsible can create, edit or view a survey, it is imperative that the questionnaire item codes are not changed, as this is the mechanics which allows tracking responses from different pilot sites. Thus, to ensure that a CDF was applied across pilot sites, instructions on the questionnaire implementation, administration and metadata were defined at the consortium level.

In terms of the administration of the questionnaire, there are differences between pilot sites regarding the length and number of drives by each participant. Therefore, the project recommendation is that the questionnaire should be completed after the last test ride, irrespective of whether a driver has multiple drives (see further details in [29]).

Following the completion of all questionnaires, each pilot site must export the test participants' response results to the SPSS file format (as illustrated in Figure 5), to ensure a common data format in the CDB for the user and acceptance evaluation area.

Quality checking has been implemented both for vehicular and subjective data. In this paper, we briefly present the procedure we set up for this second type of data.

Using the common LimeSurvey implementation should ensure that all questionnaire items and responses follow the nomenclature set out in the CDF for the official L3Pilot questionnaire. However, some partners used other implementations, and there is always the chance that some item names and codes deviate from the original. A data format map is prepared for each type of questionnaire, with all expected questions and possible answer codes and ranges. Before being uploaded to the CDB, a Matlab data quality script parses each questionnaire outcome file, searching for inconsistencies compared to the CDF.

| EXAMPLE_TJM Questionnaire_SPSS output_Untitled2.sav () - IBM SPSS Statistics Data Editor<br>File Edit View Data Transform Analyze DirectMarketing Graphs Utilities Add-ons Window Help |               |         |       |   |                                                                                       |                                          |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------|-------|---|---------------------------------------------------------------------------------------|------------------------------------------|--|--|

| 2 ■ 0 □ ~ 2 ■ ± 1 ■ A ■ 2 ■ 4 =                                                                                                                                                        |               |         |       |   |                                                                                       |                                          |  |  |

|                                                                                                                                                                                        | Name          | Type    | Width | D | Label                                                                                 | Values                                   |  |  |

| 1                                                                                                                                                                                      | id            | Numeric | 7     | 0 | id                                                                                    | None                                     |  |  |

| 2                                                                                                                                                                                      | submitdate    | Date    | 23    | 2 | submitdate                                                                            | None                                     |  |  |

| 3                                                                                                                                                                                      | lastpage      | Numeric | 7     | 0 | lastpage                                                                              | None                                     |  |  |

| 4                                                                                                                                                                                      | startlanguage | String  | 20    | 0 | startlanguage                                                                         | None                                     |  |  |

| 5                                                                                                                                                                                      | q_            | String  | 31    | 0 | Seed                                                                                  | None                                     |  |  |

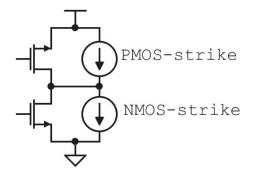

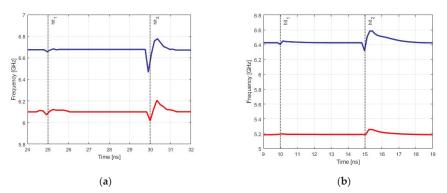

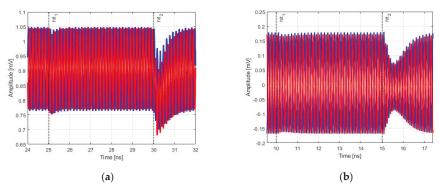

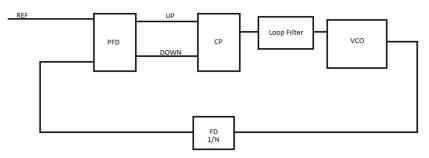

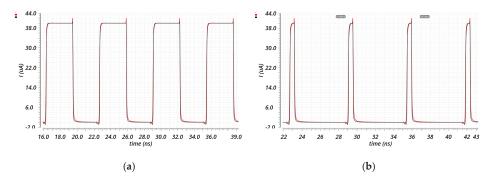

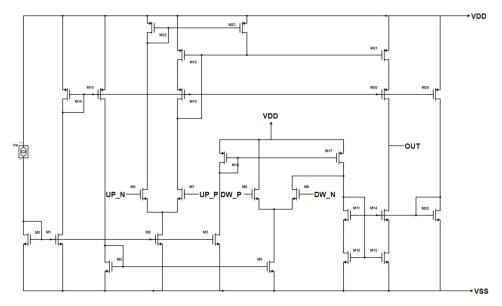

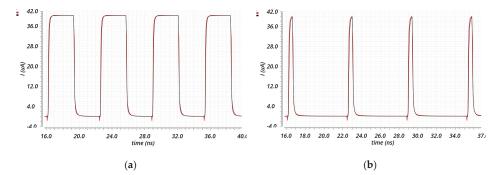

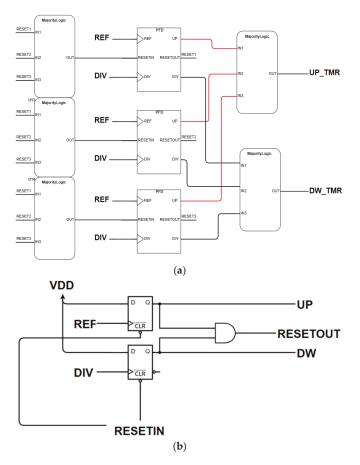

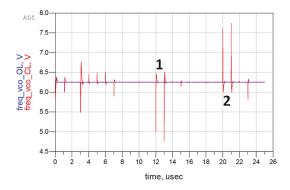

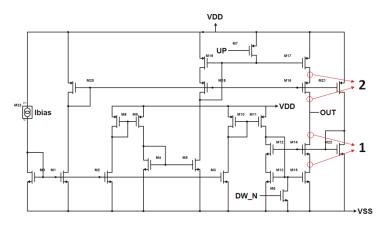

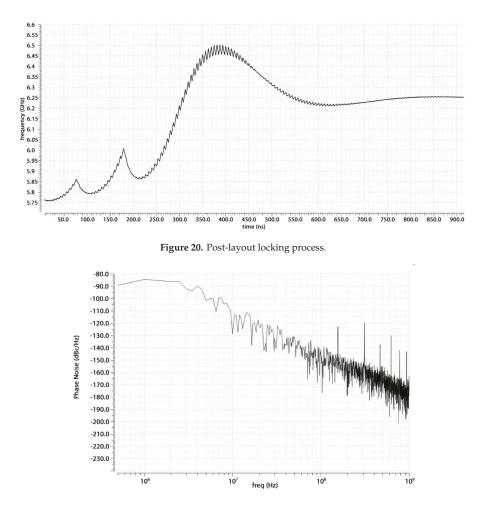

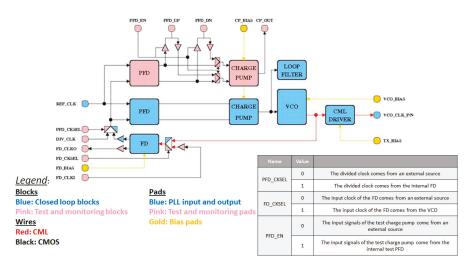

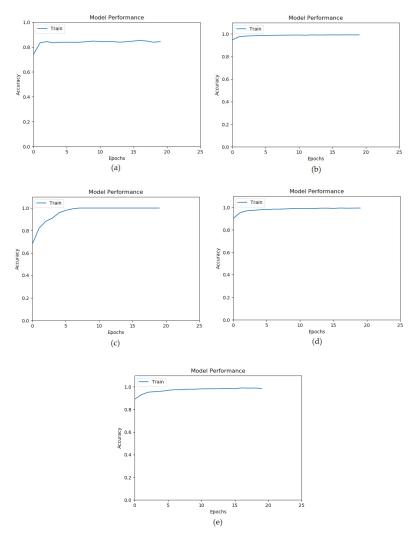

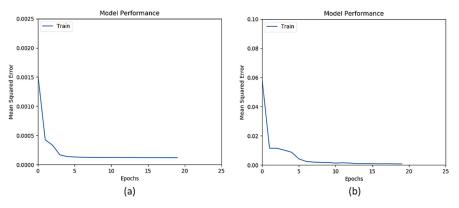

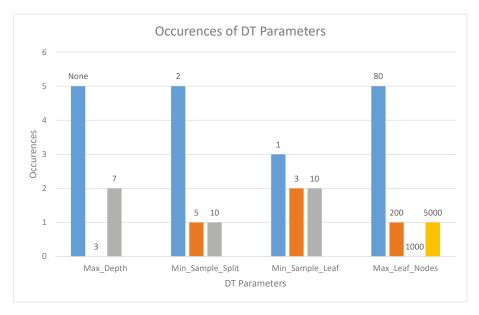

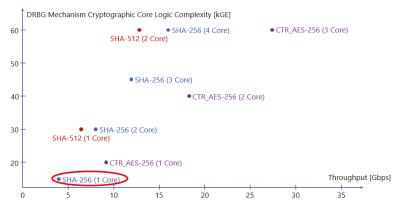

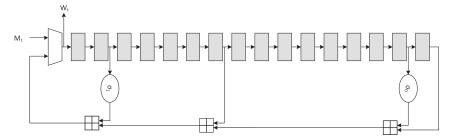

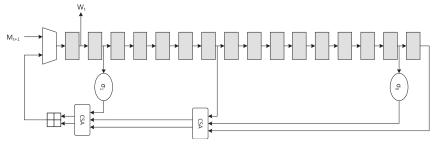

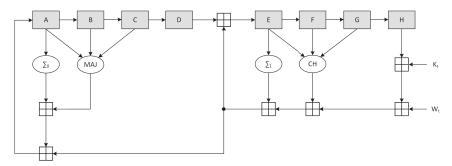

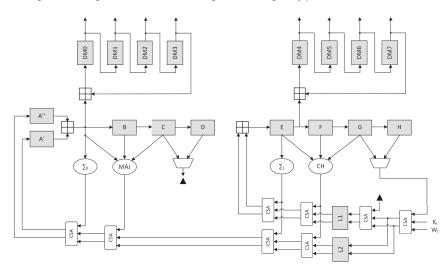

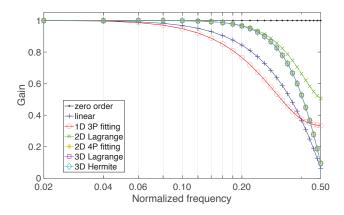

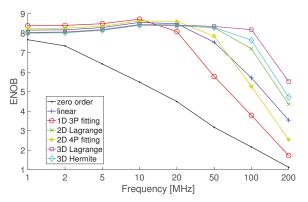

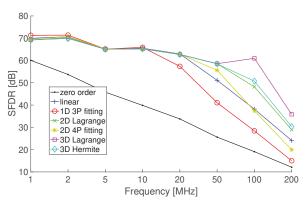

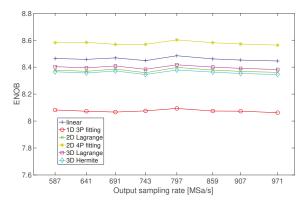

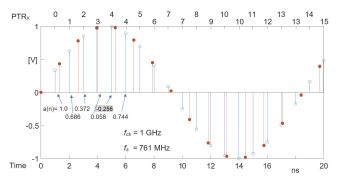

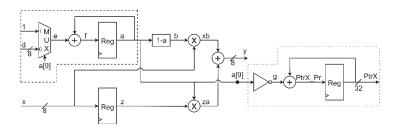

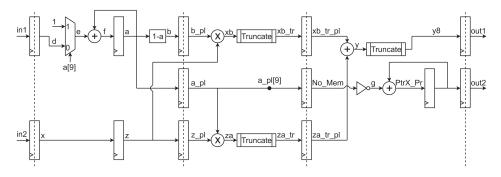

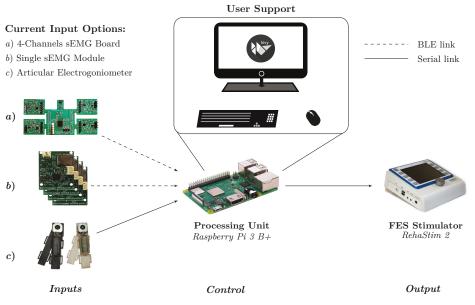

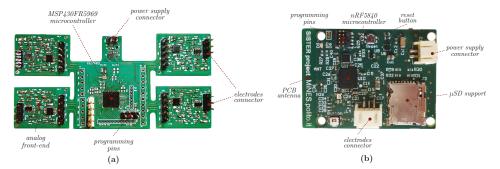

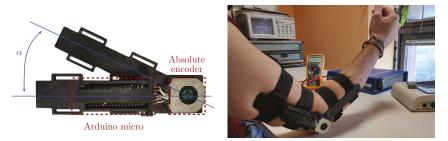

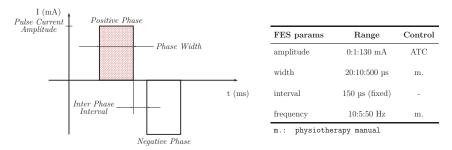

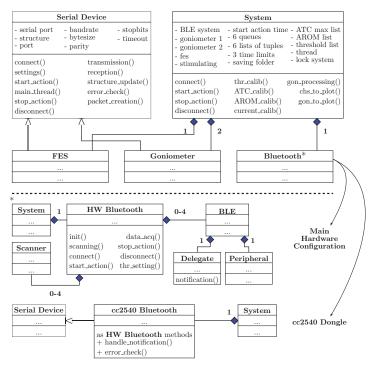

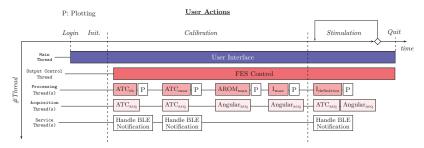

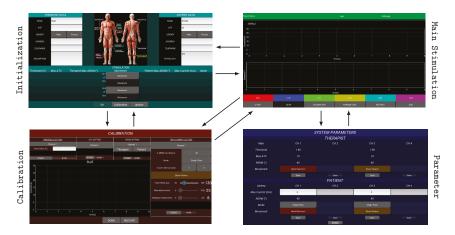

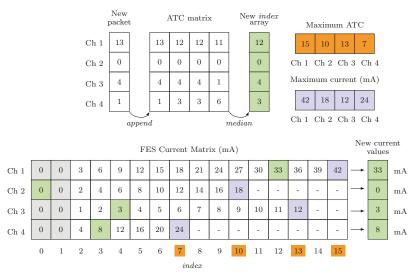

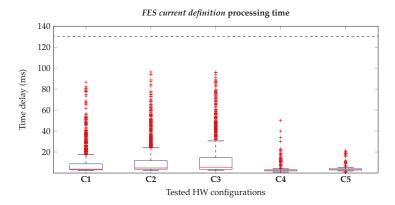

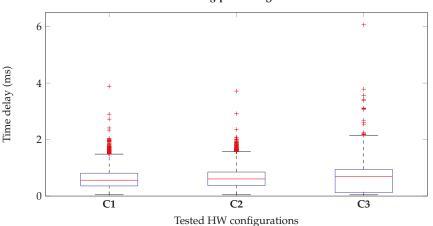

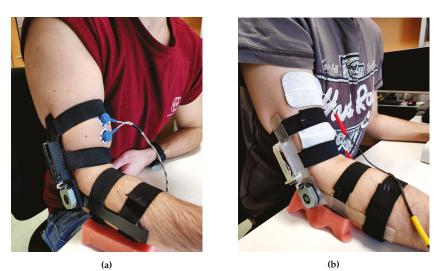

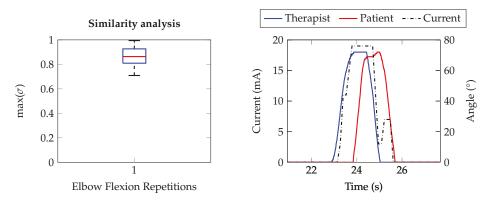

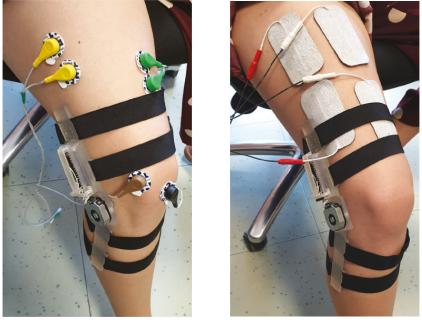

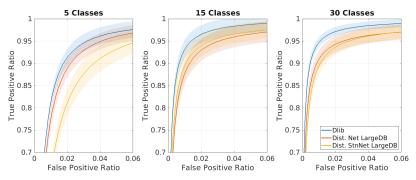

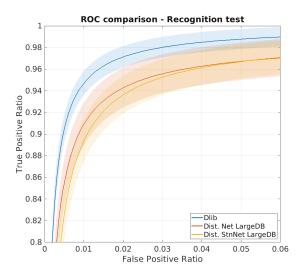

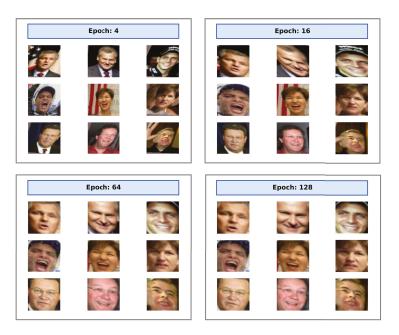

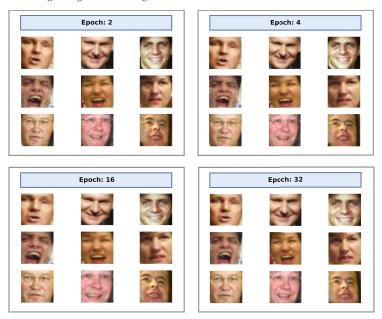

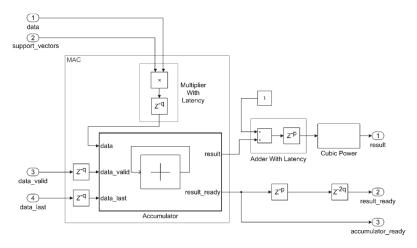

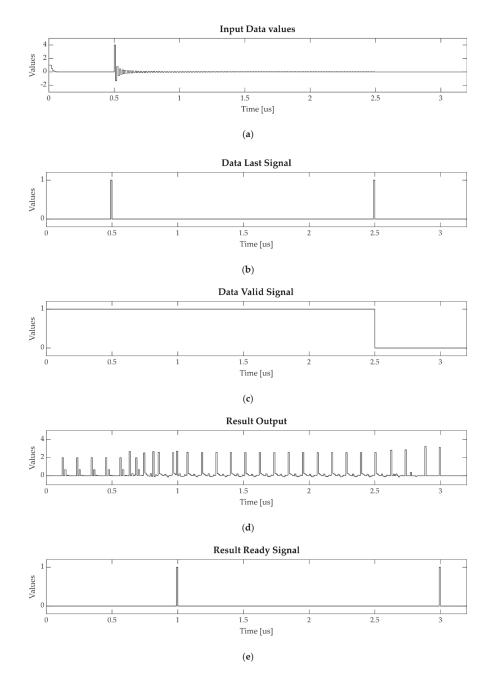

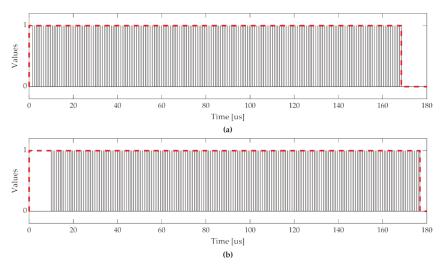

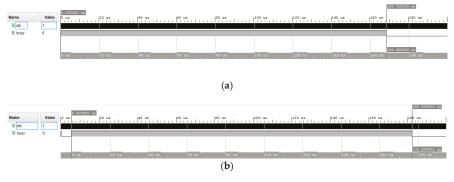

| 6                                                                                                                                                                                      | startdate     | Date    | 23    | 2 | startdate                                                                             | None                                     |  |  |