#### University of Wisconsin Milwaukee

#### **UWM Digital Commons**

Theses and Dissertations

December 2021

## Common-Mode Modeling of Neutral Point Clamped Converter **Based Dual Active Bridge**

Ryan James Olson University of Wisconsin-Milwaukee

Follow this and additional works at: https://dc.uwm.edu/etd

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Olson, Ryan James, "Common-Mode Modeling of Neutral Point Clamped Converter Based Dual Active Bridge" (2021). Theses and Dissertations. 2823.

https://dc.uwm.edu/etd/2823

This Thesis is brought to you for free and open access by UWM Digital Commons. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of UWM Digital Commons. For more information, please contact scholarlycommunicationteam-group@uwm.edu.

# COMMON-MODE MODELING OF NEUTRAL POINT CLAMPED CONVERTER BASED DUAL ACTIVE BRIDGE

by Ryan Olson

A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of

Master of Science in Engineering

at

The University of Wisconsin-Milwaukee  ${\small \mbox{December}\ \ 2021}$

#### ABSTRACT

## COMMON-MODE MODELING OF NEUTRAL POINT CLAMPED CONVERTER BASED DUAL ACTIVE BRIDGE

by

Ryan Olson

The University of Wisconsin-Milwaukee, 2021 Under the Supervision of Professor Robert Cuzner

Modern power converters designed with wide-bandgap semiconductors are known to generate substantial conducted electromagnetic interference as a side effect of high edge rate and high frequency switching. With the advancement in power electronic converters, the significant EMI challenges need to be addressed for distribution level power systems. The goal is to provide a computationally efficient method of EMI characterization for conducted emissions for this future generation of power distribution systems. The first step in making this possible is through creating an accurate EMI characterization platform for the neutral point clamped dual active bridge. In this thesis, a formalized common-mode modeling approach is carried out for transforming this mixed-mode power system into its common-mode equivalent circuit. The approach is validated through comparison of time-domain waveforms predicted by detailed mixed-mode and common-mode equivalent models of the representative power distribution system, with a proposed future validation using hardware measurements. The experimental studies highlight the utility of the proposed modeling approach to assess design mitigation strategies.

© Copyright by Ryan Olson, 2021 All Rights Reserved

| This thesis work is dedicated to my mother, Peggy, who has always loved me         |

|------------------------------------------------------------------------------------|

| unconditionally and whose good examples have taught me to work hard for the things |

| that I aspire to achieve.                                                          |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

## TABLE OF CONTENTS

| 1 | Intr | roduction                                                 | 1  |

|---|------|-----------------------------------------------------------|----|

|   | 1.1  | Power Systems                                             | 1  |

|   |      | 1.1.1 Power Electronics                                   | 2  |

|   | 1.2  | Designing Electrical Systems                              | 3  |

|   |      | 1.2.1 Grounding                                           | 3  |

|   | 1.3  | Electrical Distribution Systems                           | 4  |

|   | 1.4  | Objective and Motivation                                  | 9  |

|   | 1.5  | EMI Characterization Methodology                          | 9  |

|   | 1.6  | System Description                                        | 11 |

|   | 1.7  | Thesis Organization                                       | 12 |

| 2 | Sta  | te of the Art Methodologies                               | 15 |

|   | 2.1  | White-box Modeling                                        | 16 |

|   | 2.2  | Black-box Modeling                                        | 17 |

|   | 2.3  | Gray-box Modeling                                         | 17 |

|   |      | 2.3.1 Unterminated Behavioral Modeling                    | 22 |

|   |      | 2.3.2 CM Equivalent Modeling with Dominant EMI Sources    | 27 |

|   | 2.4  | Transformer Modeling                                      | 31 |

| 3 | Cor  | nmon Mode Modeling of Asymmetric Power Electronic Systems | 35 |

|   | 3.1  | Methodology                                               | 36 |

|   |      | 3.1.1 Common-Mode and Differential-Mode Definitions       | 37 |

|   |      | 3.1.2 Derivation of Voltage and Current Matrices          | 40 |

|   |      | 3.1.3 Common-Mode Equivalent Circuit Model                | 48 |

|   | 3.2                                                                  | .2 Derivation of Voltages for Asymmetric Parasitic Capacitor Models           |                                                                                                                                                                                                                                                                                                      |                                                    |  |

|---|----------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|

|   | 3.3                                                                  | Full-B                                                                        | ridge CM Modeling                                                                                                                                                                                                                                                                                    | 57                                                 |  |

|   |                                                                      | 3.3.1                                                                         | Derivation of the DC-side CM expression                                                                                                                                                                                                                                                              | 57                                                 |  |

|   |                                                                      | 3.3.2                                                                         | Derivation of the AC-side CM expression                                                                                                                                                                                                                                                              | 59                                                 |  |

|   |                                                                      | 3.3.3                                                                         | Full-Bridge Common-Mode Equivalent Circuit                                                                                                                                                                                                                                                           | 60                                                 |  |

|   | 3.4                                                                  | Three                                                                         | Phase Inverter CM Modeling                                                                                                                                                                                                                                                                           | 60                                                 |  |

|   |                                                                      | 3.4.1                                                                         | Derivation of the DC-side CM expression                                                                                                                                                                                                                                                              | 61                                                 |  |

|   |                                                                      | 3.4.2                                                                         | Derivation of the AC-side CM expression                                                                                                                                                                                                                                                              | 62                                                 |  |

|   |                                                                      | 3.4.3                                                                         | 3-Phase Inverter Common-Mode Equivalent Circuit                                                                                                                                                                                                                                                      | 63                                                 |  |

|   | 3.5                                                                  | Neutra                                                                        | al Point Clamped Full-Bridge CM Modeling                                                                                                                                                                                                                                                             | 63                                                 |  |

|   |                                                                      | 3.5.1                                                                         | Derivation of Super-Node (U,L,N) CM expression                                                                                                                                                                                                                                                       | 64                                                 |  |

|   |                                                                      | 3.5.2                                                                         | Derivation of Super-Nodes (U_A,L_A) and (U_B,L_B) CM expressions                                                                                                                                                                                                                                     | 65                                                 |  |

|   |                                                                      | 3.5.3                                                                         | Derivation of Super-Node (A,B) CM expression                                                                                                                                                                                                                                                         | 66                                                 |  |

|   |                                                                      | 3.5.4                                                                         | Derivation of Input Node (U,L) CM expression                                                                                                                                                                                                                                                         | 68                                                 |  |

|   |                                                                      | 3.5.5                                                                         | NPC Full-Bridge Common-Mode Equivalent Circuit                                                                                                                                                                                                                                                       | 69                                                 |  |

|   |                                                                      |                                                                               |                                                                                                                                                                                                                                                                                                      |                                                    |  |

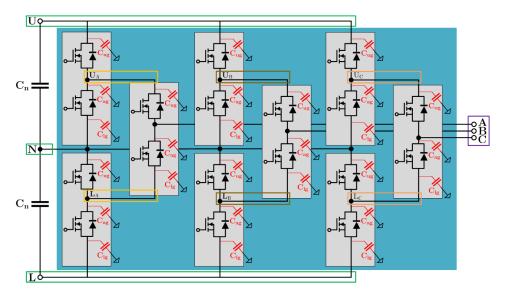

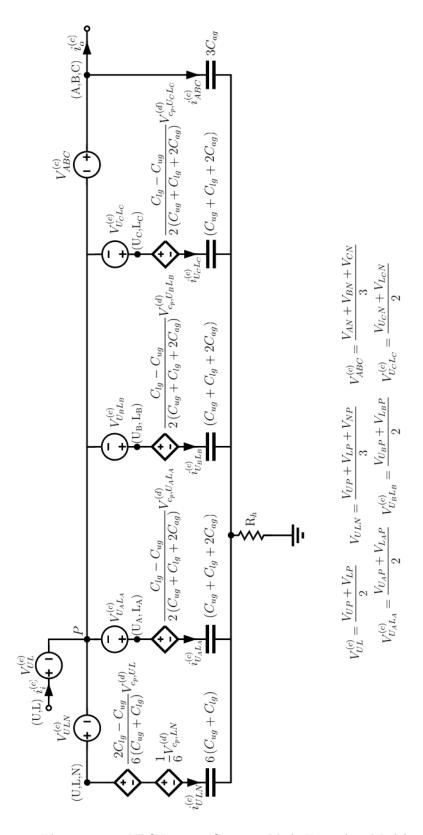

|   | 3.6                                                                  | 3-Pha                                                                         | se Neutral Point Clamped Inverter CM Modeling                                                                                                                                                                                                                                                        | 70                                                 |  |

| 4 |                                                                      |                                                                               | se Neutral Point Clamped Inverter CM Modeling                                                                                                                                                                                                                                                        | 70<br><b>73</b>                                    |  |

| 4 |                                                                      | dium-I                                                                        |                                                                                                                                                                                                                                                                                                      |                                                    |  |

| 4 | Med                                                                  | dium-I                                                                        | Frequency Transformer                                                                                                                                                                                                                                                                                | 73                                                 |  |

| 4 | Med                                                                  | dium-I<br>Parasi                                                              | Frequency Transformer tic Effects                                                                                                                                                                                                                                                                    | <b>73</b> 74                                       |  |

| 4 | Med                                                                  | dium-I<br>Parasi<br>4.1.1<br>4.1.2                                            | Frequency Transformer  tic Effects                                                                                                                                                                                                                                                                   | <b>73</b> 74 75                                    |  |

| 4 | <b>Med</b> 4.1                                                       | dium-I<br>Parasi<br>4.1.1<br>4.1.2                                            | Erequency Transformer  tic Effects                                                                                                                                                                                                                                                                   | <b>73</b> 74 75 76                                 |  |

| 4 | <b>Med</b> 4.1                                                       | dium-I<br>Parasi<br>4.1.1<br>4.1.2<br>Comm                                    | Erequency Transformer  tic Effects                                                                                                                                                                                                                                                                   | 73 74 75 76 77                                     |  |

| 4 | <b>Med</b> 4.1                                                       | Parasi 4.1.1 4.1.2 Comm 4.2.1                                                 | Erequency Transformer  tic Effects                                                                                                                                                                                                                                                                   | 73 74 75 76 77                                     |  |

| 4 | <b>Med</b> 4.1                                                       | Parasi<br>4.1.1<br>4.1.2<br>Comm<br>4.2.1<br>4.2.2<br>4.2.3                   | Erequency Transformer  tic Effects                                                                                                                                                                                                                                                                   | 73 74 75 76 77 80                                  |  |

| 4 | <b>Med</b> 4.1 4.2                                                   | dium-H<br>Parasi<br>4.1.1<br>4.1.2<br>Comm<br>4.2.1<br>4.2.2<br>4.2.3<br>Comm | Trequency Transformer  tic Effects  Leakage Inductance  Parasitic Capacitance  non-Mode Modeling: Method 1  Leakage (Stray) Capacitance  Intra- and Inter-Winding Capacitance  Medium-Frequency Transformer Common-Mode Equivalent Model .                                                           | 73 74 75 76 77 88 80 81                            |  |

|   | <b>Med</b> 4.1 4.2                                                   | dium-H Parasi 4.1.1 4.1.2 Comm 4.2.1 4.2.2 4.2.3 Comm                         | Erequency Transformer  tic Effects  Leakage Inductance  Parasitic Capacitance  non-Mode Modeling: Method 1  Leakage (Stray) Capacitance  Intra- and Inter-Winding Capacitance  Medium-Frequency Transformer Common-Mode Equivalent Model  non-Mode Modeling: Method 2                                | 73<br>74<br>75<br>76<br>77<br>78<br>80<br>81<br>81 |  |

|   | <ul><li>Med</li><li>4.1</li><li>4.2</li><li>4.3</li><li>EM</li></ul> | dium-H Parasi 4.1.1 4.1.2 Comm 4.2.1 4.2.2 4.2.3 Comm                         | Frequency Transformer  tic Effects  Leakage Inductance  Parasitic Capacitance  non-Mode Modeling: Method 1  Leakage (Stray) Capacitance  Intra- and Inter-Winding Capacitance  Medium-Frequency Transformer Common-Mode Equivalent Model  non-Mode Modeling: Method 2  ting and Validation of Models | 73 74 75 76 77 78 80 81 81                         |  |

|              |        | 5.2.1         | CM Displacement Current                              | 94  |

|--------------|--------|---------------|------------------------------------------------------|-----|

|              |        | 5.2.2         | Construction and Validation of CEM                   | 96  |

|              |        | 5.2.3         | Floating Heatsink vs. Nuetral Point Clamped Heatsink | 105 |

| 6            | Con    | clusio        | n                                                    | 109 |

|              | 6.1    | Summ          | ary                                                  | 109 |

|              | 6.2    | Future        | e Work                                               | 110 |

| Bi           | ibliog | graphy        |                                                      | 112 |

| $\mathbf{A}$ | ppen   | dix           |                                                      | 117 |

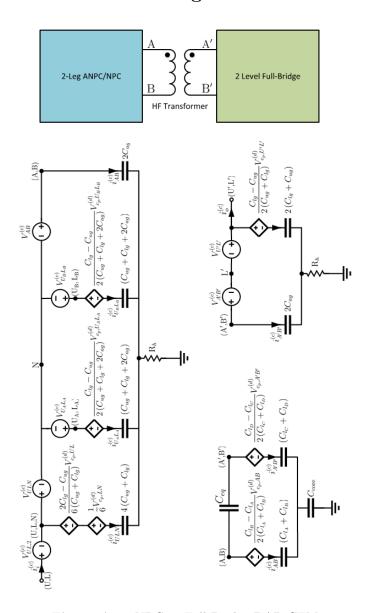

|              | A.1    | NPC t         | to 2-Level Full-Bridge DAB                           | 117 |

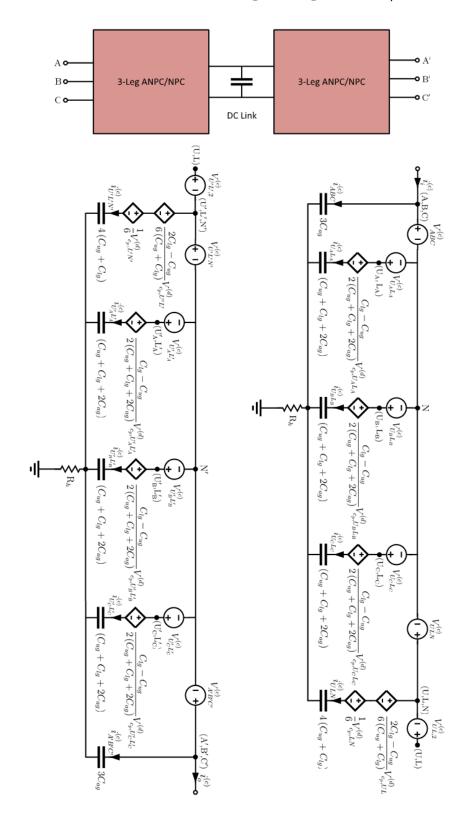

|              | A.2    | AC to         | AC Converter using 3-Leg ANPC/NPC                    | 118 |

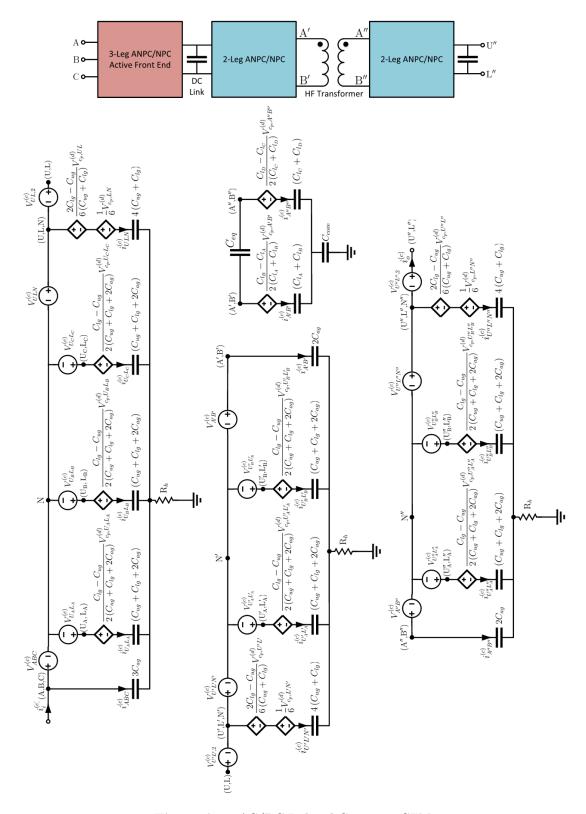

|              | Δ 3    | $\Delta C$ to | DC Isolated Converter                                | 110 |

## LIST OF FIGURES

| 1-1  | Land and Marine based electric power systems                                        | 1  |

|------|-------------------------------------------------------------------------------------|----|

| 1-2  | Pre-Electrical Distribution Stage using a Transformer                               | 5  |

| 1-3  | Conducted emissions in the distribution stage when transformer is excited           |    |

|      | with higher frequency content                                                       | 7  |

| 1-4  | Distribution stage with LISNs                                                       | 8  |

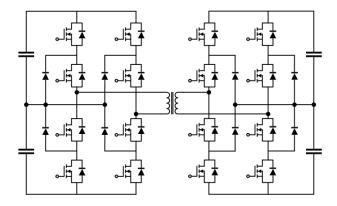

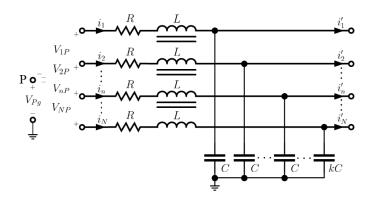

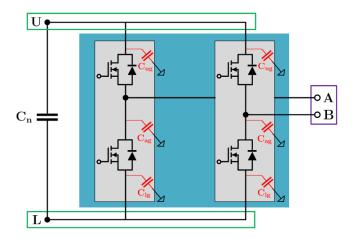

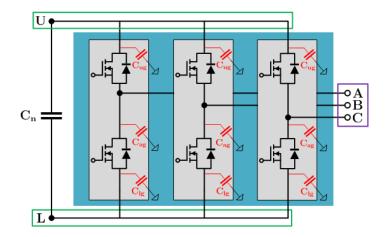

| 1-5  | Neutral Point Clamped Dual Active Bridge                                            | 11 |

| 2-1  | Impedance circuit of a Japanese automobile                                          | 18 |

| 2-2  | Artificial network of a Japanese automobile                                         | 18 |

| 2-3  | Noise and Susceptibility measurement systems using artificial network $\ . \ . \ .$ | 19 |

| 2-4  | Equivalent Norton circuit for a switching phase leg module                          | 20 |

| 2-5  | Two terminal model                                                                  | 21 |

| 2-6  | Three terminal model                                                                | 21 |

| 2-7  | Three phase inverter and DM one-port terminal model                                 | 23 |

| 2-8  | Modular terminated model and proposed DM model with LISN                            | 24 |

| 2-9  | CM Unterminated-behavioral model                                                    | 25 |

| 2-10 | Measured and predicted input and output CM current spectra where SiC                |    |

|      | inverter was operating without and with CM filters                                  | 26 |

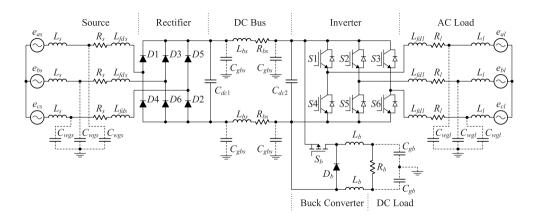

| 2-11 | DC based ship power system                                                          | 27 |

| 2-12 | CM equivalent circuit for ship power system                                         | 28 |

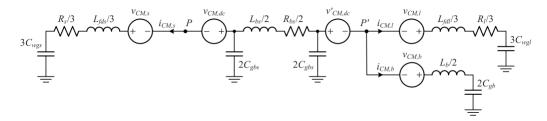

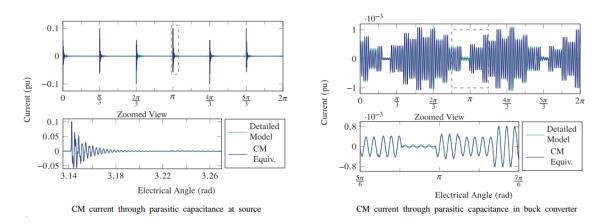

| 2-13 | CM currents through parasitic capacitance at source and in buck converter           | 28 |

| 2-14 | Half-bridge testbed for characterization of conducted EMI                           | 29 |

| 2-15 | CM equivalent circuit of half bridge testbed                                        | 30 |

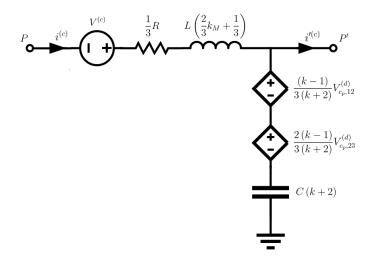

| 3-1  | Transmission Line Model used for CM Methodology                                     | 37 |

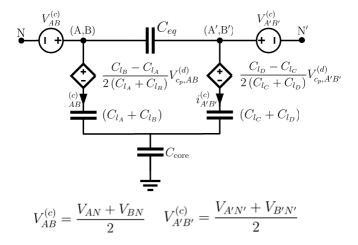

| 3-2        | Common-Mode Equivalent Model for Transformer Model                                                                                                                | 49 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

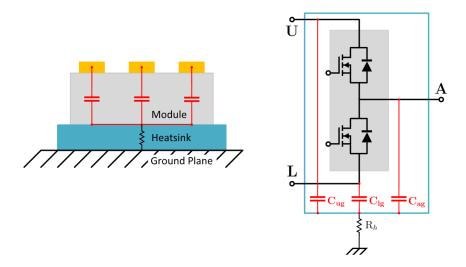

| 3-3        | SiC Power Module with Parasitic Capacitance                                                                                                                       | 50 |

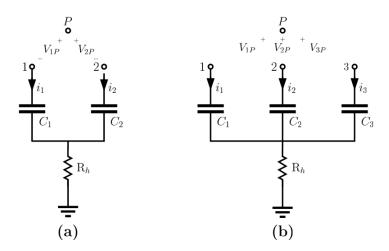

| 3-4        | 2 and 3-Line Parasitic Capacitor Models                                                                                                                           | 53 |

| 3-5        | Full-Bridge Circuit with Parasitic Capacitance                                                                                                                    | 57 |

| 3-6        | Full-Bridge, DC Parasitic Capacitance Model                                                                                                                       | 58 |

| 3-7        | Full-Bridge, DC Side CEM                                                                                                                                          | 58 |

| 3-8        | Full-Bridge, AC Parasitic Capacitance Model                                                                                                                       | 59 |

| 3-9        | Full-Bridge, AC Side CEM                                                                                                                                          | 59 |

| 3-10       | Full-Bridge Common-Mode Equivalent Model                                                                                                                          | 60 |

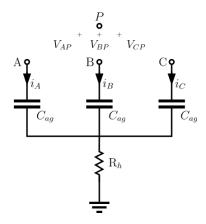

| 3-11       | 3-Phase Inverter Circuit with Parasitic Capacitance                                                                                                               | 60 |

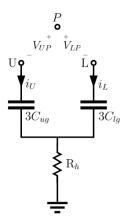

| 3-12       | 3-Phase Inverter, DC Parasitic Capacitance Model                                                                                                                  | 61 |

| 3-13       | 3-Phase Inverter, DC Side CEM                                                                                                                                     | 61 |

| 3-14       | 3-Phase Inverter, AC Parasitic Capacitance Model                                                                                                                  | 62 |

| 3-15       | 3-Phase Inverter, AC Side CEM                                                                                                                                     | 62 |

| 3-16       | 3-Phase Inverter Common-Mode Equivalent Model                                                                                                                     | 63 |

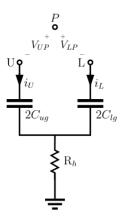

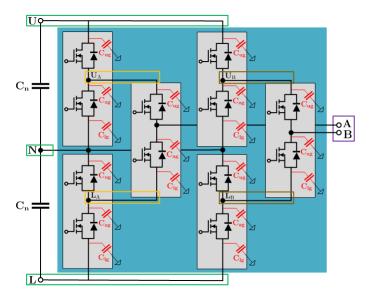

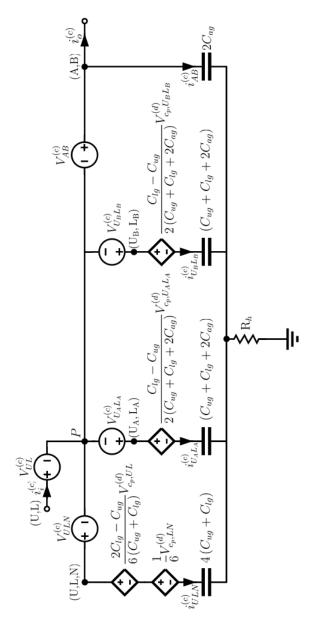

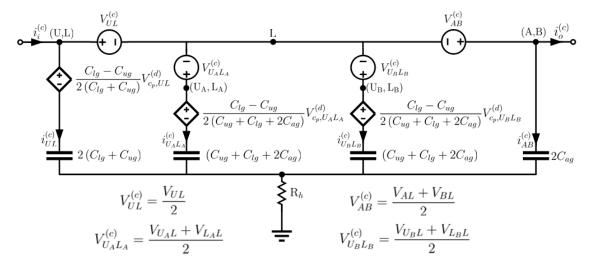

| 3-17       | NPC Full-Bridge Circuit with Parasitic Capacitance                                                                                                                | 63 |

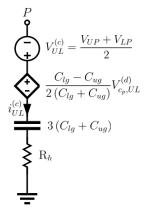

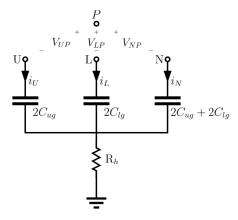

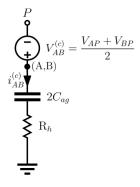

| 3-18       | NPC Full-Bridge, Super-Node (U,L,N) Parasitic Capacitance Model $\ \ldots \ \ldots$                                                                               | 64 |

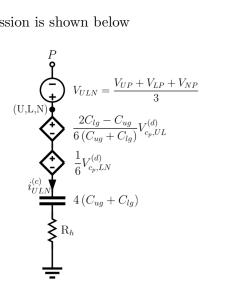

| 3-19       | NPC Full-Bridge, Super-Node (U,L,N) CEM $\ \ldots \ \ldots \ \ldots \ \ldots$                                                                                     | 65 |

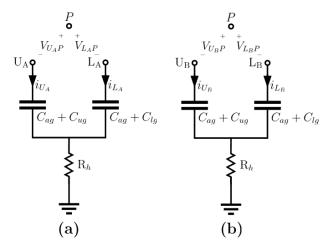

| 3-20       | NPC Full-Bridge, Super-Nodes $(\mathrm{U}_{\mathrm{A}},\!\mathrm{L}_{\mathrm{A}})$ and $(\mathrm{U}_{\mathrm{B}},\!\mathrm{L}_{\mathrm{B}})$ Capacitance Models . | 65 |

| 3-21       | NPC Full-Bridge, Super-Nodes $(U_A,\!L_A)$ and $(U_B,\!L_B)$ CEM $\ \ldots \ \ldots \ \ldots$                                                                     | 66 |

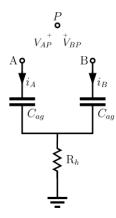

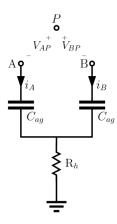

| 3-22       | NPC Full-Bridge, Super-Node (AB) Parasitic Capacitance Model                                                                                                      | 67 |

| 3-23       | NPC Full-Bridge, Super-Node (A,B) CEM                                                                                                                             | 67 |

| 3-24       | NPC Full-Bridge, Input Node (U,L) $\hdots$                                                                                                                        | 68 |

| 3-25       | NPC Full-Bridge, Input Node (U,L) CEM $\hdots$                                                                                                                    | 68 |

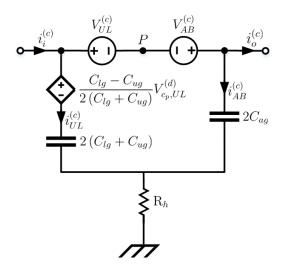

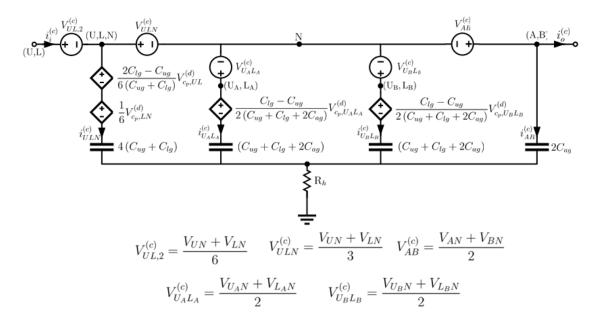

| 3-26       | NPC Full-Bridge Common-Mode Equivalent Model                                                                                                                      | 69 |

| 3-27       | NPC Inverter Circuit with Parasitic Capacitance                                                                                                                   | 70 |

| 3-28       | NPC Inverter Common-Mode Equivalent Model                                                                                                                         | 71 |

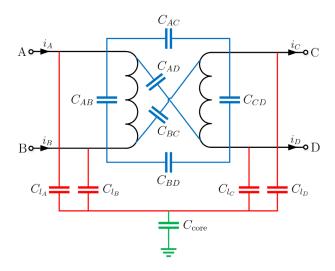

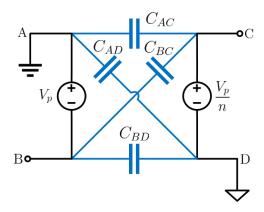

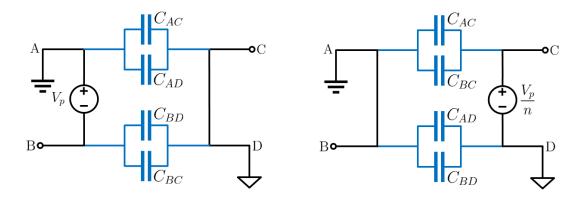

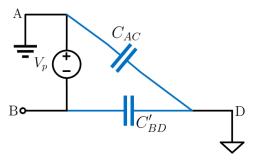

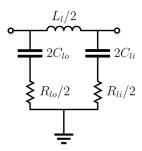

| <i>1</i> 1 | Simplified Transformer Parasitic Model                                                                                                                            | 77 |

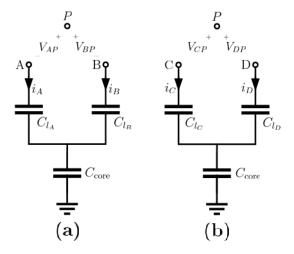

| 4-2         | HF Transformer, Input Nodes (A,B) and Output Nodes (C,D) Leakage Ca-            |                                   |

|-------------|---------------------------------------------------------------------------------|-----------------------------------|

|             | pacitance Models                                                                | 78                                |

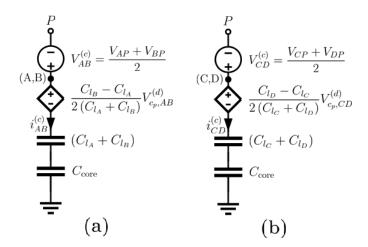

| 4-3         | HF Transformer, Input Nodes (A,B) and Output Nodes (C,D) Leakage Common         | <b>1-</b>                         |

|             | Mode Equivalent Models                                                          | 79                                |

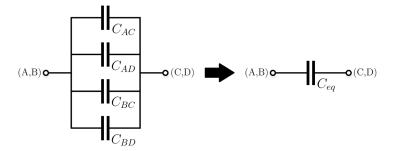

| 4-4         | HF Transformer: Inter-Winding Capacitance Model(left) and Equivalent            |                                   |

|             | $Model(right)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 80                                |

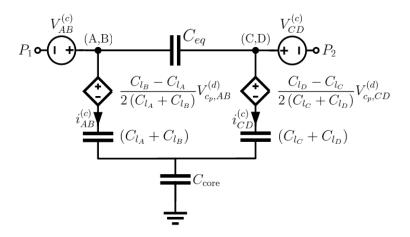

| 4-5         | HF Transformer CEM                                                              | 81                                |

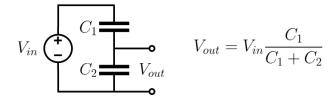

| 4-6         | Flyback HF Transformer Parasitic Model Example                                  | 82                                |

| 4-7         | Flyback HF Transformer Superposition                                            | 83                                |

| 4-8         | Capacitor Voltage Divider                                                       | 83                                |

| 4-9         | Flyback HF Transformer CEM                                                      | 84                                |

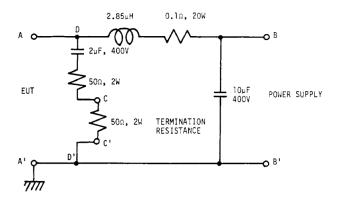

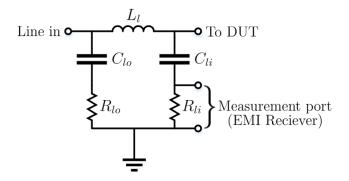

| 5-1         | Line Impedance Stabilization Network (LISN)                                     | 88                                |

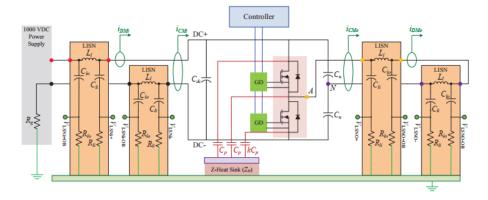

| 5-2         | Lab Validation of ANPC Dual Active Bridge                                       | 89                                |

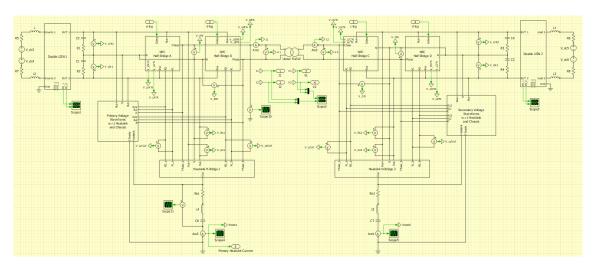

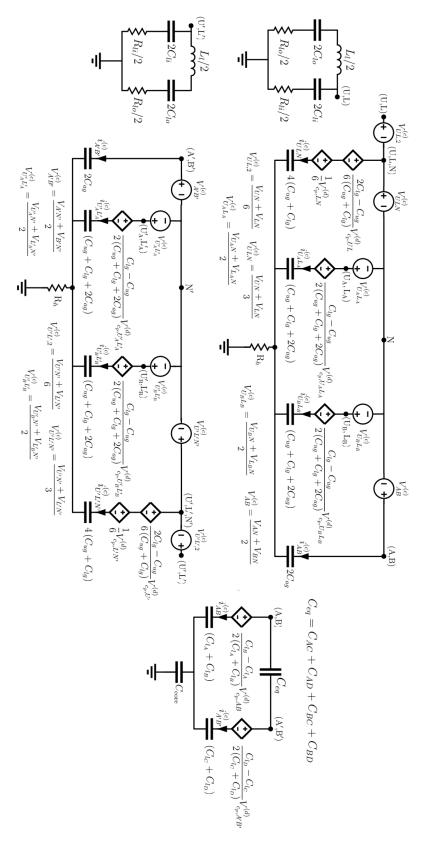

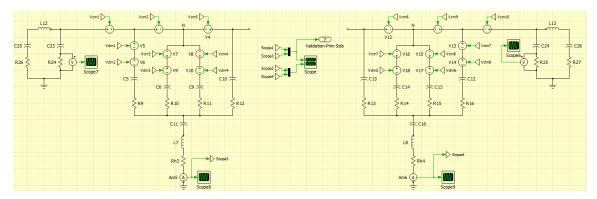

| 5-3         | PLECS MM Circuit of ANPC Dual Active Bridge                                     | 91                                |

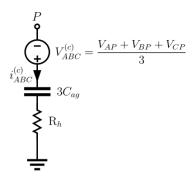

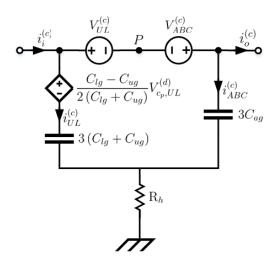

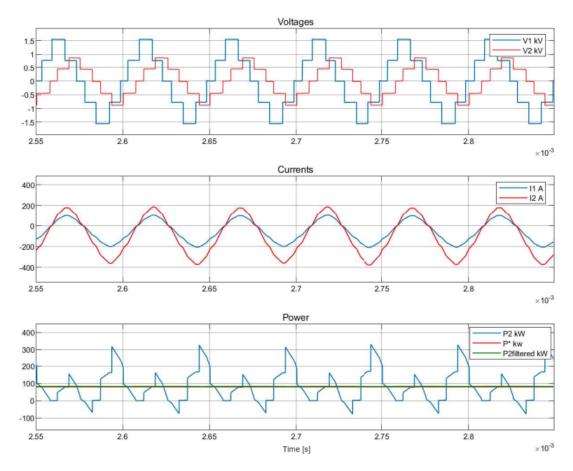

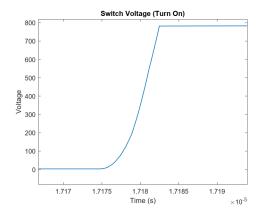

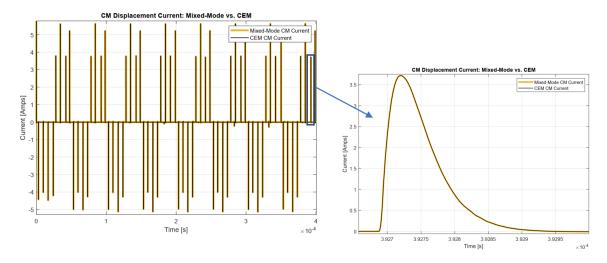

| 5-4         | Steady State Operating Conditions for NPC DAB                                   | 94                                |

| 5-5         | Typical Voltage TransitionRate $(dv/dt)$ for a MOSFET during Turn On            | 95                                |

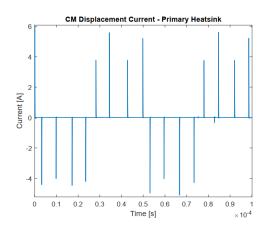

| 5-6         | CM Displacement Current through Primary Heatsink                                | 95<br>95                          |

| 5-7         | 2-Line LISN CEM                                                                 | 97                                |

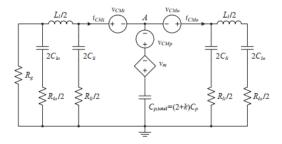

| 5- <i>1</i> | NPC Full-Bridge CEM w/ P = N                                                    | 98                                |

| 5-9         | HF Transformer CEM                                                              | 99                                |

|             |                                                                                 | 100                               |

|             | Full System CEM - NPC DAB CEM                                                   |                                   |

|             | CM Currents used for Validation of CEM                                          | <ul><li>101</li><li>102</li></ul> |

|             |                                                                                 |                                   |

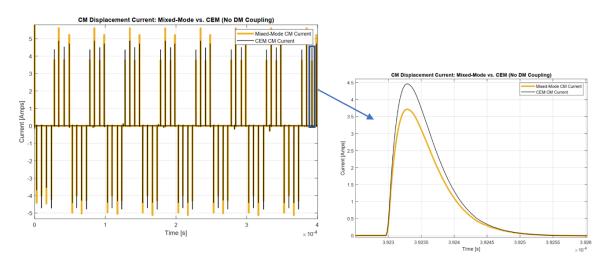

|             | CM Comparts: MM vs. CEM (No. DM Coupling)                                       | 102                               |

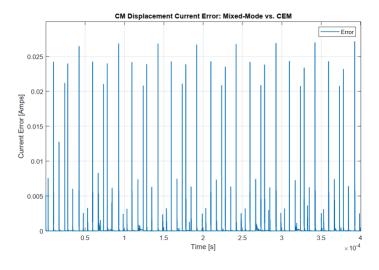

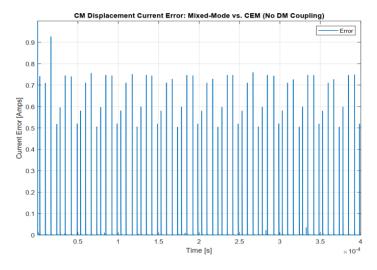

|             | CM Validation Country Error, MM vs. CEM(No DM Country)                          | 103                               |

|             | CM Displacement Computers / Neutral Clause d Heatrick                           | 104                               |

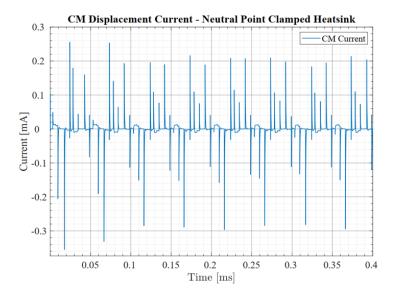

|             | CM Displacement Current w/ Neutral Clamped Heatsink                             | 106                               |

| 9-17        | NPC Full-Bridge CEM w/ P = L, Neutral Clamped Heatsink                          | 106                               |

| A-1         | NPC to Full-Bridge DAB CEM                                                      | 117                               |

| A-2 | AC/AC Converter using NPC CEM | 118 |

|-----|-------------------------------|-----|

| A-3 | AC/DC Isolated Converter CEM  | 119 |

## LIST OF TABLES

| 5.1 | HF Transformer Parameters | 92 |

|-----|---------------------------|----|

| 5.2 | System Specifications     | 93 |

#### ACKNOWLEDGEMENTS

Throughout the writing of this thesis I have received a tremendous amount of support and assistance.

I would first like to thank my supervisor, Dr. Robert Cuzner, whose expertise was invaluable in formulating the research development and methodology. Your insightful feedback has pushed me to sharpen my thought process and brought my work to a higher level.

I would like to acknowledge my colleagues in the Power Electronics group at UWM. I want to thank all of you for your patient support and continued collaboration for all of the opportunities I was given to further my research.

I am greatly indebted to my family and would like to thank them for their continued guidance and sympathetic ear. You guys have always been there for me.

Finally, I could not have completed this thesis without the support of my friends, who have provided thoughtful discussions as well as happy distractions to rest my mind outside of my research.

## Chapter 1

## Introduction

#### 1.1 Power Systems

Electric power systems are comprised of many components that produce electrical energy and transmit this energy to consumers. A electric power system is composed mainly of six main components: power plants which generate electric power, transformers that raise or lower the voltages as needed, transmission lines that carry power, substations at which the voltage is stepped down for carrying power over the distribution lines, distribution lines, and distribution transformers which lower the voltage as needed for the consumer equipment.

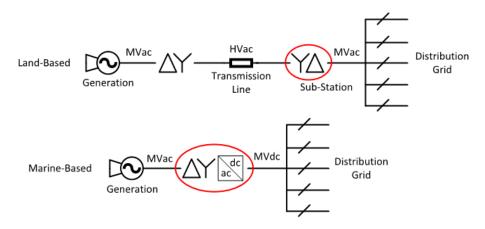

Figure 1-1: Land and Marine based electric power systems

Here are two simple single line diagrams that illustrate a typical land and marine based electric power system from generation to distribution. They are typically composed of all or most of the main components of an electric power system explained before. The main

difference between land-based systems and marine-based systems is the fact that the marine power system is an isolated system with short distances from generated power to load, very comparable to a microgrid. In contrast, land-based systems can have hundreds of kilometers between power generation and the load, with long transmission lines and several voltage transformations between them.

Research in electric power systems concentrates on the study of the emerging technologies of power electronics, distributed energy sources on the electric power system operation, and protection.

#### 1.1.1 Power Electronics

Power Electronics is a technology within power systems that deals with the conversion and control of electrical power with high efficiency solid-state electronics for a wide range of applications. The 21st century has been widely defined as the golden age of power electronic applications after the evolution of technology and major innovations in the past century. It has emerged as the high-tech frontier in power engineering due to its important role in energy conservation, renewable energy systems, and electric and hybrid vehicles. The technology embraces the areas of power semiconductor devices, converter circuits, electrical machines and drives, advanced control techniques, computer-aided design and simulation, as well as artificial intelligence.

The power conversion systems can be classified according to the type of the input and output power. These classifications are; AC to DC (rectifier), DC to AC (inverter), DC to DC (DC/DC converter), and AC to AC (AC/AC converter). Research in this area includes power electronic applications to control large scale power transmission and distribution as well as the integration of distributed and renewable energy sources into the grid.

A lot or research lately has gone into the development of power semiconductor devices with the growing demand for high power density and high efficiency systems. The performance of power semiconductor devices is currently being pushed to the limit for silicon (Si) material. We are now entering a new generation of power semiconductor devices with the development of wide bandgap (WBG) semiconductor materials, such as silicon carbide (SiC) and gallium nitride (GaN), which provide many advantages over Si. WBG semicon-

ductor materials permit smaller, faster, more reliable power electronic components with a higher efficiency allowing power electronic devices to operate at much higher temperatures, voltages, and frequencies compared to the conventional silicon based materials. However, high dv/dt and di/dt during switching transient as well as high operating frequency, mixed with their unique structure raises the concern of electromagnetic interference (EMI) and converter reliability issues.

#### 1.2 Designing Electrical Systems

When designing an electrical system, you have many specifications and requirements that must be acknowledged. In particular, we want to ensure the safety of people, provide protection of equipment through insulation reliability, and provide mitigation efforts toward EMI. The International Electrotechnical Commission (IEC) has established protection classes for electrical equipment. Classes I and II provide user and equipment protection from electric shock. They provide protection from hazardous voltage with one or more types of insulation systems, a basic insulation system and a reinforced insulation system. Insulation typically uses a material as an isolation barrier to help keep an electric current safely in its proper circuit and prevent leakage. In addition to insulation, a protective earth connection is provided for diverting fault energy if there should be an accidental breakdown of the basic insulation. A protective earth connection uses a protective conductor to direct a fault current safely into the earth and away from a human in contact, as well as diverting current from a faulty circuit for protecting devices.

#### 1.2.1 Grounding

Proper grounding is an important aspect of electrical system design for both safety and electromagnetic compatibility (EMC). Ground plays a crucial role in determining what happens in the event of unintentional faults, transients, and EMI. Improper grounding can impair the safety and EMC of a product or system, and is one of the leading contributors to EMC related failures. The biggest misconception that leads to improper grounding is confusing the terms ground with current return. When current return conductors are treated

like grounding conductors it often results with significant EMC problems. Ground serves as a circuit or system zero-volt reference, or more specifically defined as "the connecting of an electric circuit or equipment to earth or some conducting body of relatively large extent that serves in place of earth." So ground is a reference potential and ground conductors are normally non-current carrying, because significant currents flowing in a conductor can prevent it from being a reliable reference potential. The current return path is a wire or plane used to return the signal, which is usually referenced with a low voltage with respect to ground but should not be confused with ground itself.

An important part of designing safe electrical systems is knowing where and when unsafe voltages may appear on various conducting surfaces. Since ground is the zero-voltage reference, that means the voltage on every other conductor is the difference between its voltage and ground. For land-based systems, the ground reference is usually the earth. This is convenient because the earth is large and all other large metal structures can easily be connected or referenced to earth ground. Earth grounds, or protective earth connections, are typically metal rods driven into the dirt near power service entrances. Substantial exposed metal surfaces or chassis are typically required to ground the metal to the earth ground connection to ensure it cannot reach an unsafe potential.

Grounding strategies are not only important for safety, it also plays an important role in meeting conducted emissions where the ground structure is both the zero-volt reference and the preferred path for interfering common mode noise currents. It is important to know that while the ground cannot carry intentional currents, it is expected to carry fault currents and induced common mode noise currents. The proper utilization of the ground structure depends on its ability to carry unintentional currents with sufficiently low impedance to control unintentional voltages.

#### 1.3 Electrical Distribution Systems

The focal point of this thesis revolves around the electrical distribution stage of power systems, which is very important because it is one of the final stages before power consumption. From Figure 1-1, the electrical distribution system is highlighted by the red circle. A sim-

plified look at a common electrical distribution stage can be seen in the figure below.

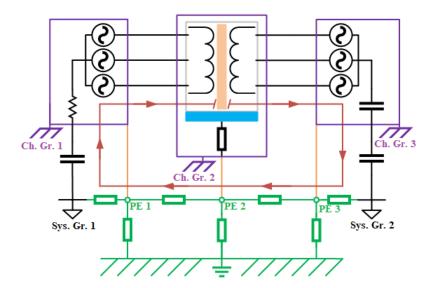

Figure 1-2: Pre-Electrical Distribution Stage using a Transformer

In this simplification of a pre-distribution stage we have two three phase voltage supplies on either side of a transformer, which will be raising or lowering a voltage as needed. On the primary side of the transformer we can consider this power supply as either a generator or a grid tied power service entrance, and the secondary side power supply can be considered as a grid tie for the distribution grid network. There are system ground reference points for both sides of the transformer due to the fact that the transformer provides isolation between primary and secondary sides. The system is much more complicated than this but it has been simplified to get the major points across to the reader.

Now, following the protection classes and grounding structures talked about in the previous section, we enclose the transformer and each power supply inside their own metal enclosure. These metal enclosures, or chassis, are then bonded to a protective earth connection. The protective earth connections are metal rods that are driven into the earth and there is a connection between each one of them through rebar or other means, which creates this equipotential surface at ground level. There is also basic insulation on the transmission lines and between each part of the system with their corresponding chassis. All of this provides safety measures to protect humans from electric shock in case of faults. The primary side supply has a high impedance path to chassis, which is used for detection

of fault current. If a fault occurs that causes a short between the power conductor and the exposed chassis, the ground connection ensures that a large amount of current is drawn and forces a circuit breaker to open and remove power from the rest of the circuit. This ensures equipment safety for downstream devices, and once the fault is cleared the circuit breaker is closed again for system operation. With a grounding strategy like this, it is expected that fault currents are carried away from the system into ground to protect humans and sensitive electrical equipment.

Another safety measure is through the use of the transformer, which is a key asset component of any electrical distribution system. A transformer has two main jobs, one is voltage transformation by stepping up or down the voltage to the desired level, and the other is to provide galvanic isolation between system ground potentials. Galvanic isolation can be extremely effective for providing human safety and improving noise immunity between circuits. Galvanic isolation is a principle of isolating functional sections of electrical systems to prevent current flow, where no direct conduction path is permitted. This type of isolation is used where two or more electric circuits must communicate, but their grounds may be at different potentials. It is an effective method of breaking ground loops by preventing unwanted current from flowing between two units sharing a ground conductor.

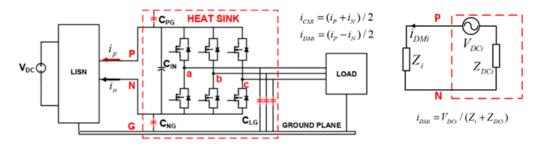

With safety concerns met, we can now begin to understand the impact that this system and its grounding structure has on conducted emissions. The term conducted emissions refers to the mechanism that enables electromagnetic energy, in the form of common-mode (CM) current, to be created in an electronic device and coupled back to its AC supply through unintentional paths, with its intent to close the current loop. These CM currents that are coupled back to the AC power can find its way to the entire power distribution network that the circuit is connected to and use the larger network to cause radiated emissions much more efficiently than the circuit could by itself. One may think that transformers and their galvanic isolation can solve this problem of conducted emissions, which may be true at low frequencies but CM currents are typically composed of much higher frequencies. At these higher frequencies, galvanic isolation can have the side effect of increasing CM coupling between the isolated circuits through parasitic capacitance.

So where is this high frequency content coming from? Well, it is the introduction of

power electronics, especially WBG devices, with their high dv/dt during switching transient as well as their high operating frequency that is the main driver for higher frequency content. Figure 1-3 introduces some power electronics to the circuit to understand the impact that higher frequency content has on conducted emissions.

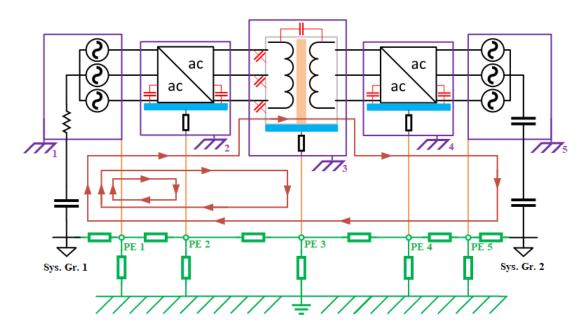

**Figure 1-3:** Conducted emissions in the distribution stage when transformer is excited with higher frequency content

These power electronics are producing multiple step trapezoidal waveforms that are exciting the transformer at much higher frequencies than the standard 60 Hz AC from the grid or generator. The power electronics are used as a way of changing the frequency of the sinusoidal-like waveforms and has many practical applications. Instead of using an AC to AC conversion stage on the secondary side, a AC to DC converter could be used for a DC distribution grid. At any rate, the transformer is being exposed to much higher frequency content and starts to exhibit different side effects that actually increase the CM coupling between isolated circuits. It is not that the galvanic isolation is breaking down, instead the higher frequency content is introducing parasitic coupling paths based on the geometric layout of the device. These parasitic coupling paths are in the form of leakage capacitance between the windings and the core, and winding capacitance from primary to secondary sides. The parasitic winding capacitance provides a coupling path across the transformer

allowing CM current into other parts of the distribution network and back to the AC supply, giving the circuit a much larger CM ground loop. The parasitic leakage capacitance allows CM current to flow from the windings to the core, into the heatsink, finds a path to the chassis, and then couples back to the AC source. The transformer is not the only device that has parasitic CM coupling paths, the power electronic devices do as well. Based off of these trapezoidal waveforms that it produces, there is parasitic paths that are induced from the device to its substrate, through the heatsink, into the chassis, and then coupled back to the AC source. All of these CM current paths provide a lot of coupling back to the source, which can then be distributed throughout a much larger system and cause a great amount of interference in these devices and other devices connected to the distribution system. As an unavoidable design consideration, EMI issues must be addressed properly otherwise the benifits of WBG power devices and medium frequency transformers can be jeopardized.

To fully understand CM conducted emissions of a system we must introduce the Line Impedance Stabilization Network (LISN). The intent of the LISN is to create an artificial impedance and ground path for conducted emissions for a specific device and its electrical system.

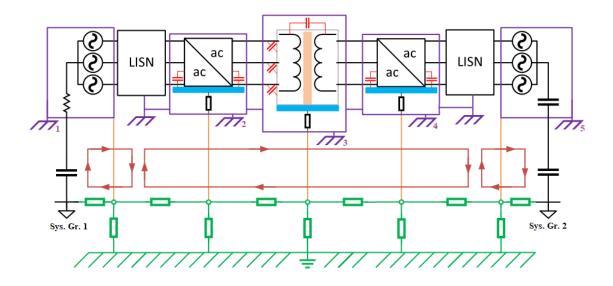

Figure 1-4: Distribution stage with LISNs

Here we have placed main components of interest between the LISNs to understand their CM emissions and the impact they have on conducted emissions as a whole. We connect common grounds between all Devices Under Test (DUT) to localize the ground path for CM conducted emissions. The LISN acts as a specialized low pass filter. The filter is designed to prevent unwanted noise from coming in on the power leads and mixing in with the DUT, likewise it will also prevent noise from leaving the DUT and getting back onto the power leads. This allows us to isolate the conducted emissions within the DUT and eliminate unwanted noise from entering the circuit so that we can design filters or other mitigation efforts to lower the amount of conducted emissions passed through or generated by the DUT. Over the years, the LISN has evolved and has been primarily used to perform CM conducted emissions measurement on common coupling power leads. The standardized impedance provided by the LISN ensures consistency between multiple tests, and an EMI receiver can measure the isolated CM conducted interference voltage produced by the DUT.

#### 1.4 Objective and Motivation

With the advancement in power electronic converters, the significant EMI challenges need to be addressed for distribution level power systems. It is important that we address these EMI issues properly such that the benefits of WBG devices are not compromised, and we can continue to develop cutting edge devices for the future generation of power electronic systems. Our goal is to provide a computationally efficient method of EMI characterization for conducted and radiated emissions for this future generation of power electronic converters.

#### 1.5 EMI Characterization Methodology

EMI characterization methodology has been emphasized in recent years. Modern power converters designed with WBG semiconductors are known to generate substantial amount of EMI as a side effect of high edge rates and high frequency switching. This has brought increased attention on filtering EMI signals for power converters and no longer focusing just on a power quality standpoint. The EMI spectrum for conducted emissions is in the 100 kHz to 30 MHz range, and anything above the conducted emissions up to 10 GHz is in the radiated emissions range. To better understand the EMI emission sources and

design optimized EMI mitigation strategies, we need to develop characterization methods and models to accurately predict EMI.

For a system to achieve electromagnetic compatibility (EMC) with itself or its surrounding environment, we must ensure that our electrical devices don't emit a large amount of EMI, through either radiated or conducted emissions, and that our device continues to function in the presence of other electromagnetic phenomena [1]. There are many regulatory agencies that have placed limits on the level of emissions that our electrical devices are allowed to generate, and often times we are mandated to abide by these limits. There is a finite region of the electromagnetic spectrum that is used on a daily basis (i.e., radio waves, microwaves, x-rays) within a huge number of products. Even if electronic devices don't contain transmitters, they can still emit electromagnetic radiation as a byproduct of their switching voltages and currents. Without a limit on the level of radiation from these unintended emitters, the electromagnetic spectrum for intended transmission could be compromised. Safety is a huge concern when it comes to compromised spectra, especially in military, medical, aerospace, and automotive products. If products in these areas were to fail from EMI such as power surges or radiated electrical fields, then peoples lives could be at serious risk. So rigorous EMC testing ensures that electrical systems can withstand and continue to function properly in the presence of these electromagnetic environments. Fines and serious action is enforced if you are caught with a non-compliant device in the market.

Different EMI characterization methodologies have been explored by many researchers around the world [2] - [31]. EMI characterization provides quantified insights into the EMC design challenge. This quantification makes the design of EMI mitigation more oriented towards optimization and more efficient by reducing the scale and number of physical experiments, reducing simulation time, and reducing unnecessary design margins. If a method quantifies the EMI with very light weight computation, the iteration process is manageable to allow the implementation of automated optimization algorithms, such as the Virtual Prototype Process (VPP) conducted within our research team.

#### 1.6 System Description

In our area of research, we are confronted with a wide range of power electronic converters. The dual active bridge (DAB) converter has been a hot topic in research lately and is well suited for applications in power distribution systems due to their high power density, low device stresses, galvanic isolation, and bidirectional operation. DAB converters have been considered as a candidate topology for solid-state transformers, and have been studied in context with renewable energy, automotive, aerospace, and marine power systems. A DAB bidirectional DC/DC converter is a topology with the advantages of decreased number of devices, soft switching commutations, low cost, and high efficiency. The use of this topology is proposed for applications where the power density, cost, weight, and reliability are critical factors. With its high demand in power electronics, we have directed our research towards an accurate EMI characterization and reduction methodology to support the design of the DAB as a sub module for much larger system applications.

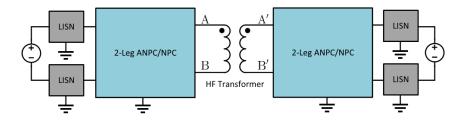

For the main topology of this thesis, the neutral point clamped (NPC) dual active bridge has been chosen.

Figure 1-5: Neutral Point Clamped Dual Active Bridge

The NPC DAB is a bidirectional DC/DC converter based on two active NPC full-bridges interfaced and isolated through a medium-frequency (MF) transformer enabling power flow in both directions in case of an active load. The main reason for choosing the NPC DAB over a conventional DAB is the decrease of voltage stress on power switches, making it a prime subject for medium voltage systems. For the conventional DAB, the input and output

voltages are applied to the power switch as a voltage stress. Therefore, with increased system voltage, there will be a need for higher rated devices to withstand the increased voltage stress. In order to solve this problem, the voltage stress applied to the power switch can be distributed using a multi-level topology, where the NPC converter is the most commonly used multi-level structure. The DC link of the NPC converter is connected in series with two capacitors to ensure a neutral point voltage. Thus, the maximum voltage applied to any power switch will be half the DC link voltage. Even though the voltage stress is reduced on devices during normal operation, there is still a chance that a switch can encounter almost twice the DC link voltage during a fault. With this in mind, there is still a need for higher rated devices to make the NPC DAB a feasible option for MV voltage systems. There is much on going research in designing higher rated switching modules, specifically the 10 kV SiC module, to enable the design of the NPC DAB as a feasible option for MV distribution systems.

The NPC DAB was described as a sub module earlier, that is because the NPC DAB alone is only an isolated DC to DC converter, but the addition of other components or converters makes it a power distribution system. On the primary side we could add in a grid tied AC supply with an active front end converter, which would allow us with opportunities for vehicle charging systems or a DC distribution system for marine applications. Or we could add a DC to AC converter on the secondary side, which would allow us to tie to the AC grid for renewable energy systems. All of these will be possible applications for the future, but we should first start with an accurate characterization of the NPC DAB.

The bulk of this thesis will be around the CM EMI methodology for the NPC DAB. A CM model of the topology for EMI studies will be derived, the CM model will be validated with simulation software, and some techniques will be performed that decrease the amount of CM emissions.

#### 1.7 Thesis Organization

A literature review on current and state of the art major modeling methods for EMI characterization performed by academic scholars and industry partners will be discussed in

Chapter 2. A computationally efficient mathematical method to isolate the common-mode paths and create equivalent circuit models for common-mode EMI conducted emissions will be discussed in Chapter 3. This method will be carried out for multiple power electronic converters including the neutral point clamped converter. An extension of this method to the high-frequency transformer will be performed and a common-mode equivalent model is developed in Chapter 4. All of the created CM equivalent models will be brought together to form a complete NPC DAB system CM equivalent model, and then validated along side a mixed-mode model created in the PLECS environment in Chapter 5. EMC testing environments and potential lab test setups is discussed, and a novel idea for reducing CM emissions within the NPC converter will also be covered in this chapter. Then finally, a summary and suggestions for future work will be described in Chapter 6.

THIS PAGE INTENTIONALLY LEFT BLANK

## Chapter 2

## State of the Art Methodologies

To characterize EMI produced by a power electronic converter, a model must be developed for the converter and its surrounding system with accuracy that meets system requirements and is validated within a required frequency range. To ensure compatibility with filter designs the models are mostly developed into an electrical circuit representing the dominant EMI producing behavior for the physical system.

With the aim to derive these hehavioristic models, various methodologies have been applied. In engineering we tend to break a modeling approach into three different categories; white-box modeling, black-box modeling, and gray-box modeling. Engineers use a white-box model when it is possible to describe the whole system using physical equations and data sheets. Such models have understandable, reasonable, and observable behaviors between influencing variables and output predictions. However, this is a rare type of modeling approach and is commonly used on very basic systems. The opposite of white-box is black-box modeling, where a model is estimated mathematically from a measured input and output. These models have an observable input and output behavior, but how the model works inside the black-box is more or less unknown. The third type of model is the gray-box model, which is a mixture of the white-box and black-box modeling approaches. In a gray-box model, a part of the model is estimated and the other part is described with measurements and formulas. Picking the right type of modeling approach for an application depends on many different factors.

In this literature review of behavioral models, these modeling methodologies will be described and categorized based under these three different categories.

#### 2.1 White-box Modeling

White-box modeling is used when it is possible to describe the whole system using physical equations and information from data sheets. This modeling approach comprises the use of direct circuit modeling and simulation, and finite element method (FEM) assisted modeling.

Several direct circuit modeling methods have been developed to predict the EMI emissions of power converters [2], [3]. These methods are implemented in simulation software tools that can be used to predict the EMI noise generated up to several MHz, which is sufficient for the design of EMI filters as these are typically determined by the first switching harmonic component that falls inside the frequency range of interest. Direct circuit modeling constructs a full system circuit and maps out as much information and behavioral details as possible, with the use of measurement and data sheets for the power semiconductor components. The modeling process involves the formulation of high-frequency models for all main subsystems, including switching devices and packages, passive components, interconnections, and grounding. To account for the effect of high dv/dt in WBG devices, detailed switch models for SiC have been used. This modeling procedure is able to provide a significant EMI prediction throughout the whole system, but based on the different operating conditions, data sheets are not always valid and this could lead to misleading information. Even though these types of models can produce a significant amount of information, it is often dependent on the researchers bias and as a result could miss out on important information regrading EMI emissions.

With FEM modeling procedure, you can virtually construct entire parts of power electronic systems and compute the electromagnetic (EM) response within a designated frequency, which would otherwise be extremely hard to compute by hand using equations. Passive component models can also involve more detailed modeling phenomena, self-capacitance, or parasitics of components using FEM simulation [4], [5]. The EM response obtained from FEM can be used for the structural design of a system to reduce induced EMI from the

geometrical layout of the physical structure. This type of modeling procedure can provide a very accurate behavioral model within a desired frequency range.

#### Disadvantages to white-box modeling

Direct circuit modeling can provide great insight to CM EMI analysis, but often times these models are very difficult to construct for very large systems. Whereas, FEA provides little insight into CM EMI analysis. These modeling processes can tend to be very complex and very time consuming. The tuning of these models requires manual changes and a whole new simulation of the entire model, making the computational cost of these models too high to achieve an efficient iterative process.

#### 2.2 Black-box Modeling

Black-box modeling makes use of network or impedance analyzer to acquire scattering parameters and impedance profiles for certain parts of the power electronic system. Based on the information gathered, researchers can interpret a behavioral model without the use of data sheet information or specific details of the system itself [6]. Even with many EMI prediction techniques available, the most common method for studying EMI is to do so with a black-box approach after the design process. This entails measuring the EMI followed by implementing various techniques to reduce the emissions. This often results in reduced efficiency and power density and increased cost to a product.

#### 2.3 Gray-box Modeling

Instead of mapping out an immense amount of behavioral details like you do in the white-box modeling procedure, the grey-box modeling method only models the behavior of the major sources of EMI with measured data. These major sources of EMI are typically considered to be the switching waveforms and dominant parasitics.

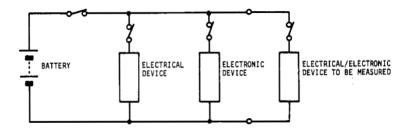

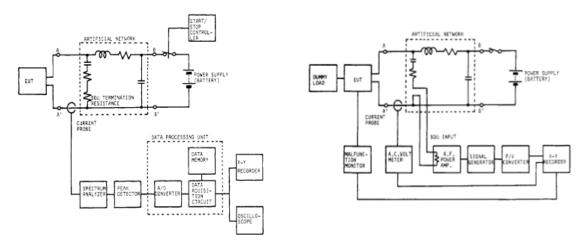

Gray-box modeling started with recognition that behavioral models of the energized system are required to capture the high frequency behavior and the interaction with other parts of the system. These studies truly began with the introduction of electronic devices into car systems. Two fundamental aspects where discovered in studying the electrical system of a car: firstly that the electronic device is disturbed by the disturbances present in the electrical network itself, secondly the device is a disturbance generator and the electrical network is the load. This recognition led to the methods used today to test for conducted emissions and complying to EMI/EMC standards. This suggested the adoption of the first LISN, or artificial network, as a means of measuring noise emission and susceptibility for electrical devices [7], [8]. The authors were able to perform laboratory measurements connected to an artificial network that represented the electrical networks used on compact passenger vehicles. The model of the electrical system was first seen as a simple impedance network with a battery source.

Figure 2-1: Impedance circuit of a Japanese automobile [8]

The intention was understand the noise emission and susceptibility of the device downstream from the rest of the electrical system, and be able to conduct these tests in a lab setting. So they began by measuring the impedance seen looking into the system by open circuiting the terminals of the device under test. With the impedance of the system, they created an artificial network to model this system.

Figure 2-2: Artificial network of a Japanese automobile [8]

From comparison you can see the resemblance to the modern day LISN. Using this artificial network, the RF conducted noise measurement systems were developed for laboratory measurements of emission level from automotive electrical devices and susceptibility level of electronic devices.

**Figure 2-3:** Noise and Susceptibility measurement systems using artificial network [8]

Advocates of Gray-box modeling have tried to find ways of extracting the important high-frequency characteristics, say dominant EMI producing sources, using standardized methods of accounting for interaction of the high-frequency noise producing component within a power system. For power electronic systems gray-box models were proposed that directly correlate the high-frequency stimulus to a power semiconductor in power electronic converters. This led to modeling approaches for behavioral models that represent the EMI noise source with an equivalent circuit, typically a current or voltage source or an ideal switch, together with some equivalent impedance representing parasitic impedances to model conducted emission propagation paths [9] - [12]. This type of behavioral model employs a time-invariant linear equivalent circuit, which can reduce the EMI computation and simulation time, but there are issues with modeling accuracy because of the simplifications involved. This oversimplification can lead to to errors in the higher frequency range. These behavioral models also characterize EMI noise source into separate CM and DM noise sources to understand the noise generation and propagation behavior, but this is based on

the assumption that there are no interactions between these noise sources.

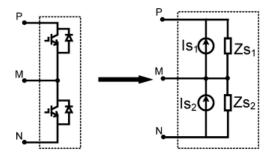

This led to terminal gray-box modeling approach to be performed [13] - [18]. This consisted of two and three terminal modeling to separate CM and DM equivalent circuits. The terminal models were developed to overcome the oversimplified aspects of previous models. The basic concept is to model the EMI emission from a switching module via a Thevenin or Norton equivalent source consisting of equivalent voltage or current sources and equivalent source impedances.

Figure 2-4: Equivalent Norton circuit for a switching phase leg module [14]

The model includes two noise current sources and two noise source impedances. The noise sources are connected with external circuit propagation path via the three terminals. The equivalent model can represent various switching patterns of this phase leg module. Different from existing modeling approaches, this method does not populate a source using assumed switching waveforms and estimated parasitic impedances. Instead, the equivalent current source and impedance are established through standardized tests and a characterization process under the specified operating conditions.

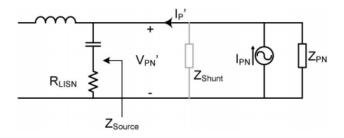

A two terminal model is a DM model, and is evaluated first since the concepts are easier to visualize and understand. The Norton equivalent circuit in Figure 2-5 is usually chosen since it closely represents the physical representation of a DM system. The model is created by using a nominal case and an attenuated case (shunt). Typically, the Norton equivalent parameters are defined by short- and open-circuit conditions, but this cannot be done for an operating converter. That is why a second measurement that is different from the nominal case is imposed. With the knowledge of the shunt impedance and the difference between the two terminal voltages, the unknown equivalent circuit can be solved.

Figure 2-5: Two terminal model [17]

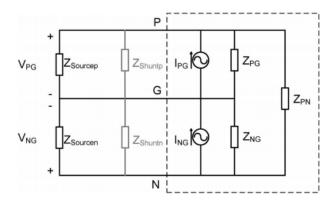

A three terminal model is composed of three impedances and two sources, because there must be an impedance between every terminal.

Figure 2-6: Three terminal model [17]

Similar to the two terminal case, the model is created by using a nominal case and at least two attenuated cases. There are several different attenuation schemes that can be implemented, but at least two attenuated cases along with the nominal system will provide enough information to solve all the unknowns. With the knowledge of the shunt impedances and source impedances along with the difference between the terminal voltages the unknown equivalent circuit can be solved.

The difference between the three and two terminal models is the method of solving for the unknowns. The two terminal model is a trivial case where there are two equations and two unknowns with an explicit solution. The three terminal model has many determining factors that have to be taken into account. Therefore, they impose a method to solve an over-determined system of nonlinear equations to minimize the error.

It took a year of refining this method but they eventually addressed the quality and challenges of EMI terminal modeling technique for switching power converters and extended the modeling technique to three phase AC systems [19]. They were able to show that the models are accurate even outside the conducted emissions range, making it a promising modeling technique.

The mixed-mode noise had been studied and there is an effective method of filtering conducted EMI separately by CM and DM, where each noise is dealt with the respective section of the EMI filter. But the fundamental mechanism by which the mixed-mode noise is excited and coupled had not been adequately investigated. The recognition of mixed-mode effects was eventually modeled and analyzed for conducted emissions at higher frequencies [20]. It wasn't until the unterminated behavioral model and the common-mode equivalent models with dominant parasitics that truly were able to predict conducted emissions at higher frequencies when mixed mode noise becomes significant.

#### 2.3.1 Unterminated Behavioral Modeling

Behavioral models are usually based on Thevenin or Norton equivalents. The two-terminal and three-terminal models were used in the past to model the CM and DM noise separately in the power converters. But it has been shown that these models have a limitation when mixed mode noise becomes significant at higher frequencies, which is usually the case with converters that are asymmetric with respect to ground. These models were also treated as one-port models and have a limitation that they can only model the input-side EMI of power converters. Since these models are extracted for specific load conditions, they are referred as "terminated" behavioral models. In certain EMI standards they authorize limits on conducted emissions for all power lines and interconnecting cable bundles. Thus, for converters where coupling between the input and output side is significant, there is a need for an "unterminated" EMI model that not only predicts the interaction of EMI on both sides but also predicts changes in EMI at the input side due to changes on the load side parameters and vice versa.

This change from terminal to termination nomenclature brought in a new behavioral modeling approach where power converters are modeled instead as multiterminal networks, single-port or two-port, using an impedance network and a number of sources to model their operation. This new behavioral model builds up a thevenin equivalent circuit representation

without knowledge of the converter internal structure, with more of a black-box approach implemented. The impedance and sources are obtained empirically by directly performing a series of standardized measurements, which are conducted from the terminals of the converter in accordance with the multiport network theory. This behavioral modeling approach has been studied in great detail and has evolved into unterminated behavioral models for predicting conducted emissions at higher frequencies with mixed mode coupling [21] - [23].

For power converters, single-port behavioral models were first developed to predict the EMI noise in converter structures. In [22], the authors explain the limitations of using single-port terminal behavioral models and propose a mixed-mode unterminated behavioral model. Their research was toward motor drive applications, which meant that the converter topology used was the power inverter system.

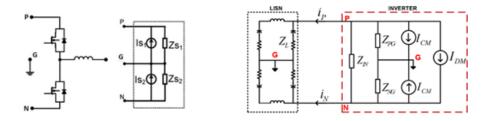

Figure 2-7: Three phase inverter and DM one-port terminal model [22]

Figure 2-7 shows a DM power inverter system under study that was used to predict DM EMI noise. The one-port terminal model used to predict DM noise at the inverter input side, and is composed of one noise source and one equivalent impedance. The impedance is dependent on the DC bus capacitor at low frequency and its equivalent series inductance at the high frequency part, while the voltage represents the switching effect of the active devices. The input impedance represents the impedance outside the inverter on the input side, which includes the LISN. With the extracted model, the DM input noise can be calculated with different input impedances. A three-phase SiC MOSFET inverter setup was built to asses the feasibility of the EMI modeling technique. The prediction matched the measurement results only during low frequency harmonics, at higher frequencies the model failed to capture the system input DM noise. Experimentally, they found out that the DM input noise is coupled with CM noise and is dependent on the CM noise propagation

path in the system. Thus, they concluded that the one-port terminal model fails to predict the DM input noise precisely when the CM and DM noise is coupled.

To include the CM parts in the DM model, they developed a mixed-mode unterminated behavioral model that includes the entire propagation path, including the parastics which are the main propagation paths of the CM noise for the inverter input side.

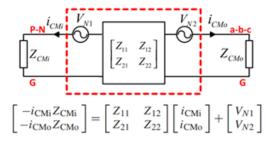

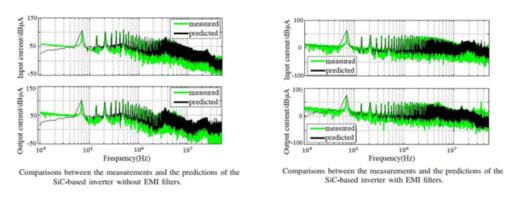

Figure 2-8: Modular terminated model and proposed DM model with LISN [22]