# Chapman University Chapman University Digital Commons

Engineering Faculty Articles and Research

Fowler School of Engineering

3-5-2021

# Implementing Inverse Design Tools for Plasmonic Digital Logic Devices

Krishna Narayan

Mark C. Harrison

Follow this and additional works at: https://digitalcommons.chapman.edu/engineering\_articles Part of the Atomic, Molecular and Optical Physics Commons, Other Electrical and Computer Engineering Commons, and the Other Physics Commons

## Implementing Inverse Design Tools for Plasmonic Digital Logic Devices

## Comments

This article was originally published in *Proceedings of SPIE*, volume 11680, Physics and Simulation of Optoelectronic Devices XXIX, in 2021. https://doi.org/10.1117/12.2577895

## Copyright

Society of Photo-Optical Instrumentation Engineers (SPIE)

## Implementing inverse design tools for plasmonic digital logic devices

Krishna Narayan<sup>a</sup>, Mark C. Harrison<sup>\*a</sup> <sup>a</sup>Fowler School of Engineering, Chapman University, One University Drive, Orange, CA, USA 92866

#### ABSTRACT

Despite the benefits that optics and photonics have brought to improving communications, there remains a lack of commercialized optical computing devices and systems, which reduces the benefits of using light as an information-carrying medium. We are developing architectures and designs of photonic logic gates for creating larger-scale functional photonic logic circuits. In contrast to other approaches, we are focusing on the development of logic devices which can be cascaded in arbitrary ways to allow for more complex photonic integrated circuit design. Additionally, optical computing often uses on-off keying, which fails to take advantage of denser encoding schemes often used to optically transmit data. We propose that devices that operate on phase-shift keying will not only be more efficient, but easier to cascade. To achieve the goal of cascadable devices operating on phase-shift keying, we have designed a plasmonic waveguide logic device using inverse design tools. These tools have allowed us to create a device with an arbitrary topology that has increased performance and reduced footprint compared to a conventional device with the same operation. In addition, inverse design simplifies the process of designing devices that operate with phase-shift keying, which can become complicated with conventional design methods. In order to implement inverse design tools for plasmonic devices and phase-shift keying, we used fully 3D FDTD simulations. We compare the inverse-designed devices to more conventional devices in order to characterize their performance. Keywords: plasmonics, photonic logic, inverse design, photonic integrated circuits, plasmonic devices

#### 1. INTRODUCTION

Conventional communication links typically rely on light to transmit information, but use electronic signals to process it<sup>1–3</sup>. By replacing the electronic processing with photonic circuits, we can allow for faster, lower power data transfer<sup>4–6</sup>. In other words, we can achieve increased information processing speed and higher-density information encoding as well. Typically, light intensity acts as an input and output for logic gates, but by using other encoding mechanisms, such as phase-shift keying (PSK), we can increase the density of our encoding.

Additionally, there are numerous photonic device architectures and geometries that are studied for use in photonic logic devices<sup>7–10</sup>. However, these architectures and geometries are often not compatible with one another, which is a barrier to designing large and complex photonic integrated circuits.

Our goal is to use surface plasmon polariton (SPP) waveguides to build faster and more compact logic gates. SPPs are electromagnetic surface waves that travel along a metal-dielectric interface. They have many benefits, including tight optical confinement which leads to small device footprints<sup>11</sup>. Using SPPs, which can be coupled beyond the diffraction-limit, we can construct photonic logic gates at the nanoscale.

To design and optimize a plasmonic logic gate, we use Lumerical FDTD, a photonic simulation software. Within Lumerical, we design our devices using a dielectric-loaded SPP (DLSPP) architecture. They consist of a metal layer on top of a substrate with a dielectric strip to define the waveguide. We are using binary

\*mharrison@chapman.edu

Physics and Simulation of Optoelectronic Devices XXIX, edited by Bernd Witzigmann, Marek Osiński, Yasuhiko Arakawa, Proc. of SPIE Vol. 11680, 1168005 · © 2021 SPIE CCC code: 0277-786X/21/\$21 · doi: 10.1117/12.2577895 phase-shift keying (BPSK) to encode the input and output of our device. Lumerical also provides us with multiple forms of optimization. For this work, we focus on using the inverse design optimization tools provided with Lumerical<sup>12</sup>. We compare the efficiency of both inverse and conventional designs and verify that inverse design creates a more compact, efficient design.

#### 2. METHODS

#### 2.1 Circuit Architecture

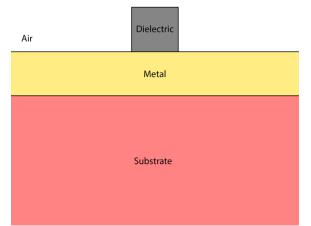

The plasmonic device uses silica stripes on gold film (Figure 1). Silica waveguides are used to help mitigate traditionally heavy loss exhibited by plasmonic circuits. This DLSPP architecture also provides a benefit when using inverse design tools, as we can optimize the dielectric material on top of the metal layer, reducing the complexity of the optimization task. The simulations are run with an operating wavelength of 1,550 nm, which is a typical wavelength used in optical communications.

Figure 1. Schematic cross-section of dielectric-loaded surface plasmon polariton waveguides. The metal material is gold and the dielectric material is SiO<sub>2</sub>.

#### 2.2 Designing an XOR gate

To initiate the procedure of designing photonic logic components, we chose to design an XOR gate, which lends itself particularly well to certain inverse design constraints and our use of binary phase-shift keying. Consider the conventional XOR gate, which has two inputs and 1 output. The output of the XOR gate is 1 if the two inputs are different from each other. When they are the same, the output is 0. Using BPSK, we assign 0° of phase to the logic 0 and 180° of phase to the logic 1 (Table 1). Therefore, the output of the logic gate should be 180° if the inputs are out of phase, and 0° if the inputs are in phase. For our photonic logic gate, the goal was to use two waveguides as inputs and a single output, but due to constraints with the inverse design tools, we initially design the device with two outputs and on-off keying at these outputs.

#### 2.3 Optimization

To optimize our photonic logic gate and explore the effectiveness of inverse design tools for this purpose, we compared simple conventionally-designed devices to a device designed with an inverse design optimization.

The inverse design tools allow us to define inputs and a figure of merit (output), and uses an adjoint-method based optimization to optimize the topology of a pre-defined region based on those constraints<sup>13</sup>. Traditional design, which is often guided by intuition, often involves parameter sweeps and is time-consuming if one wants to explore a large portion of the parameter-design space. Because inverse design uses gradient based algorithms to compute a set figure of merit in an iterative loop, fewer simulations are needed to explore the design space and the result is more compact designs with better performance using less time than conventional design methods.

| Input A             | Input B             | Output              |

|---------------------|---------------------|---------------------|

| Logic 0: 0° phase   | Logic 0: 0° phase   | Logic 0: 0° phase   |

| Logic 0: 0° phase   | Logic 1: 180° phase | Logic 1: 180° phase |

| Size of each file   | Logic 0: 0° phase   | Logic 1: 180° phase |

| Logic 1: 180° phase | Logic 1: 180° phase | Logic 0: 0° phase   |

Table 1. XOR logic gate operation with phase-shift keying.

#### 3. RESULTS

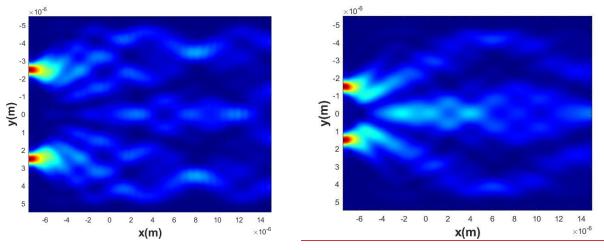

The results of conventionally-designed multi-mode interferometers (MMIs) designed with the goal of using them for an XOR gate are shown in Figure 2. The plots show the power of the optical fields in the device. For both simulations, the relative phase difference of the inputs is  $180^{\circ}$ , and the device is  $10 \ \mu m$  wide. The position of the input waveguides is shifted between the two simulations. These designs demonstrate how varying a single parameter (spacing between input waveguides) leads to drastically different results. The goal of designing an XOR gate is made much more difficult when relying solely on conventional design.

Figure 2. FDTD simulation results of conventionally designed MMIs with sources 180° out of phase.

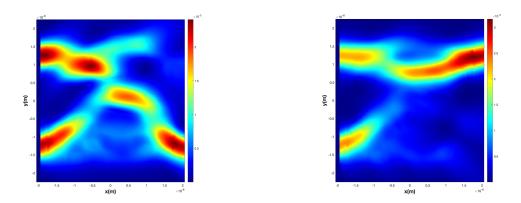

In contrast, using inverse design tools, we can accomplish complex design over multiple parameters more efficiently. For this design, we used two inputs and two outputs. We specified the relative phase of the inputs (in phase or 180° out of phase) and a single output waveguide for each condition. Figure 3 shows simulation results from inverse-designing the XOR gate. These simulations also show the power of the optical fields in the device. The simulation results show that the light will be sent to different outputs based on the relative

phase of the inputs. And in fact, the behavior shown in the simulations can be considered an XOR operation, with BPSK encoding at the inputs and on-off keying encoding at the outputs.

Figure 3. FDTD simulation results of inverse-designed XOR gate. On the left, the inputs are in phase and the signal is active at the bottom output. On the right, the inputs are 180° out of phase and the signal is active at the top output.

#### 4. CONCLUSION AND FUTURE WORK

We have demonstrated the feasibility of using plasmonic devices to construct logic gates, allowing for smaller, more efficient digital photonic components. In particular, we designed a plasmonic waveguide device using a DLSPP architecture that exhibits XOR-gate behavior using PSK-encoded inputs. Furthermore, we verified the advantages of inverse design for this process. These findings will allow us to optimize designs for other devices that behave as photonic logic gates. In the future, we will consider other digital logic gates, and consider how to re-encode the output to PSK, with the end goal of creating larger, more complex photonic integrated circuits.

#### 5. ACKNOWLEDGEMENTS

This work is supported by startup funds from Chapman University.

#### 6. **REFERENCES**

- Duan, L.-M., Lukin, M., Cirac, I. and Zoller, P., "Long-distance quantum communication with atomic ensembles and linear optics," Nature 414(6862), 413–418 (2001).

- [2] Minzioni, P., Lacava, C., Tanabe, T., Dong, J., Hu, X., Csaba, G., Porod, W., Singh, G., Willner, A. E., Almaiman, A., Torres-Company, V., Schröder, J., Peacock, A. C., Strain, M. J., Parmigiani, F., Contestabile, G., Marpaung, D., Liu, Z., Bowers, J. E., et al., "Roadmap on all-optical processing," J. Opt. 21(6), 063001 (2019).

- [3] Touch, J., Cao, Y., Ziyadi, M., Almaiman, A., Mohajerin-Ariaei, A. and Willner, A. E., "Digital optical processing of optical communications: towards an Optical Turing Machine," Nanophotonics 6(3) (2017).

- [4] Narayana, V. K., Sun, S., Mehrabian, A., Sorger, V. J. and El-Ghazawi, T., "HyPPI NoC: Bringing Hybrid Plasmonics to an Opto-Electronic Network-on-Chip," 2017 46th International Conference on Parallel Processing (ICPP), 131–140 (2017).

- [5] Sun, S., Badawy, A.-H. A., Narayana, V., El-Ghazawi, T. and Sorger, V. J., "The Case for Hybrid Photonic Plasmonic Interconnects (HyPPIs): Low-Latency Energy-and-Area-Efficient On-Chip Interconnects," IEEE Photonics J. 7(6), 1–14 (2015).

- [6] Zhang, Y., Samanta, A., Shang, K. and Yoo, S. J. B., "Scalable 3D Silicon Photonic Electronic Integrated Circuits and Their Applications," IEEE Journal of Selected Topics in Quantum Electronics 26(2), 1–10 (2020).

- [7] Abbas, M. N. and Abdulnabi, S. H., "Plasmonic reversible logic gates," J. Nanophoton. 14(01), 1 (2020).

- [8] Cui, L. and Yu, L., "Multifunctional logic gates based on silicon hybrid plasmonic waveguides," Mod. Phys. Lett. B 32(02), 1850008 (2018).

- [9] Fu, Y., Hu, X. and Gong, Q., "Silicon photonic crystal all-optical logic gates," Physics Letters A 377(3–4), 329–333 (2013).

- [10] Hassan, S. and Chack, D., "Design and performance analysis of MMI based all optical logic gates on SOI substrate," 2018 3rd International Conference on Microwave and Photonics (ICMAP), 1–2, IEEE, Dhanbad (2018).

- [11] Davis, T. J., Gómez, D. E. and Roberts, A., "Plasmonic circuits for manipulating optical information," Nanophotonics 6(3) (2017).

- [12] "Photonic Inverse Design.", Lumerical, <a href="https://www.lumerical.com/solutions/inverse-design/">https://www.lumerical.com/solutions/inverse-design/</a> (2 July 2020).

- [13] Lalau-Keraly, C. M., Bhargava, S., Miller, O. D. and Yablonovitch, E., "Adjoint shape optimization applied to electromagnetic design," Opt. Express 21(18), 21693 (2013).