# Low Operating Voltage, Solution-Processed Transistors with High-k/Self-Assembled Monolayer Dielectrics

A thesis submitted to The University of Manchester for the degree of Doctor of Philosophy in the Faculty of Science and Engineering

2020

## Navid Mohammadian

**School of Engineering**

Department of Electrical and Electronic Engineering

## **Table of Contents**

| List of I    | Publi          | ications                                                                           | 5    |

|--------------|----------------|------------------------------------------------------------------------------------|------|

| List of (    | Conf           | Perence Presentations                                                              | 6    |

| List of I    | F <b>igu</b> i | res                                                                                | 7    |

| List of 7    | Γabl           | es                                                                                 | 14   |

| Abbrev       | iatio          | ns                                                                                 | 16   |

| Abstrac      | et             |                                                                                    | 19   |

| Declara      | tion           |                                                                                    | 20   |

| Copyrig      | ght S          | Statement                                                                          | 21   |

| Acknow       | vledg          | gements                                                                            | 22   |

| Chapter      | r 1:           | Introduction                                                                       | 23   |

| 1.1          | A b            | rief history of transistors                                                        | 23   |

| 1.2          | Mo             | tivation, challenges and research aim                                              | 29   |

| 1.3          | Org            | ganisation of Manuscript                                                           | 33   |

| Chapte       | r 2:           | Literature review                                                                  | 35   |

| 2.1          | Ove            | erview of Thin-Film Transistors (TFTs)                                             |      |

| 2.1.         | .1             | TFT architectures                                                                  | 36   |

| 2.1.         | .2             | TFT operation                                                                      | 37   |

| 2.1.         | .3             | Low-voltage TFTs                                                                   | 44   |

| 2.2          | Sen            | niconductor Materials for TFTs                                                     | 45   |

| 2.2.         | .1             | Amorphous oxide semiconductors                                                     | 45   |

| 2.2.<br>tech | _              | Comparison of oxide and organic semiconductors with the conventional ogies of TFTs | 45   |

| 2.2.         | .3             | Organic semiconductors                                                             | 58   |

| 2.3          | Die            | electric materials for TFTs                                                        | 67   |

| 2.3.         | .1             | Background                                                                         | 67   |

| 2.3.         | .2             | Electrical properties                                                              | 73   |

| 2.3.         | .3             | High-κ dielectrics                                                                 | 73   |

| Chapte       | r 3:           | Experimental procedures                                                            | .112 |

| 3.1          | Mat            | terials selection                                                                  | .112 |

| 3.1.         | .1             | Contact Metals                                                                     | .112 |

| 3.1.         | .2             | Metal oxide dielectric: Ta <sub>2</sub> O <sub>5</sub>                             | .117 |

| 3.1.         | .3             | Dielectric surface modifier: OTS                                                   | .118 |

| 3.1.         | 4              | Semiconductors                                                                     | .120 |

| 3.2                      | Fab           | prication procedures                                                    | 123                               |

|--------------------------|---------------|-------------------------------------------------------------------------|-----------------------------------|

| 3.2                      | 2.1           | Cleaning procedures                                                     | 123                               |

| 3.2                      | 2.2           | Deposition of Metal Contacts                                            | 123                               |

| 3.2                      | 2.3           | Tantalum oxide dielectric deposition                                    | 124                               |

| 3.2                      | 2.4           | The deposition of DPPDTT/PMMA OSC                                       | 126                               |

| 3.2                      | 2.5           | The deposition of a-IGZO inorganic semiconductor                        | 127                               |

| 3.3                      | Me            | asurement and Characterisation techniques                               | 127                               |

| 3.3                      | 3.1           | Capacitance Measurement                                                 | 127                               |

| 3.3                      | 3.2           | Current-Voltage (I-V) Curve Measurements                                | 128                               |

| 3.3                      | 3.3           | Dielectric surface analysis                                             | 129                               |

| 3.3                      | 3.4           | Surface chemistry analysis                                              | 129                               |

| Chapte                   | er 4:         | Result and Discussion                                                   | 130                               |

| 4.1<br>Ta <sub>2</sub> C | Lov<br>05 130 | w-voltage p-channel DPPDTT/PMMA TFTs gated with OTS-modi                | fied Anodic                       |

| 4.1                      | 1.1           | Introduction                                                            | 130                               |

| 4.1                      | 1.2           | Experimental procedure                                                  | 131                               |

| 4.1                      | 1.3           | Results and discussion                                                  | 133                               |

| 4.1                      | 1.4           | Conclusion                                                              | 149                               |

| 4.2                      | Lov<br>149    | w-voltage n-channel a-IGZO TFTs gated with OTS-modified Anod            | ic Ta <sub>2</sub> O <sub>5</sub> |

| 4.2                      | 2.1           | Introduction                                                            | 149                               |

| 4.2                      | 2.2           | Experimental procedure                                                  | 150                               |

| 4.2                      | 2.3           | Results and discussion                                                  | 152                               |

| 4.2                      | 2.4           | Conclusion                                                              | 168                               |

| Chapte                   | er 5:         | Memristive Devices Based on Anodic Ta <sub>2</sub> O <sub>5</sub> Films | 169                               |

| 5.1                      | Intr          | oduction                                                                | 169                               |

| 5.2                      | Me            | mristive devices based on TaO <sub>x</sub>                              | 173                               |

| 5.3                      | Exp           | perimental procedure                                                    | 174                               |

| 5.4                      | Res           | sults and discussion                                                    | 175                               |

| 5.5                      | Cor           | nclusions                                                               | 177                               |

| Chapte                   | er 6:         | Conclusions and Future work                                             | 178                               |

| 6.1                      | Cor           | nclusions                                                               | 178                               |

| 6.2                      | Fut           | ure work                                                                | 180                               |

| Refere                   | nces .        |                                                                         | 183                               |

| Appen                    | dices         |                                                                         | 204                               |

| Appendix 1: XPS analysis | of anodised Ta films | 204 |

|--------------------------|----------------------|-----|

|--------------------------|----------------------|-----|

**Word count: 41,596**

### **List of Publications**

This thesis contains and discusses the results published in the following publications:

- N. Mohammadian and L. A. Majewski, "High Capacitance Dielectrics for Low-Voltage Operated OFETs in Organic Field-Effect Transistors," in Integrated Circuits/Microchips, K. H. Yeap and J. Sayago, *IntechOpen.*, 2020, pp. 87-110, doi: 10.5772/intechopen.91772.

- M. Sophocleous, **N. Mohammadian**, L. A. Majewski, J. Georgiou, "Solution-processed, low-voltage tantalum-based memristive switches," *Materials Letters*, vol. 269, 127676, Jun 2020, doi: 10.1016/j.matlet.2020.127676.

- N. Mohammadian, B. C. Das and L. A. Majewski, "Low-Voltage IGZO TFTs Using Solution-Deposited OTS-Modified Ta<sub>2</sub>O<sub>5</sub> Dielectric,", *IEEE Transactions on Electron Devices*, vol. 67, no. 4, pp. 1625-1631, Apr 2020, doi: 10.1109/TED.2020.2976634.

- S. Sagar, N. Mohammadian, S. Park, L. A. Majewski, B. C. Das, "Ultra-thin anodized aluminium dielectric films: the effect of citric acid concentration and low-voltage electronic applications," *Nanotechnology*, vol. 31, 255705, Apr 2020, doi: 10.1088/1361-6528/ab7fd1.

- N. Mohammadian, S. Faraji, S. Sagar, B.C. Das, M.L. Turner, L.A. Majewski, "One-Volt, Solution-Processed Organic Transistors with Self-Assembled Monolayer-Ta<sub>2</sub>O<sub>5</sub> Gate Dielectrics," *Materials*, vol. 12, 2563, Aug 2019, doi: 10.3390/ma12162563.

Additional publications not discussed in this thesis:

- M. Seck, N. Mohammadian, A. K. Diallo, S. Faraji, M. Saadi, M. Erouel, et al., "Low-voltage organic transistors with water-processed gum Arabic dielectric," Synthetic Metals, vol. 267, 116447, Sep 2020, doi: 10.1016/j.synthmet.2020.116447.

- M. Seck, N. Mohammadian, A. K. Diallo, S. Faraji, M. Erouel, N. Bouguila, L. A. Majewski, "Organic FETs using biodegradable almond gum as gate dielectric: A promising way towards green electronics," *Organic Electronics*, vol. 83, 105735, Aug 2020, doi: 10.1016/j.orgel.2020.105735.

## **List of Conference Presentations**

- N. Mohammadian, L. A. Majewski, "Solution-processed electronics: Low-voltage Organic Transistors (OFETs)," *IOP PGS Conference: Printing for the future 2020*, Jul 2020, online.

- N. Mohammadian, L. A. Majewski, "Low-power High-performance a-IGZO Thin-Film Transistor using OTS Modified Ta<sub>2</sub>O<sub>5</sub> as the gate dielectric," *innoLAE* (*innovations in Large-Area Electronics*) 2020, Jan 2020, Cambridge.

- N. Mohammadian, S. Faraji, L. A. Majewski, "Solution-processed polymer transistor using Tantalum Pentoxide dielectric," *IOP PGS Conference: Printing for the future 2019*, Apr 2019, Hertfordshire.

- N. Mohammadian, S. Faraji, M. L. Turner, L. A. Majewski, "Ultra-low voltage organic field-effect transistors (OFETs)," *innoLAE* (*innovations in Large-Area Electronics*) 2019, Jan 2019, Cambridge.

- N. Mohammadian, S. Faraji, L. A. Majewski, "High-κ Anodic Dielectrics for Low-voltage Applications," *The PGR Poster Conference 2018*, Nov 2018, Manchester.

# **List of Figures**

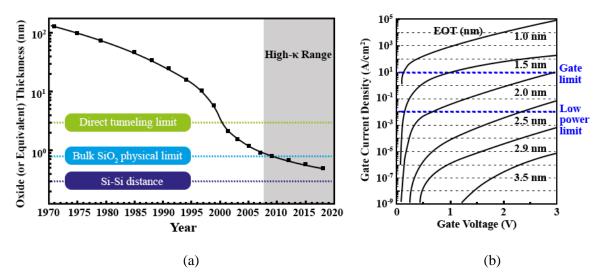

| Fig. | 1.1. (a) The semiconductor industry roadmap for gate dielectric thickness scaling [26]                     |

|------|------------------------------------------------------------------------------------------------------------|

|      | and (b) leakage current density ( $J_{leak}$ ) versus voltage for various $SiO_2$ dielectric               |

|      | thicknesses [27]                                                                                           |

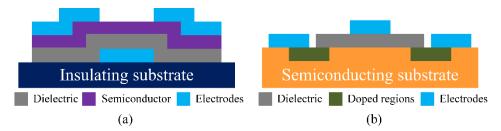

| Fig. | 2.1. Typical structures of (a) a bottom-gate top-contact TFT and (b) a MOSFET. Doped                       |

|      | regions refer to the MOSFET drain and source regions                                                       |

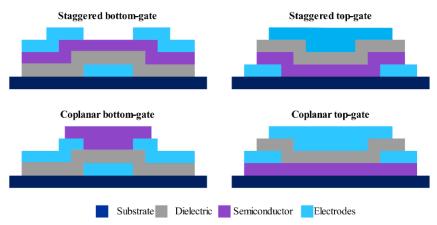

| Fig. | 2.2. The most common structures of TFTs                                                                    |

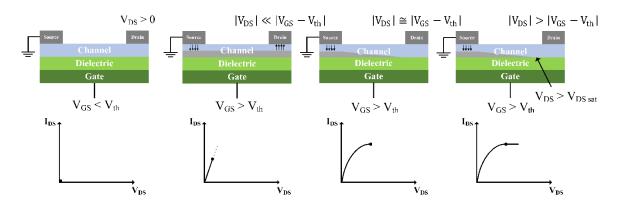

| Fig. | 2.3. Schematics of an ideal n-channel TFT operation (a) cut-off, (b) linear regime, (c                     |

|      | pinch-off, and (d) saturation regime (the same structure used in the fabrication of low-                   |

|      | voltage TFTs in this thesis)                                                                               |

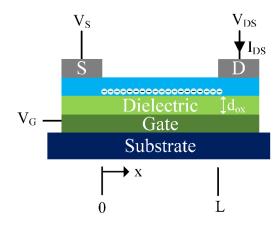

| Fig. | 2.4. The schematic of a TFT, when $V_{DS} \neq 0$ , the channel voltage $V_c$ is a function of $\Sigma$    |

|      | and d <sub>ox</sub> is the dielectric thickness                                                            |

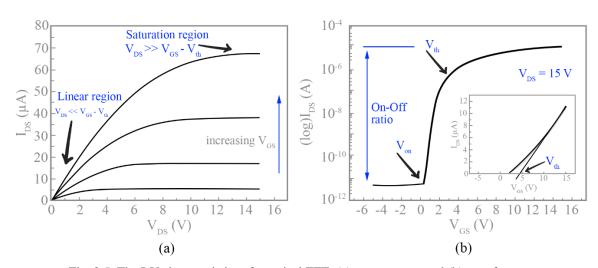

| Fig. | 2.5. The I-V characteristics of a typical TFT: (a) output curve and (b) transfer curve.40                  |

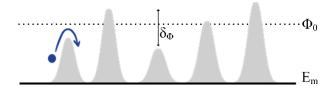

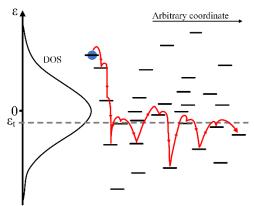

| Fig. | 2.6. Random barrier model for band transport above the band edge $E_{\rm m}$ affected by                   |

|      | random potential barriers [80]                                                                             |

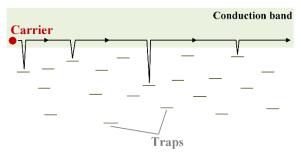

| Fig. | 2.7. A schematic of the multiple-trapping process (MTR) [86]                                               |

| Fig. | 2.8. Schematic of carrier energy relaxation via the transport energy in a Gaussian DOS                     |

|      | [92]53                                                                                                     |

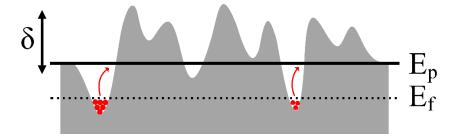

| Fig. | 2.9. The schematic of the spatial fluctuations of band edge $E_{\rm m}$ in the random band-edge            |

|      | model. The carrier motion is due to activation from Fermi level E <sub>f</sub> towards the                 |

|      | percolation level E <sub>p</sub> [80].                                                                     |

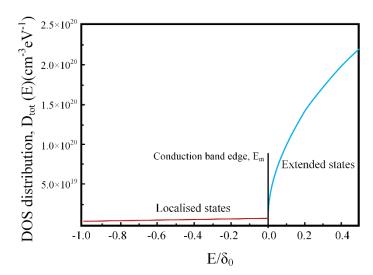

| Fig. | 2.10. Cumulative DOS D <sub>tot</sub> (E) distribution [74]54                                              |

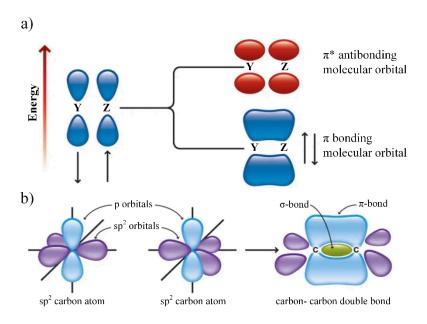

| Fig. | 2.11. sp hybridisation of a carbon atom—s and p orbitals can mix and form sp, sp <sup>2</sup> and          |

|      | sp <sup>3</sup> hybrid orbitals, respectively60                                                            |

| Fig. | 2.12. a) $\pi$ orbital formation from two p-orbitals, and b) formation of $\sigma$ - and $\pi$ - molecular |

|      | orbitals from two sp <sup>2</sup> hybridised carbon atoms                                                  |

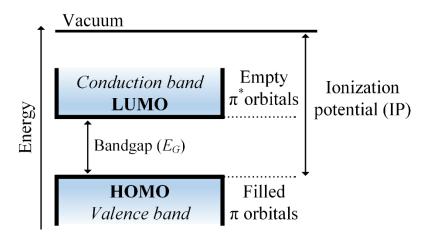

| Fig. | 2.13. Representative energy band diagram of an organic semiconductor61                                      |

|------|-------------------------------------------------------------------------------------------------------------|

| Fig. | 2.14. Chemical structure of the representative p-type small molecule semiconductors                         |

|      | [99]62                                                                                                      |

| Fig. | 2.15. Chemical structure of the representative p-type polymer semiconductors [99]63                         |

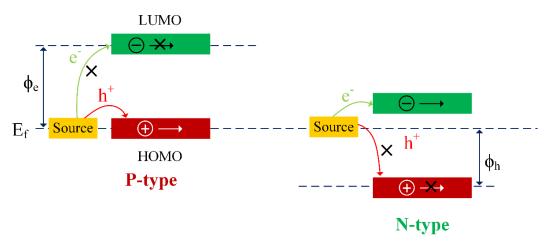

| Fig. | $2.16$ . The schematic shows the relationships among the Fermi energy ( $E_{\rm f}$ ) of the source         |

|      | electrode, the frontier energies of the organic semiconductor, and the polarity of the                      |

|      | majority charge carriers of the OFET device, where $\varphi_e$ and $\varphi_h$ denote the electron and      |

|      | hole injection barrier heights, respectively, and "x" denotes the inhibition of charge                      |

|      | injection or transport [100]64                                                                              |

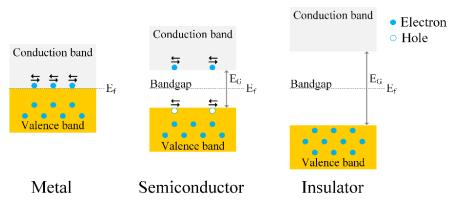

| Fig. | 2.17. The band structure of a metal, semiconductor and insulator68                                          |

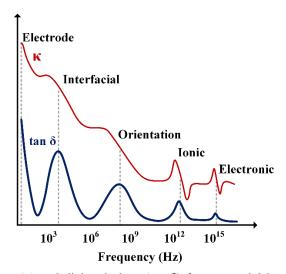

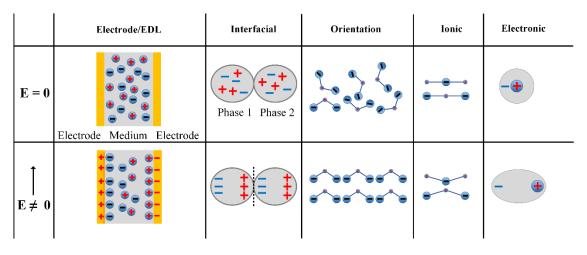

| Fig. | 2.18. Dielectric constant ( $\kappa$ ) and dielectric loss (tan $\delta$ ) for a material having electrode, |

|      | space charges (interfacial or free-counterions), orientation, relaxation, condensed-                        |

|      | counterions ionic, and electronic polarisation [5]70                                                        |

| Fig. | 2.19. The schematics of dielectric polarisation mechanisms                                                  |

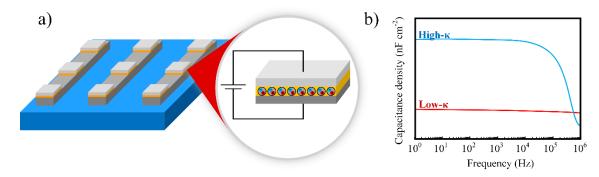

| Fig. | 2.20. a) Schematic diagram of a parallel-plate metal-insulator-metal (MIM) capacitor,                       |

|      | and b) comparison of the frequency-dependent capacitance density of ideal high- $\kappa$ and                |

|      | low-κ dielectrics72                                                                                         |

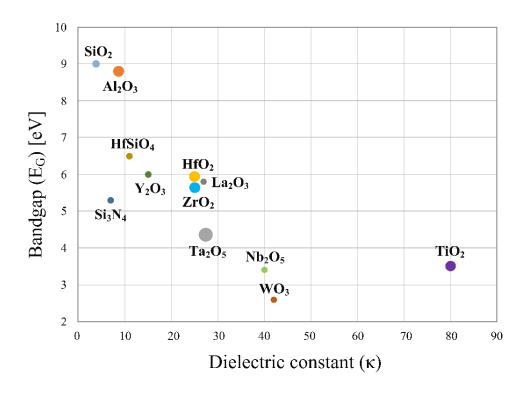

| Fig. | 2.21. Dielectric constant (κ) vs energy gap (E <sub>G</sub> ) for the most common inorganic                 |

|      | dielectric materials [146].                                                                                 |

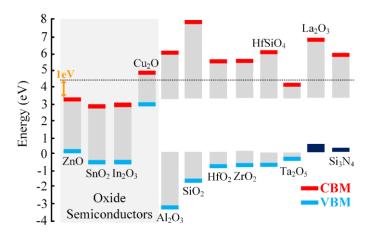

| Fig. | 2.22. Calculated band offsets of the indicated dielectrics. The values are normalised to                    |

|      | the VBM of ZnO. The dotted line indicates the minimum of 1 eV for the conduction                            |

|      | band offset [5]80                                                                                           |

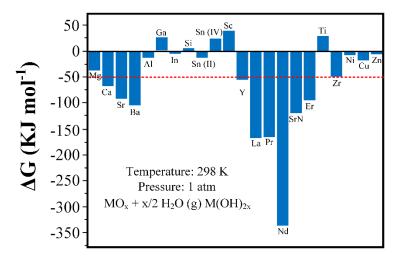

| Fig. | 2.23. $\Delta G$ for the moisture absorption reactions in high- $\kappa$ metal oxides under standard        |

|      | conditions. The $\Delta G$ values are calculated by using HSC Chemistry software [5]81                      |

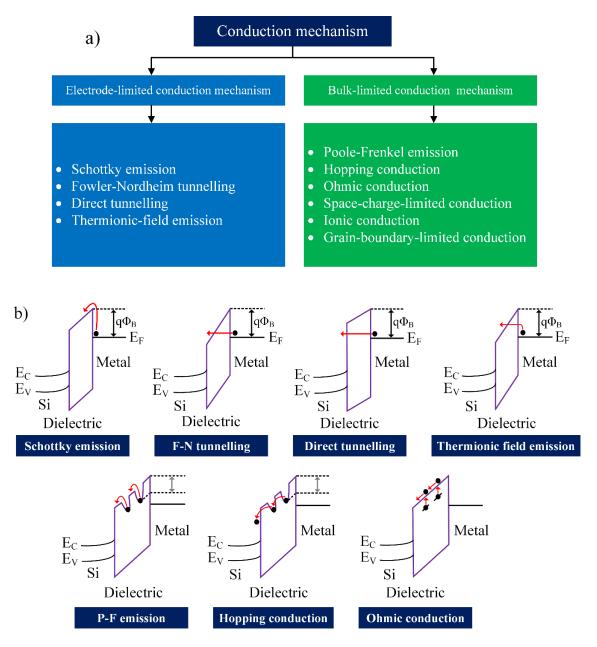

| Fig. | 2.24. (a) The classification of the conduction mechanisms and (b) their corresponding                       |

|      | energy band diagrams83                                                                                      |

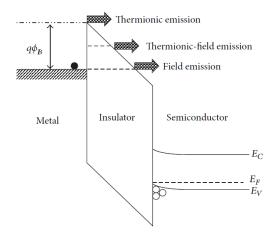

| Fig. | 2.25. The schematic of different conduction mechanisms: thermionic, thermionic-field                           |

|------|----------------------------------------------------------------------------------------------------------------|

|      | emission and field emission85                                                                                  |

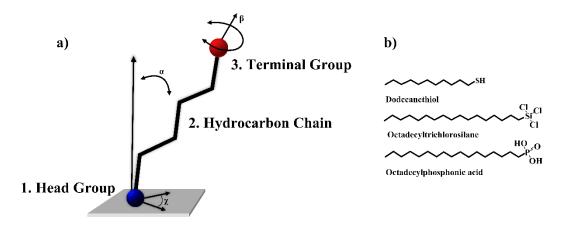

| Fig. | 2.26. (a) The representative schematic of self-assembly molecule, and (b) three                                |

|      | prominent SAMs89                                                                                               |

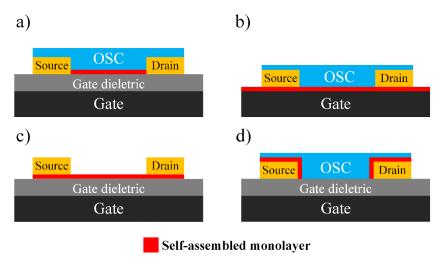

| Fig. | 2.27. SAMs role in TFTs a) dielectric primer, b) main dielectric, c) semiconductor, and                        |

|      | d) electrode modifier89                                                                                        |

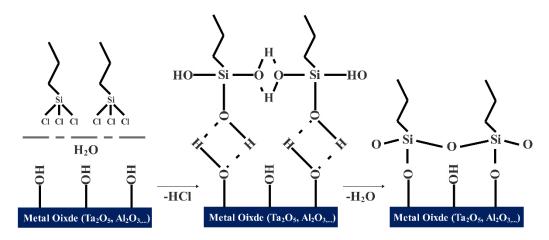

| Fig. | 2.28. The schematic representation of the silanization reaction                                                |

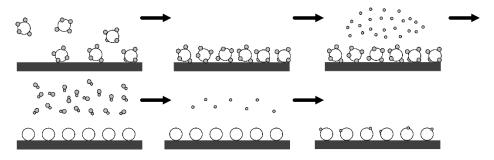

| Fig. | 2.29. Atomic layer deposition process                                                                          |

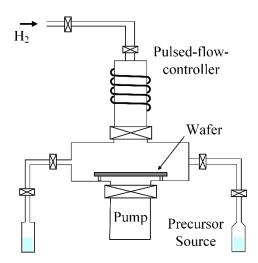

| Fig. | 2.30. Schematic of a plasma-enhanced atomic layer deposition (PEALD) system93                                  |

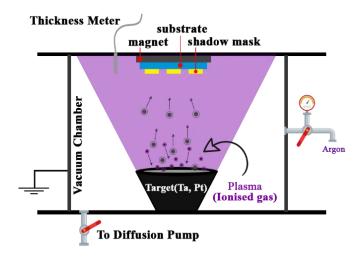

| Fig. | 2.31. Schematic of the RF magnetron sputtering process                                                         |

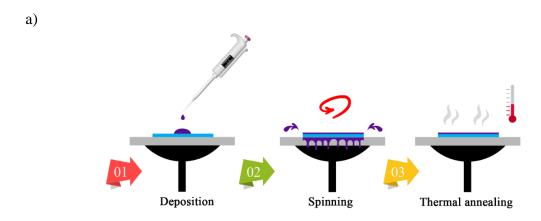

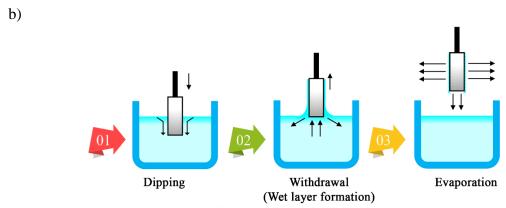

| Fig. | 2.32. Schematic of (a) the spin coating and (b) dip coating processes97                                        |

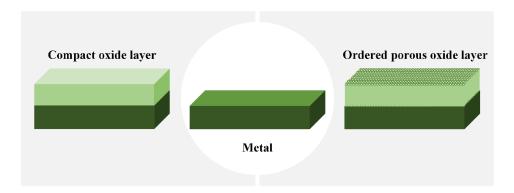

| Fig. | 2.33. Different morphologies of barrier and porous type oxide layers formed by                                 |

|      | anodisation of valve metals                                                                                    |

| Fig. | 2.34. The schematic diagram of the electrochemical cell set-up for the anodisation                             |

|      | process                                                                                                        |

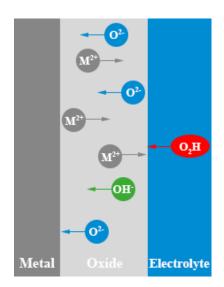

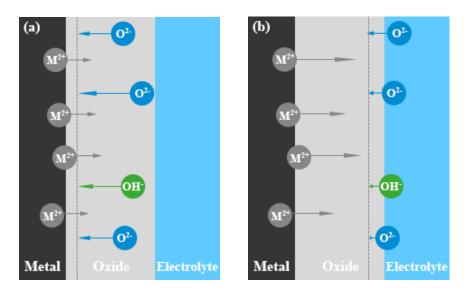

| Fig. | 2.35. The representative schematic of the migration of ions through the oxide layer                            |

|      | under the applied high electric field during the anodisation process104                                        |

| Fig. | 2.36. The representative schematic of the anodisation process where (a) inward anionic                         |

|      | transport is dominant, and (b) outward cationic transport is dominant107                                       |

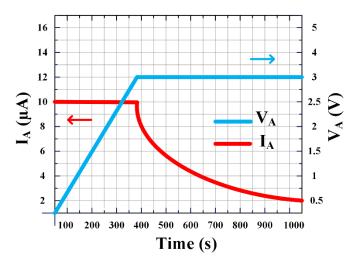

| Fig. | 2.37. Anodisation voltage (V <sub>A</sub> ) and anodisation current (I <sub>A</sub> ) vs anodisation time (t). |

|      |                                                                                                                |

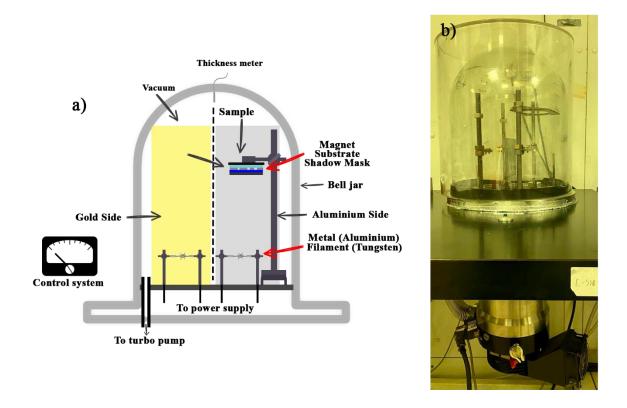

| Fig. | 3.1. (a) The schematic and (b) the actual picture of the turbo-pump thermal evaporator.                        |

|      | 116                                                                                                            |

| Fig. | 3.2. The actual picture of the employed RF magnetron sputtering system117                                      |

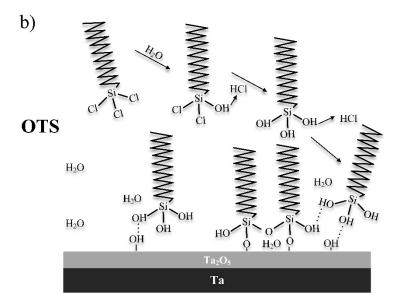

| Fig. | 3.3. (a) The chemical structure of OTS and (b) schematic of the Ta <sub>2</sub> O <sub>5</sub> surface         |

|      | passivation process [226]119                                                                                   |

| Fig. 3.4. The chemical structure of DPPDTT [99]                                                                   |

|-------------------------------------------------------------------------------------------------------------------|

| Fig. 3.5. The chemical structure of PMMA.                                                                         |

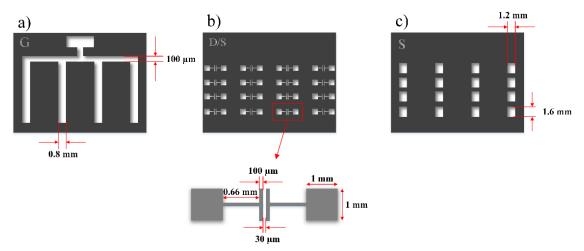

| Fig. 3.6. Schematic of (a) custom design gate electrode shadow mask, (b) drain and source                         |

| contacts shadow mask (Ossila, UK) and (c) custom design semiconductor (IGZO)                                      |

| shadow mask                                                                                                       |

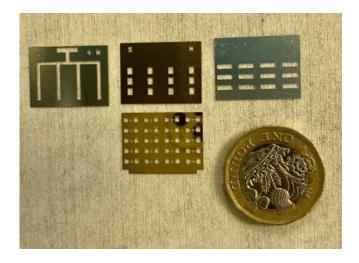

| Fig. 3.7. Actual picture of the gate electrode, drain and source contacts, semiconductor                          |

| (IGZO) layer, and capacitor top electrode shadow masks                                                            |

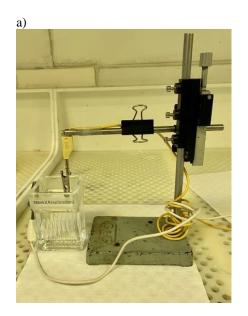

| Fig. 3.8. a) Experimental anodisation setup and b) Keithley SourceMeter 2400125                                   |

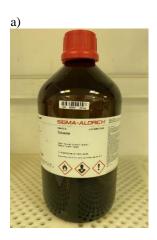

| Fig. 3.9. (a) Anhydrous toluene (Sigma-Aldrich, 99.8%) (b) <i>n</i> -octadecyltrichlorosilane                     |

| (Sigma-Aldrich, 95%)                                                                                              |

| Fig. 3.10. (a) Anhydrous 1,2-Dichlorobenzene (DCB) (Sigma-Aldrich, 99%) (b) DPPDTT                                |

| p-type OSC (Ossila, UK) (c) PMMA (Sigma-Aldrich)127                                                               |

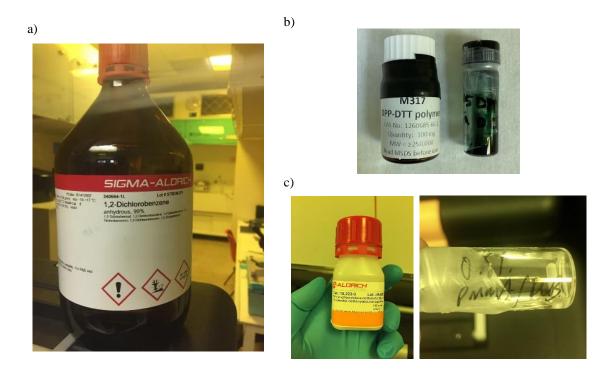

| Fig. 3.11. a) The measurement set-up and b) The Agilent E4980A LCR meter128                                       |

| Fig. 3.12. a) The measurement set-up and b) The Agilent E5270B precision IV analyser.                             |

|                                                                                                                   |

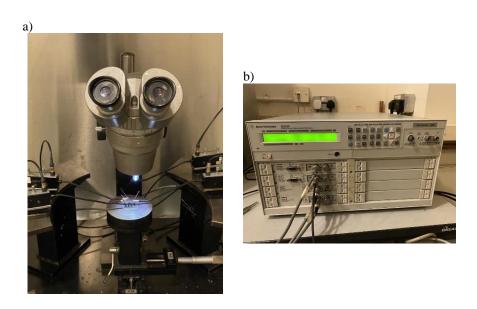

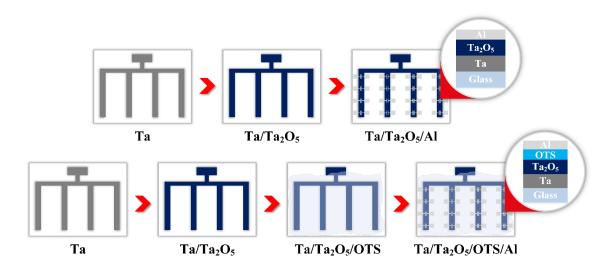

| Fig. 4.1. The schematic of the fabrication process of MIM capacitors with (a) untreated                           |

| $Ta_2O_5$ (b) OTS-treated $Ta_2O_5$ .                                                                             |

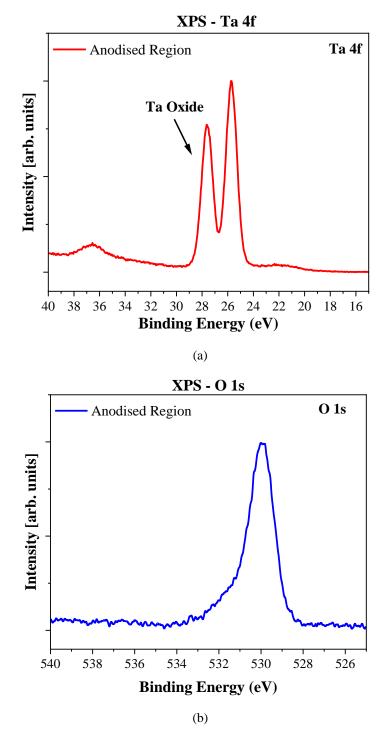

| Fig. 4.2. Normalised (a) Ta 4f spectra (b) O 1s spectra of the anodised region                                    |

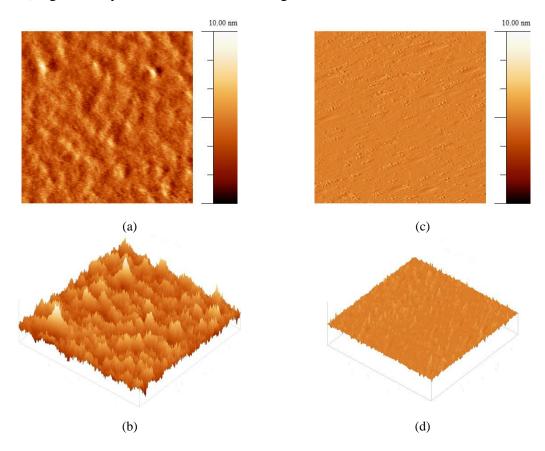

| Fig. 4.3. $500 \text{ nm} \times 500 \text{ nm} 2D$ and $3D$ AFM topographical images of (a, b) untreated and (c, |

| d) OTS-treated Ta <sub>2</sub> O <sub>5</sub> films                                                               |

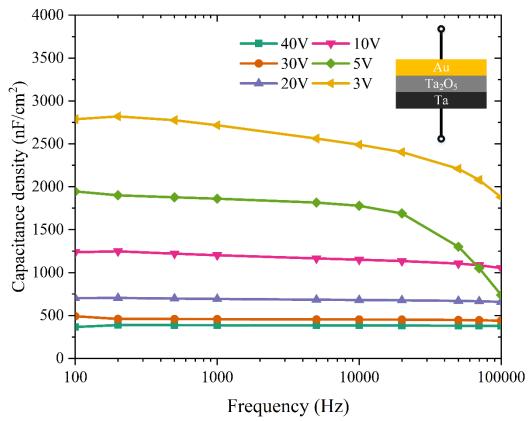

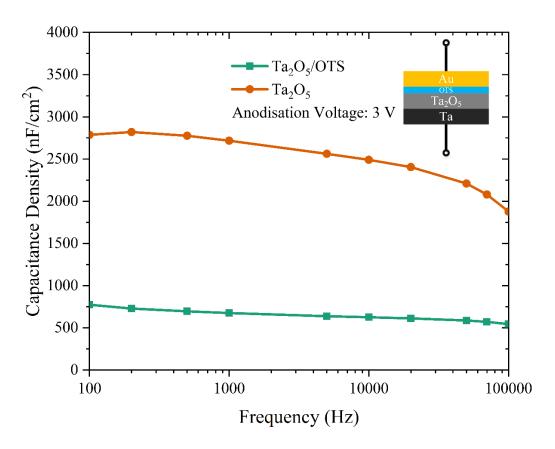

| Fig. 4.4. Capacitance density vs frequency of the studied Ta/Ta <sub>2</sub> O <sub>5</sub> /Au capacitors137     |

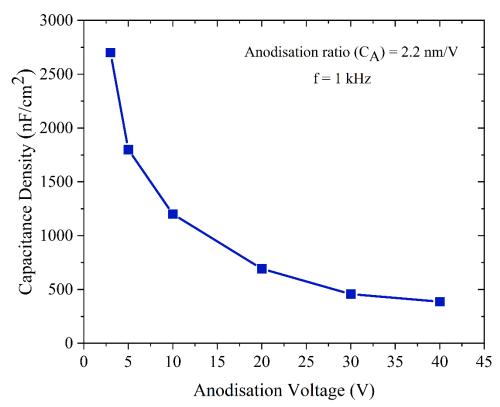

| Fig. 4.5. Capacitance density vs anodisation voltage at 1 kHz of the studied $Ta/Ta_2O_5/Au$                      |

| capacitors                                                                                                        |

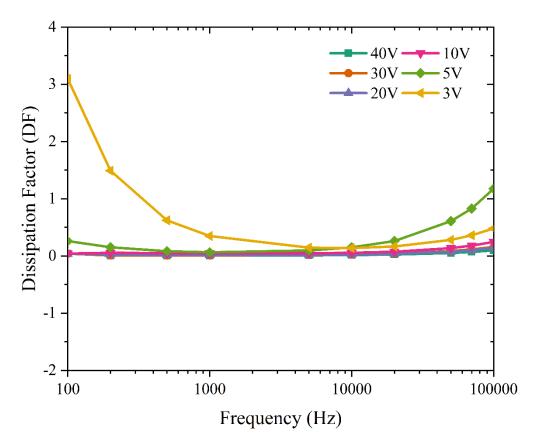

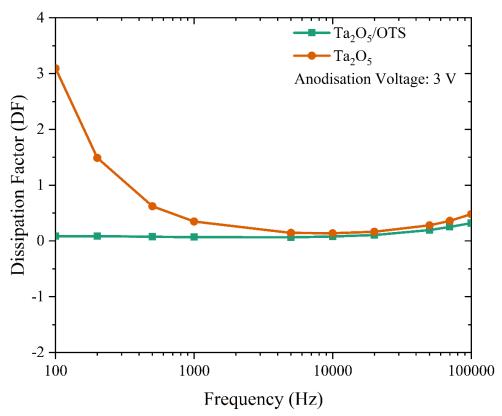

| Fig. 4.6. Dissipation factor vs frequency of the studied Ta/Ta <sub>2</sub> O <sub>5</sub> /Au capacitors139      |

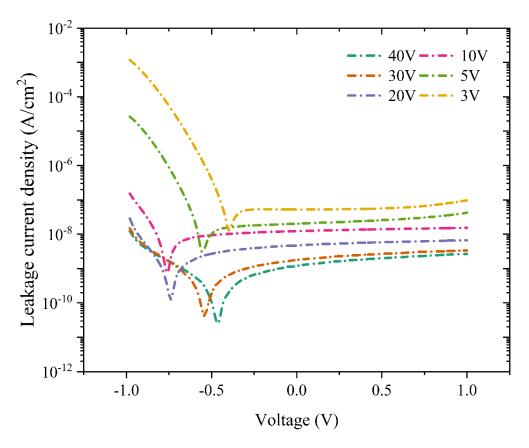

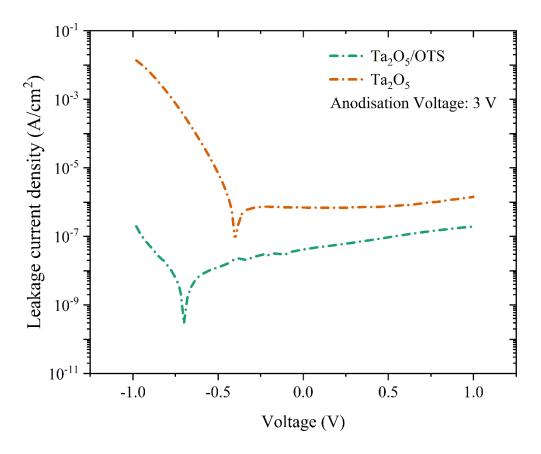

| Fig. 4.7. Leakage current density vs voltage of the studied Ta/Ta <sub>2</sub> O <sub>5</sub> /Au capacitors140   |

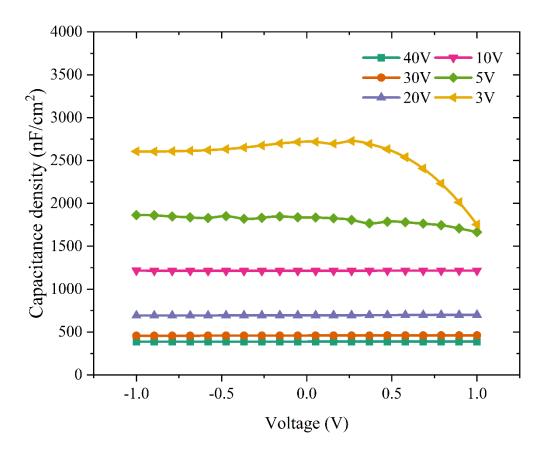

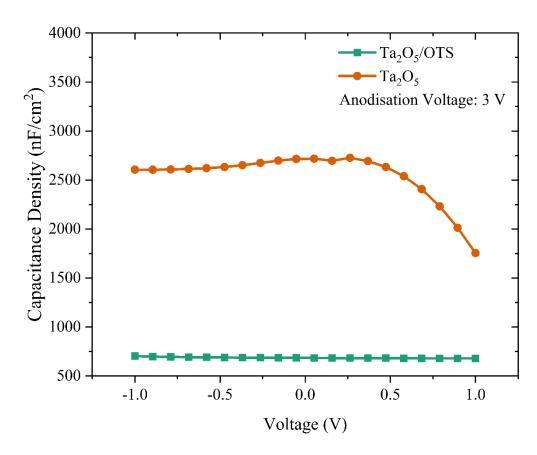

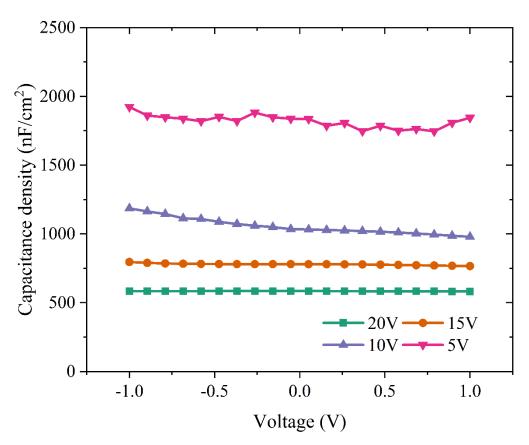

| Fig. 4.8. Capacitance density vs voltage of the studied Ta/Ta <sub>2</sub> O <sub>5</sub> /Au capacitors141       |

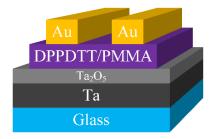

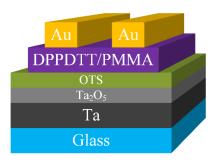

| Fig. 4.9. The schematic structure of the OTFTs using $Ta_2O_5$ anodised at $V_A = 20 \text{ V}141$                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------|

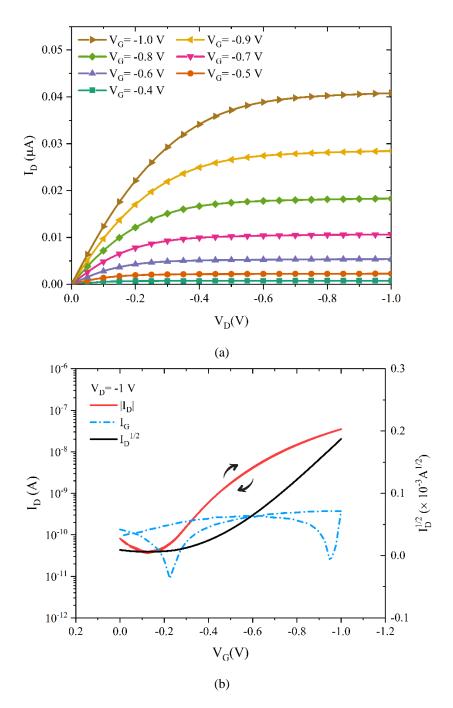

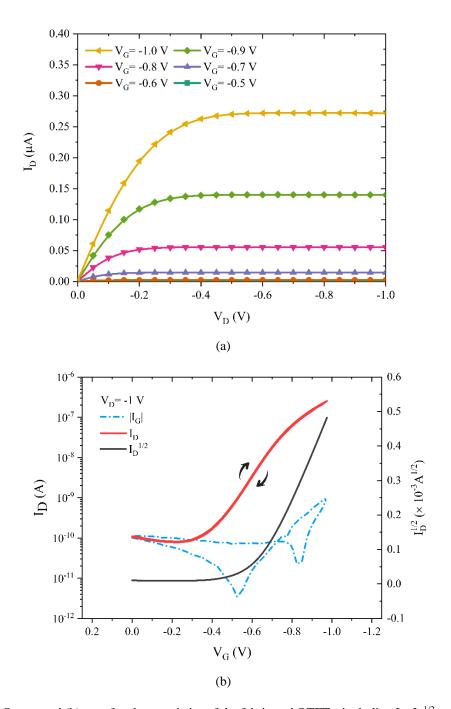

| Fig. 4.10. Representation (a) output and (b) transfer characteristics of the studied OTFTs                                                    |

| including $I_D^{1/2}$ and $I_G$ vs $V_G$ at $V_D$ = -1, respectively                                                                          |

| Fig. 4.11. Capacitance density vs frequency of the 3 V anodised Ta/Ta <sub>2</sub> O <sub>5</sub> /Au capacitors with                         |

| and without OTS treatment. 144                                                                                                                |

| Fig. 4.12. Dissipation factor vs frequency of the 3 V anodised Ta/Ta <sub>2</sub> O <sub>5</sub> /Au capacitors with                          |

| and without OTS treatment                                                                                                                     |

| Fig. 4.13. Leakage current density vs voltage of the 3 V anodised Ta/Ta <sub>2</sub> O <sub>5</sub> /Au capacitors                            |

| with and without OTS treatment                                                                                                                |

| Fig. 4.14. Capacitance density vs voltage of the 3 V anodised Ta/Ta <sub>2</sub> O <sub>5</sub> /Au capacitors with                           |

| and without OTS treatment                                                                                                                     |

| Fig. 4.15. The schematic structure of the OTFTs using OTS-modified Ta <sub>2</sub> O <sub>5</sub> anodised at V <sub>A</sub>                  |

| = 3 V                                                                                                                                         |

| Fig. 4.16. (a) Output and (b) transfer characteristics of the fabricated OTFTs including $I_D$                                                |

| $I_D^{1/2}$ and $I_G$ vs $V_G$ at $V_D = -1$ V, respectively                                                                                  |

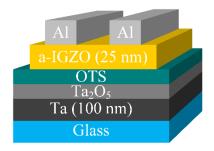

| Fig. 4.17. The schematic of the fabrication process of MIM capacitors with (a) untreated                                                      |

| Ta <sub>2</sub> O <sub>5</sub> (b) OTS-treated Ta <sub>2</sub> O <sub>5</sub>                                                                 |

| Fig. 4.18. The representative output and transfer characteristics of a-IGZO TFTs using (a                                                     |

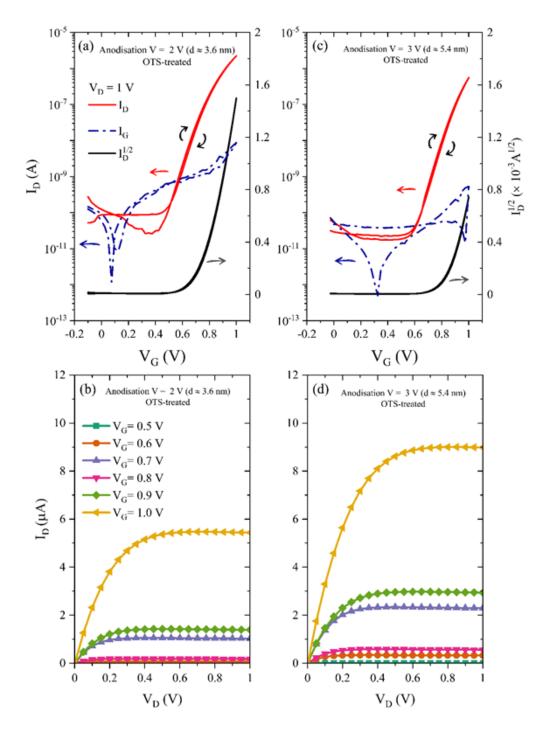

| b) 2 V anodised Ta <sub>2</sub> O <sub>5</sub> ( $\approx$ 3.6 nm), (c, d) 3 V anodised Ta <sub>2</sub> O <sub>5</sub> ( $\approx$ 5.4 nm)154 |

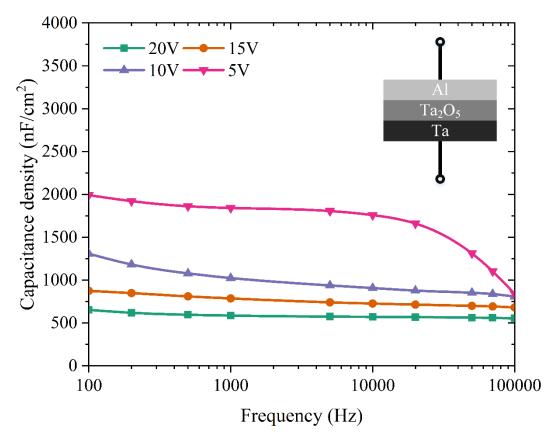

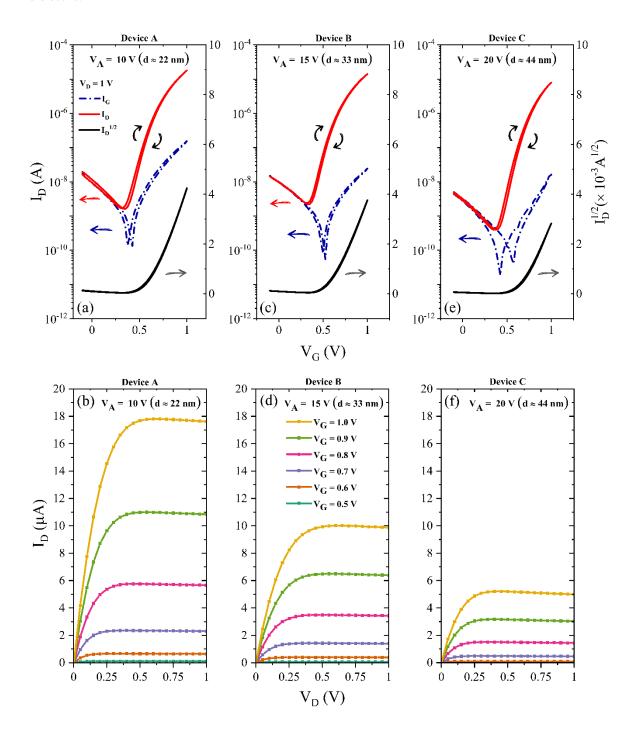

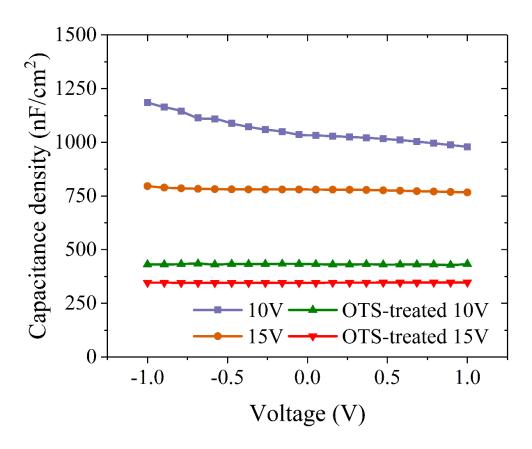

| Fig. 4.19. Capacitance density vs frequency of the studied Ta/Ta <sub>2</sub> O <sub>5</sub> /Al capacitors156                                |

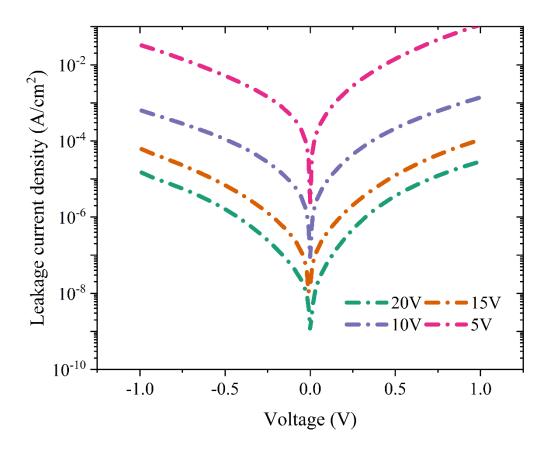

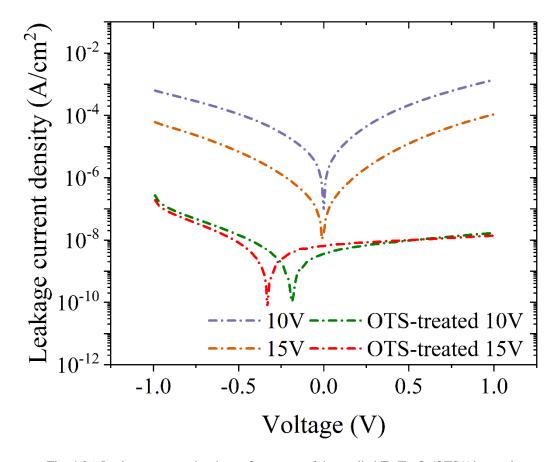

| Fig. 4.20. Leakage current density vs applied voltage of the studied Ta/Ta <sub>2</sub> O <sub>5</sub> /Al capacitors                         |

|                                                                                                                                               |

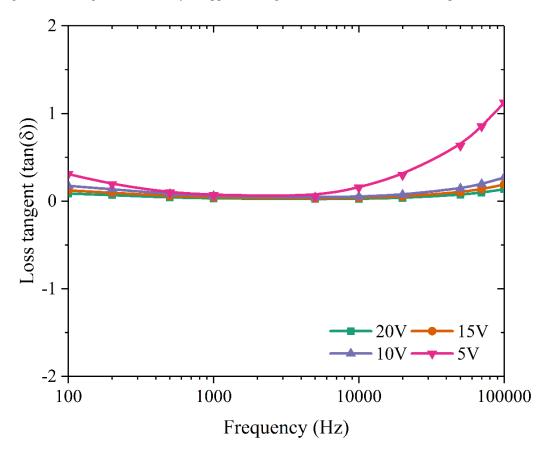

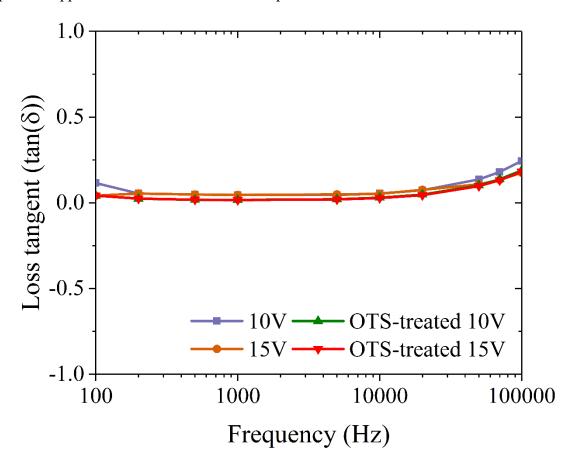

| Fig. 4.21. Loss tangent vs frequency of the studied Ta/Ta <sub>2</sub> O <sub>5</sub> /Al capacitors157                                       |

| Fig. 4.22. Capacitance density vs voltage characteristics of the studied Ta/Ta <sub>2</sub> O <sub>5</sub> /A                                 |

| capacitors                                                                                                                                    |

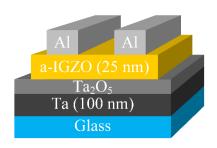

| Fig.  | 4.23. The schematic structure of the fabricated Ta/Ta <sub>2</sub> O <sub>5</sub> /IGZO/Al TFTs using pristine                              |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------|

|       | Ta <sub>2</sub> O <sub>5</sub> gate dielectric                                                                                              |

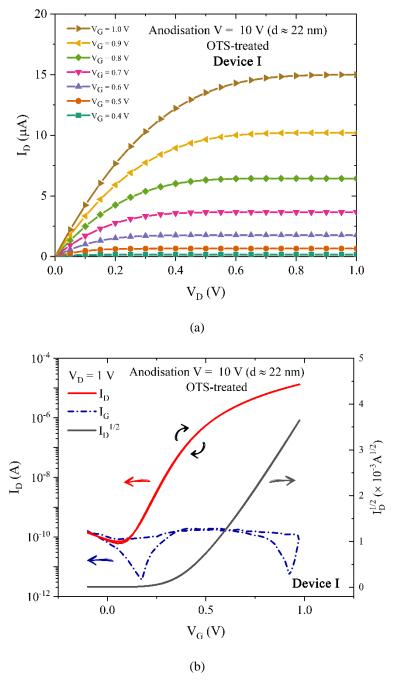

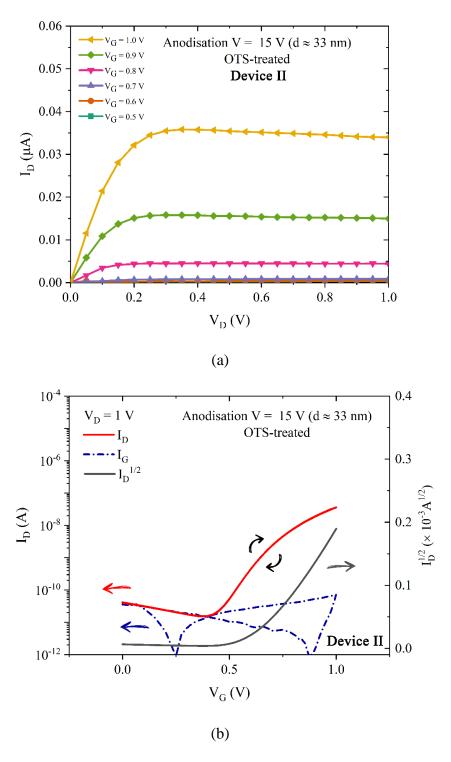

| Fig.  | 4.24. The representative output and transfer characteristics of a-IGZO TFTs using (a, b)                                                    |

|       | 10 V anodised Ta <sub>2</sub> O <sub>5</sub> (22 $\pm$ 2 nm, device A), (c, d) 15 V anodised Ta <sub>2</sub> O <sub>5</sub> (33 $\pm$ 3 nm, |

|       | device B), and (e, f) 15 V anodised $Ta_2O_5$ (44 $\pm$ 4 nm, device C)                                                                     |

| Fig.  | 4.25. Capacitance density vs frequency of the studied Ta/Ta <sub>2</sub> O <sub>5</sub> /OTS/Al capacitors.                                 |

|       |                                                                                                                                             |

| Fig.  | 4.26. Leakage current density vs frequency of the studied Ta/Ta <sub>2</sub> O <sub>5</sub> /OTS/Al capacitors.                             |

|       |                                                                                                                                             |

| Fig.  | 4.27. Loss tangent (δ) vs frequency of the studied Ta/Ta <sub>2</sub> O <sub>5</sub> /OTS/Al capacitors163                                  |

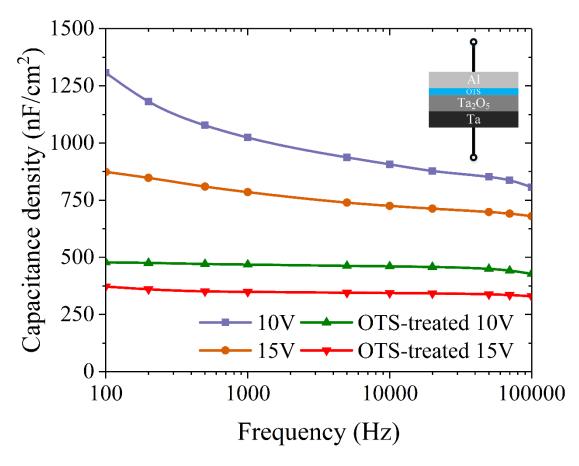

| Fig.  | 4.28. Capacitance density vs voltage characteristics of the studied Ta/Ta <sub>2</sub> O <sub>5</sub> /OTS/Al                               |

|       | capacitors                                                                                                                                  |

| Fig.  | 4.29. The schematic structure of the fabricated Ta/Ta <sub>2</sub> O <sub>5</sub> /OTS/IGZO/Al TFTs using                                   |

|       | SAM-modified Ta <sub>2</sub> O <sub>5</sub> gate dielectric                                                                                 |

| Fig.  | 4.30. The representative (a) output and (b) transfer of IGZO TFTs gated with OTS-                                                           |

|       | treated, 10 V anodised Ta <sub>2</sub> O <sub>5</sub>                                                                                       |

| Fig.  | 4.31. A representative (a) output and (b) transfer characteristics of a-IGZO TFTs gated                                                     |

|       | with OTS-treated, 15 V anodised Ta <sub>2</sub> O <sub>5</sub> 167                                                                          |

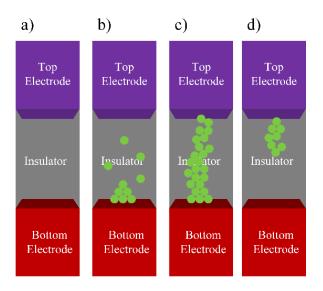

| Fig.  | 5.1. The schematic of a typical memristive device with a Metal-Insulator-Metal (MIM)                                                        |

|       | structure                                                                                                                                   |

| Fig.  | 5.2. The schematic of resistive switching based on the filamentary conduction model.                                                        |

| 8     | (a) a native insulator (HRS), (b) creation of CFs via electroforming, (c) CFs in ON state                                                   |

|       | (LRS), and (d) CFs rupture in OFF state (LRS to HRS) [272]170                                                                               |

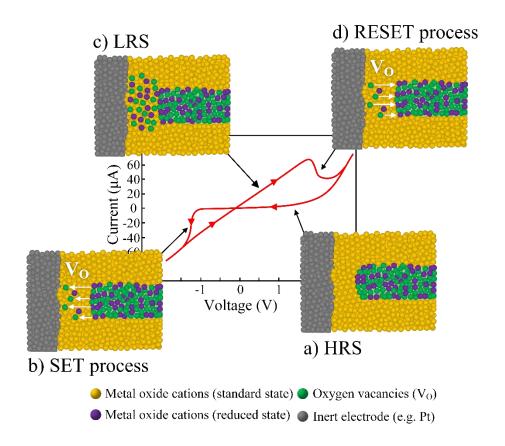

| Ei.~  | 5.3. The schematic of the SET and RESET processes of the VCM switching mechanism                                                            |

| 1 1g. | 5.5. The schematic of the SET and RESET processes of the VCM switching mechanism [274]                                                      |

|       | 17.741                                                                                                                                      |

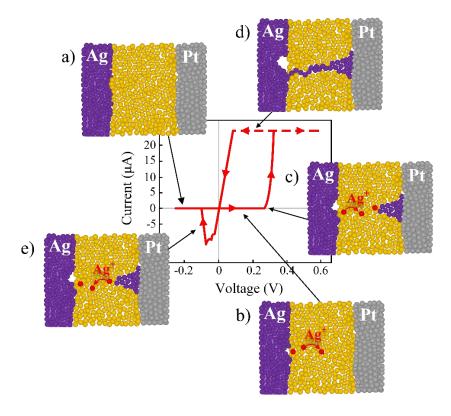

| Fig. 5.4. The schematic of the SET and RESET processes of the ECM switching mechanis      |

|-------------------------------------------------------------------------------------------|

| [275]1                                                                                    |

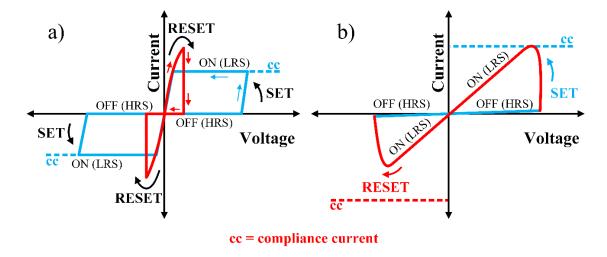

| Fig. 5.5. The schematics of I-V curve switching characteristics of memristive devices; (  |

| unipolar mode and (b) bipolar mode1                                                       |

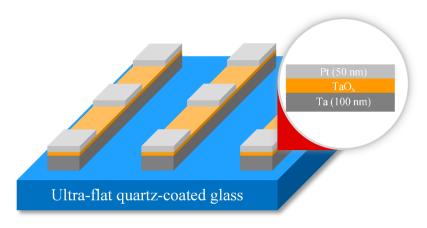

| Fig. 5.6. The schematic structure of a single memristor and 3D schematic of the fabricate |

| memristor arrays17                                                                        |

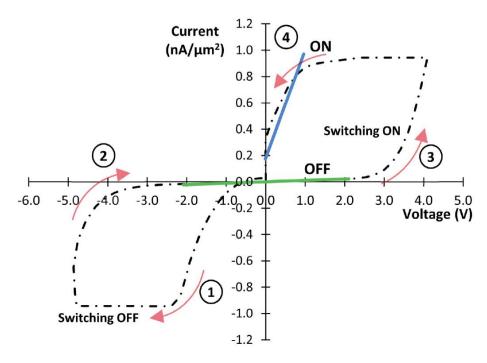

| Fig. 5.7. The representative I-V characteristic, showing the memristive behaviour of the  |

| fabricated Ta/TaO <sub>x</sub> /Pt devices [283]17                                        |

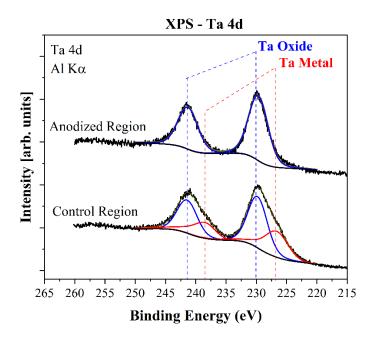

| Fig. A.1.1. Normalised peak fitted Ta 4d spectra for both control and anodised regions    |

| the sample showing only Ta oxide in the anodised region relative to a metal/oxide         |

| mixture in the control region.                                                            |

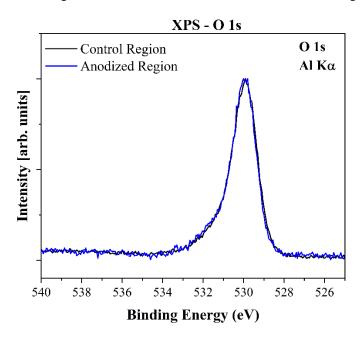

| Fig. A.1.2. Normalised O 1s spectra for both control and anodised regions20               |

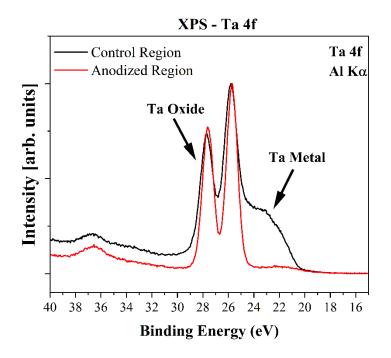

| Fig. A.1.3. Normalised Ta 4f spectra for both control and anodised regions20              |

## **List of Tables**

| Table 1.1. Key characteristics of different types of semiconductors [27][26]32                       |

|------------------------------------------------------------------------------------------------------|

| Table 2.1. Comparison between the most relevant semiconductor material technologies for              |

| TFTs46                                                                                               |

| Table 2.2. The most important electrical, physical and structural properties of some high-κ          |

| inorganic materials [146]79                                                                          |

| Table 2.3. A summary of anodisation ratios and forming electrolytes relating to the                  |

| anodisation of Al <sub>2</sub> O <sub>3</sub> and Ta <sub>2</sub> O <sub>5</sub> . CA – citric acid  |

| Table 2.4. Low-voltage transistors using Ta <sub>2</sub> O <sub>5</sub> as the gate dielectric110    |

| Table 2.5. Parameters of the previously demonstrated low-voltage OFETs using                         |

| organic/inorganic bilayer dielectrics111                                                             |

| Table 3.1. Key physical and chemical properties of tantalum (Ta)                                     |

| Table 3.2. The key physical and chemical properties of aluminium (Al)113                             |

| Table 3.3. The key physical and chemical properties of gold (Au)                                     |

| Table 3.4. The key physical and chemical properties of platinum (Pt)115                              |

| Table 4.1. The parameters of DPPDTT/PMMA OTFTs gated by 20 V anodised Ta <sub>2</sub> O <sub>5</sub> |

| dielectrics143                                                                                       |

| Table 4.2. Performance comparison of the proposed DPPDTT-PMMA OTFTs with their                       |

| counterparts in the literature                                                                       |

| Table 4.3. The electrical properties of the fabricated a-IGZO TFTs using 2 and 3 V                   |

| anodised OTS-treated Ta <sub>2</sub> O <sub>5</sub> dielectrics                                      |

| Table 4.4. The electrical properties of the fabricated a-IGZO TFTs using different, as               |

| prepared, anodically oxidised Ta <sub>2</sub> O <sub>5</sub> dielectrics160                          |

| Table 4.5. Electrical properties of the fabricated a-IGZO TFTs using OTS-modified,                   |

| anodically oxidised Ta <sub>2</sub> O <sub>5</sub> dielectrics.                                      |

| Table 5.1. Performance comparison of the fabricated Ta/TaO <sub>2</sub> | x/Pt memristors with their |

|-------------------------------------------------------------------------|----------------------------|

| counterparts in the literature.                                         | 176                        |

### **Abbreviations**

AFM Atomic force microscopy

Al<sub>2</sub>O<sub>3</sub> Aluminium oxide

ALD Atomic layer deposition

AMLCD Active-matrix liquid crystal display

AMOLED Active-matrix organic light-emitting diode

AOS Amorphous oxide semiconductor

a-Si:H Amorphous hydrogenated silicon

BBL Benzo-bisimidazobenzo-phenanthroline

BCC Body centre cubic

BJT Bipolar junction transistor

BST Barium strontium titanate

CB Conduction band

CBE Conduction-band edge

CBM Conduction band minimum

CF Conductive filament

CMOS Complementary metal-oxide-semiconductor

CP Conducting polymer

CuPc Copper phthalocyanine

CVD Chemical vapour deposition

DF Dissipation factor

DOS Density of states

DPPDTT Poly(3,6-di(2-thien-5-yl)-2,5-di (2-octyldodecyl)-

pyrrolo [3,4-c] pyrrole-1,4-dione) thieno [3,2-b]

thiophene)

DRAM Dynamic random-access memory

DRS Dielectric relaxation spectroscopy

ECM Electrochemical metallisation memory

EDL Electric double layer

EMA Effective medium approximation

eME Extended mobility edge

ESR Equivalent series resistance

F8T2 Poly(9,9-dioctylfluorene-alt-bithiophene)

FCC Face centred cubic

FET Field-effect transistor

FPD Flat panel display

GB Grain boundary

GPC Grows per cycle

HfO<sub>2</sub> Hafnium oxide

HMDS Hexamethyldisilane

HOMO Highest occupied molecular orbital

HRS High-resistance state

IGZO Indium-gallium-zinc oxide

In<sub>2</sub>O<sub>3</sub> Indium oxide

IPA Isopropyl alcohol

LCD Liquid crystal display

LRS Low-resistance state

LTPS Low-temperature polycrystalline silicon

LUMO Lowest unoccupied molecular orbital

MDMO-PPV Poly(2-methoxy-5-(3',7'-dimethyloctyloxy)-p-

phenylene vinylene)

MF Magnetic field

MIM Metal-insulator-metal

MOS Metal-oxide-semiconductor

MTR Multiple-trapping and release

NNH Nearest-neighbour hopping

ODTS *n*-octadecyltrichlorosilane

OLED Organic light emitting diodes

OPV Organic photovoltaics

OSC Organic semiconductor

OTFT Organic thin-film transistor

OTS Octyltrichlorosilane

P(VDF-TrFE) Vinylidene fluoride-trifluoroethylene

P3AT Poly(3-alkyl-thiophene)

P3HT Poly(3-hexylthiophene)

PCBM 6,6-phenyl-C61-butyric acid methyl ester

PEALD Plasma enhanced atomic layer deposition

PEN Polyethylene naphthalate

PET Polyethylene terephthalate

PMMA Polymethyl methacrylate

PVD Physical vapour deposition

RFID Radio-frequency identification

SAM Self-assembled monolayer

SiO<sub>2</sub> Silicon oxide

SnO<sub>2</sub> Tin oxide

Ta<sub>2</sub>O<sub>5</sub> Tantalum oxide

TFT Thin-film transistor

THF Tetrahydrofuran

TLC Trap-limited conduction

TT Thieno[3,2-b] thiophene

VB Valence band

VBM Valence band maximum

VCM Valence change memory

V<sub>O</sub> Oxygen vacancy

VRH Variable range hopping

XPS X-ray photoelectron spectroscopy

ZrO<sub>2</sub> Zirconium oxide

ZnO Zinc oxide

#### **Abstract**

Solution-processed thin-film transistors (TFTs) have a high potential to be the key components of future portable, battery-powered devices and circuits. TFTs can be realised in different form factors from standalone, discrete, low-cost sensors to flexible, large-area electronics. However, most of the recently demonstrated solution-processed TFTs typically operate at or above 5 V, which is still too high for many applications where operating voltage and power consumption are the main concerns. One approach to decrease the operating voltage of TFTs is to lower their threshold voltage (Vth) and subthreshold swing (SS) which can be fulfilled by increasing gate dielectric capacitance and improving the dielectric/semiconductor interface. The high capacitance dielectric can be achieved by utilising high dielectric constant (high-κ) materials, thinning the gate dielectric layer, or doing both simultaneously. Tantalum pentoxide ( $Ta_2O_5$ ) is a highly promising, high- $\kappa$  metal oxide dielectric ( $\kappa \sim 26$ ) which is used in capacitors, transistors and memory devices. Recently, it has been shown that employing thick Ta<sub>2</sub>O<sub>5</sub> films (d > 100 nm) as a gate dielectric does not only improve the characteristics of TFTs but significantly lowers their operating voltage. However, due to its relatively medium bandgap (4.4 eV), Ta<sub>2</sub>O<sub>5</sub>-based TFTs suffer from high leakage currents, particularly when Ta<sub>2</sub>O<sub>5</sub> thickness is reduced below 20 nanometres.

Typically, Ta<sub>2</sub>O<sub>5</sub> is deposited by atomic layer deposition (ALD) or RF/DC magnetron sputtering. These methods are time-consuming and increase the cost of device fabrication due to the need for high-vacuum conditions. In comparison, anodic oxidation (so-called anodisation) is a material deposition technique which is a simple, cost-efficient and straightforward method to grow high-quality metal oxide layers on the surface of metallic substrates in ambient conditions. In this thesis, ultra-thin (d ~ 7 nm), anodic Ta<sub>2</sub>O<sub>5</sub> modified with *n*-octadecyltrichlorosilane (OTS) self-assembled monolayer (SAM) has been used to realise ultra-low voltage operation of p-channel DPP-based organic TFTs (OTFTs) and n-channel a-IGZO-based metal oxide TFTs (MOTFTs). Moreover, it is shown that OTS SAM reduces the gate leakage current and improves the TFT dielectric/semiconductor interface.

First, the morphology and dielectric properties of the anodised Ta<sub>2</sub>O<sub>5</sub> films with and without OTS SAM treatment have been analysed. Several anodisation voltages were utilised to optimise the thickness of Ta<sub>2</sub>O<sub>5</sub> for each type of TFTs to guarantee their optimal operation. The results show that the poly(3,6-di(2-thien-5-yl)-2,5-di (2-octyldodecyl)-pyrrolo[3,4-c] pyrrole-1,4-dione) thieno [3,2-b] thiophene)-polymethyl methacrylate (DPPDTT-PMMA) TFTs gated with OTS-modified tantalum pentoxide anodised at 3 V (d ~ 7 nm) exhibit the best performance. The optimised devices operate at 1 V with saturation field-effect mobility larger than 0.2 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, threshold voltage -0.55 V, subthreshold swing 120 mV/dec, and current on/off ratio in excess of  $5 \times 10^3$ . As a result, the demonstrated DPPDTT-PMMA TFTs display a promising performance for applications in ultra-low voltage, organic electronics. On the other hand, it is shown that the best performing capacitors and a-IGZO TFTs are realised with 10 V anodised (22 ± 2 nm), OTS-treated Ta<sub>2</sub>O<sub>5</sub> dielectric. The fabricated Ta<sub>2</sub>O<sub>5</sub>/OTS capacitors show good stability in the 100 Hz to 100 kHz and capacitance density in excess of 400 nF/cm<sup>2</sup>. The fabricated TFTs display relatively high field-effect mobilities (2.3 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>), threshold voltages around 0.4 V, subthreshold swings below 90 mV/dec, and high current on/off ratios well in excess of 10<sup>5</sup>. It is envisaged that this approach is a promising alternative to fabricate ultra-low voltage, inexpensive TFTs and TFT-arrays for low-cost sensors and low-end, disposable electronics.

# **Declaration**

No portion of the work referred to in the thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

## **Copyright Statement**

- I. The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- II. Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made only in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- III. The ownership of certain Copyright, patents, designs, trademarks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

- IV. Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see <a href="http://documents.manchester.ac.uk/DocuInfo.aspx?DocID=24420">http://documents.manchester.ac.uk/DocuInfo.aspx?DocID=24420</a>), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see <a href="http://www.library.manchester.ac.uk/about/regulations/">http://www.library.manchester.ac.uk/about/regulations/</a>) and in The University's policy on Presentation of Theses.

## Acknowledgements

I would like to praise and thank God, the almighty, who has granted countless blessing, knowledge, and opportunity to me so that I have been finally able to accomplish this thesis.

First and foremost, I am extremely grateful to my supervisor, Dr Leszek Majewski, for his invaluable advice, continuous support, and patience during my PhD study. His immense knowledge and plentiful experience have encouraged me all the time of my academic research and daily life. Without his guidance and constant feedback, this PhD would not have been achievable.

I would also like to thank my invaluable friend, Dr Sheida Faraji, for her technical support on my study. Additionally, I would like to offer my special thanks to Mr Malachy McGowan for his great help, support, and advice regarding the cleanroom facilities. I would like to extend my sincere thanks to Dr Alex Walton and Mr Christopher Muryn from the Department of Chemistry at the University of Manchester for their help in obtaining data using XPS and AFM, respectively. I am deeply grateful to my friends and colleagues for their kind support and help with whom I have shared unforgettably pleasant moments during my academic life.

Finally and most importantly, I would like to express my gratitude and dedicate this thesis to my family especially my beloved parents and my beloved wife (Behnaz Moradi Bakhtiari) for her endless and unconditional love and support. Without her tremendous understanding and encouragement in the past few years, it would be impossible for me to complete my study.

## **Chapter 1: Introduction**

### 1.1 A brief history of transistors

Nowadays, field-effect transistors (FETs) play a crucial role in the modern electronics industry. They are typically operated as a signal amplifier [1] or an electronic switch [2] in analog and digital circuits, respectively. The development of silicon-based transistors, particularly metal-oxide-semiconductor (MOS) FETs for complementary metal-oxide-semiconductor integrated circuits (CMOS ICs) (i.e., microprocessors), has taken the electronics industry to an entirely new level and significantly changed each and every aspect of our day-to-day lives, which cannot be imagined without their valuable role anymore.

With respect to other types of transistors, e.g., bipolar junction transistors (BJTs), MOSFETs have several advantages, such as small dimensions, high performance along with low power consumption and dissipation, and high input impedance. This makes them the ideal devices for employing in CMOS ICs. Therefore, most of the electronic circuits are now manufactured using this class of transistors [3]. Nonetheless, the high performance of MOSFETs usually comes with the high cost and high-temperature processing [4], which is incompatible with the growing demand for low-cost, low-temperature, large-area processing of emerging flexible and stretchable electronics [5]. Responding to these demands requires firstly intensive research and development on realising compatible materials and active devices discussed in this thesis to achieve the end goal of fabricating large-area flexible and stretchable circuits.

Thin-film transistors (TFTs), which are well known for their important role in modern flat panel displays (FPDs), belong to the family of FET devices [6]. TFTs are made by stacking thin films that consist of three fundamental materials, namely, a semiconductor, a dielectric, and a conductor. Even though TFTs and MOSFETs have been developed simultaneously, MOSFETs have dominated the majority of microelectronics research interests and industrial production due to their much better performance. However, the

demand for low-cost, large-area flat panel displays (FPDs) fuelled research on finding a viable substitution for crystalline and polycrystalline silicon that typically require high-temperature processing.

In 1979, significantly cheaper amorphous hydrogenated silicon (a-Si:H) was developed with few constraints on substrate size, material, and topology and was subsequently introduced to thin-film transistors (TFTs) as the active layer, which resulted in an increased interest in TFTs [7]. Since then, the use of a-Si:H TFTs has gradually grown, and eventually, this type of TFTs has started to dominate the whole liquid crystal display (LCD) industry. Nowadays, a-Si:H TFTs along with indium-gallium-zinc oxide (IGZO) and poly-Si TFTs are the backbone of both active-matrix liquid crystal displays (AMLCDs) and active-matrix organic light-emitting diode (AMOLED) display technologies.

Despite the crucial role of amorphous hydrogenated silicon (a-Si:H) TFTs in display technologies, a-Si:H TFTs suffer from low mobility (typically  $\leq 1 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ), as well as instability under electrical bias stress and illumination [8]. Although Si is the most common material used in electronics due to its advantages such as abundance, low-cost manufacturing, ease of doping, and high charge carrier mobility, the focus of TFT research has been being shifted to new families of semiconductor materials that can offer more beneficial properties, for example, transparency [9], flexibility [10] and recyclability [11] along with high carrier transport, low-cost solution-based processability, and mechanical stress tolerance, for novel applications.

In addition, there are many applications for which high-performance (i.e., high switching speed, high output current) electronic switches are not needed, such as discrete sensors [12], simple displays [13], as well as basic radio-frequency identification (RFID) tags and smart cards [14]. These applications are typically realised in various shapes and sizes, and thus alternative electronic materials and device manufacturing techniques that are compatible with these applications are being developed. From a marketing point of view, the global

market size for flexible hybrid circuits is forecasted to go beyond \$3 billion in 2030 [15]. Also, it is expected that almost 5 billion flexible hybrid electronic circuits will be produced by 2030. From the most recent trends in material research, it appears that organic and metal oxide semiconductors are the two most promising alternatives to silicon for low-cost, large-area electronic applications.

In 1986, Tsumura *et al.* reported a special type of TFTs that used an organic semiconductor (OSC) as the active layer, so-called organic thin-film transistors (OTFTs). The demonstrated devices used electrochemically polymerised polythiophene, which belongs to the family of conducting (i.e., conjugated) polymers (CPs), as the active layer and were operated at 50 V [16]. Accordingly, it has been shown that the thin-film transistor design is the structure of choice for low conductivity materials such as OSCs. As a result, the TFT design was utilised to realise a wide range of field-effect transistors (FETs) using organic semiconductors [17]. Since then, the performance of organic semiconductors has continuously improved, and nowadays, OTFTs can compete with or even surpass a-Si:H

Moreover, TFTs which employs a metal oxide semiconductor (monocrystalline ZnO) as the active layer were introduced in the mid-1960s. Subsequently, FETs and TFTs using other binary oxide semiconductors (i.e.,  $In_2O_3$  and  $SnO_2$ ) were reported [19][20]. However, oxide TFTs disappeared from the literature for a long time until the 1990s when it turned out that polycrystalline ZnO (poly-ZnO) could be fabricated on large-area substrates at temperatures  $\leq 300$  °C. In the 2000s, ZnO TFTs started to attract increased attention once more with the expectation that they could substitute a-Si:H TFTs in FPDs. However, the initial poly-ZnO TFTs had several issues to be addressed, namely, relatively low mobility ( $\leq 3$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>), electrical performance instability and normally-on characteristics. Additionally, they suffer from nonuniformity properties and challenging fabrication processes similar to poly-Si TFTs due to the presence of grain boundaries (GBs) [21], as well as high background electron

concentration and low chemical durability against acidic etchants and reducing atmospheres compared to a-Si:H TFTs [22].

Crystalline indium-gallium-zinc oxide (IGZO) TFTs were first reported in 2003 [23]. Subsequently, amorphous IGZO (a-IGZO) TFTs were demonstrated in 2004. Since then, a-IGZO TFTs have shown promising characteristics in terms of switching speed (greater than a-Si:H), resolution, large-area processability and inexpensive manufacturing, which are on a par with a-Si:H TFTs [24]. As such, oxide semiconductors, specifically in their amorphous state, have started to make a remarkable growth in the display industry. At present, they are even challenging silicon in many other conventional applications and are researched for a large number of novel and disruptive applications (e.g., flexible electronics) which can benefit from their unique features such as high optical transparency, high carrier mobility, and even solution processability. However, the key issue for utilising the oxide semiconductors on plastic substrates such as polyimide (PI), polyethylene naphthalate (PEN), and polyethylene terephthalate (PET) required for flexible applications is their processing temperature which should be kept well below 200° C.

Low-voltage TFTs can operate with much lower gate-source voltages ( $V_{GS}$ ) ( $\leq 5$  V) and, consequently, have potentially lower power consumption. The demand for low-voltage TFTs is continuously growing as they have been increasingly being used in energy-efficient and (lithium-ion) battery-powered devices. One main parameter of TFTs, which affects their operation voltage, is the thickness of the gate dielectric. It turns out that reducing the thickness of the gate dielectric can decrease the operating voltage, and thus, this method is traditionally used as a method of reducing the operating voltage. SiO<sub>2</sub>, as a superior conventional gate dielectric, is continuously being thinned to realise TFTs with lower operating voltages. However, thinning SiO<sub>2</sub> to the range of 4–5 nm increases the leakage current density ( $J_{leak}$ ) exponentially due to direct tunnelling that considerably deteriorates the performance and reliability of the device ( $J_{leak} > 1$  A cm<sup>-2</sup> at 1 V gate bias, Fig. 1.1) [25].

Besides, high-temperature processing (900  $\sim$  1200 °C) of defect-free SiO<sub>2</sub> is incompatible with emerging novel applications such as stretchable, flexible and large-area electronics typically fabricated on plastic substrates which cannot tolerate higher temperatures than  $\sim$  200 °C [25].

Fig. 1.1. (a) The semiconductor industry roadmap for gate dielectric thickness scaling [26] and (b) leakage current density ( $J_{leak}$ ) versus voltage for various SiO<sub>2</sub> dielectric thicknesses [27].

To date, apart from thinning the gate dielectric, there are other methods to reduce the operating voltage of TFTs, such as using high dielectric constant ( $\kappa > \sim 10$ ) materials. Replacing the SiO<sub>2</sub> with the high- $\kappa$  materials (e.g., HfO<sub>2</sub>) as the gate dielectric was introduced to overcome the SiO<sub>2</sub> limitations, enable further miniaturisation of the device dimensions and reduce the operating voltage.

Moreover, it appears that although portable batteries have been remarkably improved over decades in terms of technology, capacity, and lifetime, their improvement has not been as fast as the development of semiconductor technologies [28]. This unbalanced improvement is also reflected in phones' battery where in some cases, they could be lasting for several days without requiring to be charged in the last decade, but most of them can barely last a full day now. This issue can be justified by two main reasons. On the one hand, increasing the energy density reached a stage where it cannot be further achievable with the current materials. On the other hand, changing battery materials requires intensive research and

development, which is much slower than what has been achieved over time. Therefore, the rapid development of low threshold voltage ( $V_{th}$ ) TFTs, which guarantees lower power consumption, is highly desirable [29]. However, before such low-power devices can be realised, a significant reduction in the operating voltage of the transistors is required. Unfortunately, it is still extremely challenging for both organic and metal oxide TFTs to achieve high performance and operating voltages  $\leq 1$  V at the same time [30][31][32].

As a result, different research groups conducted extensive research to develop low threshold voltage ( $V_{th}$ ) TFTs using high- $\kappa$  materials and gradually reduced the operating voltage that was around 20 V in early devices to 10–5 V or even 3 V in the current devices. However, it is thought that TFTs operating at 1 V or below are now needed to realise ultra-low-voltage transistors and circuits. Despite the quick improvement in power consumption and reducing the operating voltage of inorganic TFTs [33], it was only in 1999 when Dimitrakopoulos *et al.* firstly reported organic TFTs. Those OTFTs employed an 82 nm thick sol-gel barium strontium titanate (BST) layer with a dielectric constant ( $\kappa$ ) of 15 as the gate dielectric and p-type pentacene as the active layer. Using BST in those OTFTs reduced the operating voltage, which exceeded 50 V at the time to 5 V [34].

Since then, extensive research has been conducted to find and employ a variety of high-κ materials in OTFTs in both academia and industry. In particular, Ta<sub>2</sub>O<sub>5</sub>, due to its high dielectric constant ( ~ 26), was in the spotlight to be used in OTFTs. In 2002, Bartic *et al.* reported tantalum oxide (Ta<sub>2</sub>O<sub>5</sub>) deposited by e-beam as a gate dielectric material for low-voltage poly(3-hexylthiophene) (P3HT) OTFTs [35]. Those TFTs employed a 100 nm thick Ta<sub>2</sub>O<sub>5</sub> film and could operate around –3 V. In 2004, Sakai *et al.* reported low-voltage OTFTs using p-type pentacene as the semiconductor layer and a 130 nm thick Ta<sub>2</sub>O<sub>5</sub> film deposited by radio-frequency (RF) magnetron sputtering as a gate dielectric. Similar to the previously reported OTFTs, those transistors also operated at about –3 V [36]. In 2005, Ueno *et al.* employed a thick Ta<sub>2</sub>O<sub>5</sub> dielectric layer (d = 200 nm) in the p-type pentacene and n-type C<sub>60</sub>

OTFTs [37]. Although p-type OTFTs in comparison with n-type had relatively better field-effect mobility, the fabricated OTFTs operated at 10 V which made them unsuitable for low-voltage applications. In 2008, Zhou *et al.* proposed low-voltage n-type OTFTs based on a 200 nm  $Ta_2O_5$  grown by anodisation [38]. As can be seen from the literature, the use of  $Ta_2O_5$  has been limited to relatively thick  $Ta_2O_5$  films ( $\geq 100$  nm) which effectively resulted in 3 V OTFTs. However, this operating voltage is still too high for certain applications where the low power consumption of devices is paramount.

#### 1.2 Motivation, challenges and research aim

Nowadays, TFTs are situated in most electronic devices and typically consume a majority of the power budget of their circuits. Thus, designing TFTs which can operate at low voltages as possible and simultaneously have the highest performance is highly desirable [30][31][32]. This consideration becomes more significant when it comes to portable, battery-powered devices where power consumption is one of the main concerns.

Even though the necessity of the low operating voltage is dependent on different criteria and can differ from application to application, the operating voltage should be as low as 1 V. For instance, some medical purposes require to sense and detect biological species in an aqueous media since it is necessary to avoid electrolytic hydrolysis of water caused by high ionic conduction in an analyte at higher voltages and stabilise operation in aqueous solutions. Although the operating voltage of TFTs has generally been reduced over the past decades, it has reached the range of 3–5 V where the further reduction is challenging and not trivial due to intrinsic properties of the conventional gate dielectrics (e.g., SiO<sub>2</sub>).

Moreover, low-voltage TFTs are preferred to a typical TFT operating at lower voltages or, in particular, at sub-threshold voltages due to several reasons. Firstly, operating a TFT in a sub-threshold voltage is not trivial and needs several aspects to be considered. For example, most transistor modelling has focused on the saturation region (i.e., "on" state), not the sub-threshold region. Secondly, operating a TFT at sub-threshold increases significantly its

sensitivity as small changes in gate voltage causes exponentially changes in the drain current. In terms of contact resistance, it also suffers from high contact resistance comparing to that of in the above-threshold region. Additionally, the ratio of "on" to "off" drain current is orders of magnitude smaller in the subthreshold regime. Therefore, to achieve the goal of this project, TFTs which natively have the ability to operate at low voltages are preferred.

For totally different applications where downscaling of the channel in order to situate more transistors in ICs is not the case, increasing the  $\kappa/d$  ratio is leading to reduction of the operating voltage by increasing the gate dielectric capacitance. This can happen by substituting SiO<sub>2</sub> with a high- $\kappa$  material (e.g., Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, ZrO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>, etc.) and thinning the dielectric thickness which can increase the induced charges with lower leakage current and allows to decrease threshold voltage (V<sub>th</sub>) and subthreshold swing (SS), two key features of TFTs without compromising the value of the drain current (I<sub>D</sub>).

However, controlling and mitigating the gate leakage current in nanoscale dielectrics is challenging and increases the necessity of having dielectric materials with larger bandgap; therefore, selecting an appropriate material with the highest bandgap and dielectric constant is essential. Unfortunately, a trade-off should be considered as materials with a higher dielectric constant have a lower bandgap [25].

Among all of high- $\kappa$  materials, Ta<sub>2</sub>O<sub>5</sub> shows promising characteristics leading to be employed in a variety of electronic devices such as metal-oxide-metal (MOM) capacitors and diodes, TFTs, and memory devices. However, due to relatively medium bandgap (4.4 eV) in comparison with other gate dielectrics, the minimum thickness of Ta<sub>2</sub>O<sub>5</sub> films used in TFTs are typically thick and above 100 nm. These thick dielectrics guarantee the optimum performance in the application of TFTs but impede the devices to operate at low voltages ( $\leq$  3 V). Despite the numerous advantages of Ta<sub>2</sub>O<sub>5</sub> dielectric for different types of devices such as high dielectric constant ( $\kappa \approx 26$ ), high transparency, high melting point (1785 °C),

and showing good thermal and chemical stability, it has been reported that to realise ultra-low-voltage TFTs ( $\leq$  1 V), the thickness of Ta<sub>2</sub>O<sub>5</sub> dielectric requires to decrease sufficiently to below 50 nm [5]. This thickness reduction can be really challenging as it requires several optimisation steps, careful considerations, and possible trade-offs. The development of ultrathin high- $\kappa$  dielectric ( $\leq$  ~ 20 nm) leading to the decrease of the threshold voltage (V<sub>th</sub>) and subthreshold swing (SS) which allow operating voltage to be lowered with the same drain current (I<sub>D</sub>) in organic and inorganic TFTs.

Moreover, although bandgap and dielectric constant are two critical parameters for selecting a dielectric, they are not only parameters as other criteria such as moisture absorption, crystal structure and surface roughness have to be considered, as well. Besides, although the gate dielectric can be deposited by a variety of well-established methods, low-temperature processing techniques should be considered first as they help to reduce manufacturing costs and are compatible with large-area plastic electronics. An effective strategy to realise room temperature processing of high-κ metal oxide materials enabling low-voltage TFTs is to use the solution processing techniques like anodic oxidation (anodisation). Anodisation can provide room temperature oxidation and deliver a smooth film with a precise thickness that can be used in various applications such as memory devices, transistors, and diodes. Therefore, anodisation as a high-quality, inexpensive deposition technique can benefit manufacturing procedures with minimum changes and decrease the production cost of ICs. Semiconductors play an essential role in active devices, and therefore, extensive research to find new semiconductor materials is in progress which can open new horizons for next solidstate electronics. Table 1.1 compares the key characteristics of two well-established semiconductors, namely, a-Si:H and poly-Si with organic and metal oxide semiconductors. Overall, metal oxide and organic semiconductors show superior functionalities, especially

for novel applications such as transparent, flexible, large-area electronics due to room

temperature and solution-based processability, and large-area uniformity. In this study, two promising semiconductor materials, organic and metal oxide were used to realise one-volt TFTs.

| Channel material                               | a-Si:H    | Poly-Si (e.g.,  | Organic         | Metal oxide      |

|------------------------------------------------|-----------|-----------------|-----------------|------------------|

|                                                |           | LTPS)           |                 | (e.g., IGZO)     |

| Manufacturing cost                             | Low       | High            | Low             | Low              |

| Microstructure                                 | Amorphous | Polycrystalline | Mainly          | Amorphous        |

|                                                |           |                 | Polycrystalline |                  |

| Stability                                      | Poor      | Good            | Poor            | Superior to a-Si |

| Uniformity                                     | Good      | Poor            | Good            | Good             |

| Yield                                          | High      | Low             | High            | High             |

| Max. mobility (cm <sup>2</sup> V <sup>-1</sup> | ≈1        | ≈100            | ≈10             | ≈100             |

| s <sup>-1</sup> )                              |           |                 |                 |                  |

| Device type                                    | n-type    | n- and p-type   | Mainly p-type   | Mainly n-type    |

| Process temperature                            | 150-350   | 250-550         | RT-250          | RT-400           |

| (°C)                                           |           |                 |                 |                  |

| Large-area scalability                         | High      | *Low            | High            | High             |

| Solution manufacturing                         | No        | No              | Yes             | Yes              |

<sup>\*</sup> In practice, the large-area scalability of poly-Si is not low, and it is possible to make large-area poly-Si displays, but due to poly-Si fabrication costs, it is not financially viable.

Table 1.1. Key characteristics of different types of semiconductors [27][26].

Herein, the primary aim to conduct this research was to find and develop promising high- $\kappa$  dielectrics which can not only deliver TFTs with the operating voltages at or below 1 V and reasonable leakage current density ( $J_{leak} \leq 1 \text{ nA/cm}^2$ ) but also is compatible with both organic and inorganic semiconductors on both rigid and flexible substrates. This aim was fulfilled by the development of ultrathin  $Ta_2O_5$  dielectric for p-type organic and n-type oxide TFTs which operate at or below 1 V. The ultrathin tantalum pentoxide films have been investigated from scratch in order to be used as a gate dielectric in TFTs, which has shown promising gate dielectric characteristics especially when it is passivated with a self-assembled monolayer (SAM) like OTS forming a hybrid high- $\kappa$ /low- $\kappa$  dielectric.

This thesis reports research results concerning pristine and OTS-treated high- $\kappa$  Ta<sub>2</sub>O<sub>5</sub> as the gate dielectric for n-type a-IGZO-based TFTs and p-type organic diketopyrrolopyrrole (DPP)-Based OTFTs. The key aspects of the study focus on the understanding of theoretical concepts, fabrication, characterisation and potential applications of the fabricated devices.

Theoretical concepts of this research are based on previous works conducted in the literature. Fabrication is based on our group findings and experiences, which aim to be as reproducible and straightforward as possible along with maximum optimisation. Characterisation is one of the most vital parts of the research. Therefore, in this research, scientific matters have been considered to achieve precise, reliable results. The developed dielectric was then used in other devices such as memory devices and possibly can be employed in MIM diodes to realise the quite full range of active devices. Moreover, due to the nature of realised TFTs (n-type and p-type), they can pave the way towards low-voltage CMOS-based circuits, which are highly desirable for future and emerging applications.

#### 1.3 Organisation of Manuscript

Chapter 2 of this thesis is a literature review that consists of the theory and operation mechanism of TFTs, theory of dielectric and its different types and high- $\kappa$  dielectric, which can be utilised in low-voltage, high-performance thin-film transistors by the room temperature solution-processed technique. The review provided herein is expected to be a useful resource for assessing the development of high- $\kappa$  metal oxide dielectric theory and referencing the tantalum oxide film as a promising gate dielectric. Although the whole literature view may be looks saturated by information at first glance, it is suggested that the reader peruse sections of interest.

The purpose of Chapter 3 is to describe the methodology and experimental work. It is mainly focused on anodisation, preparation and processing procedures of high-κ metal oxides and growth of Ta<sub>2</sub>O<sub>5</sub>, SAMs surface modification and fabrication of a-IGZO TFTs and OTFTs, which can operate as low as 1 V and utilising a low-cost low-temperature technique providing a high-quality pores-free gate dielectric with excellent characteristics.

Chapter 4 comprises complete results and discussions and categorised into two subsections of characterisation of Ta<sub>2</sub>O<sub>5</sub>/OTS dielectric layers and evaluation of fabricated

TFTs and OTFTs using the corresponding dielectrics. In each section, the proposed dielectric layers used in the fabrication of transistors are separately presented and analysed.

Chapter 5 demonstrates the application of anodised tantalum oxide films for realising low-cost solution-processed memristive devices. The results show a high potential of these devices in resistive random-access memory (ReRAM) applications and neuromorphic computing.

Chapter 6 summarises the conclusions for this thesis and provides potential future work and detailed recommendation on the proposed anodised tantalum oxide films.

## **Chapter 2:** Literature review

#### 2.1 Overview of Thin-Film Transistors (TFTs)

The concept of thin-film transistors (TFTs) was first reported by Weimer in 1962 [33]. TFTs are a class of the now large family of field-effect transistors (FETs). A typical TFT is comprised of three terminals (gate, source, and drain) and made by stacking thin films of various electronic materials such as a semiconductor, a dielectric, and a conductor. Depending on their fabrication process and purpose, some TFTs possess additional passive layers (e.g., substrate planarization layer, semiconductor passivation layer, and device encapsulation layers, etc.). The structure of TFTs has been shown to be compatible with low conductivity semiconductor materials and is now abundantly utilised in a-Si:H TFTs and a-Si:H TFT-based circuits [39]. As shown in Fig. 2.1 (a), in bottom-gate top-contact TFTs the semiconductor layer is situated between the drain and source electrodes and the dielectric layer is inserted between the semiconductor and a transversal electrode (gate). TFTs employ an electric field to modulate the current obtained by the accumulated charge carriers at the dielectric/semiconductor interface and control the current flow between the source and drain with the applied voltage bias to the gate electrode [40]. As such, a typical TFT operates similarly to the metal-oxide-semiconductor field-effect transistor (MOSFET). Even though TFTs and MOSFETs have been developed simultaneously, MOSFETs have dominated most microelectronics research interests and industrial production due to their much higher performance. However, the high MOSFET performance usually comes with the high manufacturing cost and high-temperature processing (greater than 1000 °C) [41] which is incompatible with the increasing demand for low-cost, low-temperature, large-area processing of flexible, stretchable and electronics. Other dissimilarities between TFTs and MOSFETs, as shown in Fig. 2.1, include structural and material differences [42]. For example, TFTs usually use an insulator as the substrate (e.g., glass or flexible films such as