# Self-powered and Self-configurable Active Rectifier Using Low Voltage Controller for Wide Output Range Energy Harvesters

Zheng Jun Chew, Member, IEEE, Yang Kuang, and Meiling Zhu

Abstract—This paper presents a self-configurable and selfpowered active rectifier that operates from 0.25-20 V for energy harvesting applications. The proposed circuit self-startups from a low voltage using a charge pump and amplifies the voltage with a voltage doubler (VD) topology to provide succeeding circuits such as boost converters with a higher voltage. When the voltage of the energy harvester reaches a high threshold, the circuit switches its topology to a full-wave rectifier (FR) that does not amplify the voltage. The start-up circuit can limit its voltage intake to prevent boosting the high voltage, which may damage the whole circuit. Comparators with a maximum operating voltage of 5.5 V used in the implementation of the rectifier are protected by a diode and resistor based circuit. A piezoelectric energy harvester (PEH) that has a wide open-circuit voltage of 0.4–15 V under the acceleration of 0.04-0.3 g was used to test the circuit. The experiment results showed the rectifier can startup from 0.25 V and switch its topology according to the PEH voltage. The voltage and power conversion efficiencies are over 90% in most cases.

Index Terms—energy harvesting, full-wave rectifier, self-configurable, self-powered, voltage doubler, wide range.

#### I. INTRODUCTION

**E**NERGY harvesting has been long sought as an alternative to batteries for powering wireless sensor nodes, especially for industrial monitoring applications because the need to replace the large numbers of batteries is costly [1]. Common energy harvesters are solar cells [2], thermoelectric generators [3], piezoelectric [4], and electromagnetic transducers [5]. The voltage amplitude output by the energy harvesters could be low, high, or span across a wide range due to factors such as ambient conditions [4], structural designs [6], dimensions [7], and transduction mechanisms [8]. For example, under normal operating conditions, an electromagnetic transducer outputs 1–60 V of open-circuit voltage  $V_{\rm OC}$  when it is harvesting energy from a current-carrying rail track [9]. A piezoelectric energy

This work was supported by EPSRC, through the project Zero Power, Large Area Rail Track Monitoring (EP/S024840/1) and Royal Society Industry Fellowship, through the project High Performance Energy Harvesting Sensor Systems for Critical Asset Monitoring (INF\R2\202021). All data are provided in full in the results section of this paper.

Z. J. Chew, Y. Kuang, and M. Zhu are with the College of Engineering, Mathematics and Physical Sciences, University of Exeter, Exeter EX4 4QF U.K. (e-mail: z.j.chew@exeter.ac.uk; y.kuang@exeter.ac.uk; m.zhu@exeter.ac.uk).

harvester (PEH) that output an  $V_{\rm OC}$  range of 0.5–11.6 V when excited at 0.05–0.25 g was also reported [10]. The output power of the aforementioned devices spans from hundreds of microwatts to over hundreds of milliwatts, which is enough to power wireless sensor nodes [11]. Thus, neither the low nor the high voltage range can be ignored. Since the first interface for transducers that usually have an ac output is generally a rectifier to convert the ac energy to dc, rectifiers require attention to manage wide output ranges efficiently.

Various types of rectifiers have been reported but very few can rectify wide output ranges efficiently. Standard rectifying circuits such as full-wave bridge rectifier (FBR) and voltage doubler (VD) are still widely implemented especially by using passive diodes. This is because passive diode-based rectifiers are simple and robust [12]. However, diodes have a forward voltage drop  $V_{\rm F}$  of around 0.2–0.6 V. If an energy harvester has a low voltage or high current, the losses in the rectifier are high with only a fraction of the power delivered to the end device even when an optimally designed transducer generates a significant amount of usable power. FBRs and VDs suffer from  $2V_{\rm F}$  and  $V_{\rm F}$  per rectifying cycle, respectively [13]. VDs have a lower loss than FBRs but they are not suitable for all the scenarios as VDs amplify the rectified voltage. When the energy harvester voltage becomes high, further increment of the high voltage by VDs could damage the circuits after the VDs, unless the circuits have high voltage ratings. This might not be feasible for some technologies due to the inherent voltage limitations and high costs [13], [14].

Instead of diodes, active rectifiers use MOSFETs to have improved performance in rectifying both high and low ac voltage because MOSFETs do not have  $V_F$  when they are turned on [15], [16]. Commonly used simple and low power design comprises two PMOS and two NMOS, which still have a voltage drop that needs to be overcome due to their inherent on/off threshold voltage [17]. The voltage drop of the NMOS can be reduced by driving their gate using comparators that take the voltage of an energy harvester directly as their input to produce the switching signals [17], [18]. The operating voltage of such design is limited by the supply and breakdown voltages of the comparator because the voltage to the input of the comparator cannot exceed these voltages, which is 5 V in many standard low power fabrication technologies [15], [18]. High voltage comparators are available but their power consumption rises with the supply voltage [19], which is undesirable in energy harvesting due to limited power.

As the only power source, the energy harvester also needs

to output sufficiently high power and voltage to start-up the circuits for proper operation. The start-up voltage of active rectifiers could be over 1.2 V, which is similar to or even higher than  $V_{\rm F}$  of passive rectifiers as they rely on the energy harvesters to directly produce the voltage required for their start-up [15], [18], [20]. To start-up from low voltage, voltage multipliers have been used to amplify the voltage for starting-up [8], [21]. Given that ambient conditions in the real world are highly dynamic, there will be occasions that energy harvesters output very high voltage. When the start-up circuit amplifies the already high voltage, the voltage from the start-up circuit could be so high that it damages the entire circuit.

Rectifiers that can reconfigure as FR or VD to operate over an extended voltage range than conventional fixed topology rectifiers have been proposed. They were implemented using either a passive rectifier [20] or an active rectifier [22]. However, they do not address the aforementioned issues, especially in operating above 5 V using low voltage and power driver for the active rectifier and starting-up from sub-1 V. This paper presents a self-powered and self-configurable active rectifier to address the narrow operating range issue of conventional active rectifiers for any energy harvesting applications. It uses different topologies of either FR or VD based on the voltage of the energy harvester to rectify the wide voltage range. Diode-resistor and transistor based solutions are applied on low voltage nanopower comparators and the startup circuit, respectively. This allows the comparators to operate with the high voltage from the energy harvester as their input signal and the start-up circuit to limit high voltage intake, which avoids amplification of the high voltage that will damage the circuit. A PEH that has a wide output range was used to test the circuit as a use example.

## II. SYSTEM DESCRIPTION

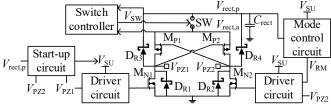

Fig. 1 shows the diagram of the proposed rectifying circuit. It consists of a passive diode-based FBR in parallel with an active rectifier that can switch its topology, a control circuit that configures the rectifier topology, two driver circuits to switch the NMOS, and a start-up circuit. The whole system operation and switching mechanism will be explained here.

# A. Whole System Operation

The two terminals of the PEH, each with the voltages  $V_{\rm PZ1}$  and  $V_{\rm PZ2}$ , respectively are connected to the circuit. The passive FBR and active rectifier are connected in parallel to output a rectified voltage  $V_{\rm rect}$ . The PEH voltage is rectified by the FBR formed by four Schottky diodes,  $D_{\rm R1-4}$  when the circuit is starting up for the first time without energy stored in its energy storage capacitors. The output of the FBR  $V_{\rm rect,p}$  is fed into the start-up circuit, which is a charge pump driven directly by the

Fig. 1. System architecture of the proposed rectifying circuit.

PEH. Once the output from the start-up circuit  $V_{\rm SU}$  reaches the minimum operating voltage to run the driver circuits, the active rectifier will be operating as a VD by default to give a higher rectified voltage to succeeding circuits at the output of the rectifier for an easier start-up in case of a low PEH voltage. The switching from one topology to another is based on the voltage requirement and limit of the succeeding circuits. The mode control circuit monitors  $V_{\rm rect}$  to decide on the topology to be used. The rectifier switches to the full-wave rectifier (FR) when  $V_{\rm rect}$  is sufficiently high as further voltage amplification in VD mode will be too high for the succeeding circuits and switches back to VD when  $V_{\rm rect}$  becomes too low.

## B. Rectifier Operations and Topology Switching

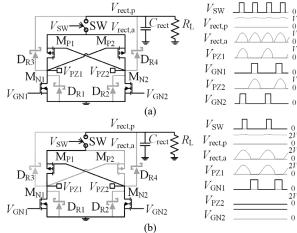

The rectifier configures itself as either FR or VD using the same set of components. Fig. 2 shows the components in use and some key voltage waveforms of the rectifier in FR and VD modes once  $V_{SU}$  is sufficiently high for the whole system operation. The active rectifier is formed by two gate crosscoupled PMOS  $M_{P1,2}$  that are driven by  $V_{PZ}$  with an arbitrary amplitude V and two NMOS  $M_{N1,2}$  that are driven by driver circuits with the outputs  $V_{GN1}$  and  $V_{GN2}$  applied to the gates of M<sub>N1</sub> and M<sub>N2</sub>, respectively. A normally-off switch SW links the outputs of the passive and active rectifiers at specific times for a proper operation of the circuit. When the output of the active rectifier  $V_{\text{rect,a}}$  is higher than the passive rectifier  $V_{\text{rect,p}}$ , SW is turned on by the signal  $V_{SW}$ . As SW closes, the outputs of both passive and active rectifiers are connected as a common output of  $V_{\text{rect}}$ . The active rectifier is the dominating element in rectifying ac voltage as the MOSFETs provide a current path with a lower voltage drop than  $V_{\rm F}$  of the diodes that form the FBR. The switch is open to prevent energy backflow from the smoothing capacitor  $C_{\text{rect}}$  when  $V_{\text{rect,a}}$  is lower than  $V_{\text{rect,p}}$ . As a FR,  $M_{P1}$  and  $M_{N2}$  are used to rectify the half cycle of the PEH output voltage when  $V_{PZ1} > 0$  while  $M_{P2}$ and  $M_{N1}$  are used for the other half cycle when  $V_{PZ2} > 0$ .

To operate as a VD, NMOS  $M_{N2}$  is constantly turned on to bypass diode  $D_{R2}$ . Thus, the anode of  $D_{R4}$  and the terminal of the PEH at  $V_{PZ2}$  are pulled to ground. As a sufficiently large  $C_{rect}$  tends to hold charges at the output of the rectifier, there is usually a positive voltage at the cathode of  $D_{R3}$  and  $D_{R4}$ . Thus,

Fig. 2. Illustration of the operation of the proposed circuit as a (a) FR and (b) VD. Greyed out components are not a conduction path.

$D_{R4}$  can be regarded as open circuited since it is reverse biased by the voltage at its cathode and ground connection at its anode.  $M_{P1}$  is always turned on as its gate is connected to  $V_{PZ2}$ , which is always LOW. This in turn connects the source and gate of  $M_{P2}$  together, which makes  $M_{P2}$  always off. As  $V_{PZ1}$  goes to zero,  $V_{GN1}$  from the driver circuit turns HIGH to turn on  $M_{N1}$  to charge up the intrinsic capacitor of the PEH. As the piezoelectric voltage increases again, the energy from the PEH is transferred to the output of the rectifier via  $M_{P1}$  and SW, which will be toggled as explained earlier.  $D_{R1}$  and  $D_{R3}$  are still valid current paths as VD but as in the case of the FR,  $M_{P1}$  and  $M_{N1}$  are the dominating elements, which without  $V_F$  provide a lower loss current path than the diodes.

# III. SYSTEM DESIGN AND ANALYSIS

Low power is one of the main considerations as most of the harvested energy should be for the end device instead of being used by the interface circuit [12]. Thus, various methods to enable the low voltage components to operate over a wide voltage range are used in the rectifier, driver circuit, start-up circuit, and control circuit that all have different operating conditions as part of these individual subsystems.

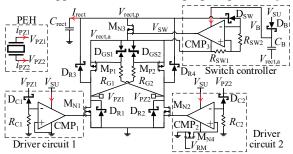

#### A. Rectifier

Apart from  $D_{R1-4}$ ,  $M_{P1,2}$ , and  $M_{N1,2}$ , resistors  $R_{G1,2}$  and gate protection diodes D<sub>GS1,2</sub> are also part of the rectifier as shown in Fig. 3 to protect M<sub>P1,2</sub>. A MOSFET may have a high drainsource voltage  $V_{\rm DS}$  rating but its gate-source voltage  $V_{\rm GS}$  rating is usually much lower. The possible high voltage from a PEH may cause  $V_{\text{rect,a}}$  at the source of  $M_{P1,2}$  to be high and the high voltage is held by  $C_{\text{rect}}$ . In the conventional cross-coupled connection, the gate of the PMOS at one side is connected directly to the terminal of the PEH at the other side as shown in Figs. 1 and 2. Thus, the voltage applied to the gate is  $V_{\rm PZ}$ , which can be slightly lower than zero at its trough. With  $V_{\text{rect,a}}$ remains high due to  $C_{\text{rect}}$ ,  $V_{\text{GS}}$  can be very high that it exceeds the breakdown  $V_{GS}$  of  $M_P$  and permanently damages  $M_P$ . With a  $D_{GS}$  in between the source and gate of  $M_P$  and  $R_G$  between the gate and the ground as shown in Fig. 3, the gate voltage  $V_{\rm G}$ of M<sub>P</sub> no longer goes to a very low voltage that creates a high  $V_{\rm GS}$ . D<sub>GS</sub> suppresses  $V_{\rm GS}$  to be within its clamping voltage if  $V_{\rm GS}$  exceeds that voltage. The gate voltage of M<sub>P</sub> drops across  $R_{\rm G}$ . Thus, an appropriate value of  $R_{\rm G}$  is required to reduce power dissipation without affecting the switching of  $M_P$  as  $R_G$ forms an RC circuit with the parasitic capacitance of M<sub>P</sub>. The RC time constant needs to be much shorter than the period of the vibration applied to the PEH for a proper operation [23].

Fig. 3. Schematic of the rectifier, switch controller, and driver circuit.

## B. Switch Controller

The switch SW is realized by an NMOS M<sub>N3</sub>, which has its drain and source connected to the output of the passive and active rectifiers, respectively. Since the voltage at the source of  $M_{N3}$  is  $V_{rect,a}$ ,  $M_{N3}$  is turned off when the voltage applied to its gate equals  $V_{\text{rect,a}}$ . To turn on  $M_{\text{N3}}$ , the voltage applied to its gate has to be at least  $V_{\text{rect,a}}$  plus the threshold voltage  $V_{\text{TH}}$  of M<sub>N3</sub>. A switch controller that comprises a comparator CMP<sub>3</sub>, a diode  $D_{SW}$ , and two resistors  $R_{SW}$  is used to toggle  $M_{N3}$ . CMP<sub>3</sub> is driven by using a bootstrap capacitor power supply that is referenced to  $V_{\text{rect,a}}$ . The start-up circuit charges up the bootstrap capacitor  $C_{\rm B}$  to voltage  $V_{\rm SU}$  via diode  $D_{\rm B}$  when  $V_{\rm rect,a}$ reaches its trough. As  $V_{\text{rect,a}}$  increases, the voltage  $V_{\text{B}}$  across  $C_{\text{B}}$ increases accordingly to a level that is equal to  $V_{SU}$  plus  $V_{rect,a}$ minus  $V_F$  of  $D_B$  to power up CMP<sub>3</sub>. With the ground pin of CMP<sub>3</sub> at  $V_{\text{rect,a}}$ , this gives CMP<sub>1</sub> an output voltage of higher than  $V_{\text{rect,a}}$  by  $V_{\text{SU}}$  minus  $V_{\text{F}}$  to fully turn on  $M_{\text{N1}}$  and a LOW output voltage of  $V_{\text{rect,a}}$ , which is low enough to turn off  $M_{\text{N3}}$ .

The positive input of CMP<sub>3</sub> is biased at the voltage  $V_{\rm rect,a}$  via  $R_{\rm SW1}$ . The negative input is linked to  $V_{\rm rect,a}$  via  $R_{\rm SW2}$  and  $V_{\rm rect,p}$  via  $D_{\rm SW}$ .  $D_{\rm SW}$  is reverse biased when  $V_{\rm rect,a}$  is lower than  $V_{\rm rect,p}$ . Thus, the voltage at the negative and positive inputs are equal at  $V_{\rm rect,a}$  for CMP<sub>3</sub> to output a voltage  $V_{\rm SW}$  that is LOW to keep  $M_{\rm N1}$  off. When  $V_{\rm rect,a}$  becomes higher than  $V_{\rm rect,p}$ ,  $D_{\rm SW}$  is forward biased and conducts current. This causes the voltage at the negative input to become slightly lower than the positive input due to the voltage drop across  $R_{\rm SW2}$ . Thus, the switching voltage  $V_{\rm SW}$  becomes HIGH to turn on  $M_{\rm N3}$ . As the inputs and ground of CMP<sub>3</sub> and  $C_{\rm B}$  are referenced to  $V_{\rm rect,a}$ , a low voltage comparator can be used to implement CMP<sub>3</sub>.

## C. Driver Circuit

As mentioned earlier, conventional active rectifiers that connect the negative input of the comparator directly to the PEH have a limited operating voltage range unless a high voltage comparator is used [18]. The comparator turns on the NMOS whenever the voltage of the PEH at its negative input goes to zero or below as shown in Fig. 2. Since the comparator turns on the NMOS when the PEH voltage is LOW, the high voltage of the PEH is not needed and can be decoupled from the comparator. The proposed driver circuit uses a resistor  $R_{\rm C}$ and a diode D<sub>C</sub> with its anode connected to the negative input of CMP<sub>1,2</sub> to isolate the high voltage. The other end of  $R_C$  is connected to the ground and the cathode of D<sub>C</sub> is connected to the terminal of the PEH.  $D_C$  is reverse biased when  $V_{PZ}$  is higher than its  $V_{\rm F}$  since its anode is connected to the ground via  $R_{\rm C}$ . Thus,  $D_{\rm C}$  can be regarded as open-circuited, which prevents very high  $V_{PZ}$  to be directly applied to the negative input of CMP and damaging it. Before M<sub>N1,2</sub> are switched on,  $D_{R1,2}$  are the current path due to their lower  $V_F$  than the inherent body diode of MOSFETs. Thus, the trough of  $V_{\rm PZ}$ will go below zero to  $-V_F$ . This causes  $D_C$  to be forward biased, which applies a negative voltage at the input of CMP. With the positive input of CMP<sub>1,2</sub> at zero, which is higher than the negative voltage, CMP<sub>1,2</sub> output a HIGH signal  $V_{GN1,2}$  to turn on M<sub>N1,2</sub>. Thus, this circuit design allows an active rectifier to be implemented using low voltage comparators regardless of the high PEH voltage with negligible power dissipation at  $D_C$  and  $R_C$  as their voltage drop is very low.

The positive input and ground terminal of CMP<sub>2</sub> are joined together and floated when the circuit is first started up. They are disconnected from the system ground by  $M_{N4}$ , which is in an OFF state initially. The floating voltage at the positive input of CMP<sub>2</sub> is always higher than the negative input that is pulled to the ground by  $R_{C2}$ . Thus, CMP<sub>2</sub> has an always-HIGH output that constantly turns on  $M_{N2}$  for a VD topology by default.  $M_{N4}$  will be turned on by the control circuit when  $V_{PZ}$  is sufficiently high to connect the negative input and ground pin of CMP<sub>2</sub> to the system ground. CMP<sub>2</sub> will then operate as described in the earlier paragraph, where it turns on  $M_{N4}$  for the rectifier to operate as a FR when  $V_{PZ2}$  reaches its trough.

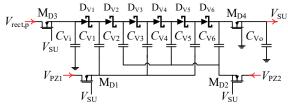

# D. Start-up Circuit

The start-up circuit consists of Schottky diodes  $D_V$ , flying capacitors  $C_V$ , four MOSFETs  $M_{D1-4}$ , and filter capacitors  $C_{Vi}$  and  $C_{Vo}$ , as shown in Fig. 4.  $M_{D1-4}$  are used as the voltage regulator here by applying a regulating voltage at their gate.  $M_{D1-4}$  are turned on when the applied  $V_{GS} \ge V_{TH}$  of  $M_D$ . The voltage relationship can be rewritten as (1) and rearranged as (2). The applied gate voltage  $V_G$  limits the maximum voltage  $V_S$  that can present at the source terminal of  $M_D$ .  $M_{D1-3}$  limit the voltage intake of  $V_{PZ}$  and  $V_{rect,p}$ , which can be very high.  $M_{D4}$  further limits the output from the charge pump to ensure  $V_{SU}$  is always within a safe level for the circuits.

$$V_{\rm G} - V_{\rm S} \ge V_{\rm TH} \tag{1}$$

$$V_{\rm S} \le V_{\rm G} - V_{\rm TH} \tag{2}$$

The circuit has an even number of stages n with each  $D_V$ – $C_V$  pair forming a multiplier stage. The start-up circuit takes  $V_{\text{rect,p}}$  as its input with the PEH driving its flying capacitors  $C_V$  to provide an amplified voltage  $V_{\text{SU}}$  and current  $I_{\text{SU}}$  as in (3) for starting-up the driver and control circuits [24]. The source voltages  $V_{\text{S-MD3}}$  of  $M_{\text{D3}}$  and  $V_{\text{FLY}}$  of  $M_{\text{D1,2}}$  are equal to  $V_{\text{rect,p}}$  and  $V_{\text{PZ}}$ , respectively, if they are lower than the condition on the right of (2). Otherwise, the voltages are limited by the  $V_G$  applied and  $V_{\text{TH}}$  of  $M_D$ . Since the flying capacitors are driven directly by  $V_{\text{PZ}}$ ,  $f_{\text{PZ}}$  is the vibration frequency of the PEH.

$$V_{\text{SU}} = V_{\text{S-MD3}} - V_{\text{F-DV}} + n \left( V_{\text{FLY}} - V_{\text{F-DV}} \right) - n I_{\text{SU}} \left( C_{\text{V}} f_{\text{PZ}} \right)^{-1}$$

(3)

Depletion-mode MOSFETs are used as  $M_{D1-4}$  as they are normally closed devices that allow current flow even when  $V_G$  applied to their gate is zero to enable cold start-up of the circuit. However, their channel resistance is usually higher than enhancement-mode MOSFETs such as  $M_{P1,2}$  and  $M_{N3,4}$ . By taking one stage that is formed by  $C_{V1}$  and  $D_{V1}$  as an example,  $C_{V1}$  will be charged up to a voltage that is equal to  $V_{\text{rect,p}}$  minus  $V_F$  of  $D_{V1}$  and the voltage drop of  $M_{D3}$ , and then

Fig. 4. Schematic of the start-up circuit.

boosted by  $V_{PZ1}$  minus the voltage drop of  $M_{D1}$ . The voltage drop of M<sub>D</sub> increases with their resistances, which reduces the peak voltage at each stage and the output voltage of the startup circuit. Thus,  $V_{SU}$  is applied to the gate of  $M_{D1-3}$  to reduce their resistance for a higher  $V_{SU}$ . Depletion-mode MOSFETs have a negative  $V_{TH}$  where  $V_G$  has to be lower than  $V_S$  to meet the condition as given by (1). Instead of generating a negative  $V_{\rm G}$  using an additional circuit, which consumes more power,  $C_{\text{Vi}}$  and  $C_{\text{Vo}}$  are used to hold the voltage at the source of  $M_{\text{D3,4}}$ so that the minimum  $V_G$  can simply be zero to limit the voltage at the source of  $M_D$  to a voltage that is equal to the  $V_{TH}$  of  $M_D$ . A diode in between  $C_{Vn}$  and  $C_{Vo}$  to prevent backflow of the charges is not required in this design. When the rectifier is in FR mode, the amplitude of  $V_{PZ}$  is sufficiently high where the voltage at  $C_{Vn}$  has already exceeded  $V_{SU}$ , which is regulated by M<sub>D4</sub>. In VD mode, the even-number stages are not acting as the multiplying stage because  $V_{PZ2}$  is at the ground. Thus,  $D_{Vn}$ at the last stage directly acts as the blocking diode here.

## E. Mode Control Circuit

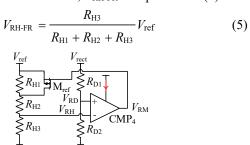

The mode control circuit is shown in Fig. 5, which consists of a comparator CMP<sub>4</sub>, a PMOS  $M_{ref}$ , and some resistors. Resistive voltage dividers are used to scale down  $V_{rect}$  and a reference voltage  $V_{ref}$  to an appropriate ratio as  $V_{RH}$  at the negative and  $V_{RD}$  at the positive inputs of CMP<sub>4</sub>, respectively.  $V_{RH}$  is lower than  $V_{RD}$  in VD mode and vice versa in FR mode for CMP<sub>4</sub> to output  $V_{RM}$  that toggle  $M_{N4}$  as explained earlier in the driver circuit section and  $M_{ref}$  for switching the rectifying topology as  $V_{rect}$  reaches a threshold. Switching  $M_{ref}$  on and off leads to the rectifier operation as a VD and FR, respectively.

As the rectifier switches from VD to FR,  $V_{\rm rect}$  and hence,  $V_{\rm RD}$  reduce by half. If  $V_{\rm RH}$  is unchanged, it could be higher than  $V_{\rm RD}$ , causing CMP<sub>4</sub> to output a LOW signal that switches the circuit to operate as a VD again and amplify  $V_{\rm rect}$ . This will trigger the circuit to switch back to FR again and the cycle repeats, alternating between the two rectifying modes in an unstable state. Thus, the value of  $V_{\rm RH}$  needs to be adaptive to the rectifying mode. The reference in VD mode  $V_{\rm RH-VD}$  has to be higher than the one in FR mode  $V_{\rm RH-FR}$ , which decreases as  $V_{\rm RD}$  is halved. This is achieved by a reconfigurable resistive divider network formed by  $V_{\rm RH-SR}$  and  $V_{\rm RH-VD}$  is turned on in VD mode, it acts as a closed switch to bypass the resistor  $V_{\rm RH-VD}$  is given as (4):

$$V_{\text{RH-VD}} = \frac{R_{\text{H3}}}{R_{\text{H2}} + R_{\text{H3}}} V_{\text{ref}}$$

(4)

When  $M_{ref}$  is turned off, it does not have any effect on the resistive divider network. Thus,  $V_{RH-FR}$  is expressed as (5):

Fig. 5. Schematic of the mode control circuit.

Equation (4) slightly differ from (5) in the denominator where  $R_{\rm H1}$  is excluded from (4) as  $M_{\rm ref}$  is switched on as explained earlier. Thus,  $V_{\rm RH-VD}$  is higher than  $V_{\rm RH-FR}$  because of its smaller denominator. When  $M_{\rm ref}$  is turned off in FR mode,  $R_{\rm H1}$  is included in the voltage divider to reduce  $V_{\rm RH}$  as  $V_{\rm RD}$  is lowered due to the switching from VD to FR to prevent the repetitive mode toggling issue [20].

The diode-resistor or transistor-based method applied to the other circuits in earlier subsections are not used here as they isolate high voltage from the circuits or limit the voltage intake, which does not allow the scaling of the voltage. Although it is possible to use a resistive voltage divider in the other circuits, they are not ideal as the resistive networks continually dissipate power. Also, when the PEH voltage is very low, the scaled-down voltage will be even lower, which might not be recognized by the comparators as a valid signal.

#### IV. EXPERIMENTAL VERIFICATION

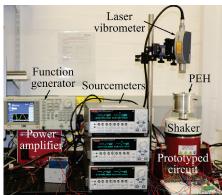

Fig. 6 shows the experimental setup with the PEH, which uses a piezoelectric stack as its active element (PICMA® P-887.91, PI ceramic) fixed on an electromagnetic shaker (V20, Data Physics). The acceleration exerted by the shaker was measured by a laser Doppler vibrometer (CLV2534, Polytech). The voltages and currents, which are represented by the arrows as indicated in Figs. 3–5 were measured using sourcemeter units (2612B, Keithley), which have the accuracies of within ±0.03% [25]. The terminals of the PEH were connected to a resistor first to characterize its power bandwidth. The frequency range of the bandwidth was used to test the circuit. The optimal resistance for each tested vibration is different [10]. Thus, the resistance was manually tuned until maximum power output from the PEH is obtained.

## A. System Implementation

The circuit was implemented using discrete components on a breadboard. The enhancement-mode MOSFETs were chosen based on their low channel resistances, low gate charge, and low  $V_{\rm TH}$ .  $M_{\rm N1-4}$  are BSS806N and  $M_{\rm P1,2}$  are DMG2301LK. An external  $D_{\rm GS}$  is not used as  $M_{\rm P1,2}$  has a built-in gate protection diode. These MOSFETs have a breakdown voltage of 20 V, which sets the maximum operating voltage limit of this circuit. The chosen  $M_{\rm D}$  (BSS159) has a  $|V_{\rm TH}|$  of 2.4–3.5 V, which is a common voltage range for many circuits if the applied  $V_{\rm G}$  is 0. Comparators with a minimum operating voltage of 1 V and

Fig. 6. Experimental setup.

quiescent current  $I_Q$  of around 0.3  $\mu$ A were used as CMP<sub>1-3</sub> (TS881) and CMP<sub>4</sub> (LTC1540) so that the circuit can operate from low voltage at low power. LTC1540 has a built-in bandgap reference voltage of 1.182 V to be used as  $V_{\text{ref}}$ .

CDBH0230 was used as  $D_{R1-4}$ ,  $D_{C1,2}$ ,  $D_{SW}$ , and  $D_B$  for their low  $V_F$  of 0.24 V. SDM02U30LP3 were chosen as  $D_V$  due to their low  $V_F$  of around 0.1 V so that the start-up circuit can generate a  $V_{SU}$  of at least 1 V with as few stages as possible. This is to ensure  $D_V$  and  $C_V$ , especially those at the later stages do not experience very high voltage but are still able to start-up the circuit. Assuming that the minimum voltage is 0.25 V, which is higher than  $V_F$  of CDBH0230 for the FBR to conduct and based on [3], a six-stage charge pump was used as the start-up circuit. SDM02U30LP3 was not used as the FBR as its leakage current is about 100 times of CDBH0230, which incurs higher losses and degrades the performance of the FBR.

From the datasheet, the input capacitance of  $M_{P1,2}$  is around 0.2 nF [26]. To ensure a time constant that is much shorter than the period of the vibration,  $R_{\rm G}$  was chosen to be 330 k $\Omega$ . Even with the gate protection circuit implemented, it is still best to avoid operating the circuit at very high voltage for a prolonged time. Considering that  $M_{P1,2}$  have a  $V_{\rm GS}$  of 12 V, the circuit was set to switch from VD to FR at around 11 V.  $R_{\rm H1}$ ,  $R_{\rm H2}$ , and  $R_{\rm H3}$  were set to be 100 M $\Omega$ , 20 M $\Omega$ , and 30 M $\Omega$ , respectively. This gives  $V_{\rm RH-VD}$  and  $V_{\rm RH-FR}$  the values of 11.06 V and 3.69 V, respectively.  $R_{\rm D1}$  is 20 M $\Omega$  and  $R_{\rm D2}$  is 1.37 M $\Omega$ , so that the maximum  $V_{\rm RD}$  is 1.182 V, which is equal to  $V_{\rm ref}$  when  $V_{\rm rect}$  is 20 V.  $R_{\rm C}$  and  $R_{\rm SW}$  are 10 M $\Omega$ . The resistor values are in the tens of megaOhms range to limit the maximum power dissipation to nanowatts range.

## B. Testing Methods

The first test was to determine the start-up capability of the prototype from the low voltages of the PEH. A range of low accelerations and frequencies was applied to the PEH via the shaker until the circuit started to operate. Then, the circuit was tested by sweeping across a frequency range around the bandwidth of the PEH, over a range of accelerations and resistive loads. The test includes verification of the topology switching and voltage regulation, power losses, as well as the voltage  $\eta_V$  and power  $\eta_P$  conversion efficiencies of the circuit as given by (6)–(8). The power at the different parts of the circuit was determined using (6).  $\Delta t$  of 0.5 ms is the sampling

Fig. 7. Open-circuit voltage (top), current (marker), and power (bottom) with an optimal resistive load of the PEH excited by different accelerations.

period and  $t_N$  is 70 s to ensure sufficient data sample is taken. The subscript x represents the measurements made at different parts of the system such as 'PZ', 'rect', and so on.

$$P_{x} = \frac{\sum_{k=1}^{N} v_{x}(t_{k}) i_{x}(t_{k}) \Delta t}{t_{y}}$$

(6)

$$\eta_{\rm V} = \frac{V_{\rm rect}}{|V_{\rm PZ}|} \times 100\% \tag{7}$$

$$\eta_{\rm P} = \frac{P_{\rm rect}}{P_{\rm PZ}} \times 100\% \tag{8}$$

## V. RESULTS AND DISCUSSIONS

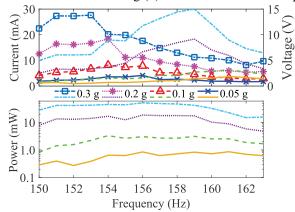

Fig. 7 shows the open-circuit voltage of the PEH that ranges from 0.4--15 V under the acceleration of 0.05--0.3 g, which is common in industrial environments [27]. When an optimal resistive load is connected to the PEH, the output current amplitude is 2--27.7 mA and power is  $287.6 \,\mu\text{W}\text{--}51.74$  mW. The vibration frequency of interest in this work is around 150--163 Hz, which is the power bandwidth of the PEH used [10].

# A. Start-up

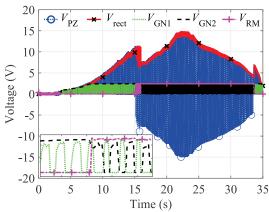

Fig. 8 shows the measured  $V_{\rm PZ}$ ,  $V_{\rm SU}$ ,  $V_{\rm GN2}$ , and  $V_{\rm CV6}$  when the PEH was excited at a vibration frequency of 153 Hz that swept over the accelerations from 0.04–0.2 g. The inset shows the transient state of the circuit. The start-up circuit can operate as soon as there is a voltage from the PEH. The start-up circuit produces  $V_{\rm SU}$  of up to 1.1 V from  $|V_{\rm PZ}|$  of 0.25 V at the acceleration of 0.04 g to startup the rectifying circuit. The output voltage  $V_{\rm GN2}$  from CMP2 is fluctuating initially but becomes steady at around 0.65 V within 2 s and follows the amplitude of  $V_{\rm SU}$  closely afterwards. As  $V_{\rm GN2}$  reaches 0.6 V, which is sufficiently high to fully turn on  $M_{\rm N2}$ ,  $V_{\rm PZ}$  in the negative half cycle reduces to almost zero. The gap between  $|V_{\rm rect}|$  and  $|V_{\rm PZ}|$  is large before  $V_{\rm SU}$  reached 0.6 V as  $V_{\rm PZ}$  is rectified by the passive FBR. When  $V_{\rm SU}$  is higher than 0.6 V for the active rectifier to operate,  $|V_{\rm rect}|$  becomes close to  $|V_{\rm PZ}|$ .

The acceleration was gradually increased to 0.2 g after 14 s where the amplitude of  $V_{PZ}$  reached 3.5 V. The voltage  $V_{CV6}$  at

Fig. 8. Measured  $V_{\rm PZ}$ ,  $V_{\rm rect}$ ,  $V_{\rm GN2}$ ,  $V_{\rm SU}$ , and  $V_{\rm CV6}$  with the PEH excited by the acceleration from 0.04–0.2 g. Inset shows the enlarged view of the area from time 0 to 2.5 s.

the last multiplier stage of the charge pump before  $M_{D4}$  of the start-up circuit is about 11 V, which is too high for most of the low power comparators. With the voltage regulation using  $M_{D4}$  as described in Section III.D,  $V_{SU}$  is regulated at 2.5 V.

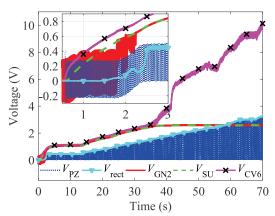

# B. Rectification and Self-configurability

Fig. 9 shows the measured  $V_{PZ}$ ,  $V_{rect}$ ,  $V_{GN1}$ ,  $V_{GN2}$ , and  $V_{RM}$  as the PEH was excited by a gradually increased acceleration until the PEH voltage is 15 V and back to 0 g at 159 Hz to test the topology switching functionality of the circuit. The circuit begins its operation in VD mode by default, where  $V_{\rm PZ}$  can be seen to have zero amplitude in the negative half cycle.  $V_{GN2}$  is also HIGH to keep  $M_{N2}$  always turned on.  $V_{rect}$  increases with the acceleration until it reaches around 11.22 V at 15.8 s.  $V_{\rm RM}$ becomes HIGH to turn on M<sub>N4</sub> and switches the circuit to FR mode where  $V_{PZ}$  can be seen to have an equal amplitude in both the positive and negative half-cycles.  $V_{\text{rect}}$  also reduces following the switch.  $V_{\rm GN2}$  now becomes pulses to turn on  $M_{\rm N2}$ at the appropriate time when  $V_{GN1}$  is LOW as shown in the inset. The results indicate the proposed diode-resistor circuit enables the low voltage comparators with the supply voltage of 2.5 V to operate using high voltage of over 10 V from the PEH as their input signal without being damaged. As the acceleration reduces,  $V_{PZ}$  decreases until  $V_{rect}$  drops to 3.77 V at 33.6 s. The circuit then switches back to VD mode when  $V_{\rm RM}$  goes LOW.  $V_{\rm rect}$  can be seen to increase and the negative half cycle of  $V_{PZ}$  disappears again. The voltages for topology switching are in good agreement with the calculated one.

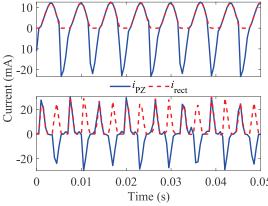

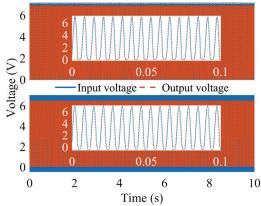

Fig. 10 shows the measured currents  $i_{PZ}$  from the PEH and  $i_{rect}$  output by the rectifier at the acceleration of 0.3 g as an example. The frequencies used are 150 Hz and 159 Hz to get a low and high voltage, respectively. The MOSFETs are switching appropriately in either VD at 150 Hz or FR mode at 159 Hz, where the waveform of the rectified current  $i_{rect}$  closely follows the waveform of the input current  $i_{PZ}$ . In VD mode,  $i_{PZ}$  in the negative half cycle is used to charge up the PEH itself and is not passed through the output of the rectified as  $i_{rect}$ . In FR mode,  $i_{PZ}$  in the negative half cycle is rectified as  $i_{rect}$  at the output of the rectifier. There is no backflow of  $i_{rect}$  from the rectifier output back to the PEH in both operation modes where the amplitude of  $i_{rect}$  does not go to negative.

Fig. 9. Measured  $V_{\rm PZ}$ ,  $V_{\rm rect}$ ,  $V_{\rm GN1}$ ,  $V_{\rm GN2}$ , and  $V_{\rm RM}$  with the PEH excited by sweeping back and forth over a range of acceleration at 159 Hz. Inset shows the enlarged view of the area from time 15.8 to 15.9 s.

# C. Efficiencies and Losses

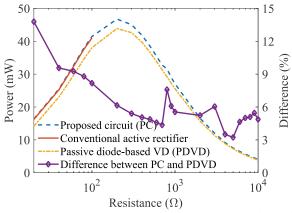

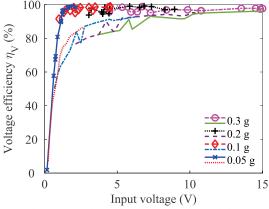

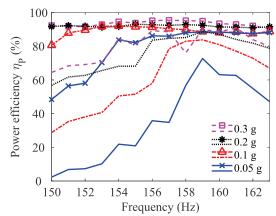

Fig. 11 shows the output power versus different resistive loads from the proposed circuit, a conventional active rectifier, and a passive diode-based VD using BAS70, which has low  $V_{\rm F}$  and reverse leakage current [28], with the PEH excited by an acceleration of 0.3 g at 159 Hz as an example. The power curves gradually increase until they reach a peak, which corresponds to the optimal load of the PEH before decreasing. Although the power output by the conventional active rectifier is similar to the proposed circuit, it can only operate up to the load of 100  $\Omega$  as further increase of the load will cause  $V_{\rm PZ}$  to exceed its voltage limit. The passive diode-based VD has an output power of typically around 5% lower than the proposed circuit in this test due to the inherent  $V_{\rm F}$  of the diodes, which lowers the output voltage as shown in Figs. 12 and 13. The difference can be over 13% especially when the input voltage is low at near to 1 V as shown in Fig. 12. There is also a voltage drop in the negative half cycle due to  $V_{\rm F}$  during the voltage amplification, which increases the losses.

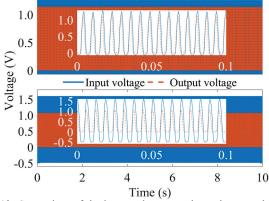

Fig. 14 compares the voltage conversion efficiencies of the proposed circuit with passive diode-based rectifiers from 0.05 – 0.3 g. Apart from the test condition at 0.05 g, the efficiency of the proposed circuit is over 90%, with a peak voltage efficiency of 99.14%. The amplitude of the gate threshold voltage of M<sub>P1,2</sub> used ranges from 0.3 V–1 V. Thus, when the

Fig. 10. Measured  $i_{\rm PZ}$  and  $i_{\rm rect}$  when the rectifier is in VD mode (top) and FR mode (bottom) with the PEH excited by an acceleration of 0.3 g at 150 Hz and 159 Hz, respectively.

Fig. 11. Comparison of the output power with different resistive loads of 10  $\Omega$  to 10 k $\Omega$  connected to the output of the PC, a conventional active rectifier and a PVD with the PEH excited by an acceleration of 0.3 g at 159 Hz.

input voltage to the rectifier is below 1 V, it is possible that M<sub>P1</sub>? are not fully turned on and causes the efficiency to be lower than 90% as shown in Fig. 12. However, the prototyped circuit still outperforms the passive rectifier in all the test conditions, especially at low input voltage with an efficiency of about 20% higher. The efficiency of the passive rectifier becomes higher than 90% when the input voltage to the rectifier is over 4 V while the prototyped circuit can achieve such efficiency with an input voltage of about 1.5 V. It should be noted that the rectifier begins its operation as a VD that increases the amplitude of the piezoelectric voltage  $V_{PZ}$  by default. This means the actual output voltage from the PEH is about half of the input voltage to the rectifier. With the proposed circuit, the amplitude of  $V_{PZ}$  is amplified to allow the circuit to rectify voltage that is initially lower than the gate threshold voltage of the MOSFETs used in the rectifier. This is not possible in other conventional active rectifiers that only operate in a fixed FR mode where their minimum input voltage with a voltage conversion efficiency of 90% is usually beyond the threshold voltage of the MOSFETs [18], [29].

Fig. 15 compares the power conversion efficiencies of the proposed and passive rectifier circuits under the same test conditions as in Fig. 14. Similarly, the prototyped circuit has a higher efficiency than the passive diode-based rectifier in most of the test conditions. The efficiency is generally about 90%, with a peak of 95.43% except for the accelerations of 0.05 g

Fig. 12. Comparison of the input and output voltages between the proposed circuit (top) and passive rectifier (bottom) under low voltage condition with a  $20 \Omega$  load. The insets show the detailed waveforms.

Fig. 13. Comparison of the input and output voltages between the proposed circuit (top) and passive rectifier (bottom) with a 300  $\Omega$  load. The insets show the detailed waveforms.

and 0.1 g especially when the voltage is low, which occurs at the vibration frequencies near 150 Hz and 163 Hz. This is because  $M_{Pl,2}$  cannot be fully turned on when the voltage is low as explained earlier, causing higher power dissipation in the MOSFETs. However, the passive rectifier performs poorer especially in low voltage, high current conditions around 150 Hz. For example, the passive rectifier has an efficiency of 2% while the prototyped circuit achieves an efficiency of 48.42% when the excitation acceleration is 0.05 g at 150 Hz. The efficiency of the passive rectifier is less than 70% most of the time in all the tests with different accelerations.

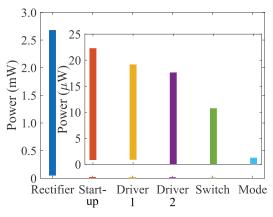

Fig. 16 shows the range of power consumed by different parts of the circuit. The power consumed by the circuit with  $CMP_{1-4}$  was calculated by using (6) plus the Ohmic loss ( $V^2/R$ ) of any of the resistive branches. The power dissipated by the start-up circuit  $P_{\text{loss, SU}} = P_{\text{rect,p}} + P_{\text{PZ1}} + P_{\text{PZ2}}$  -  $P_{\text{SU}}$ . The power loss in the rectifier was obtained by subtracting  $P_{\text{rect}}$  and power consumed by the other circuits from  $P_{PZ}$ . The primary power loss in the prototyped circuit is caused by conduction loss of the MOSFETs with a turn-on resistance of a few hundreds milliOhms in each of the MOSFETs. The range of the power dissipated by the MOSFETs is from 48.71 µW to 2.68 mW, depending on the current from the PEH that ranges from a few to tens of milliamperes in the tested conditions. The mode control circuit consumes the lowest power at 0.39-1.26 µW as CMP<sub>3</sub> toggles M<sub>N4</sub> and M<sub>ref</sub> very infrequently. However, the resistive networks of  $R_{\rm H}$  and  $R_{\rm D}$  dissipate power continuously,

Fig. 14. Voltage conversion efficiency comparison of the proposed circuit (with markers) and passive rectifier under different tests.

Fig. 15. Power conversion efficiency comparison of the proposed circuit (with markers) and passive rectifier under different tests.

which increases with  $V_{\rm rect}$ . The switch controller, start-up, and driver circuits have comparable power consumptions as they are involved in switching operations regularly. The start-up circuit has the highest power losses among them but is in a couple of microwatts. This is because it supplies energy to all the other functional circuits. The total current consumed by all the other circuits has to flow through the diodes  $D_V$ , which have a voltage drop  $V_F$ . This causes  $0.83-22.30~\mu W$  of power to be dissipated in the circuit. The switch controller consumes the least power at  $0.43-10.77~\mu W$  as it only turns  $M_{\rm N3}$  on very briefly when  $V_{\rm rect,a}$  is higher than  $V_{\rm rect,p}$ .

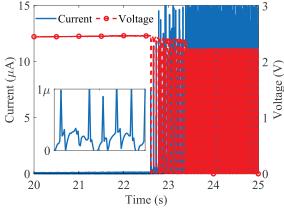

All the driver circuits consume 0.11-19.18 µW of power. Among them, driver circuit 1 that consists of CMP<sub>1</sub> has a higher minimum power consumption as it is switching M<sub>N1</sub> regularly. Driver circuit 2 that consists of CMP2 and is also involved in the mode switching of the rectifier has a lower minimum power consumption range. It has virtually no power dissipation when CMP<sub>2</sub> is floated in the VD mode. Fig. 17 shows the current consumed and the voltage  $V_{GN2}$  output by CMP<sub>2</sub>. It can be clearly seen that the current is very low when the rectifier is in VD mode with  $V_{\rm GN2}$  always HIGH. Once the rectifier switches to FR mode, the current consumption increases drastically due to the regular switching operation involved. This also suggests that the proposed driver circuit for enabling the rectifier to begin its operation in VD mode by default does not draw much energy, which is especially crucial to ensure a successful start-up of the rectifier.

Fig. 16. Power consumption of the different parts of the prototyped circuit. Inset is the enlarged view of the results on the right of 'rectifier'.

Fig. 17. Measured current consumed and voltage  $V_{\rm GN2}$  output by CMP<sub>2</sub> as the rectifier switches from VD mode to FR mode.

# D. Comparison With Other Rectifiers

Table I summarizes and compares some common features of the proposed rectifier with other circuits. The other circuits that were implemented as an active rectifier have a limited operating voltage range because of the direct connection of the energy harvester to the comparators, which have a low voltage rating of up to 5 V to drive the NMOS of the rectifier. The prototyped circuit can operate up to 20 V using low voltage comparators that are powered by a voltage supply of 1–2.5 V using the voltage regulation method described in Section III. Although the prototyped circuit was designed to operate up to 20 V, the circuit can be easily implemented to operate at a higher voltage by changing M<sub>P1,2</sub>, M<sub>N1,2</sub>, and D<sub>C1,2</sub> to have a higher voltage rating while using the same low voltage comparators. The passive diode-based rectifier can operate up to 20 V as no comparators are involved in rectification [20]. The efficiencies are up to 98% because the rectifier was tested using an energy harvester with high voltage and low current output, which has low power dissipation in the diodes. The circuits in [20], [22] are configurable to different rectifying topologies of either FR or VD just like this work. However, the minimum input voltage from the energy harvester that is required for the circuits to start operating is much higher than the proposed circuit because they do not have a start-up circuit. They rely on the energy harvester to generate a voltage that is sufficiently high for their start-up. The circuit in [29] can start-up at a low voltage that is close to the proposed circuit due to the low  $V_{\rm TH}$  CMOS fabrication technology used. The peak  $\eta_V$  of the proposed circuit is the highest among all the circuits that are compared at 99.14%. The peak  $\eta_P$  of the proposed circuit is also the highest among the active rectifiers.

# VI. CONCLUSION

A self-powered and self-configurable active rectifier for energy harvesters with a wide voltage range is presented. The circuit is able to startup from the low output voltage of an energy harvester and operates using VD topology by default to boost the voltage. Even though the voltage of the energy harvester is low, the voltage that has been amplified is sufficiently high to reach the gate threshold voltage of the MOSFETs used as the rectifier. This allows the rectifier to operate at higher efficiency and wider range than conventional active rectifiers that operate using a fixed topology. The circuit switches its topology to a FR, which does not amplify the voltage as the voltage of the energy harvester becomes sufficiently high. Low power and voltage comparators were used as the driver and control circuits. A novel and simple resistor-diode based solution was introduced to allow the low voltage comparators to operate using the high voltage from the energy harvester as the input signal. This allows the control and driver circuits to be fabricated using standard low voltage technology when implemented as integrated circuits. The circuit was tested using a PEH that has a wide output range and achieved voltage and power conversion efficiencies of over 90% in most of the tested conditions.

TABLE I

PERFORMANCE SUMMARY AND COMPARISON

| Reference                                  | [19]            | [29]                            | [30]            | [21]             | This<br>work    |

|--------------------------------------------|-----------------|---------------------------------|-----------------|------------------|-----------------|

| Technology                                 | 0.18 μm<br>CMOS | $0.35  \mu m$ low $V_{TH}$ CMOS | 0.5 μm<br>CMOS  | Discrete         | Discrete        |

| Structure                                  | Active<br>FR    | Active<br>FR                    | Active<br>FR/VD | Passive<br>FR/VD | Active<br>FR/VD |

| Self-<br>configurable                      | No              | No                              | Yes             | Yes              | Yes             |

| Start-up<br>mechanism                      | N/A             | N/A                             | N/A             | N/A              | Charge<br>pump  |

| $V_{\text{in,min}}\left(\mathbf{V}\right)$ | N/A             | 0.38                            | 1.8             | 1.2              | 0.25            |

| $V_{\text{in,max}}\left(\mathbf{V}\right)$ | 3               | 3.3                             | 5               | 20               | 20              |

| Peak $\eta_{V}$ (%)                        | 99              | 98                              | 83.8            | 98               | 99.14           |

| Peak $\eta_P$ (%)                          | 90              | 90                              | 81              | 98               | 95.43           |

#### REFERENCES

- [1] R. Bogue, "Wireless sensors: A review of technologies, products and applications," *Sens. Rev.*, vol. 30, no. 4, pp. 285-289, 2010.

- [2] K. Ali, and D. J. Rogers, "An orientation-independent multi-input energy harvesting wireless sensor node," *IEEE Trans. Ind. Electron.*, vol. 68, no. 2, pp. 1665-1674, 2021.

- [3] H. O. Tabrizi, H. M. P. C. Jayaweera, and A. Muhtaroğlu, "Fully integrated autonomous interface with maximum power point tracking for energy harvesting TEGs with high power capacity," *IEEE Trans. Power Electron.*, vol. 35, no. 5, pp. 4905-4914, 2020.

- [4] Z. J. Chew, T. Ruan, M. Zhu, M. Bafleur, and J. M. Dilhac, "Single piezoelectric transducer as strain sensor and energy harvester using timemultiplexing operation," *IEEE Trans. Ind. Electron.*, vol. 64, no. 12, pp. 9646-9656, 2017.

- [5] Y. Kuang, Z. J. Chew, T. Ruan, and M. Zhu, "Magnetic field energy harvesting from current-carrying structures: Electromagnetic-circuit coupled model, validation and application," *IEEE Access*, vol. 9, pp. 46280-46291, 2021.

- [6] Y. Kuang, A. Daniels, and M. Zhu, "A sandwiched piezoelectric transducer with flex end-caps for energy harvesting in large force environments," J. Phys. D: Appl. Phys., vol. 50, no. 34, Aug. 1 2017, Art. no. 345501.

- [7] M. Zhu, E. Worthington, and A. Tiwari, "Design study of piezoelectric energy-harvesting devices for generation of higher electrical power using a coupled piezoelectric-circuit finite element method," *IEEE Trans. Ultrason.*, Ferroelectr., Freq. Control, vol. 57, no. 2, pp. 427-437, 2010.

- [8] G. Yang, B. H. Stark, S. G. Burrow, and S. J. Hollis, "Optimization of passive voltage multipliers for fast start-up and multi-voltage power supplies in electromagnetic energy harvesting systems," *JPCS*, vol. 557, Nov. 27 2014, Art. no. 012028.

- [9] Y. Kuang, Z. J. Chew, T. Ruan, T. Lane, B. Allen, B. Nayar, and M. Zhu, "Magnetic field energy harvesting from the traction return current in rail tracks," *Appl. Energ.*, vol. 292, Jun. 15 2021, Art. no. 116911.

- [10] Y. Kuang, Z. J. Chew, J. Dunville, J. Sibson, and M. Zhu, "Strongly coupled piezoelectric energy harvesters: Optimised design with over 100 mW power, high durability and robustness for self-powered condition monitoring," *Energy Conversion and Management*, vol. 237, Jun. 1 2021, Art. no. 114129.

- [11] Z. J. Chew, T. Ruan, and M. Zhu, "Energy savvy network joining strategies for energy harvesting powered TSCH nodes," *IEEE Trans. Ind. Informat.*, vol. 17, no. 2, pp. 1505-1514, 2021.

- [12] Z. J. Chew, T. Ruan, and M. Zhu, "Strain energy harvesting powered wireless sensor system using adaptive and energy-aware interface for enhanced performance," *IEEE Trans. Ind. Informat.*, vol. 13, no. 6, pp. 3006-3016, 2017.

- [13] A. Tabesh, and L. G. Fréchette, "A low-power stand-alone adaptive circuit for harvesting energy from a piezoelectric micropower generator," *IEEE Trans. Ind. Electron.*, vol. 57, no. 3, pp. 840-849, 2010.

- [14] S. Stanzione, C. v. Liempd, R. v. Schaijk, Y. Naito, F. Yazicioglu, and C. V. Hoof, "A high voltage self-biased integrated dc-dc buck converter with fully analog MPPT algorithm for electrostatic energy harvesters," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3002-3010, 2013.

- [15] M. Nielsen-Lönn, P. Angelov, J. J. Wikner, and A. Alvandpour, "Self-powered micro-watt level piezoelectric energy harvesting system with wide input voltage range," *Analog Integr. Circuits Signal Process.*, vol. 98, no. 3, pp. 441-451, Mar. 1 2019.

- [16] T. Hehn, F. Hagedorn, D. Maurath, D. Marinkovic, I. Kuehne, A. Frey, and Y. Manoli, "A fully autonomous integrated interface circuit for piezoelectric harvesters," *IEEE J. Solid-State Circuits*, vol. 47, no. 9, pp. 2185-2198, 2012.

- [17] G. A. Rincón-Mora, and S. Yang, "Tiny piezoelectric harvesters: Principles, constraints, and power conversion," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 63, no. 5, pp. 639-649, 2016.

- [18] S. Fan, R. Wei, L. Zhao, X. Yang, L. Geng, and P. X. L. Feng, "An ultralow quiescent current power management system with maximum power point tracking (MPPT) for batteryless wireless sensor applications," *IEEE Trans. Power Electron.*, vol. 33, no. 9, pp. 7326-7337, 2018.

- [19] C. Peters, D. Spreemann, M. Ortmanns, and Y. Manoli, "A CMOS integrated voltage and power efficient AC/DC converter for energy harvesting applications," *J. Micromech. Microeng.*, vol. 18, no. 10, Sep. 29 2008, Art. no. 104005.

- [20] Z. J. Chew, and M. Zhu, "Adaptive self-configurable rectifier for extended operating range of piezoelectric energy harvesting," *IEEE Trans. Ind. Electron.*, vol. 67, no. 4, pp. 3267-3276, 2020.

- [21] D. Cabello, E. Ferro, P.-R. Ó, B. Martínez-Vázquez, V. M. Brea, J. M. Carrillo, and P. López, "On-chip solar energy harvester and PMU with cold start-up and regulated output voltage for biomedical applications," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 67, no. 4, pp. 1103-1114, 2020.

- [22] H. M. Lee, and M. Ghovanloo, "An adaptive reconfigurable active voltage doubler/rectifier for extended-range inductive power transmission," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 59, no. 8, pp. 481-485, 2012.

- [23] J. Liang, and W.-H. Liao, "Improved design and analysis of self-powered synchronized switch interface circuit for piezoelectric energy harvesting systems," *IEEE Trans. Ind. Electron.*, vol. 59, no. 4, pp. 1950-1960, 2012.

- [24] J. F. Dickson, "On-chip high-voltage generation in mnos integrated circuits using an improved voltage multiplier technique," *IEEE J. Solid-State Circuits*, vol. 11, no. 3, pp. 374-378, 1976.

- [25] Tektronix, "2600B system sourcemeter® SMU instruments," [Online]. Available: https://download.tek.com/datasheet/1KW-60906-0 Series 2600BDatasheet 112718.pdf. Accessed on Aug. 11, 2021.

- [26] Diodes Inc., "P-channel enhancement mode MOSFET," DMG2301LK Datasheet., 2016. [Online]. Available: https://www.diodes.com/assets/Datasheets/DMG2301LK.pdf. Accessed on May. 29, 2020.

- [27] A. C. Waterbury, and P. K. Wright, "Vibration energy harvesting to power condition monitoring sensors for industrial and manufacturing equipment," *Proc. Inst. Mech. Eng. C J. Mech. Eng. Sci.*, vol. 227, no. 6, pp. 1187-1202, 2013.

- [28] Z. J. Chew, T. Ruan, and M. Zhu, "Power management circuit for wireless sensor nodes powered by energy harvesting: On the synergy of harvester and load," *IEEE Trans. Power Electron.*, vol. 34, no. 9, pp. 8671-8681, 2019.

- [29] C. Peters, J. Handwerker, D. Maurath, and Y. Manoli, "A sub-500 mV highly efficient active rectifier for energy harvesting applications," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, no. 7, pp. 1542-1550, 2011.