# Manuscript version: Author's Accepted Manuscript

The version presented in WRAP is the author's accepted manuscript and may differ from the published version or Version of Record.

#### **Persistent WRAP URL:**

http://wrap.warwick.ac.uk/163701

#### How to cite:

Please refer to published version for the most recent bibliographic citation information.

# **Copyright and reuse:**

The Warwick Research Archive Portal (WRAP) makes this work by researchers of the University of Warwick available open access under the following conditions.

Copyright © and all moral rights to the version of the paper presented here belong to the individual author(s) and/or other copyright owners. To the extent reasonable and practicable the material made available in WRAP has been checked for eligibility before being made available.

Copies of full items can be used for personal research or study, educational, or not-for-profit purposes without prior permission or charge. Provided that the authors, title and full bibliographic details are credited, a hyperlink and/or URL is given for the original metadata page and the content is not changed in any way.

## **Publisher's statement:**

Please refer to the repository item page, publisher's statement section, for further information.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk.

# 3.3 kV SiC JBS diodes employing a P<sub>2</sub>O<sub>5</sub> surface passivation treatment to improve electrical characteristics

Arne Benjamin Renz School of Engineering University of Warwick Coventry, UK A.Renz@warwick.ac.uk

Vasantha Pathirana

Cambridge Microelectronics Ltd.

Capital Park, Fulbourn

Cambridge, UK

Vasantha.Pathirana@camutronics.com

Ruizhu Wu

School of Engineering

University of Warwick

Coventry, UK

Robert.Wu.1@warwick.ac.uk

Guy William Clarke Baker School of Engineering University of Warwick Coventry, UK Guy.Baker@warwick.ac.uk Oliver James Vavasour School of Engineering University of Warwick Coventry, UK O.Vavasour.1@warwick.ac.uk

Tanya Trajkovic

Cambridge Microelectronics Ltd.

Capital Park, Fulbourn

Cambridge, UK

Tanya.Trajkovic@camutronics.com

Jose Angel Ortiz-Gonzalez

School of Engineering

University of Warwick

Coventry, UK

J.A. Ortiz-Gonzalez@warwick.ac.uk

Philip Mawby

School of Engineering

University of Warwick

Coventry, UK

P.A.Mawby@warwick.ac.uk

Vishal Ajit Shah

School of Engineering

University of Warwick

Coventry, UK

Vishal.Shah@warwick.ac.uk

Yeganeh Bonyadi

Lyra Electronics Ltd.

Warwick University Campus

Wellesbourne, UK

Ybonyadi@lyraelectronics.com

Xiaoyun Rong

School of Engineering

University of Warwick

Coventry, UK

Xiaoyun.Rong@warwick.ac.uk

Peter Michael Gammon

School of Engineering

University of Warwick

Coventry, UK

P.M.Gammon@warwick.ac.uk

Abstract-3.3 kV Schottky barrier diodes and Junction Barrier Schottky diodes have been fabricated, employing a phosphorous pentoxide (P2O5) surface treatment prior to metal deposition in an attempt to further condition the power device's interface. For SBD structures, the treatment consistently reduces the leakage current in molybdenum, tungsten and niobium SBDs, for the tungsten treatment by more than four orders of magnitude. X-ray photoelectron spectroscopy (XPS) analysis on the treated SBD interface revealed formation of a metal phosphate between P2O5 and the metal. When compared to an untreated sample, the P2O5 treatment has increased the valence band to fermi level offset by 0.2 eV to 3.25 eV, indicating that the treatment results in a degenerately n-doped SiC surface. When applied to fully optimised 3.3 kV JBS power structures utilizing a hybrid JTE design, P2O5 treatments improved blocking capabilities across the entire dataset by as much as 1,000 V.

Keywords—Schottky diodes, surface conditioning, phosphorous pentoxide, refractory metals, XPS

# I. INTRODUCTION

Silicon carbide (SiC) and its unique material properties, including lower specific on-resistance and higher critical electric field compared to silicon (Si), have established it as the most mature amongst the wide bandgap semiconductor materials. SiC Schottky barrier diodes remain the most prominent and reliable SiC devices, with improvements still ongoing. At 1700 V, junction barrier Schottky (JBS) diodes offer lower losses and higher frequency switching than Si PiN diodes, giving it a dominant market position [1, 2].

The wide bandgap of SiC leads to a high Schottky barrier height (SBH) at the metal-semiconductor interface, relative to Si. However, the SBH can be controlled by the choice of Schottky metal, leading to a trade-off between low forward voltage drop (V<sub>F</sub>) and low reverse current (I<sub>R</sub>). The use of titanium (Ti) on SiC results in a relatively low SBH (1.17 eV [3]), which favours V<sub>F</sub> reduction over I<sub>R</sub>. Ti has become the industry standard metal, preferred over nickel (Ni), which results in a relatively high SBH (~1.35 eV [2]). Recently, the trend towards lower SBHs has been taken further, with a shift towards molybdenum (Mo)[4], and molybdenum nitride (MoN) [3, 5], the latter further reducing the SBH to 0.86 eV. Further attempts to modulate the barrier height by varying the annealing temperatures have been undertaken in titanium (Ti) [6], tungsten (W) [7] and tungsten carbide (WC) [8, 9] as well as on Schottky diodes on more heavily doped epitaxial layers [10, 11]. Recently, the use of surface treatments prior to metal deposition has been shown to further influence this key tradeoff between using different metals [4]. The use of a novel phosphorous pentoxide (P2O5) treatment, applied prior to metallisation, was shown to highly dope the SiC subsurface to a depth of no more than 50 nm, lowering the SBH by an average of 0.11 eV, but yet it also reduced the I<sub>R</sub> by an average of two orders of magnitude. The high-melting point of Mo is key to this, as it prevents the formation of silicides during the Schottky contact anneal, leaving the enhancement of the subsurface in place. For metals with lower melting points, such as Ti and Ni, which form silicides, the P2O5 enhancement has no effect.

In this paper, the first fully optimized 3.3 kV JBS diodes are produced using the  $P_2O_5$  enhancement. Given the prior

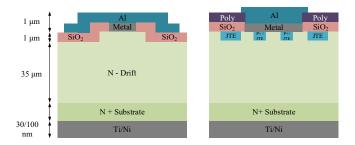

Figure 1: (left) Cross section of the fabricated unterminated Schottky

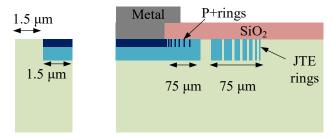

Figure 2: Detailed JBS designs of : (left) the half-cell of the active area, using a shallow, highly doped p+ implant on top of the JTE implant; (right) the hybrid termination consisting of P+ rings and multiple JTE rings. P+ ring widths are fixed at 3  $\mu$ m (3, 3, 4, 6, 8, 11  $\mu$ m gaps). JTE ring widths are 14, 11, 7, 5, 4 and 3  $\mu$ m (3, 3, 4, 5, 7 and 9  $\mu$ m gaps).

success of the refractory metal Mo, this process is applied to other refractory metals, tungsten (W) and niobium (Nb) for the first time. The reasons for the enhancement are then investigated via XPS. Finally, the P<sub>2</sub>O<sub>5</sub> treated Nb and Mo diodes are then developed into fully optimised JTE-terminated 3.3 kV JBS diodes to see how the P<sub>2</sub>O<sub>5</sub> treatment affects high voltage leakage currents, the device breakdown and the onstate.

# II. DEVICE FABRICATION

Two types of diodes were fabricated, shown in Fig. 1. Simple, small area (4.39 × 10<sup>-2</sup> mm<sup>2</sup>) mesa isolated Schottky diodes, without termination, were first produced to test the effects of the P<sub>2</sub>O<sub>5</sub> treatment across various metal contacts. Then, fully optimised JBS diodes (active areas 1.56 mm<sup>2</sup> and 42.25 mm<sup>2</sup>) were then produced such that the P<sub>2</sub>O<sub>5</sub> treatment could be trialled on an industry standard process to high current and high reverse voltage. A novel hybrid termination design is shown in Fig.2 and was optimised for the 3.3 kV JBS diodes. This comprised of P+ floating rings comprising (75 µm total width, 200 nm depth,  $3 \times 10^{19}$  cm<sup>-3</sup> box profile doping) and multiple floating JTE rings (75 µm total width, 500 nm depth,  $2 \times 10^{17}$  cm<sup>-3</sup> box profile doping), both utilising Al+ implants at 500°C. These same two implants were used to form the P region in the active area, shown in Fig.2 (left), to shift the electric field away from the substrate. Both devices were fabricated on a  $4 \times 10^{15}$  cm<sup>-3</sup> nitrogen-doped, 35  $\mu m$  thick 4H-SiC drift region, which was grown on highly n- doped substrates. The wafers were laser-cut into 2cm × 2cm chips, before they were cleaned using a standard RCA 1/HF (10%)/ RCA 2/ HF (10%) process. After performing both p-implants in the JBS diodes, they underwent post-implantation activation at 1,650°C for 45 minutes, followed by a sacrificial oxidation step at 1,300°C for 2 hours in nitrous oxide ambient. Both the Schottky and JBS diodes then underwent the P<sub>2</sub>O<sub>5</sub> deposition process at 1,000°C for 2 hrs in N<sub>2</sub> ambient, detailed in [4]. The P<sub>2</sub>O<sub>5</sub> was then removed in dilute HF (10%) before

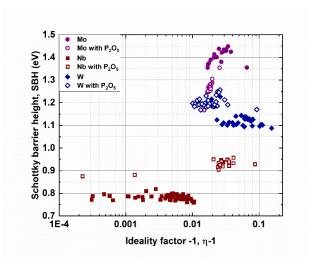

Figure 3: Ideality factors and SBHs for the Schottky diodes, measured between 1 x  $10^{-7}$  and 10 A cm<sup>-2</sup>.

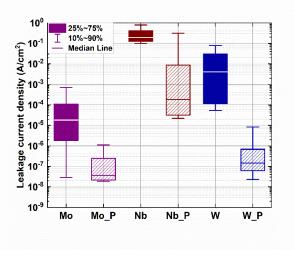

Figure 4: Leakage current densities of more than 100 devices each, measured at -200 V, for a device area of  $4.39 \times 10^4$  cm<sup>2</sup>.

a 1  $\mu$ m thick field oxide (silicon dioxide) was deposited. Ti (30 nm)/Ni (100 nm) ohmic contacts were then formed on the backside of the samples after an RTA at 1,000°C for 2 minutes in Ar (5 slm) ambient. In the next step, 100 nm thick Schottky contact metals (Mo, Nb or W) were deposited, then annealed at 500°C for 2 minutes. Finally, a 1  $\mu$ m thick Al metal overlay was evaporated on top of the Schottky contact to serve as a field plate, and to aid wire-bonding for switching tests.

#### III. SCHOTTKY DIODE ELECTRICAL RESULTS

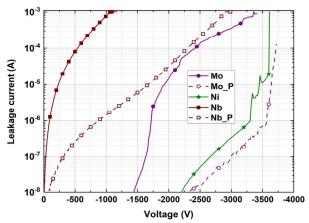

The rectifying characteristics of the unterminated W, Nb and Mo Schottky diodes were auto-probed at room temperature using a Keysight B1505A with a Semiprobe semi-automatic probe station. On-state parameters ideality factor ( $\eta$ ) and SBH were extracted for at least 50 devices (Fig. 3), each under the assumption that thermionic emission (TE) is the governing transport mechanism. The leakage current density ( $J_R$ ) up to -200 V was measured for at least 100 of each of the devices, shown in Fig. 4. Excellent rectifying characteristics appear across the entire dataset with a tight ideality factor distribution, shown in Table 1, with all datasets having a standard deviation of less than 0.04 A/cm².

The  $P_2O_5$ -treatment reduced the SBH of the Mo diodes to 1.26 eV, compared to 1.40 eV for the untreated Mo devices and a reduction in the median  $J_R$  of nearly  $500\times$ . Untreated Nb Schottky diodes have a very low average barrier height of 0.78 eV, which is increased using the  $P_2O_5$  treatment to 0.93 eV, bringing about a reduction in the median  $J_R$  by three orders of magnitude. Similarly, the  $P_2O_5$  treatment resulted in an increase in SBH from 1.12 to 1.20 eV for the W diodes, bringing about a reduction in leakage by over 4 orders of magnitude. Therefore, the  $P_2O_5$  treatment has differing effects on the SBH, with the barrier height increasing for W and Nb,

TABLE 1: Summary of measured barrier heights (average), ideality factors (average) and leakage current (median) measured at -200V. Device area for leakage current measurements is  $4.38 \times 10^{-4}$  cm<sup>2</sup>.

| Contact metal / treatment | SBH (eV)          | Ideality factor | J <sub>R</sub> at 200 V<br>(A/cm <sup>2</sup> ) |

|---------------------------|-------------------|-----------------|-------------------------------------------------|

| Mo                        | $1.409\pm0.033$   | $1.036\pm0.035$ | 1.835 x 10 <sup>-5</sup>                        |

| Mo + P                    | $1.264\pm0.036$   | $1.013\pm0.002$ | 3.715 x 10 <sup>-8</sup>                        |

| Nb                        | $0.782 \pm 0.012$ | $1.005\pm0.003$ | 0.195                                           |

| Nb + P                    | $0.928 \pm 0.022$ | $1.030\pm0.017$ | 1.850 x 10 <sup>-4</sup>                        |

| W                         | $1.126\pm0.035$   | $1.063\pm0.036$ | 4.120 x 10 <sup>-3</sup>                        |

| W + P                     | $1.200\pm0.021$   | $1.020\pm0.014$ | 1.460 x 10 <sup>-7</sup>                        |

yet going down in Mo. However, it appears that it has a consistent effect in lowering the leakage current. Given the magnitude of the leakage current reduction, and the fact that the Mo SBH actually reduced rather than increased, the reason for the leakage current reduction appear attributable to more than just the SBH. In [4], investigations into the interface showed that potential leakage paths were being filled by the  $P_2O_5$  treatment, and that the SiC subsurface may have been doped by the phosphorous. To investigate further, information on the band structures of the Schottky diodes was sought via x-ray photoelectron spectroscopy (XPS).

## IV. SCHOTTKY DIODE XPS INVESTIGATION

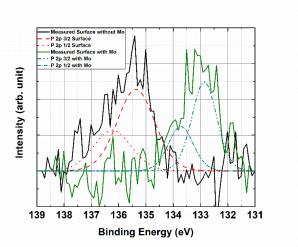

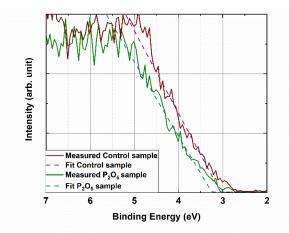

Four samples were prepared for XPS analysis with and without the P<sub>2</sub>O<sub>5</sub> treatment, both as a bare pre-metallised surface (2 samples) and fully fabricated Schottky diode with a Mo layer sufficiently thin (3-4 nm) to analyse the interface beneath it (2 samples). Core spectra were taken for Si 2p, C 1s, O 1s, P 2p and the valence band. The P 2p spectrum of Fig. 5 shows the chemical state of the phosphorus: The P<sub>2</sub>O<sub>5</sub>treated surfacereceived an HF oxide strip and no metal deposition and displays a P 2p 3/2 peak at 135.36 eV, indicating P<sub>2</sub>O<sub>5</sub>, whereas in the sample with the thin Mo/4H-SiC interface, it occurs at 132.86 eV. The bare P<sub>2</sub>O<sub>5</sub>-treated surface indicates that the phosphorus does not react with the SiC, but the shift after Mo metal deposition indicates that a chemical reaction occurs between the P and the Mo. The similarity to previously-reported metal phosphate spectra [12, 13] suggests that a Mo phosphate complex is formed at the interface. However, the valence band spectra, shown in Fig.6, determined a Fermi level of 3.05 eV above the valence band edge for the untreated surface and 3.25 eV for the P<sub>2</sub>O<sub>5</sub>-treated sample. This extremely high Fermi level indicates that the phosphorus still acts as an n-type dopant at the surface, giving it a degenerately n-doped surface/interface.

Figure 5 P2p region showing a  $P_2O_5$  peak for the  $P_2O_5$ -treated bare surface and for a Schottky sample with a 3-4 nm Mo layer.

Figure 6 Valence band extraction for a measured control sample and P2O5-treated sample including fits.

## V. 3.3 KV JBS DIODES – ELECTRICAL RESULTS

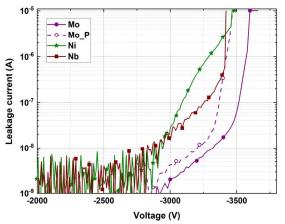

Fully optimised 1.56 mm<sup>2</sup> Nb and Mo JBS were measured up to 3.3 kV to investigate if the P<sub>2</sub>O<sub>5</sub>-treated diodes remained beneficial when subject to the high current and high electric fields of an industrially relevant power device structure. For benchmarking reasons, the results were compared to a Ni JBS diode of the same design. Firstly, the functionality of the termination design was tested by breakdown measurements of PiN diodes on the individual chips, eliminating the effect of barrier lowering on the leakage performance, hence showing

Figure 7 Leakage current measurement on PiN diodes (area is 1.56 mm²) at room temperature, up to 3,700 V.

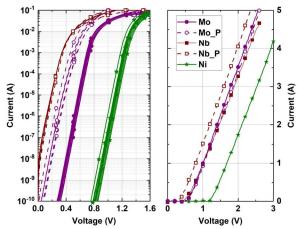

Figure 8, left, the exponential turn-on characteristics of the small JBS diodes (active area of 1.56 mm²). These results were used for the extraction of barrier heights and ideality factors (extracted for current values between 1 x 10<sup>-7</sup> and 10 A cm²) at room temperature. Right, static on-state characteristics of the large JBS diodes (active area of 42.25 mm²).

best possible leakage performance. As Fig. 7 shows, the devices were able to successfully block voltages higher than 3.6 kV without an occurrence of premature breakdown. Leakage currents exceeded a current level of 1 x 10<sup>-7</sup> A only at voltages higher than 3 kV, proving the general applicability of the termination design irrespective of the surface treatment or Schottky contact metal.

Having successfully demonstrated the termination design using PiN diodes, the static characteristics of the JBS diodes could now be measured. Exponential on-state characteristics of small (active area of 1.56 mm<sup>2</sup>) JBS diodes can be seen in in Fig. 8, while all the results are summarized in Table 2. A reduction of barrier height due to P2O5 treatment is evident once more for the Mo devices, those with the treatment having an average SBH of 0.86 eV, 0.3 eV lower than the average untreated diode SBH. The treatment had a more minor effect on the Nb diodes, where the treated devices had an average SBH of 0.84 eV, an increase of 0.03 eV compared to the untreated devices. Fig. 8 also shows the static oncharacteristics of the large (active area of 42.25 mm<sup>2</sup>) JBS diodes up to 5 A. The Nb and Mo diodes were fairly consistent, turning on after 0.5 V. A similar specific onresistance (R<sub>ON,SP</sub>) could be extracted across the entire dataset from 15 m $\Omega$  cm<sup>2</sup> (Mo,Ni) to 17 m $\Omega$  cm<sup>2</sup> (Mo + P<sub>2</sub>O<sub>5</sub>), to 18  $m\Omega$  cm<sup>2</sup> for the Nb devices. This is consistent with previously reported Ni 3.3 kV JBS diodes [14], which had a Ron, sp of 12 mΩ cm<sup>2</sup>. These results showed that the impact of the  $P_2O_5$ treatment on barrier height lowering/ increase, is consistent with the results in section III. The high current results do not suggest a large advantage to using the treatment, but they

TABLE 2: Summary of measured barrier heights (average), ideality factors (average) and reverse blocking (typical) measured at 1  $\mu$ A for 1.56 mm² JBS diodes.  $R_{ON,SP}$  for 42.25 mm² JBS diodes.

| Contact metal / treatment | SBH (eV)        | Ideality factor | $V_R$ at 1 $\mu A$ $(V)$ | $\frac{R_{ON,SP}}{(m\Omega cm^2)}$ |

|---------------------------|-----------------|-----------------|--------------------------|------------------------------------|

| Mo                        | $1.15\pm0.03$   | $1.03\pm0.04$   | 1720                     | 15                                 |

| Mo + P                    | $0.86 \pm 0.05$ | $1.04 \pm 0.01$ | 3560                     | 17                                 |

| Nb                        | 0.81 (typical)  | 1.07 (typical)  | 100                      | 18                                 |

| Nb + P                    | $0.84 \pm 0.06$ | $1.02\pm0.01$   | 900                      | 18                                 |

| Ni                        | $1.50 \pm 0.04$ | $1.04 \pm 0.02$ | 3300                     | 15                                 |

Figure 9 Leakage current measurements, up to 3,800V. Measurements were carried out at room temperature. The device area is 1.56 mm<sup>2</sup>.

show no detriment, which is important given the impact the treatment has on the off-state characteristics.

The off-state characteristics of selected 'average' 1.56 mm<sup>2</sup> JBS diodes are depicted in Fig. 9. Once the leakage current has exceeded the noise base of the equipment, barrier lowering can be seen which causes a steady increase in leakage with voltage in all shown devices. A general correlation can be seen between the SBH extracted from the on-state characteristics and the breakdown voltage and leakage current profiles: Using a leakage currents of 1 µA as a limit, the Ni devices reach this at 3300 V, the untreated Mo device at 1720 V and the untreated Nb at just 100 V. However, the most significant outcome of these results is the impact of the P<sub>2</sub>O<sub>5</sub> treatment, which boosts the Mo voltage to 3560 V, and the Nb to 900 V. These results suggest that the SBH formed by the Nb diodes is likely too small to be a realistic prospect for 3.3 kV diodes. However, the SBH of the Mo+P devices appears to be high enough to support the rated voltage, despite evidence that the Mo phosphate barrier may be lower than the pure Mo. This, we suggest, is due to the effects previously reported [4], that the P<sub>2</sub>O<sub>5</sub> treatment terminates potential leakage paths at the SiC surface. This suggests that to utilize Mo as a contact metal in SiC, a P<sub>2</sub>O<sub>5</sub> treatment is useful in order to minimize leakage and maximise breakdown voltage, actions that allow the scaling of the technology to

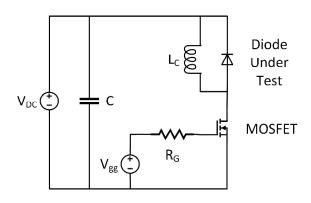

Figure 10 Circuit diagram of the clamped inductive switching rig with  $V_{DC}-DC$  Power supply,  $R_{\rm G}$  - gate resistor,  $I_{\rm G}$  - gate current,  $L_{\rm C}-$  Inductor.

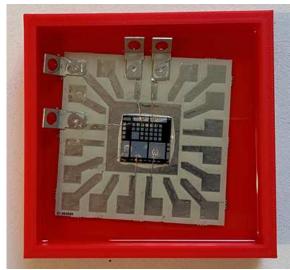

Figure 11 Chip prototype package for the double-pulse switching test. The substrate of the bare die was connected to the IMS board using conductive silver paste. The terminals were soldered onto the board after wire bonding. Then, the whole board was covered with silicone gel, after having been placed in a 3D-printed box.

large current ratings, without exceeding industry standard offstate leakage targets (typically 1 mA at the rated voltage).

Both the static on- and off-state results confirm the trends which could be seen on unterminated device structures in chapter III, proving the general applicability of the  $P_2O_5$  treatment on optimised and multi-implanted power device structures.

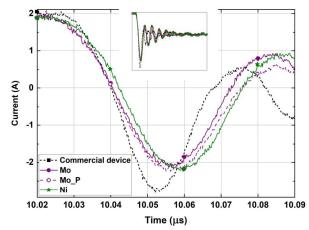

# VI. DOUBLE PULSE SWITCHING TEST

The dynamic switching characteristics of the SiC JBS diodes were tested using a clamped inductive switching circuit ([15-19]). The circuit schematic of the test rig is shown in Fig.10, whilst the final packaging prototype can be seen in Fig.11. Since the leakage performance of the Nb JBS diodes was poor, this was only measured on the Mo (with and without  $P_2O_5$  treatment) and the Ni JBS diodes. In the testing rig, the switching events are dominated by the low side transistor, which are then responded to by the high side JBS diode. The switching rate of the bottom side MOSFET events were varied by altering the gate resistance  $R_G$ , hence varying the RC time constant.

A 1200V/20 A SiC MOSFET was used as a switching device. The commonly used double-pulse switching setup was implemented, in which the first pulse is used to charge the inductor, whilst the second pulse is deployed to record the turn-on and turn-off behaviour of both devices. For the purpose of this investigation, measurements were carried out at room temperature only, using a  $V_{\rm DC}$  of 500 V and a gate resistance of 18  $\Omega$ . Measurements could not be carried out at rated voltage due to limitations of the electric rig, but are intended to serve as a precursor to verify the general switching characteristics of the design.

The same JBS diodes (active area of  $1.56~\text{mm}^2$ ) that had undergone static characterisation were used. To enable connection to the testing rig, each chip was placed on an insulated metal substrate (IMS) board, where its 2  $\mu$ m thick Al anode pad metal was bonded to the outer metal pads on the board, before the terminals were soldered to the board. To avoid arcing, the board was then placed in a 3D-printed package, which was filled with silicone gel and left to cure at

Figure 12 Turn-off characteristic of the measured devices. Measurements were taken at room temperature using a  $V_{DC}$  of 500 V and  $R_{\rm G}$  of 18  $\Omega.$  In the inset, the entire turn-off waveforms are shown.

room temperature overnight. Fig. 11 shows the final layout of the devices which were tested in the switching rig.

In Fig. 12., the turn-off characteristic of the JBS diodes at rated current (2 A) are shown. For the purposes of benchmarking, this was compared to a commercially available and already packaged 1,700 V JBS diode with slightly higher current rating (5A). With the configuration, a moderate current fall rate (dI/dt) of approximately 150 A/µs could be achieved for the commercial device, which was about 40 A/µs faster than for any of the measured Mo diodes, with the Ni device showing the slowest response of all measured devices. For the commercial devices, this comes at the expense of a slightly higher reverse recovery current (I<sub>RR</sub>) of 2.82 A. All the 3.3 kV JBS devices had I<sub>RR</sub> values of approximately 2.2 A. The higher switching rates of the commercial device (probably due to a difference in package) in combination with the also increased reverse recovery current resulted in similar extracted charge (Q<sub>R</sub>) values of approximately 78 nC for all measured devices.

## CONCLUSION

The application of a phosphorous pentoxide treatment consistently lowered leakage current levels of Mo, W, and Nb SBDs, with the treated W devices showing the most significant reduction of four orders of magnitude. In the Mo devices, the treatment resulted in a lower Schottky barrier height, as extracted by the forward I-V characteristics. However, the same process increased the SBH of the W and Nb treated devices compared to the untreated devices. XPS analysis on the Schottky interface revealed the formation of a metal-phosphorus-oxygen complex at the Schottky interface. Put together, this suggests that the metal phosphate that forms with Mo has a lower work function that the original, resulting in the lower SBH, whereas in the W and Nb, the resulting phosphate has a higher work function greater than the original metal. XPS also revealed that the P2O5 treatment appears to heavily n-type dope the Schottky subsurface (<50 nm), given an increase in the valence band to fermi level offset to 3.25 eV.

For the fully realized 3.3 kV PiN diodes, the functionality of the hybrid termination was proven with breakdown voltages exceeding 3,500 V on all measured devices. The on-state of the JBS diodes was then characterised, where the same

impact of the surface passivation treatment on barrier heights and ideality factors could be seen. All the large area devices had a  $R_{\rm SP,\,ON}$  between 15-17 m $\Omega cm^2$ . Most significantly, off-state characterisation of the JBS diodes revealed a reduction in leakage current levels and the maximization of the breakdown voltage in the  $P_2O_5$ -treated samples, with the Mo treated device showing leakage currents below 1 x  $10^{-6}$  A up to 3,560 V. The Nb devices had extreme leakage at low reverse voltage, so only dynamic charactictics of the Mo and Ni devices were then measured using a clamped inductive switching circuit at room temperature. No difference was evident between the devices, their switching performance all similar to that of a commercial 1.7 kV diode, all devices having  $Q_R$  values of approximately 78 nC.

In summary, Mo appears to be an appropriate low work function metal that could be used to realise SiC JBS diodes rated at 3.3 kV and above with low on-state losses. However, through a combination of effects, namely manipulating the metal work function, doping the subsurface and terminating defects, a phosphorous pentoxide treatment is an essential step in minimising the off-state leakage, such that the optimal breakdown voltage can be reached. While  $P_2O_5$  treatment also benefits the Nb and W diodes, the resulting SBHs are respectively too low (causing early onset leakage current) and too high (resulting in large on-state losses), compared to the  $P_2O_5$  treated Mo devices.

#### ACKNOWLEDGMENT

The work presented in this paper was carried out as part of the Engineering and Physical Sciences Research Council (EPSRC) funded Project EP/R00448X/1, and Innovate UK funded TRASiCA project, no. 102897. We gratefully acknowledge the advice and support of Brian Doherty from CuttingEdge Ions related to the SiC implants, and Dr. Mark Crouch and Corinne Maltby for their support during device fabrication.

## REFERENCES

- [1] F. Roccaforte, P. Fiorenza, G. Greco, R. Lo Nigro, F. Giannazzo, M. Saggio, "Emerging trends in wide band gap semiconductors (SiC and GaN) technology for power devices," *Microelectronic Engineering*, vol. 187, pp. 66-77, 2018.

- [2] F. Roccaforte, G. Brezeanu, P. Gammon, F. Giannazzo, S. Rascunà, and M. Saggio, "Schottky Contacts to Silicon Carbide: Physics, Technology and Applications," Advancing Silicon Carbide Electronics Technology, I: Metal Contacts to Silicon Carbide: Physics, Technology, Applications, 2018.

- [3] R. Rupp, R. Elpelt, R. Gerlach, R. Schömer, and M. Draghici, "A new SiC diode with significantly reduced threshold voltage," 2017 29th International Symposium on Power Semiconductor Devices and IC's (ISPSD), pp. 355-358, 2017.

[4] A.B. Renz, V.A. Shah, O.J. Vavasour, Y. Bonyadi, F. Li, P.M.

- [4] A.B. Renz, V.A. Shah, O.J. Vavasour, Y. Bonyadi, F. Li, P.M. Gammon, "The improvement of Mo/4H-SiC Schottky diodes via a P<sub>2</sub>O<sub>5</sub> surface passivation treatment," *Journal of Applied Physics*, vol. 127, no. 2, p. 025704, 2020.

- [5] L. Stöber, J. Konrath, F. Patocka, M. Schneider, and U. Schmid, "Controlling 4H–SiC Schottky barriers by molybdenum and molybdenum nitride as contact materials," *IEEE Transactions on Electron Devices*, vol. 63, no. 2, pp. 578-583, 2015.

- [6] G. Bellocchi, M. Vivona, C. Bongiorno, S. Rascuna and F. Roccaforte, "Barrier Height Tuning in Ti/4H-SiC Schottky diodes," *Solid-State Electronics*, vol. 186, p. 108042, 2021.

- [7] V.E. Gora, A. Chawanda, C. Nyamhere, F.D. Auret, F. Mazunga and S.M. Tunhuma, "Comparison of nickel, cobalt, palladium, and tungsten Schottky contacts on n-4H-silicon carbide," *Physica B: Condensed Matter*, vol. 535, pp. 333-337, 2018.

- [8] M. Vivona, G. Greco, G. Bellocchi, L. Zumbo, M. Saggio and F. Roccaforte, "Electrical properties of inhomogeneous tungsten carbide Schottky barrier on 4H-SiC," *Journal of Physics D: Applied Physics*, vol. 54, no. 5, p. 055101, 2020.

- [9] L. Knoll, V. Teodorescu, and R. Minamisawa, "Ultra-thin epitaxial tungsten carbide Schottky contacts in 4H-SiC," *IEEE Electron Device Letters*, vol. 37, no. 10, pp. 1318-1320, 2016.

- [10] M. Hara, M. Kaneko, and T. Kimoto, "Nearly Fermi-level-pinning-free interface in metal/heavily-doped SiC Schottky structures," *Japanese Journal of Applied Physics*, vol. 60, no. SB, p. SBBD14, 2021.

- [11] M. Vivona, G. Greco, M. Spera, P. Fiorenza, F. Giannazzo and F. Roccaforte, "Ni Schottky barrier on heavily doped phosphorous implanted 4H-SiC," arXiv preprint, 2102.08927, In Press, 2021.

- [12] D. Clark, T. Fok, G. Roberts, and R. Sykes, "An investigation by electron spectroscopy for chemical analysis of chemical treatments of the (100) surface of n-type InP epitaxial layers for Langmuir film deposition," *Thin Solid Films*, vol. 70, no. 2, pp. 261-283, 1980.

- [13] P. H. Lo, W. T. Tsai, J. T. Lee, and M. P. Hung, "The electrochemical behavior of electroless plated Ni - P alloys in concentrated NaOH solution," *Journal of the Electrochemical Society*, vol. 142, no. 1, p. 91, 1995.

- [14] Y. Pan, L. Tian, H. Wu, Y. Li, and F. J. M. E. Yang, "3.3 kV 4H-SiC JBS diodes with single-zone JTE termination," Microelectronic Engineering, vol. 181, pp. 10-15, 2017.

- [15] B.A. Hull, J.J. Sumakeris, M.J. O'Loughlin, Q. Zhang, J. Richmond and A.R. Hefner, "Performance and stability of large-area 4H-SiC 10-kV junction barrier Schottky rectifiers," *IEEE Transactions on Electron Devices*, vol. 55, no. 8, pp. 1864-1870, 2008.

- [16] J. Qi, X. Yang, X. Li, K. Tiang, K. Wang and M. Yang, "Temperature Dependence of 1.2 kV 4H-SiC Schottky Barrier Diode for Wide Temperature Applications," 2019 IEEE 10th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), pp. 822-826, 2019.

- [17] M. Adamowicz, S. Giziewski, J. Pietryka, and Z. Krzeminski, "Performance comparison of SiC Schottky diodes and silicon ultra fast recovery diodes," in 2011 7th International Conference-Workshop Compatibility and Power Electronics (CPE), 2011: IEEE, pp. 144-149.

- [18] A. Kumar, K. Vechalapu, S. Bhattacharya, V. Veliadis, E. Van Brunt and B. Hull, "Effect of capacitive current on reverse recovery of body diode of 10kV SiC MOSFETs and external 10kV SiC JBS diodes," 2017 IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), pp. 208-212, 2017

- [19] Y. Jiang, W. Sung, X. Song, H. Ke, S. Lui and E. Van Brunt, "10kV SiC MPS diodes for high temperature applications," 2016 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), pp. 43-46, 2016.