# Kent Academic Repository

# Full text document (pdf)

# **Citation for published version**

Wright, Daniel, Batty, Mark and Dongol, B (2021) Owicki-Gries Reasoning for C11 Programs with Relaxed Dependencies. In: Formal Methods 2021.

# DOI

# Link to record in KAR

https://kar.kent.ac.uk/95154/

# **Document Version**

Updated Version

# Copyright & reuse

Content in the Kent Academic Repository is made available for research purposes. Unless otherwise stated all content is protected by copyright and in the absence of an open licence (eg Creative Commons), permissions for further reuse of content should be sought from the publisher, author or other copyright holder.

# Versions of research

The version in the Kent Academic Repository may differ from the final published version. Users are advised to check http://kar.kent.ac.uk for the status of the paper. Users should always cite the published version of record.

# Enquiries

For any further enquiries regarding the licence status of this document, please contact: **researchsupport@kent.ac.uk**

If you believe this document infringes copyright then please contact the KAR admin team with the take-down information provided at http://kar.kent.ac.uk/contact.html

# Owicki-Gries Reasoning for C11 Programs with Relaxed Dependencies (Extended Version)\*

Daniel Wright<sup>1</sup>, Mark Batty<sup>1</sup>, and Brijesh Dongol<sup>2</sup>

<sup>1</sup> University of Kent <sup>2</sup> University of Surrey

**Abstract.** Deductive verification techniques for C11 programs have advanced significantly in recent years with the development of operational semantics and associated logics for increasingly large fragments of C11. However, these semantics and logics have been developed in a restricted setting to avoid the *thin-air-read* problem. In this paper, we propose an operational semantics that leverages an intra-thread partial order (called *semantic dependencies*) induced by a recently developed denotational event-structure-based semantics. We prove that our operational semantics is sound and complete with respect to the denotational semantics. We present an associated logic that generalises a recent Owicki-Gries framework for RC11 (repaired C11), and demonstrate the use of this logic over several example proofs.

### 1 Introduction

Significant advances have now been made on the semantics of (weak) memory models using a variety of axiomatic (aka declarative), operational and denotational techniques. Several recent works have therefore focussed on logics and associated verification frameworks for *reasoning* about program executions over weak memory models. These include specialised separation logics [9, 11, 15, 26] and adaptations of classical Owicki-Gries reasoning [7, 17]. At the level of languages, there has been a particular focus on C11 (the 2011 C/C++ standard).

Due to the complexity of C11 [4], many reasoning techniques have restricted themselves to particular fragments of the language by only allowing certain types of memory accesses and/or reordering behaviours. Several works (e.g., [7,10,15,17]) assume a memory model that guarantees that program order (aka sequenced-before order) is maintained [18]. While this restriction makes the logics and proofs of program correctness more manageable, it precludes reasoning about observable executions displaying certain real-world phenomena, e.g., those exhibited by the load-buffering litmus test under Power or ARMv7.

<sup>\*</sup> We thank Simon Doherty for discussions on an earlier version of this work. Wright is supported by VeTSS. Batty is supported by EPSRC grants EP/V000470/1 and EP/R032971/1, and the Royal Academy of Engineering. Dongol is supported by EPSRC grants EP/V038915/1, EP/R032556/1, EP/R025134/2, VeTSS and ARC Discovery Grant DP190102142.

```

Init: x = y = r1 = r2 = 0

Thread 1

1: r1 := [x]

2: [y] := r1+1

{r1 \in \{0,1\}}

{r1 \neq 1 \lor r2 \neq 1}

```

**Fig. 1.** Load-buffering with a semantic dependency

```

Init: x = y = r1 = r2 = 0

Thread 1

1: r1 := [x]

2: [y] := r1

\{r1 = 0\}

\{r1 = r2 = 0\}

```

Fig. 2. Load-buffering with two dependencies

Load buffering and the thin air problem. C11 suffers from the out of thin air problem [5], where the language does not impose any ordering between a read and the writes that depend on its value. The intention is to universally permit aggressive compiler optimisation, but in doing so, this accidentally allows writes to take illogical values. The ARM and Power processors allow the relaxed outcome r1 = 1 and r2 = 2 in Fig. 1, where there is nothing to enforce the order of the load and store in the second thread [25]. In Fig. 2, each thread reads and then writes the value read – a data dependency from read to write. This dependency makes optimisation impossible, so the relaxed outcome r1 = r2 = 1 is forbidden on every combination of compiler and target processor. C++ erroneously allows the outcome r1 = r2 = 1, producing the value 1 "out of thin air".

Formally handling load buffering while avoiding out of thin air behaviours turns out to be an enormously complex task. Although several works [6, 14, 16, 19, 23] have been dedicated to providing semantics for different variations of the load buffering example, many of these have also been shown to be inconsistent with expected behaviours under certain litmus tests [13,23]. This work builds on top of the recent MRD (Modular Relaxed Dependencies) semantics by Paviotti et al [23]. MRD avoids thin air, and aims for compatibility with the existing ISO C and C++ standards.

A key component of MRD is the calculation of a *semantic dependency relation*, which describes when certain reorderings are disallowed. The program in Fig. 1 contains only the semantic dependency between lines 1 and 2, whereas the program in Fig. 2 contains semantic dependencies between lines 1 and 2, and lines 3 and 4. The program in Fig. 1 may therefore execute line 4 before line 3, while the program in Fig. 2 must execute both threads in order.

Contributions. Although precise, there is currently no direct mechanism for reasoning about programs under MRD because MRD is a denotational semantics defined over an event structure [27]. This paper addresses this gap by developing an operational semantics for MRD, which we then use as a basis for a deductive Owicki-Gries style verification framework. The key idea of our operational semantics is to take the semantic dependency relation as the only order in which programs must be executed, thereby allowing intra-thread reordering. This changes the fundamental meaning of sequential composition, allowing statements that occur "later" in the program to be executed early.

Our semantics is also designed to take non multi-copy atomicity into account, whereby writes are not propagated to all threads at the same time and hence

$\mathbf{2}$

may appear take effect out-of-order [1,2]. Note that this phenomenon is distinct from the reordering of operations within a thread (described above), and it is possible to separate the two. Here, we adapt the operational model of weak memory effects by Doherty et al [10] so that it follows semantic dependency rather than the more restrictive thread order used in earlier works [7, 10, 15, 17].

Finally, we develop a logic capable of reasoning about program executions that exhibit both of the phenomena described above. Our logic makes use of the technique by Dalvandi et al [7] of including assertions that enable reasoning about the "views" of each thread. Since we have concurrent programs, the logic we develop incorporates Owicki-Gries style reasoning for programs, in which assertions are shown to be both locally correct and globally stable (interference free). However, unlike earlier works [7,17], since we relax thread order, the standard approach to Hoare-style proof decomposition is not possible.

*Overview.* This paper is organised as follows. We recap MRD in Section 2 and an operational semantics for RC11 in Section 3. Then in Section 4, we present a combined semantics, where program order in RC11 is replaced by a more relaxed order defined by MRD. A Hoare-like logic for reasoning about relaxed program execution together with Owicki-Gries-like rules for reasoning about interference is given in Section 5. We present an example proof in Section 6.

## 2 MRD and semantic dependencies

In this section, we review the MRD semantics for a simple C-like while language. This provides a mechanism for defining (in a denotational manner) a relaxed order in which statements within a thread are executed, which precludes development of a program logic.

Events and actions Weak memory literature uses a variety of terminology to refer to internal representations of changes to global memory, which complicates attempts to unify multiple models. In the following, we use *events* to refer to the objects created and manipulated by MRD, normally represented as integers. We use *actions* to refer to objects of the form  $i: \mathbb{R} x v$ ,  $i: \mathbb{W} x v$ , referring to a read or write of value v at global location x arising from line i of the input program.

Program syntax. We assume shared variables x, y, z, ... from a set X, registers  $r_1, r_2, ...$  from a set Reg, and register files  $\rho : Reg \to Val$  mapping registers to values from a set Val. Expressions  $e, e_1, e_2, ...$  are taken from a set E, whose syntax we do not specify, but which can be evaluated w.r.t. a register file using  $eval \in E \times (Reg \to Val) \to Val$ . Thus,  $eval(e, \rho)$  is the value of e given the register values in  $\rho$ . For basic commands, we have variable assignments (or stores) [y] := e and register assignments (or loads) r := [x]. In this paper, we assume that stores and loads are relaxed [3,10,18] unless they are explicitly specified to be a releasing store (denoted  $[y] :=^R e$ ) or an acquiring load (denoted  $r :=^A [x]$ ). Finally, we assume a simple language of programs. The only unconventional aspect of this language is that we require each (variable or register) assignment be

decorated with a unique *control label*. This allows a semantics which does not, in general, respect program order to refer to an individual statement without ambiguity. The syntax of commands (for a single thread) is defined by the following grammar, where B is an expression that evaluates to a boolean and i is a control label. Note that since guards are expressions, they must not mention any shared variables — any guard that relies on a shared memory variable must load its values into a local register prior to evaluating the guard.

ACom ::= i: skip | i:  $[x] := {R | e | i : r := {R | [x] | i : r := e}}$ Com ::= ACom | Com; Com | if B then Com else Com | while B do Com

We use  $[x] := {R \choose i} e$  to denote that the releasing annotation R is optional (similarly  $r := {A \choose i} [x]$  for the acquiring annotation A). For simplicity, we focus attention on the core atomic features of C11 necessary to probe the thin-air problem, and omit more complex instructions such as CAS, fences, non-atomic accesses and SC accesses [4].

We assume a top level parallel composition operator. Thus, a program is of the form  $C_1 || C_2 || \ldots || C_n$  where  $C_i \in Com$ . We further assume each atomic command ACom in the program has a unique label across all threads.

Denotational MRD. For the purposes of this paper (i.e., the development of the operational semantics and associated program logic), the precise details of the MRD semantics [23] are unimportant. The most important aspect that we use is the set of *semantic dependency* relations that it generates, which precisely characterise the order in which atomic statements are executed.

In MRD, the *denotation* of a program P is returned by the semantic interpretation function  $\llbracket P \rrbracket$ . This gives a *coherent event structure* of the form:

$$(L, S, \vdash, \leq)$$

where

- $-L = (E, \sqsubseteq, \#, Lab)$  is an *event structure* [27] equipped with a labelling function Lab from events (represented internally as integer identifiers) to actions. The set E contains all events in the structure,  $a_1 \sqsubseteq a_2$  for  $a_1, a_2 \in E$  iff  $a_1$  is program ordered before  $a_2$ . Events in # cannot happen simultaneously, e.g., two reads of a variable returning different values are in conflict.

- -S = (A, LK, RF, DP) is a set of *partial executions*, each of which represents a possible interaction of the program with the memory system. Each execution in S is a tuple of relations representing *lock/unlock order*, a *reads-from relation* and *dependency order* between operations of *that* execution, and the set of events to be executed. An execution is *complete* if every read in A is linked to a write to the same location of the same value by an RF edge.

- $\vdash$  is a *justification relation* used in the construction of the program's dependency relation.

- $\leq$  is the preserved program order (c.f., [2]), a subset of the program order of F that is respected by the memory model.

To develop our operational semantics, we only require some of these components. From S, we only require the dependency order. From the labelled event structure, we use the labelling function Lab to connect actions to events. From the coherent event structure, we use  $\leq$  to enforce ordering alongside dependency order.<sup>3</sup>

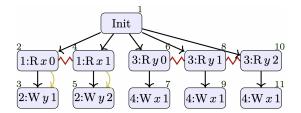

*Example 1.* The event structure in Fig. 3 represents the denotation of the program in Fig. 1. Note first that each store of a value into a register generates multiple events – one for each possible value. This is because MRD cannot make assertions about which values it may or may not observe during interpretation of the structure, it can only be provided with global value range restrictions prior to running. Instead, each read must indicate a write whose value it is observing during the axiomatic checks, subject to various coherence restrictions. A read will only appear in a *complete execution* if it can satisfy this requirement.

Events 2 and 4 are in *conflict* (drawn as a red zigzag) as they represent different potential values being read at line 1. Likewise, events 6, 8, and 10 represent different potential values at line 3. A single execution can observe events 2 and 6, but not events 2 and 4. Events 2 and 3 are in *program order* (represented by the black arrow). MRD generates a *dependency order* between events 2 and 3 and events 4 and 5 (represented by the yellow arrow). The read at line 1 is stored in register r1, which is in turn accessed by the write in line 2, leading to a data dependency. There is no semantic dependency between any events arising from lines 3 and 4, because there is no way for the value read at line 3 to influence the value written at line 4. This means that lines 1 and 2 must be executed in order, but line 4 is free to execute before line 3. For example, consider the traces  $H_1$  and  $H_2$  below.

$$\begin{array}{rcl} H_1 &=& {\rm Init} & 2{:}{\rm W}\,y\,1 & 4{:}{\rm W}\,x\,1 & 1{:}{\rm R}\,x\,1 & 3{:}{\rm R}\,y\,1 \\ H_2 &=& {\rm Init} & 1{:}{\rm R}\,x\,1 & 4{:}{\rm W}\,x\,1 & 2{:}{\rm W}\,y\,1 & 3{:}{\rm R}\,y\,1 \end{array}$$

For the program in Fig. 1, the trace  $H_1$  is *disallowed* since in  $H_1$ , the operations at lines 2 and 1 are swapped in a manner inconsistent with the dependency order. The trace  $H_2$  is *allowed*, since lines 3 and 4 are free to execute in any order.

## 3 Operational semantics with relaxed write propagation

To reason about the relaxed propagation of writes, Doherty et al [10] build an operational semantics that is equivalent to a declarative (aka axiomatic) semantics [18], which defines consistency of *tagged action graphs*. The operational semantics allows the stepwise construction of such graphs, in contrast to a declarative approach which only considers complete executions that are either accepted or rejected by the axioms of the memory model. We do not discuss

<sup>&</sup>lt;sup>3</sup> MRD also defines a set of axioms that describes when a particular execution is consistent with a denotation. We do not discuss these in detail here, but they are used in the soundness and completeness proofs.

Fig. 3. Coherent event structure for the program in Fig. 1

the declarative semantics here, focusing instead on the operational model, which we generalise in Section 4. We also note that like other prior works [15, 17, 18], the existing operational semantics [10] assumes program order within a thread is maintained.

Formally, tagged actions are triples (g, a, t), where g is a tag (uniquely identifying the action); a is a read or write action (potentially annotated as a releasing write or acquiring read), and t is a thread (corresponding to the thread that issued the action). We let TA be the set of all tagged actions,  $Wr, Wr_R, Rd, Rd_A \subseteq TA$  be the set of write, releasing write, read and acquiring reads, respectively. Note that Wr is the set of all writes, including those from  $Wr_R$  (similarly, Rd).

A tagged action graph is a tuple  $(D, \mathsf{sb}, \mathsf{rf}, \mathsf{mo})$  where D is a set of tagged actions, which may correspond to read or write actions, and  $\mathsf{sb}$ ,  $\mathsf{rf}$  and  $\mathsf{mo}$  are relations over D. Here,  $\mathsf{sb}$  is the sequenced before relation, where  $b_1 \mathsf{sb} b_2$  iff  $b_1$  and  $b_2$  are tagged actions of the same thread and  $b_1$  is executed before  $b_2$ .  $\mathsf{rf} \subseteq \mathsf{Wr} \times \mathsf{Rd}$  is the reads-from relation [2] relating each write to the read that reads from that write. Finally,  $\mathsf{mo} \subseteq \mathsf{Wr} \times \mathsf{Wr}$  denotes modification order (aka coherence order), which is the order in which writes occur in the system, and hence the order in which writes must be seen by all threads. Note that if  $b_1 \mathsf{mo} b_2$ , then  $b_1$  and  $b_2$  must act on the same variable. Moreover,  $\mathsf{mo}|x$  is a total order, where  $\mathsf{mo}|x$  is the relation  $\mathsf{mo}$  restricted to writes of variable x.

We assume tagged action graphs are initialised with writes corresponding to the initialisation of the program, and relations sb, rf and mo are initially empty.

Following Lahav et al [18], the so-called repairing or restricted C11 model (which is the model in [7, 10, 15]) instantiates sequence-before order to the *program order* relation [2]. This disallows statements within a thread from being executed out-of-order (although writes may be propagated to other threads in a relaxed manner). In Section 4, we present an alternative instantiation of **sb** using the semantic dependencies generated by MRD to enable out-of-order executions within a thread can be considered.

To characterise the operational semantics, we must define three further relations: *happens before*, denoted hb (which captures a notion of causality); *from read*, denoted fr (which relates each read to the write that overwrites the value read), and *extended coherence order*, denoted **eco** (which fixes the order of writes

$$READ \xrightarrow{b = (g, a, t)}{g \notin tags(D)} a \in \{i: R x n, i: R^{A} x n\} \\ (D, sb, rf, mo) w \in OW_{\sigma}(t) var(w) = x wrval(w) = n \\ (D, sb, rf, mo) \xrightarrow{b} (D \cup \{b\}, sb +_{D} b, rf \cup \{(w, b)\}, mo) \\ wruth b = (g, a, t) g \notin tags(D) a \in \{i: W x n, i: W^{R} x n\} \\ \sigma = (D, sb, rf, mo) w \in OW_{\sigma}(t) var(w) = x \\ (D, sb, rf, mo) \xrightarrow{b} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D, sb, rf, mo) \xrightarrow{b} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D, sb, rf, mo) \xrightarrow{b} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D, sb, rf, mo) \xrightarrow{b} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D, sb, rf, mo) \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D, sb, rf, mo) \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D, sb, rf, mo) \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D, sb, rf, mo) \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D, sb, rf, mo) \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D, sb, rf, mo) \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D, sb, rf, mo) \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D, sb, rf, mo) \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D, sb, rf, mo) \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D, sb, rf, mo) \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D \cup \{b\}, sb +_{D} b, rf, mo[w, b]) \\ READ \xrightarrow{c} (D \cup \{b\}, mo[w$$

Fig. 4. Memory semantics

and reads). Formally we have:

$$\mathsf{hb} = (\mathsf{sb} \cup (\mathsf{rf} \cap \mathsf{Wr}_R \times \mathsf{Rd}_A))^+ \qquad \mathsf{fr} = (\mathsf{rf}^{-1};\mathsf{mo}) \setminus Id \qquad \mathsf{eco} = (\mathsf{rf} \cup \mathsf{mo} \cup \mathsf{fr})^+$$

where Id is the identity relation, ; denotes relational composition, and + denotes transitive closure. Note that there is only a happens-before relation between a write-read pair related by rf if the write is releasing and the read is acquiring.

With these basic relations in place, we are now in a position to define the transition relation governing the operational rules for read and write actions. The rules themselves are given in Fig. 4. Assuming  $\sigma$  denotes the set of all tagged action graphs, each transition is a relation  $\longrightarrow \subseteq \Sigma \times TA \times \Sigma$ . We write  $\sigma \xrightarrow{b} \sigma'$  to denote  $(\sigma, b, \sigma') \in \cdots$ .

To accommodate relaxed propagation of writes, the semantics allows different threads to have different views of the system, formalised by a set of *observable* writes. These are in turn defined in terms of a set of *encountered writes*, denoted  $EW_{\sigma}(t)$ , which are the writes that thread t is aware of (either directly or indirectly) in state  $\sigma$ :

$$EW_{\sigma}(t) = \{ w \in \mathsf{Wr} \cap D_{\sigma} \mid \exists b \in D_{\sigma}. \ tid(b) = t \land (w, b) \in \mathsf{eco}_{\sigma}^?; \mathsf{hb}_{\sigma}^? \}$$

Here  $R^{?}$  is the reflexive closure of relation R and *tid* returns the thread identifier of the given tagged action. Thus, for each  $w \in EW_{\sigma}(t)$ , there must exist a tagged action b of thread t such that w is either eco-, hb- or eco; hb-prior to b. From these we determine the *observable writes*, which are the writes that thread t can observe in its next read. These are defined as:

$$OW_{\sigma}(t) = \{ w \in \mathsf{Wr} \cap D_{\sigma} \mid \forall w' \in EW_{\sigma}(t). \ (w, w') \notin \mathsf{mo}_{\sigma} \}$$

Observable writes are writes that are not succeeded by any encountered write in modification order, i.e., the thread has not seen another write overwriting the value being read.

We now describe each of the rules in Fig. 4. Relations rf and mo are updated according to the write actions in D that are observable to the thread t executing the given action. A read action b may read from any write  $w \in OW_{\sigma}(t)$ . In the post state, we obtain a new tagged action set  $D \cup \{b\}$ , sequenced-before relation

$$\frac{n = eval(e, \gamma(t)) \quad a = i:W^{[R]} x n}{(i: [x] :=^{[R]} e, \gamma) \xrightarrow{a}_{t} (\mathbf{skip}, \gamma)} \qquad \frac{a = i:R^{[A]} x n \quad \rho' = \gamma(t)[r := n]}{(i: r :=^{[A]} [x], \rho) \xrightarrow{a}_{t} (\mathbf{skip}, \gamma[t := \rho'])}$$

$$\frac{PROG}{(P, \gamma) \xrightarrow{a}_{t} (P[t := C], \gamma')} \qquad FULL \underbrace{(P, \gamma) \xrightarrow{a}_{t} (P', \gamma') \quad \sigma \xrightarrow{b}_{t} \sigma'}_{(P, (\sigma', \gamma'))}$$

Fig. 5. Interpreted operational semantics of programs (sample)

$\mathsf{sb} +_D b$  (defined below) and reads-from relation  $\mathsf{rf} \cup \{(w, b)\}$ . Relation mo is unmodified. Formally,  $\mathsf{sb} +_D b$  introduces b at the end of  $\mathsf{sb}$  for thread t:

$sb +_D b = sb \cup (\{b' \in D \mid tid(b') \in \{tid(b), 0\}\} \times \{b\})$

Note that we assume that initialisation is carried out by a unique thread with id 0, and that we require the set D as an input to cope with initialisation where **sb** may be empty for the given thread.

The write rule is similar except that it leaves rf unchanged and updates mo to mo[w, b]. Given that R[x] is the relational image of x in R, we define  $R_{\downarrow x} = \{x\} \cup R^{-1}[x]$  to be the set of all elements in R that relate to x (inclusive). The insertion of a tagged write action b directly after a w in **mo** is given by

$$\mathsf{mo}[w,b] = \mathsf{mo} \cup (\mathsf{mo}_{\Downarrow w} \times \{b\}) \cup (\{b\} \times \mathsf{mo}[w])$$

Thus, mo[w, b] effectively introduces b immediately after the w in mo.

The final component of the operational semantics is a set of rules that link the program syntax in Section 2 with the memory semantics. In prior work, this was through a set of operational rules that generate the actions associated with each atomic statement, combined with the rules in Fig. 4 to formalise the evolution of states. A sample of these rules for reads and writes from memory are given in Fig. 5. These are then lifted to the level of programs using the rules PROG and FULL, where the transition rule  $\stackrel{b}{\Longrightarrow}$  combines the thread-local semantics  $\stackrel{a}{\longrightarrow}_t$  and global-state semantics  $\stackrel{b}{\longrightarrow}$ . Note that we model parallel composition as functions from thread identifiers to commands, thus P[t := C] represents the program, where the command for thread t is updated to C.

The rules in [10] generate actions corresponding to program syntax (i.e.,  $\xrightarrow{a}_{t}$ ) in *program order*.<sup>4</sup> In this paper, we follow a different approach — the actions will be generated by (and executed in) the order defined by MRD. This therefore allows both reordering of program statements and relaxed write propagation.

# 4 Operational Semantics over MRD

Recall that the MRD semantic interpretation function  $\llbracket P \rrbracket$  outputs a coherent event structure  $\mu = (L, S, \vdash, \leq)$ . In this section, we develop an operational se-

<sup>&</sup>lt;sup>4</sup> We present the rules from [10] in Appendix A.

mantics for traversing  $\mu$ , while generating state configurations that model relaxed write propagation. In essence, this generalises the operational semantics in Section 3 so that threads are executed out-of-order, as allowed by MRD.

#### 4.1 Program Futures

Defining our operational semantics over raw syntax would force us to evaluate statements in program order. Therefore we convert this syntax into a set of atomic statements. We call this the *atomic set* of C, written  $\overline{C}$ . MRD evaluates while loops using step-indexing, treating them as finite unwindings of **if-thenelse** commands. For these, we generate a fresh unique label for each iteration of the while loop for each of the atomic commands within the loop body. Recall that the parallel composition of commands is modelled by a function from thread identifiers to (sequential) commands. The atomic set of a program P is therefore  $\lambda t$ .  $\overline{P(t)}$ .

To retain the ordering recognised during program execution, we introduce *futures*, which are sets of MRD events partially ordered by the semantic dependency and preserved program order relations. Essentially, instead of taking our operational steps in program order over the syntax, we can nondeterministically execute any statement which our futures tell us we have executed all necessary predecessors of.

For an execution S = (A, LK, RF, DP) of an event structure  $\mu$ , we can construct an initial future  $f = (A, \preceq)$ , where  $\preceq = DP \cup \leq_{|A|}$  and  $\leq_{|A|}$  is the preserved program order  $\leq$  (see Section 2) restricted to events in A. We say that an action a is available in a future  $(K, \preceq)$  iff there exists some event g with label a such that  $g \in K$  and g is minimal in  $\preceq$ , i.e., for all events  $g' \in K$ ,  $g' \not\preceq g$ . If a is available in f, then the future of a in f, denoted  $a \triangleright f$ , is the future

$$a \triangleright f \iff (K', \preceq_{|K'})$$

where  $K' = K \setminus \{g \mid \lambda_{\mu}(g) = a\}$

We lift this to a set of futures F to describe the *candidate futures of a in* F, denoted  $a \triangleright F$ :

$$a \triangleright F = \{a \triangleright f \mid f \in F \land a \text{ available in } f\}$$

Note that a is enabled in F iff  $a \triangleright F \neq \emptyset$ .

Essentially,  $a \triangleright F$  consumes an event g with label a from each of the futures in F provided a is available, discarding all futures in which a is not available. Intuitively, if an event is minimal in a program future then it may be executed immediately. If it is not minimal, its predecessors must be executed first.

### 4.2 Future-based Transition Relation

Our operational semantics is defined by the transition relation in FUTURE-STEP given below, which generalises FULL in Fig. 5. The transition relation is defined over  $(\overline{Q}, (\sigma, \gamma), F)$ , where  $\overline{Q}$  is the atomic set corresponding to the program text,  $(\sigma, \gamma)$  is a configuration and F is a set of *futures*. The rule generalises FULL in the obvious way, i.e., by evolving the configuration as allowed by  $\xrightarrow{(g,a,t)}$  and  $\xrightarrow{a}_t$  and consuming an available action a in F. Below, we use  $\uplus$  to denote disjoint union and f[k := v] to denote function updates where f(k) is updated to v.

$$\overline{Q}(t) = \overline{C} \uplus \{i: s\} \qquad a \triangleright F \neq \emptyset$$

FUTURE-STEP

$$\frac{(i:s,\gamma) \xrightarrow{a}_{t} (\mathbf{skip},\gamma') \qquad \sigma \xrightarrow{(g,a,t)} \sigma'}{(\overline{Q},(\sigma,\gamma),F) \xrightarrow{\mu} (\overline{Q}[t:=\overline{C}],(\sigma',\gamma'),a \triangleright F)}$$

Once a minimal action is chosen in a step of the operational semantics, it is checked for consistency and added to the set of executed events. The set of futures is pruned to remove the chosen event, and to exclude any futures that are incompatible with the chosen event. The operational semantics continues until it has consumed all of the futures.

The following theorem establishes equivalence of our operational semantics and the MRD denotational semantics. A proof is provided in the appendix.

**Theorem 1 (Soundness and Completeness).** Every execution generated by the MRD model can be generated by the operational semantics, and every final state generated by the operational semantics corresponds to a complete execution of the MRD semantics.

#### 4.3 Example

Recall the program in Fig. 1 and its event structure representation in Fig. 3. Let  $\Delta_S = \{(x, x) \mid x \in S\}$  be the diagonal of set S. We first derive our set of futures from this structure:

| $\{2 \prec 3, 6, 7\}$ | $\{2 \prec 3, 8, 9\}$ | $\{2 \prec 3, 10, 11\}$ |

|-----------------------|-----------------------|-------------------------|

| $\{4 \prec 5, 6, 7\}$ | $\{4 \prec 5, 8, 9\}$ | $\{4 \prec 5, 10, 11\}$ |

where  $\{2 \prec 3, 6, 7\}$  represents the future  $(\{2, 3, 6, 7\}, 2 \prec 3 \cup \Delta_{\{2,3,6,7\}})$ . The atomic set of the program is

$$\overline{P} = \begin{cases} 1 \mapsto \{1 : r1 := [x], 2 : [y] := r1 + 1\}, \\ 2 \mapsto \{3 : r2 := [y], 4 : [x] := 1\} \end{cases}$$

The initial configuration is  $(\sigma_0, \gamma_0)$ , where  $\sigma_0 = (\{(0_x, 0: W x 0, 0), (0_y, 0: W y 0, 0)\}, \emptyset, \emptyset, \emptyset)$  and  $\gamma_0 = \{1 \mapsto \{r1 \mapsto 0\}, 2 \mapsto \{r2 \mapsto 0\}\}$ , assuming the initialising thread has identifier 0.

To find out which events we can execute, we check our futures set. We cannot execute events 3 or 5, which both have pre-requisite events that have not yet been executed. These events are the only available events generated by line 2, so we cannot attempt to execute line 2. We can, however, execute any other line. Suppose we execute line 4, which corresponds to  $4 : [\mathbf{x}] := 1$  in  $\overline{P}(2)$ . To use the transition relation  $\stackrel{\mu}{\Longrightarrow}$ , we need to do the following: (1) determine the

corresponding action, a and new thread-local state using  $\xrightarrow{a}_{2}$ ; (2) generate a tagged action b = (g, a, 2) for a fresh tag g and a new global state using  $\xrightarrow{b}$ ; and (3) check that a is available in the current set of futures.

For (1), we can only create one action  $a = 4:W \times 1$  and the local state is unchanged. For (2), we generate a new global state using the WRITE rule in Fig. 4 (full details elided). For (3), we take our candidate futures  $a \triangleright F$  by examining which MRD events have the label 4:W  $\times 1$  — in this case events 7, 9, and 11. All futures can execute one of these events so the new future set contains all futures in F, each minus the set  $\{7, 9, 11\}$ .

## 5 Hoare Logic and Owicki-Gries Reasoning

Recall that the standard Owicki-Gries methodology [22] decomposes proofs of parallel programs into two cases:

- *local correctness* conditions, which define correctness of an assertion with respect to an individual thread, and

- non-interference conditions, which ensures stability of an assertion under the execution of statements in other threads.

The standard Owicki-Gries methodology has been shown to be applicable to a weak memory setting with relaxed write propagation (but without relaxed program order) [7]. Note that an alternative characterisation (also in a model without relaxed program order) has been given in [17].<sup>5</sup> Unfortunately, the unrestricted C11 semantics captured by MRD relaxes program order and hence sequential composition in order to allow behaviours such as those in Fig. 1, which requires a fundamental shift in Hoare-style proof decomposition. We show that the modular Owicki-Gries rules, for reasoning about concurrent threads remain unchanged.

Like Dalvandi et al [7], we assume assertions are predicates over state configurations. In the current paper, the operational semantics is dictated by the set of futures generated by MRD, thus we require two modifications to the classical meaning. First, like prior work [7], we assume predicates are over state configurations, which include (local) register files and (shared) event graphs. This takes into account relaxed write propagation. Second, we introduce Hoare-triples with futures generated by MRD, which takes into account relaxed program execution.

In the development below, we refer to the *preprocessed form* of a program P given by  $\mathcal{P}(P) = (\mu, \overline{P})$ , where  $\mu$  is the coherent event structure  $\llbracket P \rrbracket$  and  $\overline{P}$  the set normal form of P. We let  $F_{\mu}$  be the initial set of futures corresponding to  $\mu$ .

**Definition 1 (Hoare triple).** Suppose X and Y are predicates over state configurations, P is a concurrent program, and  $\mathcal{P}(P) = (\mu, \overline{P})$ . The semantics of a

<sup>&</sup>lt;sup>5</sup> This characterisation uses standard assertions but assumes a non-standard interpretation of Hoare-triples and introduces a stronger interference freedom check. In fact, for the model in [17], the introduction of auxiliary variables is unsound.

Hoare triple is given by  $\{X\}$  Init; P  $\{Y\}$ , where

$$\{X\} \text{ Init; } P \{Y\} \stackrel{\widehat{}}{=} (Init \Rightarrow X) \land \\ (\forall \mathbb{C}, \mathbb{C}'. \ X(\mathbb{C}) \land ((\overline{P}, \mathbb{C}, F_{\mu}) \stackrel{\mu}{\Longrightarrow}^{*} (\emptyset, \mathbb{C}', \emptyset)) \Rightarrow Y(\mathbb{C}') )$$

That is,  $\{X\} P \{Y\}$  holds iff for every pair of state configurations  $\mathbb{C}$ ,  $\mathbb{C}'$ , assuming  $X(\mathbb{C})$  holds and we execute  $\overline{P}$  with respect to the future  $F_{\mu}$  until  $\overline{P}$  terminates in  $\mathbb{C}'$ , we have  $Y(\mathbb{C}')$ .

Although Definition 1 provides meaning for a Hoare triple, we still require a method for decomposing the proof outline. To this end, we introduce the concept of a *future predicate*, which is a predicate parameterised by both futures and configuration states. To make use of future predicates, we introduce a notion of a Hoare triple for programs in set normal form.

For the definitions below, assume P is a program and  $\mathcal{P}(P) = (\mu, \overline{P})$ . We say an atomic set  $\overline{Q}$  is a *sub-program* of an atomic set  $\overline{P}$  iff for all  $t, \overline{Q}(t) \subseteq \overline{P}(t)$ . We say a set of futures F' is a *sub-future* of set of futures F iff for each  $f' \in F'$ there exists an  $f \in F$  such that f' is an up-closed subset of f. For example, if  $F = \{\{1 \prec 2, 3, 4\}, \{1 \prec 2, 3\}\}$ , then  $\{\{2, 4\}, \{1 \prec 2\}\}$  is a sub-future of F, but  $\{\{1, 3\}\}$  is not. We say the sub-program  $\overline{Q}$  corresponds to a sub-future Fiff  $labels(\overline{Q}) = labels(\{Lab_{\mu}[\pi_1 f] \mid f \in F\})$ , where we assume *labels* returns the set of all labels of its argument,  $\pi_1$  is the project of the first component of the given argument, and R[S] is the relational image of set S over relation R.

**Definition 2 (Hoare triple (single step)).** Suppose I and I' are future predicates, P is a program and  $\mathcal{P}(P) = (\mu, \overline{P})$ . If G is a sub-future of  $F_{\mu}$ , corresponding to a sub-program  $\overline{Q}$  of  $\overline{P}$ , we define

$$\{I\}_G \ \overline{Q} \ \{I'\}$$

$$\widehat{=} \ \forall \mathbb{C}, \mathbb{C}', G'. \ I(G)(\mathbb{C}) \land ((\overline{Q}, \mathbb{C}, G) \xrightarrow{\mu} (\overline{Q}', \mathbb{C}', G')) \ \Rightarrow \ I'(G')(\mathbb{C}')$$

We say I is *future stable* for  $(F, \overline{P})$  iff for all sub-futures G of F with corresponding sub-programs  $\overline{Q}$  of  $\overline{P}$ , we have  $\{I\}_G \overline{Q} \{I\}$ .

**Lemma 1 (Invariant).** Suppose X and Y are configuration-state predicates, P is a program and  $\mathcal{P}(P) = (\mu, \overline{P})$ . If  $X \Rightarrow I(F_{\mu}), I(\emptyset) \Rightarrow Y$  and I is future stable for  $(F_{\mu}, \overline{P})$ , then  $\{X\}$ Init;  $P\{Y\}$  provided Init  $\Rightarrow X$ .

By construction, the sets of futures corresponding to different threads are disjoint, i.e., for each future  $f \in F_{\mu}$ , we have that  $f = \bigcup_t f_{|t}$ , where  $f_{|t}$  denotes the future f restricted to events of thread t. The only possible inter-thread dependency in MRD is via the reads from relation [23], which does not contribute to the set of futures. This observation leads to a technique for an Owicki-Gries-like modular proof technique for decomposing the monolithic invariant I into an invariant per thread.

We define  $F_{|t} = \{f_{|t} \mid f \in F\}$ . Then, we obtain the following lemma for decomposing invariants in the same way as Owicki and Gries.

**Lemma 2** (Owicki-Gries). For each thread t, let  $I_t$  be a future predicate corresponding to t. If  $Init \Rightarrow X, X \Rightarrow \forall t. I_t(F_{\mu|t}), and \forall t. I_t(\emptyset) \Rightarrow Y$ , then  $\{X\}P\{Y\}$  holds provided both of the following hold.

1. For all threads t,  $I_t$  is future stable for  $(F_{\mu|t}, \overline{P})$ . (local correctness)

- 2. For all threads  $t_1$ ,  $t_2$  such that  $t_1 \neq t_2$ , sub-futures  $F_1$  of  $F_{\mu|t_1}$ , and  $F_2$  of

- $F_{\mu|t_2}$ , if  $\overline{Q}$  corresponds to  $F_2$ , then we have<sup>6</sup>  $\{I_{t_1}(F_1) \wedge I_{t_2}\}_{F_2} \overline{Q} \{I_{t_1}(F_1)\}.$ (global correctness)

Thus, we establish  $\{X\}P\{Y\}$  through a series of smaller proof obligations. We require that (1) the initialisation of the program guarantees X, (2) whenever X holds then for each thread t,  $I_t$  holds for the initial future  $F_{\mu|t}$ , (3) if  $I_t(\emptyset)$  holds for all t, then the post-condition Y holds, (4) each  $I_t$  is maintained by the execution of each thread, and (5)  $I_t$  at each sub-future of t is stable with respect to steps of another thread.

## 6 A Verification Example

With the verification framework now in place, we present a correctness proof for the program in Fig. 1. The program and invariant are given in Fig. 6. First, in Section 6.1, we present assertions for reasoning about state-configurations.

#### 6.1 View-based assertions

As we can see from Fig. 5, the states that we use are *configurations*, which are pairs of the form  $(\sigma, \gamma)$ , where  $\sigma$  is an tagged action graph representing the shared state and  $\gamma$  is mapping from threads to register files representing the local state. Like prior work [7], we use assertions that describe the *views* of each thread, recalling that due to relaxed write propagation, the views of each thread may be different. Note that the formalisation of a state in prior work is a time-stamp based semantics [7]. Nevertheless, the principles for defining thread-view assertions also carry over to our setting of tagged action graphs.

In this paper, the programs we consider are relatively simple, and hence, we only use two types of view assertions: synchronised view, denoted  $[x = v]_t$ , which holds iff both thread t observes the last write to x and this write updates the value of x to v, and possible view, denoted  $[x \approx v]_t$ , which holds iff t may observe a write to x with value v. Formally, we define

$$\begin{split} & [x=v]_t(\sigma,\gamma) \cong \exists w. \ OW_{\sigma}(t)_{|x} = \{w\} \land wrval(w) = v \\ & [x\approx v]_t(\sigma,\gamma) \cong \exists w \in OW_{\sigma}(t)_{|x}. \ wrval(w) = v \end{split}$$

where  $OW_{\sigma}(t)|x$  denotes the writes in  $OW_{\sigma}(t)$  restricted to the variable x. Recall that, by definition, for any state  $\sigma$  generated by the operational semantics, the

<sup>&</sup>lt;sup>6</sup> Technically speaking, each instance of  $I_{t_1}(F_1)$  in the Hoare-triple is a function  $\lambda x$ .  $I_{t_1}(F_1)$ .

Fig. 6. Proof outline for load buffering with semantic dependencies

last write to each variable in **mo** order is observable to every thread. Examples of these assertions in the context of an Owicki-Gries-style proof outline is given in Fig. 6.

#### 6.2 Example proof

To reduce the domain of our future predicate, we collapse the event-based futures used by the operational semantics into sets of label-based futures. An event future  $F_E$  can be converted into a label future  $F_L$  by applying the labelling function to all events in  $F_E$ . This makes the futures {3} and {5} equivalent, as both are instances of  $\{2:W \ y \ 2\}$ , thus  $I(\{3\}) = I(\{5\})$ . This isn't always a valid step, as some events which share labels may not be related by  $\leq$  in the same way. Thus, the technique can only be used if the label-based representation describes exactly the futures generated by MRD, which is the case for our example.

We describe our initial set of label futures as  $\{\{1_u < 2, 3_v, 4\} \mid u \in \{0, 1\} \land v \in \{0, 1, 2\}\}$ , using the notation  $\{i_v\}$  to refer to an action with the line number i with a read that returns the value v. We verify that this is a valid step: all futures generated by MRD are described by these labels, and they do not describe any potential futures not generated by MRD. We partition this into  $F = \{\{1_u < 2\} \mid u \in \{0, 1\}\}$  and  $G = \{\{3_v, 4\} \mid v \in \{0, 1, 2\}\}$  representing the future sets of threads 1 and 2, respectively. We let  $F_1 = \{\{2\}\}\}$  be the future set after executing line 1,  $G_3 = \{\{4\}\}\}$  be the future set after executing line 3 (reading some value for y), and  $G_4 = \{\{3_v\} \mid v \in \{0, 1, 2\}\}$  be the future set after executing line 4.

Our future predicate I must output a configuration predicate for every subfuture of the initial set. Our partitioning fully describes these sub-futures, so we now attach our assertions to these futures.

To simplify the visualisation, we interleave the future predicate components with the program to provide Hoare-style pre/post-assertions, and place the assertion above a line of code if that line of code is contained in the applied future. We use indentation to denote that an assertion applies to more than one future. In this example G contains both lines 3 and 4, hence both lines are indented

14

w.r.t. the first assertion in thread 2. We apply Lemma 2, and in the discussion below, we describe the local and global correctness checks.

For local correctness in thread 1, we must establish that  $\{I\}_F\{1,2\}\{I\}_{\emptyset}$ . By the definition of the future F, line 1 must be executed before line 2. This means we only need to verify that  $\{I\}_F\{1\}\{I\}_{F_1}$  and  $\{I\}_{F_1}\{2\}\{I\}_{\emptyset}$ , which is identical to a standard Hoare logic proof and relatively uninteresting.

In thread 2, no order is imposed between lines 3 and 4. This means to establish local correctness we must check that:

$$\begin{array}{l} - \{I\}_G \ 3: \ r2 \ := \ y \ \{I\}_{G_3} \\ - \{I\}_G \ 4: \ x \ := \ 1 \ \{I\}_{G_4} \\ - \{I\}_{G_3} \ 4: \ x \ := \ 1 \ \{I\}_{\emptyset} \\ - \{I\}_{G_4} \ 3: \ r2 \ := \ y \ \{I\}_{\emptyset} \end{array}$$

The first three are trivial: line 3 modifies neither x nor r1 and line 4 does not modify r1. For the final step, the first disjunct of  $\{I\}_{G_4}$  is the same as the first disjunct of  $\{I\}_{\emptyset}$ , and the second disjunct ensures that we cannot observe r2 = 1 after executing line 3.

For global correctness, we must check that every assertion in thread 1 continues to hold after every line of thread 2, and vice versa. These checks are also straightforward, so omit a detailed discussion. The only noteworthy aspect is that for line 3 (and similarly, line 4), our precondition is the conjunction  $\{I\}_{G_4} \wedge \{I\}_G$ , as both G and  $G_3$  are subfutures corresponding to line 3.

The proof described above has actually been encoded and checked using our existing Isabelle/HOL development [7,8] by manually encoding the re-ordering in thread 2. We aim to develop full mechanisation support as future work.

## 7 Related work

Work based on assumptions unsound in C++. Most logics for weak memory are based on simplifying assumptions that exclude thin air reads by ensuring program order is respected, even when no semantic dependency exists [7, 10, 11, 15, 17]. These assumptions incorrectly exclude the relaxed outcome of load buffering tests like Fig. 1, introducing unsoundness when applied to languages like C++: compiling Fig. 1 for an ARM processor produces code that does exhibit the relaxed behaviour. The logic of Lundberg et al [20] correctly discards many of this spurious program ordering, but it does not handle concurrency. We provide an operational semantics of C++ that solves the thin air problem, where prior attempts use simplifying assumptions like those of prior logics [7, 21].

Thin-air-free semantics. Each of the concurrency definitions that solves the outof-thin-air problem is remarkably complex [6,14,16,19,23,24], and so too is MRD. We choose to base our logic on MRD because MRD's semantic dependency relation hides much of the complexity of the model that calculates it. Where previously we would rely on program ordering, now we consider the semantic dependency provided by MRD. Logics for thin-air-free models. There are four logics built above concurrency models that solve the thin air problem: three of these are very simple and apply to only a handful of examples [13, 14, 16], and one is a separation logic built above the Promising Semantics [26]. Unfortunately, the Promising Semantics allows unwanted out-of-thin-air behaviour, forbidden by MRD [23], and as a result may not support type safety [13].

## 8 Conclusions and future work

The subtle behaviour of concurrent programs written in optimised languages necessitates good support for reasoning, but existing logics make unsound assumptions that rule out compiler optimisations, or use underlying concurrency models that admit out of thin air behaviour (see Section 7). We present a logic built above MRD. MRD has been recognised as a potential solution to the thin air problem in C and C++ by the ISO [12] and is the best guess at a C++ model that allows optimisation and forbids thin-air behaviours.

We follow a typical path for constructing a logic and start with an operational semantics that we show equivalent to MRD, and then as far a possible, follow the reasoning style of Owicki Gries. In each case, we diverge from a typical development because we cannot adopt program order into our reasoning system and instead must follow semantic dependency. Our logic supplants linear program order with a partial order, and where traditional pre- and post-conditions are indexed by the program counter, here we index them by their position in the partial order. This approach will work with any memory model that can provide a partially ordered structure over individual program actions.

The challenge in using the logic presented here is in managing the multitude of proof obligations that follow from the branching structure and lack of order in semantic dependency. This problem represents an avenue for further work: it may be possible to obviate the need for some of these additional proof obligations within the logic or to provide tools to more conveniently manage them.

### References

- Adve, S.V., Gharachorloo, K.: Shared memory consistency models: A tutorial. IEEE Computer 29(12), 66–76 (1996)

- Alglave, J., Maranget, L., Tautschnig, M.: Herding cats: Modelling, simulation, testing, and data mining for weak memory. ACM Trans. Program. Lang. Syst. 36(2), 7:1–7:74 (2014)

- Batty, M., Dodds, M., Gotsman, A.: Library abstraction for C/C++ concurrency. In: Giacobazzi, R., Cousot, R. (eds.) POPL. pp. 235–248. ACM (2013)

- Batty, M., Owens, S., Sarkar, S., Sewell, P., Weber, T.: Mathematizing C++ concurrency. In: Ball, T., Sagiv, M. (eds.) POPL. pp. 55–66. ACM (2011)

- Batty, M., Memarian, K., Nienhuis, K., Pichon-Pharabod, J., Sewell, P.: The problem of programming language concurrency semantics. In: Vitek, J. (ed.) ESOP. Lecture Notes in Computer Science, vol. 9032, pp. 283–307. Springer (2015), https://doi.org/10.1007/978-3-662-46669-8\_12

- Chakraborty, S., Vafeiadis, V.: Grounding thin-air reads with event structures. Proc. ACM Program. Lang. 3(POPL), 70:1–70:28 (2019), https://doi.org/10. 1145/3290383

- Dalvandi, S., Doherty, S., Dongol, B., Wehrheim, H.: Owicki-Gries reasoning for C11 RAR. In: Hirschfeld, R., Pape, T. (eds.) ECOOP. LIPIcs, vol. 166, pp. 11:1– 11:26. Schloss Dagstuhl - Leibniz-Zentrum für Informatik (2020), https://doi. org/10.4230/LIPIcs.ECOOP.2020.11

- Dalvandi, S., Dongol, B., Doherty, S.: Integrating Owicki-Gries for C11-style memory models into Isabelle/HOL. CoRR abs/2004.02983 (2020), https://arxiv. org/abs/2004.02983

- Dang, H., Jourdan, J., Kaiser, J., Dreyer, D.: Rustbelt meets relaxed memory. Proc. ACM Program. Lang. 4(POPL), 34:1–34:29 (2020), https://doi.org/10. 1145/3371102

- Doherty, S., Dongol, B., Wehrheim, H., Derrick, J.: Verifying C11 programs operationally. In: Hollingsworth, J.K., Keidar, I. (eds.) PPoPP. pp. 355–365. ACM (2019), https://doi.org/10.1145/3293883.3295702

- 11. Doko, M., Vafeiadis, V.: Tackling real-life relaxed concurrency with FSL++. In: ESOP. pp. 448–475 (2017)

- 12. Giroux, O.: ISO WG21 SG1 concurrency subgroup vote (2019), https://github. com/cplusplus/papers/issues/554, unanimously approved: OOTA is a major problem for C++, modular relaxed dependencies is the best path forward we have seen, and we wish to continue to pursue this direction

- Jagadeesan, R., Jeffrey, A., Riely, J.: Pomsets with preconditions: a simple model of relaxed memory. Proc. ACM Program. Lang. 4(OOPSLA), 194:1–194:30 (2020). https://doi.org/10.1145/3428262, https://doi.org/10.1145/3428262

- Jeffrey, A., Riely, J.: On thin air reads: Towards an event structures model of relaxed memory. Log. Methods Comput. Sci. 15(1) (2019), https://doi.org/10. 23638/LMCS-15(1:33)2019

- Kaiser, J., Dang, H., Dreyer, D., Lahav, O., Vafeiadis, V.: Strong logic for weak memory: Reasoning about release-acquire consistency in iris. In: ECOOP. pp. 17:1– 17:29 (2017)

- Kang, J., Hur, C., Lahav, O., Vafeiadis, V., Dreyer, D.: A promising semantics for relaxed-memory concurrency. In: Castagna, G., Gordon, A.D. (eds.) POPL. pp. 175–189. ACM (2017), http://dl.acm.org/citation.cfm?id=3009850

- Lahav, O., Vafeiadis, V.: Owicki-Gries reasoning for weak memory models. In: ICALP (2). LNCS, vol. 9135, pp. 311–323. Springer (2015)

- Lahav, O., Vafeiadis, V., Kang, J., Hur, C., Dreyer, D.: Repairing sequential consistency in C/C++11. In: Cohen, A., Vechev, M.T. (eds.) PLDI. pp. 618–632. ACM (2017)

- Lee, S., Cho, M., Podkopaev, A., Chakraborty, S., Hur, C., Lahav, O., Vafeiadis, V.: Promising 2.0: global optimizations in relaxed memory concurrency. In: Donaldson, A.F., Torlak, E. (eds.) PLDI. pp. 362–376. ACM (2020), https://doi.org/10. 1145/3385412.3386010

- Lundberg, D., Guanciale, R., Lindner, A., Dam, M.: Hoare-style logic for unstructured programs. In: de Boer, F., Cerone, A. (eds.) Software Engineering and Formal Methods (2020)

- Nienhuis, K., Memarian, K., Sewell, P.: An operational semantics for C/C++11 concurrency. In: OOPSLA. pp. 111–128. ACM (2016)

- 22. Owicki, S.S., Gries, D.: An axiomatic proof technique for parallel programs I. Acta Informatica 6, 319–340 (1976), https://doi.org/10.1007/BF00268134

- Paviotti, M., Cooksey, S., Paradis, A., Wright, D., Owens, S., Batty, M.: Modular relaxed dependencies in weak memory concurrency. In: Müller, P. (ed.) Programming Languages and Systems. pp. 599–625. Springer International Publishing, Cham (2020)

- Pichon-Pharabod, J., Sewell, P.: A concurrency semantics for relaxed atomics that permits optimisation and avoids thin-air executions. In: Bodík, R., Majumdar, R. (eds.) Proceedings of the 43rd Annual ACM SIGPLAN-SIGACT Symposium on Principles of Programming Languages, POPL 2016, St. Petersburg, FL, USA, January 20 - 22, 2016. pp. 622–633. ACM (2016). https://doi.org/10.1145/2837614.2837616, https://doi.org/10.1145/2837614.

- Podkopaev, A., Lahav, O., Vafeiadis, V.: Bridging the gap between programming languages and hardware weak memory models. Proc. ACM Program. Lang. 3(POPL), 69:1-69:31 (2019), https://doi.org/10.1145/3290382

- Svendsen, K., Pichon-Pharabod, J., Doko, M., Lahav, O., Vafeiadis, V.: A separation logic for a promising semantics. In: Ahmed, A. (ed.) ESOP. Lecture Notes in Computer Science, vol. 10801, pp. 357–384. Springer (2018), https://doi.org/10.1007/978-3-319-89884-1\_13

- Winskel, G.: Event structures. In: Brauer, W., Reisig, W., Rozenberg, G. (eds.) Petri Nets: Central Models and Their Properties, Advances in Petri Nets 1986, Part II, Proceedings of an Advanced Course, Bad Honnef, Germany, 8-19 September 1986. Lecture Notes in Computer Science, vol. 255, pp. 325–392. Springer (1986), https://doi.org/10.1007/3-540-17906-2\_31

18

$$\begin{array}{c} \displaystyle \frac{n = eval(e, \gamma) \quad a = \mathrm{i:W} \, x \, n}{(i: \, [x] := e, \gamma) \stackrel{a}{\longrightarrow}_{t} (\mathsf{skip}, \gamma)} & \displaystyle \frac{n = eval(e, \gamma) \quad a = \mathrm{i:W}^{R} \, x \, n}{(i: \, [x] :=^{R} e, \gamma) \stackrel{a}{\longrightarrow}_{t} (\mathsf{skip}, \gamma)} \\ \\ \displaystyle \frac{a = \mathrm{i:R} \, x \, n}{(i: \, r := [x], \gamma) \stackrel{a}{\longrightarrow}_{t} (\mathsf{skip}, \gamma[r := n])} & \displaystyle \frac{a = \mathrm{i:R}^{A} \, x \, n}{(i: \, r :=^{A} \, [x], \gamma) \stackrel{a}{\longrightarrow}_{t} (\mathsf{skip}, \gamma[r := n])} \\ \\ \displaystyle \frac{n = eval(e, \gamma)}{(i: \, r := e, \gamma) \stackrel{a}{\longrightarrow}_{t} (\mathsf{skip}, \gamma[r := n])} \\ \\ \displaystyle \frac{n = eval(e, \gamma)}{(i: \, r := e, \gamma) \stackrel{a}{\longrightarrow}_{t} (\mathsf{skip}, \gamma[r := n])} \\ \\ \hline \\ \displaystyle \frac{(C_{1}, \gamma) \stackrel{a}{\longrightarrow}_{t} (C'_{1}, \gamma')}{(C_{1}; C_{2}, \gamma) \stackrel{a}{\longrightarrow}_{t} (C'_{1}; C_{2}, \gamma')} \\ \\ \hline \\ eval(B, \gamma) = true \\ \hline \\ (\mathsf{if} \ B \ \mathsf{then} \ C_{1} \ \mathsf{else} \ C_{2}, \gamma) \stackrel{\tau}{\longrightarrow}_{t} (C_{1}, \gamma)} & \displaystyle \frac{eval(B, \gamma) = false}{(\mathsf{if} \ B \ \mathsf{then} \ C_{1} \ \mathsf{else} \ C_{2}, \gamma) \stackrel{\tau}{\longrightarrow}_{t} (C_{2}, \gamma)} \\ \\ \hline \\ \hline \\ P_{\mathrm{ROG}} \frac{(P(t), \gamma) \stackrel{a}{\longrightarrow}_{t} (C, \gamma')}{(P, \gamma) \stackrel{a}{\longrightarrow}_{t} (P[t := C], \gamma')} \end{array}$$

Fig. 7. Uninterpreted operational semantics of commands and programs, where  $\xrightarrow{\tau}$  represents an internal transition

$$\frac{P \xrightarrow{\tau} P'}{(P,(\sigma,\gamma)) \xrightarrow{\tau} (P',(\sigma,\gamma))} \xrightarrow{(P,\gamma) \xrightarrow{a} t} (P',\gamma') \qquad b = (g,a,t) \qquad \sigma \xrightarrow{b} \sigma' \xrightarrow{(P,\gamma)} \sigma'$$

Fig. 8. Interpreted operational semantics of programs

# A Operational Semantics of Doherty et al.

This section presents the operational semantics from [10]. We formally model parallel composition as a function  $T \rightarrow Com$ , where T is the type of a thread identifier. The uninterpreted semantics is given in Fig. 7 and the interpreted semantics in Fig. 8.

Example 2. Consider the following program:

Init: x = y = r1 = r2 = 0Thread 1 1: r1 := [x]2: y := 1 $\{r1 \neq 1 \lor r2 \neq 1\}$

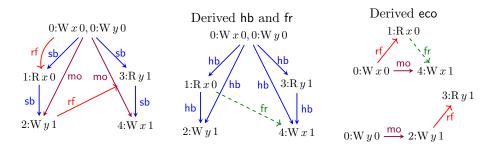

Consider the first tagged action graph below, which represents a possible state after executing lines the program above for the model in [10], which is a model where sb and program order coincide. For clarity, we have omitted the tags and thread identifiers of each event.

The derived happens-before and from-read relations are given in the second figure, and the derived extended coherence order in the third.

*Example 3.* Suppose  $\sigma$  is the state depicted in Example 2. We have  $OW_{\sigma}(1) = \{0: W \ x \ 0, 4: W \ x \ 1, 2: W \ y \ 1\}$  (omitting the tag and thread id of the events) since thread 1 has "encountered" 2: W y 1, but not yet encountered 4: W x 1. Similarly,  $OW_{\sigma}(2) = \{2: W \ y \ 1, 4: W \ x \ 1\}$  since it has encountered both 2: W y 1 and 4: W x 1.

# B Equivalence between MRD and the operational semantics

#### **B.1** Operational executions are event-structure executions

Lemma 3. Given some program P such that

$$(P, (\emptyset, \lambda x. (\lambda y.0)), F) \longrightarrow^* (skip, (\sigma, \Gamma)), F')$$

we name the components of  $\sigma$  to be  $(D, sb, \mathsf{rf}_D, \mathsf{mo})$ . There must exist an execution  $X = (E, \mathsf{DP}, \mathsf{rf}_E, \leq)$  in  $\llbracket P \rrbracket_{n, (\lambda x. \ 0)} \emptyset$  and a bijection over events  $\mathcal{E} : E \to D$ such that  $\mathcal{E}(E) = D$  and  $\mathcal{E}(\mathsf{rf}_E) = \mathsf{rf}_D$  where  $\mathcal{E}(e) = (d, a, t) \implies \lambda(e) = a$ .

Suppose the contrapositive: that for any execution X in the MRD structure, either  $D \neq \mathcal{E}(E)$  or  $\mathsf{rf}_D \neq \mathcal{E}(\mathsf{rf}_E)$ .

If there are no executions containing exactly the actions in D, then we cannot arrive at event set D by application of  $\xrightarrow{a}$  - it requires  $a \triangleright f$  for at least one future, and the initial future set is derived directly from the set of executions. There must therefore exist at least one execution such that  $D = \mathcal{E}(E)$ . Considering only these executions, we now show that at least one must have equivalent rf edges to  $rf_D$ .

We know that MRD exhaustively generates  $\mathsf{rf}$  edges which do not create a cycle in  $\mathsf{rf} \cup \mathsf{DP} \cup \leq$ . There cannot be an edge in all  $\mathsf{rf}_E$  which is simply absent from  $\mathsf{rf}_D$  with no new edge added, as this would imply that  $\mathsf{rf}_D$  is incomplete. This is forbidden by the read execution rule. To arrive at a complete  $\mathsf{rf}_D$  relation which contains an edge not present in any potential  $\mathsf{rf}_E$  where E = D, the proposed edge must cause such a cycle. Given that futures are ordered by  $\mathsf{DP} \cup \leq$ , the new cyclical edge must connect a maximal event to a minimal one. Once again, the requirement that  $e \triangleright f$  for some f prevents executing a maximal event before a minimal one. Thus, there must be some  $\mathsf{rf}_E$  which is equal to  $\mathsf{rf}_D$ .

# B.2 The operational semantics covers all event-structure executions.

**Lemma 4.** Let  $X = (E, DP, rf, \leq)$  be a complete execution of the MRD model  $\llbracket P \rrbracket_n \lambda_{x. 0, \emptyset}$  for large enough n to ensure termination. Let the relation  $\xrightarrow{R}$  be  $DP \cup rf \cup \leq$ , observing that E is partially ordered by  $\xrightarrow{R}^*$ . There exists a relation  $\xrightarrow{R'}$  disjoint from  $\xrightarrow{R}$  such that  $\xrightarrow{R \cup R'}$  is total and acyclic over E, giving the chain  $e_1 \xrightarrow{R \cup R'} e_2 \dots e_k$ , and an execution of the operational semantics  $\sigma_1 \xrightarrow{w, e_1} \sigma_2 \dots \sigma_k$  such that  $e_1 \dots e_k \sim \sigma_k$ , where  $e_1 \dots e_n$  denotes X with the event set and relations restricted to  $\{e_1 \dots e_n\}$  and  $(E, rf_E, dp, ppo) \sim (D, rf_D, mo)$  iff  $\lambda(E) = D \wedge \lambda(rf_E) = rf_D$ .

Proof sketch The existence of an acyclic  $\xrightarrow{R \cup R'}$  is given by the acyclicity of  $\xrightarrow{R}$  asserted by the MRD axiomatic check. We proceed by induction over  $\xrightarrow{R \cup R'}$  and  $\xrightarrow{w:e}$ . The base case is trivial: take any arbitrary  $\xrightarrow{R'}$  which makes  $\xrightarrow{R \cup R'}$  total. Because  $e_1$  must be minimal in  $\xrightarrow{R}$ , it must be minimal in  $\xrightarrow{rf}$  and minimal in DP. Being minimal in  $\xrightarrow{rf}$  means it cannot be a read or RMW event. Being minimal in DP means it must be in an available future. Let  $\sigma_1$  be  $(\{\lambda(e_1)\}, \emptyset, \emptyset)$ . It remains to show that  $e_1..e_{n-1} \sim \sigma_{n-1} \implies e_1..e_n \sim \sigma_n$  for  $n \leq k$ . There are 3 cases for the event type  $e_n$ : a read event, a write event, or an RMW event.

In the case where  $e_n$  is a read, to use the semantic rule for creating state  $\sigma_n$  requires an event  $\lambda(w) \in OW_{\sigma_{n-1}}(tid(e_n))$  such that  $var(w) = var(e_n) \land wrval(w) = wrval(e_n)$ . This adds  $(\lambda(w), \lambda(e_n))$  to  $rf_D$ .

Given X is complete, there must be some write w' such that  $w' \xrightarrow{r_f} e_n$ . It must also be true that  $w' \xrightarrow{R \cup R'} e_n$ , due to the inclusion of rf in  $\xrightarrow{R}$ . Therefore, we can use w' as w.

The event w will be in  $OW_{\sigma_{n-1}}(tid(w))$  if it is maximal in mo. Suppose some event w'' exists such that  $(w, w'') \in mo$ . By the construction of mo, it must also be true that  $w \xrightarrow{R \cup R'} {}^{*} w''$ . If  $w \xrightarrow{R} {}^{*} w''$ , then the axiomatic checks in MRD prevent the  $w \xrightarrow{rf} e_n$  edge from being added. Otherwise, by lemma 5, there exists another choice of  $\xrightarrow{R'}$  such that w' is added to  $\sigma_n$  before w and (w, w') is no longer maximal in mo.

In the case where  $e_n$  is an initialising write, we only need D such that  $e_n \in D$ . If  $e_n$  is a non-initialising write, meaning there is some event  $w \in X$  which is a write to the same variable as  $e_n$ , we must show that w is in  $OW(e_n)$ . This follows by the same reasoning as in the read case.

**Lemma 5.** If  $e_i \xrightarrow{R \cup R'} e_j \wedge e_i \xrightarrow{R} e_j$  in the chain  $e_1..e_n$  then there exists a valid choice of relation  $\xrightarrow{R''}$  such that  $e_j \xrightarrow{R \cup R''} e_i$ , the union  $\xrightarrow{R \cup R''}$  is acyclic, and there exists an event  $e'_n$  in  $e_1..e_n$  such that

1.  $e_1..e_n$  under  $\xrightarrow{R \cup R'}$  is equal to  $e_1..e'_n$  under  $\xrightarrow{R \cup R''}$

2.  $\sigma'_n$ , the result of running the operational semantics under  $\xrightarrow{R \cup R''}$ , is equal to  $\sigma_n$  excepting relation edges between  $e_i$  and  $e_j$

*Proof.* Begin by enforcing that  $e_j \xrightarrow{R''} e_i$ . A cycle in  $\xrightarrow{R \cup R''}$  would have the shape  $e_i \xrightarrow{R \cup R''} e_j$ . As we can trivially prevent  $e_i \xrightarrow{R''} e_j$  by construction, this relation edge must contain one or more event pairs e and e' such that  $e \xrightarrow{R} e'$ . This event pair can be moved  $\xrightarrow{R''}$ -before  $e_j$  unless  $e_j \xrightarrow{R} e_j$ , and it can be moved  $\xrightarrow{R''}$ -after  $e_i$  unless  $e' \xrightarrow{R} e_i$ . If both of these are true, then  $e_i \xrightarrow{R} e_j$ , which we know is untrue.

To find  $e'_n$ , choose any element which is not equal to  $e_j$  from the set of events which are maximal in  $\xrightarrow{R}$  and make it maximal in  $\xrightarrow{R''}$ . There must be some element in this set which is not  $e_j$ , as otherwise we would have  $\forall e.e \xrightarrow{R} e_j$  and it would again be true that  $e_i \xrightarrow{R} e_j$ .

What remains is to create two arbitrary orderings  $R''_1$  and  $R''_2$  such that  $e_1 \xrightarrow{R \cup R''_1} e_j$  and  $e_j \xrightarrow{R \cup R''_2} e_n$  and both  $\xrightarrow{R \cup R''_1}$  and  $\xrightarrow{R \cup R''_2}$  are acyclic. Partition all remaining events into those which are and are not  $\xrightarrow{R}$ -before  $e_j$ , then construct  $\xrightarrow{R''_1}$  over the first and  $\xrightarrow{R''_2}$  over the second. These are individually trivial by the acyclicity of  $\xrightarrow{R}$ , and their union must be acyclic as their event sets are disjoint.

It is trivial to establish that  $e_1..e_n = e_1..e_{n'}$  by the fact that all relation edges in X are preserved in  $\xrightarrow{R}$ . To show that  $\sigma_n$  is equivalent to  $\sigma_{n'}$  excepting  $(e_i, e_j)$  edges, it suffices to show that if  $(e, e') \in mo$  then  $(e, e') \in mo'$ , as rf edges are constrained by  $\xrightarrow{R}$ . Events are only relocated around points  $e_i$  and  $e_j$ , so any such edges would have the shape  $(e, e_j)$  or  $(e_i, e)$  in  $\sigma_n$  and become  $(e_j, e)$  or  $(e, e_i)$  respectively. Focusing on the first case, any such reordering is only required if  $e_j \xrightarrow{R}^* e_i$ , as this forces e to be placed  $\xrightarrow{R \cup R''}^*$ -after  $e_j$  in our construction of  $\xrightarrow{R''}$ . This makes the initial mo edge impossible to observe. The same reasoning holds for the  $(e_i, e)$  edge.

22

## **C** Further Examples

#### C.1 Partial conditional

Our first example is the partial conditional example, whose proof outline is given in Fig. 9. The program contains no dependencies in Thread 1 and non-trivial dependencies in thread 2. In particular, in Thread 2 the dependencies are condition on the values read for x and y.

- If r1 = r2 = 1, then we have dependencies between lines 3 and 5, and between lines 4 and 6, but lines 3/4 and 5/6 are mutually independent.

- If  $r_1 = 1$  and  $r_2 = 0$ , there is a dependency between lines 3 and 7.

- If r1 = 0 and r2 = 1, there is a dependency between lines 4 and 8.

This is reflected by the futures F for thread 1 and G for thread 2 in Fig. 9.

```

Init: x = y = r1 = r2 = 0

Thread 1

Thread 2

{[x=0]_2 \land [y=0]_2}_F

\{I\}_G

\{ [x = 0]_2 \land [y \in \{0, 1\}]_2 \}_{F_2}

\{ [x = 0]_2 \land [y \in \{0, 1\}]_2 \}_{F_2}

1: [x] := 1

\{ [x \in \{0, 1\}]_2 \land [y = 0]_2 \}_{F_1}

2: [y] := 1

\begin{cases} r2 = m \land I \}_{G_{4n}} \\ 3: r1 := [x] ; \\ \{r1 = m \land I \}_{G_{3m}} \\ 4: r2 := [y] ; \end{cases}

\{[x\in \bar{\{0,1\}}]_2 \land [y\in \{0,1\}]_2\}_{\emptyset}

\{r1=m\wedge r2=n\wedge I\}_{G_{3_m,4_n}}

if r1 = 1 & r2 = 1 {

\begin{array}{l} \{r1 = 1 \wedge r2 = 1 \wedge I\}_{G_{3_1,4_1}}^{\circ} \\ \{r1 = 1 \wedge r2 = 1 \wedge [w = 0]_2 \wedge [z = 1]_2\}_{G_{3_1,4_1,6}} \\ \texttt{5: [w] := 1 ;} \end{array}

\{ r1 = 1 \wedge r2 = 1 \wedge [w = 1]_2 \wedge [z = 0]_2 \}_{G_{3_1, 4_1, 5}}

6: [z] := 1 ; }

if r1 = 0 & r2 = 1 {

\begin{array}{l} \{r1=0 \wedge r2=1 \wedge I\}_{G_{3_0,4_1}} \\ \text{7: z := 1 } \end{array} \}

if r1 = 1 & r2 = 0

\begin{aligned} \{r1 &= 1 \wedge r2 = 0 \wedge I\}_{G_{3_1,4_0}} \\ & 8: \text{ w } := 1 \text{ ;} \\ \{[w &= r1]_2 \wedge [z = r2]_2\}_{\emptyset} \end{aligned}

\{[w = r1]_2 \land [z = r2]_2\}

```

**Fig. 9.** Partial conditional:  $F = \{\{1,2\}\}\ G = \{\{3_1 \prec 5, 4_1 \prec 6\}, \{3_1 \prec 8, 4_0\}, \{4_1 \prec 7, 3_0\}, \{3_0, 4_0\}\}\$ and  $I = [w = 0]_2 \land [z = 0]_2$

#### C.2 Random number generator (RNG)

Our next example is the random number generator (RNG) litmus test (see Fig. 10) from [6], which in a poorly defined semantics has the potential to terminate so that line 7 is executed. Our proof outline shows that this cannot be the case in our semantics, i.e., the program satisfies the postcondition  $[x \not\approx 99]_{1,2,3}$ .

**Fig. 10.** RNG, where  $F = \{\{1 \prec 2\}\}, G = \{\{3 \prec 4\}\}, H = \{\{5 \prec 6\}\}$

The program is similar to Fig. 6, but contains semantic dependencies between lines 1 and 2, between lines 3 and 4, and between lines 5 and 7. This means that no reorderings are permitted within any of the threads, thus its proof is straightforward. In fact, we have used our existing Isabelle/HOL formalisation [8] for a model that assumes program order to discharge the proof obligations.

**Theorem 2.** The proof outline in Fig. 10 is valid.

#### C.3 LB+data-add+ctrl

24

The next two examples are designed to test whether a chain of semantic dependencies on data, addresses and control are properly modelled by the semantics.

**Fig. 11.** Simple LB+data-add+ctrl, where  $F = \{\{1 \prec 2\}\}$  and  $G = \{\{3 \prec 4\}\}$

The proofs of both programs are straightforward since they do not contain any intra-thread re-orderings. Again, we have shown correctness of both proof outlines using our existing Isabelle/HOL formalisation [8].

Theorem 3. The proof outlines in Fig. 11 and Fig. 12 are valid.

**Fig. 12.** LB+data-add+ctrl, where  $F = \{\{1 \prec 2 \prec 3 \prec 4 \prec 5\}\}$  and  $G = \{\{6 \prec 7\}\}$