Copyright

by

Avijit Dutta

2007

# The Dissertation Committee for Avijit Dutta Certifies that this is the approved version of the following dissertation:

# **Synthesis for Circuit Reliability**

| Committee:            |

|-----------------------|

|                       |

| Nur Touba, Supervisor |

|                       |

| Tony Ambler           |

|                       |

| Margarida Jacome      |

|                       |

| Zhigang Pan           |

|                       |

| Abhijit Jas           |

## **Synthesis for Circuit Reliability**

by

Avijit Dutta, B.E.; M.S.E.

## **Dissertation**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin May, 2007

## **Dedication**

My thanks go, as always, to my maternal grandparents, to whom this dissertation is dedicated. I am indebted to my maternal grandparents for standing beside me all these years and constantly motivating me in my efforts. I wouldn't have been what I am, without their help.

And

My thanks go to my supervising professor, Nur A. Touba.

## Acknowledgements

I wish to thank my advisor, Professor Nur A. Touba for his continued guidance and encouragement. His research philosophy of maintaining a balance between pure theoretical and practical aspects of research has influenced me a lot.

Finally, my thanks go to the other committee members, Prof.

Margarida Jacome, Prof. Tony Ambler, Prof. David Z. Pan and Dr. Abhijit

Jas for their input and support.

### **Synthesis for Circuit Reliability**

Publication No.\_\_\_\_

Avijit Dutta, Ph.D.

The University of Texas at Austin, 2007

Supervisor: Nur A. Touba

For modern logic circuits, circuit reliability is an important design consideration. Ionizing radiation from high-energy neutrons and alpha particles can cause a single-event upset (SEU) that may cause a bit flip in some latch or memory element thereby altering the state of the system resulting in a soft error. As process technology scales well below 100 nanometers, the higher operating frequencies, lower voltage levels, and smaller noise margins make integrated circuits increasingly susceptible to SEUs resulting in a dramatic increase in soft errors. In this dissertation, a non-intrusive technique is presented to detect soft errors in multilevel combinational logic circuit with minimal overhead. Another low cost error correcting code based technique is presented to detect and correct the most likely soft errors in memory. This technique is then extended to design a low cost unequal error protection code which can protect data residing in a router buffer effectively. The dissertation also contains a fast algorithm to accurately estimate signal probabilities of circuit lines. This algorithm can be used to estimate soft error rates in a logic circuit. Finally, the dissertation also includes a low cost test data compression technique to reduce the deterministic test data to be stored on tester during off-line testing of a circuit.

## **Table of Contents**

| List of Tables                                                                               | X  |

|----------------------------------------------------------------------------------------------|----|

| List of Figures                                                                              | xi |

| Chapter 1 Introduction                                                                       | 1  |

| 1.1 Concurrent error detection                                                               | 2  |

| 1.2 Low cost error correction code for memories                                              | 3  |

| 1.3 Accurate signal probability estimation                                                   | 5  |

| 1.4 Test data compression                                                                    | 6  |

| Chapter 2 Synthesis of non-intrusive concurrent error detection using detecting function.    |    |

| 2.1 Related work                                                                             | 8  |

| 2.2 Overview and proposed scheme                                                             | 14 |

| 2.3 Forming even edf function                                                                | 15 |

| 2.4 Coverage versus area tradeoffs                                                           | 19 |

| 2.5 Experimental results                                                                     | 20 |

| 2.6 Conclusion                                                                               | 24 |

| Chapter 3 Multiple bit upset tolerant memory using a selective cycle based SEC-DED-DAEC code |    |

| 3.1 Introduction                                                                             | 25 |

| 3.2 Related work                                                                             | 26 |

| 3.3 Binary linear block codes                                                                | 29 |

| 3.4 Proposed code                                                                            | 30 |

| 3.5 Code design procedure                                                                    | 33 |

| 3.6 Encoding/Decoding algorithm                                                              | 38 |

| 3.7 Conclusions                                                                              | 39 |

| Chapter 4 Multiple bit upset tolerant router memory using a low cos protection code          |    |

| 4.1 Introduction                                                                             | 41 |

| 4.2 NoC router architecture45                                                   |    |

|---------------------------------------------------------------------------------|----|

| 4.3 Store-and-forward routing                                                   |    |

| 4.4 Unequal error protection code                                               |    |

| 4.5 Proposed code                                                               |    |

| 4.6 Code design procedure54                                                     |    |

| 4.7 Encoding/decoding algorithm                                                 |    |

| 4.8 Conclusion                                                                  |    |

| Chapter 5 Iterative OPDD based signal probability calculation                   |    |

| 5.1 Related work66                                                              |    |

| 5.2 Combining information across OPDDs69                                        |    |

| 5.3 Unknown solution space exploration                                          |    |

| 5.4 Runtime complexity analysis                                                 |    |

| 5.5 Experimental results80                                                      |    |

| 5.6 Conclusion84                                                                |    |

| Chapter 6 Using limited depth sequential expansion for decompressing test vecto | rs |

| 85                                                                              |    |

| 6.1 Introduction85                                                              |    |

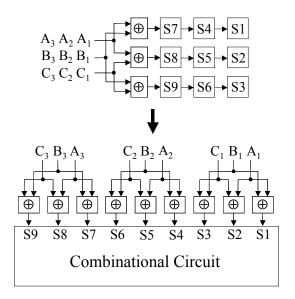

| 6.2 Combinational encoding flexibility90                                        |    |

| 6.3 Sequential encoding flexibility94                                           |    |

| 6.4 Selecting decompressor design87                                             |    |

| 6.5 Synthesis procedure for decompressor99                                      |    |

| 6.6 Experimental results100                                                     |    |

| 6.7 Conclusions                                                                 |    |

| Chapter 7 Conclusion and future work                                            |    |

| 7.1 Conclusion                                                                  |    |

| 711 Concission                                                                  |    |

| 7.2 Future work                                                                 |    |

|                                                                                 |    |

# **List of Tables**

| Table 2.1: | Comparison of proposed method with duplication           | 22     |

|------------|----------------------------------------------------------|--------|

| Table 3.1: | Comparison of proposed SEC-DED-DEAC code with other code | des.36 |

| Table 4.1: | Check bit requirements                                   | 51     |

| Table 4.2: | Comparison of proposed SEC-DAED-SDAEC code with other    | codes  |

|            |                                                          | 59     |

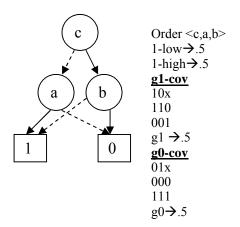

| Table 5.1: | U-effect for OPDD in Fig 5.2                             | 76     |

| Table 5.2: | Cumulative U-effects of OPDDs in Figs 5.2-5.4            | 76     |

| Table 5.3: | Cutting algorithm                                        | 81     |

| Table 5.4: | [Kodavarti 93]                                           | 82     |

| Table 5.5: | Proposed                                                 | 83     |

| Table 6.1: | Design details                                           | 101    |

| Table 6.2: | Results for s38584                                       | 102    |

| Table 6.3: | Results for Design A                                     | 103    |

| Table 6.4: | Results for Design B                                     | 105    |

# **List of Figures**

| Figure 2.1:  | Non-intrusive CED                                             | 12 |

|--------------|---------------------------------------------------------------|----|

| Figure 2.2:  | Basic approach for structured implementation of non-intrusive |    |

|              | CED                                                           | 12 |

| Figure 2.3:  | Block diagram of proposed scheme                              | 14 |

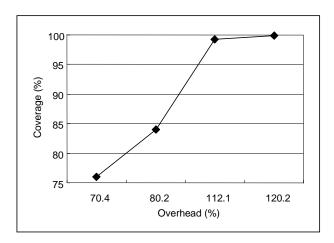

| Figure 2.4:  | Coverage vs. overhead for dc2                                 | 23 |

| Figure 2.5:  | Coverage vs. overhead for misex1                              | 23 |

| Figure 2.6:  | Coverage vs. Overhead for br1                                 | 23 |

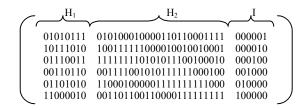

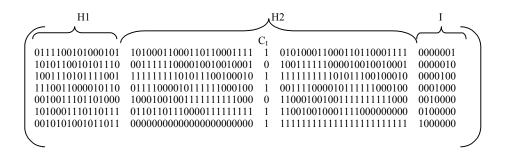

| Figure 3.1:  | H-matrix for proposed (22, 16) code                           | 34 |

| Figure 3.2:  | H-matrix for proposed (39,32) code                            | 34 |

| Figure 3.3:  | Pseudo greedy search algorithm                                | 36 |

| Figure 3.4:  | H-matrix for proposed (72,64) code                            | 36 |

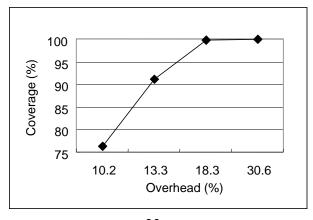

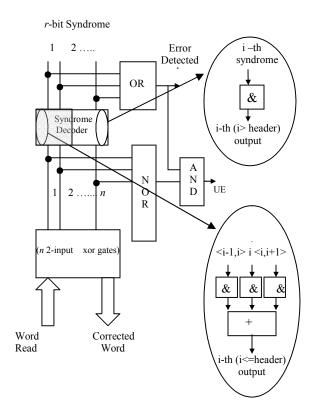

| Figure 3.5:  | Error detection and correction block diagram                  | 39 |

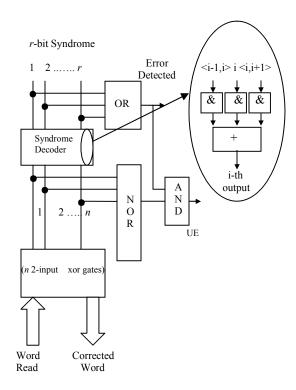

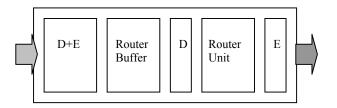

| Figure 4.1:  | Basic router architecture                                     | 46 |

| Figure 4.2:  | ECC scheme for NoC router                                     | 47 |

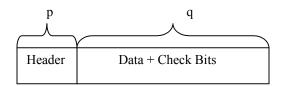

| Figure 4.3:  | Packet structure for store-and-forward routing                | 50 |

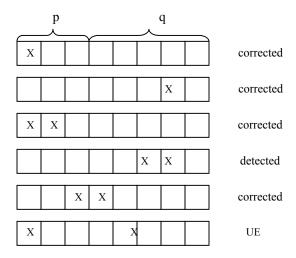

| Figure 4.4:  | Error profiles                                                | 53 |

| Figure 4.5:  | Algorithm to construct H <sub>2</sub> matrix                  | 56 |

| Figure 4.6:  | Algorithm to construct H <sub>1</sub> matrix                  | 57 |

| Figure 4.7:  | H-matrix for proposed (8,24,6) code                           | 58 |

| Figure 4.8:  | H-matrix for proposed (16,48,7) code                          | 58 |

| Figure 4.9:  | Constructing H <sub>2</sub> -matrix for (16,48,7) code        | 60 |

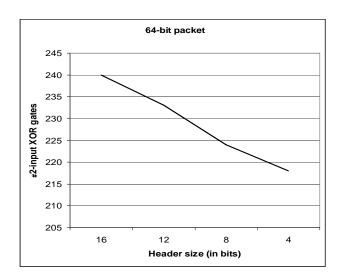

| Figure 4.10: | XOR gate overhead vs header size                              | 62 |

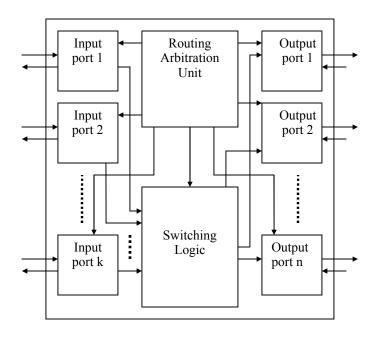

| Figure 4.11: | Error detection and correction block diagram                  | 63 |

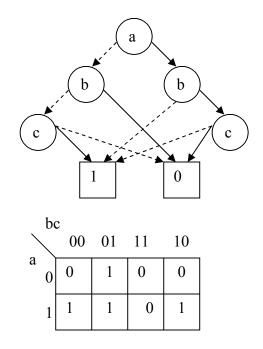

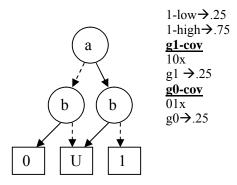

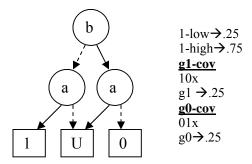

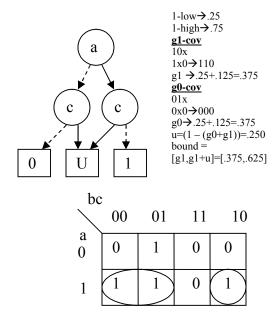

| Figure 5.1: | Binary decision diagram and karnaugh map73                                  |

|-------------|-----------------------------------------------------------------------------|

| Figure 5.2: | OPDD with variable ordering <a,b,c>73</a,b,c>                               |

| Figure 5.3: | OPDD with variable ordering <b,a,c>74</b,a,c>                               |

| Figure 5.4: | OPDD with variable ordering <a,c,b>74</a,c,b>                               |

| Figure 5.5: | OPDD using USSE generated ordering                                          |

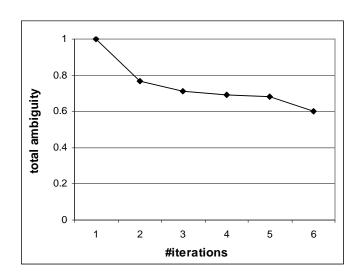

| Figure 5.6: | #iterations vs total ambiguity (normalized) (c880)83                        |

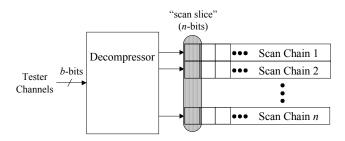

| Figure 6.1: | Block diagram of test vector decompression86                                |

| Figure 6.2: | Example of including decompressor constraints at pseudo-PI's for            |

|             | ATPG Backtrace                                                              |

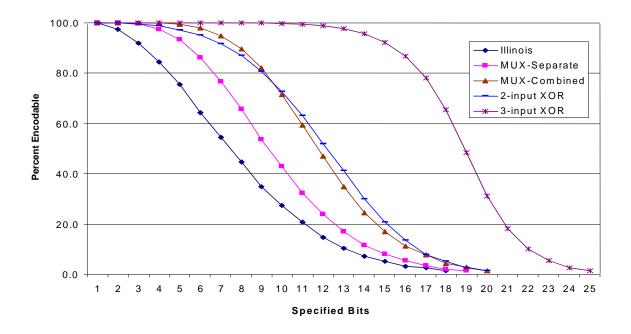

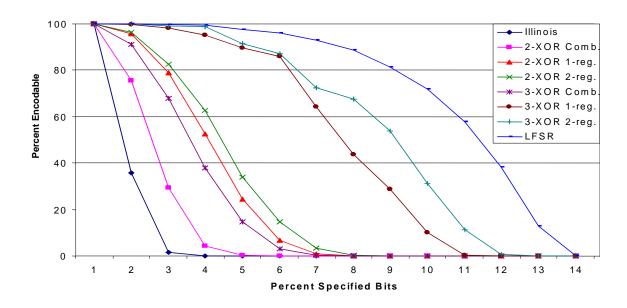

| Figure 6.3: | Probability of encoding scan slice for 16 tester channels expanding to fill |

|             | 160 scan chains93                                                           |

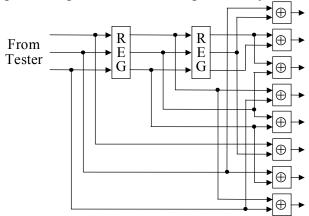

| Figure 6.4: | Example of limited dependence sequential decompressor with two              |

|             | registers                                                                   |

|             | 95                                                                          |

| Figure 6.5: | Probability of encoding test cubes for 8 tester channels expanding to fill  |

|             | 80 scan chains                                                              |

### **Chapter 1: Introduction**

Circuit reliability has become an important design consideration. When ionizing radiation from high-energy neutrons and alpha particles strike a sensitive region in a semiconductor device, they generate a dense track of electron-hole pairs that may be collected by a p-n junction resulting in a very short duration pulse of current causing a single-event upset (SEU) in the signal value. An SEU may cause a bit flip in some latch or memory element thereby altering the state of the system resulting in a soft error. As process technology scales well below 100 nanometers, the higher operating frequencies, lower voltage levels, and smaller noise margins make integrated circuits increasingly susceptible to SEUs resulting in a dramatic increase in soft errors. Studies indicate that the soft error failure rate will become unacceptable even in mainstream commercial applications. It is projected that soft errors in logic circuits will be the limiting factor for system reliability as technology continues to scale. The problem of soft error is even more prominent in memories. Constant technology process improvement has resulted in very dense memory cells that store information with less capacitance and lower voltage. Consequently, less charge is required to produce one or more soft errors in memories. While off-line tests can detect manufacturing defects, on-line error detecting and correcting schemes are required to detect soft-errors and recover from soft-errors. Based on the current technological trends, there is a great need for concurrent error detection and correction techniques to increase reliability of both combinational logic circuits and memories.

This dissertation primarily addresses the threat to reliability arising from increasing soft error rates and proposes several concurrent error detection and correction methodologies. For off-line testing, the dissertation presents a very low cost solution to

effectively reduce the deterministic test data to be stored for manufacturing test of a circuit.

This chapter provides background on the issues related to soft errors in logic circuit as well as in memories. It also presents the problem of test data compression and its necessity in the context of off-line manufacturing test. Section 1.1 describes the reliability concerns in combinational logic due to soft errors and describes the need for efficient concurrent error detection techniques. Section 1.2 describes the problems in memories caused by single event induced multiple bit upsets and present a low cost error correcting code to design multiple bit upset tolerant memories. Section 1.2 also describes a low cost unequal protection code that can protect data residing in router memories by providing more protection to the more important part of the data packet. Section 1.3 presents a memory efficient algorithm with low runtime complexity to accurately estimate signal probability bounds of the circuit lines. This algorithm can be used for accurate estimation of soft error rates in combinational logic circuits. Accurate estimate of soft error rate can help in insertion of appropriate protection hardware in logic circuits. In section 1.4 the problem of test data compression in offline testing is described. In this section a limited depth sequential expansion based test data compression technique is presented to reduce both test data and testing time.

#### 1.1 CONCURRENT ERROR DETECTION

One way to detect soft errors is to use concurrent error detection (CED) circuitry that monitors the outputs of a circuit for the occurrence of an error. If an error is detected, then the system can recover thereby preventing a failure. Detecting errors in logic circuits is much more expensive than in memories. While CED can be efficiently incorporated in memories due to their regular structure, logic circuits with their irregular structure present a much greater challenge. It is projected that in systems where

memory CED is employed, soft errors in logic circuits will be the limiting factor for system reliability as technology continues to scale. In this dissertation we focus on the problem of providing CED in logic circuits. The simplest CED scheme for logic circuits is to use duplication where the circuit is duplicated and the outputs are compared with an equality checker. While this is very simple to implement and provides very high error coverage, it requires over 100% overhead. So there is a need for CED schemes that provide high coverage of soft-errors and at the same time have low overhead. A new method for synthesizing non-intrusive concurrent error detection (CED) circuitry is presented. The idea is to use single-bit parity to detect all errors affecting an odd number of bits and then synthesize a circuit to detect the even errors. A novel statistical sampling and expanding methodology is proposed for constructing the even error detection circuitry. A major feature of the proposed methodology is that it allows very efficient tradeoffs between error coverage and overhead. While CED schemes that use a fixed checker based on a particular error detecting code are not amenable to simplification without a major impact on coverage, the proposed scheme can easily facilitate significant reductions in overhead with only a small loss in coverage. Experimental results show that the proposed scheme can provide very high levels of soft error protection at a fraction of the cost of duplication. In chapter 2, detailed description of the proposed non-intrusive concurrent error detection scheme for combinational logic circuit is provided.

#### 1.2 LOW COST ERROR CORRECTING CODES FOR MEMORIES

Conventional error correcting code (ECC) schemes used in memories and caches cannot correct double bit errors caused by a single event upset (SEU). As memory density increases, multiple bit upsets in nearby cells become more frequent. In this dissertation, we propose a methodology for deriving an error correcting code through heuristic search that can detect and correct the most likely double bit errors in a memory

while minimizing the miscorrection probability of the unlikely double bit errors. A key feature of the proposed ECC is that it uses the same number of check bits as the conventional single error correcting/double error detecting (SEC-DED) codes commonly used, and has nearly identical syndrome generator/encoder area and timing overhead. Hence, there is very little additional cost to using the proposed ECC. The proposed ECC scheme can be very useful for small memories e.g., content addressable memory (CAM), register files where interleaving is not possible. The proposed ECC can be used instead of or in addition to bit interleaving to provide greater flexibility for optimizing a memory layout and/or provide better protection from multiple bit upsets. The proposed code designs the parity check matrix of the linear block code while avoiding certain types of linear dependencies involving the columns of the parity check matrix. This selective linear dependency avoidance based algorithm is further extended to design a low cost unequal error protection code. This kind of code can be used to protect router memories from single event induced multiple bit upsets. The network-on-chip (NoC) paradigm is seen as a way of facilitating the integration of a large number of computational and storage blocks on a chip to meet several performance and power constraints. However due to continued scaling of process technologies, the devices and interconnects have become more sensitive to new types of reliability hazards such as, single event upsets and crosstalk. This dissertation presents a low cost error correcting code based techniques to protect the NoC routers against the single event upset induced soft errors and also against crosstalk. An unequal protection error correcting code based methodology is provided for the most commonly used store-and-forward routing strategy. The proposed code has the same check bit overhead as the conventional single error correcting (SEC) code. The encoding/decoding overhead and latency are also similar to the conventional low cost SEC code. The proposed codes belong to the class of unequal error protection codes as they provide different levels of error correction capability for different portions of the same packet. The proposed code provides more protection for the important parts of the data. Chapter 3 and 4 describes the proposed codes in detail and also provides detailed comparison with the existing codes.

#### 1.3 ACCURATE SIGNAL PROBABILITY ESTIMATION

Estimating the reliability of circuits is essential in synthesis of reliable circuits. Accurate estimation of circuit reliability requires accurate estimation of soft-error rates. The effects of single event upsets (SEU) on digital circuit can be categorized in three ways: 1) SEUs can cause a transient error in combinational logic part which can be propagated and captured in flip-flops. 2) SEUs can directly change the contents of memory elements. 3) SEUs can cause permanent damage on SRAM based combinational circuits e.g., FPGAs. In our research so far, we have looked into the first category involving combinational circuits and their effect on circuit reliability. An SEU causes a soft-error if and only if it propagates to the latch boundary and gets latched making a bitflip error. Most SEUs on combinational logic are masked and they don't reach the latch boundary. Moreover even if the SEU effect reaches the latch boundary it still may not be captured if it does not reach the latch at the appropriate latching-window. Accurate estimation of signal probability is required to find out whether the effect of an SEU will propagate to the flip-flop inputs through the combinational gates. The effect can only propagate if for all the gates on the propagation path all the other inputs have noncontrolling logic values. To calculate actual soft-error probability accurate estimation of signal probabilities on the propagation path of the SEU effect is required. In this proposal, we present an efficient method to accurately compute tight bounds on the signal probabilities for combinational circuits. This dissertation presents an improved method to accurately estimate signal probabilities using ordered partial decision diagrams (OPDDs)

[Kodavarti 93] for partial representation of the functions at the circuit lines. OPDDs which are limited to a certain maximum number of nodes are built iteratively with different variable orderings to efficiently explore different regions of the function. Signal probability bounds (upper and lower) are computed from the OPDDs. From each OPDD, information is extracted to tighten the signal probability bound and guide the variable ordering for the next OPDD. By restricting the size of each OPDD to a small number of nodes, they can be constructed and processed quickly to obtain a fast and accurate estimate of signal probabilities. Experimental results demonstrate the effectiveness of the approach compared with existing methods. Chapter 5 describes in detail the proposed approach.

#### 1.4 TEST DATA COMPRESSION

In this dissertation till now we have focused on online methodologies to design reliable circuits. The proposed concurrent error detection/correction methodologies primarily focus on protecting circuits from single event induced soft errors. Another threat to circuit reliability is the manufacturing defects. Offline testing typically screens off the defective circuits. Offline testing techniques target the permanent faults and deterministic test data targeting the permanent faults are typically stored on the tester. For offline testing the test data volume and test time are the two major concerns. In this dissertation we present a low overhead input data compression technique to reduce the deterministic test data that needs to be stored on the tester. The proposed scheme can reduce the test time significantly. The proposed technique uses a limited depth sequential expansion based approach and incorporates the constraints directly into ATPG backtrace.

Existing techniques that incorporate decompressor constraints in the ATPG search/backtrace (e.g., Illinois scan) are based on combinational expansion in which each scan slice must be encoded using only the free-variables arriving form the tester in the

current clock cycle. Sequential expansion is more powerful as it allows free-variables across multiple clock cycles to be used, however conventional approaches for sequential expansion that are based on linear finite state machines (LFSRs) and ring generators are not amenable to including the constraints in the ATPG backtrace because the constraints are too complex. This dissertation investigates the use of limited dependence sequential expansion to combine the benefits of sequential decompression with the benefits of incorporating the decompressor constraints in the ATPG backtrace. Analytical and experimental results are presented showing the benefits of the proposed approach. Chapter 5 describes the proposed compression technique in detail.

# Chapter 2: Synthesis of Non-Intrusive Concurrent Error Detection Using an Even Error Detecting Function

A new method for synthesizing non-intrusive concurrent error detection (CED) circuitry is presented. The idea is to use single-bit parity to detect all errors affecting an odd number of bits and then synthesize a circuit to detect the even errors. A novel statistical sampling and expanding methodology is proposed for constructing the even error detection circuitry. A major feature of the proposed methodology is that it allows very efficient tradeoffs between error coverage and overhead. While CED schemes that use a fixed checker based on a particular error detecting code are not amenable to simplification without a major impact on coverage, the proposed scheme can easily facilitate significant reductions in overhead with only a small loss in coverage. Experimental results show that the proposed scheme can provide very high levels of soft error protection at a fraction of the cost of duplication.

#### 2.1 RELATED WORK

When ionizing radiation from high-energy neutrons and alpha particles strike a sensitive region in a semiconductor device, they generate a dense track of electron-hole pairs that may be collected by a p-n junction resulting in a very short duration pulse of current causing a *single-event upset (SEU)* in the signal value. An SEU may cause a bit flip in some latch or memory element thereby altering the state of the system resulting in a *soft error*. Additionally, an SEU may occur in an internal node of combinational logic and subsequently propagate to and be captured in a latch. As process technology scales well below 100 nanometers, the higher operating frequencies, lower voltage levels, and smaller noise margins make integrated circuits increasingly susceptible to SEUs resulting

in a dramatic increase in soft errors. Studies indicate that the soft error failure rate will become unacceptable even in mainstream commercial applications [Ziegler 96], [Cohen 99]. One way to detect soft errors is to use concurrent error detection (CED) circuitry that monitors the outputs of a circuit for the occurrence of an error [Gössel 93], [Nicolaidis 98]. If an error is detected, then the system can recover thereby preventing a failure. Detecting errors in logic circuits is much more expensive than in memories. While CED can be efficiently incorporated in memories due to their regular structure, logic circuits with their irregular structure present a much greater challenge. It is projected that in systems where memory CED is employed, soft errors in logic circuits will be the limiting factor for system reliability as technology continues to scale [Shivakumar 02], [Bowman 03, 04]. This chapter focuses on the problem of providing CED in logic circuits. The simplest CED scheme for logic circuits is to use duplication where the circuit is duplicated and the outputs are compared with an equality checker. While this is very simple to implement and provides very high error coverage, it requires over 100% overhead. A lot of research has been done on alternate schemes that are still applicable to any logic circuit but require less hardware overhead than duplication. One class of techniques uses time redundancy. Multiple sampling of the outputs has been proposed in [Franco 94], [Metra 98], [Nicolaidis 99], [Favalli 02]. Self-dual functions have been proposed in [Saposhnikov 96, 98a]. These approaches have low hardware costs, but reduce performance. Another class of techniques involves re-synthesizing the functional logic so that it has a more regular structure such that simple error detecting codes can be used to provide high coverage. Techniques have been developed for parity codes [De 94], [Touba 97], [Bolchini 97]; Berger codes [Jha 93], [Saposhnikov 98b]; and Bose-Lin codes [Das 99]. In cases where it is not desirable to re-synthesize the functional logic (e.g., cores, macrocells, handcrafted designs, legacy designs, etc.), these

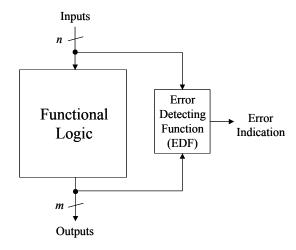

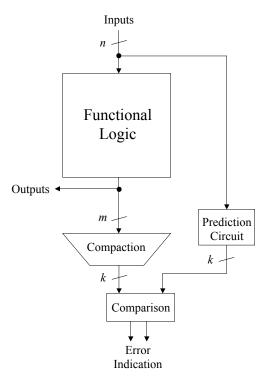

techniques are not applicable. A third class of techniques uses non-intrusive CED where the functional logic is not modified. As shown in [Gössel 93], this problem can be formulated as follows (see illustration in Fig. 2.1). For a functional circuit with ninputs,  $A=a_i,...,a_n$ , and m outputs  $Z=z_i,...,z_m$ , let  $EDF(a_i,...,a_n, z_i,...,z_m)$  be the error detecting function which is a Boolean function that is equal to 0 if the output vector Z is error-free, equal to 1 if the output vector Z has an error due to a fault in the specified fault class, and equal to X (don't care) in all other cases (i.e., for input vector A, no fault can cause the output vector to be equal to Z). Any implementation of the Boolean function EDF will detect all errors due to the specified fault class. As pointed out in [Almukhaizim 04a], the EDF could be passed directly to a synthesis tool to produce the CED circuitry and if the synthesis algorithm could search exhaustively, it could find the optimal non-intrusive CED circuit. However, synthesis tools use heuristics to search the large space of solutions and consequently may obtain a sub-optimal solution. In fact the nature of the EDF function makes it particularly hard for synthesis tools to handle as it has a very large don't care space and many exclusive-or (XOR) factors which most synthesis tools are not good at finding. Thus, passing the EDF directly to a synthesis tool generally does not produce good results as shown in [Almukhaizim 04a]. Rather than trying to directly synthesize the EDF, researchers have explored structured implementations for the EDF. The basic approach for this is to place a compaction circuit at the outputs of the function logic to reduce them from m down to k and then synthesize a prediction circuit that independently predicts the k outputs. This is illustrated in Figure 2.2. One approach for compacting the outputs is to use a parity code which XORs together different subsets of the outputs [Sogomonyan 74], [Fujiwara 87]. If the parity code is selected so that no errors are masked, then 100% coverage can be maintained. In [Almukhaizim 04b], it was observed that the overhead for using a parity code is dominated by the prediction logic and a method based on entropy was proposed to guide the selection of the parity code to minimize the prediction logic. A technique for selecting the parity code with bounded error masking was described in [Tarnick 94]. In [Almukhaizim 04a], a more general design methodology that is not limited to parity was described for synthesizing the compaction circuit to ensure no error masking. In [Mohanram 03], CED based on a parity code is selectively disabled for some input vectors to tradeoff less coverage for less overhead in the prediction logic. In [Morozov 00], a technique for using a Berger code was described.

Figure 2.1: Non-intrusive CED

Figure 2.2: Basic approach for structured implementation of non-intrusive CED

In this chapter, a new method for synthesizing non-intrusive CED circuitry is presented. The idea is to use single-bit parity to detect all errors affecting an odd number of bits and then synthesize a circuit to detect the even errors. The key concept behind this approach is that most of the errors in the EDF function are single-bit errors. By using single-bit parity, all of the odd errors in the EDF function (which includes the single-bit errors) become don't cares leaving only the even errors. The smaller number of even errors in the EDF function can be efficiently synthesized with most synthesis tools. In effect, the proposed method forces a decomposition of the EDF function in which the odd errors are covered with a single parity function and the even errors are covered via conventional logic synthesis with don't cares. Forming the *EDF* function for even errors by exhaustive simulation of all input vectors and all faults can be done only for small circuits. In order to handle larger circuits, a novel statistical sampling and expanding methodology is proposed. While most CED schemes use a fixed checker structure based on an error detecting code that it not amenable to simplification without a significant impact on error coverage. One of the nice features of the proposed scheme is that it provides very easy and efficient tradeoffs between coverage and overhead. A systematic approach is described for simplifying the even error detecting function that results in large reductions in overhead with only a minor loss in error coverage. The chapter is organized as follows: Sec. 2.2 provides an overview of the proposed scheme and its architecture. Sec. 2.3 describes the procedure for forming the even error detecting function. Sec. 2.4 explains how the proposed scheme allows for very efficient tradeoffs in coverage versus overhead. Experimental results are presented in Sec. 2.5. Section 2.6 concludes the chapter.

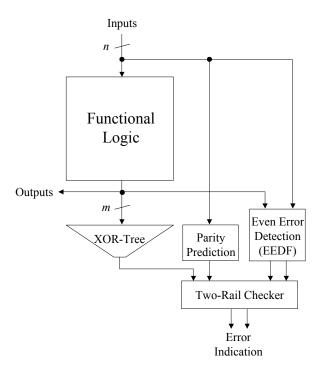

#### 2.2 OVERVIEW OF PROPOSED SCHEME

The proposed scheme involves combining single-bit parity with an even error detecting circuit. A block diagram for the proposed approach is shown in Fig. 2.3. The even error detecting circuit generates a two-bit error indication signal which normally has opposite values in the fault-free case and indicates an error by having equal values. An XOR-tree is used to compute the parity of the outputs of the functional logic. The parity predictor circuit predicts the complement of the parity of the outputs such that its output together with the XOR-tree output forms a two-bit error indication. The two pairs of error indication signals are then merged using a two-rail checker.

Figure 2.3: Block diagram of proposed scheme

To simplify things, the even error detection function (*EVEN\_EDF*) will be described in the rest of the chapter as a single output function. The process of converting it so that it

produces a two-bit error indication signal is trivial. It can be done by simply extracting one XOR factor, inverting it, and making it a separate output (i.e., extract any factor E2 such that  $EVEN\_EDF=E1 \oplus E2$  and use E1 and E2' as outputs with the XOR gate removed). Thus, anytime  $EVEN\_EDF$  is a 1, E1 and E2' will have equal values indicating an error, and anytime  $EVEN\_EDF$  is a 0, E1 and E2' will have opposite values which is the normal error-free case. Synthesizing the parity predictor circuit is exactly the same as for previously proposed methods. Synthesizing the even error detecting circuit is done by forming the  $EVEN\_EDF$  function and giving it to a synthesis tool to synthesize. The challenge is how to form the  $EVEN\_EDF$  function and that is the subject of the next section.

#### 2.3 FORMING EVEN\_EDF FUNCTION

Given a functional logic circuit *F* with *n* inputs and *m* outputs, the simplest way to get the complete *EVEN\_EDF* function that provides 100% coverage of all errors would be to exhaustively simulate *F* for all input vectors and faults. For each input vector, each fault is injected and the corresponding faulty output vector is obtained. If the faulty output vector has an even number of errors, then the minterm corresponding to the input vector and faulty output vector pair would be added to the ON-set of the *EVEN\_EDF* function. This would continue until the complete ON-set for *EVEN\_EDF* is formed. The OFF-set for *EVEN\_EDF* is described by the functional logic circuit *F* itself. The DC-set includes anything that is not in the ON-set or OFF-set.

Forming the exact *EVEN\_EDF* function through exhaustive simulation is intractable for all but the smallest circuits. Thus a less computationally complex procedure needs to be used for forming the *EVEN\_EDF* function which will not necessarily obtain the exact ON-set. The proposed method involves using statistical methods to approximate the ON-set. Fortunately, good results can still be obtained even

if the exact ON-set is not known. If some extra minterms from the DC-set are included in the ON-set, there is no loss of coverage, but possibly the synthesis tool may not obtain as optimal of a result. If some minterms are missing from the ON-set, there may be some loss of coverage. If the approximate ON-set is reasonably close to the exact ON-set, the impact in terms of either the optimality of the synthesis or the coverage can be kept very small. Moreover, if one is interested in trading off less coverage for less overhead, this can be nicely facilitated by approximating the ON-set in a way that the missing minterms simplify the logic implementation.

The proposed method for approximating the ON-set of the *EVEN\_EDF* function involves random sampling of the input space for each fault combined with a *bit-stripping* operation. The procedure is described as follows:

Input: Functional logic circuit F, fault list, and number of simulations to do per fault (L).

Output: Approximate ON-set for EVEN EDF function.

<u>Step 1: Prune fault list</u> – All faults that have a structural path to only one output are pruned from the fault list as they will never cause even errors.

Step 2: Randomly simulate L input vectors for each fault in fault list – The value of L is a parameter for this procedure that allows tradeoffs between runtime versus accuracy.

Step 3: For any vector that causes an even error, perform bit-stripping – Select a bit in the input vector and flip its value to the opposite of its current value and fault simulate. If the error is no longer even, then the input bit is flipped back to its original value. Otherwise, the input bit is changed to an X since an even error occurs regardless of the value of that input bit. This process is repeated for all the bits in the input vector one by one. The order in which the bits are processed is selected randomly each time a new

vector is processed so that no particular order is repeated. The purpose of bit-stripping is to convert the input vector into an input cube that covers a large set of minterms.

Step 4: Add to the ON-set each input cube obtained in step 3 along with its corresponding output cube – Each input cube found in step 3 is fault simulated to obtain its corresponding 3-valued output cube. Together they specify a cube of minterms that are added to the ON-set of the *EVEN EDF* function.

The procedure above produces an approximation of the ON-set for the EVEN EDF function. Rather than simulating all of the input vectors for each fault (which would be exponential), only L vectors are simulated per fault where L is a user-specified value based on the desired level of accuracy in approximating the ON-set. Each input vector that causes an even error is expanded into a cube using bit-stripping. The resulting cube after bit-stripping contains many input vectors that also cause an even error. Some input vectors that cause an even error may not be found using this procedure because they may not be contained in any of the input cubes generated through bit-stripping. The larger the value of L, the more input cubes that are generated per fault and hence the less chance of missing an input vector that causes an even error for the fault. Missing input vectors that cause even errors means the ON-set for the EVEN EDF function will be missing minterms which may result in some loss of coverage. However, on the good side, the minterms that are included in the EVEN EDF function are contained in cubes (due to the way they were generated) and thus may simplify the logic implementation of the approximate EVEN EDF function compared to the exact EVEN EDF function that gives 100% coverage. The other source of approximation in the procedure is that one output cube is associated with all the input vectors contained in an input cube. In reality, of course, each input vector corresponds to only a single output vector and not a whole cube of output vectors. While the output cube is guaranteed to contain the correct output vector, it also contains many other output vectors thereby resulting in extra minterms being placed in the ON-set which should actually be in the DC-set. There is no risk of any minterms from the OFF-set ending up in the ON-set since the output cube always contains an even error (this is ensured by the way the bit-stripping is done) and thus it can never contain a fault-free output vector. The fact that the approximate ON-set contains some minterms from the DC-set does not impact the coverage at all. Potentially it could make the logic implementation of the approximate EVEN\_EDF function more complex compared with the exact EVEN\_EDF, but the fact that the additional minterms in the ON-set are contained in cubes (due to the way they were generated) the impact generally will not be significant.

Even though the experiments are performed with single stuck-at fault model, the proposed algorithm behaves in a conservative way for transient faults. If a transient fault is such that it causes an odd number of errors at the output when the corresponding stuckat fault causes an even number of errors, the fault will still be detected by the odd error detection circuit. This scenario may arise when the transient fault propagates to the outputs only through some of the possible paths (shorter paths) due to the transient nature of the fault. On the other hand if an even number of errors are caused at the output when the corresponding stuck-at fault causes an odd number of errors, by the transient fault, then there could be some loss of coverage because the corresponding input vector and faulty output pair was not included in the ON-set of the EVEN\_EDF function. However not all even errors are possible for each odd error. It will depend on the distribution of the long paths and short paths and probability of transient errors. Therefore there can only be minimal loss in coverage. Extensive path length analysis and transient error probabilities will be required to analyze the actual probability of transient errors causing an odd error to degenerate into even error. The faults in the CED circuitry will also be detected

because the CED circuitry is an irredundant part of the final synthesized circuit and we are considering only single fault at a time. Some patterns will eventually uncover the fault in the CED part. False alarms i.e. flagging error when there is no error are also not possible since the bit-stripping procedure ensures that none of the fault-free response vector and input vector combinations is part of the ON-set of the EVEN\_EDF function. Since the procedure is based on pure random sampling, no special ATPG is required to construct the EVEN\_EDF function. The proposed algorithm provides a very easy and efficient trade-off between simulation time and fault coverage by controlling the parameter *L*, while constructing the EVEN\_EDF function.

#### 2.4 COVERAGE VERSUS AREA OVERHEAD TRADEOFFS

If the coverage is not high enough, the procedure described in Sec. 2.3 can be repeated with a larger value of L to obtain a more accurate approximation of the EVEN EDF function and then the even error detecting circuit can re-synthesized.

If lower overhead is desired for the CED circuitry, a strategy for achieving this while minimizing the loss of coverage is as follows. When the input cubes are generated via bit-stripping in Step 3 of the procedure described in Sec. 2.3, a threshold can be set on the size of the cubes. If the size of the input cube is not larger than the threshold, then the input cube is simply discarded and not added to the ON-set. The reasoning behind this strategy is that small input cubes contain only a small number of input vectors while requiring a potentially large amount of logic to implement (depending on the extent to which they can be merged or factored with other cubes). By discarding these cubes, the impact on the overall coverage is minimal while the benefit in reducing overhead is substantial. This strategy can be very effective in trading off a small loss in coverage for a large reduction in overhead. This is one of the key advantages of the proposed schemes and will be highlighted in the experimental results.

#### 2.5 EXPERIMENTAL RESULTS

Experiments were performed on some MCNC benchmark circuits [Yang 91]. The area results for the circuits were obtained using Synopsis Design Analyzer. The area reported is the cell area.

Table 2.1 compares the area overhead for the self-checking circuits implemented using the duplication method and the proposed scheme. Both are non-intrusive and hence do not require re-synthesis of the functional logic. The circuit information and the optimized area for the MCNC benchmark circuits with no CED can be found under the first major heading. Under the second and third major headings the results corresponding to the duplication method and the proposed scheme are given, namely the area for the circuit with CED and the percentage area overhead compared with the optimized functional logic without CED. For the proposed scheme different tradeoffs between area overhead and coverage are shown. The last coverage/overhead entry for each circuit shows the case where no even error detecting circuit is used (i.e., where only single-bit parity is used). To increase coverage, the even errors have to be detected.

With a sufficiently large value of L, 100% coverage was obtained for most circuits to give a reference point. Note that the percentage area overhead was computed as follows:

% overhead = (area with CED – optimized area without CED) / (optimized area without CED)  $\times 100$

The coverage was computed in the manner described in Sec. 2.4 where faults were randomly injected in the functional logic and random patterns were simulated. The coverage is defined as the number of output vectors that contained errors that were detected by the CED. Of course, duplication always provides 100% coverage.

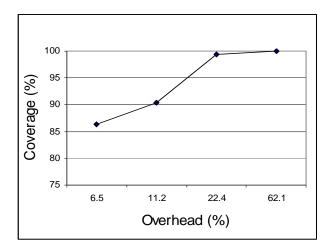

As can be seen from the results, significant reductions in area overhead can be achieved with relatively small reductions in coverage. It is interesting to note that in most cases, getting the last 1-2% of coverage is very expensive. By going from 100% down to 99-98% coverage, a significant reduction in the CED overhead can be achieved. The likely reason for this is that there are a number of hard to sensitize paths that lead to even errors. Since few patterns sensitize these paths, the probability of soft errors occurring along these paths is very small. However, detecting these soft errors requires a lot of hardware. This phenomenon is illustrated in Figs. 2.4-2.6 which are graphs of coverage versus overhead. As can be seen in these graphs, the CED hardware required to increase the coverage rises somewhat linearly until the coverage reaches the high 90's at which point a lot of hardware is required to detect the last few percent of soft errors. The proposed method provides a very efficient way to take advantage of this phenomenon by allowing the designer the option of reducing the CED overhead significantly with only small loss in coverage.

Table 2.1: Comparison of Proposed Method with Duplication

| Circuit |      |      | Duplication |       | Proposed |              |              |             |

|---------|------|------|-------------|-------|----------|--------------|--------------|-------------|

| Name    | Num. | Num. | Area        | Area  | Overhead | Area         | Overhead     | Coverage    |

|         | PI   | PO   |             |       | (%)      |              | (%)          | (%)         |

| apla    | 10   | 12   | 5348        | 12298 | 130.2    | 8252         | 54.3         | 100         |

|         |      |      |             |       |          | 7487         | 40.3         | 99.2        |

|         |      |      |             |       |          | 6417         | 20.5         | 88          |

|         |      |      |             |       |          | 6150         | 11.5         | 72.4        |

| br1     | 12   | 8    | 2876        | 6614  | 129.5    | 3756         | 30.6         | 100         |

|         |      |      |             |       |          | 3402         | 18.3         | 99.8        |

|         |      |      |             |       |          | 3258         | 13.3         | 91.2        |

| 1.1     | 20   | 7    | 0120        | 10040 | 122.5    | 3169         | 10.2         | 76.4        |

| chkn    | 29   | 7    | 8120        | 18940 | 133.5    | 16516        | 103.4        | 99.8        |

|         |      |      |             |       |          | 15687        | 93.2         | 98.7        |

|         |      |      |             |       |          | 15509        | 91.4         | 96.7        |

| 402     | 8    | 7    | 2021        | 7046  | 133.2    | 15395        | 89.6         | 90          |

| dc2     | 8    | /    | 3021        | 7046  | 133.2    | 4894         | 62.1<br>22.4 | 100         |

|         |      |      |             |       |          | 3697         |              | 99.4        |

|         |      |      |             |       |          | 3359         | 11.2         | 90.3        |

| 27/10   | 8    | 18   | 4176        | 9396  | 131.3    | 3217<br>5846 | 6.5          | 84.6        |

| exp     | 8    | 18   | 41/0        | 9396  | 131.3    | 5203         | 24.6         | 100         |

|         |      |      |             |       |          | 5094         | 22.2         | 97.4<br>80  |

|         |      |      |             |       |          | 4927         |              |             |

| i       | 4    | 7    | 1236        | 3414  | 176.2    | 2224         | 18.4<br>80.2 | 70.2<br>100 |

| wim     | 4    | /    | 1230        | 3414  | 170.2    | 2007         | 62.4         | 98.9        |

|         |      |      |             |       |          | 1928         | 56.3         | 80.2        |

|         |      |      |             |       |          | 1903         | 54.0         | 74.2        |

| 5xp1    | 7    | 10   | 2320        | 5220  | 125.0    | 4461         | 92.3         | 100         |

| элрт    | ,    | 10   | 2320        | 3220  | 123.0    | 4245         | 83.6         | 98          |

|         |      |      |             |       |          | 4129         | 78.4         | 88          |

|         |      |      |             |       |          | 4036         | 74.0         | 81          |

| b12     | 15   | 9    | 1208        | 3020  | 150.1    | 2356         | 110.2        | 100         |

|         |      |      |             |       |          | 2391         | 98.4         | 97.3        |

|         |      |      |             |       |          | 2379         | 97.6         | 78.4        |

|         |      |      |             |       |          | 2343         | 94.2         | 72.2        |

| cu      | 14   | 11   | 1180        | 3068  | 160.2    | 2950         | 150.1        | 100         |

|         |      |      |             |       |          | 2430         | 106.4        | 98.2        |

|         |      |      |             |       |          | 2289         | 94.3         | 72          |

|         |      |      |             |       |          | 2230         | 89.7         | 64.2        |

| sao2    | 10   | 4    | 2124        | 4885  | 129.9    | 3557         | 67.5         | 100         |

|         |      |      |             |       |          | 3241         | 52.6         | 97.8        |

|         |      |      |             |       |          | 3160         | 48.8         | 82          |

|         |      |      |             |       |          | 3107         | 46.3         | 71.3        |

| misex1  | 8    | 7    | 849         | 1970  | 132.0    | 1867         | 120.2        | 99.8        |

|         |      |      |             |       |          | 1793.1       | 112.1        | 99.2        |

|         |      |      |             |       |          | 1528.4       | 80.2         | 84          |

|         |      |      |             |       |          | 1446.2       | 70.4         | 76          |

Figure 2.4: Coverage vs. Overhead for dc2

Figure 2.5: Coverage vs. Overhead for misex1

Figure 2.6: Coverage vs. Overhead for br1

## **2.6 CONCLUSION**

The proposed method provides an efficient way to achieve high levels of soft error protection with reduced overhead. It is non-intrusive and thus does not require any modification to the functional logic itself.

# Chapter 3: Multiple Bit Upset Tolerant Memory Using a Selective Cycle Avoidance Based SEC-DED-DAEC Code

### 3.1 Introduction

Ionizing radiation from high-energy neutrons and alpha particles can cause a single-event upset (SEU) that may alter the state of the system resulting in a soft error. Memories, which occupy a large percentage of the area of a chip, are especially sensitive to SEUs. Constant technology process improvement has resulted in very dense memory cells that store information with less capacitance and lower voltage. Consequently, less charge is required to produce one or more soft errors in memories. Recent studies characterizing different bit errors arising from an SEU suggest that 1–5% of the SEUs can cause multiple bit upsets (MBUs) [Maiz 03]. Depending on the underlying technology and the incident particle, several types of multiple-bit errors are possible [Satoh 00], [Makihara 00], [Kawakami 04]. It has been shown that incident neutron particles can react with the die contaminants and generate secondary particles with enough energy to create multiple errors. The distance between the bits in error depends on the initial angle of incidence, die contaminant types, and the scattering angle for the secondary particles. Based on this, the probability of adjacent double bit errors is much higher than other multiple bit errors.

A SEC-DED code [Hamming 50] is capable of correcting one error and detecting all possible double errors. It is commonly used in memories and caches, but cannot correct more than a 1-bit error in a word. In order to correct the most commonly occurring MBUs, this chapter proposes a low cost ECC methodology to correct double adjacent bit errors. It involves constructing a single-error-correcting, double-error-detecting, double-adjacent-error-correcting (SEC-DED-DAEC) code by selectively

avoiding certain types of linear dependencies in the parity check matrix. A key feature of the proposed SEC-DED-DAEC code is that it uses the same number of check bits and has nearly identical syndrome generator/encoder area and timing overhead as the conventional SEC-DED codes. Consequently, there is very little additional cost to using it. Specific *H*-matrices for 16, 32 and 64-bit data words are given in the chapter, and their properties are directly compared with commonly used SEC-DED codes published elsewhere.

While the focus in the chapter is on SEC-DED-DAEC codes, the proposed methodology is flexible and can be used to construct codes for correcting any subset of double errors.

### 3.2 RELATED WORK

A number of approaches for extending the basic SEC-DED Hamming code [Hamming 50] have been previously proposed. A special class of SEC-DED codes known as Hsiao codes [Hsiao 70] was proposed to improve the speed, cost, and reliability of the decoding logic. The codes constructed in the proposed methodology can be thought of as a special class of Hsiao codes. Another class of SEC-DED codes [Reddy 78], [Chen 83] was proposed to detect any number of errors affecting a single byte. These codes are known as single-error-correcting double-error-detecting single-byte-error-detecting (SEC-DED-SBD) codes. For protecting byte-organized memories, SEC-DED-SBD codes are more suitable than the conventional SEC-DED code.

To provide byte error correction capability, single-byte-error-correcting, double-byte-error-detecting (SBC-DBD) codes [Berlekamp 68], [Reed 60], [Wolf 69], [Bossen 70] [Chen 96] were proposed. These codes perform at a higher order Galois field and consequently the encoding and decoding are more complex. Moreover, they require more check bits thereby increasing the size of the memory.

To provide complete double error correction capability, a double-error-correcting triple-error-detecting (DEC-TED) code may be used at the cost of much larger overhead in terms of both the check bits and more complex hardware to implement the error correction and detection [Lin 83], [Berlekamp 68], [Lala 78].

The Reed-Solomon (RS) code and Bose-Chaudhuri-Hocquenghem (BCH) codes are able to detect and correct multiple bytes of errors with very low overhead in terms of additional check bits required. However, these codes typically work at the block level and are applied to multiple words at a time. Other similar codes include the extended Hamming code [Bossen 70] which performs at a higher order Galois field GF ( $2^K$ ) and can correct up to k-bit burst errors. Other multiple error correcting codes include the optimal rectangular code (ORC), adaptive cross-parity code (APX) code, and others. The general drawbacks with these methods are latency and speed. Most of these codes require several cycles to correct the first error. Moreover, the encoding and decoding are much more complex and require several table lookups for multiplication in higher order fields.

Another class of multiple error-correcting approaches combines coding with circuit level techniques to sense multiple errors in a memory. In [Vargas 94] and [Calin 95], an asynchronous built in current sensor (BICS) on the vertical power lines of a memory along with a parity bit per memory word is used. A conventional SEC-DED code and the BICS approach are combined in [Gill 05] to detect multiple bit upsets affecting the same memory word.

Even though several powerful error correcting codes exist, the SEC-DED code has remained an attractive choice mainly because of its fast and simple encoding/decoding and low hardware overhead. One of the most commonly used techniques to minimize the probability of multiple bit upsets in a single word is *bit interleaving* [Maiz 04] which is a memory layout architecture in which physically adjacent bits are assigned

to different logical words. For k-way interleaving, k adjacent failing bits appear as k different single-bit errors in k different logical words rather than as a k-bit error in a single logical word. A simple SEC-DED code can be used along with bit interleaving to help protect from multiple bit upsets. However, there can be some limitations/drawbacks for bit interleaving. In some cases, it may negatively impact floorplanning, access time, and/or power consumption. The proposed SEC-DED-DAEC code requires very little overhead and can be used instead of or in addition to bit interleaving to provide greater flexibility for optimizing a memory design. For a fixed depth of interleaving, a larger physical distance between cells in error can be tolerated using the proposed code, or to tolerate a fixed physical distance of cells in error, the required depth of interleaving can be reduced. The proposed methodology places an additional tool in the hands of a memory designer for optimizing a memory layout. Moreover, for small memories, e.g., content addressable memory or register files, interleaving may not be feasible. The proposed coding methodology is particularly useful in this case to provide protection from MBUs.

A class of systematic SEC-DED-DAEC codes was proposed much earlier in [Abramson 59]. However, it was not targeted for memories. Its encoding and decoding are not as efficient as conventional SEC-DEC codes. One check bit is dedicated to differentiate between single and double bit errors. This check bit computes the parity of the entire message and hence incurs a lot of decoding delay and large decoder overhead. Moreover, the encoding and decoding involve the use of a linear finite state machine (LFSM) and hence the latency is increased. Some extensions of the basic code in [Abramson 59] have been suggested. In [Elspas 60], the SEC-DED-DAEC code was extended to higher order fields GF  $(2^K)$ , and in [Bernstein 63], the code was modified for arithmetic operations.

The ECC methodology proposed in this chapter constructs a different SEC-DED-DAEC code from the ones described in [Abramson 59], [Elspas 60], and [Bernstein 63]. The proposed SEC-DED-DAEC codes are targeted for memories and have the same number of check bits and nearly identical encoding and decoding latency as conventional SEC-DED codes. The proposed codes are constructed by selectively avoiding certain type of cycles in the parity check matrix. Moreover it tries to minimize the miscorrection (non-adjacent double error mistaken as an adjacent double error) probability.

### 3.3 BINARY LINEAR BLOCK CODES

The proposed SEC-DED-DAEC code falls into the category of systematic binary linear block codes. A binary (n, k) linear block code is a k-dimensional subspace of a binary n-dimensional vector space. An n-bit codeword of the code contains r=(n-k) check bits and k data bits. The  $(r \times n)$  parity-check matrix (H-matrix) completely defines the code. C is a codeword of the code if and only if

$$H.C^T = 0 (1)$$

where  $C^T$  is the transpose of the codeword C. The H-matrix corresponds to a systematic code if it can be represented as

$$H=[P_{r\times k},I_{r\times r}] \tag{2}$$

where I is the  $r \times r$  identity matrix. For a systematic code, the first k-bits of the codeword can be designated as the data bits and the last r bits can be designated as the check bits. For the targeted application, only systematic codes are useful. For a systematic code with a parity check matrix of the form given by Eqn. 2, the generator matrix can be simply obtained as

$$G = [I_{K \times K}, P^T] \tag{3}$$

The H-matrix represents a set of linear equations involving the bits of the message. The syndrome is defined as the r-bit vector obtained upon multiplying the

received n-bit message with the H-matrix in GF (2). In the error free case, the syndrome is the all-zero vector. An error vector is defined as an r-bit vector where the bits that are in error have the value 1 and all the other bits are 0. An erroneous message  $V_e$  can be represented as

$$V_e = V + E \tag{4}$$

where E is the error vector and V is the error free message (i.e., codeword).

$$S = H.V_e = H.(V+E) = H.V + H.E = H.E$$

(5)

where S is the syndrome for the particular message  $V_e$ . In the next section, we will discuss the proposed linear systematic block code.

### 3.4 PROPOSED CODE

The proposed SEC-DED-DAEC code has the following properties:

- 1. All single-bit errors can be corrected

- 2. All double bit errors can be detected

- 3. All adjacent double bit errors can be corrected

The miscorrection probability for non-adjacent double errors is reduced

The characteristics of a linear block code are completely determined by its Hmatrix. To detect all single-bit errors, the corresponding error syndromes should be

unique. Note that the syndrome for a single-bit error at the bit position p is the same as

the p-th column of the H-matrix. To uniquely identify all the single-bit errors, all the

columns of the H-matrix must be unique.

To detect all the double bit errors, the corresponding syndromes should be different from all the single-bit error syndromes. The syndrome for a double bit error is given by the exclusive-or (XOR) of the corresponding columns of the H-matrix. So there cannot be any 3-cycle in the H-matrix. A k-cycle refers to a set of k linearly dependent

columns of the parity check matrix, i.e., when XORed together, the output is an all-zero column. To be able to correct all the adjacent double bit errors, the syndromes for the adjacent double bit errors should be different from each other and also different from all the single-error syndromes. Next we define the conditions that must be satisfied by the *H*-matrix for the proposed code:

- 1. No all 0 columns.

- 2. All columns are distinct

- 3. No linear dependency involving 3 or less columns i.e., no 2-cycle and 3-cycle are allowed.

- 4. No linear dependency involving columns  $C_i, C_j, C_k, C_m$  where m > k > j > i, such that j = i + l and m = k + l.

Moreover the code tries to minimize the number of 4-cycles involving  $C_i$ ,  $C_j$ ,  $C_k$ ,  $C_m$  where m > k > j > i, such that j = i + l or k = j + l or m = k + l.

Condition 1 ensures that no single-bit error case match the error free case.

Condition 2 ensures that all the single error syndromes are unique. Every single error syndrome matches one of the columns of the H-matrix. Since all the columns of the H-matrix are distinct, the single-bit errors are uniquely identifiable and hence correctable. Additionally this condition ensures that there are no pairs of double errors of the form (i,j) and (j,k) such that the corresponding syndromes are the same. Assume that such double errors exist, then  $(C_i \oplus C_j) \oplus (C_j \oplus C_k) = 0$ , i.e.,  $(C_i \oplus C_k) = 0$  but that contradicts the fact that all the columns of the H-matrix are distinct. This ensures that syndromes for adjacent errors of the form (i,i+1) and (i+1,i+2) are different.

Condition 3 ensures that the syndromes for all double bit errors are different from that of the single-bit errors. The syndrome for a double bit error is determined by the XOR of the columns corresponding to the erroneous bit positions. If the *H*-matrix is free

of 3-cycles then the XOR of any two columns of the *H*-matrix is not identical to any of the columns of the *H*-matrix. This ensures that the syndromes of all the double bit errors are different from the single-bit error syndromes, and condition 2 ensures that the double bit error syndromes are non-zero. Hence all the double bit errors are detectable.

Condition 4 along with condition 2, ensures that a syndrome for an adjacent double bit error is different from all other adjacent double bit error syndromes. If we assume that the only errors are single-bit errors or adjacent double bit errors, then with an *H*-matrix satisfying conditions 1 through 4, we can uniquely identify the syndromes for all single-bit errors and adjacent double bit errors and hence can correct all single-bit errors and all double adjacent bit errors and detect all double bit errors.

$$Pr (miscorrection) = \frac{\#4BC}{C_2^n - (n-1)}$$

(6)

While constructing the *H*-matrix, an effort is made to reduce the miscorrection probability by keeping the number of 4BCs small. While designing the *H*-matrix,

additional constraints can be imposed to reduce the encoding and decoding overhead. This can be achieved by limiting the number of 1's in any row of the *H*-matrix.

### 3.5 CODE DESIGN PROCEDURE

The design of the *H*-matrix is essentially a systematic search process to satisfy all the conditions mentioned in the previous section. For an  $(r \times n)$  matrix, there are  $2^{(r \times n)}$  possible choices, so an exhaustive search approach is ruled out for reasonably large values of r and n. Figure 3.1 shows a H-matrix for a (22,16) code. Even for this code, an exhaustive search is not practical even if the domain of columns considered is restricted. The *weight* of a column of the H-matrix is defined as the number of 1's in the column. If we limit the H-matrix to only weight-3 and weight-1 columns, then there are  $C_3^6 = 20$  choices out of which 16 columns can be chosen in  $C_{16}^{20} = 4845$  ways. For each choice there are  $(16! > 2 \times 10^{13})$  column permutations which should be searched for the best code. So an exhaustive search will have to search  $(4845 \times 16!) > (2 \times 10^{13})$  matrices for the best code. The search space increases further if arbitrary weighted columns are allowed. Note that For the H-matrix in Fig. 3.1, no column of weight two is allowed because any weight-2 column will create a 3-cycle with two weight-1 columns.

Constructing the best *H*-matrix for a SEC-DED-DAEC code that satisfies all of the conditions discussed in Sec. 3.4 is NP-complete. A pseudo-greedy search procedure can be used as shown in Fig. 3.3. The outer while loop stops once a valid code is found or the maximum backtrack limit is exceeded. The inner while loop finds a set of valid columns (that does not introduce any forbidden cycles) for the current column position. If no valid column is found for the current column position, then the last choice for a column has to be undone. This corresponds to a backtrack. If multiple valid columns are found for the current column position then the one that minimizes the number of bad 4-cycles in the currently constructed code space is chosen. Once an initial *H*-matrix is

found, a limited number of column permutations are tried to avoid a local optimum and search for a better *H*-matrix in terms of reduced miscorrection probability.

Figure 3.1: *H*-matrix for proposed (22,16) code

Figure 3.2: *H*-matrix for proposed (39,32) code

```

Input: n, maxIter, maxBacktrack, maxPermute

Output: H-matrix

avail\_col = All\ 1-weight columns, followed by 3-weight columns, followed by 5-weight columns, and so forth up to the largest weight columns being considered

currentCol = 0; backtrack = 0

while (currentCol < n) {

Iter = 0

```

```

validColPool[currentCol] = {}

while ( iter < maxIter ) {

Iter++

C = Untried least-weighted column from avail col

Check for existence of forbidden 4-cycles

if (! 4FCfound) {

validColPool[currentCol] =

validColPool[currentCol] \cup C }

}

if ( empty(validColPool[currentCol]) ) {

backtrack++

if ( backtrack > maxBacktrack ) {

// no code found

return

} else {

currentCol--

if (currentCol < 0) currentCol = 0;

continue;

} } else {

sCol = selectMin4BC(validColPool[currentCol]))

add sCol to H-matrix

currentCol++

backtrack=0;

}}

permuteC = 0; orig4BC=count4BC(H-matrix);

while ( permuteC < maxPermute) {</pre>

permuteC++

permuteColumns()

Check for existence of forbidden 4-cycles

if ((!4FC)&&(count4BC(H-matrix)<orig4BC)) {

```

# H-matrix ← current H-matrix; }}

Figure 3.3: Pseudo-greedy search algorithm

Figure 3.4: *H*-matrix for proposed (72,64) code

Table 3.1: Comparison of proposed SEC-DED-DEAC code with other codes

| (n,k)   | Codes                         | 2-    | Max   | Forbidden | Total 4- | Bad 4- |

|---------|-------------------------------|-------|-------|-----------|----------|--------|

|         |                               | Input | Logic | 4-Cycles  | Cycles   | Cycles |

|         |                               | XOR   | Depth | (4FC)     |          | (4BC)  |

|         |                               | Gates |       |           |          |        |

|         |                               |       |       |           |          |        |

|         | SEC-DED (IBM system/3)        | 48    | 4     | 13        | 252      | 122    |

|         | Hsiao Code [Hsiao 70]         | 48    | 4     | 8         | 252      | 120    |

|         | SEC-DED-DAEC in [Abramson 59] | 70    | 5     | 0         | 252      | 128    |

| (22,16) | Proposed SEC-DEC-DAEC (Fig.   | 48    | 4     | 0         | 251      | 118    |

|         | 3.1)                          |       |       |           |          |        |

|         | SEC-DED (IBM 8130)(40,32)     | 96    | 4     | 82        | 776      | 254    |

|         | Hsiao Code [Hsiao 70]         | 96    | 4     | 23        | 1363     | 425    |

|         | SEC-DED-DAEC in [Abramson 59] | 132   | 6     | 0         | 1343     | 386    |

| (39,32) | Proposed SEC-DED-DAEC (Fig.   | 96    | 4     | 0         | 1363     | 379    |

|         | 3.2)                          |       |       |           |          |        |

|         | SEC-DED (IBM 3081)            | 256   | 6     | 230       | 8912     | 1292   |

|         | Hsiao Code [Hsiao 70]         | 208   | 5     | 122       | 8392     | 1399   |

|         | SEC-DED-DAEC in [Abramson 59] | 296   | 7     | 0         | 8194     | 1335   |

| (72,64) | Proposed SEC-DED-DAEC (Fig.   | 224   | 5     | 0         | 8289     | 1316   |

|         | 3.4)                          |       |       |           |          |        |

The number of the 2-input XOR gates required for the encoding/decoding can be computed from the H-matrix. It is equal to  $\sum_{\#rows} (row \ weight - 1)$ . The encoding and decoding delays are determined by the maximum logic-depth of the encoder and the decoder circuit which is equal to  $log_2$  (max. 1's in any row). Figure 3.2 shows an H-matrix for the (39,32) code constructed using the search process as discussed above using only weight-1 and weight-3 columns. Another H-matrix is shown for a (72,64) code in Fig. 3.4. In this case, weight-1, weight-3, and weight-5 columns are used.

Table 3.1 shows the number of XOR gates and maximum logic depth for the syndrome generator, number of forbidden 4-cycles, total number of 4-cycles, and the number of bad cycles (4BCs) for the (22, 16), (39, 32) and (72,64) codes for both the proposed code and the SEC-DED-DAEC code described in [Abramson 59] as well as some Hsiao codes and SEC-DED codes commonly used in industry. Note that the SEC-DED code and the Hsiao code cannot correct adjacent double bit errors because of the existence of forbidden cycles (4FCs). The check-bit overhead for a random double error correcting code (DEC) is unacceptably high. For example to protect a 32-bit word, a DEC needs at least 11 check bits. To protect a 64-bit word, a DEC code needs 14 check bits. Using a DEC code can increase the memory size considerably and hence is not an attractive choice for memory ECC. The XOR gate overhead for the proposed code is similar to that of the Hsiao code. The proposed code also has minimal logic depth among the codes and also minimum check bit overhead. The total number of bad 4-cycles is lower for the proposed code than for [Abramson 59], and consequently it has a lower miscorrection probability.

### 3.6 ECODING /DECODING ALGORITHM

The proposed code is systematic. During encoding, the data bits can be directly copied and the check bits are generated using an XOR network corresponding to the *G*-matrix. The decoding algorithm is as follows:

- 1. Generate the syndrome using an XOR network corresponding to the *H*-matrix.

- 2. If the syndrome is the all zero vector, then no error is detected, otherwise one or more errors occurred.

- 3. If the syndrome matches any of the *H*-matrix columns, then a single error is detected and the error position is the corresponding column position. The corresponding bit should be flipped to correct the error.

- 4. Else if the syndrome matches any of the *n-1* adjacent double error syndromes, then a double adjacent error is detected and the corresponding bit positions are generated using the error correction logic.

- 5. Else an uncorrectable error (UE) (i.e., a double non-adjacent error or more than two errors) has occurred.