Copyright

by

Junghyo Nah

2010

# The Dissertation Committee for Junghyo Nah Certifies that this is the approved version of the following dissertation:

# High Performance Germanium Nanowire Field-Effect Transistors and Tunneling Field-Effect Transistors

| Committee:                |

|---------------------------|

|                           |

| Emanuel Tutuc, Supervisor |

|                           |

| Sanjay K. Banerjee        |

|                           |

| Jack C. Lee               |

|                           |

| Ananth Dodabalapur        |

|                           |

| Leonard F. Register       |

|                           |

| Li Shi                    |

# High Performance Germanium Nanowire Field-Effect Transistors and Tunneling Field-Effect Transistors

by

Junghyo Nah, B. E.; M. S. E.

## Dissertation

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin

December, 2010

# **Dedication**

To my wife and parents for their love and support

## Acknowledgements

I would like to express my sincere gratitude to my advisor Prof. Emanuel Tutuc for his outstanding guidance and support. It is great honor to become his first graduate. His patience, enthusiasm, and encouragement were contributed to the success of my research. In addition to his academic guidance, I would also like to thank for his friendship.

I would like to acknowledge Prof. Sanjay K. Banerjee, Prof. Jack Lee, Prof. Leonard F. Register, Prof. Ananth Dodabalapur, and Prof. Shi Li for serving as my dissertation committee and for their constructive comments and guidance in my dissertation work.

During my years at the University of Texas at Austin, I learned a lot from my friends and colleagues and I would like to acknowledge them for their helpful discussions and collaborations, En-Shao, Kamran, Babak, Dave, Seyoung, Kayoung, Micha, Beomseok, Jaehyun, Jaehun, Jamil, Fahmida, Jiwon, Dr. Jooyun Jung, Dr. Yonghyun Kim, Dr. Domingo Ferrer, Dr. Kazunori Hoshino and Dr. Davood Shahrjerdi. I am especially thankful to En-Shao and Babak for their sincere friendship in every circumstance. I would like to thank Dr. Ravi Pillarisetty at Intel for helping me to have invaluable experience at the prestigious research institution. I am also thankful to the entire Microelectronics Research Center staff for their support.

I should also express my gratitude to my old friends for their friendship, especially ByungKwon, JongHun, SangWook, SooHo, ChanWui, ChangGyu, KiWon, JiHyun, HyunJin, JiYoon, SungHo, JeongSik, JongHyuk, and JeongSoo.

Finally, I would like to express special thanks to my parents. I would not be where I am without their endless love, dedication, and support. I would also like to thank

my sister Young Sim and my sister-in-law Hyun Soo for their support and love. My deepest gratitude goes to my lovely wife, Soo Young, who has always been on my side during good and bad times. My life has been blessed ever since I first meet her. Thanks to her love and companionship, every moment of life is being beautifully scripted in my memory.

# High Performance Germanium Nanowire Field-effect Transistors and Tunneling Field-effect Transistors

| Publication No. |  |

|-----------------|--|

|-----------------|--|

Junghyo Nah, Ph. D.

The University of Texas at Austin, 2010

Supervisor: Emanuel Tutuc

The scaling of metal-oxide-semiconductor (MOS) field-effect transistors (FETs) has continued for over four decades, providing device performance gains and considerable economic benefits. However, continuing this scaling trend is being impeded by the increase in dissipated power. Considering the exponential increase of the number of transistors per unit area in high speed processors, the power dissipation has now become the major challenge for device scaling, and has led to tremendous research activity to mitigate this issue, and thereby extend device scaling limits. In such efforts, non-planar device structures, high mobility channel materials, and devices operating under different physics have been extensively investigated. Non-planar device geometries reduce short-channel effects by enhancing the electrostatic control over the channel. The devices using high mobility channel materials such as germanium (Ge), SiGe, and III-V can outperform Si MOSFETs in terms of switching speed. Tunneling field-effect transistors use interband tunneling of carriers rather than thermal emission, and can

potentially realize low power devices by achieving subthreshold swings below the thermal limit of 60 mV/dec at room temperature.

In this work, we examine two device options which can potentially provide high switching speed combined with reduced power, namely germanium nanowire (NW) field-effect transistors (FETs) and tunneling field-effect transistors (TFETs). The devices use germanium (Ge) – silicon-germanium (Si<sub>x</sub>Ge<sub>1-x</sub>) core-shell nanowires (NWs) as channel material for the realization of the devices, synthesized using a 'bottom-up' growth process. The device design and material choice are motivated by enhanced electrostatic control in the cylindrical geometry, high hole mobility, and lower bandgap by comparison to Si. We employ low energy ion implantation of boron and phosphorous to realize highly doped contact regions, which in turn provide efficient carrier injection. Our Ge-Si<sub>x</sub>Ge<sub>1-x</sub> core-shell NW FETs and NW TFETs were fabricated using a conventional CMOS process and their electrical properties were systematically characterized. In addition, TCAD (Technology computer-aided design) simulation is also employed for the analysis of the devices.

## **Table of Contents**

| List of Tables xii                                                                                                    |   |

|-----------------------------------------------------------------------------------------------------------------------|---|

| List of Figures xiii                                                                                                  |   |

| CHAPTER 1: RESEARCH BACKGROUND 1                                                                                      |   |

| 1.1 Motivation1                                                                                                       |   |

| 1.2 Challenges in device scaling                                                                                      |   |

| 1.3 Future transistor options                                                                                         |   |

| 1.3.1 Gate-all-around device structure                                                                                |   |

| 1.3.2 High mobility channel material10                                                                                |   |

| 1.3.3 Tunneling field-effect transistors                                                                              |   |

| 1.4 Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell nanowires for field-effect and tunneling field-effect transistors | S |

| 1.5 Chapter organization                                                                                              |   |

| CHAPTER 2: GROWTH AND DOPING OF GERMANIUM NANOWIRES 17                                                                |   |

| 2.1 Growth of Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell nanowires                                               |   |

| 2.2 Doping of semiconductor nanowires                                                                                 |   |

| 2.2.1 Metal-Semiconductor contacts                                                                                    |   |

| 2.2.2 Nanowire doping techniques                                                                                      |   |

| 2.3 Doping of Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell nanowires using low energy ion implant                  |   |

| 2.3.1TRIM simulation                                                                                                  |   |

| 2.3.2 Fabrication of back-gated Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NW FETs29                             |   |

| 2.3.3 Capacitance calculation                                                                                         |   |

| 2.3.4 Electrical characterization of boron doped Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell nanowires            |   |

| 2.3.5 Electrical characterization of phosphorus doped Ge-Si <sub>x</sub> Ge <sub>1-x</sub> coreshell nanowires        |   |

| 2.3.6 Ni-nanowire contact resistances in doped Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NWs                    |   |

| 2.4 Summary                                                                                                           |   |

| CHAPTER 3: HIGH PERFORMANCE GERMANIUM NANOWIRE FIELD-EFFECTRANSISTORS                                                  | CT 50     |

|------------------------------------------------------------------------------------------------------------------------|-----------|

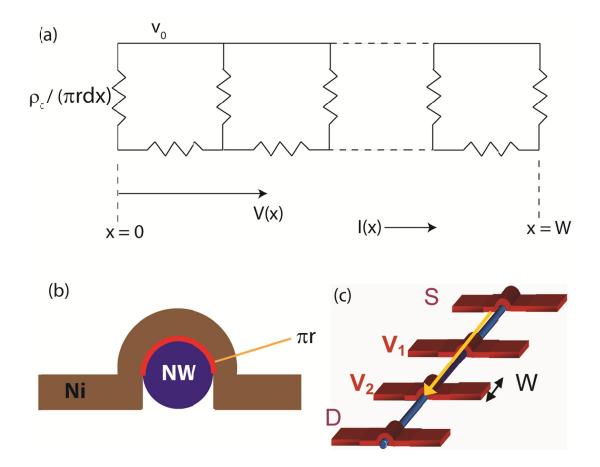

| 3.1 Fabrication process of $\Omega$ -shaped gate Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NV                    |           |

| 3.2 Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NW FETs with highly doped source and                               |           |

| 3.3 Scaling properties of Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NW FETs                                      | 58        |

| 3.3.1 Electrical characteristics                                                                                       | 59        |

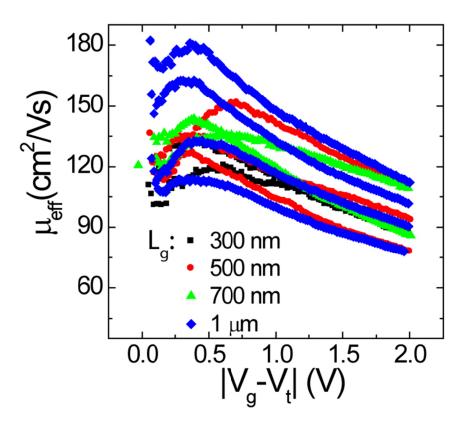

| 3.3.2 Effective mobility                                                                                               | 61        |

| 3.3.3 Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NW FETs benchmarking                                             | 65        |

| 3.3.4 Short-channel effects                                                                                            | 69        |

| 3.3.5 TCAD simulation results                                                                                          | 72        |

| 3.4 Performance dependence on SiGe shell contents                                                                      | 78        |

| 3.5 Summary                                                                                                            | 85        |

| CHAPTER 4: GERMANIUM NANOWIRE TUNNELING FIELD-EFFECT TRANS                                                             | ISTORS 87 |

| 4.1 Fabrication process of Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NW TFETs                                    | 88        |

| 4.2 Electrical characteristics of Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell TFETs                                | 91        |

| 4.2.1 Principle of NW TFET operation                                                                                   | 92        |

| 4.2.2 Diode characteristics                                                                                            | 93        |

| 4.2.3 Output and transfer characteristics                                                                              | 94        |

| 4.2.4 Suppression of ambipolar behavior                                                                                | 97        |

| 4.2.5 Temperature dependent device characteristics                                                                     | 99        |

| 4.3 Diffusion of boron and phosphorus in germanium                                                                     | 102       |

| 4.4 Flash-assisted rapid thermal process                                                                               | 105       |

| 4.5 Dopant activation of phosphorus-implanted nanowires using flas rapid thermal process                               |           |

| 4.6 Enhanced-performance of Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NW TFETs us assisted rapid thermal process |           |

| 4.7 Summary                                                                                                            | 115       |

| CHAPTER 5: SUMMARY AND FUTURE WORKS                                                                                    | 116       |

| 5.1 Summary                                                                                                            | 116       |

| 5.2 Suggestion for future work                                                                                         | 119       |

| Refere | rences | 121 |

|--------|--------|-----|

|        |        |     |

| Vita   |        | 131 |

## **List of Tables**

| Device fabrication process flow of back-gated NWFETs31                                      | Table 2-1: |

|---------------------------------------------------------------------------------------------|------------|

| Ion-implanted NW resistivities and NW-to-Ni contact resistances 48                          | Table 2-2: |

| Device fabrication process flow of Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NW FETs. | Table 3-1: |

| 52                                                                                          |            |

| Ion-implanted NW resistivities and NW-to-Ni contact resistances 90                          | Table 4-1: |

| P-implanted NW resistivities and NW-to-Ni contact resistances109                            | Table 4-2: |

# **List of Figures**

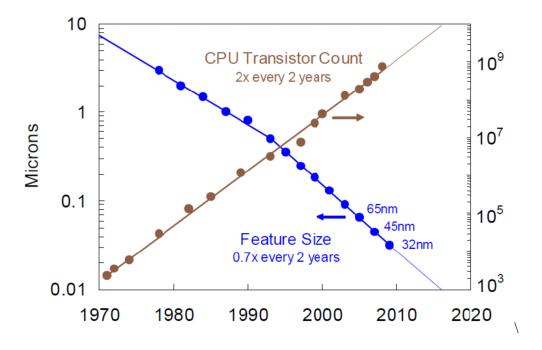

| Figure 1-1: | Historical scaling trend of CMOS following Moore's law [4]1                         |

|-------------|-------------------------------------------------------------------------------------|

| Figure 1-2: | Scaling of MOSFETs below sub 100 nm regime [source: Intel]2                         |

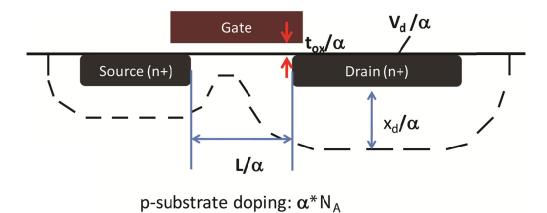

| Figure 1-3: | Schematic of MOSFET indicating device scaling parameters3                           |

| Figure 1-4: | Schematic of MOSFET indicating leakage current sources4                             |

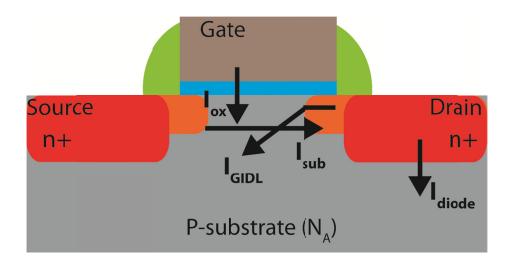

| Figure 1-5: | (a) The ideal switch instantly turns ON/OFF (b) The $I_d$ - $V_g$                   |

|             | characteristicsof a MOSFET showing a subthreshold swing of 60                       |

|             | mV/dec at room temperature (black line). The I <sub>OFF</sub> and SS can be further |

|             | increased due to short-channel effects (orange line) (c) Energy band                |

|             | profile of a conventional n-type FET. The carrier injection depends on              |

|             | the thermionic emission of electrons over the potential barrier in the              |

|             | channel6                                                                            |

| Figure 1-6: | Power density vs. gate length. The data demonstrate that the                        |

|             | subthreshold power consumption approaches to the active power                       |

|             | consumption at short channel lengths. [40]                                          |

| Figure 1-7: | Device structures providing enhanced gate control over the channel (a)              |

|             | FinFET [9] (b) Tri-gate FET [16] (c) Ω-gated FET [11] (d) Gate-all-                 |

|             | around (GAA) FET [17]9                                                              |

| Figure 1-8: | V <sub>t</sub> roll-off, SS, and DIBL are not affected by the gate length scaling,  |

|             | demonstrating immunity to short-channel effect due to GAA device                    |

|             | geometry realized along a NW [17]10                                                 |

|             | geometry realized along a NW [17]10                                                 |

| Figure 1-9:  | (a)Schematic representation of a TFET structure, having a n-doped                           |

|--------------|---------------------------------------------------------------------------------------------|

|              | source, a p-doped drain, and a gated intrinsic channel. (b) Energy band                     |

|              | profile along a TFET. The carrier injection into the channel relies on                      |

|              | BTBT, which enables the SS smaller than 60 mV/dec12                                         |

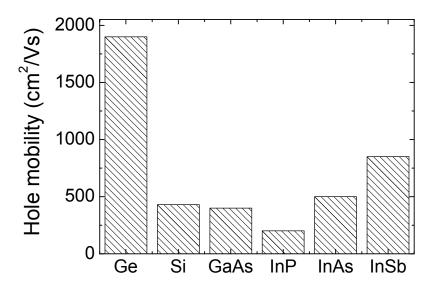

| Figure 1-10: | Hole mobility of the group IV semiconductors and group III-V                                |

|              | compound semiconductors                                                                     |

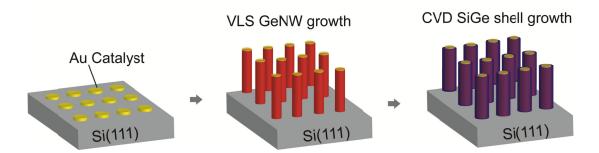

| Figure 2-1:  | Schematics of the Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NW growth process. The Au |

|              | droplets form during the H <sub>2</sub> anneal and serve as a catalyst for VLS Ge           |

|              | NW growth. After Ge NW growth, the Ge surface is passivated with                            |

|              | $Si_xGe_{1-x}$ shell                                                                        |

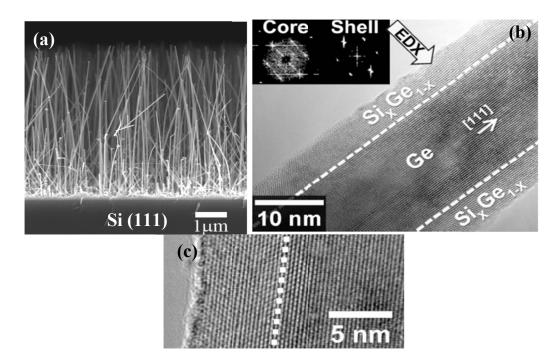

| Figure 2-2:  | SEM and TEM of Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NWs (a) Cross sectional SEM  |

|              | showing an epitaxial NW growth on Si(111) substrate (b) TEM                                 |

|              | micrograph of a NW and Fourier transform of core and shell region (c)                       |

|              | High resolution TEM of the same NW. The dashed lines in (b), (c)                            |

|              | indicate the interface between the core and shell of a NW [62]19                            |

| Figure 2-3:  | Energy band diagram of a metal-semiconductor contact in thermal                             |

|              | equilibrium                                                                                 |

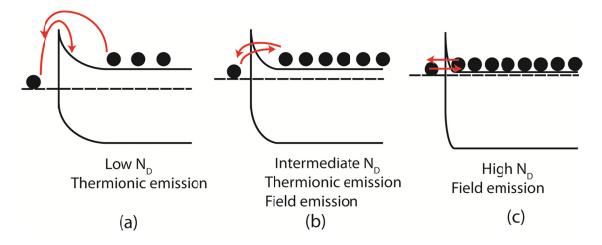

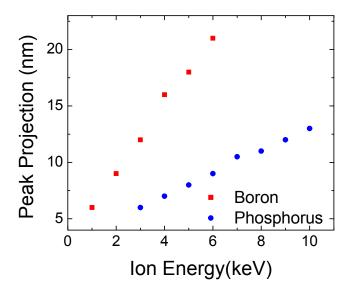

| Figure 2-4:  | The conduction mechanism for a metal contact to <i>n</i> -type substrate. (a)               |

|              | Metal contact on a lightly doped substrate. Electron flows as a result of                   |

|              | thermionic emission over the potential barrier (b) Metal contact on a                       |

|              | substrate with an intermediate doping level. Thermionic-field emission                      |

|              | dominates (c) Metal contact on a highly doped substrate. Electron                           |

|              | tunneling dominated conduction [66]21                                                       |

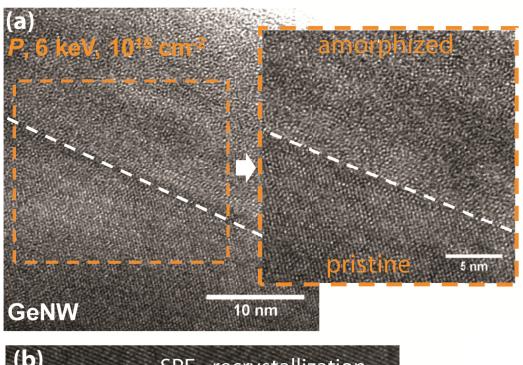

| Figure 2-5:   | (a) Phosphorus-implantation damaged Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell nanowire  |

|---------------|-----------------------------------------------------------------------------------------------|

|               | (energy: 6 keV, dose: $10^{15}$ cm <sup>-2</sup> ). The white-dashed line shows the           |

|               | boundary between the amorphized NW and the pristine NW (b) Solid-                             |

|               | phase-epitaxy (SPE) recrystalized NW using thermal anneal24                                   |

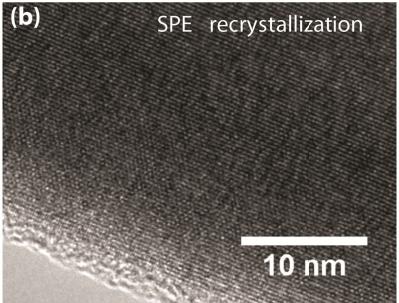

| Figure 2-6:   | Peak projection range of boron and phosphorus in a Ge substrate as a                          |

|               | function of ion energy (TRIM simulation)                                                      |

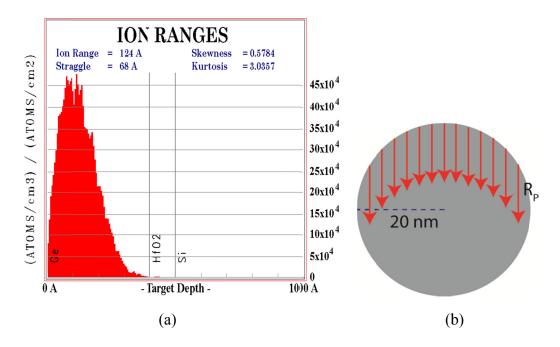

| Figure 2-7:   | (a) Boron distribution in a Ge layer. The boron atoms are implanted at the                    |

|               | energy of 3 keV. Ge layer represents Ge NW on a $HfO_2/Si$ substrate.                         |

|               | The peak concentration of implanted B is located at ~12 nm. (b)                               |

|               | Schematic representation of B peak distribution in a NW using the R <sub>P</sub> in           |

|               | TRIM simulation                                                                               |

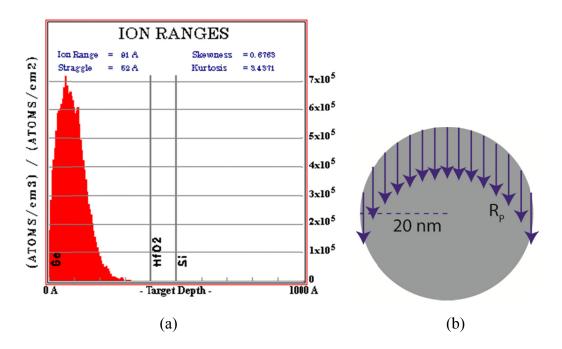

| Figure 2-8:   | (a) Phosphorus distribution in a Ge layer. Phosphorus atoms are                               |

|               | implanted at the energy of 6 keV. Ge layer represents Ge NW on a                              |

|               | $HfO_2/Si$ substrate. The peak concentration of implanted P is located at 9                   |

|               | nm. (b) Schematic representation of P peak distribution in a NW using                         |

|               | the R <sub>P</sub> in TRIM simulation. 28                                                     |

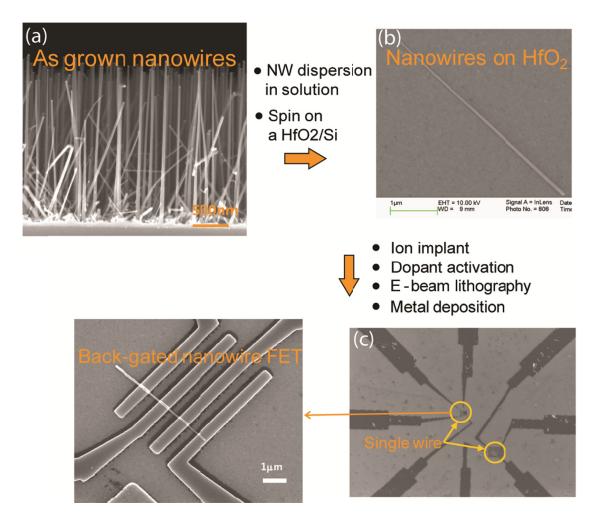

| Figure 2-9: 1 | Fabrication process of back-gated NW FETs with multi-terminal contacts.                       |

|               | (a) As-grown $Ge-Si_xGe_{1-x}$ core-shell NW on a Si (111) substrate (b)                      |

|               | Dispersion of NWs on a HfO <sub>2</sub> /Si substrate (c) Back-gated NW FETs                  |

|               | with multi terminal contacts                                                                  |

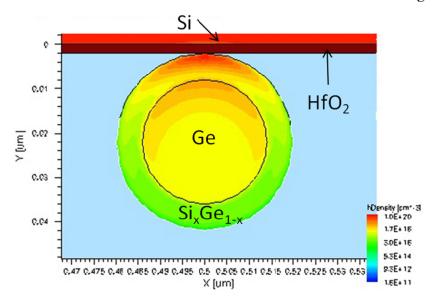

| Figure 2-10   | : Schematic representation of a back-gated Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NW |

|               | FET used in the simulation. Holes are mainly populated at the interface                       |

|               | between a NW and substrate                                                                    |

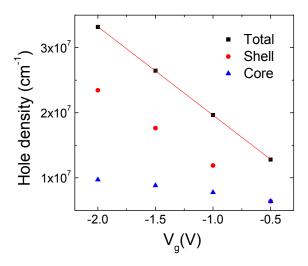

| Figure 2-11:  | Total hole density vs. gate voltage. The total hole density is the sum of                     |

|               | the hole density in the NW core and shell                                                     |

| Figure 2-12: | Capacitance vs. NW diameter (d) for each nanowire doping condition                            |

|--------------|-----------------------------------------------------------------------------------------------|

|              | (intrinsic, highly doped and metallic NW condition). The capacitances                         |

|              | were calculated using $C_L = e \cdot (dp/dVg)$ . Blue triangles represent the                 |

|              | capacitance values calculated using finite element method (Ansoft Q3D                         |

|              | Extractor®) by assuming a metallic NW                                                         |

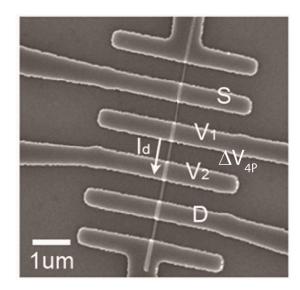

| Figure 2-13: | SEM of a NW device used for electrical characterization. The drain                            |

|              | current $(I_d)$ flows from source $(S)$ to drain $(D)$ , and $V_1$ and $V_2$ are used to      |

|              | probe the voltage drop ( $\Delta V_{4p}$ ) along the NW34                                     |

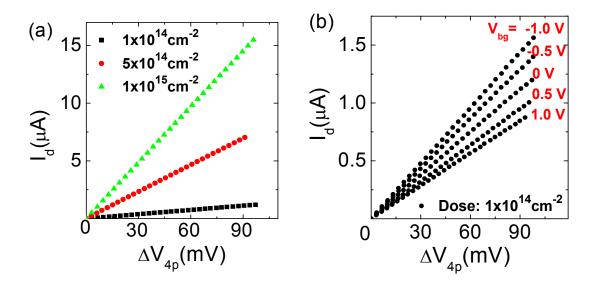

| Figure 2-14: | (a) $I_d$ vs $\Delta V_{4p}$ data measured for NWs implanted with different B doses.          |

|              | The data show a conductance increase with the implant dose. (b) $I_d$ vs                      |

|              | $\Delta V_{4p}$ measured at different $V_{bg}$ values for a B-implanted NW with a dose        |

|              | of 10 <sup>14</sup> cm <sup>-2</sup> [70] [Sample:Ge52AB001~B003]35                           |

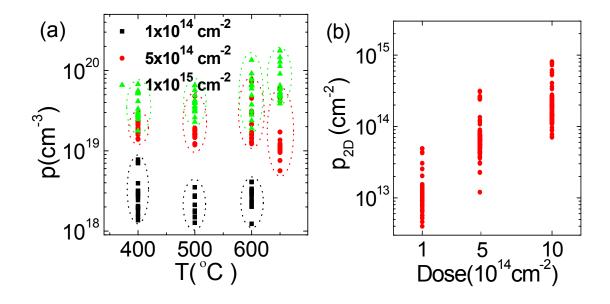

| Figure 2-15: | (a) Activated dopant concentration $(p)$ vs the activation temperature $(T)$                  |

|              | for different implant doses. (b) Activated dopant dose per unit area $(p_{2D})$               |

|              | vs the implant dose. These data show that roughly 15%-25% of the                              |

|              | implanted ions are active dopants in the NWs [70]. [Sample:                                   |

|              | Ge52A_B001~B011]37                                                                            |

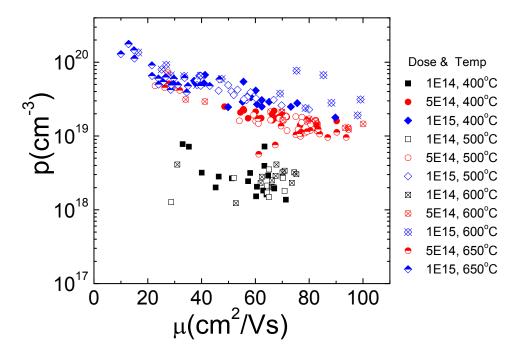

| Figure 2-16: | Doping concentration $(p)$ vs mobility $(\mu)$ for different implant doses and                |

|              | activation temperatures. These data show that implant doses above 5 $\times$                  |

|              | $10^{14}  \mathrm{cm}^{-2}$ follow the general relation between doping density vs mobility.   |

|              | 38                                                                                            |

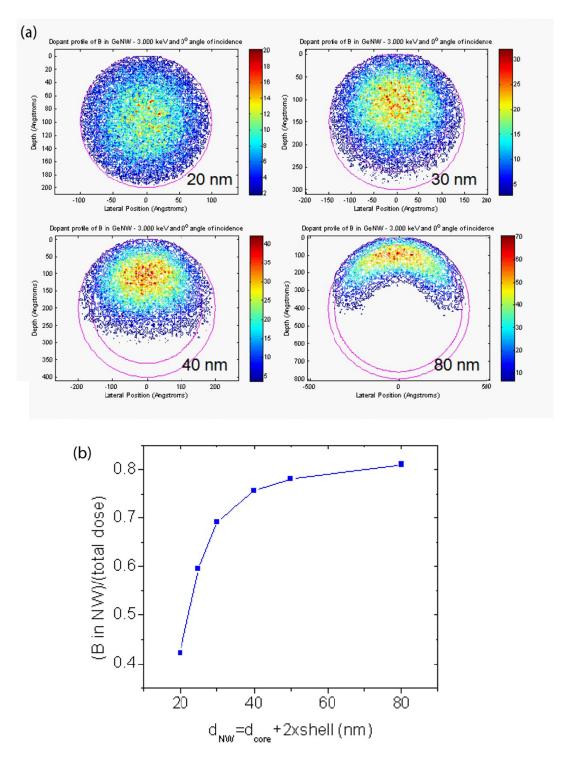

| Figure 2-17: | (a) Implanted boron distributions in Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NWs with |

|              | different diameters (ion energy: 3keV) (b) Dopant loss as a function of                       |

|              | the NW's diameter. Dopant loss is higher for NWs with smaller                                 |

|              | diameters                                                                                     |

xvi

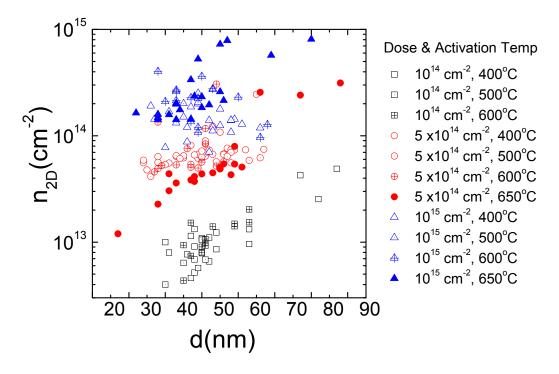

| Figure 2-18: Activated dopant dose per unit area vs nanowire diameter (d) for each                  |

|-----------------------------------------------------------------------------------------------------|

| ion implant dose, demonstrating higher dopant loss due to lateral                                   |

| straggle for the NWs with smaller diameters                                                         |

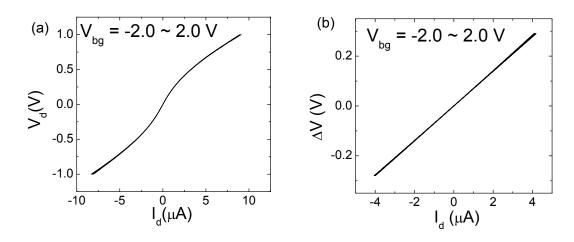

| Figure 2-19: Representative current vs voltage characteristics of phosphorus doped                  |

| NWs (P dose: $10^{15}$ cm <sup>-2</sup> , RTP: 400 °C for 5 min) (a) $I_d$ - $V_d$ characteristics  |

| of a back-gated NW FET measured using a 2-point configuration for                                   |

| different gate voltages, $V_{bg}$ = -2.0 $\sim$ 2.0 V. Non linear characteristics                   |

| were observed at low drain bias condition. (b) $I_d$ - $V_d$ characteristics of a                   |

| back-gated NW FET measured in a 4-point configuration for different                                 |

| gate voltages, $V_{bg}$ = -2.0 $\sim$ 2.0 V. Gate dependence was very weak for                      |

| all devices, consistent with high doping level. ctivated dopant dose per                            |

| unit area vs nanowire diameter (d) for each ion implant dose,                                       |

| demonstrating higher dopant loss due to lateral straggle for the NWs                                |

| with smaller diameters41                                                                            |

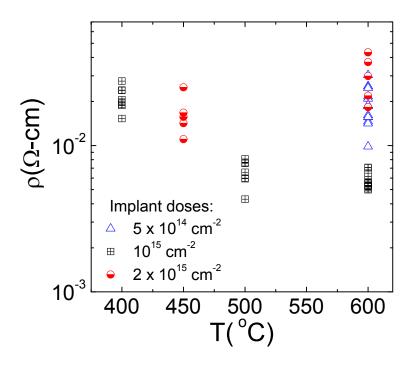

| Figure 2-20: Resistivities ( $\rho$ ) vs the activation temperature ( $T$ ) for different P-implant |

| doses. [Index: Ge48P002,P004,P009,P010,P011]42                                                      |

| Figure 2-21: Resistivities ( $\rho$ ) vs NW's diameters for different P-implant doses,              |

| activated at 600°C. [Index: Ge48P002,P004,P009,P010,P011]43                                         |

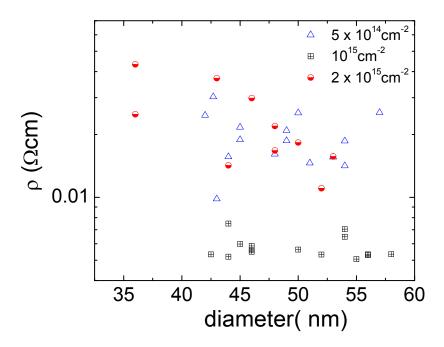

| Figure 2-22: (a) Transmission line model for a metal/semiconductor nanowire                         |

| contact. (b) Schematic representation of metal (Ni) deposited on a NW.                              |

| The line denotes the circumference of the NW in contact with the                                    |

| deposited Ni. (c) Schematic representation of a multi-terminal device                               |

| used for device characterization                                                                    |

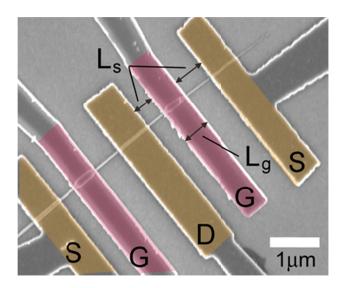

| Figure 3-2: | SEM of a dual-gated NW FET. The red regions (G) represent the gates,                                      |

|-------------|-----------------------------------------------------------------------------------------------------------|

|             | and the yellow regions represent the S/D. $L_g$ denotes a gated channel                                   |

|             | length and $L_s$ denotes a ungated channel length                                                         |

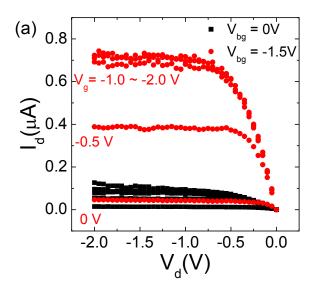

| Figure 3-3: | Electrical characteristics of a Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NW FET with               |

|             | undoped S/D, and with a channel length $L_g = 720$ nm. (a) $I_d$ vs $V_d$ data                            |

|             | measured at different $V_g$ values. (b) $I_d$ vs $V_g$ data measured at different $V_d$                   |

|             | values. The data in both panels were measured at two back-gate biases:                                    |

|             | $V_{bg}$ =0 V (square, black symbols) and $V_{bg}$ = -1.5 V (round, red symbols).                         |

|             | [Ge52AF002,F008]54                                                                                        |

| Figure 3-4: | Electrical characteristics of a Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NW FET with               |

|             | undoped S/D, and with a channel length $L_g = 720$ nm. (a) $I_d$ vs $V_d$ data                            |

|             | measured at different $V_g$ values. (b) $I_d$ vs $V_g$ data measured at different $V_d$                   |

|             | values. The data in both panels were measured at two back-gate biases:                                    |

|             | $V_{bg} = 0 \text{ V (square, black symbols)}57$                                                          |

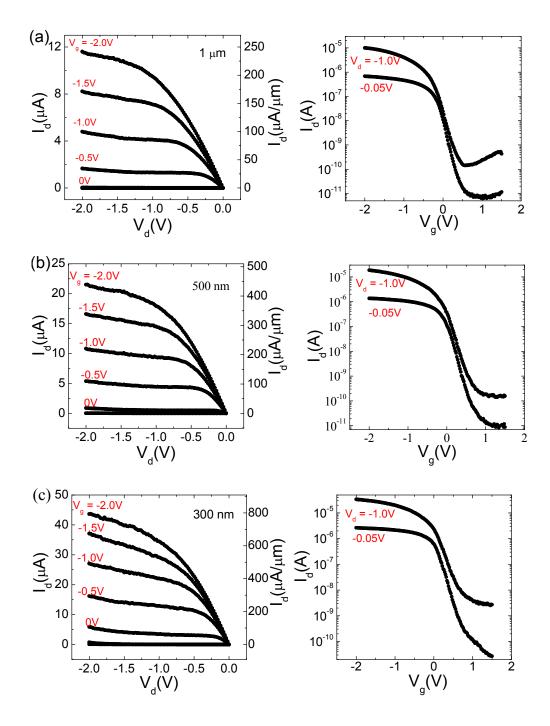

| Figure 3-5: | Electrical characteristics of a Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NW FET at different       |

|             | gate lengths (a) $L_g = 1 \mu m d = 48 \text{ nm}$ (b) $L_g = 500 \text{ nm} d = 49 \text{ nm}$ (c) $L_g$ |

|             | = 300 nm $d$ = 55 nm. In each panel, the left-side (right-side) graphs                                    |

|             | show $I_d - V_d$ ( $I_d$ - $V_g$ ) characteristics. The axis on the right side of output                  |

|             | characteristics show $I_d$ normalized to the NW diameter $(d)$ .                                          |

|             | [Ge52AF010]60                                                                                             |

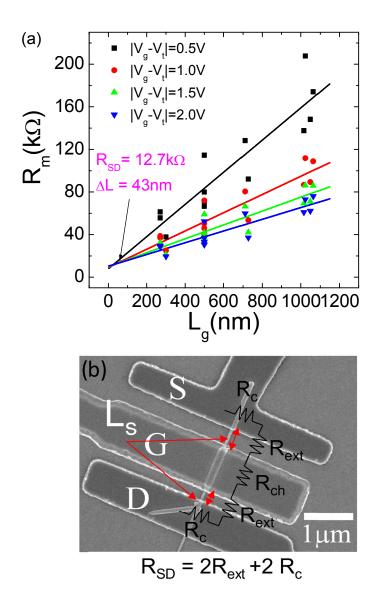

| Figure 3-6: | (a) Measured device resistance $R_m$ at $V_d = -0.05$ V for different gate                                |

|             | lengths. The common intercept determine both the external resistance                                      |

|             | and the effective channel length reduction. (b) Scanning electron                                         |

|             | micrograph of a fabricated NWFET, showing resistance components of                                        |

|             | the device                                                                                                |

|             | XVIII                                                                                                     |

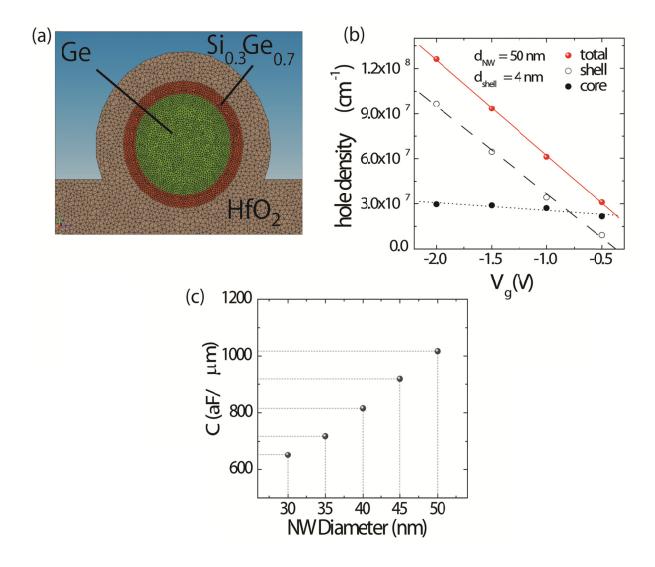

| Figure 3-7:  | (a) Schematic representation of a Ge-Si $_x$ Ge $_{1-x}$ core-shell NW FET used in               |

|--------------|--------------------------------------------------------------------------------------------------|

|              | the simulation. (b) Total hole density versus gate voltage. The total hole                       |

|              | density is the sum of the hole densities in the NW core and shell. (c)                           |

|              | Capacitance versus NW diameter. The capacitance values were                                      |

|              | calculated using the relation $C_{\text{ox}} = e \cdot (dp/dVg)$ 63                              |

| Figure 3-8:  | Effective mobility of the Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NW FETs for four       |

|              | different channel lengths as a function of gate overdrive65                                      |

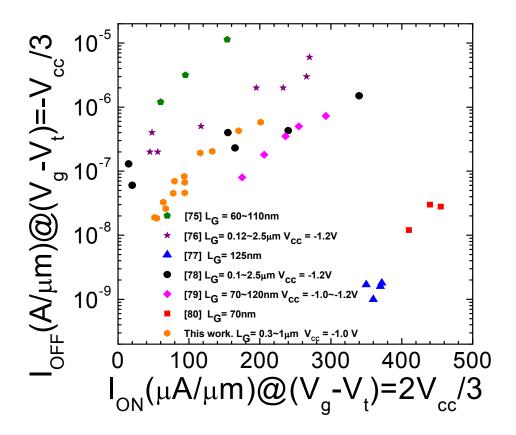

| Figure 3-9:  | ON-OFF characteristics of the Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NW FETs along      |

|              | with planar Ge pMOSFETs. The ON-OFF characteristics of the                                       |

|              | NWFETs are comparable or better than those of most recent Ge                                     |

|              | pMOSFETs [75-80]. ON-currents in the NW FETs can be further                                      |

|              | increased by the device scaling66                                                                |

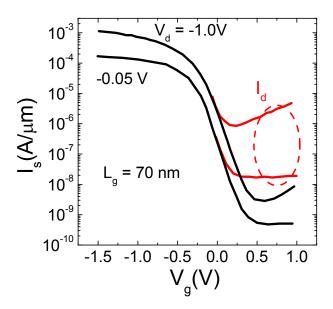

| Figure 3-10: | Transfer characteristics of Ge $p$ MOSFET measured at the source (black)                         |

|              | and the drain (red). A large difference between $I_d$ and $I_s$ is originated the                |

|              | reverse-based diode leakage current between the drain $(p+)$ and the                             |

|              | substrate ( <i>n</i> ) [79]67                                                                    |

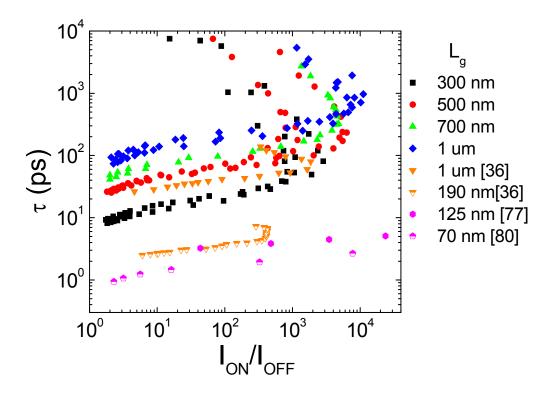

| Figure 3-11: | Intrinsic gate delay ( $\tau$ ) versus $I_{ON}/I_{OFF}$ ratio for different $L_g$ values along   |

|              | with Ge-Si core-shell NW FETs [36] and Ge pMOSFETs [77, 80] data                                 |

|              | from the literatures. The gate delay of our $\text{Ge-Si}_x\text{Ge}_{1\text{-}x}$ core-shell NW |

|              | FETs is expected to further reduced with the gate length scaling68                               |

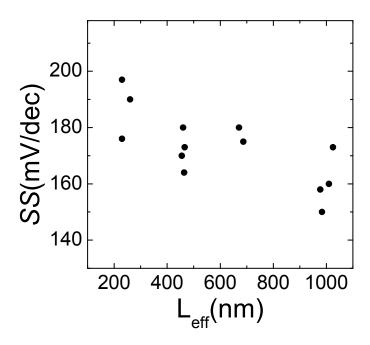

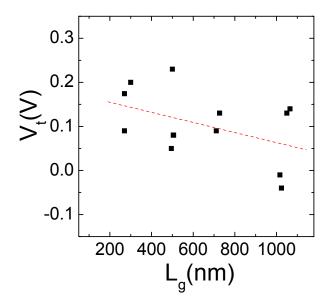

| Figure 3-12: | Subthreshold swing (SS) versus effective gate length. The SS values are                          |

|              | generally high and slightly increase with the device scaling70                                   |

| Figure 3-13  | : DIBL of $Ge\text{-}Si_xGe_{1\text{-}x}$ core-shell NWFETs as a function of the channel         |

|              | length71                                                                                         |

| Figure 3-14: | Threshold voltage vs. the gate lengths. Slight $V_t$ shift with the device                                                          |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------|

|              | scaling71                                                                                                                           |

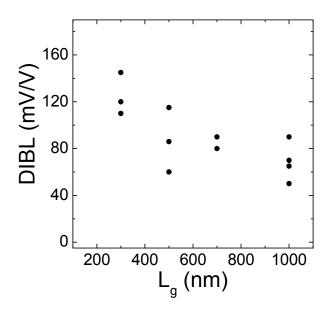

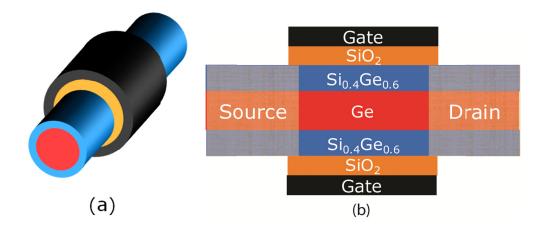

| Figure 3-15: | (a) Schematics of a Ge-Si $_x$ Ge $_{1-x}$ core-shell NWFET with gate-all-around                                                    |

|              | (GAA) device geometry. (b) The cross section of the NW FET. The                                                                     |

|              | shaded regions represent B-doped S/D regions (B: $10^{20}$ cm <sup>-3</sup> )73                                                     |

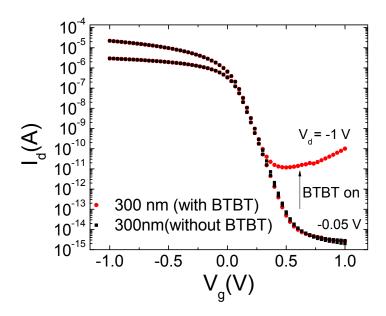

| Figure 3-16: | The $I_d$ - $V_g$ characteristics of Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NWFET with $L_g$ =                             |

|              | 300 nm. Black (■): transfer characteristics without band-to-band                                                                    |

|              | tunneling (BTBT) model, Red (•): transfer characteristics including                                                                 |

|              | BTBT model in the simulation)                                                                                                       |

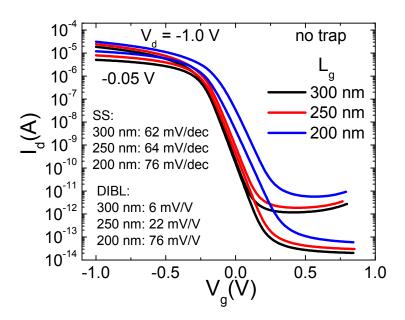

| Figure 3-17: | The $I_d$ - $V_g$ characteristics of Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NWFETs for different                           |

|              | gate lengths from 300 nm to 200 nm                                                                                                  |

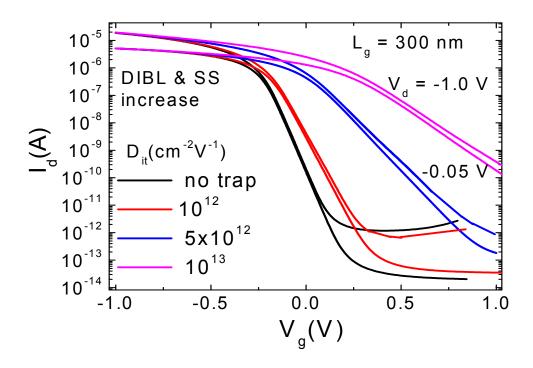

| Figure 3-18: | Impact of density of interface trap (Dit) on the performance of Ge-                                                                 |

|              | Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NWFETs with the gate length of 300 nm77                                                |

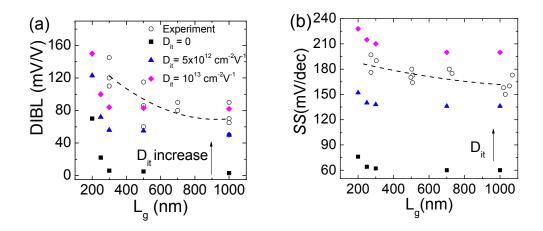

| Figure 3-19: | : (a) DIBL vs. gate length for different interface trap level $(D_{it})$ (b)                                                        |

|              | Subthreshold swing (SS) vs. gate length for different $D_{it}$                                                                      |

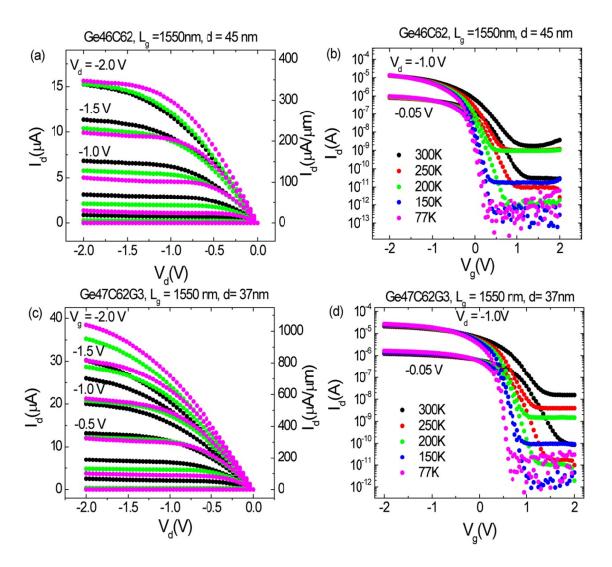

| Figure 3-20  | : Electrical characteristics of Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NW FETs with                                        |

|              | different shell compositions measured for different temperature from                                                                |

|              | 300K to 77K. (a),(b) $I_d$ - $V_d$ and $I_d$ - $V_g$ characteristics $L_g$ = 1550 nm, $d$ = 45                                      |

|              | nm, and Si <sub>0.5</sub> Ge <sub>0.5</sub> shell (c),(d) $I_d$ - $V_d$ and $I_d$ - $V_g$ characteristics $L_g$ = 1550              |

|              | nm, $d = 37$ nm, and Si <sub>0.7</sub> Ge <sub>0.3</sub> shell. The right <i>y</i> -axis on $I_d$ - $V_d$ graph show                |

|              | $I_d$ normalized to the NW diameter                                                                                                 |

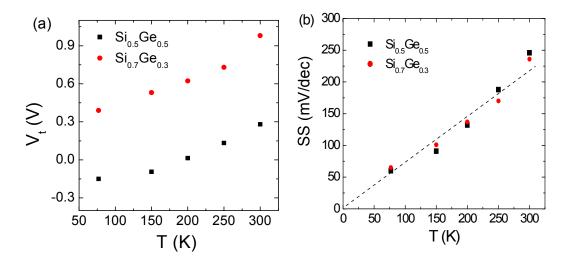

| Figure 3-21: | (a) Threshold voltage $vs.$ temperature $(T)$ ( $\bullet$ ) (b) Subthreshold swing                                                  |

|              | (SS) vs. T. [Ge-Si <sub>0.5</sub> Ge <sub>0.5</sub> core-shell NW FET ( $\blacksquare$ ), Ge-Si <sub>0.7</sub> Ge <sub>0.3</sub> NW |

|              | FET1 80                                                                                                                             |

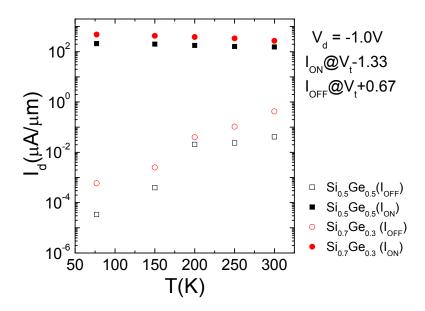

| Figure 3-22:  | $I_{ON}$ & $I_{OFF}$ vs. Temperature (T). The $I_d$ is normalized to the diameter (d)                                                              |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|               | of the NWs. The $I_{ON}$ values of the NW FET with $Si_{0.7}Ge_{0.3}$ shell are                                                                    |

|               | approximately two times higher than that of the NW FET with $Si_{0.5}Ge_{0.5}$                                                                     |

|               | shell. The $I_{OFF}$ values are also higher for the NW FET with $Si_{0.7}Ge_{0.3}$                                                                 |

|               | shell                                                                                                                                              |

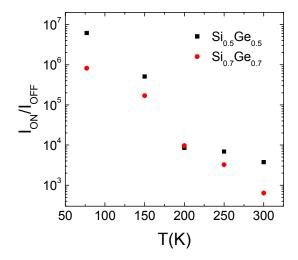

| Figure 3-23:  | ON-OFF current ratio vs. temperature (T). The NW FET with Si <sub>0.5</sub> Ge <sub>0.5</sub>                                                      |

|               | shell shows higher ON-OFF current ratio82                                                                                                          |

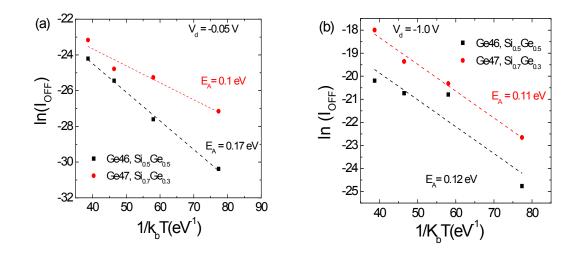

| Figure 3-24:  | Arrhenius plot of $I_{OFF}$ measured from 300K to 150K at (a) $V_d = -0.05 \text{ V}$                                                              |

|               | and (b) $V_d = -1.0$ V. Low activation energies of both devices indicate                                                                           |

|               | that the $I_{OFF}$ current are attributed to BTBT or TAT of carriers84                                                                             |

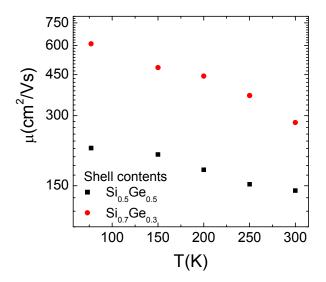

| Figure 3-25:  | Peak mobility versus temperature plot of the NW FETs with Si <sub>0.5</sub> Ge <sub>0.5</sub>                                                      |

|               | ( $\blacksquare$ ) and Si <sub>0.7</sub> Ge <sub>0.3</sub> ( $\bullet$ ) shell. At 77 K, the NW FET with Si <sub>0.7</sub> Ge <sub>0.3</sub> shell |

|               | demonstrates about three times higher mobility by comparison to the                                                                                |

|               | NW FET with Si <sub>0.5</sub> Ge <sub>0.5</sub> shell84                                                                                            |

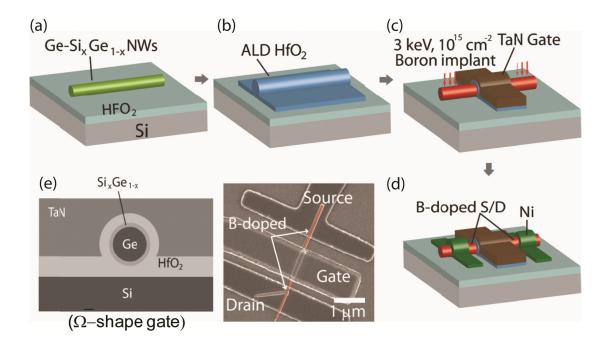

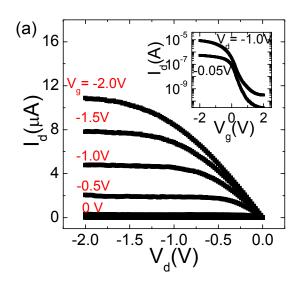

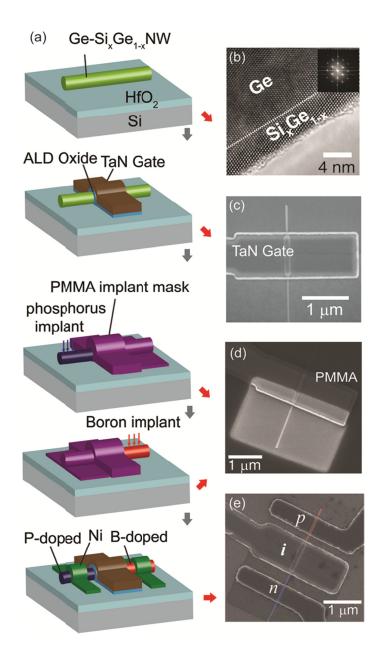

| Figure 4-1: 0 | Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NW TFET <b>a.</b> Schematic representation of the NW                                               |

|               | TFET fabrication process flow <b>b.</b> Transmission electron micrograph of a                                                                      |

|               | Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NW, evincing a single crystal shell grown                                                          |

|               | epitaxially on the Ge core c. Scanning electron micrograph (SEM) of the                                                                            |

|               | gate electrode d. SEM of ion-implant window. e. SEM showing a NW                                                                                   |

|               | TFET device. The red (blue) colored region represents the <i>B</i> -doped ( <i>P</i> -                                                             |

|               | doped) NW section                                                                                                                                  |

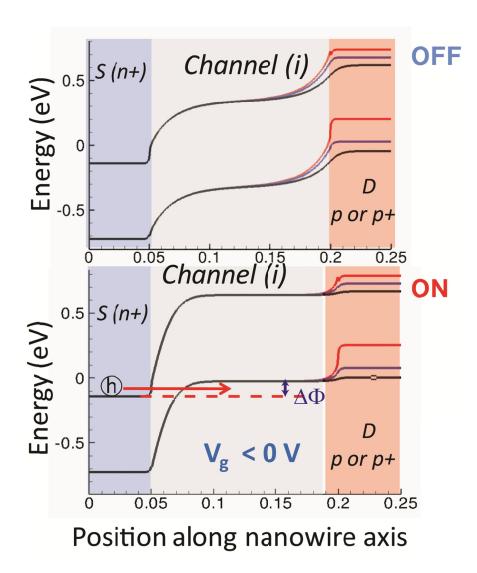

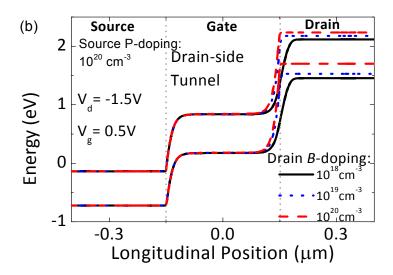

| Figure 4-2: Energy band profiles of NW TFET with p-i-n device structure along a                                   |

|-------------------------------------------------------------------------------------------------------------------|

| NW for OFF-state (top) and ON-state (bottom). The device turns on by                                              |

| BTBT of holes from the source to the channel when the valence band in                                             |

| the channel is pulled above the conduction band of the source with a                                              |

| negative gate bias. Red, blue, and black lines in the drain regions                                               |

| represent B-doping concentration $10^{20}$ , $10^{19}$ , and $10^{18}$ cm <sup>-3</sup> , respectively            |

| 92                                                                                                                |

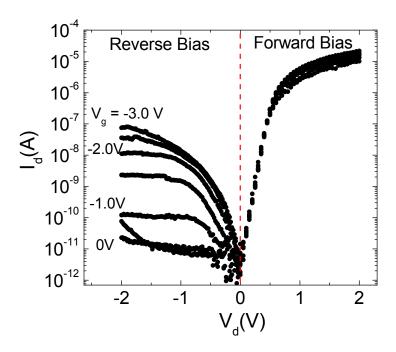

| Figure 4-3: Diode characteristics of a Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NW TFET: The $I_d$ - $V_d$ |

| characteristics of a NW TFET, with $L_g = 600$ nm, and $d = 36$ nm, on a                                          |

| log-lin scale. The phosphorous and boron implant doses are (P: 10 <sup>15</sup> cm <sup>-1</sup>                  |

| <sup>2</sup> , B: 10 <sup>15</sup> cm <sup>-2</sup> ). Recombination dominates the current in forward bias,       |

| while BTBT dominates the current in reverse bias94                                                                |

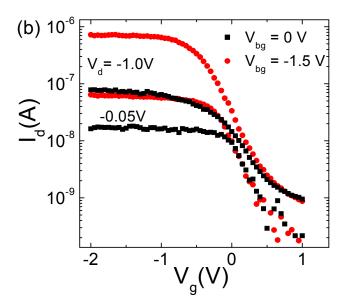

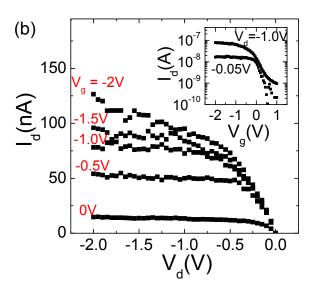

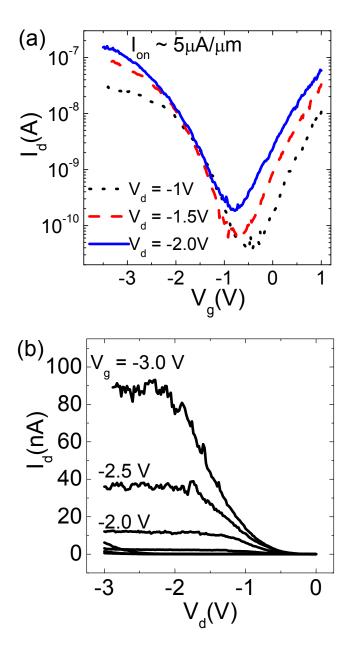

| Figure 4-4: Electrical characteristics of a Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NW TFET: (a)          |

| Transfer characteristics ( $I_d$ - $V_g$ ) of a NW TFET with $L_g$ = 600 nm, and                                  |

| $d = 36$ nm, and (P : $10^{15}$ cm <sup>-2</sup> , B : $10^{15}$ cm <sup>-2</sup> ) implant doses. (b) The        |

| output characteristics ( $I_d$ - $V_d$ ) measured for the same device96                                           |

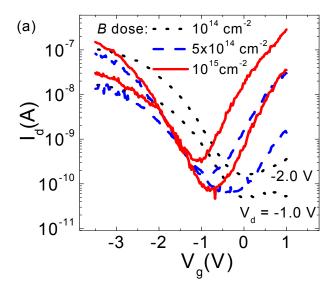

| Figure 4-5: (a) $I_d - V_g$ characteristics of Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NW TFETs at        |

| different drain implant doses. As the drain B-implant dose decreases                                              |

| from 10 <sup>15</sup> to 10 <sup>14</sup> cm <sup>-2</sup> , the ambipolar behavior is suppressed. The            |

| source of these devices is implanted with a phosphorus dose of 10 <sup>15</sup> cm <sup>-1</sup>                  |

| <sup>2</sup> . (b) Energy band profiles for different drain concentrations, showing                               |

that the drain-channel junction becomes wider as the doping

concentration decreases, which in turn prevents BTBT of electrons from

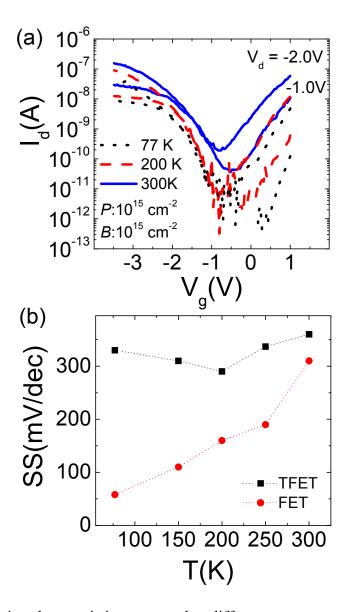

| Figure 4-6: I | Device characteristics measured at different temperatures. a. NW TFET $I_d$                          |

|---------------|------------------------------------------------------------------------------------------------------|

|               | - $V_g$ characteristics measured at different temperatures. b. $SS$ vs. $T$ for a                    |

|               | NW TFET (squares), compared to that of a conventional NW FET                                         |

|               | (circles)                                                                                            |

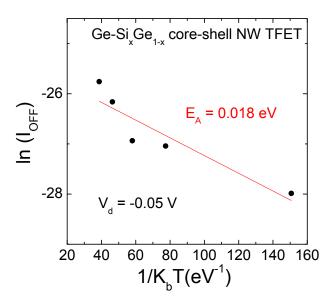

| Figure 4-7:   | Activation energy extracted from the leakage floor of a NW TFET                                      |

|               | (B:10 <sup>15</sup> cm <sup>-2</sup> P:10 <sup>15</sup> cm <sup>-2</sup> ) using Arrhenius plot      |

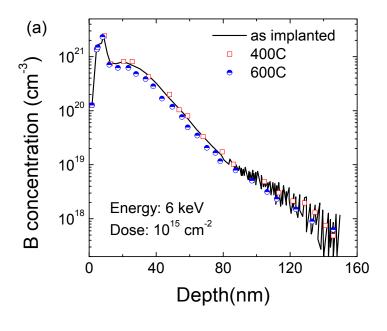

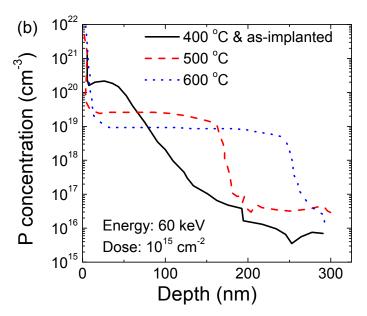

| Figure 4-8:   | Profile of implanted dopants in Ge substrate (a) Profiles of boron                                   |

|               | implanted at the energy of 6 keV with a dose of $10^{15}$ cm <sup>-2</sup> , and annealed            |

|               | at 400°C and 600°C for 1 min [86] (b) Profiles of phosphorus implanted                               |

|               | at the energy of 60 keV with a dose of $10^{15}$ cm <sup>-2</sup> , and annealed at 400,             |

|               | 500, and 600°C for 30 min [82]. It is noted that as-implanted dopant                                 |

|               | profile is the same as the one of 400 °C                                                             |

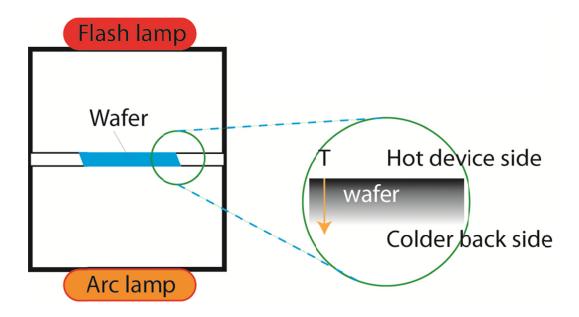

| Figure 4-9:   | Schematic representation of the flash lamp tool. The Arc lamp under the                              |

|               | wafer is used for the bulk heating of the wafer and high energy flash                                |

|               | lamp is used for the dopant activation [91]106                                                       |

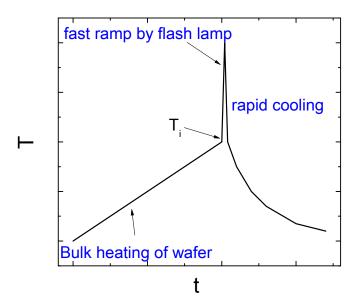

| Figure 4-10   | : Time vs temperature profile of an fRTP process, consisting of bulk                                 |

|               | heating, flash heating, and rapid cooling steps107                                                   |

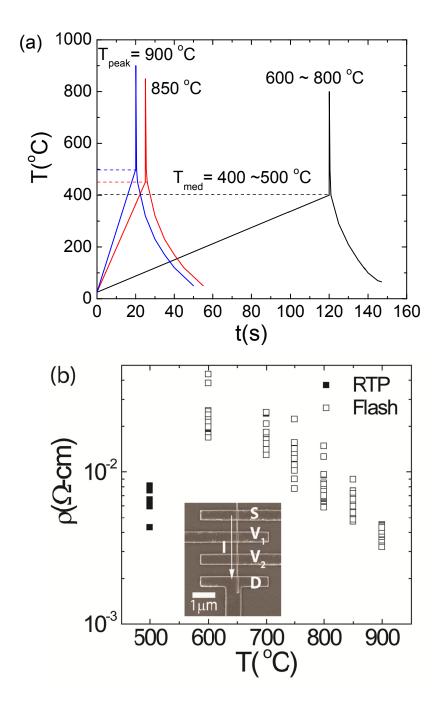

| Figure 4-11:  | (a) Temperature vs time profiles used for the activation of the P-                                   |

|               | implanted NWs. (b) Resistivities ( $\rho$ ) of phosphorus-doped Ge-Si <sub>x</sub> Ge <sub>1-x</sub> |

|               | core-shell NWs vs the activation temperature (T). The NWs are P-                                     |

|               | implanted with a dose of $10^{15}$ cm <sup>-2</sup> at the energy of 6 keV. (Inset)                  |

|               | Scanning electron micrograph of a NW device with multi-terminals. The                                |

|               | current (I) flows from S to D, and $V_1$ and $V_2$ are used to probe the                             |

|               | voltage drop along the NW                                                                            |

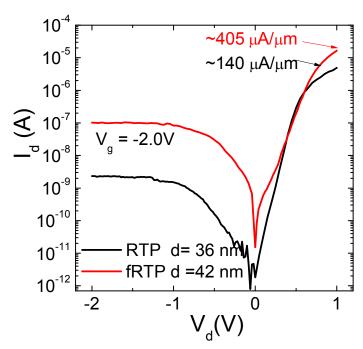

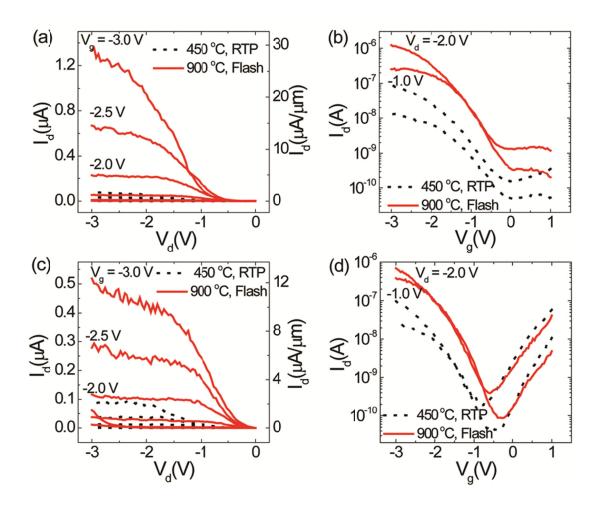

| Figure 4-12: | Diode characteristics of Ge-Si <sub>x</sub> Ge <sub>1-x</sub> core-shell NW TFETs: The $I_d$ - $V_d$  |

|--------------|-------------------------------------------------------------------------------------------------------|

|              | characteristics of NW TFETs on a log-lin scale, measured at $V_g$ = -2.0V.                            |

|              | The red (black) solid line represents a fRTP- (RTP-) activated NW                                     |

|              | TFET. The phosphorous and boron implant doses are the same in both                                    |

|              | devices (P: $10^{15}$ cm <sup>-2</sup> , B: $10^{15}$ cm <sup>-2</sup> ). Recombination dominates the |

|              | current in forward bias, while BTBT dominates the current in reverse                                  |

|              | bias111                                                                                               |

## **CHAPTER 1**

## **Research Background**

### 1.1 MOTIVATION

The metal oxide semiconductor field-effect transistors (MOSFETs) have been the most important building blocks of CMOS (Complementary metal-oxide-semiconductor) circuits since their first introduction in 1960 [1, 2]. For the past 40 years, transistor scaling has been continued as predicted by "Moore's law" [3]. It prospects the scaling of the gate length by a factor of 0.7 per every 2~3 years, doubling the number of transistors on integrated circuits [Figure 1-1, 1-2].

Figure 1-1: Historical scaling trend of CMOS following Moore's law [4].

Figure 1-2: Scaling of MOSFETs below sub 100 nm regime [source: Intel].

The device scaling provides advantages, such as higher packing density, the higher circuit speed, and the lower power consumption. With these reasons, pursuing Moore's law has been a driving force for semiconductor industry to invest enormous efforts into scaling process technologies. Currently, the 32-nm process technology has already been employed in production [Figure 1-2]. However, continuing this scaling trend down to sub 10 nm regime appears to slow down and is challenged by technical and physical limitations [4-7]. To further extend device scaling limits, non-planar device structures [8-19], different channel materials other than Si [20-25], and devices working under different physics have been explored [26-29]. Recently, bottom-up grown semiconductor nanowires have been widely employed to examine such device options, motivated by the conveniences that they provide for the control of dimensions and compositions of NWs [30-38]. In particular, germanium (Ge)- Silicon Germanium (Si $_{\rm x}$ Ge1- $_{\rm x}$ ) core-shell NWs have gained increasing attentions as a channel materials to realize high performance transistors with low power consumption thanks to their unique physical properties [36-38].

In the remaining sections, the challenges with device scaling are first clarified and the possible future transistor options to overcome such challenges will be explored. Finally, the potential advantages of Ge-Si<sub>x</sub>Ge<sub>1-x</sub> core-shell NWs for the realization of high performance nanowire field-effect transistors (FETs) and tunneling field-effect transistors (TFETs) are discussed.

#### 1.2 CHALLENGES IN DEVICE SCALING

The device scaling generates both economical benefits and device performance gains. However, as the transistors shrink aggressively, the device performances can be degraded by the so-called short-channel effects. The scaling theory, described by Dennard, provides scaling guidelines such that MOSFETs can be scaled without reliability and performance degradation [39]. For example, when the channel length ( $L_g$ ) of a MOSFET scales by a factor  $\alpha$ , it is necessary to scale down a gate oxide thickness ( $t_{\alpha x}$ ) and a depletion width ( $x_d$ ) to keep the overall electric field unchanged in the device [Figure 1-3]. This scaling rule has worked well to scale the device down to near 100 nm regime. However, as the device dimensions approach sub-100nm regime, the device scaling faces several challenges, neccetiating new materials and process technologies [4-7].

Figure 1-3: Schematic of MOSFET indicating device scaling parameters.

The most detrimental effect in device scaling is the increase of leakage current. The leakage current ( $I_{leak}$ ) in transistors is composed of four major leakage components as illustrated in Figure 1-4:

$$I_{leak} = I_{sub} + I_{ox} + I_{GIDL} + I_{diode}$$

1.1

,where  $I_{sub}$  is the subthreshold current,  $I_{ox}$  is the gate oxide tunneling currents,  $I_{GIDL}$  is the gate induced drain leakage current, and  $I_{diode}$  is the reverse bias diode leakage from the drain to the substrate. With the device scaling, the  $I_{sub}$  has exponentially increased due to the threshold voltage shift induced by drain induced barrier lowering (DIBL). The higher channel doping concentration ( $N_A$ ), which is necessary to suppress short-channel effects causes the higher junction capacitance and diode leakage current ( $I_{diode}$ ). As the gate oxide ( $SiO_2$ ) thickness reaches few atomic layers,  $I_{ox}$  greatly increases to affect device performance. In addition, the increased electric field between the gate and the drain terminal affects the gate induced drain leakage current ( $I_{GIDL}$ ). As a result, total leakage current ( $I_{leak}$ ) continuously increase with the device scaling, leading to higher  $I_{OFF}$  current as shown in Figure 1-5(b).

Figure 1-4: Schematic of MOSFET indicating leakage current sources.

Different from the ideal switch that turns ON and OFF instantly as shown in Figure 1-5(a), the switching in MOSFETs is fundamentally limited by the subthreshold swing (SS). The subthreshold swing is defined as the gate voltage needed to change the drain current by one order of magnitude,  $SS = -[d(logI_d)/dV_g]^{-1}$ ;  $I_d$  is the drain current, and  $V_g$  is the gate voltage. Thus, to realize high-speed and low-power devices, a small SS value is desirable. Figure 1-5(c) shows the energy band profile of a conventional n-type MOSFET, illustrating carrier injection mechanisms affecting the SS values. MOSFETs, the conduction occurs by injection of electrons from source into the channel. The carrier distribution in the source, given by the product  $g(E) \cdot f_e(E)$ , where g(E) is the density of state and f<sub>e</sub>(E) is the Fermi distribution of electrons in the source, allows high energy electrons to be injected into the channel when a potential barrier is present (OFF state), as shown in Figure 1-5(c). Indeed, the thermal broadening of the Fermi distribution limits the SS values to  $kT/q \cdot \ln(10) = 60 \text{ mV/dec}$  at room temperature [Figure 1-5(b)]. Due to this limit, the switching action close to the ideal switch can never be achieved in MOSFETs. With the scaling of device, the SS and I<sub>OFF</sub> can be further increased due to short-channel effects [Figure 1-5(b) orange line].

Figure 1-5: (a) The ideal switch instantly turns ON/OFF (b) The  $I_d$ - $V_g$  characteristics of a MOSFET showing a subthreshold swing of 60 mV/dec at room temperature (black line). The  $I_{OFF}$  and SS can be further increased due to short-channel effects (orange line) (c) Energy band profile of a conventional n-type FET. The carrier injection depends on the thermionic emission of electrons over the potential barrier in the channel.

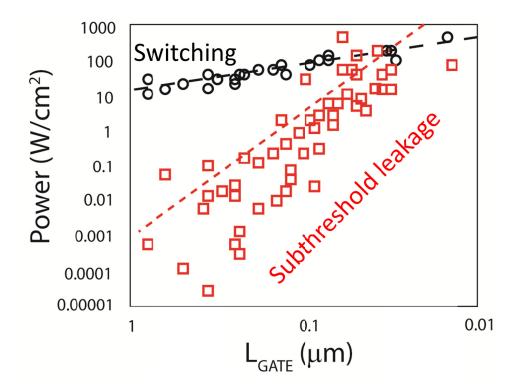

Therefore, considering the growing number of transistors on a chip and  $I_{OFF}$  increase due to short-channel effects, the power consumption management has now become the biggest challenge for continuing the device scaling. Figure 1-6 shows the active and passive power density calculated from the highest density logic regions for the reported CMOS devices [40]. Indeed, the data show that the leakage power is expected to surpass switching power at the channel length  $\sim$ 40 nm.

Figure 1-6: Power density vs. gate length. The data demonstrate that the subthreshold power consumption approaches to the active power consumption at short channel lengths. [40]

#### 1.3 FUTURE TRANSISTOR OPTIONS

Previous section discussed the challenges for the continuing MOSFET scaling. In attempts to overcome such challenges, several new approaches have been explored recently.

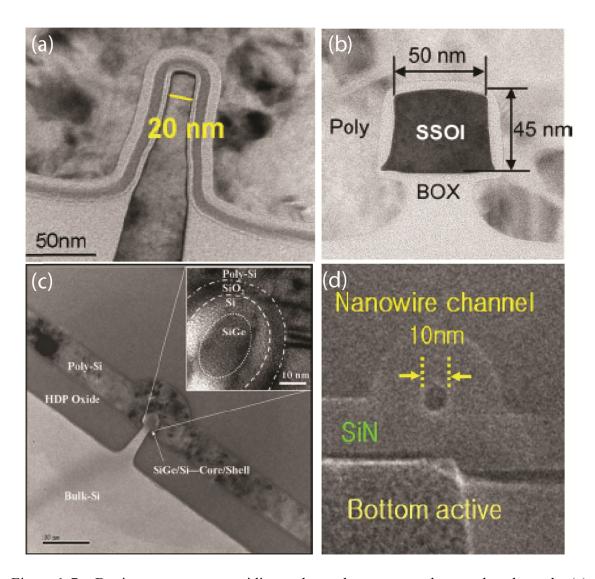

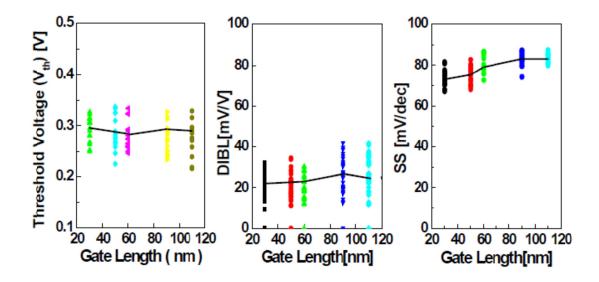

### 1.3.1 Gate-all-around device structure

Non-planar device structures have been proposed to provide better electrostatic control over the channel. As the device dimensions shrink, the planar MOSFETs are suffering from increased short-channel effects. Thus, non-planar device structures, such as FinFETs (fin field-effect transistors), tri-gated FETs, Ω-gated FETs and GAA FETs (gate-all-around field-effect transistors) have attracted much attentions to provide enhanced gate controls over the channel and thereby reduce the short-channel effects [Figure 1-7] [8-19]. Among device geometries, theoretical studies suggest that the GAA structure implemented with the reduced channel thickness can provide the most efficient gate control.[41, 42] Experimental results have also demonstrated greatly improved short-channel device characteristics in GAA FETs, showing immunity to short-channel effects down to gate lengths of 30 nm [Figure 1-8] [17]. Thus, by employing GAA device geometry in MOSFETs, the device scaling can be extended without suffering from stand-by power dissipation due to short-channel effects while maintaining the performance of the devices.

Figure 1-7: Device structures providing enhanced gate control over the channel (a) FinFET [9] (b) Tri-gate FET [16] (c)  $\Omega$ -gated FET [11] (d) Gate-all-around (GAA) FET [17]

Figure 1-8. V<sub>t</sub> roll-off, SS, and DIBL are not affected by the gate length scaling, demonstrating immunity to short-channel effect due to GAA device geometry realized along a NW [17].

## 1.3.2 High mobility channel material

On-current saturation in conventional Si MOSFETs with the device scaling necessitates high mobility channel materials to boost drive currents ( $I_{Dsat}$ ) [43-47]. This saturation phenomenon in very short channel Si MOSFETs is believed to be limited by carrier injection from the source to the channel, where the injection velocity from the source ( $v_s$ ) in short channel devices is set by thermal injection velocity ( $v_{inj}$ ), experimentally demonstrated as ~40% of  $v_s$  [43-45]. In addition, the experimental results show that measured carrier velocity has a proportional relation with the low field effective mobility ( $\mu$ ) [46]. Thus, higher  $v_{inj}$  values can be achieved by employing high mobility channel materials.

The performance metrics, such as drive current and logic gate delay can be express in terms of  $v_{inj}$ , explaining the advantage of high mobility channel materials.

$$\tau = \frac{I_{Dsat} \approx Q_{inv} \times v_{inj}}{I_{Dsat}} = \frac{L_g \times V_{CC}}{(V_{CC} - V_t) \times v_{inj}}$$

1.1

1.2

where  $\tau$  is the logic gate delay,  $Q_{inv}$  is the inversion charge density,  $C_L$  is the load capacitance,  $V_{CC}$  is the supply voltage,  $L_g$  is a MOSFET gate length, and  $V_t$  is the threshold voltage. By coupling equation 1.1 and 1.2, the advantages incorporating high mobility channel material for MOSFETs can be identified as the increase in the drive current and the reduction in the gate delay. Therefore, the high mobility channel materials, such as III-V compound semiconductors and germanium (Ge), have brought the attractions as channel materials for the deeply scaled MOSFETs, which can extend the device scaling trend without sacrificing the performance of the devices [20-23,47].

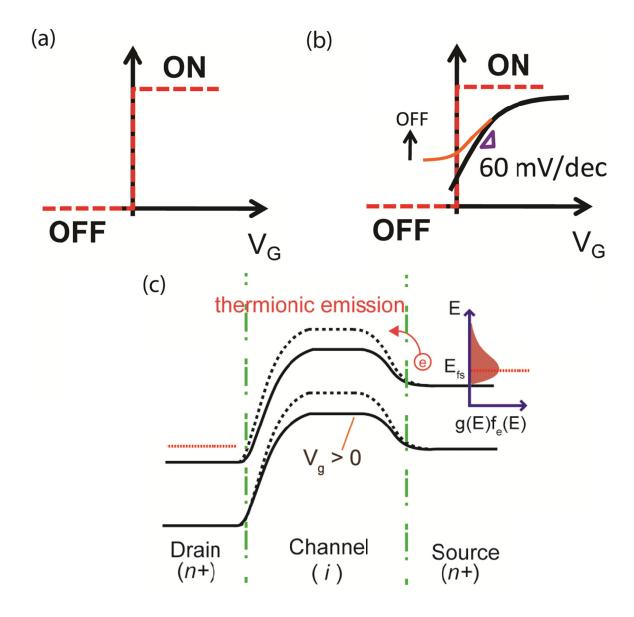

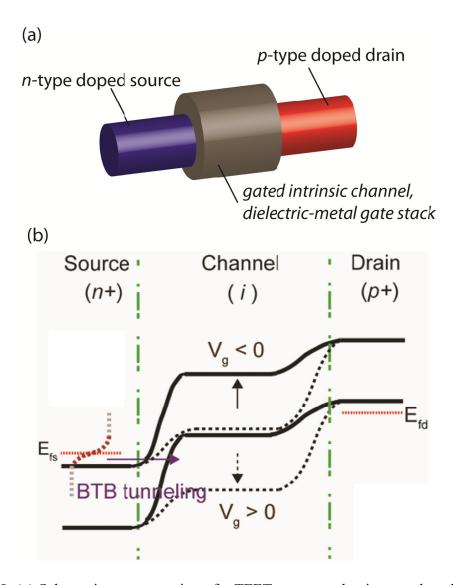

### 1.3.3 Tunneling field-effect transistors

As discussed in Chapter 1.2, the scaling of MOSFETs has been stymied by the increase in dissipated passive power, which stems from short-channel effects with shrinking device dimensions. Therefore, the need for novel devices, which can potentially provide a reduced dissipation power at switching speeds comparable to Si MOSFETs looms increasingly large. Tunneling field-effect transistors (TFETs) have gained significant attention as promising candidates to replace MOSFETs [48-56]. TFETs consist of gated *p-i-n* structures, e.g. a *p*-doped drain (source), an intrinsic channel, and an *n*-doped source (drain) [Figure 1-9(a)]. The carrier injection from the highly doped source into the channel relies on band-to-band tunneling (BTBT) at the reversed biased source-channel junction. TFETs have been theoretically shown to exhibit a steep turn-off, below the thermal limit of 60 mV/dec, and a sufficiently high ON-current comparable to that of Si MOSFETs, depending on the host semiconductor [48-50]. In

particular, the semiconductors with low bandgap and tunneling effective mass are desirable to employ as a channel material for TFETs [51].

Figure 1-9. (a) Schematic representation of a TFET structure, having a n-doped source, a p-doped drain, and a gated *intrinsic* channel. (b) Energy band profile along a TFET. The carrier injection into the channel relies on BTBT, which enables the SS smaller than 60 mV/dec.

The carrier injection mechanism in a TFET differs from that of a FET. Figure 1-9(b) shows the energy band diagram along a TFET, consisting of a *p*-doped drain, an intrinsic channel, and an *n*-doped source, with the intrinsic segment being controlled by the gate bias. The switching of this device depends on the modulation of the energy band in the intrinsic segment. When the valence band in the channel is pulled above the conduction band at the source by applying a negative gate bias, the electric field at the source-channel junction becomes sufficiently high and holes are injected into the channel via BTBT. Similarly, when the valence band in the channel is pulled down with a positive gate voltage, the tunneling barrier width at source-channel junction becomes wide and tunneling is prevented, although tunneling at the drain-channel junction may be enabled. A key aspect of carrier injection in TFETs is that the high energy carriers in the source are prevented from tunneling at the source-channel junction [Figure 1-9(b)], effectively leading to a lower effective temperature of the carriers in the channel, and consequently an *SS* value below 60 mV/dec.

# $\textbf{1.4 Ge-Si}_{x}Ge_{1\text{-}x} \text{ core-shell nanowires for field-effect and tunneling field-effect transistors}$

In the previous chapter, possible device options to mitigate performance degradation and power dissipation problems entailed with the device scaling were introduced. To examine such options,  $Ge-Si_xGe_{1-x}$  core-shell NWs are employed in this study, where  $Ge-Si_xGe_{1-x}$  core-shell NWs consist of a Ge core and a  $Si_xGe_{1-x}$  shell grown epitaxially on the Ge surface, described in more detail in Chapter 2.1.

The Ge-Si<sub>x</sub>Ge<sub>1-x</sub> core-shell NWs provide a number of advantages to realize high performance NW FETs and TFETs. First of all, thanks to NW's cylindrical geometry, GAA device geometry can be easily implemented on a NW. The efficient energy band

modulation of the channel using a gate bias is important for both NW FETs and TFETs. In FETs, it helps to minimize short-channel effects and OFF-state leakage currents, and thereby it enables further device scaling. In TFETs, since the switching of the device relies on the modulation of energy band profile in an *intrinsic* channel, a strong gate coupling to the channel realizes higher ON-state current as well as better *SS* characteristics. Secondly, Ge has the highest hole drift mobility due to its low hole effective mass, which is especially advantageous property for deeply scaled high performance *p*-type MOSFETs. [Figure 1-10] Thirdly, thanks to smaller bandgap of Ge (0.67 eV), higher BTBT currents by comparison to Si TFETs can be achieved in Gebased TFETs. Lastly, by optimizing Si<sub>x</sub>Ge<sub>1-x</sub> shell thicknesses and compositions of the NWs and thereby enhancing hole confinement effects and strain effects, the channel mobility can be further increased.

Figure 1-10: Hole mobility of the group IV semiconductors and group III-V compound semiconductors.

In addition to above mentioned physical advantages over Si, there are also several advantages in device fabrication aspects. Most of all, Ge is a CMOS compatible material. Thus, the fabrication technologies developed for Si can also be applied for Ge. Moreover, since Ge can be easily integrated on Si substrates [57, 58], a cylindrical channel similar to a NW can even be fabricated by "top-down" process [19]. Lastly, low thermal budget process can be easily employed for the dopant activation [59, 60], relieving thermal requirements for contemporary high-κ metal gate process [61].

Therefore,  $Ge-Si_xGe_{1-x}$  core-shell NWs are the promising channel material to realize both high performance NW FETs and NW TFETs.

#### 1.5 CHAPTER ORGANIZATION

This chapter briefly presented the historical trend of the CMOS device scaling and entailing problems, such as performance degradation and stand-by power dissipation. To alleviate these problems and continue the scaling trend, the device structure providing an enhanced electrostatic control over the channel, high mobility channel materials, and TFETs were proposed as possible options to examine. In this research, Ge-Si<sub>x</sub>Ge<sub>1-x</sub> coreshell NWs are employed for the realization of high performance NW FETs and TFETs thanks to their structural and physical advantages. Chapter 2 will present the growth of Ge-Si<sub>x</sub>Ge<sub>1-x</sub> core-shell NWs and the electrical characteristics of the doped NWs realized by low energy ion implantation. In Chapter 3, the fabrication of high performance of Ge-Si<sub>x</sub>Ge<sub>1-x</sub> core-shell NW FETs with highly doped source and drain will be presented, where the NW FETs are fabricated using a conventional CMOS process. The scaling properties of the devices will be presented and further investigated with TCAD

simulation. Chapter 4 will present the fabrication and electrical characteristics of Ge- $Si_xGe_{1-x}$  core-shell NW TFETs, consisting of a gated *p-i-n* structure. In addition, enhanced performance of NW TFETs by employing flash-assisted rapid thermal process will be presented. Chapter 5 will summarize the findings of this research and provide suggestions for future work.

## **CHAPTER 2**

# Growth and doping of germanium nanowires

The discussion in the Chapter 1 demonstrated the scaling trend of MOSFETs and explained the needs for new materials, device structures, and physics to continue the device scaling. As one of the candidates, Ge-Si<sub>x</sub>Ge<sub>1-x</sub> core-shell NWs have gained interests because the gate-all-around (GAA) device geometry can be easily realized in NWs, where better electrostatic control over the channel than any other device geometry can be achieved. In addition, Ge's high hole mobility makes them a favorable platform to realize high performance field-effect transistors (FETs). Furthermore, Ge's lower bandgap by comparison to Si is an attractive property for the realization of tunneling field-effect transistors (TFETs). With these reasons as noted in the Chapter 1, Ge-Si<sub>x</sub>Ge<sub>1-x</sub> core-shell NWs is considered as a promising material for the study of both FETs and TFETs. However, the biggest challenge to employ the NWs for both FETs and TFETs is an ability to reliably dope the NWs. For instance, high doping concentration up to  $10^{20}$ cm<sup>-3</sup> is necessary for the efficient carrier injection from the metal contact to a NW, which is a basic requirement for the high performance NW FETs. Also, doping a NW with different polarities of dopants is required to realize gated p-i-n TFETs. Therefore, two prerequisites for this study are to establish the growth process of high quality Ge-Si<sub>x</sub>Ge<sub>1-x</sub> core-shell NWs and reliable NWs doping techniques

In this chapter, the growth process of  $Ge-Si_xGe_{1-x}$  core-shell NWs will be first introduced, followed by NW-doping using low energy ion implantation is then described. Specifically, the NW-doping with low energy boron- and phosphorus-implantation is investigated for different activation temperatures and ion doses.

### 2.1 GROWTH OF GE-SI<sub>x</sub>Ge<sub>1-x</sub> CORE-SHELL NANOWIRES

Ge-Si<sub>x</sub>Ge<sub>1-x</sub> core-shell NWs were grown on Si (111) substrate in a chemical vapor deposition (CVD) chamber via the vapor-liquid-soild (VLS) growth mechanism. The growth process of Ge-Si<sub>x</sub>Ge<sub>1-x</sub> core-shell nanowires is outlined in Figure 2-1. Si (111) substrate is first cleaned with diluted hydrofludic (HF) acid (1:50 = HF: $H_2O$ ) to remove the native oxide layer on a wafer, followed by 1 nm of Au deposition using e-beam evaporator. Then, the substrate is transferred to load in CVD chamber. The wafer is annealed in the growth chamber at a substrate temperature of 350 °C in H<sub>2</sub> ambient, which forms droplet from the pre-deposited Au film. Then, the Ge core is first grown at a total pressure of 5 Torr and at the wafer temperature of 285 °C using 60 SCCM (cubic centimeter per minute at STP) GeH<sub>4</sub> (10 % diluted in He). The Si<sub>x</sub>Ge<sub>1-x</sub> shell is grown in the same chamber in ultrahigh vacuum. This is done by rerouting the gas flow through a turbo pump, then coflowing 7 SCCM of SiH<sub>4</sub> with 60 SCCM of GeH<sub>4</sub> at a growth chamber temperature of 400 °C, which results in the epitaxial growth of Si<sub>x</sub>Ge<sub>1-x</sub> shell on the Ge-core. The Si and Ge content can be tuned by changing the SiH<sub>4</sub> and GeH<sub>4</sub> partial pressure during the shell growth process, realizing the band engineered core-shell NW heterostructure. Figure 2-2(a) shows as-grown Ge-Si<sub>x</sub>Ge<sub>1-x</sub> core-shell NWs on a Si (111) substrate. To verify the shell thickness and the content of Si<sub>x</sub>Ge<sub>1-x</sub> shell, transmission electron microscopy and energy dispersive X-ray spectroscopy were used [Figure 2-2 (b), (c)]. The  $Si_xGe_{1-x}$  shell has a thickness of  $\sim 4$  nm and an approximate Si content of x =0.3. The role of the  $Si_xGe_{1-x}$  shell is two-fold. First, it acts as a passivation layer for the Ge surface, which is known to have a high density of interface traps in contact with a dielectric. Secondly, thanks to a positive band offset between Si<sub>x</sub>Ge<sub>1-x</sub> and Ge valence band, it serves as a barrier and confines the holes in the Ge core. In particular, we chose a reduced Si content, x = 0.3, in order to minimize the strain in the Ge-Si<sub>x</sub>Ge<sub>1-x</sub> core-shell heterostructure, while still maintaining the interface passivation.

Figure 2-1: Schematics of the  $Ge-Si_xGe_{1-x}$  core-shell NW growth process. The Au droplets form during the  $H_2$  anneal and serve as a catalyst for VLS Ge NW growth. After Ge NW growth, the Ge surface is passivated with  $Si_xGe_{1-x}$  shell.

Figure 2-2: SEM and TEM of Ge-Si<sub>x</sub>Ge<sub>1-x</sub> core-shell NWs (a) Cross sectional SEM showing an epitaxial NW growth on Si(111) substrate (b) TEM micrograph of a NW and Fourier transform of core and shell region (c) High resolution TEM of the same NW. The dashed lines in (b), (c) indicate the interface between the core and shell of a NW [62].

#### 2.2 DOPING OF SEMICONDUCTOR NANOWIRES

#### 2.2.1 Metal-Semiconductor contacts

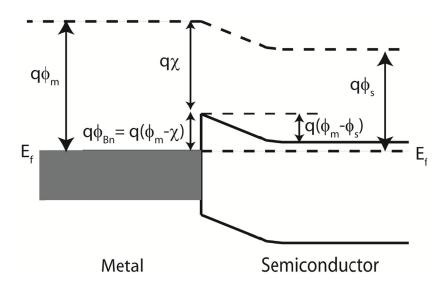

Figure 2-3: Energy band diagram of a metal-semiconductor contact in thermal equilibrium.

When the metal makes a contact with the semiconductor (n-type), the Fermi level ( $E_f$ ) in the two materials must be the same and the vacuum level must be continuous. Thus, the energy band diagram for the ideal metal-semiconductor contact can be drawn as shown in the Figure 2-3. There exists the finite barrier height  $q\phi_{Bn}$  from the metal to semiconductor conduction band, described by

$$q\phi_{Bn} = q\phi_m - q\chi \qquad 2.1$$

,where  $\phi_m$  is the metal work function and  $\chi$  is the semiconductor electron affinity. On the semiconductor side, the built-in potential  $(V_{bi})$  exists from a semiconductor to a metal contact, simply determined by the work function difference between two materials.

$$V_{bi} = q(\phi_m - \phi_s) 2.2$$

Thus, to achieve ohmic contact between a metal and a semiconductor, it is ideal to choose the metal having a similar or smaller work function compared with that of semiconductor. However, the experimentally observed barrier heights for most semiconductors, such as Si, Ge, and III-V materials are relatively independent of metal work functions, which is attributed to Fermi level pinning, where the Fermi levels in semiconductors are pinned at a certain energy level in the bandgap and cause a depletion-type contacts [63-65]. Therefore, the barrier height engineering to obtain ohmic contacts becomes an impractical approach. Another approach to implement ohmic contacts is to make the barrier width sufficiently thin, so that electrons can easily tunnel through the barrier from the metal to semiconductor and vice versa. Figure 2-4 shows the schematics of the conduction mechanisms between a metal and semiconductor for different semiconductor doping concentrations.

Figure 2-4: The conduction mechanism for a metal contact to *n*-type substrate. (a) Metal contact on a lightly doped substrate. Electron flows as a result of thermionic emission over the potential barrier (b) Metal contact on a substrate with an intermediate doping level. Thermionic-field emission dominates (c) Metal contact on a highly doped substrate. Electron tunneling dominated conduction [66].

For lightly doped semiconductor in Fig. 2-4(a), the current flows by thermionic emission of carriers, where the electrons thermally excited over the barrier. As a result, the potential barrier prevents efficient carrier transports between the two materials, which cause significant degradation in device performance. For a substrate with a medium level doping concentration, electrons are thermally excited to an energy level where the tunnel barrier is sufficiently thin for the tunneling. [Fig. 2-4(b)] For a highly doped substrate shown in Fig. 2-4(c), the electron tunneling between the metal and semiconductor can easily occur thanks to narrow tunnel barrier and thereby realizes low contact resistance. Therefore, the ability dope the semiconductor nanowires up to very high level (10<sup>20</sup> cm<sup>-3</sup>) in controllable manners is the most crucial challenge to employ the NWs for device applications.

# 2.2.2 Nanowire dopoing techniques

As discussed in the previous section, the doping of semiconductor is the essential requirement to enable efficient carrier injection from the metal to semiconductor. The NW-doping in this research is important in two aspects. First, doping the NWs up to very high level realizes the low contact resistance between the metal and a semiconductor nanowire as well as eliminate ambipolar behavior, and thereby high performance NW FETs can be realized. Secondly, for the realization of high performance NW TFETs, consisting of a gated p-i-n structure, the highly doped NW in the source region is also important to form a thinner tunnel junction between the source (n+ or p+) and the intrinsic channel junction, which increases BTBT currents. In addition, the ambipolar behavior can be controlled by the precise modulation of the drain doping concentration.

However, NW-doping is not trivial as bulk substrate doping due to NW's reduced dimensions.

To dope NWs, several doping methods have been investigated. In *situ* doping of Ge NWs, grown using the vapor-liquid-solid (VLS) mechanism, can be achieved by coflowing dopant gases, e.g. B<sub>2</sub>H<sub>6</sub> or PH<sub>3</sub>, along with the growth precursors. While high doping levels can be realized using this approach, the dopant atoms are primarily incorporated either via conformal NW growth (B<sub>2</sub>H<sub>6</sub>) or through the NW surface (PH<sub>3</sub>) rather than Au catalyst [67, 68]. This results in the entire NW being doped, with a doping concentration proportional to the exposure to the doping agent. Moreover, due to the nature of the *in situ* doping mechanism, axial doping modulation, or uniform doping concentrations are difficult to achieve.

Semiconductor doping using ion implantation, on the other hand, is a widely employed technique in semiconductor device manufacturing, as it allows for precise control of the doping level and depth, and uniform doping concentration. However, semiconductor NW doping using ion implantation is much more difficult with respect to planar, bulk devices, due to ion beam-induced damage and the resulting NW amorphization. While in the case of bulk substrates, high energy ion bombardment may cause an amorphization of the semiconductor crystal structure, the amorphized region can be recrystallized by a subsequent process with the bulk crystal structure underneath the amorphous layer serving as a template for crystal regrowth. The recrystallization of semiconductor NW after ion implantation may not always be possible however, if the entire NW body is amorphized during the ion implantation. For instance, Fig. 2-5(a) is the transmission electron micrograph (TEM) of a Ge-Si<sub>x</sub>Ge<sub>1-x</sub> core-shell NW, phosphorus-implanted (ion energy: 6 keV, dose: 10<sup>15</sup> cm<sup>-2</sup>) at a normal incidence with respect to the NW surface.

Figure 2-5: (a) Phosphorus-implantation damaged Ge-Si $_x$ Ge $_{1-x}$  core-shell nanowire (energy: 6 keV, dose:  $10^{15}$  cm $^{-2}$ ). The white-dashed line shows the boundary between the amorphized NW and the pristine NW (b) Solid-phase-epitaxy (SPE) recrystalized NW using thermal anneal.

It clearly shows that the boundary (white colored dashed line) between the amorphized region and the pristine region of the NW. In this case, the NW is not fully-amorphized and the amorphized section of the NW was recrystallized by thermal annealing at 600 °C for 3 min, using the pristine NW region as a template for NW recrystallization. [Figure 2-5(b)]

#### 2.3 DOPING OF GE-SI<sub>x</sub>Ge<sub>1-x</sub> core-shell NWs using low energy ion implantation